(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7316028号**

**(P7316028)**

(45)発行日 令和5年7月27日(2023.7.27)

(24)登録日 令和5年7月19日(2023.7.19)

|                        |              |

|------------------------|--------------|

| (51)国際特許分類             | F I          |

| H 04 N 25/70 (2023.01) | H 04 N 25/70 |

| H 04 N 25/76 (2023.01) | H 04 N 25/76 |

| H 04 N 25/63 (2023.01) | H 04 N 25/63 |

| H 04 N 25/40 (2023.01) | H 04 N 25/40 |

請求項の数 14 (全16頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2018-145411(P2018-145411) |

| (22)出願日  | 平成30年8月1日(2018.8.1)         |

| (65)公開番号 | 特開2020-22096(P2020-22096A)  |

| (43)公開日  | 令和2年2月6日(2020.2.6)          |

| 審査請求日    | 令和3年7月30日(2021.7.30)        |

|          |                                            |

|----------|--------------------------------------------|

| (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74)代理人  | 110003281<br>弁理士法人大塚国際特許事務所                |

| (72)発明者  | 石井 美絵<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

| (72)発明者  | 大下内 和樹<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内   |

| 審査官      | 鈴木 明                                       |

最終頁に続く

(54)【発明の名称】 撮像素子及びその制御方法、及び撮像装置

**(57)【特許請求の範囲】****【請求項1】**

遮光された複数の第1の画素をそれぞれ含む複数の第1の画素ブロックと、遮光されていない複数の第2の画素をそれぞれ含む複数の第2の画素ブロックとを有する画素部と、前記複数の第1の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第1の読み出し手段と、

前記複数の第2の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第2の読み出し手段と、

前記複数の第1の画素ブロックから前記複数の第1の読み出し手段に画素信号を読み出す第1の読み出し動作と、前記複数の第2の画素ブロックから前記複数の第2の読み出し手段に画素信号を読み出す第2の読み出し動作と、を制御する制御手段と、を有し、

前記制御手段は、前記第2の読み出し動作の開始に先立って、前記複数の第1の画素ブロックそれぞれに含まれる前記複数の第1の画素すべてからの画素信号の前記第1の読み出し動作を終了するように制御することを特徴とする撮像素子。

**【請求項2】**

前記制御手段は、前記複数の第1の画素と前記複数の第2の画素の電荷の蓄積動作の開始時間をずらすことで、画素信号の読み出し時における前記複数の第1の画素と前記複数の第2の画素の電荷の蓄積時間を揃えることを特徴とする請求項1に記載の撮像素子。

**【請求項3】**

遮光された複数の第1の画素をそれぞれ含む複数の第1の画素ブロックと、遮光されて

いない複数の第2の画素をそれぞれ含む複数の第2の画素ブロックとを有する画素部と、前記複数の第1の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第1の読み出し手段と、

前記複数の第2の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第2の読み出し手段と、

前記複数の第1の画素ブロックから前記複数の第1の読み出し手段に画素信号を読み出す第1の読み出し動作と、前記複数の第2の画素ブロックから前記複数の第2の読み出し手段に画素信号を読み出す第2の読み出し動作と、を制御する制御手段と、を有し、

前記制御手段は、前記第2の読み出し動作の開始に先立って、前記複数の第1の画素ブロックそれぞれに含まれる前記複数の第1の画素の内、予め決められた一部の第1の画素からの画素信号の読み出しを終了するように前記第1の読み出し動作を制御すると共に、前記予め決められた一部の第1の画素を除く第1の画素からの画素信号を、前記第2の読み出し動作と並行して行うように前記第1の読み出し動作を制御することを特徴とする撮像素子。

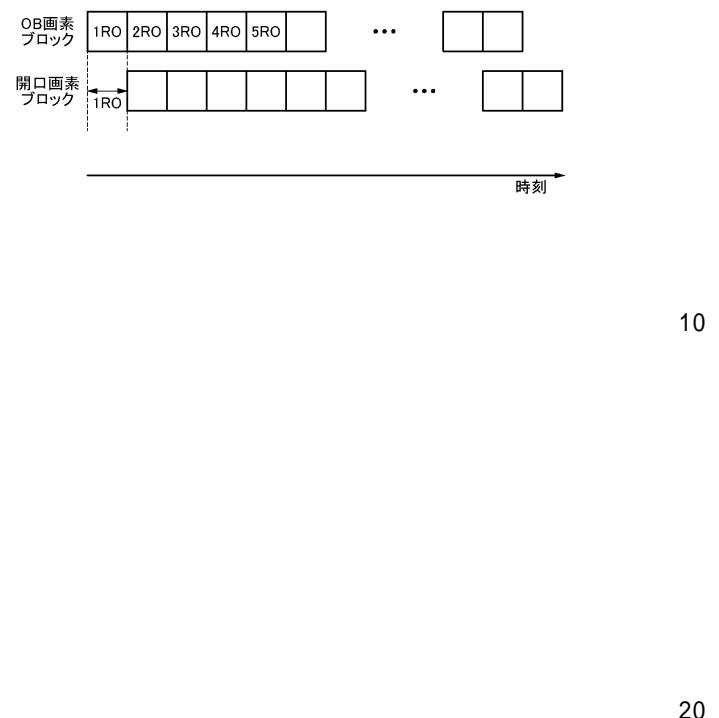

10

#### 【請求項4】

前記複数の第1の画素ブロックは、前記複数の第2の画素ブロックの周辺部に配置されていることを特徴とする請求項1乃至3のいずれか1項に記載の撮像素子。

#### 【請求項5】

遮光された複数の第1の画素をそれぞれ含む複数の第1の画素ブロックと、遮光されていない複数の第2の画素をそれぞれ含む複数の第2の画素ブロックとを有する画素部と、

前記複数の第1の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第1の読み出し手段と、

前記複数の第2の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第2の読み出し手段と、

前記複数の第1の画素ブロックから前記複数の第1の読み出し手段に画素信号を読み出す第1の読み出し動作と、前記複数の第2の画素ブロックから前記複数の第2の読み出し手段に画素信号を読み出す第2の読み出し動作と、を制御する制御手段と、を有し、

前記複数の第1の画素ブロックは、前記複数の第2の画素ブロックから成る領域の長辺部と短辺部に配置され、

前記制御手段は、前記第2の読み出し動作の開始に先立って、前記長辺部に配置された前記第1の画素ブロックそれぞれに含まれる前記複数の第1の画素すべてからの画素信号の読み出しを終了するように前記第1の読み出し動作を制御すると共に、前記短辺部に配置された前記第1の画素ブロックそれぞれに含まれる前記複数の第1の画素すべてからの画素信号を読み出す前記第1の読み出し動作を、前記第2の読み出し動作と並行して行うように制御することを特徴とする撮像素子。

20

30

#### 【請求項6】

前記第2の画素ブロックの画素信号と並行して読み出された前記第1の画素ブロックの画素信号に基づいて、前記第2の読み出し動作中の駆動信号の変動に伴う前記第2の画素ブロックの画素信号のばらつきを補正する補正手段を更に有することを特徴とする請求項3乃至5のいずれか1項に記載の撮像素子。

40

#### 【請求項7】

前記長辺部に配置された前記第1の画素ブロックの画素信号に基づいて黒レベルを補正し、前記短辺部に配置された前記第1の画素ブロックの画素信号に基づいて、前記第2の読み出し動作中の駆動信号の変動に伴う前記第2の画素ブロックの画素信号のばらつきを補正する補正手段を更に有することを特徴とする請求項5に記載の撮像素子。

#### 【請求項8】

前記第1の画素ブロックに含まれる前記複数の第1の画素の数は、前記第2の画素ブロックに含まれる前記複数の第2の画素の数よりも少ないと特徴とする請求項1乃至7のいずれか1項に記載の撮像素子。

#### 【請求項9】

前記画素部および前記制御手段と、前記複数の第1の読み出し手段および前記複数の第2の読み出し手段とが、積層された異なる基板に配置されていることを特徴とする請求項1乃至8のいずれか1項に記載の撮像素子。

**【請求項10】**

前記第2の読み出し動作の開始に先立って前記第1の読み出し動作によって読み出された画素信号に基づいて、黒レベルを補正する補正手段を更に有することを特徴とする請求項1乃至9のいずれか1項に記載の撮像素子。

**【請求項11】**

請求項1乃至9のいずれか1項に記載の撮像素子と、

前記複数の第2の画素ブロックからの画素信号の読み出し開始に先立って、前記複数の第1の画素ブロックから読み出された画素信号に基づいて、黒レベルを補正する補正手段とを有することを特徴とする撮像装置。 10

**【請求項12】**

遮光された複数の第1の画素をそれぞれ含む複数の第1の画素ブロックと、遮光されていない複数の第2の画素をそれぞれ含む複数の第2の画素ブロックとを有する画素部と、前記複数の第1の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第1の読み出し手段と、前記複数の第2の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第2の読み出し手段と、前記複数の第1の画素ブロックから前記複数の第1の読み出し手段に画素信号を読み出す第1の読み出し動作と、前記複数の第2の画素ブロックから前記複数の第2の読み出し手段に画素信号を読み出す第2の読み出し動作と、を制御する制御手段と、を有する撮像素子の制御方法であって、 20

前記第2の読み出し動作の開始に先立って、前記複数の第1の画素ブロックそれぞれに含まれる前記複数の第1の画素すべてからの画素信号の前記第1の読み出し動作を終了するように制御することを特徴とする撮像素子の制御方法。

**【請求項13】**

遮光された複数の第1の画素をそれぞれ含む複数の第1の画素ブロックと、遮光されていない複数の第2の画素をそれぞれ含む複数の第2の画素ブロックとを有する画素部と、前記複数の第1の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第1の読み出し手段と、前記複数の第2の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第2の読み出し手段と、前記複数の第1の画素ブロックから前記複数の第1の読み出し手段に画素信号を読み出す第1の読み出し動作と、前記複数の第2の画素ブロックから前記複数の第2の読み出し手段に画素信号を読み出す第2の読み出し動作と、を制御する制御手段と、を有する撮像素子の制御方法であって、 30

前記第2の読み出し動作の開始に先立って、前記複数の第1の画素ブロックそれぞれに含まれる前記複数の第1の画素の内、予め決められた一部の第1の画素からの画素信号の読み出しを終了するように前記第1の読み出し動作を制御すると共に、前記予め決められた一部の第1の画素を除く第1の画素からの画素信号を、前記第2の読み出し動作と並行して行うように前記第1の読み出し動作を制御することを特徴とする撮像素子の制御方法。

**【請求項14】**

遮光された複数の第1の画素をそれぞれ含む複数の第1の画素ブロックと、遮光されていない複数の第2の画素をそれぞれ含む複数の第2の画素ブロックとを有する画素部と、前記複数の第1の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第1の読み出し手段と、前記複数の第2の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第2の読み出し手段と、前記複数の第1の画素ブロックから前記複数の第1の読み出し手段に画素信号を読み出す第1の読み出し動作と、前記複数の第2の画素ブロックから前記複数の第2の読み出し手段に画素信号を読み出す第2の読み出し動作と、を制御する制御手段と、を有し、前記複数の第1の画素ブロックは、前記複数の第2の画素ブロックから成る領域の長辺部と短辺部に配置された撮像素子の制御方法であって、 40

前記第2の読み出し動作の開始に先立って、前記長辺部に配置された前記第1の画素ブ

10

20

30

40

50

ロックそれぞれに含まれる前記複数の第1の画素すべてからの画素信号の読み出しを終了するように前記第1の読み出し動作を制御すると共に、前記短辺部に配置された前記第1の画素ブロックそれぞれに含まれる前記複数の第1の画素すべてからの画素信号を読み出す前記第1の読み出し動作を、前記第2の読み出し動作と並行して行うように制御することを特徴とする撮像素子の制御方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、撮像素子及びその制御方法、及び撮像装置に関する。

**【背景技術】**

**【0002】**

近年、デジタル一眼レフカメラやビデオカメラに、CMOS撮像素子が多く使用されている。このCMOS撮像素子に関しては、多画素化、高速撮像化のニーズが高まっており、CMOS撮像素子の高速な読み出し技術が要求されている。

**【0003】**

CMOS撮像素子の高速化の手法としては、従来では画素アレイの列ごとに共有していたAD変換回路を、画素ごと、または比較的少数の複数画素ごとに共有するように、より多くのAD変換回路を用いる手法が知られている。

**【0004】**

例えば、特許文献1では、画素とAD変換回路を異なる基板に設けて、両基板をCu-Cu接合などにより貼り合せて接続する構成が提案されている。画素基板とAD変換回路基板とを分けることで、画素の光学特性を損なわずに、かつ比較的少数の複数画素ごとに1つのAD変換回路を有する構成を取ることができ、飛躍的に高速に画素の読み出しをすることが可能となる。

**【0005】**

また、上記のような積層構成の撮像素子として、特許文献2には、複数の画素ブロックが行列状に配置された画素基板と、各画素ブロックに対応したAD変換回路を含む複数の処理部が行列状に配置された処理基板とを備える構成が記載されている。一例として、各画素ブロックは $4 \times 4$ 画素の合計16個の画素からなり、複数の処理部は平行に動作する。

**【0006】**

ところで、撮像素子は通常、信号レベルの基準信号となる信号（黒基準信号）を得るために、光に反応しないように遮光されたオプティカルブラック画素（以下、「OB画素」と呼ぶ。）を備えている。そして、遮光されていない画素（以下、「開口画素」と呼ぶ。）から読み出された開口画素信号は、OB画素から読み出されたOB画素信号の信号レベルを基準として演算処理される。通常、画面上部（長辺部）や画面左部（短辺部）などの画面の周辺部に、数行または数列程度のOB画素が設けられる。これにより、画素信号を所定のレベルにクランプすることができ、長時間露光による暗電流や、例えば垂直方向のシェーディングなどの暗時信号を補正することができる。

**【先行技術文献】**

**【特許文献】**

**【0007】**

**【文献】特開2009-177207号公報**

特開2014-155175号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0008】**

一般的に、開口画素信号の読み出しに先立ってOB画素信号を読み出し、その後、開口画素信号を読み出しながらOB画素信号から求めた黒基準信号の信号レベルを順次補正して処理していくことが望ましい。そのため、列毎にAD変換部を備え、画素アレイの上から順次読み出すような従来のCMOS撮像素子では、開口画素領域の上部や左部にOB画

10

20

30

40

50

素を配置している。

**【0009】**

しかしながら、特許文献2のように、画素ブロックごとに処理部が対応して配置される構成の場合、開口画素の信号読み出し開始時に黒基準信号が取得できていないという課題があった。

**【0010】**

本発明は上記問題点を鑑みてなされたものであり、複数の画素ブロックから並行して信号を読み出し可能な撮像素子において、遮光画素の信号を用いた処理を、読み出した画像信号に対して順次行えるように読み出し制御することを目的とする。

**【課題を解決するための手段】**

10

**【0011】**

上記目的を達成するために、本発明の撮像素子は、遮光された複数の第1の画素をそれぞれ含む複数の第1の画素ブロックと、遮光されていない複数の第2の画素をそれぞれ含む複数の第2の画素ブロックとを有する画素部と、前記複数の第1の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第1の読み出し手段と、前記複数の第2の画素ブロックそれぞれに対して設けられ、それぞれA/D変換手段を備える複数の第2の読み出し手段と、前記複数の第1の画素ブロックから前記複数の第1の読み出し手段に画素信号を読み出す第1の読み出し動作と、前記複数の第2の画素ブロックから前記複数の第2の読み出し手段へ画素信号を読み出す第2の読み出し動作と、を制御する制御手段と、を有し、前記制御手段は、前記第2の読み出し動作の開始に先立って、前記複数の第1の画素ブロックそれぞれに含まれる前記第1の画素すべてからの画素信号の第1の読み出し動作を終了するように制御する。

20

**【発明の効果】**

**【0012】**

本発明によれば、複数の画素ブロックから並行して信号を読み出し可能な撮像素子において、遮光画素の信号を用いた処理を、読み出した画像信号に対して順次行えるように読み出し制御することができる。

**【図面の簡単な説明】**

**【0013】**

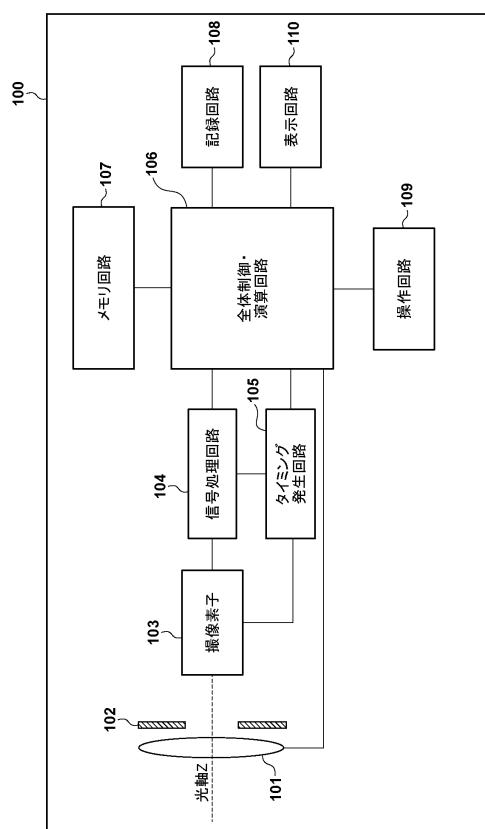

**【図1】**本発明の実施形態における撮像装置の概略構成を示すブロック図。

30

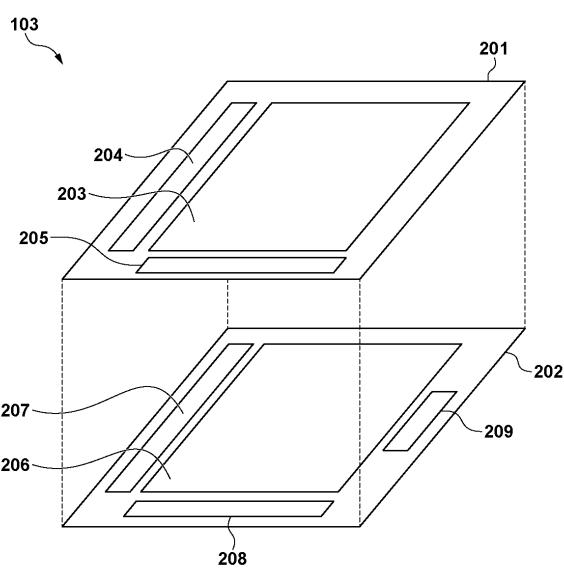

**【図2】**実施形態における撮像素子の構成例を示す模式図。

**【図3】**実施形態における撮像素子の構成例を示す平面図。

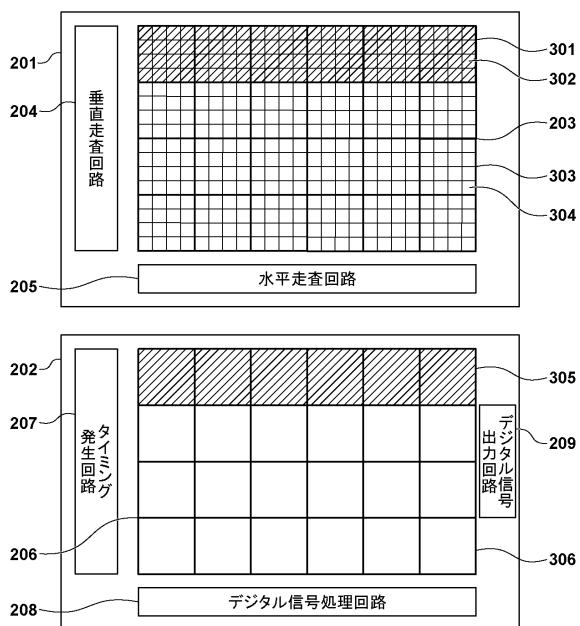

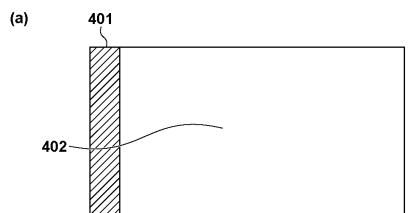

**【図4】**実施形態における撮像素子の画素領域の構成例を示す図。

**【図5】**実施形態における撮像素子の画素と読み出し回路の構成を示す図。

**【図6】**実施形態における画素の画素信号の読み出し動作の一例を示すタイミングチャート。

**【図7】**第1の実施形態における撮像素子の読み出し制御を示す図。

**【図8】**第1の実施形態の信号処理回路におけるクランプ処理を説明する図。

**【図9】**第1の実施形態の変形例における撮像素子の他の読み出し制御を示す図。

**【図10】**第2の実施形態における撮像素子の読み出し制御を示す図。

40

**【発明を実施するための形態】**

**【0014】**

以下、添付図面を参照して本発明を実施するための形態を詳細に説明する。ただし、本形態において例示される構成部品の寸法、形状、それらの相対配置などは、本発明が適用される装置の構成や各種条件により適宜変更されるべきものであり、本発明がそれらの例示に限定されるものではない。

**【0015】**

<第1の実施形態>

図1は、本発明の実施形態における撮像装置100の概略構成を示すブロック図である。図1において、撮像装置100の撮像光学系は、撮像レンズ101及び絞り102を備

50

える。撮像レンズ 101 及び絞り 102 を通過した光は、撮像レンズ 101 の焦点位置近傍に結像する。なお、撮像レンズ 101 は、1 枚のレンズとして図示しているが、実際には複数のレンズから成るレンズ群で構成される。撮像素子 103 は CMOS 撮像素子であり、撮像レンズ 101 により結像された被写体像を光量に応じて電気信号に変換し、更に、データ処理可能な画像信号に変換する機能を有する。信号処理回路 104 は、撮像素子 103 から出力される画像信号に対して、信号增幅、基準レベル調整等の各種の補正や、データの並べ替えなどを行う。なお、基準レベル調整等、一部の信号処理機能は、撮像素子 103 の中に設けても良い。タイミング発生回路 105 は撮像素子 103 や信号処理回路 104 に駆動タイミング信号を出力する。

#### 【0016】

10

全体制御・演算回路 106 は、撮像素子 103 や信号処理回路 104 などを含む撮像装置 100 全体の統括的な駆動及び制御を行う。また、信号処理回路 104 から出力された画像信号に対して、所定の画像処理や欠陥補正等を施す。メモリ回路 107 及び記録回路 108 は、全体制御・演算回路 106 から出力された画像信号等を記録保持する不揮発性メモリあるいはメモリカード等の記録媒体である。操作回路 109 は撮像装置 100 に備え付けられた操作部材からの信号を受け付け、全体制御・演算回路 106 に対してユーザーの命令を反映する。表示回路 110 は撮影後の画像やライブビュー画像、各種設定画面等を表示する。

#### 【0017】

20

次に、撮像素子 103 の構成について、図 2 から図 4 を用いて説明する。図 2 及び図 3 は、本発明の実施形態における撮像素子 103 の構成例を示す図である。図 2 において、撮像素子 103 は、画素領域基板 201 と読み出し回路基板 202 を積層させた構成を有する。各基板の配線は、シリコン貫通電極等を用いて電気的に接続される。画素領域基板 201 は、画素領域 203 と、画素を駆動して走査する垂直走査回路 204 と、水平走査回路 205 とを備える。読み出し回路基板 202 は、複数の読み出し回路からなる読み出し領域 206、タイミング発生回路 (TG) 207、デジタル信号処理回路 208、デジタル信号出力回路 209 を備える。

#### 【0018】

30

次に、上記構成を有する撮像素子 103 を構成する各ブロックについて、図 3 を参照して詳細に説明する。画素領域基板 201 上にある画素領域 203 は、光学的に遮光されたオプティカルブラック (OB) 領域 (網掛けで示す領域) と、被写体像を受光する開口領域とから構成される。ここでは、開口領域の上部 (長辺部) に数行程度の OB 領域が配置された構成となっている。OB 領域には、遮光された画素 302 (以下、「OB 画素 302」と呼ぶ。) が行列状に配置され、開口領域には、遮光されていない画素 304 (以下、「受光画素 304」と呼ぶ。) が行列状に配置されている。OB 領域に配されている OB 画素 302 から読み出された画素信号は、基準信号レベルへのクランプ処理のための補正值の取得に用いられる。

#### 【0019】

ここで、図 3 において太枠で囲まれた、OB 画素 302 が  $4 \times 4$  画素の合計 16 個配置された画素ブロックを、OB 画素ブロック 301 と呼ぶ。同様に、受光画素 304 が  $4 \times 4$  画素の合計 16 個配置された画素ブロックを、開口画素ブロック 303 と呼ぶ。なお、図 3 に示すように、画素ブロックが OB 領域と開口領域を跨ぐことは無く、互いに別々の画素ブロックに分かれるように配置する。すなわち、OB 領域は、OB 画素ブロック 301 のみを含み、開口領域は開口画素ブロック 303 のみを含む。

40

#### 【0020】

一方、読み出し回路基板 202 には、読み出し回路 305, 306 が行列状に配置されている。読み出し回路 305, 306 はそれぞれ、対応した位置に配された画素ブロック (OB 画素ブロック 301、開口画素ブロック 303) に接続され、対応する画素ブロックから並行に出力される画素信号を、並行に処理することができる。なお、読み出し回路 305, 306 は同じ構成を有するが、説明の都合上、OB 画素ブロック 301 に接続さ

50

れている読み出し回路をO B画素読み出し回路305、開口画素プロック303に接続されている読み出し回路を開口画素読み出し回路306と呼ぶ。

#### 【0021】

対応する画素プロックと読み出し回路の位置関係について、簡単に説明する。例えば、図3における $6 \times 4$ 個の画素プロックのうち、画素領域基板201上の一一番左上のO B画素プロック301は、読み出し回路基板202上の一一番左上にあるO B画素読み出し回路305に接続されている。以下、同様にそれぞれ対応するプロックが接続される。このように接続されることにより、画素部からの出力線を短くすることができ、出力線の配線抵抗を増やさずに撮像素子103を構成することができる。

#### 【0022】

TG207は、垂直走査回路204や水平走査回路205、及びO B画素読み出し回路305、開口画素読み出し回路306や、デジタル信号処理回路208、デジタル信号出力回路209に信号を送り、その駆動を制御する。

#### 【0023】

垂直走査回路204、水平走査回路205は、画素領域203の画素それぞれに駆動信号を送り、画素の電荷リセットや蓄積、転送、読み出し回路への出力等の駆動を制御する。O B画素読み出し回路305及び開口画素読み出し回路306は、TG207からの制御により、それぞれ対応する画素プロックの各画素(O B画素302、受光画素304)の出力信号を受け取って、アナログデジタル変換(AD変換)を行う。そして、デジタル信号処理回路208を介して、デジタル信号出力回路209より、撮像素子103の外部に順次出力される。

#### 【0024】

なお、説明の簡略化のために、図3では、O B画素プロック301及び開口画素プロック303は、それぞれ $4 \times 4 = 16$ 個の画素からなる構成を示しているが、本発明はこれに限られるものではない。また、画素プロック及び読み出し回路として、それぞれ $6 \times 4 = 24$ 個を記載しているが、実際の撮像素子103は数千～数万個の画素プロック及び読み出し回路からなる。

#### 【0025】

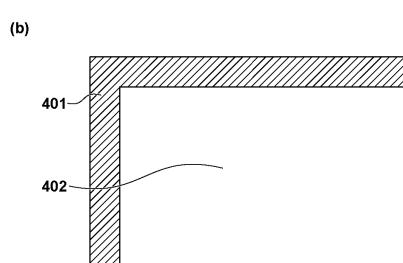

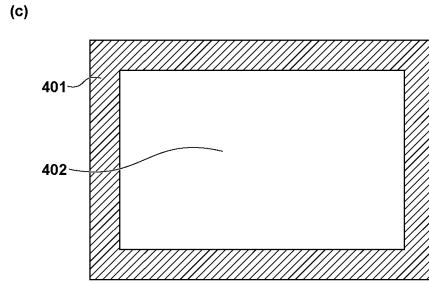

また、画素領域203におけるO B領域と開口領域の配置も、図3の構成に限られるものではない。図4は、画素領域203におけるO B領域と開口領域の配置の他の配置例を示す図である。図4(a)は、開口領域402の左部(短辺部)に数列程度のO B領域401を配置した構成である。また、図4(b)のように、上部(長辺部)及び左部(短辺部)に数行、数列程度のO B領域401を配置した構成、また、図4(c)のように、周囲を囲むように(周辺部に)数行、数列程度のO B領域401を配置した構成であっても良い。また、これら以外の配置であってもよい。

#### 【0026】

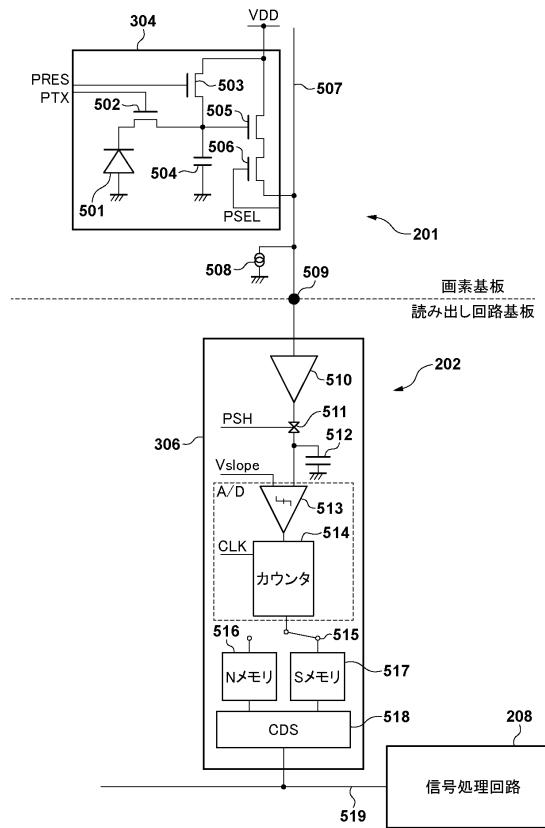

図5は、撮像素子103の受光画素304と開口画素読み出し回路306の構成を示す図である。図の簡略化のため、図5では、1つの画素と1つの読み出し回路のみを示しているが、O B画素302とO B画素読み出し回路305も同様の構成となる。画素領域基板201に形成された受光画素304は、シリコン貫通電極509を介して、読み出し回路基板202に形成された開口画素読み出し回路306に接続される。

#### 【0027】

受光画素304において、フォトダイオード(PD)501(光電変換部)は、撮像レンズ101によって結像された被写体像を受けて電荷を発生し、発生した電荷を蓄積する。PD501で蓄積された電荷は、転送MOSトランジスタ(転送スイッチ)502を介して電荷保持部であるフローティングディフェュージョン部(FD)504に転送される。FD504に転送された電荷は、選択スイッチ506がオンされると、ソースフォローアンプを形成する増幅MOSトランジスタ(SF)505を介して電荷に対応した電圧として出力線507に出力される。出力線507には電流源508が接続されている。

#### 【0028】

10

20

30

40

50

なお、選択スイッチ 506 は垂直走査回路 204 及び水平走査回路 205 の制御により、画素ブロック単位で制御され、各画素ブロックから選択された画素の画素信号が同時に各出力線 507 に出力される。リセットMOSトランジスタ(リセットスイッチ)503 は、FD504 の電位、及び、転送スイッチ 502 を介して PD501 の電位を VDD にリセットする。転送スイッチ 502、リセットスイッチ 503、選択スイッチ 506 は、それぞれ、不図示の垂直走査回路 204 に接続されている信号線を介して制御信号 PTEX、PRES、PSEL により制御される。垂直走査回路 204 からの信号線は行単位で制御可能であり、更に水平走査回路 205 によるオン、オフを制御する信号線を接続して制御することにより、画素ブロック内の所定の画素の駆動を制御することができる。

#### 【0029】

次に、開口画素読み出し回路 306 の回路構成について説明する。アンプ 510 は、出力線 507 に現れた信号を増幅し、容量 512 は信号電圧を保持するために用いられる。容量 512 への書き込みは、制御信号 PSH によりオン、オフされるスイッチ 511 により制御される。比較器 513 の一方の入力には、不図示のスロープ電圧発生回路から供給された参照電圧である Vslope が入力され、他方の入力には、容量 512 に書き込まれたアンプ 510 の出力が入力される。比較器 513 はアンプ 510 の出力と参照電圧 Vslope を比較し、その大小関係によってローレベル、ハイレベルの 2 値のいずれかを出力する。具体的には、参照電圧 Vslope がアンプ 510 の出力に対して小さい時にはローレベル、大きい時にはハイレベルを出力する。参照電圧 Vslope の遷移開始と同時に CLK が動き出し、カウンタ 514 は比較器 513 の出力がハイレベルの時に CLK に対応してカウントアップし、比較器 513 の出力がローレベルに反転すると同時にカウントを停止する。

#### 【0030】

Nメモリ 516 には、FD504 のリセットレベルの信号(以下、「N信号」と呼ぶ。)を A/D 変換したデジタル信号が保持される。また、Sメモリ 517 には、PD501 の信号を FD504 の N 信号に重畠した信号(以下、「S+N信号」と呼ぶ。)を A/D 変換したデジタル信号が保持される。Nメモリ 516、Sメモリ 517 のどちらに書き込まれるかはスイッチ 515 により振り分けられる。

#### 【0031】

CDS 回路 518 は、上述したように、Sメモリ 517 に保持された S+N 信号から N メモリ 516 に保持された N 信号を差分し、リセットノイズ成分が除去された S 信号(光信号)を得る。S 信号は、TG207 の制御により、デジタル信号出力線 519 を介してデジタル信号処理回路 208 へ出力される。そして、クランプ等の演算処理が行われた後、デジタル信号出力回路 209 を介して撮像素子 103 の外部に出力される。

#### 【0032】

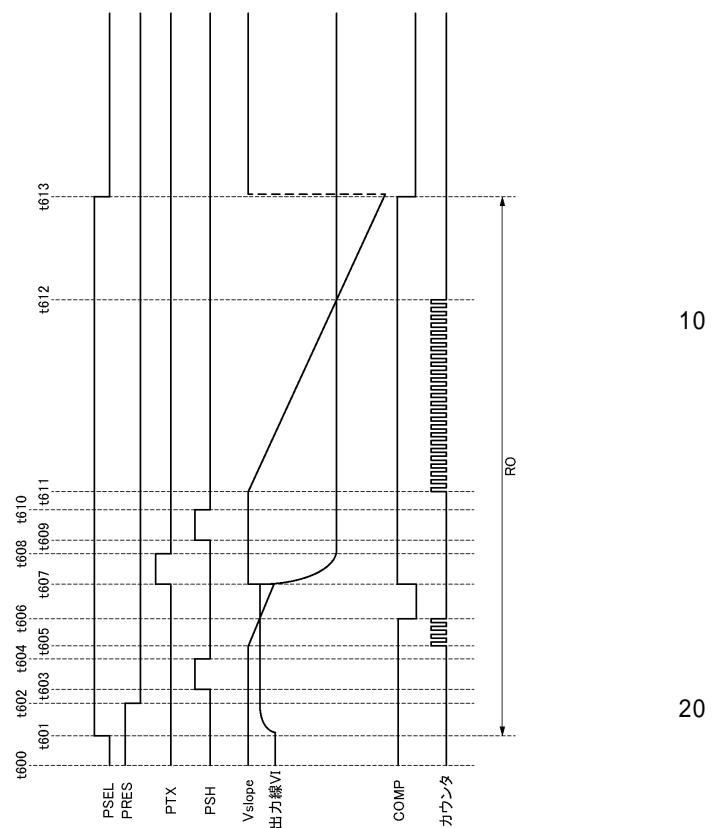

図 6 は、図 5 に示す回路構成を有する撮像素子 103 の画素(OB 画素 302、受光画素 304)からの、画素信号の読み出し動作の一例を示すタイミングチャートである。各駆動パルスのタイミング、参照電圧 Vslope、カウンタを示している。また、各タイミングにおける、アンプ 510 より出力された電位 V1 もあわせて示している。COMP は比較器 513 の出力レベルを示す。

#### 【0033】

PD501 からの信号の読み出しに先立って、リセットスイッチ 503 の制御信号 PRES が Hi となる(t600)。これによって、SF505 のゲートがリセット電源電圧にリセットされる。時刻 t601 で制御信号 PSEL を Hi とし、SF505 を動作状態とする。そして、時刻 t602 で制御信号 PRES を Lo とすることで FD504 のリセットを解除する。このときの FD504 の電位を出力線 507 にリセット信号レベル(N 信号)として読み出し、読み出し回路(OB 画素読み出し回路 305、開口画素読み出し回路 306)に入力する。時刻 t603、t604 で制御信号 PSH を Hi、Lo としてスイッチ 511 をオン、オフすることにより、出力線 507 に読み出された N 信号はアンプ 510 で所定のゲインで増幅された後、容量 512 に保持される。容量 512 に保持さ

10

20

30

40

50

れたN信号の電位は比較器513の一方の端子に入力される。

#### 【0034】

時刻t604でスイッチ511がオフされた後、時刻t605から時刻t607まで、不図示のスロープ電圧発生回路は、参照電圧Vslopeを時刻と共に初期値から減少させていく。時刻t605の参照電圧Vslopeの遷移開始と共に、CLKをカウンタ514に供給し、カウンタ514の値はCLKの数に応じて増加していく。そして、比較器513に入力された参照電圧VslopeがN信号と同じレベルになると、比較器513の出力COMPはローレベルとなり（時刻t606）、同時にカウンタ514の動作も停止する。この、カウンタ514の動作が停止した時のカウント値が、N信号がAD変換された値となり、Nメモリ516に保持される。

10

#### 【0035】

次に、デジタル化されたN信号をNメモリ516に保持した後の時刻t607、t608で制御信号PTXを順次Hi、LoとしてPD501に蓄積された光電荷をFD504に転送する。すると、電荷量に応じたFD504の電位変動が出力線507にS+N信号（光成分+リセットノイズ成分）として読み出され、読み出し回路（OB画素読み出し回路305、開口画素読み出し回路306）に入力される。S+N信号はアンプ510で所定のゲインで增幅された後、時刻t609、t610で制御信号PSHを順次Hi、Loとしてスイッチ511をオン、オフすることにより容量512に保持される。容量512に保持された電位は比較器513の一方の端子に入力される。

20

#### 【0036】

時刻t610でスイッチ511がオフされた後、時刻t611から時刻t613まで、付図示のスロープ電圧発生回路は、参照電圧Vslopeを時刻と共に初期値から減少させていく。時刻t611の参照電圧Vslopeの遷移開始と共に、CLKをカウンタ514に供給し、カウンタ514の値はCLKの数に応じて増加していく。そして、比較器513に入力された参照電圧VslopeがS+N信号と同じレベルになると、比較器513の出力COMPはローレベルとなり（時刻t612）、同時にカウンタ514の動作も停止する。この、カウンタ514の動作が停止した時のカウント値が、S+N信号がAD変換された値となり、Sメモリ517に保持される。

20

#### 【0037】

上述した時刻t601からt613までの時間ROが、画素（OB画素302、受光画素304）の画素信号を読み出す時間である。この読み出し駆動を画素ブロック（OB画素ブロック301、開口画素ブロック303）を構成する画素数分繰り返すことにより、1フレーム分の読み出しが完了する。

30

#### 【0038】

しかし、全画素ブロックに対して、同時に上記の読み出し動作を行った場合、開口画素ブロック303の最初の画素読み出し時に、黒基準信号が取得することができないため、デジタル信号処理回路208にてクランプ処理を行うことができない。

#### 【0039】

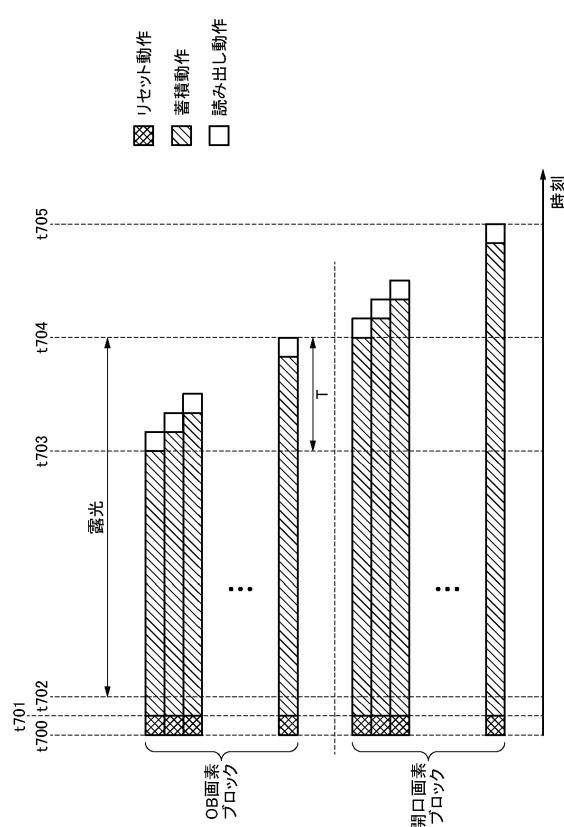

そこで、本発明の第1の実施形態による電荷蓄積及び画素信号の読み出し駆動について、図7を用いて説明する。図7は、画素領域を構成するすべてのOB画素ブロック301と開口画素ブロック303の動作例を模式的に表した図であり、横軸は時刻を示している。第1の実施形態は、OB画素ブロック301と開口画素ブロック303とで、画素信号の読み出し動作のタイミングをずらすことを特徴とする。

40

#### 【0040】

撮影の開始に伴い、時刻t700において、全画素のリセット動作を行う。ここでは、垂直走査回路204が、制御信号PRES、PTXを全行についてONすることで、一括リセット動作を行う。一括リセットの後、制御信号PRES、PTXを全行についてOFFすることで、時刻t701より全画素同時に蓄積動作が開始される。そして、時刻t702で不図示のシャッタが開くことにより、露光が開始する。ここでは、シャッタが閉じる時刻t704までが開口領域の露光時間となり、ここで蓄積動作を終了して、以降、開

50

口画素ブロック 303 からの画素信号の読み出しが開始される。一方、開口画素ブロック 303 の蓄積動作の終了時刻  $t_{704}$  に先立って、時刻  $t_{703}$  より OB 画素ブロック 301 の画素信号の読み出し動作を行う。

#### 【0041】

画素の読み出し駆動は、図 6 で示したタイミングチャートに従うことで実施でき、1 画素の読み出しが終わったら、順次、次の画素の読み出しを行うことで、各 OB 画素ブロック 301 を構成する OB 画素 302 の画素信号を順次読み出していく。

#### 【0042】

ここで、時刻  $t_{703}$  は、OB 画素 302 の 1 つの画素信号の読み出しにかかる時間 ( $R_O$ )  $\times$  OB 画素ブロック 301 を構成する画素数 (図 4 の例では 16 画素) の時間に相当する時間  $T$  だけ、時刻  $t_{704}$  よりも前にする。このように制御することで、開口画素ブロック 303 の画素信号の読み出しを開始する前に、OB 画素ブロックの画素信号の読み出しを終了することができる。そして、前もって読み出された OB 画素ブロック 301 の画素信号から、デジタル信号処理回路 208 にて黒基準信号を演算することで、開口画素ブロック 303 の画素信号の読み出し時にクランプ処理を行うことができる。なお、クランプ処理に関しては後述する。

10

#### 【0043】

なお、通常、蓄積時間の間は読み出し回路の駆動スイッチをオフしてパワーを落とし、読み出し動作開始前に読み出し回路を駆動させる省電駆動を行う。本実施形態においては、OB 画素読み出し回路 305 と開口画素読み出し回路 306 の駆動スイッチを別々に制御し、OB 画素読み出し回路 305 を先に省電駆動から復帰させる。

20

#### 【0044】

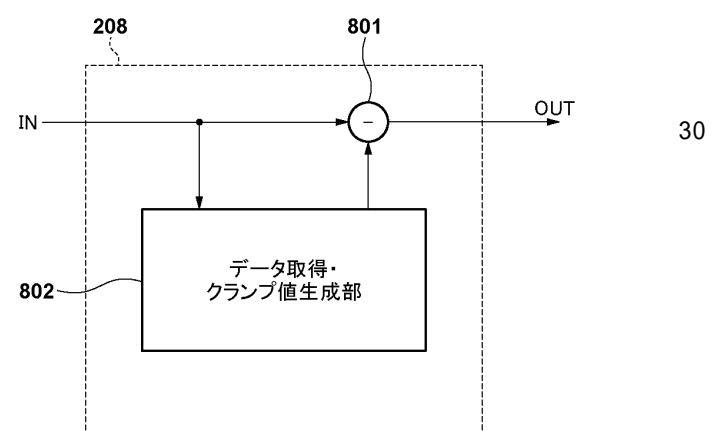

続いて、図 8 を用いて、デジタル信号処理回路 208 における、クランプ処理について説明する。OB 画素読み出し回路 305 及び開口画素読み出し回路 306 より送られた画素信号は、図 8 の IN より入力される。TG 207 からの制御信号に基づいて、OB 画素ブロック 301 の画素信号が入力された場合には、データ取得・クランプ値生成部 802 に画素信号が送られる。データ取得・クランプ値生成部 802 にて OB 領域の画素信号の平均化処理を行い、黒基準信号を算出する。例えば、全 OB 画素ブロック 301 の画素信号の平均化処理を行い、黒基準信号を算出し、これを元にクランプ値を算出する。

30

#### 【0045】

そして、開口画素ブロック 303 の画素信号が読み出されてデジタル信号処理回路 208 に入力されると、減算回路 801 にてクランプ値の減算処理を行う。これにより、暗電流等の影響による黒レベルのずれ分を取り除き、画素信号の黒レベルを黒基準信号に合わせることができる。

#### 【0046】

上記の通り第 1 の実施形態によれば、開口領域の画素信号の読み出しに先立って、OB 領域の画素信号を読み出すことにより、適切にクランプ処理を行うことができる。なお、本第 1 の実施形態においては撮像素子 103 が有するデジタル信号処理回路 208 にてクランプ処理を行ったが、撮像装置が有する信号処理回路 104 にて行っても良い。

40

#### 【0047】

また、図 3 に示す例では、OB 画素ブロック 301 を構成する OB 画素 302 の画素数と開口画素ブロック 303 を構成する受光画素 304 の画素数は同じであるが、必ずしも同じでなくても良い。例えば、OB 画素ブロック 301 を構成する画素 302 の画素数を開口画素ブロック 303 を構成する受光画素 304 の画素数よりも少なくすれば、より少ないタイムラグで、開口領域の画素信号を読み出すことができる。その場合、画素のサイズを変えずに、例えば、 $2 \times 4$  画素にするなど、単純に OB 画素ブロック 301 を構成する画素 302 の画素数を少なくしても良いし、画素のサイズを大きくすることで、画素数を少なくしてもよい。また、両方を組み合わせてもよい。

#### 【0048】

< 第 1 の実施形態の変形例 >

50

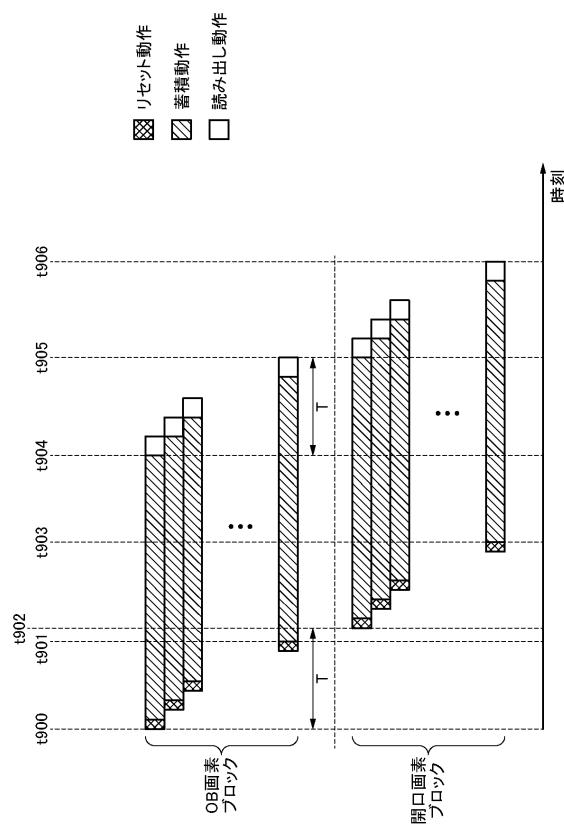

図9は、撮像素子103の別の動作例を模式的に表した図である。図7に示した動作の場合、OB画素ブロック301のOB画素302と、開口画素ブロック303の受光画素304の蓄積時間に、わずかではあるが差が生じてしまう。高温撮影時など、暗電流が多くなる状態での撮影においては、暗電流量差が生じ、正しく黒基準信号を取得できない可能性もある。また、全画素一括でリセットを行っているため、同じ画素ブロック内の画素においても蓄積時間にわずかな違いが生じる。シャッタを用いた静止画撮影では、シャッタで遮光することで蓄積時間の違いをわずかに抑えることができる。これに対し、シャッタを使用しない動画撮影などでは、通常、リセット動作のタイミングをずらして露光時間及び蓄積時間を揃える、所謂ローリング駆動を行う。

#### 【0049】

そこで、図9に示す動作では、ローリング駆動を行うと共に、OB画素ブロック301の画素信号の読み出しにかかる時間Tだけ、OB画素ブロック301のリセットを早める。つまり、時刻t900からt901において、垂直走査回路204によって、OB画素ブロック301のOB画素302に対してのみ、制御信号PRES、PTXを送ることで、リセット動作を行う。更に、各画素の読み出し開始時間を考慮して、リセット動作の開始時間をずらす。リセット動作の後、順次OB画素ブロック301のOB画素302の蓄積動作が開始される。そして、時刻t900から時間T経過した後、時刻t902からt903において、開口画素ブロック303の受光画素304のリセット動作を行い、それ受光画素304の蓄積動作を開始する。以下、図7での説明と同様に、所定の蓄積時間が経過した後、時刻t904からOB画素ブロック301の画素信号の読み出しを行い、時刻t905から開口画素ブロック303の画素信号の読み出しを開始する。

10

#### 【0050】

このように、OB領域の画素信号読み出しにかかる時間分だけ、前もってリセット、蓄積動作を開始することにより、OB領域と開口領域の蓄積時間を揃えることが可能となる。

#### 【0051】

##### <第2の実施形態>

次に、本発明の第2の実施形態について説明する。第2の実施形態では、OB画素信号を用いて、画素信号読み出し動作時の電源やGNDの変動などの影響による黒レベルのずれを補正する方法について説明する。一般的に、撮像素子に供給する各種基準電源やGNDは共通であり、画素信号の読み出し動作中にこれらの電源やGNDが変動すると、その際に読み出されていた画素の信号はほぼ一様のレベル差が生じる。このレベル差を補正しないと、パターンノイズとなって出力画像の画質が劣化してしまう。

30

#### 【0052】

図10は、第2の実施形態による画素信号の読み出し駆動の動作例を模式的に表した図である。第2の実施形態においては、OB画素ブロック301の画素信号を先に読み始めるとともに、開口画素ブロック303の画素信号の読み出し時にもOB画素ブロック301の画素信号を読み出す。図10の1つの は図6で示した1画素の読み出し時間(R0)に相当し、各画素ブロックにおける画素の読み出し動作を示している。

#### 【0053】

本第2の実施形態では、図10に示すように、例えば、1画素の読み出し時間分だけOB画素ブロック301の画素信号を先に読み出す。そして、この先に読み出したOB画素ブロックの画素信号を用いて、デジタル信号処理回路208にて主に暗電流成分のクランプを行う。以下、このクランプ処理を「暗電流補正」と呼ぶ。より具体的には、複数のOB画素ブロック301からそれぞれ1つのOB画素302を読み出し、得られた複数の画素信号を演算して、暗電流補正の補正值として使用する。

40

#### 【0054】

一方、開口画素ブロック303の画素信号と同じタイミングで読み出したOB画素ブロック301の画素信号を、その同じタイミングで読み出した開口画素ブロック303の画素信号のクランプに使用する。この処理は、画素信号の読み出し動作中における電源やGNDの変動を補正するための処理で、以下、「読み出し時変動レベル補正」と呼ぶ。なお

50

、同じタイミングで読み出した画素信号をデジタル信号処理回路 208 に送る際には、O B 画素ブロック 301 の画素信号を優先する。そして、暗電流補正と同様に、複数の O B 画素ブロック 301 からそれぞれ読み出された複数の O B 画素 302 の画素信号に基づいて、読み出し時変動レベル補正の補正值を算出して使用する。

#### 【0055】

なお、暗電流補正のために開口領域 402 より先に読み出す O B 画素ブロック 301 の画素数は、画素ブロックあたり 1 画素に限定する必要はなく、更に多くても良い。暗電流補正のクランプ値算出に使用する画素数が多いほど、精度良く補正值を算出することができる。この場合、O B 画素ブロック 301 を構成する画素の数は、暗電流補正の補正值の算出に使用する画素の分、多くするのが好適である。例えば、図 3 では O B 画素ブロック 301 は、開口画素ブロック 303 と同じ 16 画素から成っているが、縦 5 行、横 4 列の 20 画素とし、4 画素分の画素信号を開口領域 402 より先に O B 画素ブロック 301 から読み出すようにしても良い。

#### 【0056】

読み出し時変動レベル補正に使用するクランプ値は、同じタイミングで読み出された複数の O B 画素ブロック 301 の画素信号から平均値を算出した結果を元に算出し、開口領域の画素信号の補正を行う。なお、この際、O B 領域を大きく取れれば良いが、撮像素子 103 の面積が大きくなってしまうため、O B 領域はそれほど大きくできず、読み出し時変動レベル補正用の画素信号を得るために O B 画素 302 の数をそれほど多くすることは通常困難である。その場合、読み出し時のノイズが大きいと補正值の誤差が大きくなる可能性がある。そこで、例えば、暗電流補正に使用した黒レベルとの差分から変動レベルを演算し、更に誤補正にならないよう、補正係数をかけてクランプに使用しても良い。

#### 【0057】

また、撮像素子 103 のレイアウトによっては、画素領域の暗時信号が水平方向や垂直方向にシェーディングをもつ場合もある。この場合、そのシェーディングの特徴に応じて、水平方向や垂直方向が同じ位置に配置された O B 画素の画素信号を用いて開口領域の画素信号を補正しても良い。

#### 【0058】

このように、開口領域の画素信号の読み出しに先立って、O B 領域の画素信号を読み出し、かつ、開口領域と同じタイミングでも O B 領域の画素信号を読み出して補正值の算出に用いることにより、適切にクランプ処理を行うことができる。

#### 【0059】

##### (第 2 の実施形態の変形例)

次に、本発明の第 2 の実施形態の変形例について説明する。図 4 (b) のような画素配置の撮像素子 103 において、開口領域 402 の上部（長辺部）に配置された O B 領域 401（以下、V O B）の画素信号は図 7 や図 9 に従って駆動する。また、開口領域 402 の左部（短辺部）に配置された O B 領域 401（以下、H O B）の画素信号は、開口領域 402 と同じタイミングで読み出しを行う。そして、先に読み出された V O B の画素信号を用いて暗電流補正を行い、開口領域 402 と同じタイミングで読み出された H O B の画素信号を用いて、読み出し時変動レベルの補正を行ってもよい。

#### 【符号の説明】

#### 【0060】

103：撮像素子、104：信号処理回路、105：タイミング発生回路、106：全体制御・演算回路、201：画素領域基板、202：読み出し回路基板、203：画素領域、204：垂直走査回路、205：水平走査回路、206：読み出し領域、207：タイミング発生回路、208：デジタル信号処理回路、301：O B 画素ブロック、302：O B 画素、303：開口画素ブロック、304：受光画素、305：O B 画素読み出し回路、306：開口画素読み出し回路

10

20

30

40

50

## 【図面】

## 【図 1】

## 【図 2】

10

20

## 【図 3】

## 【図 4】

30

40

50

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

---

フロントページの続き

(56)参考文献      特開2009-105756(JP,A)

特開2008-219293(JP,A)

特開2015-126043(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H04N 25/00 - 25/79