## (12)发明专利申请

(10)申请公布号 CN 109871235 A

(43)申请公布日 2019.06.11

(21)申请号 201910143641.5

(22)申请日 2007.09.21

(30)优先权数据

11/525420 2006.09.22 US

(62)分案原申请数据

200710170152.6 2007.09.21

(71)申请人 英特尔公司

地址 美国加利福尼亚州

(72)发明人 R.埃克索哈 S.斯托里

(74)专利代理机构 中国专利代理(香港)有限公司 72001

代理人 张凌苗 刘春元

(51)Int.Cl.

G06F 9/302(2006.01)

权利要求书7页 说明书8页 附图5页

(54)发明名称

响应指令执行舍入运算

(57)摘要

在一个实施例中，本发明包括一种方法，用于在处理器中接收舍入指令和立即值，确定立即值的舍入模式替换指示符是否有效，并且如果是这样的话，则在处理器的浮点单元中，响应该舍入指令并且根据在立即操作数中规定的舍入模式，以源操作数执行舍入运算。对其他的实施例进行了描述并要求其权益。

1. 一种处理器，包括：

多个寄存器，其包括第一寄存器和第二寄存器；

控制寄存器，其具有第一字段以指示当前浮点舍入模式以及第二字段以指示非正常是否被转换为零；

状态寄存器，其具有第三字段以存储值，所述值指示不精确异常是否已经发生；

控制单元，其用于接收舍入指令并且用于对舍入指令的字段解码，舍入指令用于识别第一寄存器，所述第一寄存器用于存储具有多个封装的双精度浮点值的源操作数，所述舍入指令用于指示使用当前浮点舍入模式，并且所述舍入指令用于指示抑制状态寄存器的第三字段的值的改变；以及

执行单元，其耦合至控制单元，并且耦合至多个寄存器，所述执行单元响应于舍入指令而：

当第二字段指示所述非正常被转换为零时将源操作数的非正常转换为零；

根据当前浮点舍入模式执行舍入运算，以生成对应于源操作数的封装的双精度浮点值的整数值化的封装的双精度浮点值；以及

在第二寄存器中存储整数值化的封装的双精度浮点值。

2. 如权利要求1所述的处理器，其中舍入指令的比特在舍入指令指示抑制状态寄存器的第三字段的值的改变时具有一的值。

3. 如权利要求1所述的处理器，其中当前浮点舍入模式是以下之一：

向负无穷舍入；

向正无穷舍入；

舍入到零；以及

舍入到最接近的偶数。

4. 如权利要求1所述的处理器，其中舍入指令包括在具有第二舍入指令的指令集体体系结构(ISA)中以指示封装数据寄存器存储标量值，并且其中第二舍入指令使得处理器对标量值执行舍入运算以生成整数值化的浮点值。

5. 一种系统，包括：

存储器控制器；以及

处理器核，其耦合至存储器控制器，所述处理器核包括：

多个寄存器，其包括第一寄存器和第二寄存器；

控制寄存器，其具有第一字段以指示当前浮点舍入模式以及第二字段以指示非正常是否被转换为零；

状态寄存器，其具有第三字段以存储值，所述值指示不精确异常是否已经发生；

控制单元，其用于接收舍入指令并且用于对舍入指令的字段解码，舍入指令用于识别第一寄存器，所述第一寄存器用于存储具有多个封装的双精度浮点值的源操作数，所述舍入指令用于指示使用当前浮点舍入模式，并且所述舍入指令用于指示抑制状态寄存器的第三字段的值的改变；以及

执行单元，其耦合至控制单元，并且耦合至多个寄存器，所述执行单元响应于舍入指令而：

当第二字段指示所述非正常被转换为零时将源操作数的非正常转换为零；

根据当前浮点舍入模式执行舍入运算,以生成对应于源操作数的封装的双精度浮点值的整数值化的封装的双精度浮点值;以及

在第二寄存器中存储整数值化的封装的双精度浮点值。

6. 如权利要求5所述的系统,其中舍入指令的比特在舍入指令指示抑制状态寄存器的第三字段的值的改变时具有一的值。

7. 如权利要求5所述的系统,其中当前浮点舍入模式是以下之一:

向负无穷舍入;

向正无穷舍入;

舍入到零;以及

舍入到最接近的偶数。

8. 如权利要求5所述的系统,其中舍入指令包括在具有第二舍入指令的指令集体系结构(ISA)中以指示封装数据寄存器存储标量值,并且其中第二舍入指令使得处理器对标量值执行舍入运算以生成整数值化的浮点值。

9. 如权利要求5所述的系统,进一步包括耦合到处理器核的通信设备。

10. 如权利要求5所述的系统,进一步包括耦合到处理器核的I/O设备。

11. 如权利要求5所述的系统,进一步包括耦合到处理器核的图形引擎。

12. 如权利要求5所述的系统,进一步包括耦合到处理器核的外围元件互连(PCI)Express总线。

13. 如权利要求5所述的系统,进一步包括耦合到处理器核的音频I/O。

14. 一种系统,包括:

存储器;以及

处理器,其耦合至存储器,所述处理器包括:

多个寄存器,其包括第一寄存器和第二寄存器;

控制寄存器,其具有第一字段以指示当前浮点舍入模式以及第二字段以指示非正常是否被转换为零;

状态寄存器,其具有第三字段以存储值,所述值指示不精确异常是否已经发生;

控制单元,其用于接收舍入指令并且用于对舍入指令的字段解码,舍入指令用于识别第一寄存器,所述第一寄存器用于存储具有多个封装的双精度浮点值的源操作数,所述舍入指令用于指示使用当前浮点舍入模式,并且所述舍入指令用于指示抑制状态寄存器的第三字段的值的改变;以及

执行单元,其耦合至控制单元,并且耦合至多个寄存器,所述执行单元响应于舍入指令而:

当第二字段指示所述非正常被转换为零时将源操作数的非正常转换为零;

根据当前浮点舍入模式执行舍入运算,以生成对应于源操作数的封装的双精度浮点值的整数值化的封装的双精度浮点值;以及

在第二寄存器中存储整数值化的封装的双精度浮点值。

15. 如权利要求14所述的系统,其中舍入指令的比特在舍入指令指示抑制状态寄存器的第三字段的值的改变时具有一的值。

16. 如权利要求14所述的系统,其中当前浮点舍入模式是以下之一:

向负无穷舍入；

向正无穷舍入；

舍入到零；以及

舍入到最接近的偶数。

17. 如权利要求14所述的系统，其中舍入指令包括在具有第二舍入指令的指令集体系结构(ISA)中以指示封装数据寄存器存储标量值，并且其中第二舍入指令使得处理器对标量值执行舍入运算以生成整数值化的浮点值。

18. 如权利要求14所述的系统，进一步包括耦合到处理器的音频I/O设备。

19. 如权利要求14所述的系统，进一步包括耦合到处理器的通信设备。

20. 如权利要求14所述的系统，进一步包括耦合到处理器的I/O设备。

21. 如权利要求14所述的系统，进一步包括耦合到处理器的大容量存储装置以存储多媒体应用。

22. 如权利要求14所述的系统，进一步包括耦合到处理器的外围元件互连(PCI)Express总线。

23. 如权利要求14所述的系统，进一步耦合到处理器的盘驱动器以存储多媒体应用。

24. 如权利要求14所述的系统，进一步耦合到处理器的图形引擎。

25. 一种处理器，包括：

源矢量寄存器，用于存储与舍入指令的源操作数相关联的多个封装的双精度浮点值；以及

执行电路，用于对多个双精度浮点值进行舍入以生成将存储在目的矢量寄存器中的多个舍入整数封装的双精度浮点值，执行电路用于根据具有多个比特的立即进行舍入，所述多个比特包括一个或多个比特的第一集合以指定将由执行电路使用的舍入模式以及一个或多个比特的第二集合以指示精度异常是否将被抑制。

26. 如权利要求25所述的处理器，进一步包括：

电路，用于对立即进行解码以确定将由执行电路使用的舍入模式以及确定精度异常是否将被抑制。

27. 如权利要求25所述的处理器，其中响应于具有第一值的一个或多个比特的第一集合，执行电路选择最接近的舍入模式以生成对应于最接近的整数值的舍入结果。

28. 如权利要求27所述的处理器，其中响应于具有第二值的一个或多个比特的第一集合，执行电路选择截尾舍入模式以生成截尾结果。

29. 如权利要求27所述的处理器，其中响应于具有第三值或第四值的一个或多个比特的第一集合，执行电路分别选择向负无穷的舍入模式或向正无穷的舍入模式。

30. 如权利要求25所述的处理器，其中执行电路是浮点执行电路。

31. 如权利要求25所述的处理器，进一步包括：

多个核，执行电路集成到多个核之一。

32. 如权利要求25所述的处理器，进一步包括：

通信互连，用于将处理器耦合至一个或多个设备。

33. 如权利要求32所述的处理器，其中通信互连包括外围元件互连Express(PCI)互连。

34. 一种方法，包括：

在源矢量寄存器中存储与舍入指令的源操作数相关联的多个封装的双精度浮点值；以及

对多个双精度浮点值进行舍入以生成将存储在目的矢量寄存器中的多个舍入整数封装的双精度浮点值，其中根据具有多个比特的立即执行舍入，所述多个比特包括一个或多个比特的第一集合以指定舍入模式以及一个或多个比特的第二集合以指示精度异常是否将被抑制。

35. 如权利要求34所述的方法，进一步包括：

对立即进行解码以确定将使用的舍入模式以及确定精度异常是否将被抑制。

36. 如权利要求34所述的方法，其中响应于具有第一值的一个或多个比特的第一集合，选择最接近的舍入模式以生成对应于最接近的整数值的舍入结果。

37. 如权利要求36所述的方法，其中响应于具有第二值的一个或多个比特的第一集合，选择截尾舍入模式以生成截尾结果。

38. 如权利要求37所述的方法，其中响应于具有第三值或第四值的一个或多个比特的第一集合，分别选择向负无穷的舍入模式或向正无穷的舍入模式。

39. 一种具有存储于其上的程序代码的机器可读介质，所述程序代码在由机器执行时使得机器执行如下操作：

在源矢量寄存器中存储与舍入指令的源操作数相关联的多个封装的双精度浮点值；以及

对多个双精度浮点值进行舍入以生成将存储在目的矢量寄存器中的多个舍入整数封装的双精度浮点值，其中根据具有多个比特的立即执行舍入，所述多个比特包括一个或多个比特的第一集合以指定舍入模式以及一个或多个比特的第二集合以指示精度异常是否将被抑制。

40. 如权利要求39所述的机器可读介质，进一步包括程序代码以使得机器执行以下操作：

对立即进行解码以确定将使用的舍入模式以及确定精度异常是否将被抑制。

41. 如权利要求39所述的机器可读介质，进一步包括程序代码以使得机器执行以下操作：响应于具有第一值的一个或多个比特的第一集合，选择最接近的舍入模式以生成对应于最接近的整数值的舍入结果。

42. 如权利要求41所述的机器可读介质，进一步包括程序代码以使得机器执行以下操作：响应于具有第二值的一个或多个比特的第一集合，选择截尾舍入模式以生成截尾结果。

43. 如权利要求42所述的机器可读介质，进一步包括程序代码以使得机器执行以下操作：响应于具有第三值或第四值的一个或多个比特的第一集合，分别选择向负无穷的舍入模式或向正无穷的舍入模式。

44. 一种处理器，包括：

第一寄存器；

第二寄存器；

控制寄存器，用于存储缺省浮点舍入模式的指示符，以及非正常作为零指示符；

解码器，用于接收舍入指令，所述舍入指令用于识别第一寄存器，第一寄存器存储具有多个封装的双精度浮点值的源操作数，所述舍入指令具有多个可能的替换浮点舍入模式的

舍入模式替换指示符以指示将替换缺省浮点舍入模式,所述舍入指令用于识别替换浮点舍入模式;以及

执行单元,其耦合至解码器,并且耦合至第一和第二寄存器,执行单元响应于舍入指令而:

将源操作数的非正常封装的双精度浮点值转换为零;

根据识别的替换浮点舍入模式对封装的双精度浮点值执行舍入运算,以生成整数值化的双精度浮点值;以及

在第二寄存器中存储整数值化的双精度浮点值。

45. 如权利要求44所述的处理器,其中替换浮点舍入模式是向负无穷的舍入。

46. 如权利要求44所述的处理器,其中替换浮点舍入模式是向正无穷的舍入。

47. 如权利要求44所述的处理器,其中替换浮点舍入模式是舍入到零。

48. 如权利要求44所述的处理器,其中替换浮点舍入模式是舍入到最接近的偶数。

49. 如权利要求44所述的处理器,其中多个可能的替换浮点舍入模式包括向远离零的方向舍入模式。

50. 如权利要求44所述的处理器,其中舍入模式替换指示符是单比特,并且其中所述单比特是零以指示将替换缺省浮点舍入模式。

51. 如权利要求44所述的处理器,其中舍入指令包括在具有第二舍入指令的指令集体系结构(ISA)中以指示封装数据寄存器存储标量值,并且其中第二舍入指令使得处理器对标量值执行舍入运算以生成整数值化的浮点值。

52. 如权利要求44所述的处理器,进一步包括状态寄存器,其包括不精确异常字段,并且其中执行单元响应于舍入指令,如果在舍入指令的执行期间不精确异常发生则不更新不精确异常字段。

53. 如权利要求44所述的处理器,其中舍入指令具有舍入模式控制比特以识别替换浮点舍入模式。

54. 一种系统,包括:

存储器控制器;以及

处理器核,其耦合至存储器控制器,所述处理器核包括:

第一寄存器;

第二寄存器;

控制寄存器,用于存储缺省浮点舍入模式的指示符,以及非正常作为零指示符;

解码器,用于接收舍入指令,所述舍入指令用于识别第一寄存器,寄存器存储具有多个封装的双精度浮点值的源操作数,所述舍入指令具有多个可能的替换浮点舍入模式的舍入模式替换指示符以指示将替换缺省浮点舍入模式,所述舍入指令用于识别替换浮点舍入模式;以及

执行单元,其耦合至解码器,并且耦合至第一和第二寄存器,执行单元响应于舍入指令而:

将源操作数的非正常封装的双精度浮点值转换为零;

根据识别的替换浮点舍入模式对封装的双精度浮点值执行舍入运算,以生成整数值化的双精度浮点值;以及

在第二寄存器中存储整数值化的双精度浮点值。

55. 如权利要求54所述的系统,其中替换浮点舍入模式是向负无穷的舍入。

56. 如权利要求54所述的系统,其中替换浮点舍入模式是向正无穷的舍入。

57. 如权利要求54所述的系统,其中替换浮点舍入模式是舍入到零。

58. 如权利要求54所述的系统,其中替换浮点舍入模式是舍入到最接近的偶数。

59. 如权利要求54所述的系统,其中多个可能的替换浮点舍入模式包括向远离零的方向舍入模式。

60. 如权利要求54所述的系统,其中舍入模式替换指示符是单比特,并且其中所述单比特是零以指示将替换缺省浮点舍入模式。

61. 如权利要求54所述的系统,其中处理器核根据向远离零的方向舍入模式执行舍入运算。

62. 如权利要求54所述的系统,其中舍入指令包括在具有第二舍入指令的指令集体体系结构(ISA)中以指示封装数据寄存器存储标量值,并且其中第二舍入指令使得处理器对标量值执行舍入运算以生成整数值化的浮点值。

63. 如权利要求54所述的系统,进一步包括状态寄存器,其包括不精确异常字段,并且其中执行单元响应于舍入指令,如果在舍入指令的执行期间不精确异常发生则不更新不精确异常字段。

64. 如权利要求54所述的系统,其中舍入指令具有舍入模式控制比特以识别替换浮点舍入模式。

65. 如权利要求54所述的系统,进一步包括耦合到处理器核的通信设备。

66. 如权利要求54所述的系统,进一步包括耦合到处理器核的I/O设备。

67. 如权利要求54所述的系统,进一步包括耦合到处理器核的图形引擎。

68. 如权利要求54所述的系统,进一步包括耦合到处理器核的外围元件互连(PCI)Express总线。

69. 如权利要求54所述的系统,进一步包括耦合到处理器核的盘驱动器。

70. 如权利要求54所述的系统,进一步包括耦合到处理器核的大容量存储装置。

71. 如权利要求54所述的系统,进一步包括耦合到处理器核的音频I/O。

72. 一种系统,包括:

存储器;以及

处理器,其耦合至存储器,所述处理器包括:

第一寄存器;

第二寄存器;

控制寄存器,用于存储缺省浮点舍入模式的指示符,以及非正常作为零指示符;

解码器,用于接收舍入指令,所述舍入指令用于识别第一寄存器,第一寄存器存储具有多个封装的双精度浮点值的源操作数,所述舍入指令具有多个可能的替换浮点舍入模式的舍入模式替换指示符以指示将替换缺省浮点舍入模式,所述舍入指令用于识别替换浮点舍入模式;以及

执行单元,其耦合至解码器,并且耦合至第一和第二寄存器,执行单元响应于舍入指令而:

将源操作数的非正常封装的双精度浮点值转换为零；

根据识别的替换浮点舍入模式对封装的双精度浮点值执行舍入运算，以生成整数值化的双精度浮点值；以及

在第二寄存器中存储整数值化的双精度浮点值。

73. 如权利要求72所述的系统，其中替换浮点舍入模式是向负无穷的舍入。

74. 如权利要求72所述的系统，其中替换浮点舍入模式是向正无穷的舍入。

75. 如权利要求72所述的系统，其中替换浮点舍入模式是舍入到零。

76. 如权利要求72所述的系统，其中替换浮点舍入模式是舍入到最接近的偶数。

77. 如权利要求72所述的系统，其中多个可能的替换浮点舍入模式包括向远离零的方向舍入模式。

78. 如权利要求72所述的系统，其中舍入模式替换指示符是单比特，并且其中所述单比特是零以指示将替换缺省浮点舍入模式。

79. 如权利要求72所述的系统，其中处理器根据向远离零的方向舍入模式执行舍入运算。

80. 如权利要求72所述的系统，其中舍入指令包括在具有第二舍入指令的指令集体系结构(ISA)中以指示封装数据寄存器存储标量值，并且其中第二舍入指令使得处理器对标量值执行舍入运算以生成整数值化的浮点值。

81. 如权利要求72所述的系统，进一步包括状态寄存器，其包括不精确异常字段，并且其中执行单元响应于舍入指令，如果在舍入指令的执行期间不精确异常发生则不更新不精确异常字段。

82. 如权利要求72所述的系统，其中舍入指令具有舍入模式控制比特以识别替换浮点舍入模式。

83. 如权利要求72所述的系统，进一步包括耦合到处理器的音频I/O。

84. 如权利要求72所述的系统，进一步包括耦合到处理器核的通信设备。

85. 如权利要求72所述的系统，进一步包括耦合到处理器的I/O设备。

86. 如权利要求72所述的系统，进一步包括耦合到处理器的大容量存储装置。

87. 如权利要求72所述的系统，进一步包括耦合到处理器的外围元件互连(PCI)Express总线。

88. 如权利要求72所述的系统，进一步包括耦合到处理器的盘驱动器。

89. 如权利要求72所述的系统，进一步包括耦合到处理器的图形引擎。

## 响应指令执行舍入运算

### 技术领域

[0001] 本发明一般涉及处理器对数据执行的数学运算,特别是涉及舍入运算。

### 背景技术

[0002] 处理器对数据执行各种各样的数学运算。数据可能属于不同的类型,包括例如具有不同内在精度的整数值和浮点(FP)值。当处理FP值时,在其它这样的操作之中,数学运算、比如乘法或加法的结果有可能产生需要将其转换为较低精度格式的结果。相应地,可以执行舍入运算以将该FP结果进行舍入。

[0003] 尽管这样的舍入运算可以作为不同数学运算的一部分来执行,但是在一些处理器体系结构中,限制了或不能够作为独立运算对数据元素执行舍入运算,或者无需多个复杂的步骤。例如,处理器可以配置为根据缺省舍入模式执行FP值到整数值的舍入。然而,因为种种理由,可能需要根据不同的模式来将给定的源操作数进行舍入。为了完成这样的运算,可能出现保存处理器的当前配置状态、加载包括关于所要求的舍入模式的信息在内的新的配置状态、执行舍入运算、以及恢复原始处理器状态等的复杂步骤。这些操作可能是耗费时间的,提高了复杂性并且耗费了过多的处理周期。另外,虽然随着新的程序设计语言的发展,所希望的是支持其它的舍入模式,但是,在处理器中所执行的舍入运算通常仍然按照有限数量的舍入模式、即已在电气和电子工程师学会(IEEE)标准754-1985(1985年发表)中所阐述的舍入模式进行。

### 发明内容

[0004] 根据本发明的第一方面,提供了一种方法,包括:

在处理器中接收舍入指令和立即值;

确定所述立即值的舍入模式替换指示符是否是有效的;以及

如果有效,则响应所述舍入指令并且根据在所述立即值中规定的舍入模式,在所述处理器的浮点单元中对源操作数执行舍入运算。

[0005] 根据本发明的第二方面,提供了一种装置,包括:

控制器,接收舍入指令和与所述舍入指令相关的立即数据元素,其中,所述控制器基于所述立即数据元素的替换指示符来确定是否替换缺省舍入模式;以及

执行单元,耦合于所述控制器,响应所述舍入指令来执行舍入运算,其中,如果替换所述缺省舍入模式,则所述执行单元根据所述立即数据元素的舍入模式来执行所述舍入运算。

[0006] 根据本发明的第三方面,提供了一种系统,包括:

执行单元,如果替换指示符存在于控制字段中,则根据与舍入指令相关的控制字段中规定的舍入模式,对第一操作数执行舍入指令以获得舍入的结果;以及

耦合于所述执行单元的动态随机存取存储器(DRAM)。

[0007] 根据本发明的第四方面,提供了一种机器可读介质,在其上存储了指令,如果所述

指令由机器执行,就会使机器执行包括以下步骤的方法:

根据由所述指令规定的模式来执行舍入运算;以及

在第一存储区中存储所述舍入运算的结果。

## 附图说明

- [0008] 图1是根据本发明的一个实施例的方法的流程图。

- [0009] 图2是根据本发明的一个实施例的处理器的一部分的框图。

- [0010] 图3是根据本发明的一个实施例、结合指令使用的立即数据元素的框图。

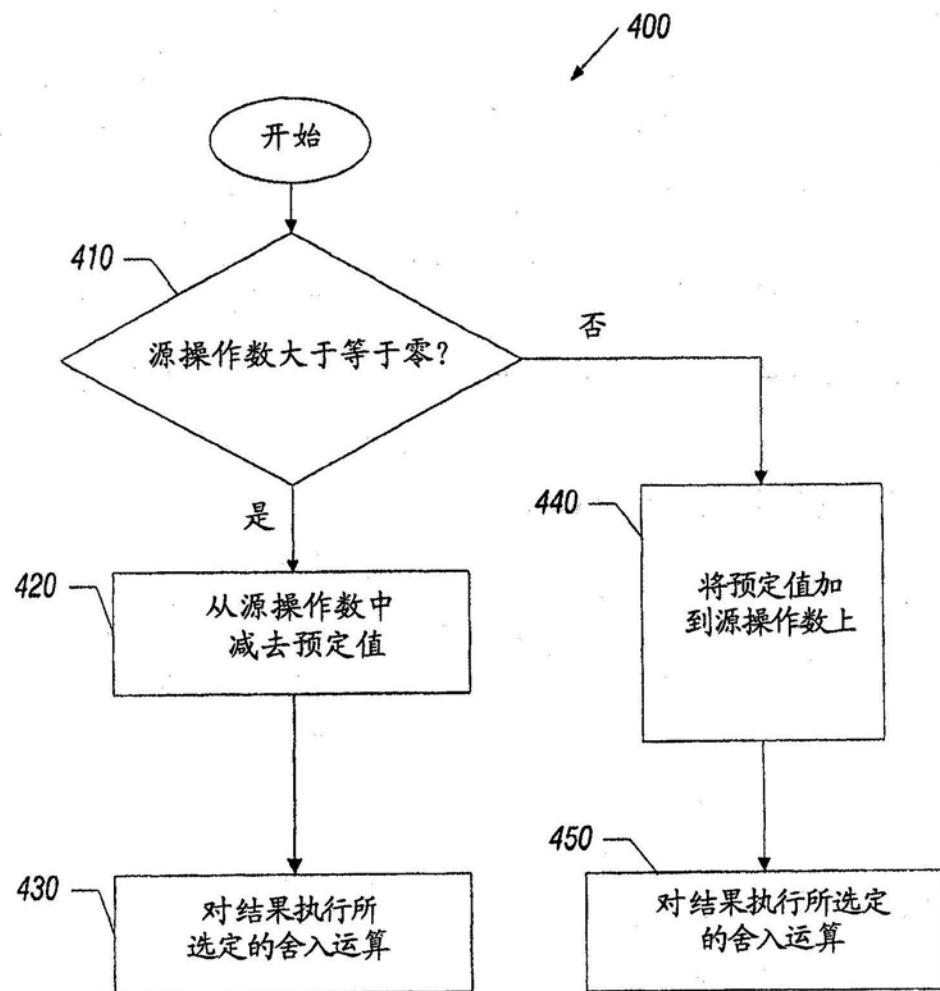

- [0011] 图4是根据本发明的一实施例的用于执行舍入运算的方法的流程图。

- [0012] 图5是根据本发明的一个实施例的系统的框图。

## 具体实施方式

[0013] 在不同的实施例中,在处理器中、例如在处理器的浮点单元(FPU)中可使用指令集体系结构(ISA)的多个舍入指令来有效地执行舍入运算。除了在电气和电子工程师学会(IEEE)标准754-1985(1985年发表)(在这里IEEE 标准用于二元浮点运算或者IEEE 标准754)中阐明的舍入模式之外,实施例可用于根据其它舍入模式来执行舍入运算。例如,如下所述,在有些实施例中,指令可提供对部分远离零的以及远离零的舍入运算的支持。此外,这些舍入运算可以和许多数据类型一起使用。在有些实现中,舍入运算可以对单指令多数据(SIMD)数据类型执行,以便可以对扩展的数据类型、比如封装数据元素执行指令,其中将多种数据元素封装到单一的位置例如处理器的扩充寄存器中。

[0014] 为了提供灵活性并且提供有效的指令执行,实施例可提供基于ISA 的指令,该指令可以对源操作数执行。这些基于ISA的指令可以是用于执行到源操作数的最接近整数值的舍入的舍入运算的不同实现。这样的源操作数可能已经是有限精度格式(即,不是算术运算的结果,而是从寄存器/存储器中读出的数据)。这样的指令可用于不同的应用,包括多媒体应用、游戏应用等等。此外,实施例可在基于编译程序的基本要素上来实现以实现舍入运算,这些舍入运算适用于不同的程序设计语言。注意,在不同的实施例中,舍入指令可采用浮点数作为源操作数,将其舍入到最接近的整数值,并且将结果也作为具有整数值的浮点值进行存储。

[0015] 在不同的实施例中,至少部分根据与该指令一起接收到的信息、例如与该指令一起接收到的立即数据,可处理对该执行的控制。在不同的实现中,这样的立即数据可替换 override)由处理器当前所使用的缺省舍入模式。在这样的替换情况中,该立即数据可进一步提供对该舍入模式的控制。此外,该立即数据可为精度异常(即精度抑制)的替换作准备。如此可将立即数据用于提供特定舍入运算的非粘性控制,如此该运算可在最少周期中执行。这也许如此,如同当与指令结合接收的立即数据包括舍入控制信息的时候,可能不需要更新出现于配置寄存器中的这种信息,其中配置寄存器比如为扩展控制和状态寄存器(CSR),例如存在于依据Intel<sup>®</sup> 体系结构(例如,IA-32体系结构)的处理器中的多媒体扩展CSR(MXCSR)。然而,需要理解的是,可在不同的处理器类型中使用这些实施例,并且本发明的范围不是限于这个方面。

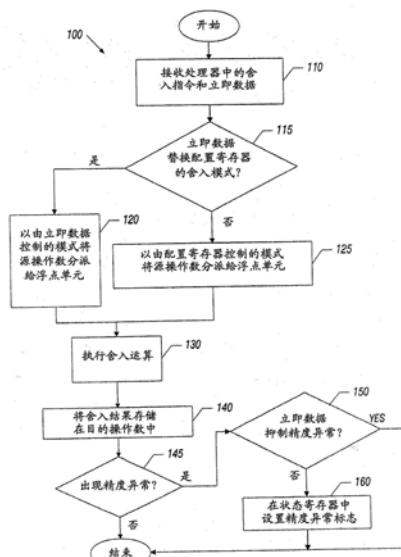

[0016] 现在参照图1,所示的是根据本发明的一个实施例的方法的流程图。如图1所示,方

法100首先接收在处理器之中的舍入指令以及相关的立即数据(步骤110)。例如,在许多实现中,可在处理器中接收用户级指令、例如,ISA的指令。除指令之外,同时也可提供立即数据。如下面要进一步进行描述,这种立即数据可包括多个字段以控制运算的各个方面。

[0017] 仍参照图1,控制从步骤110转到判断步骤115。在判断步骤115,可确定该立即数据是否替换配置寄存器的舍入模式。亦即,立即数据的字段可能包括替换指示符,它指出是否替换缺省舍入模式。在不同的实施例中,这种缺省舍入模式可存在于配置寄存器、比如CSR、例如,MXCSR的字段中,但本发明的范围不限于这个方面。如果该立即数据包括替换指示符,则控制转到步骤120。在步骤120,可将由指令识别的源操作数分派给例如处理器的浮点单元(FPU)。此外,可将该源操作数与信息一起分派以控制舍入运算的舍入模式。可从立即数据获得控制信息,即,如同在立即数据的舍入状态字段中所规定的。如同将要在下面进一步描述的,在有些实现中,控制单元、比如处理器的控制选择单元可接收指令以及立即数据,并且将立即数据解码以确定是否替换缺省舍入模式,以及如果是这样的话,则获得该立即数据中规定的舍入模式。

[0018] 仍参照图1,如果在判断步骤115确定立即数据不包括替换指示符,则控制转移到步骤125。在步骤125,可分派源操作数用于在FPU进行执行。此外,可在例如配置寄存器中规定的缺省舍入模式的基础上执行舍入运算。

[0019] 无论如何,控制都会从两个步骤120和125传递到步骤130,在那里可执行舍入运算。该舍入运算按照舍入模式删除了该输入(即源操作数)的分数精度。在不同的实施例中,可实现执行舍入运算的不同方式。例如,在许多实现中,FPU可包括加法器和舍入单元用以执行舍入运算。为了根据IEEE标准754执行舍入模式,加法器可拥有源操作数作为第一操作数以及常量值、例如零用作第二操作数。然后可将加法器的输出馈送到舍入单元,该舍入单元根据所选择的操作模式将结果进行舍入。因此,舍入单元可将它的输入值舍入成为整数值化的浮点结果。

[0020] 在其它的实施例中,除IEEE 标准754舍入模式之外还可执行其它舍入模式。在这类实现中,可向FPU加法器馈送源操作数以及以源操作数的值和该舍入模式为基础的特定数据值作为第二操作数,将要在下面进行进一步描述。然后可对该结果执行舍入运算,其中,该舍入运算可为IEEE 标准754运算。在其它扩展的舍入模式的实现中,可将源操作数和零值提供给FPU 加法器的输入,并且然后可将所得值根据送到舍入单元的控制信息进行舍入。

[0021] 在执行之后,可将舍入运算的结果存储在目的操作数中(步骤140)。在不同的实施例中,目的操作数可以是处理器的扩展存储寄存器,但是本发明的范围不限于此。此外,可确定在舍入运算期间是否发生了精度异常(判断步骤145)。亦即,可以确定该舍入运算是否形成了能够引发异常的不精确的结果。如若不是,方法100可以结束。

[0022] 如果产生了精度异常,则控制可转到判断步骤150。在判断步骤150,可确定立即数据是否包括了用于抑制精度异常的字段。亦即,在有些实现中,立即数据可包括抑制字段。这个字段的值可指示出,如果产生精度异常的话,相关的舍入指令是否应该抑制精度异常。如果精度抑制指示符存在,则即使精度异常发生,也不会采取更进一步地动作,并且方法100可以结束。如果立即数据不包括用于抑制精度异常的指示符,则控制可以转到步骤160。在步骤160,可在状态寄存器中设置精度异常的标志。例如,在有些实现中,状态寄存器可对

应于MXCSR,但是本发明的范围不限于这个方面。以在状态寄存器中的这个标志的状态为基础,可能发生精度异常(例如,如果该标志是无屏蔽的)。如果是这样的话,则可例如经由软件处理器来执行适当的处理以处理该异常。如果标志是被屏蔽的,即使精度异常发生了并且在状态寄存器进行了标记,则相对于设置的标志不会采取任何动作。尽管在图1的实施例中对于这个具体实现进行了描述,但是可以理解的是,本发明的范围不限于这个方面。

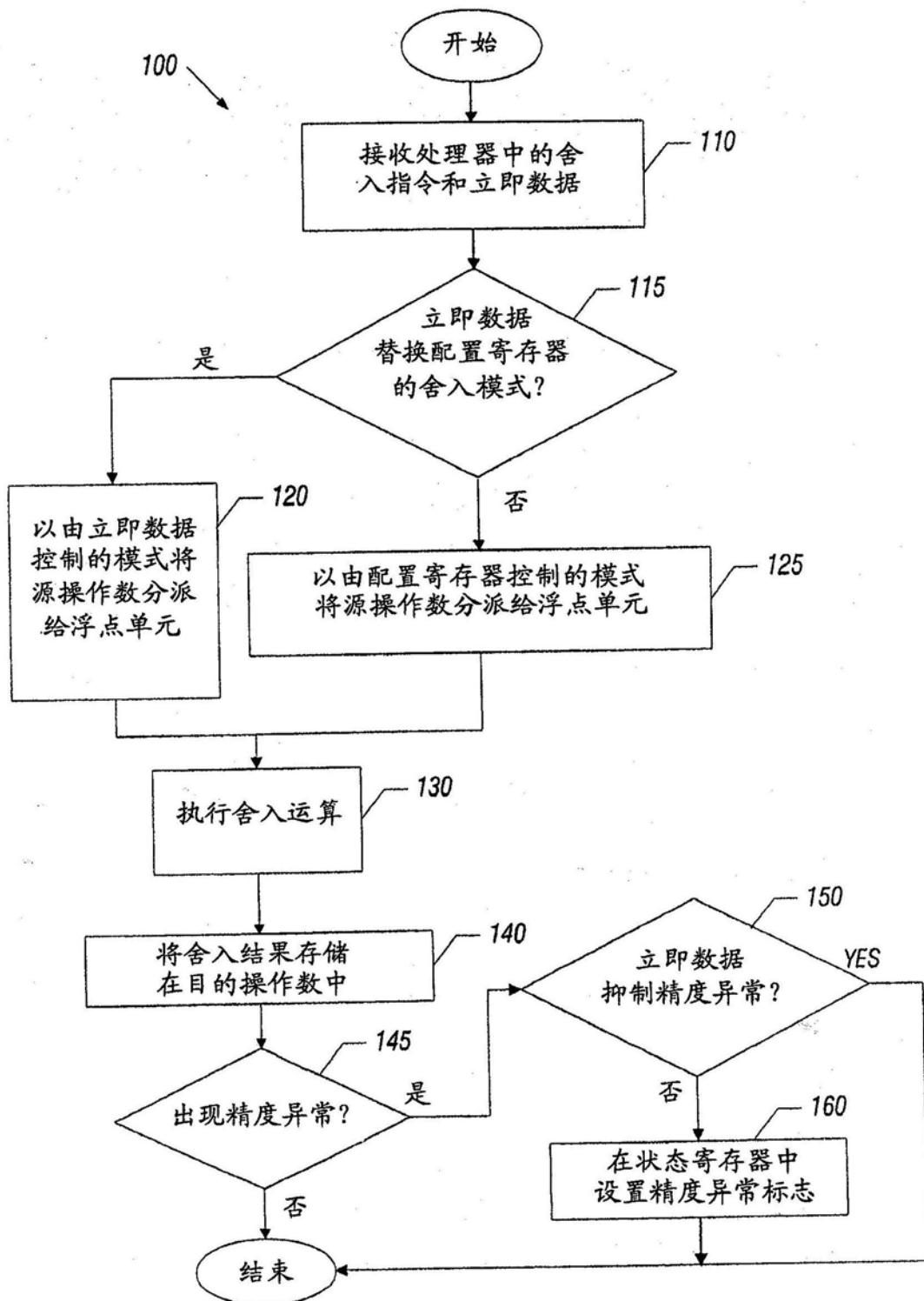

[0023] 现在参照图2,所示的是根据本发明的一个实施例的处理器一部分的框图。如图2所示,处理器200可包括控制选择单元210,经过耦合用以从寄存器205(它可能是通用处理器寄存器)接收例如由微操作( $\mu$ op)产生的输入的指令信息以及与此相关的立即数据。 $\mu$ op可响应于执行给定舍入运算的单一ISA的指令而产生。在不同的实施例中,控制选择单元210可以对立即数据解码,其中该控制选择单元210可由硬件、软件、固件或它们的组合来实现。在立即数据的基础上,可以确定是否替换例如在存储了当前舍入控制状态220的控制或者配置寄存器中所表示的处理器的当前舍入模式。如果是这样的话,控制选择单元210可以解码立即数据的模式字段,即舍入模式字段,来确定恰当的舍入模式。

[0024] 控制选择单元210可耦合于浮点单元(FPU)240以在输入信息的基础上向其提供控制指令。如图2中进一步所示,扩展寄存器文件、比如所谓的扩展(XMM)寄存器230可出现在处理器200之内,其中该处理器200可包括在作为用于舍入运算的源和目的操作数的指令中所确定的寄存器。因此,XMM寄存器230可耦合于FPU 240以对其提供源操作数并从其中接收目的操作数。

[0025] 在不同的实施例中,FPU 240可包括各种电路以对数据执行操作。在图2的实施例中,FPU 240包括FPU加法器242。具体地,如图2所示,FPU加法器242可被耦合以接收输入操作数,例如第一源操作数和第二源操作数(即,操作数S1和S2)。FPU 240也可包括FPU舍入器244,它耦合于FPU加法器242的输出。在不同的实施例中,FPU加法器242可产生运算的无限精确结果。然而,给定了存储器及其它约束,可能会将结果进行舍入来以所希望的格式例如单精度或者双精度浮点元素提供最终结果。相应地,FPU舍入器244可从FPU加法器242接收无限精确的结果并且执行舍入运算,例如由处理器200的当前舍入模式所指示的,或者以来自立即数据的控制为基础,其中该立即数据与指令一起获得,即经由控制选择单元210。注意,尽管FPU舍入器244通常可接收在FPU加法器242中作为数学运算结果出现的无限精确的结果,但是在不同的实现中,拥有舍入指令的源操作数可能已经是有限精度格式。在这些情况下,FPU舍入器244可接收其输入值(例如对应于给定舍入指令的源操作数)并且产生例如对应于最接近的整数值的舍入结果。

[0026] 因此,以给定的舍入指令为基础,FPU 240可以对例如来自XMM寄存器230之一、由来自控制选择单元210的信息所控制的给定源操作数执行舍入运算。此外,在舍入运算完成的时候,可将结果存储到例如在XMM寄存器230之中不同的寄存器上。如果精度异常在运算期间发生,通常可在FP状态寄存器225设置标志来表明。然而,在不同的实施例中,如果与舍入指令有关的立即数据指示了精度抑制,则不设置这样的标志。尽管在图2的实施例中对于这个具体实现进行了描述,但是可以理解的是,本发明的范围不限于这个方面。例如,在有些实施例中,例如由舍入控制状态220和FP状态寄存器225所表示的控制和情况状态可被存储在单一CSR例如MXCSR 中。

[0027] 注意,可通过不同的形式向控制选择单元210提供立即数据。例如,在有些实现中,

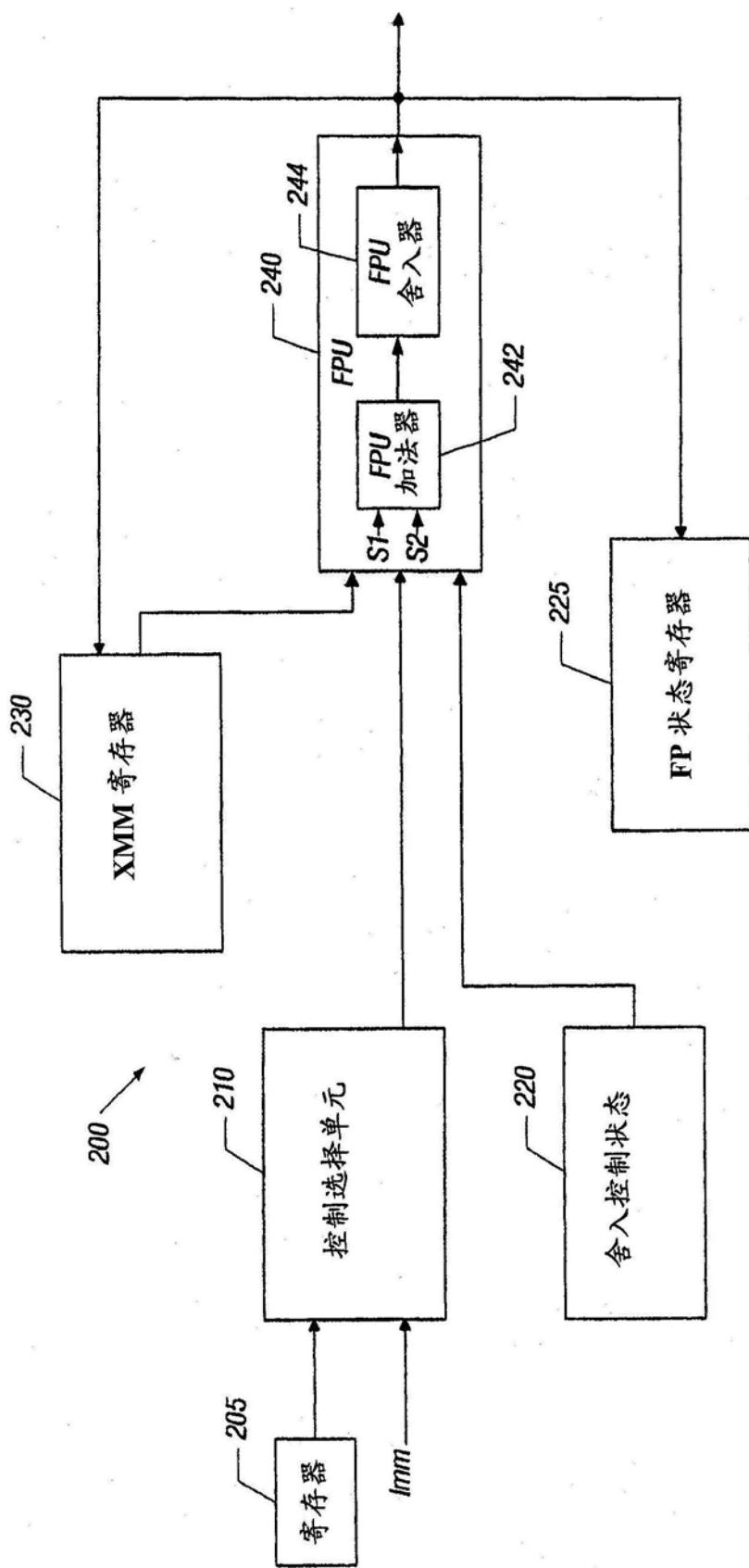

立即数据可以是单字节数据元素的形式,但是本发明的范围不限于此。此外,在立即数据元素之内可实现不同方式的编码控制信息。现在参照图3,所示的是根据本发明的一个实施例的立即数据元素的框图。如图3所示,立即数据元素300可为包括替换指示符310、模式控制字段320、精度替换指示符330和保留字段340的8比特字。尽管在图3的实施例显示了这个具体实现,但是本发明的范围不限于这种方式。

[0028] 在图3的实施例中,替换指示符310可用来确定与立即数据元素300有关的舍入指令的替换状态。如下面表1所示,替换指示符310可设置为逻辑低电平来指示缺省舍入模式(例如由配置寄存器如MXCSR所表示)的替换。逻辑高电平值指示缺省模式的使用。

[0029] 表1

|                |

|----------------|

| 舍入模式替换指示符      |

| 0: 使用直接值的1:3比特 |

| 1: 使用缺省舍入模式    |

[0030] 如果替换指示符310指示将要替换缺省舍入模式,那么可对舍入模式字段320进行解码以确定与舍入指令相关的舍入模式。如下面表2所示,在有些实现中,可支持六种舍入模式,包括由IEEE 标准754规定的四种舍入模式,以及两种扩展的舍入模式,将在下面对其更进一步地进行讨论。

[0031] 表2

|                  |

|------------------|

| 舍入模式字段           |

| 000: 最接近的偶数      |

| 001: 朝-∞的方向      |

| 010: 朝+∞的方向      |

| 011: 截断(舍入到0)    |

| 100: 部分向远离0的方向舍入 |

| 101: 向远离0的方向舍入   |

[0032] 立即数据元素300还包括精度抑制指示符330,可对其进行设置来指示不精确结果的容差,使得精度异常即使在相关指令的运算期间发生时也不会导致在状态寄存器中的异常标志的设置。具体地,如下面表3所示,精度抑制指示符330可以采用以下形式:

表3

|                     |

|---------------------|

| 精度抑制指示符             |

| 1: 没有对不精确(精度)字段进行更新 |

| 0: 正常行为             |

[0033] 注意,精度抑制指示符330可与不同语言、例如C99、Fortran和Java的用户级指令结合使用。最后,在一些实施例中,可以为额外的信息保留保留字段340。还要注意,在表1-3中规定的具体值、以及指示符和字段的具体位置和大小不受限制,并且各种改变、修改和扩展都在本发明的范围之内。

[0034] 如同上面描述的,在许多实现中,舍入运算可响应ISA的单指令来执行。以这种方法,提供了用户级的支持,并且可以有效地执行舍入运算。在给定的ISA中,可出现并使用若干这类舍入指令来处理具体的舍入运算,例如双精度和单精度浮点值以及封装和标量值的舍入。这些舍入指令也可用于将浮点数据元素的分数部分舍去。除ISA级指令的存在之外,

立即数据或者其它的控制字段信息可以允许舍入模式(连同其它属性一道)的有效局部控制,而不必修改处理器的当前缺省状态。

[0035] 如下面表4所示,在ISA之中可以出现不同风格的舍入指令以对不同类型的数据元素实现有效的舍入运算。

[0036] 表4

| 指令                            | 描述                                                 |

|-------------------------------|----------------------------------------------------|

| ROUNDPD xmm1, xmm2/m128, imm8 | 将在xmm2/m128中封装的双精度浮点值进行舍入并且将结果放入xmm1。由imm8确定舍入的模式。 |

| ROUNDPS xmm1, xmm2/m128, imm8 | 将在xmm2/m128中封装的单精度浮点值进行舍入并且将结果放入xmm1。由imm8确定舍入的模式。 |

| ROUNDSD xmm1, xmm2/m64, imm8  | 将在xmm2/m64中低封装的双精度浮点值进行舍入并且将结果放入xmm1。由imm8确定舍入的模式。 |

| ROUNDSS xmm1, xmm2/m32, imm8  | 将在xmm2/m32中低封装的单精度浮点值进行舍入并且将结果放入xmm1。由imm8确定舍入的模式。 |

[0037] 作为这些ISA指令如何操作的例子,可使用ROUNDPD 指令,通过在直接元素(即IMM 8)中规定的舍入模式来将在源操作数(即可从XMM寄存器或者存储器得到的第二操作数)中的两个双精度浮点值进行舍入,并且将结果放到目的操作数(即可以是XMM寄存器的第一操作数)中。直接元素可以指定用于舍入运算的控制字段。再参考表1-3,立即数据的比特4(即图3的指示符330)可以控制精度异常的处理器的行为,而比特0(即图3的指示符310)可以选择舍入模式控制的源。最后,比特3:1(即图3的字段320)可以指定非粘性舍入模式值。注意,在有些实施例中,如果任何源操作数是信令而不是数字(SNaN),那么它将要转换为静止的NaN (QNaN)。如果将配置寄存器对于非正常设置为零(DAZ),那么非正常可在舍入之前转换为零。如果将配置寄存器对于非正常刷新(flush denormal)设置为零(FTZ),那么非正常可在舍入之后转换为零。

[0038] 作为这些ISA 指令如何操作的另一个例子,ROUNDPS 指令可用来在源操作数中将四个封装的单精度浮点值进行舍入并且将结果放到目的操作数中。为了说明的目的,具体的舍入指令可以采用以下形式:

ROUNDPS xmm0, xmm1, imm8(舍入到最接近的整数)。

[0039] 这个指令可取第一寄存器即xmm1中的封装单精度值,如同由立即数据(即imm8)的舍入模式所规定的将每个值舍入到最接近的整数值,并且将结果存储到第二寄存器、即xmm0中。下面的表5显示了存在于源操作数(即xmm1)中、各对应于有限精度浮点值的典型值以及存储在目的操作数(即xmm0)中、对应于整数值化的浮点数、即与初始源值最接近的整数值的所得舍入值。

[0040] 表5

|       |      |      |      |      |

|-------|------|------|------|------|

| 1.01f | 2.9f | 3.6f | 4.2f | xmm1 |

|-------|------|------|------|------|

|      |      |      |      |      |

|------|------|------|------|------|

| 1.0f | 3.0f | 4.0f | 4.0f | xmm0 |

|------|------|------|------|------|

[0041] 注意,在另外的实现中,舍入运算可响应从源FP值生成的整数值(即,与整数值化FP值相反)的指令。其它的实施例可以实现到较低精度浮点表示法的舍入。这样的实施例可根据标准舍入模式或者特殊的舍入模式来提供舍入源值的有效部件,其中特殊的舍入模式由配置寄存器中缺省舍入模式或者在与该指令有关的立即数据中规定的局部舍入模式来进行控制。

[0042] 在不同的实施例中,立即数据可提供控制信息以执行不同于IEEE 标准754舍入运

算的舍入模式。这些舍入模式可以包括部分向远离零的方向舍入以及向远离零的方向舍入模式。现在参照图4,所示的是根据本发明的一个实施例执行舍入运算的方法的流程图。如图4所示,方法400可用来执行这些扩展的舍入模式。方法400可通过确定源操作数是否大于或等于零(菱形步骤410)来开始。如果是这样的话,控制可以转到步骤420,在那里可从源操作数减去预定的值(步骤420)。例如,FP加法器可以在所选择的具体舍入模式的基础上从源操作数减去给定的值。当然,这个减法可通过与预定值的负值相加来执行。然后,可对FP加法的结果执行所选定的舍入运算(步骤430)。在有些实现中,IEEE 标准754舍入运算、例如截尾(也称为舍入到零)可对结果执行以获得扩展的舍入模式结果。如果在菱形步骤410确定该源操作数小于零,那么控制转移到步骤440。在步骤440,可在FP加法器中将预定的值(它可能是与以上所述相同的值)加到源操作数上。然后,在步骤450,可对结果执行选定的舍入运算以获得由此产生的舍入值。

[0043] 虽然本发明的范围不限于这个方面,但是部分向远离零的方向舍入运算可以使用0.5的值作为其预定的值,而向远离零的方向舍入运算可以使用1”,它对应于小于但不等于一的最接近的可表示的FP值。对于单精度和双精度FP值,0.5可分别对应于0x3f000000和0x3fe000000000000。对于单精度和双精度FP值,-0.5可分别对应于0xbff00000和0xbfe000000000000。对于单精度和双精度FP值,1”可分别对应于0x3f7fffff和0x3fefffffffffffff。对于单精度和双精度FP值,-1”可以分别对应于0xbff7ffff 和0xbfefffffffffffff。在下面表6中显示的是用于执行这些操作的源代码例子。

Table 6

|                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| <b>ROUND_HALF_AWAY_ZERO(A):</b>                                                                                                         |

| IF (A <= 0)                                                                                                                             |

| A←ROUND_TOWARD_ZERO(A - 0.5)                                                                                                            |

| ELSE IF (A > 0)                                                                                                                         |

| A←ROUND_TOWARD_ZERO(A + 0.5)                                                                                                            |

| 2) Round Away From Zero (A). “The result shall be the value closest to and no smaller in magnitude than the infinitely precise result.” |

| IF (A <= 0)                                                                                                                             |

| A←ROUND_TOWARD_ZERO(A - 1)                                                                                                              |

| ELSE IF (A > 0)                                                                                                                         |

| A←ROUND_TOWARD_ZERO(A + 1)                                                                                                              |

[0044] 在这些例子中,运算ROUND\_TOWARD\_ZERO是IEEE 标准754的截尾操作,它对加法/减法运算的结果执行。注意,在执行这些扩展舍入模式的运算中,可提供预定的值作为给FP加法器的第二源操作数(例如,如同在图2实施例中的S2)。另一方面,在有些实施例中,如同其它的舍入运算一样,第二源操作数可以为零,并且可将控制信号发送到舍入单元以实现选定的扩展舍入模式运算。

[0045] 这样,在不同的实施例中,可实现对于执行舍入的增强。这些增强可以避免执行各

种操作的需要,例如存储控制寄存器的状态、执行空FP运算以及重新设置状态,或者甚至是转换数字到整数以及回到浮点的近似简化。通过抑制不精确的精度异常,用于舍入的相符不同语言的支持可简单化,而实现也可以遵守某些舍入功能的标准舍入模式,例如在C99语言中。

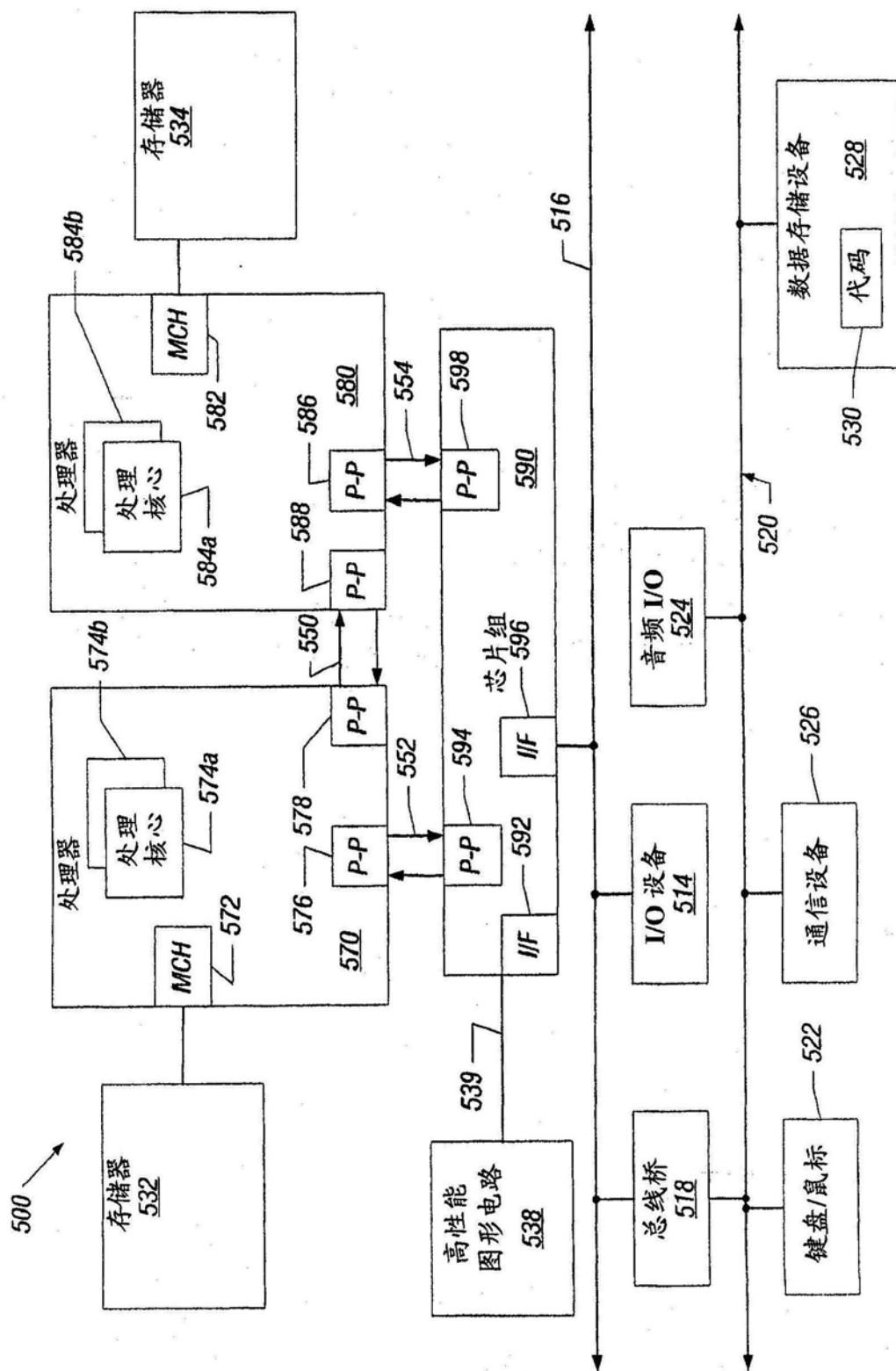

[0046] 实施例可以在许多不同的系统类型中实现。现在参照图5,所示的是根据本发明的一个实施例的系统的框图。如图5所示,多处理器系统500是点对点互连系统,并且包括经由点对点互连550耦合的第一处理器570和第二处理器580。如图5所示,处理器570和580中每一个都可以是多核处理器,包括第一和第二处理器核(即,处理器核574a和574b以及处理器核584a和584b)。注意,每一个核都可响应根据本发明的一个实施例的ISA级指令来执行舍入运算。

[0047] 第一处理器570此外还包括点对点(P-P)接口576和578。类似地,第二处理器580包括P-P接口586和588。如图5所示,存储控制器集线器(MCH)572和582将处理器耦合到各自的存储器上,即存储器532和存储器534,它们可能是本地连接到各自处理器的主存储器的部分。

[0048] 第一处理器570和第二处理器580可分别经由P-P互连552和554耦合到芯片组590上。如图5所示,芯片组590包括P-P接口594和598。此外,芯片组590包括接口592以将芯片组590与高性能图形引擎538相耦合。在一个实施例中,高级图形接口(AGP)总线539可用来将图形引擎538耦合到芯片组590。AGP总线539可符合加速图形端口接口规格修订版本2.0,它于1998年5月4日由加利福尼亚Santa Clara的英特尔公司发表。另一方面,点对点互连539可以耦合这些元件。

[0049] 随后,芯片组590可经由接口596耦合到第一总线516。在一个实施例中,第一总线516可以是外围元件互连(PCI)总线,如由PCI局部总线规范,生产版本,修订版2.1,日期是1995年6月所定义的,或者例如PCI Express<sup>TM</sup>总线或者其它第三代输入/输出(I/O)中间连接总线的总线,但本发明的范围不限于此。

[0050] 如图5所示,各种I/O设备514可耦合到第一总线516,以及总线桥518,其中该总线桥518将第一总线516耦合到第二总线520。在一个实施例中,第二总线520可以是少引线数(LPC)总线。在一个实施例中,各种设备可以耦合到第二总线520,其中包括例如键盘/鼠标522、通讯装置526以及诸如可包括代码530的磁盘驱动器或者其它大容量存储装置之类的数据存储单元528。此外,音频I/O 524可耦合到第二总线520。注意,其它的体系结构也是可能的。例如,代替图5的点对点体系结构,系统可以实现多点总线或者其它这样的体系结构。

[0051] 实施例可通过编码来实现,并且可存储在存储介质上,其中已经在该存储介质上存储了用于为系统编制程序使其执行指令的指令。该存储介质可包括但是不局限于任何类型的盘,包括软盘、光盘、光盘只读存储器(CD-ROM)、可重写光盘(CD-RW)、以及磁光盘、半导体装置例如只读存储器(ROM)、随机存取存储器(RAM)例如动态随机存取存储器(DRAM)、静态随机存取存储器(SRAM)、可擦除可编程只读存储器(EPROM)、闪速存储器、电可擦除可编程只读存储器(EEPROM)、磁或光卡、或者任何其它类型的适于存储电子指令的介质。

[0052] 尽管已经针对有限数量的实施例描述了本发明,但是本领域的技术人员能够从中知道多种修改和变化。所附的权利要求覆盖了落入本发明的真正的精神和范围之内的所有这样的修改和变化。

图1

图2

图3

图4

图5