(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6697160号

(P6697160)

(45) 発行日 令和2年5月20日(2020.5.20)

(24) 登録日 令和2年4月28日(2020.4.28)

(51) Int.Cl.

**A63F 5/04 (2006.01)**

F 1

A 6 3 F 5/04 6 1 1 B

A 6 3 F 5/04 6 0 1 C

請求項の数 1 (全 49 頁)

(21) 出願番号 特願2016-176450 (P2016-176450)

(22) 出願日 平成28年9月9日 (2016.9.9)

(65) 公開番号 特開2018-38725 (P2018-38725A)

(43) 公開日 平成30年3月15日 (2018.3.15)

審査請求日 令和1年7月29日 (2019.7.29)

早期審査対象出願

(73) 特許権者 390031783

サミー株式会社

東京都品川区西品川一丁目1番1号住友不

動産大崎ガーデンタワー

(74) 代理人 100092897

弁理士 大西 正悟

(74) 代理人 100157417

弁理士 並木 敏章

(72) 発明者 石原 謙二

東京都豊島区東池袋三丁目1番1号サンシ

ャイン60 サミー株式会社内

(72) 発明者 柴崎 隆行

東京都豊島区東池袋三丁目1番1号サンシ

ャイン60 サミー株式会社内

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

抽選契機を満たすことで抽選を行い、抽選結果に基づいて利益を付与可能な遊技機において、

前記遊技機は、

前記抽選結果に対応する抽選結果信号を送信する主制御手段と、

前記主制御手段から送信される前記抽選結果信号を受信して演出制御の内容を決定し、決定した演出制御の内容に対応する演出制御信号を第1の通信形態で送信する副制御手段と、

前記副制御手段から前記演出制御信号を受信して演出制御を行う複数の演出制御手段と

、

を備え、

前記複数の演出制御手段には、前記副制御手段から送信される前記第1の通信形態の演出制御信号を受信して演出制御を行うことが可能であるとともに、前記演出制御信号を第2の通信形態の演出制御信号に変換して送信することが可能である第1の演出制御手段と、前記第1の演出制御手段から第2の通信形態で送信される前記演出制御信号を受信して演出制御を行うことが可能である第2の演出制御手段とを含み、

前記第1の演出制御手段及び前記第2の演出制御手段は、

前記演出制御信号を受信するための入力部に繋がって前記第1の通信形態の信号を受信することができる第1の入力手段と、

10

20

前記入力部に繋がって前記第2の通信形態の信号を受信することができる第2の入力手段と、

第1の入力手段と第2の入力手段の作動を切替え設定するための第3の入力手段と、

を有し、

前記第1の演出制御手段においては、前記第3の入力手段により前記第1の入力手段を作動させて前記副制御手段から前記第1の通信形態の演出制御信号を受信し、

前記第2の演出制御手段においては、前記第3の入力手段により前記第2の入力手段を作動させて前記第1の演出制御手段から前記第2の通信形態の演出制御信号を受信するよう構成され、

前記第2の演出制御手段は、前記第2の入力手段としてクロック信号入力端子と、データ信号入力端子を有し、出力手段としてクロック信号出力端子とデータ信号出力端子と、を有し

前記クロック信号入力端子から受信するクロック信号に同期して前記データ信号入力端子から前記演出制御信号を受信し、

前記クロック信号入力端子から受信するクロック信号から遅延して前記クロック信号出力端子から出力する前記クロック信号に同期して、前記データ信号入力端子から受信した前記演出制御信号を波形整形して前記データ信号出力端子から送出するリピート機能を有することを特徴とする遊技機。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

本発明は、遊技機において演出装置の制御を行う演出制御装置に関し、特に演出装置への制御情報の送信に特徴を有する遊技機の演出制御装置に関する。

##### 【背景技術】

##### 【0002】

一般的に、スロットマシン、ぱちんこ機等の遊技機には、LEDを用いた表示装置、液晶表示装置、音声発生装置などを用いて構成される演出装置が設けられ、これらにより遊技状態に応じて様々な演出が行なわれる。これらの演出装置の作動は、演出制御装置により、LEDの点灯・点滅表示、液晶表示装置における各種図柄表示、音声発生装置からの音響発生を制御して行なわれる。このため、演出制御装置はCPU上で動作するソフトウェアを備え、このソフトウェアによりLEDの発光制御、液晶表示装置での図柄の演出制御、音声発生装置からの音響による演出制御が行われる。

##### 【0003】

演出装置の一つであるLEDを用いた表示装置は、複数のLEDと、これら複数のLEDによる照明を受けて発光して演出表示を行う発光演出部材とを備え、複数のLEDをそれぞれ発光制御することにより、対応する発光演出部材を発光表示させて所望の演出が行われる。このため、演出制御装置はこれらの複数のLEDの点灯・点滅制御をそれぞれ個別に制御する必要がある。遊技機内には、多様な位置に設けられた複数の発光演出部材の位置に対応して多数のLEDが配設されており、これらLEDの発光制御を行う複数のLED制御回路が発光演出部材に対応して設けられている。演出制御装置とこれらの多様な位置に配設されているLED制御回路との間は所定の接続インターフェイスを介して接続され、LEDの発光輝度制御情報が各LED制御回路に送信される。

##### 【0004】

遊技機には、動作に応じて誘導ノイズを発生する電磁部品が多数使用されており、これら電磁部品からの誘導ノイズが演出制御装置とLED制御回路との間の接続インターフェイスを流れる信号（発光輝度制御情報信号）に重畠され、演出制御装置から各LEDに誤った発光輝度制御情報信号が送られる可能性がある。このため、演出制御装置とLED制御回路を繋ぐ接続インターフェイスを電磁部品から遠ざけたり、電磁部品からの誘導ノイズの影響を受けにくい接続インターフェイスを用いたりする工夫が必要である。

##### 【0005】

30

40

50

演出制御装置はCPUと、ROM、RAM等の記憶素子が設けられて構成されるが、これらの間はパラレルバスで接続されて各種情報の送受信が行われている。このため、演出制御装置とLED制御回路のような各周辺回路との接続インターフェイスにもパラレルバス接続を用いるのが簡単であるが、接続ライン本数が多くなりすぎるという問題がある。そこで、演出制御装置と各種周辺回路とをシリアルインターフェイス（シリアルバスとも呼ばれる）により接続することが一般的に行われている。このシリアルインターフェイスとしては、I2Cバス（I2Cシリアルインターフェイスとも呼ばれる）や、3線シリアルインターフェイスが、遊技機に限らず一般の各種機器で使用されている。

#### 【0006】

I2Cバスはクロック線、データ線の2種類の信号線を使用するインターフェイスであり、3線シリアルインターフェイスはイネーブル線、クロック線、データ線の3種類の信号線を使用するインターフェイスであり、各信号線のそれぞれにより信号が送られる。このため、遊技機内の電磁部品からの誘導ノイズが各信号線を通って送られる信号に重畳されて誤信号が発生する可能性がある。一方、このような誘導ノイズの影響を受けにくい接続インターフェイスとしてLVDSインターフェイス（LVDS信号を用いるインターフェイス）がある。LVDSインターフェイスはクロック信号、データ信号などを2線間の差動電圧の形態で送信するシリアルインターフェイスであり、誘導ノイズがこれら2線に同相で重畳されても、差動電圧は影響を受けないためである。

#### 【0007】

このような遊技機の接続装置構成の一例が特許文献1に開示されている。特許文献1の装置では、メインCPUと副制御回路とをI2Cバスのシリアルインターフェイスを介して接続している。副制御回路ではメインCPUからI2Cシリアルインターフェイスを介して送られてくる情報、例えばLEDの発光輝度制御情報をLVDS信号に変換して、LVDSシリアルインターフェイスを用いてLEDサウンド基板（ここにはLED制御回路を備える）に送信するように構成されている。LEDサウンド基板では、受信したLVDS信号をLED制御信号（LEDの発光輝度制御）に変換してLED制御を行っている。

#### 【先行技術文献】

#### 【特許文献】

#### 【0008】

#### 【特許文献1】特開2012-170790号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

一般的に、演出制御装置とLED制御回路を含む周辺回路との接続インターフェイスは、遊技機に限らず、標準シリアルインターフェイスとして使用されるI2Cバス、または、3線シリアルインターフェイスを用いることが好ましい。しかし、遊技機内に配置された電磁部品からの誘導ノイズの影響を受け易いところには、この影響を受け難いLVDSインターフェイスで接続することが好ましいということも考慮する必要がある。従って、電磁部品からの誘導ノイズの影響を受け難いところでは標準シリアルインターフェイス接続（3線シリアルもしくはI2Cインターフェイス接続）を用い、電磁部品の近くを通るところではLVDSインターフェイス接続を用いるということが考えられる。しかし、このような2種類の異なる接続を用いるとこれらに合わせて2種類の異なるLED制御回路を用いる必要があり、遊技機の設計が複雑になる、コストアップになるというような問題がある。このため、一つのLED制御回路で両方のインターフェイス接続に対応できるようにすることが望ましいが、このような接続は従来では確立されていない。

#### 【0010】

本発明は、このようなことに鑑みてなされたものであり、1種類の演出表示手段を、標準シリアルインターフェイス（I2Cバスまたは3線シリアルインターフェイス）接続にも、LVDSインターフェイス接続にも使用可能な構成とした遊技機を提供することを目的とする。

10

20

30

40

50

**【課題を解決するための手段】****【0011】**

このような目的達成のために、本発明に係る遊技機は、抽選契機を満たすことで抽選を行い、抽選結果に基づいて利益を付与可能な遊技機において、遊技機は、抽選結果に対応する抽選結果信号を送信する主制御手段（例えば、実施形態の主制御基板60、メインCPU61、主制御基板200、メインCPU201、制御装置CD）と、主制御手段から送信される抽選結果信号を受信して演出制御情報の内容を決定し、決定した演出制御情報の内容に対応する演出制御信号を第1の通信形態で送信する副制御手段（例えば、実施形態のサブメイン制御基板70A、サブメインCPU71、演出制御基板300、サブメインCPU301、制御装置CD）と、副制御手段から演出制御情報を受信して演出制御を行う複数の演出制御手段（例えば、実施形態のLED制御回路LC）と、を備え、複数の演出制御手段には、副制御手段から送信される第1の通信形態（例えば、実施形態のI2Cバス、3線シリアルインターフェイス、標準シリアルインターフェイス）の演出制御信号を受信して演出制御を行うことが可能であるとともに、演出制御信号を第2の通信形態（例えば、実施形態のLVDSインターフェイス）の信号に変換して送信することが可能である第1の演出制御手段と、第1の演出制御信号から第2の通信形態で送信される演出制御信号を受信して演出制御を行うことが可能である第2の演出制御手段とを含み、第1の演出制御手段及び第2の演出制御手段は、演出制御信号を受信するための入力部に繋がって第1の通信形態の信号を受信することができる第1の入力手段（例えば、実施形態の入力回路IC1、IC2、IC2）と、入力部に繋がって第2の通信形態の信号を受信することができる第2の入力手段（例えば、実施形態の差動入力回路DIC1、DIC2）と、第1の入力手段と第2の入力手段の作動を切替え設定するための第3の入力手段（例えば、実施形態のモード指定端子MODE）と、を有し、第1の演出制御手段においては、第3の入力手段により第1の入力手段を作動させて副制御手段から第1の通信形態の演出制御信号を受信し、第2の演出制御手段においては、第3の入力手段により第2の入力手段を作動させて1の演出制御手段から第2の通信形態の演出制御信号を受信するように構成され、第2の演出制御手段は、第2の入力手段としてクロック信号入力端子（例えば、実施形態の差動クロック信号入力端子（DCI1、DCI2）と、データ信号入力端子（例えば、実施形態の差動データ信号入力端子（DDI1、DDI2）を有し、出力手段としてクロック信号出力端子（例えば、実施形態の差動クロック信号出力端子（DCO1、DCO2）とデータ信号出力端子（例えば、実施形態の差動データ信号出力端子（DDO1、DDO2）と、を有し、クロック信号入力端子から受信するクロック信号に同期してデータ信号入力端子から演出制御信号を受信し、クロック信号入力端子から受信するクロック信号から遅延してクロック信号出力端子から出力するクロック信号に同期して、データ信号入力端子から受信した演出制御信号を波形整形してデータ信号出力端子から送出するリピート機能を有することを特徴とする。

**【発明の効果】****【0012】**

上記構成の遊技機によれば、1種類の演出出力制御手段を、標準シリアルインターフェイス（I2Cバスまたは3線シリアルインターフェイス）接続およびLVDSインターフェイス接続のいずれによっても使用可能となり、装置構成が簡単となり、装置設計が容易となり、装置のコストダウンを図ることができる。

**【図面の簡単な説明】****【0013】**

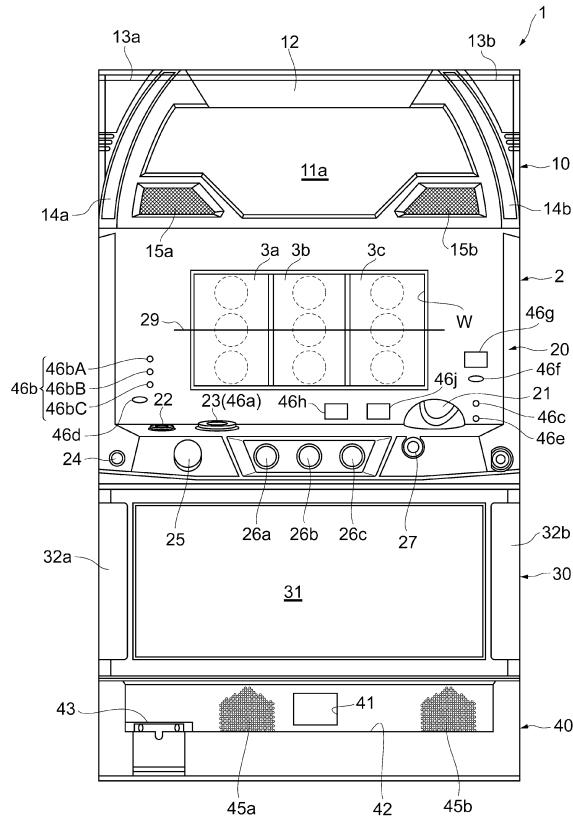

【図1】第1実施形態に係る、スロットマシンの正面図である。

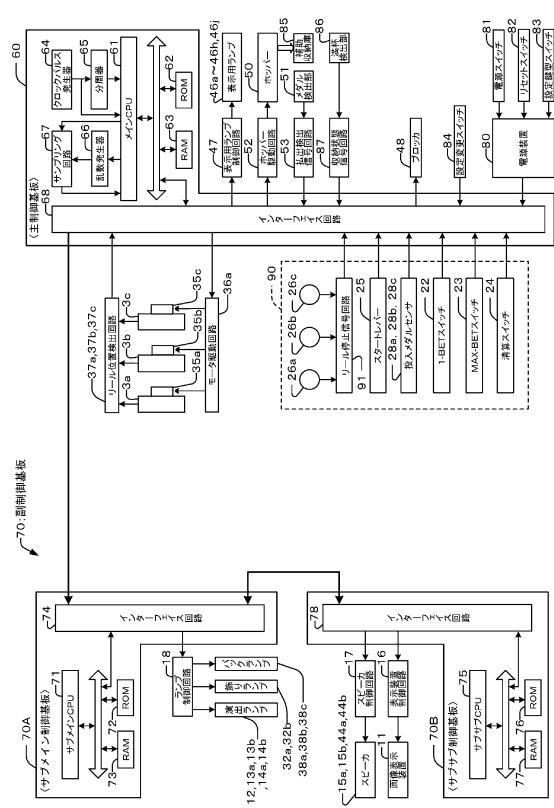

【図2】上記スロットマシンの制御ブロック図である。

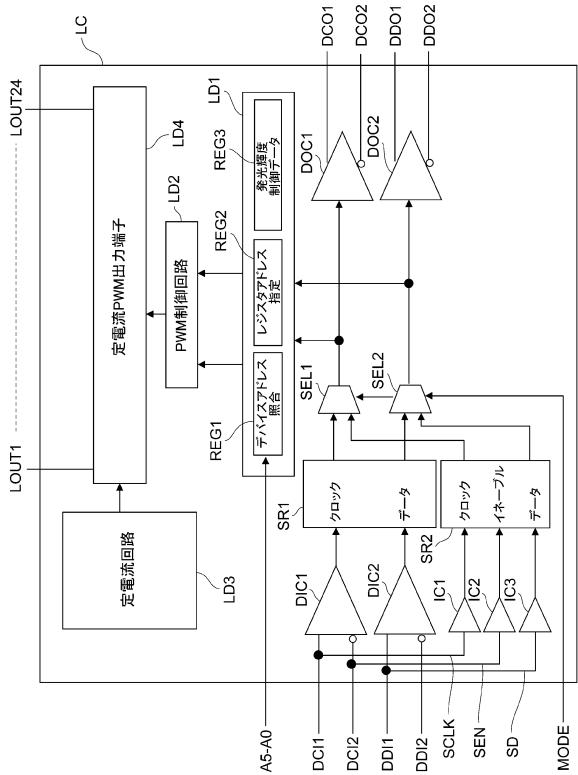

【図3】LED制御回路の機能ロック図である。

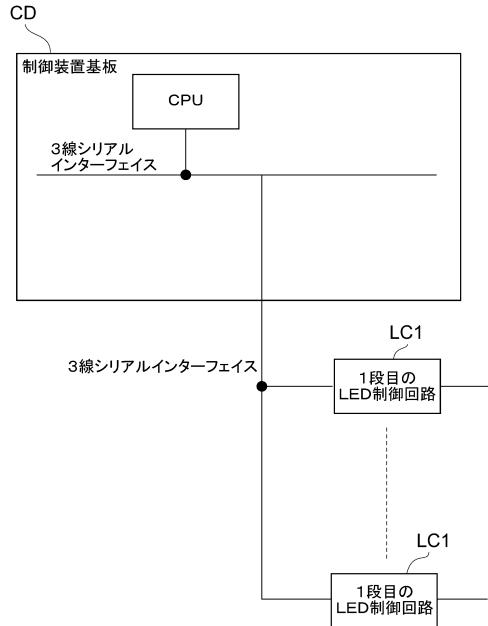

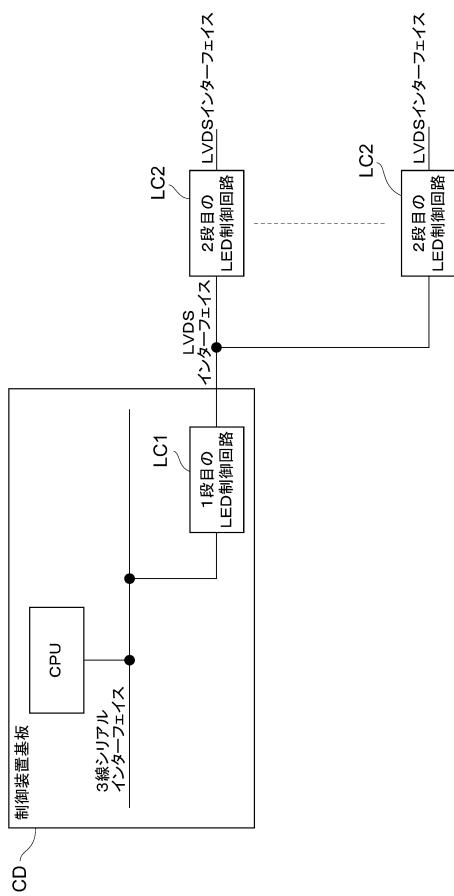

【図4】制御装置とLED制御回路との接続例を示す接続説明図である。

【図5】制御装置とLED制御回路との別の接続例を示す接続説明図である。

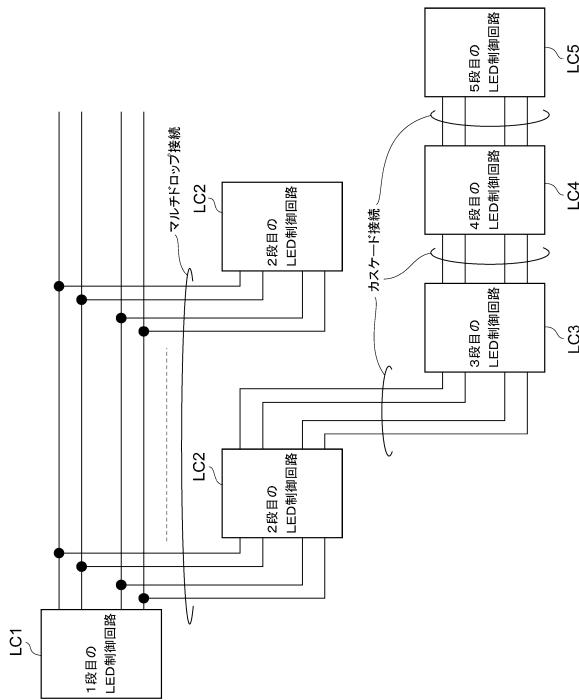

【図6】複数のLED制御回路のマルチドロップ接続例、カスケード接続例を示す接続説

10

20

30

40

50

明図である。

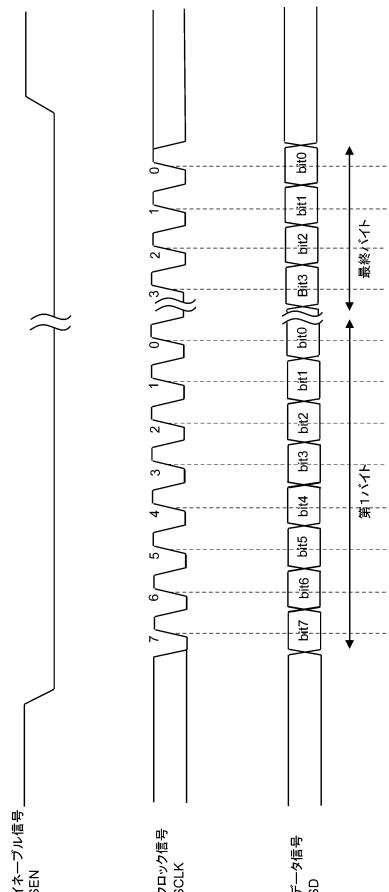

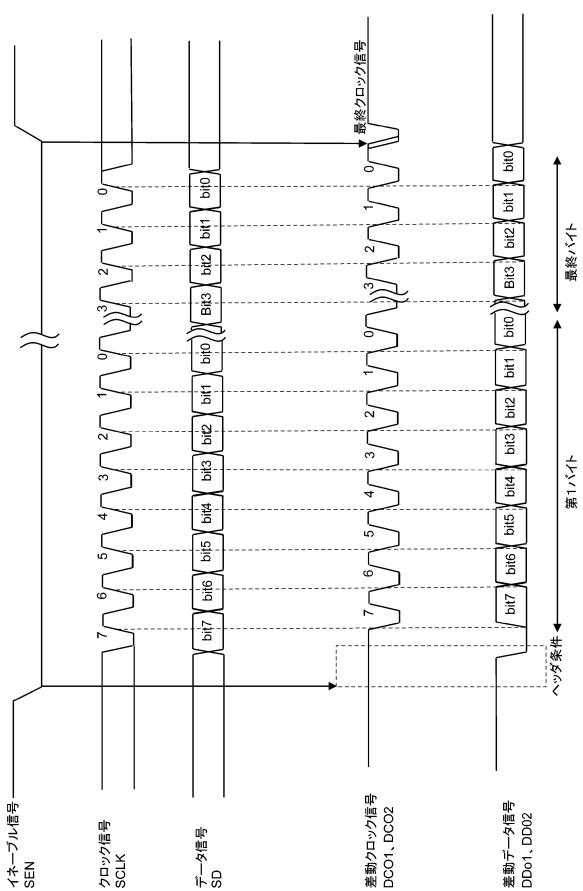

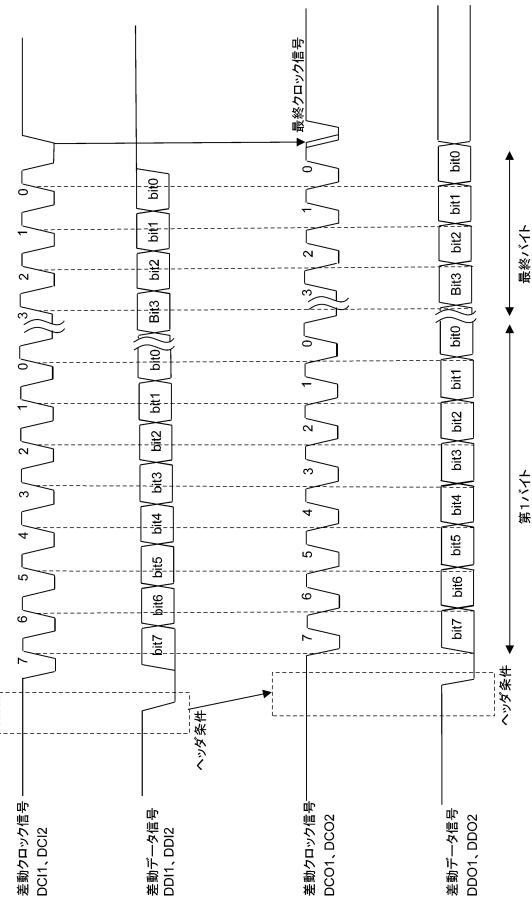

【図7】3線シリアルインターフェイスのイネーブル信号、クロック信号、データ信号の時間変化を示すタイムチャートである。

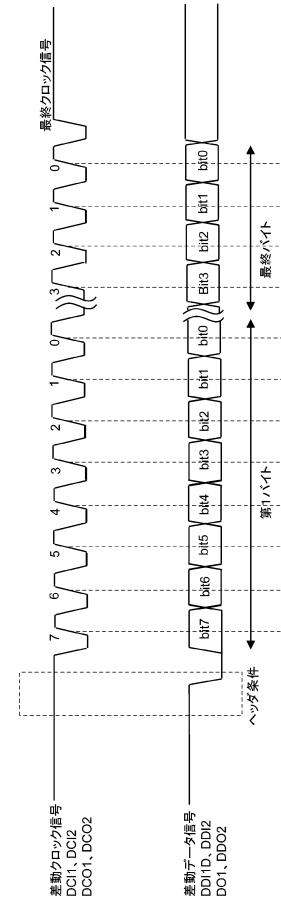

【図8】LVDSインターフェイスのクロック信号、データ信号の時間変化を示すタイムチャートである。

【図9】3線シリアルインターフェイスからLVDSインターフェイスへの3線 2線ブリッジ機能を示すための各信号の時間変化を示すタイムチャートである。

【図10】LVDSインターフェイスからLVDSインターフェイスへの2線 2線リピータ機能を示すための各信号の時間変化を示すタイムチャートである。

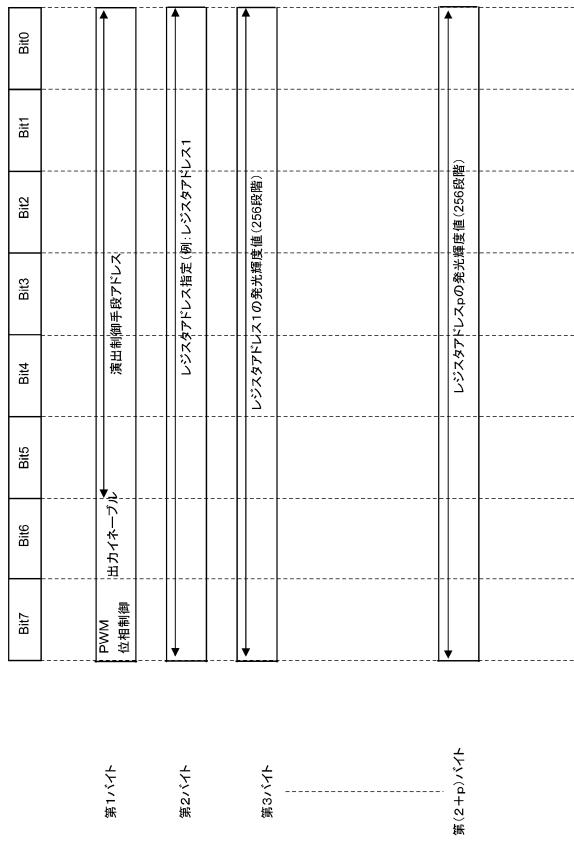

【図11】演出制御情報のバイト構成、ビット構成を示す模式図である。 10

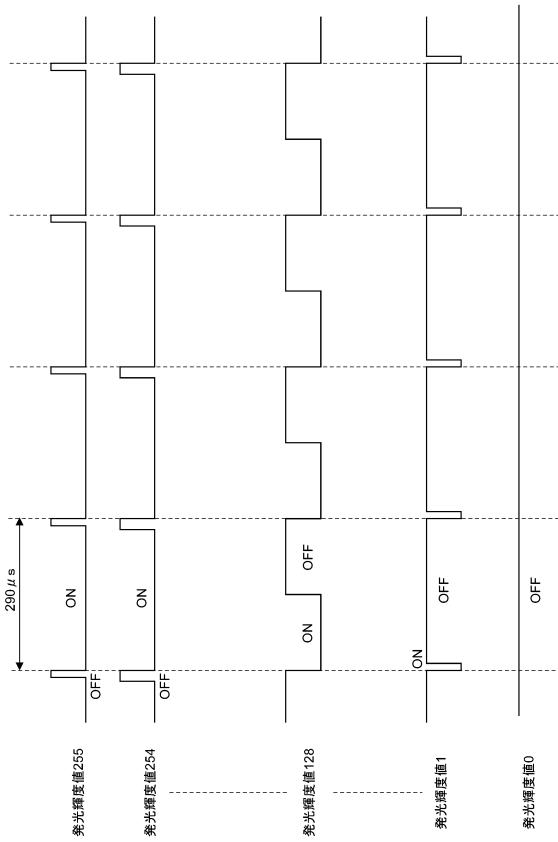

【図12】LED制御回路の発光輝度値とPWM制御の関係を示す模式図である。

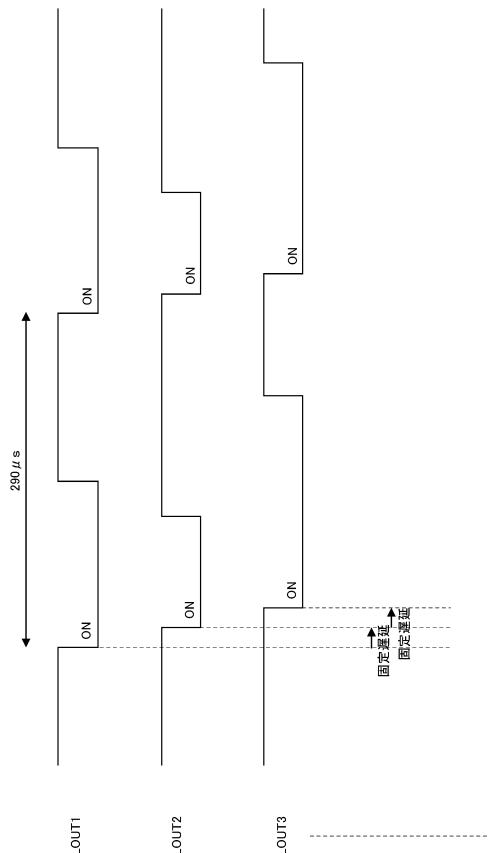

【図13】LED制御回路のPWM位相制御の個別制御を示す模式図である。

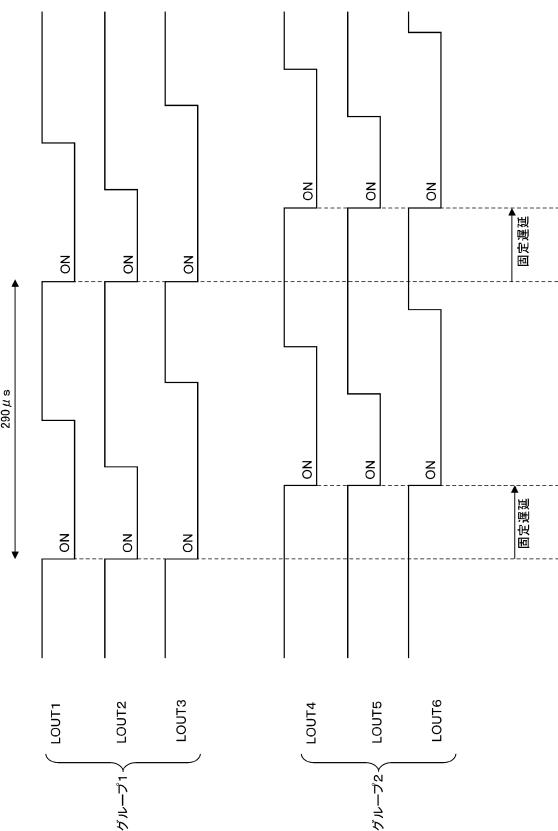

【図14】LED制御回路のPWM位相制御のグループ制御を示す模式図である。

【図15】LED制御回路のPWM位相制御のグループ制御を示す模式図である。

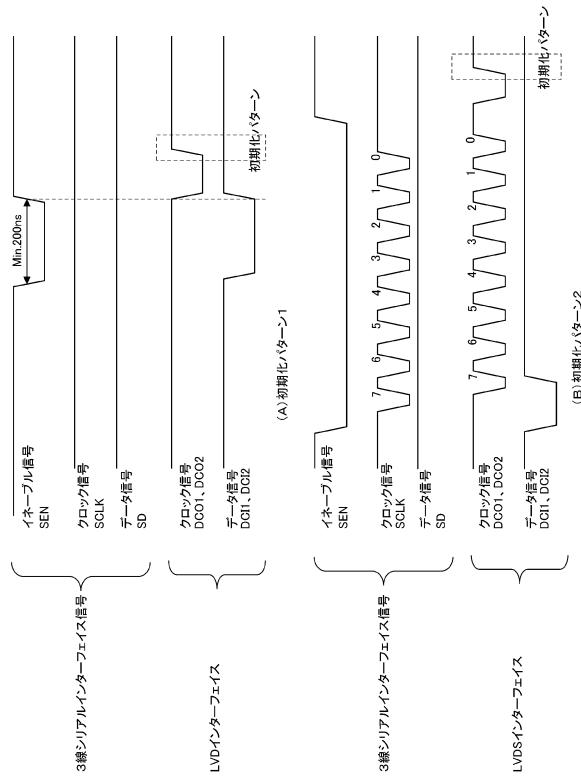

【図16】(A)は初期化パターン1を示すタイムチャートである。(B)は初期化パターン2を示すタイムチャートである。

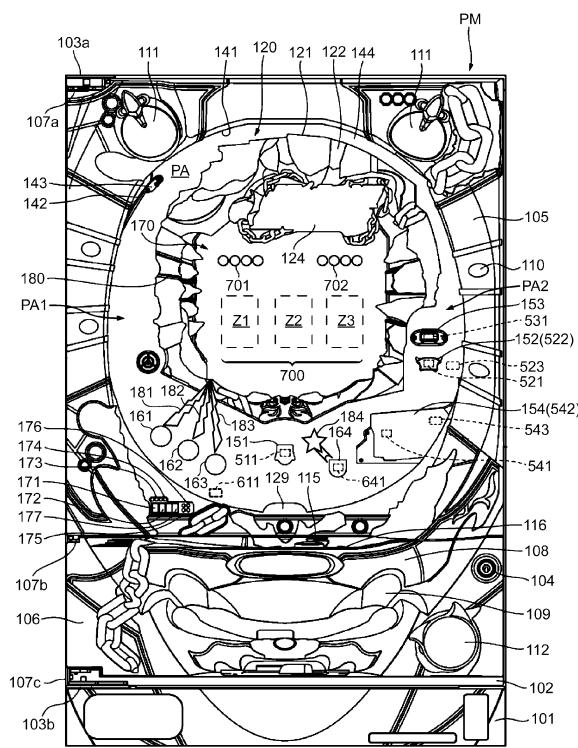

【図17】第2実施形態に係る、ぱちんこ遊技機の正面図である。

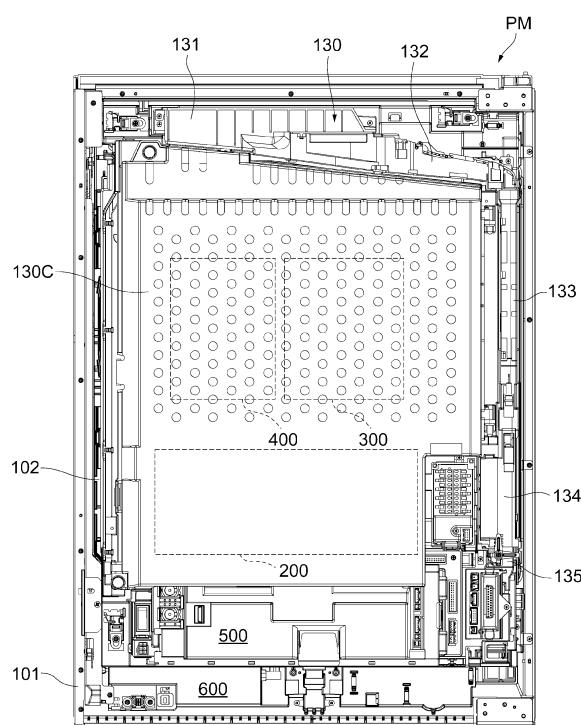

【図18】上記ぱちんこ遊技機の背面図である。

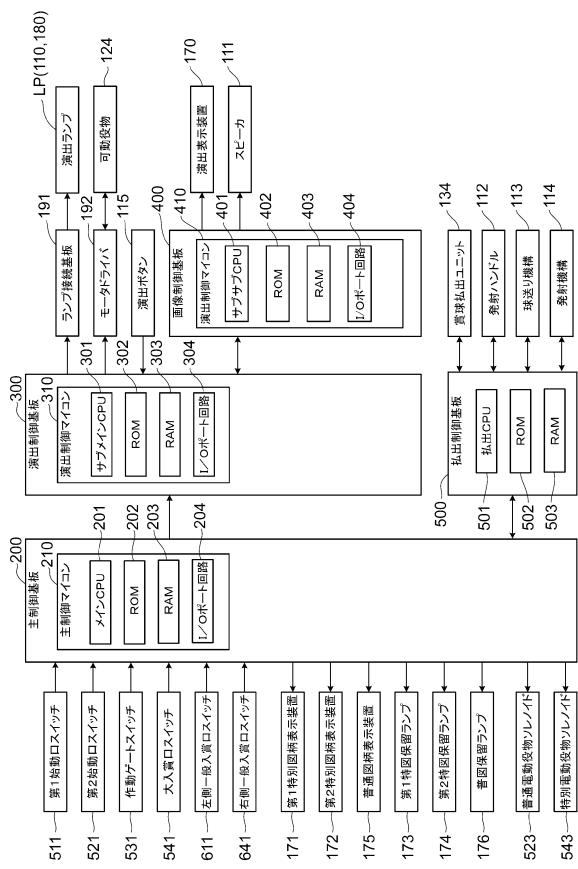

【図19】上記ぱちんこ遊技機の制御プロック図である。

【発明を実施するための形態】 20

【0014】

[第1実施形態]

以下、本発明に係る遊技機の一実施形態としてのスロットマシン(図1参照)について説明する。まず、スロットマシンの構成について図1、図2を参照しながら説明する。

【0015】

<スロットマシンの外観>

本実施形態に係るスロットマシンは、図1に示すように、本体筐体の前面に開閉可能に取り付けられた前扉2を備えており、この前扉2の前面には、上部から順に、上パネルアセンブリ10、中パネルアセンブリ20、下パネルアセンブリ30及び受け皿アセンブリ40が取り付けられている。 30

【0016】

上記上パネルアセンブリ10の中央部には、その裏面側に配された画像表示装置(液晶表示装置)11(図2参照)の表示画面11aが前方を臨むように配置されており、その周辺部には、第1演出ランプ12、第2演出ランプ13a, 13b、第3演出ランプ14a, 14bが配置されている。表示画面11aの下方左右には、一対の上部スピーカ15a, 15bが配置されている。これら演出ランプはそれぞれ、外部から視認されるランプ表示部(演出表示部材)およびその裏側に設けられたLEDから構成され、LEDからの照明によりランプ表示部が発光する構成となっており、これをLEDランプとも称する。すなわち、第1演出ランプ12、第2演出ランプ13a, 13b、第3演出ランプ14a, 14bはLEDランプ構成であり、LEDの発光制御によりランプ表示部の発光制御が行われる。 40

【0017】

上記中パネルアセンブリ20の中央部には、本体筐体内に横並びに配設された3個のリール3a, 3b, 3cの表面が臨む表示窓Wが設けられており、この表示窓Wの下方には、遊技メダル(遊技媒体)を投入するためのメダル投入口21、クレジットされた範囲内で1枚の遊技メダルをベットするための1-BETスイッチ22、最大ベット許容数(例えば3枚)の遊技メダルを一度にベットするためのMAX-BETスイッチ23、ベットされた遊技メダル、および/または、クレジットされた遊技メダルを払い出すための清算スイッチ24、全リール3a, 3b, 3c(リールのことを「回胴」とも称する)を回転開始させる際に操作されるスタートレバー(スタートスイッチ)25、各リール3a, 3

50

b, 3 c の回転を個別に停止させるための 3 個のストップスイッチ 2 6 a, 2 6 b, 2 6 c (図中左側のストップスイッチ 2 6 a はリール 3 a に対応し、中央のストップスイッチ 2 6 b はリール 3 b に対応し、右側のストップスイッチ 2 6 c はリール 3 c に対応する)、及びメダル投入口 2 1 から投入されて滞留した遊技メダルを返却するためのリジェクトスイッチ 2 7 等が設けられている。

#### 【0018】

上記メダル投入口 2 1 の内部は、投入された遊技メダルが有効に受け入れられる場合に当該遊技メダルが通過する受入通路 (後述のホッパー 5 0 に通ずる) と、投入された遊技メダルが受け入れられない場合に当該遊技メダルが通過する返却通路 (後述の遊技メダル払出口 4 1 に通ずる) とに分岐しており、その分岐部には、ブロック 4 8 (図 2 参照) が設けられている。このブロック 4 8 は、投入された遊技メダルが有効に受け入れられる期間においては、メダル投入口 2 1 に投入された遊技メダルを受入通路に導き、それ以外の期間においては、メダル投入口 2 1 に投入された遊技メダルを返却通路に導くように、受入通路と返却通路を選択的に、一方を開状態に他方を閉状態にできるように構成されている。以下の説明において、ブロック 4 8 が O N 状態とは、メダル投入口 2 1 に投入された遊技メダルが受入通路に導かれる状態 (遊技メダル受入可能状態) を示し、ブロック 4 8 が O F F 状態とは、メダル投入口 2 1 に投入された遊技メダルが返却通路に導かれる状態 (遊技メダル受入不可状態) を示すものとする。

#### 【0019】

メダル投入口 2 1 の内部には、遊技メダルを検知するための 3 つの投入メダルセンサ 2 8 a, 2 8 b, 2 8 c (図 2 参照) が設けられている。投入メダルセンサ 2 8 a は、遊技メダルがメダル投入口 2 1 に投入されたことを検出するものであり、投入された遊技メダルが流下する通路上において、上記ブロック 4 8 が設置された位置よりも上流側の位置に設置されている。投入メダルセンサ 2 8 b は、メダル投入口 2 1 に投入された遊技メダルが受入通路に導かれ有効に受け入れられたことを検出するものであり、上記ブロック 4 8 が設置された位置よりも下流側 (後述のホッパー 5 0 寄り) の位置に配置されている。投入メダルセンサ 2 8 c は、メダル投入口 2 1 に投入された遊技メダルが、受入通路と返却通路との分岐部を通過したことを検出するものであり、当該分岐部近傍 (ブロック 4 8 が設置された位置よりも少し投入メダルセンサ 2 8 b 寄りの位置) に配置されている。

#### 【0020】

投入メダルセンサ 2 8 a 及び投入メダルセンサ 2 8 b が共に遊技メダルを検出した場合は、遊技メダルがメダル投入口 2 1 に投入され、かつ投入された遊技メダルが有効に受け入れられたことを意味する。一方、投入メダルセンサ 2 8 a は遊技メダルを検出したが、投入メダルセンサ 2 8 b は遊技メダルを検出しない場合は、遊技メダルがメダル投入口 2 1 に投入されたが、投入された遊技メダルが有効に受け入れられずに返却されたことを意味する。3 つの投入メダルセンサ 2 8 a, 2 8 b, 2 8 c が所定の順序 (2 8 a, 2 8 c, 2 8 b の順序) とは異なる順序で遊技メダルの通過を検出した場合や一部の投入メダルセンサで遊技メダルの通過が検出されない場合は、遊技メダルが逆流するなどの異常通過が起きたことを意味する。

#### 【0021】

上記表示窓 W は、3 個のリール 3 a ~ 3 c が全て停止した際に、リール毎に 3 個の図柄、合計 9 個の図柄が遊技者から視認可能に表示されるように構成されている。リール 3 a ~ 3 c の各中段の図柄表示領域を水平 (横一直線) に結ぶ入賞ライン 2 9 は、規定数の遊技メダルがベットされることにより有効化される入賞ラインであり、有効化された入賞ライン 2 9 上に停止表示された図柄組合せにより遊技役の成立の有無が判定されるように構成されている。以下、有効化された入賞ライン 2 9 のことを、適宜「有効ライン 2 9」と称する。

#### 【0022】

スロットマシンには、各種の表示用ランプが配置されている。本実施形態では、表示用ランプとして、MAX - BET スイッチ表示ランプ 4 6 a、BET 数表示ランプ 4 6 b、

10

20

30

40

50

投入可能表示ランプ46c、遊技開始表示ランプ46d、再遊技表示ランプ46e、状態表示ランプ46f、回数表示ランプ46g、貯留枚数表示ランプ46h、及び払出数表示ランプ46jを備えている。これらの表示用ランプは、後述の主制御基板60（主制御手段100）により制御されるように構成されている。これら表示用ランプもそれぞれ、外部から視認されるランプ表示部（演出表示部材）およびその裏側に設けられたLEDから構成されるLEDランプ構成であり、LEDの発光制御によりランプ表示部の発光制御が行われる。

#### 【0023】

MAX-BETスイッチ表示ランプ46aは、遊技メダルをベットすることができる状況下で点灯されるものであり、MAX-BETスイッチ23の内部に配置され、点灯時にはMAX-BETスイッチ23を部分的または全体的に光らせるようになっている。その他の表示用ランプは、上記中パネルアセンブリ20において表示窓Wの側部または下部に配置されている。

#### 【0024】

BET数表示ランプ46b（以下「BETランプ46b」とも称する）は、ベットされた遊技メダルの枚数を表示するもので、ベットされた遊技メダルが、1枚の場合に点灯される1-BET表示ランプ46bAと、2枚の場合に点灯される2-BET表示ランプ46bBと、3枚の場合に点灯される3-BET表示ランプ46bCとから構成されている。投入可能表示ランプ46cは、遊技メダルを投入することができる状況下で点灯される。遊技開始表示ランプ46dは、スタートレバー25を操作して遊技を開始させることができる状況下で点灯される。再遊技表示ランプ46eは、任意の遊技において後述の再遊技役が成立し、後述の自動ベット処理により遊技メダルが自動的にベットされた際に点灯される。

#### 【0025】

状態表示ランプ46fは、貯留されているメダルを精算するときに点灯される。貯留枚数表示ランプ46h（以下「CREランプ46h」とも称する）は、貯留（クレジット）された遊技メダルの枚数を7セグメント表示する。払出数表示ランプ46j（以下「WINランプ46j」とも称する）は、後述の小役が成立した際に払い出される遊技メダルの枚数を7セグメント表示する。

#### 【0026】

このWINランプ46jは、スロットマシンに何らかの異常（エラー）が発生した際に、そのエラーの種類を示す文字（アルファベット）を表示するようにも構成されている。本実施形態において設定されるエラーとしては、HPエラー、HEエラー、H0エラー、CEエラー、CPエラー、CHエラー、C0エラー、C1エラー、FEエラー、E1エラー、E5エラー、E6エラー、E7エラー等がある。HPエラーは、後述するメダル検出部51の払出センサにより遊技メダルの通過に異常があったと判断した場合のエラーであり、HEエラーは、後述のホッパー50の中の遊技メダルが空と判断した場合のエラー（ホッパーエンプティエラー）であり、H0エラーは、払出センサに異常入力があったと判断したときのエラーである。CEエラーは、投入メダルセンサにより遊技メダルが滞留したと判断した場合のエラー（遊技メダル滞留エラー）であり、CPエラーは、投入された遊技メダルが不正通過したと判断した場合のエラーであり、C0エラーは、投入メダルセンサに異常入力があったと判断したときのエラーであり、C1エラーは投入メダルセンサの通過に異常があったと判断した場合のエラーである。FEエラーは、後述の補助収納庫85が満杯と判断した場合のエラー（補助収納庫満杯エラー）であり、E1エラーは、電源復帰が正常に行えない場合のエラーであり、E5エラーは、全回胴停止時の図柄の組合せが異常（成立許容役以外の役を構成する対応図柄が停止表示）となる場合のエラーであり、E6エラーは、役決定確率を定めるための設定値が範囲外となる場合のエラーであり、E7エラーは、各抽選等において用いる乱数の更新状態の異常を検知した場合のエラーである。E1、E5、E6、E7の各エラー（これらを総称して「E系エラー」とも称する）は、後述の設定変更により解除され、その他のエラーは、後述のリセットスイッチ8

10

20

30

40

50

2の操作により解除されるようになっている。

**【0027】**

このWINランプ46jは、ストップスイッチ26a～26cの操作順（押し順）を示す、後述のナビ番号を表示する機能も有している。以下、ナビ順番号を表示する際のWINランプ46jのことを、適宜「メイン側押し順表示器」と称する。

**【0028】**

上記下パネルアセンブリ30の中央部には、透明な下パネルカバー31が取り付けられており、その左右両端部には、飾りランプ32a, 32bが配置されている。下パネルカバー31の裏面側には、所定の図柄が設けられた半透明の下パネルベース及び下パネル照明灯（いずれも図示せず）が取り付けられており、この下パネル照明灯を点灯させることにより、下パネルベースの図柄を後面側から照明するように構成されている。これら飾りランプ32a, 32bもそれぞれ、外部から視認されるランプ表示部（演出表示部材）およびその裏側に設けられたLEDから構成されるLEDランプ構成であり、LEDの発光制御によりランプ表示部の発光制御が行われる。

10

**【0029】**

上記受け皿アセンブリ40には、遊技メダルを払い出すための遊技メダル払出口41が開設されているとともに、遊技メダル払出口41に臨むようにして遊技メダルを貯留するための遊技メダル貯留皿42が設けられており、この遊技メダル貯留皿42の左には、灰皿43が設けられている。遊技メダル払出口41の左右には、受け皿アセンブリ40の背面側に配置された一対の下部スピーカ44a, 44b（図2参照）の前面に対向して、多数の小孔からなるスピーカ口45a, 45bが形成されている。

20

**【0030】**

本体筐体内には、遊技の結果、所定の入賞態様が構成された場合に獲得される遊技メダルを払い出すためのホッパー50（図2参照）が設けられており、このホッパー50には遊技メダルを検出するためのメダル検出部51（図2参照）が設けられている。このホッパー50は、投入されて有效地に受け入れられた遊技メダルを物理的に収容する機能を有している。ホッパー50の近傍位置には、ホッパー50から溢れた遊技メダルを収納するための補助収納庫85（図2参照）が設けられるとともに、この補助収納庫85が満杯状態（助収納庫85から遊技メダルが溢れる可能性のある状態）であるか否かを検出する満杯検出部86（図2参照）が設けられている。

30

**【0031】**

<リール>

各リール3a, 3b, 3cはそれぞれステッピングモータ35a, 35b, 35c（図2参照）の駆動により回転するように構成されている。各リール3a, 3b, 3cは透光性を有する部材により構成されており、その外周面には、複数種類の図柄（図3参照）が表示された、透光性を有するリールテープが貼り付けられている。各リール3a, 3b, 3cの内面側には、バックランプ38a, 38b, 38c（図2参照）が配設されており、このバックランプ38a, 38b, 38cを点灯させることにより、表示窓W内に臨む各リール3a, 3b, 3cの領域を内面側から全体的に照明したり、各リール3a, 3b, 3c上に停止表示された所定の図柄組合せ（例えば、有効ライン29上や、有効ライン29上とは異なる入賞ライン上に並んだ遊技役の対応図柄等）を目立たせるように各リール3a, 3b, 3cの一部領域のみを照明したりするように構成されている。これらのバックランプはLEDが用いられている。

40

**【0032】**

<遊技を行うための基本操作>

スロットマシンで遊技を行うには、まず実際にメダル投入口21に遊技メダルを投入することによりベットするか、1-BETスイッチ22またはMAX-BETスイッチ23の何れかを操作してクレジットの範囲内で規定数の遊技メダルをベットすることにより、複数の入賞ラインのうち入賞ライン29を有効化する。本実施形態では、入賞ライン29を有効化するために必要となる遊技メダルの規定数が、後述する非RT、RT1～RT5

50

、B B - A、B B - B の各遊技状態の何れにおいても 3 枚に設定される。ただし、規定数についてはこれに限定されるものではなく、R T 状態等に応じて規定数を異なる値に設定するなど、適宜変更することが可能である。遊技メダルのベット数に応じて、有効化される入賞ラインを変更するようにしてもよい。

#### 【 0 0 3 3 】

次に、遊技者がスタートレバー 2 5 を操作すると、ベット数が確定する（ベットされた遊技メダルが遊技の用に供される）とともに、後述する役決定処理が行われ、その後、最小遊技時間（1つの遊技において全リールが回転開始してから、次の遊技において全リールを回転開始させるまでに最低限確保しなければならないとされる時間（例えば、4.1 秒間）のこと）が経過したことを確認した後、各リール 3 a ~ 3 c が回転を開始し、リール 3 a ~ 3 c の外周表面に表示された複数種類の図柄が表示窓 W 内を上下に（通常、上から下に）移動表示される。そして、リール 3 a ~ 3 c の回転が所定の速度に達して定速回転となると各ストップスイッチ 2 6 a ~ 2 6 c が有効化され（ストップスイッチの操作が有効に受付け可能とされ）、遊技者がストップスイッチ 2 6 a を操作するとリール 3 a の回転が停止し、ストップスイッチ 2 6 b を操作するとリール 3 b の回転が停止し、ストップスイッチ 2 6 c を操作するとリール 3 c の回転が停止するように構成されている。10

#### 【 0 0 3 4 】

ここで、有効ライン 2 9 上に停止表示された図柄組合せが予め定めた入賞態様（遊技メダルを獲得することができる遊技役の対応図柄）となっている場合には、各入賞態様に対応した枚数の遊技メダルがホッパー 5 0 により払い出されるか、またはクレジットとして加算される。20

#### 【 0 0 3 5 】

##### < 制御基板と各機器との接続 >

本実施形態では、スロットマシンを制御する主な制御基板として図 2 に示すように、主制御基板 6 0 、サブメイン制御基板 7 0 A 、及びサブサブ制御基板 7 0 B の 3 つの制御基板を備えている（サブメイン制御基板 7 0 A とサブサブ制御基板 7 0 B を総称して副制御基板 7 0 と称する）。遊技の進行に係る主たる制御（リール 3 a ~ 3 c の駆動制御や役決定処理等を含む）が主制御基板 6 0 上に配設された制御回路により行われ、バックランプ 3 8 a ~ 3 8 c 等のランプによる照明制御等は、サブメイン制御基板 7 0 A 上に配設されたランプ制御回路 1 8 により行われるように構成されている。画像表示装置 1 1 による演出画像表示制御、上部スピーカ 1 5 a , 1 5 b 等のスピーカからの音声発生制御は、主に、サブサブ制御基板 7 0 B 上に配設された制御回路により行われるように構成されている。主制御基板 6 0 と副制御基板 7 0 との間の情報伝達は、主制御基板 6 0 からサブメイン制御基板 7 0 A への一方向のみ行うことが可能となっており、サブメイン制御基板 7 0 A とサブサブ制御基板 7 0 B との間の情報伝達は、双方向で行うことが可能となっている。30

#### 【 0 0 3 6 】

主制御基板 6 0 には、遊技に関する各種の演算処理を行うメイン C P U 6 1 と、制御プログラム等を記憶した読み出し専用の記憶装置である R O M 6 2 と、情報の書き込み及び読み出しが可能な記憶装置である R A M 6 3 とが配設されており、R O M 6 2 に記憶された制御プログラムに従って各駆動回路等が動作することにより、スロットマシンにおける遊技の進行に係る制御が行われるようになっている。上記 R O M 6 2 及び R A M 6 3 は不揮発性の記憶装置であり、電力が供給されない場合でも記憶している情報を保持し得るように構成されている。メイン C P U 6 1 と、R O M 6 2 および R A M 6 3 とはパラレルバス接続されて情報の授受が行われる構成となっている。40

#### 【 0 0 3 7 】

上記メイン C P U 6 1 には、駆動パルスを発生するためのクロックパルス発生器 6 4 、クロックパルス発生器 6 4 で発生した駆動パルスを分周するための分周器 6 5 、役決定処理（役抽選）等に用いる乱数を発生するための乱数発生器 6 6 、及び乱数発生器 6 6 で発生した乱数をサンプリングして抽選を行うためのサンプリング回路 6 7 が接続されている。クロックパルス発生器 6 4 及び分周器 6 5 は、メイン C P U 6 1 に対し、所定の時間毎50

に割込みを発生させるためのインターバルタイマとしても機能するように構成されている。メインC P U 6 1は、このインターバルタイマからのパルス（クロック信号）に応じて、所定の割込処理を実行したり、設定した各種タイマの計時データの更新やリセットを行ったりするようになっている。主制御基板6 0のパラレルバスはインターフェイス回路6 8に接続され、インターフェイス回路6 8は、パラレルバス延長機能と、パラレルバスと3線シリアルバスのインターフェイス変換機能とを有し、主制御基板6 0と副制御基板7 0との間はパラレルバス延長機能によってパラレルバス接続し、主制御基板6 0と、周辺回路（モータ駆動回路3 6 a、スイッチ基板9 0、表示用ランプ制御回路4 7、ホッパー駆動回路5 2、リール位置検出回路3 7 a, 3 7 b, 3 7 c、払出検出信号回路5 3及び収納状態信号回路8 7）との間は、インターフェイス変換機能によって3線シリアルインターフェイスで接続するよう構成されている。このため、メインC P U 6 1はパラレルバス接続を用いてサブメインC P U 7 1へ信号送信を行う。また、メインC P U 6 1は、3線シリアルインターフェイス接続を用いて、モータ駆動回路3 6 a、表示用ランプ制御回路4 7、ホッパー駆動回路5 2に信号送を行とともに、リール位置検出回路3 7 a, 3 7 b, 3 7 c、スイッチ基板9 0、払出検出信号回路5 3及び収納状態信号回路8 7からの信号を受信するよう構成されている。なお、主制御基板6 0と周辺回路との接続では3線シリアルインターフェイ接続構成が用いられているが、これに替えてI C 2バス（I 2 Cシリアルインターフェイス）接続を用いてもよい。また、メインC P U 6 1からサブメインC P U 7 1への信号送信はパラレルバス接続に限定されない。メインC P U 6 1からサブメインC P U 7 1へ3線シリアルインターフェイス接続を用いて信号送信してもよい。10

20

#### 【0038】

モータ駆動回路3 6 aは、リール3 a, 3 b, 3 cをそれぞれ回転駆動するステッピングモータ3 5 a, 3 5 b, 3 5 cの回転・停止制御を行うための回路であり、表示用ランプ制御回路4 7は、上述した各種の表示用ランプの制御を行うための回路である。上述のように表示用ランプ制御回路4 7との接続ではインターフェイス回路6 8において3線シリアルインターフェイスにインターフェイス変換されるため、表示用ランプ制御回路4 7では3線シリアルインターフェイス信号の形態で送られてくるL E D発光制御情報信号をL E D制御信号に変換し、表示用ランプ4 6 a ~ 4 6 h, 4 6 jの発光制御が行われる。但し、表示用ランプ4 6 a ~ 4 6 h, 4 6 jに至る配線部分に電磁部品からの誘導ノイズの影響を受けることを考えて、L V D Sインターフェイス接続も用いられるが、これについては後述する。リール位置検出回路3 7 a, 3 7 b, 3 7 cは、リール3 a, 3 b, 3 cの各々に設置されたリールセンサ（図示せず）からの各検出信号に基づき、リール3 a, 3 b, 3 cの回転位置をそれぞれ検出する回路である（検出回路3 7 aはリール3 aに対応し、検出回路3 7 bはリール3 b、検出回路3 7 cはリール3 cに対応する）。ホッパー駆動回路5 2は、小役が成立した際に、ホッパー5 0を駆動して遊技メダルの払い出を行わせる回路であり、払出検出信号回路5 3は、ホッパー5 0から遊技メダルが払い出されたことがメダル検出部5 1により検出された際に、主制御基板6 0に払出検出信号を送信する回路である。さらに、収納状態信号回路8 7は、補助収納庫8 5が満杯状態であるか否かを示す収納状態信号を、上記満杯検出部8 6の検出結果に応じて、主制御基板6 0に送信する回路である。30

40

#### 【0039】

このスロットマシンには、電源装置8 0からの電力が主制御基板6 0を介して供給されるようになっている。この電源装置8 0には、電源スイッチ8 1、リセットスイッチ8 2及び設定鍵型スイッチ8 3が接続されており、これら各スイッチからの信号がインターフェイス回路6 8を介して、メインC P U 6 1に送信されるよう構成されている。メインC P U 6 1は、インターフェイス回路6 8を介して、設定変更スイッチ8 4からの信号を受信するよう構成されている。

#### 【0040】

電源スイッチ8 1は、電源装置8 0からスロットマシンへの電源投入及び電源断の操作

50

を受け付けるスイッチであり、リセットスイッチ 8 2 は、スロットマシンにおいて所定のエラー（上述の E 系エラーを除くエラー）が発生した場合に、エラーの原因が取り除かれてエラーが解消された際に遊技店員等により操作されるスイッチである。このリセットスイッチ 8 2 が操作されることにより、主制御基板 6 0 及び副制御基板 7 0 において記憶されたエラー発生の情報がクリアされ、それに伴いエラー解消時の処理が主制御基板 6 0 及び副制御基板 7 0 において実行される。設定鍵型スイッチ 8 3 は、役決定確率（遊技役の当選確率）等の設定確認及び設定変更を行う場合に操作されるスイッチであり、設定変更スイッチ 8 4 は、役決定確率等の設定（設定値）を、例えば 6 段階で変更するためのスイッチである。

## 【0041】

10

前扉 2 が開いた状態（以下「ドア開状態」と称する）で、かつスロットマシンに電源が供給されている状態（電源スイッチ 8 1 が ON 状態）において設定鍵型スイッチ 8 3 が ON 状態に操作されることにより、設定確認が可能となる。ドア開状態であり、かつスロットマシンに電源が供給されていない状態（電源スイッチ 8 1 が OFF 状態）において設定鍵型スイッチ 8 3 が ON 状態に操作され、その状態のまま電源スイッチ 8 1 が ON 状態に操作される（スロットマシンに電源が投入される）ことにより、設定変更が可能となる。設定鍵型スイッチ 8 3 は、所定の鍵部材（設定キー）を、本体側に設けられた所定の錠部材に差し込んで回動させることにより、ON 状態と OFF 状態が切り替えられるようになっている。設定確認は、遊技実行中の状態（遊技メダルがベットされている状態（自動ベットされた場合を含む）や、リールが回転している状態）では実行することができず、遊技待機中の状態でのみ実行することが可能となっている。

## 【0042】

20

電源装置 8 0 からの電力は、主制御基板 6 0 を介してサブメイン制御基板 7 0 A に供給され、さらにサブメイン制御基板 7 0 A を介してサブサブ制御基板 7 0 B に供給されるようになっている（電源装置 8 0 から直接、サブメイン制御基板 7 0 A とサブサブ制御基板 7 0 B に電力を供給するようにしてもよい）。電源装置 8 0 から主制御基板 6 0 に電力を供給する回路上と、主制御基板 6 0 を介してサブメイン制御基板 7 0 A に電力を供給する回路上には、電圧の供給状態を監視する供給電圧監視回路（図示略）がそれぞれ設けられている。各々の供給電圧監視回路は、供給電圧が所定の電圧値まで低下したときに電源断と判定し電源断検出信号をメイン CPU 6 1、後述のサブメイン CPU 7 1 に出力するようになっている。各々の供給電圧監視回路は、供給電圧が所定の電圧値（電源断判定のための電圧値とは異なる値（例えば、高い値）とするが、同じ値としてもよい）まで復帰したときに電源投入と判定し電源投入検出信号をメイン CPU 6 1、サブメイン CPU 7 1 に出力するようになっている。主制御基板 6 0 の電源断を検出するときの電圧値は、サブメイン制御基板 7 0 A の電源断を検出するときの電圧値よりも高い値に設定され、サブメイン制御基板 7 0 A よりも先に主制御基板 6 0 が、電源断時に実行するようにプログラムされた処理（電源断処理）を行うように構成されている（電源投入に関しても同様としてもよい）。

30

## 【0043】

メイン CPU 6 1 には、スイッチ基板 9 0 に接続されているかまたはスイッチ基板 9 0 上に搭載されている、リール停止信号回路 9 1、スタートレバー 2 5、投入メダルセンサ 2 8 a , 2 8 b , 2 8 c 、1 - BET スイッチ 2 2、MAX - BET スイッチ 2 3 及び清算スイッチ 2 4 からの各信号が、インターフェイス回路 6 8 を介して入力されるようになっている。

40

## 【0044】

メイン CPU 6 1 には、インターフェイス回路 6 8 を介してブロック 4 8 が接続されており、このブロック 4 8 を ON ・ OFF 制御するように構成されている。以下の説明において、ブロック 4 8 を ON ・ OFF 制御するための信号を、適宜「ブロック信号」と称する。図示は省略しているが、スロットマシンには、前扉 2 の開閉状態を検出するドアセンサが設けられており、このドアセンサからの信号が、インターフェイス回路 6 8 を介して

50

メインCPU61に入力されるようになっている。メインCPU61は、ドアセンサからの信号により、前扉2が閉じた状態（以下「ドア閉状態」と称する）であるか開いた状態（ドア開状態）であるかを判断するようになっている。

#### 【0045】

図示は省略しているが、メインCPU61は、所定の遊技状態（例えば、後述のATモードやボーナス遊技状態）となったときに、データカウンタやホールコンピュータ等に対し外部接続用端子基板等を介して所定の信号（以下、適宜「外端信号」と称する）を出力し、この外端信号により、所定の遊技状態に設定された回数等を管理したり遊技者に提示したりできるように構成されている。

#### 【0046】

サブメイン制御基板70Aには、主に演出の管理に関する各種の演算処理を行うサブメインCPU71と、制御プログラム等を記憶した読み出し専用の記憶装置であるROM72と、情報の書き込み及び読み出しが可能な記憶装置であるRAM73とが配設されており、ROM72に記憶された制御プログラムに従って各駆動回路等が動作することにより、スロットマシンにおける画像演出や音声演出の管理に関する制御、ランプ演出（LED演出）に関する制御等が行われるようになっている。上記ROM72及びRAM73は不揮発性の記憶装置であり、電力が供給されない場合でも記憶している情報を保持し得るように構成されている。サブメインCPU71と、ROM72およびRAM73とはパラレルバス接続である。サブメインCPU71には、不図示のクロックパルス発生器及び分周器が接続されており、このクロックパルス発生器及び分周器は、サブメインCPU71に対し、所定の時間毎に割込みを発生させるためのインターバルタイマとしても機能するように構成されている。サブメインCPU71は、このインターバルタイマからのパルス（クロック信号）に応じて、所定の割込処理を実行したり、設定した各種タイマの計時データの更新やリセットを行ったりするようになっている。

#### 【0047】

上記サブメインCPU71は、インターフェイス回路74を介して、主制御基板60からの各種信号を受信し、ランプ制御回路18に対し信号を送信するように構成されている。ランプ制御回路18は、バックランプ38a～38c等のランプ(LED)の点灯を制御する回路である。このインターフェイス回路74はパラレルバス延長機能と、パラレルバス接続と3線シリアルインターフェイスのインターフェイス変換機能とを有している。パラレルバス延長機能はサブメインCPU71が主制御基板のメインCPU61からの信号受信を行うために使用されている。インターフェイス変換機能はサブメインCPU71がランプ制御回路18に発光制御情報信号を送信するために使用される。ランプ制御回路18では3線シリアルインターフェイス信号の形態で送られてくるLED発光制御情報信号をLED制御信号に変換し、演出ランプ12, 13a, 13b, 14a, 14bと、飾りランプ32a, 32bと、バックランプ38a～38cの発光制御が行われる。但し、これらの配線部分に電磁部品からの誘導ノイズの影響を受けることを考慮して、LVD�インターフェイス接続も用いられるが、これについては後述する。

#### 【0048】

サブメインCPU71は、インターフェイス回路74を介して、サブサブ制御基板70Bに各種信号を送信するとともに、サブサブ制御基板70Bから各種信号を受信するように構成されている。以下、主制御基板60からサブメイン制御基板70Aに送信される信号を「制御コマンド」と称し、サブメイン制御基板70Aからサブサブ制御基板70Bに送信される信号を「演出コマンド」と称する。サブサブ制御基板70Bからサブメイン制御基板70Aに送信される信号を「状態コマンド」とも称する。

#### 【0049】

サブサブ制御基板70Bには、主に画像演出及び音声演出の制御に関する各種の演算処理を行うサブサブCPU75と、制御プログラム等を記憶した読み出し専用の記憶装置であるROM76と、情報の書き込み及び読み出しが可能な記憶装置であるRAM77とが配設されており、ROM76に記憶された制御プログラムに従って各駆動回路等が動作すること

10

20

30

30

40

50

により、画像演出や音声演出に関する制御等が行われるようになっている。上記 R O M 7 6 及び R A M 7 7 は不揮発性の記憶装置であり、電力が供給されない場合でも記憶している情報を保持し得るように構成されている。

#### 【 0 0 5 0 】

上記サブサブ C P U 7 5 は、インターフェイス回路 7 8 を介して、サブメイン制御基板 7 0 A からの報知信号または演出信号を受信し、表示装置制御回路 1 6 、スピーカ制御回路 1 7 に対し信号を送信するとともに、サブメイン制御基板 7 0 A に状態信号を送信するように構成されている。表示装置制御回路 1 6 は、画像表示装置 1 1 を制御して所定の演出画像を表示させる回路であり、スピーカ制御回路 1 7 は、上部スピーカ 1 5 a , 1 5 b 等のスピーカから発生させる音声等の種類や音量を制御する回路である。なお、画像表示装置 1 1 は、ストップスイッチ 2 6 a ~ 2 6 c の操作順（押し順）を表示する押し表示器（以下、適宜「サブ側押し順表示器」と称する）としても機能するように構成されている。

10

#### 【 0 0 5 1 】

<制御基板によるランプ制御回路の演出制御>

次に、主制御基板 6 0 と表示用ランプ制御回路 4 7 との間の通信（発光演出制御通信）の構成、サブメイン制御基板 7 0 A とランプ制御回路 1 8 との間の通信の構成を説明する。まず、主制御基板 6 0 からの表示用ランプ制御回路 4 7 、表示ランプ 4 6 a ~ 4 6 h 、4 6 j のランプ演出制御を説明する。主制御基板 6 0 のメイン C P U 6 1 は R O M 6 2 に記憶されているソフトウェアを動作させ、遊技機の遊技状態に応じて表示ランプ 4 6 a ~ 4 6 h 、4 6 j の発光輝度制御を行うための演出制御情報を決定し、表示用ランプ制御回路 4 7 に演出制御情報を送信する。

20

#### 【 0 0 5 2 】

表示ランプ 4 6 a ~ 4 6 h 、4 6 j は上述のようにランプ表示部（演出表示部材）およびその裏側に設けられた L E D から構成される L E D ランプ構成である。 L E D としては、単色で発光する単色 L E D あるいは三原色の L E D 素子から構成されるカラー L E D があり、各表示ランプ 4 6 a ~ 4 6 h 、4 6 j にはそれぞれその大きさに応じて一つもしくは複数の L E D が用いられる。単色 L E D は赤色 L E D 、緑色 L E D 、青色 L E D があり、それぞれ発光輝度制御を行ってその明るさが変化する演出制御を行う。カラー L E D は、赤色 L E D 素子、緑色 L E D 素子、青色 L E D 素子の組み合わせで構成され、各 L E D 素子の発光輝度制御を行い、白色を含む各種カラー発光を行わせる。この制御は、赤色 L E D 素子、緑色 L E D 素子、青色 L E D 素子の発光輝度値の割合を変化させて発光色を制御し、輝度値の大きさの制御を行うことによりその発光色の明るさ制御を行う。メイン C P U 6 1 は各 L E D ランプの演出制御の内容を決定して、演出制御情報として表示用ランプ制御回路 4 7 に送信し、表示用ランプ制御回路 4 7 はメイン C P U 6 1 からの演出制御情報に基づいて表示ランプ 4 6 a ~ 4 6 h 、4 6 j を構成する L E D の発光輝度制御を行う。このように表示用ランプ制御回路 4 7 は L E D 制御回路を有する。図 2 においては一つの表示用ランプ制御回路 4 7 を示しているが、表示ランプ 4 6 a ~ 4 6 h 、4 6 j には多数の L E D が用いられており、これらの発光輝度制御を行うために、表示用ランプ制御回路 4 7 は複数個の L E D 制御回路で構成される。なお、各 L E D 制御回路は表示ランプに対応する位置に設けられている。

30

#### 【 0 0 5 3 】

次に、サブメイン制御基板 7 0 A のランプ制御回路 1 8 による演出ランプ 1 2 、1 3 a 、1 3 b 、1 4 a 、1 4 b , 飾りランプ 3 2 a 、3 2 b 、バックランプ 3 8 a 、3 8 b 、3 8 c のランプ演出制御を説明する。これらランプも L E D からの照明で発光する L E D ランプであり、単色 L E D もしくはカラー L E D が用いられる。これらランプに用いられる L E D は多数であり、図 2 では一つのランプ制御回路 1 8 を示すが、ここにはこれら多数のランプの発光制御のための複数の L E D 制御回路が配設されている。主制御基板 6 0 による役抽選結果等を含む制御コマンドがサブメイン制御基板に送信されると、サブメイン制御基板 7 0 A は、主制御基板 6 0 から受信した制御コマンドに基づいて、C P U 7 1

40

、ROM72、RAM73等によりLEDの発光輝度制御を行うための演出制御情報を生成する。具体的には、当選役を遊技者に報知するために、役を連想させる色でLEDを発光させる使用方法がある（例えば、レモン図柄で構成される小役の場合、対応する色としてLEDを黄色に発光する）。この場合、LED点灯制御テーブルにより複数の発光パターンの中から実行する発光パターンを決定して演出制御情報を生成しても良いし、当選役と1対1で発光態様が決定するようにしても良い。これにより、例えば、同じ色でLEDを発光させる場合であっても、一部のLEDのみを点灯させる発光パターンや、複数のLEDを点灯させる発光パターン等を備えることで、遊技者に対する期待度を変化させることができる。

## 【0054】

10

&lt;制御基板の接続インターフェイス&gt;

メダル投入、スタートレバー操作、ストップスイッチ操作、等の遊技機の遊技状態を示す情報がRAM63上に記憶され、メインCPU61上で動作するソフトウェアは、これらの遊技機の遊技状態を示す情報を契機に、制御対象となる表示用ランプの演出制御情報をROM62より読み出す。主制御基板60上ではメインCPU61とROM62、RAM63とは、一般に、8ビットパラレルバスによって接続されている。後述するように、主制御基板60と周辺回路との接続は8ビットパラレルバスではなく、シリアルインターフェイスで接続される。8ビットパラレルバスはインターフェイス回路68に接続される。インターフェイス回路68のインターフェイス変換機能は8ビットパラレルバスのインターフェイスをシリアルインターフェイスに変換する。8ビットパラレルバスのインターフェイスでは1個のクロック信号の時間で8本の信号線に8ビットの信号を同時に送受信するが、シリアルインターフェイスでは1本の信号線に1個のクロック信号の時間で1ビットの信号を送信し、8個のクロック信号の時間で8ビットの信号を送受信する。ROM62から8ビットパラレルバスを介して読み出された演出制御情報は、インターフェイス回路68によってシリアルインターフェイスのデータ信号に変換されて、表示用ランプ制御回路47に送信される。上述のように表示用ランプ制御回路47は複数のLED制御回路を有しており、これらLED制御間では3線シリアルインターフェイス接続およびLVDシリアルインターフェイス接続が用いられるがそれについては後述する。

20

## 【0055】

30

メインCPU61上で動作するソフトウェアが演出ランプ12、13a、13b、14a、14b、飾りランプ32a、32b、バックランプ38a、38b、38cの演出内容を決定すると、主制御基板60からサブメイン制御基板70Aに8ビットパラレルバスを介して演出コマンドを送信する。サブメイン制御基板70Aには、主に演出の管理に関する各種の演算処理を行うサブメインCPU71と、制御プログラム等を記憶した読み出し専用の記憶装置であるROM72と、情報の書き込み及び読み出しが可能な記憶装置であるRAM73とが配設されており、ROM72に記憶された制御プログラムに従って各駆動回路が動作することにより、画像演出や音声演出の管理に関する制御、LEDランプ演出に関する制御等が行われるようになっている。LEDランプ演出に関する演出制御情報は、パラレルバスに接続されたROM72からインターフェイス回路74に送信される。インターフェイス回路74は8ビットパラレルバスのインターフェイスをシリアルインターフェイスに変換する。ROM72から8ビットパラレルバスを介して読み出された演出制御情報は、インターフェイス回路74によってシリアルインターフェイスのデータ信号に変換されて、ランプ制御回路18に送信される。上述のようにランプ制御回路18は複数のLED制御回路を有しており、これらLED制御間では3線シリアルインターフェイス接続およびLVDシリアルインターフェイス接続が用いられるがそれについては後述する。

40

## 【0056】

主制御基板70、サブメイン制御基板70A上のCPUとROM、RAMの間はCPUの入出力処理ビット数に一致する8ビットパラレルバスが使用される。しかし、8ビットパラレルバスのままCPUを実装する制御基板と周辺回路との間で各種情報を送受信する

50

と、膨大なインターフェイス線が必要となる。例えば、遊技機内では数百個のLEDが配設されているが、各LEDについて8ビットのデータ線、すなわち、8本のデータ線が必要であり、制御基板と遊技機内の数百個のLEDと接続するためのインターフェイス線の数は膨大となる。このため、8ビットパラレルバスのインターフェイスを、インターフェイス回路68あるいはインターフェイス回路74によって、シリアルインターフェイスに変換して制御基板から周辺回路に各種制御情報を送信するようにしている。制御基板と周辺回路とのシリアルインターフェイスとしては、I2Cバス(I2Cシリアルインターフェイスとも呼ばれる)、3線シリアルインターフェイス等の標準シリアルインターフェイスが使用される。標準シリアルインターフェイスは遊技機に限らず、CPUを用いる一般的な制御機器においてCPUを実装する制御基板と周辺回路とを接続するインターフェイスとして標準化されたインターフェイスであり、市販部品が豊富であることから、これらの標準シリアルインターフェイスを使用することが好ましい。I2Cバスは1992年に標準化がなされ、その後、順次3.4Mbpsまでの高速化が図られているが、接続距離長との関係で100kbps、400kbpsの通信速度で使用する例が多い。3線シリアルインターフェイスは数十Mbpsまでの高速動作での通信が可能である。遊技機内では多数のLED、例えば数百個のLEDが使用される。これらの多数のLEDのそれぞれを所定に周期で発光輝度制御を行うためには、I2Cバスよりも3線シリアルインターフェイスが好ましい。

#### 【0057】

本実施形態では、主制御基板60のシリアルインターフェイス回路68およびサブメイン制御基板70Aのシリアルインターフェイス回路74からの送信のための接続に、3線シリアルインターフェイスを用いている。しかし、本実施形態は3線シリアルインターフェイスに限定するものではなく、I2Cバスを用いても良い。3線シリアルインターフェイス、I2Cバス以外の他のシリアルインターフェイスであっても良い。

#### 【0058】

主制御基板60(メインCPU61)はROM62に記憶されているソフトウェアによって抽選を行い、サブメイン制御基板70A(サブメインCPU71)はROM72に記憶されているソフトウェアが抽選結果に基づいて演出制御情報を決定するが、以下の説明ではこれらの主制御基板60(メインCPU61)、サブメイン制御基板70A(サブメインCPU71)を単に「制御装置」とも称する。表示用ランプ制御回路47とランプ制御回路18は制御装置からの演出制御内容を受信し、LEDランプを構成するLEDの発光輝度制御を行うためのLED制御回路(上述のように複数のLED制御回路)のことをしており、以下の説明では、これらの表示用ランプ制御回路47とランプ制御回路18を「LED制御回路」と称して説明する。また、表示用ランプ制御回路47とランプ制御回路18が制御する表示用ランプ46a～46h、46j、演出ランプ12、13a、13b、14a、14b、飾りランプ32a、32b、バックランプ38a、38b、38cはそれぞれ一つもしくは複数のLEDを備えており、LED制御回路はこれらの個々のLEDの発光輝度制御を行う。また、説明の簡易化、明瞭化のために、主制御基板60、および、サブメイン制御基板70AのメインCPU61とサブメインCPU71を単に「CPU」と称する。

#### 【0059】

上記説明から分かるように、本実施形態では、制御装置で作成されて8ビットパラレルバスを介して送られてくるLEDの演出制御情報は、インターフェイス回路68、74で3線シリアルインターフェイスに変換され、3線シリアルインターフェイス接続によりLED制御回路に送信される。この後さらに、LVDSSシリアルインターフェイス接続も用いられるがそれについては後述する。

#### 【0060】

##### <制御装置とLED制御回路の接続インターフェイス>

このようにして送られてくるLEDの演出制御情報を受けて、LED制御回路は遊技機内に配設されたLEDの発光輝度制御を行う。LEDの発光輝度制御はLEDに所定の周

10

20

30

40

50

期で定電流を流し、所定の周期内において定電流を流す PWM パルスのパルス幅を変化させることで発光輝度値を変化させる発光輝度制御が一般的である。このための定電流値での PWM パルス制御を行うための LED 制御回路が必要であり、複数の数の LED 毎に、例えば、24個の LED 每に1つの LED 制御回路を備えて発光輝度制御するように構成されている。一般的に、遊技機内には数百個の LED が使用されていることから、遊技機内に配設される LED 制御回路の数は数十個から百個以上となる。ここで、制御装置は標準シリアルインターフェイスによって周辺回路と接続されるのが好ましく、従来は、制御装置と各 LED 制御回路との接続、さらには LED 制御回路相互の接続は、I2Cシリアルインターフェイス、または、3線シリアルインターフェイス等の標準シリアルインターフェイスを用いて接続されていた。本実施形態では標準シリアルインターフェイスとして3線シリアルインターフェイスを用いており、以下においては3線シリアルインターフェイスを用いた構成について説明する。

#### 【0061】

数十個から百個もある LED 制御回路の全てを制御装置と3線シリアルインターフェイスを用いて直接接続すると、制御装置には膨大な数の3線シリアルインターフェイスの接続線が必要となる。従って、1つあるいは数個の LED 制御回路を1段目の LED 制御回路として制御装置と直接接続し、残りの LED 制御回路を順次接続する。例えば、残りのいくつかを2段目の LED 制御回路として1段目の LED 制御回路に接続し、さらに残りのいくつかを3段目の LED 制御回路として2段目の LED 制御回路に接続するというよう 10 うに、順次接続（カスケード接続）することが良く行われる。このような接続構成することで、制御装置に設ける3線シリアルインターフェイスの接続線の数を抑制することが可能となる。

#### 【0062】

制御装置と周辺回路との接続は標準シリアルインターフェイスである3線シリアルインターフェイスを用いることを基本としている。3線シリアルインターフェイスはイネーブル信号、クロック信号、データ信号のそれぞれを送信する3本の信号線を有する。既に説明したように、3線シリアルインターフェイスを用いて LED を駆動制御するための演出制御情報を送信すると、遊技機内の電磁部品からの誘導ノイズがイネーブル信号、クロック信号、データ信号のそれぞれの信号線に重畠され、信号が乱れる可能性がある。このため、制御装置と周辺回路との接続を3線シリアルインターフェイスに代えて誘導ノイズの影響を受け難い接続インターフェイスを用いることが考えられる。しかし、制御装置と周辺回路（例えば、モータ駆動回路36a、スイッチ基板90、表示用ランプ制御回路47、ホッパー駆動回路52、リール位置検出回路37a, 37b, 37c、払出検出信号回路53及び収納状態信号回路87、等）との接続には、従来から3線シリアルインターフェイスが使用されているおり、制御装置から周辺回路への最初の接続（1段目の接続）は3線シリアルインターフェイスを使用するのが望ましい。このことから、例えば、1段目の LED 制御回路は制御装置と3線シリアルインターフェイスを用いて接続し、1段目の LED 制御回路と2段目以降の LED 制御回路とは、外部からの誘導ノイズの影響を受け難い L V D S インターフェイスを用いて接続するということが考えられる。L V D S インターフェイスは低電圧差動信号であり、ANSI/TIA/EIA-644として主に画像情報の送受信用に標準化された規格である。クロック信号、データ信号のそれぞれの信号線を2線とし、2線の差動電圧で送信する。この場合、電磁部品からの誘導ノイズがクロック信号、データ信号のそれぞれの2線に同相で誘導されても、差動電圧であるクロック信号、データ信号は影響を受けないため、誤動作する可能性が低い。

#### 【0063】

以上説明したように、本実施形態では、制御装置と1段目の LED 制御回路との接続は3線シリアルインターフェイスを用いて接続し、1段目の LED 制御回路と2段目の LED 制御回路とは L V D S インターフェイスを用いて接続し、2段目以降の下位の LED 制御回路の相互接続は L V D S インターフェイスを用いて接続する構成としている。このような構成では、1段目の LED 制御回路は3線シリアルインターフェイスの入力端子と L

10

20

30

40

50

VDS信号の出力端子を有し、2段目以降のLED制御回路はLVDSインターフェイスの入力端子とLVDSインターフェイスの出力端子を有することになる。この場合に、1つのLED制御回路が1段目のLED制御回路としても、2段目以降のLED制御回路としても動作可能であるように構成すれば、同一構成のLED制御回路を1段目のLED制御回路としても、2段目以降のLED制御回路としても使用可能となり好ましい。

#### 【0064】

このように1段目としても2段目としても共用できる構成のLED制御回路を図3に示している。以下、図3を用いて、このLED制御回路LCの構成を説明する。LED制御回路LCは、図の左側に位置して、3線シリアルインターフェイスまたはLVDSインターフェイスの信号を受信する4本の入力端子DCI1、DCI2、DDI1、DDI2を備え、図の右側に位置して、LVDSインターフェイスの信号を出力する4本の出力端子DCO1、DCO2、ODO1、ODO2を備える。さらに、左側に位置するモード指定端子MODEと、同じく左側に位置するアドレス照合のための入力端子A5-A0と、上側に位置する24個のLEDの発光輝度制御を行うための24本の出力端子LOUT1~LOUT24とを備える。10

#### 【0065】

LVDSインターフェイスの信号を受信する場合には、LED制御回路LCの4本の信号入力端子DCI1、DCI2、DDI1、DDI2から差動クロック信号および差動データ信号を受信する。差動入力端子DCI1、DCI2から受信した差動クロック信号が差動入力回路DIC1に入力され、差動入力端子DDI1、DDI2から受信した差動データ信号が差動入力回路DIC2に入力される。差動入力回路DIC1、DIC2のそれぞれは2線の入力端子の差動電圧を検出する回路である。差動入力回路DIC1、DIC2のそれぞれの出力はシフトレジスタSR1のクロック端子、データ端子に入力される。シフトレジスタSR1はクロック端子に入力されるクロック信号の立ち上がりエッジのタイミングでデータ端子に入力されたデータ信号をシフトレジスタの内部に取り込む、すなわちデータ信号をラッチする。20

#### 【0066】

4本の入力端子DCI1、DCI2、DDI1、DDI2の内の3本の入力端子DCI1、DCI2、DDI1は3線シリアルインターフェイスの入力端子としても用いられるようになっている。3線シリアルインターフェイスの入力信号を受信する場合には、3本の入力端子DCI1、DCI2、DDI1のそれぞれからクロック信号、イネーブル信号、データ信号を受信し、入力回路IC1、IC2、IC3のそれぞれに入力される。入力回路IC1、IC2、IC3のそれぞれの出力はシフトレジスタSR2のクロック端子、イネーブル端子、データ端子に入力される。シフトレジスタSR2はイネーブル端子がロー信号の状態である時に、クロック端子、データ端子に入力される信号を有効な信号と判断し、クロック端子に入力されるクロック信号の立ち上がりエッジのタイミングでデータ信号に入力されたデータ信号をシフトレジスタSR2の内部に取り込む。すなわちデータ信号をラッチする。30

#### 【0067】

シフトレジスタSR1、SR2のクロック端子、データ端子の出力のそれぞれは図示のようにセレクタSEL1、SEL2に接続されている。モード端子MODEはシフトレジスタSR1、SR2に繋がって、これらにハイ信号およびロー信号のいずれかを供給する設定となっている。モード指定端子MODEをハイ信号に設定すると、セレクタSEL1、SEL2のそれぞれはシフトレジスタSR2からのクロック信号とデータ信号をセレクタSEL1、SEL2の入力信号として選択する。モード端子MODEをロー信号に設定すると、セレクタSEL1、SEL2のそれぞれはシフトレジスタSR1からのクロック信号とデータ信号をセレクタSEL1、SEL2の入力信号として選択する。40

#### 【0068】

セレクタSEL1、SEL2の出力端子はレジスタ回路LD1の入力端子と差動出力回路DOC1、DOC2の入力端子とに接続されている。セレクタSEL1、SEL2から50

差動出力回路 D O C 1、D O C 2 に入力されたクロック信号とデータ信号は差動出力回路 D O C 1、D O C 2 によって差動クロック信号、差動データ信号に変換される。このため、差動出力回路 D O C 1、D O C 2 からの合計 4 本の出力端子は L V D S インターフェイスの信号を出力する。これにより出力端子 D C O 1、D C O 2 からは差動クロック信号を、出力端子 D D O 1、D D O 2 からは差動データ信号を L V D S 信号として出力するように構成されている。このように、L E D 制御回路は 3 線シリアルインターフェイスの入力信号を L V D S インターフェイスの出力信号として出力する構成となっている。すなわち、3 線シリアル - L V D S 変換機能（第 1 変換機能と称する）と L V D S - L V D S 変換機能（第 2 変換機能と称する）とを有する構成となっている。

10

#### 【 0 0 6 9 】

前述のように、セレクタ S E L 1、S E L 2 の出力端子はレジスタ回路 L D 1 にも接続されている。レジスタ回路 L C 1 は、入力端子 D C I 1、D C I 2、D D I 1、D D I 2 を介して 3 線シリアルインターフェイスまたは L V D S インターフェイスを用いて受信した演出制御情報を記憶する。演出制御情報はそれぞれのインターフェイスのデータ信号に含まれ、後述するように演出制御情報には、L E D 制御回路のデバイスアドレスを指定する情報、レジスタアドレスを指定する情報、発光輝度値を指定する情報が含まれ、それらが R E G 1、R E G 2、R E G 3 に記憶される。

#### 【 0 0 7 0 】

L E D 制御回路 L C はアドレス照合のための 6 本の入力端子 A 5 - A 0 から設定される 6 ビットのアドレス情報と、演出制御情報に含まれるデバイスアドレス情報を照合し、自らの L E D 制御回路 L C の制御対象の L E D を制御するための演出制御情報であるのか否かを判断する。レジスタ回路 L D 1 のレジスタアドレス指定 R E G 2 は受信する演出制御情報をどのレジスタアドレスに記憶するのかを指定し、演出制御情報に含まれる発光輝度値情報は R E G 2 で指定されるアドレスに記憶される。レジスタ回路 L D 1 に接続されている P W M 制御回路 L D 2 は、レジスタアドレス R E G 2 が指定するレジスタアドレスは 2 4 本の L E D 駆動端子 L O U T 1 ~ L O U T 2 4 の出力端子を指定する。P W M 制御回路 L D 2 は、発光輝度値情報に基づいて P W M パルスのデューティ比に相当する P W M パルスを作成する。定電流回路 L D 3 は 2 4 本の L E D 駆動端子子 L O U T 1 ~ L O U T 2 4 から出力する P W M パルス信号の定電流値を設定する。これらのレジスタ回路 L D 1、P W M 制御回路 L D 2、定電流回路 L D 3 の情報に基づいて、定電流 P W M 出力端子 L D 4 から 2 4 本の L E D 駆動端子 L O U T 1 ~ L O U T 2 4 に定電流 P W M パルス信号を出力して 2 4 個の L E D の発光輝度制御を行うように構成されている。

20

#### 【 0 0 7 1 】

##### < L E D 制御回路 >

以上のように構成された L E D 制御回路の入力端子からの信号受信、出力端子からの信号出力の詳細動作を説明する。例えば、制御装置 C D ( 主制御基板 6 8、サブメイン制御基板 7 0 A ) の近傍に配設されている表示用ランプ 4 6 a、4 6 h、4 6 j の L E D を駆動するための L E D 制御回路 ( 表示用ランプ制御回路 4 7 の一部 ) は、制御装置 C D に直接接続される 1 段目の L E D 制御回路 L C 1 として ( 図 4 参照 ) 、3 線シリアルインターフェイスを用いて制御装置 C D と接続されている。制御装置 C D と離れた位置に配設される L E D 制御回路、例えば、残りの表示用ランプ 4 6 b、4 6 c、4 6 d、4 6 e、4 6 f の発光輝度制御を行う L E D 制御回路は 2 段目以降の L E D 制御回路 L C 2、L C 3、等として用いられる。このときは、L V D S インターフェイスを用いて、1 段目の L E D 制御回路に 2 段目の L E D 制御回路、2 段目の L E D 制御回路に 3 段目の L E D 制御回路と、順次上位から下位の L E D 制御回路が接続される。なお、これらの 1 段目、2 段目の L E D 制御回路 L C 2、L C 3 は図 2 では表示用ランプ制御回路 4 7 として図示されている。

30

#### 【 0 0 7 2 】

以上説明したように、L E D 制御回路 L C は 3 線シリアルインターフェイスを入力イン

40

50

ターフェイスとし、LVDSインターフェイスを出力インターフェイスとする3線シリアル-LVDS変換機能（第1変換機能）と、LVDSインターフェイスを入力インターフェイスとし、LVDSインターフェイスを出力インターフェイスとするLVDS-LVDS変換機能（第2変換機能）とを有している。そして、LED制御回路LCを1段目のLED制御回路LC1として動作させる場合には第1変換機能が使用され、2段目以降のLED制御回路LC2、LC3、等として動作させる場合には第2変換機能が使用される。

#### 【0073】

LED制御回路LCの第1変換機能は、図3に図示するモード指定端子MODEをハイ信号に設定することにより発揮する。3線シリアルインターフェイス信号のクロック信号入力端子SCLKに入力されたクロック信号は入力回路IC1に入力され、イネーブル信号入力端子SENに入力されたイネーブル信号は入力回路IC2に入力され、データ信号入力端子SDに入力されたデータ信号は入力回路IC3に入力される。入力回路IC1、IC2、IC3の出力はシフトレジスタSR2のクロック端子、イネーブル端子、データ端子に入力される。ここで、モード指定端子MODEはハイ信号に設定されているため、セレクタSEL1、セレクタSEL2のそれぞれには、シフトレジスタSR2からのクロック信号と、データ信号が選択されて入力される。

#### 【0074】

LED制御回路LCの第2変換機能は、図3に図示するモード指定端子MODEをロー信号に設定することにより発揮する。LVDSインターフェイスの差動クロック信号入力端子DCI1、DCI2に入力された差動クロック信号は差動入力回路DIC1に入力され、差動データ信号入力端子DDI1、DDI2に入力された差動データ信号は差動入力回路DIC2に入力される。差動入力回路DIC1、DIC2の出力はシフトレジスタSR1のクロック端子、データ端子に入力される。ここでモード指定端子はロー信号に設定されているため、セレクタSEL1、SEL2のそれぞれには、シフトレジスタSR1からのクロック信号と、データ信号が選択されて入力される。

#### 【0075】

LED制御回路LCの第1変換機能が使用される場合であっても、第2変換機能が使用される場合であっても、LED制御回路LCはLVDSインターフェイスの差動クロック信号と差動データ信号を出力する。具体的にはセレクタSEL1、セレクタSEL2に入力された3線シリアルインターフェイス、または、LVDSインターフェイスのクロック信号とデータ信号のそれぞれが、セレクタSEL1、セレクタSEL2から差動出力回路DOC1、DOC2に入力される。差動出力回路DOC1は差動クロック信号出力端子DCO1、DCO2から差動クロック信号を出力し、差動出力回路DOC2は差動データ信号出力端子DDO1、DDO2から差動データ信号を出力する。これらの差動クロック信号、差動データ信号はLED制御回路内のシフトレジスタSR1、SR2、セレクタSEL1、SEL2を経由して差動出力回路DCO1、DCO2から出力される信号であり、3線シリアルインターフェイス、あるいは、LVDSインターフェイスの入力端子の信号が仮に誘導ノイズが重畠された信号であっても、波形整形された差動クロック信号、差動データ信号として出力される信号である。また3線シリアルインターフェイス、あるいは、LVDSインターフェイスの入力端子のクロック信号、データ信号より遅延した時間で出力される差動クロック信号、差動データ信号を出力する。すなわち、第1変換機能では3線シリアルインターフェイスの入力信号が波形整形されてLVDSインターフェイスの出力信号として出力される3線-2線ブリッジ機能として動作し、第2変換機能では、LVDSインターフェイスの入力信号が波形整形されてLVDSインターフェイスの出力信号として出力される2線-2線リピータ機能として動作する。

#### 【0076】

以上説明したように、本実施形態のLED制御回路LCは、モード指定端子MODEをハイ信号、または、ロー信号に設定することによって、第1変換機能を動作させて1段目のLED制御回路LC1として使用可能であり、第2変換機能を動作させて2段目以降のLED制御回路LC2、LC3、等として使用可能であるように構成されている。なお、

10

20

30

40

50

L E D 制御回路を第 1 変換機能で動作させる場合にモード指定端子 M O D E はロー信号に、第 2 変換機能で動作させる場合に、モード指定端子 M O D E をハイ信号に設定するよう構成してもよい。

#### 【 0 0 7 7 】

<制御装置と L E D 制御回路の間の接続構成>

図 4 を用いて制御装置 C D と 1 段目の L E D 制御回路 L C 1 との第 1 の接続形態例を説明する。制御装置 C D は 3 線シリアルインターフェイスで周辺回路と接続されるので、この例では制御装置 C D と複数の L E D 制御回路が並列になって 3 線シリアルインターフェイスで直接接続されている。この接続形式をマルチドロップ接続といい、これらの L E D 制御回路を 1 段目の L E D 制御回路 L C 1 と称する。前述のように 3 線シリアルインターフェイスは電磁部品からの誘導ノイズの影響を受けやすいので、できる限り制御装置 C D の近傍に配設したり、電磁部品から離れて通るように配設したりするのが望ましい。前述のように、L E D 制御回路 L C 1 の入力端子 D C I 1 , D C I 2 , D D I 1 に 3 線シリアルインターフェイス接続されると、図 3 を用いて説明したように、制御装置 C D から送られてくる制御信号に基づいて、それぞれの L E D 制御回路 L C 1 の L E D 駆動端子 L O U T 1 ~ L O U T 2 4 から対応する L E D に発光駆動信号が送られ、それら L E D の発光制御が行われる。さらに、各 L E D 制御回路 L C 1 の出力端子 D C O 1 , D C O 2 , D D O 1 , D D O 2 から L V D S 信号が後段側の L E D 制御回路に送られるようになっている。このことから分かるように、ここに示す複数の 1 段目の L E D 制御回路 L C 1 は、モード指定端子 M O D E をハイ信号として第 1 変換機能（3 線シリアル - L V D S 変換機能）を発揮するようにして用いられる。図 4 では、複数個の 1 段目の L E D 制御回路 L C 1 が制御装置 C D に接続される構成（マルチドロップ接続の構成）としているが、1 個の 1 段目の L E D 制御回路 L C 1 が制御装置 C D に接続される構成であってもよい。

10

20

30

#### 【 0 0 7 8 】

次に、図 5 を用いて、制御装置 C D および 1 段目の L E D 制御回路 L C 1 に加えて、2 段目の L E D 制御回路 L C 2 が接続される構成を説明する。ここでは、制御装置 C D の基板（図 2 における主制御基板 6 0 、サブメイン制御基板 7 0 A ）に 1 段目の L E D 制御回路 L C 1 を配設した例を示している。制御装置 C D と 1 段目の L E D 制御回路 L C 1 は、図 4 と同様に 3 線シリアルインターフェイスを用いて接続される。そして、制御装置 C D の基板上の 1 段目の L E D 制御回路 L C 1 は、複数の 2 段目の L E D 制御回路 L C 2 に L V D S インターフェイスを用いてマルチドロップ接続され、これら 2 段目の L E D 制御回路 L C 2 のそれから、図示しない下位の L E D 制御回路に L V D S インターフェイスを用いて接続される。図 5 の構成では、1 段目の L E D 制御回路 L C 1 は、モード指定端子 M O D E をハイ信号として第 1 変換機能（3 線シリアル - L V D S 変換機能）を発揮するようにして用いられ、複数の 2 段目の L E D 制御回路 L C 2 は、モード指定端子 M O D E をロー信号として第 2 変換機能（L V D S - L V D S 変換機能）を発揮するようにして用いられる。なお、これら各 L E D 制御回路 L C 1 , L C 2 は、制御装置 C D から送られてくる制御信号に基づいて、それぞれの L E D 駆動端子 L O U T 1 ~ L O U T 2 4 から対応する L E D に発光駆動信号が送られ、それら L E D の発光制御が行われる。

40

#### 【 0 0 7 9 】

<複数の L E D 制御回路間の相互接続>

図 6 を用いて、図 4 および図 5 で示した 1 段目の L E D 制御回路 L C 1 に、複数段の L E D 制御回路 L C （第 2 段目～第 5 段目の L E D 制御回路 L C 2 ~ L C 5 ）を順次接続する接続構成例を説明する。これを図 1 に示した表示用ランプ 4 6 a ~ 4 6 h , 4 6 j を例にして説明する。表示用ランプ 4 6 h が制御装置 C D （主制御基板 6 0 ）の近傍に配設され、電磁部品からの誘導ノイズの影響をほぼ受けない位置にあるため、表示用ランプ 4 6 h の発光輝度制御を行う L E D 制御回路 L C を 1 段目の L E D 制御回路 L C 1 として用い、制御装置 C D と 3 線シリアルインターフェイスを用いて接続する。すなわち、この L E D 制御回路 L C 1 は、モード指定端子 M O D E をハイ信号として第 1 変換機能（3 線シリアル - L V D S 変換機能）を発揮するようにして用いる。表示用ランプ 4 6 a , 4 6 j は

50

表示用ランプ 46 h から同じ程度の距離だけ離れて配設されているので、表示用ランプ 46 a、46 h のそれぞれを制御する LED 制御回路を 2 段目の LED 制御回路 LC 2 とし、LED 制御回路 LC 1 とそれぞれマルチドロップ接続している。一方、中パネルアセンブリ 20 の右側周辺部に配置された表示用ランプ 46 c、46 e、46 f、46 g を制御する LED 制御回路は、LED 制御回路 LC 2 から、順次、カスケード接続して 3 段目～5 段目の LED 制御回路 LC 3～LC 5 としている。この場合、3 段目～5 段目の LED 制御回路 LC 3～LC 5 は、モード指定端子 MODE をロー信号として第 2 変換機能 (LVDS - LVDS 変換機能) を発揮するようにして用いられる。この場合においても、各 LED 制御回路 LC 1～LC 5 は、制御装置 CD から送られてくる制御信号に基づいて、それぞれの LED 駆動端子 LOUT 1～LOUT 24 から対応する LED に発光駆動信号が送られ、それら LED の発光制御が行われる。10

#### 【0080】

以上においては、表示用ランプ 46 a～46 h, 46 j の発光制御接続構成を例にして説明しており、この場合には図 6 の第 1 段目～第 5 段目の LED 制御回路 LC 1～LC 5 は、図 2 に示す表示用ランプ制御回路 47 に対応する。これと同様な構成がランプ制御回路 18 でも用いられ、図 6 の 1 段目～5 段目の LED 制御回路 LC 1～LC 5 がランプ制御回路 18 を構成し、これらにより演出ランプ、飾りランプ、バックランプの発光制御が行われる。

#### 【0081】

図 6 では、1 段目の LED 制御回路 LC 1 に 2 段目以降の LED 制御回路 LC 2、LC 3、等をマルチドロップ接続、および、カスケード接続する接続構成を説明したが、2 段目以降の LED 制御回路 LC の接続構成は、図 6 に図示した接続構成に限定されない。例えば、複数の 2 段目の LED 制御回路 LC 2 は比較的近い位置に配設され、3 段目、4 段目の LED 制御回路 LC 3、LC 4 は相互に離れた位置に配設されることがある。このような場合には、比較的近い位置に配設されている複数の 2 段目の LED 制御回路 LC 2 をマルチドロップ接続し、相互に離れた位置に配設される 3 段目、4 段目の LED 制御回路 LC 3、LC 4 は順次カスケード接続する、というように、マルチドロップ接続とカスケード接続を適宜組み合わせて、LED 制御回路 LC を相互に接続することが好ましい。20

#### 【0082】

< 3 線シリアルインターフェイスと LVDS インターフェイスとの間の信号変換 >30

3 線シリアルインターフェイスと LVDS インターフェイスとでは信号形式が異なる。図 7 - 図 10 を用いて、演出制御情報をそれぞれの信号形式を用いて送信する方法を説明する。モード指定端子 MODE をハイ信号として第 1 変換機能 (3 線シリアル - LVDS 変換機能) を発揮するようにして用いられる 1 段目の LED 制御回路 LC 1 による信号変換や、モード指定端子 MODE をロー信号として第 2 変換機能 (LVDS - LVDS 変換機能) を発揮するようにして用いられる 2 段目以降の LED 制御回路 LC 2～による信号変換について図 7 - 図 10 を用いて説明する。

#### 【0083】

< 3 線シリアルインターフェイス >

本実施形態では制御装置 CD は遊技機内の複数の LED 制御回路 LC のそれぞれが制御する LED の発光輝度情報を演出制御情報として送信する。図 2 に示した表示用ランプ制御回路 47 の場合には、制御装置 CD は全ての表示用ランプ 46 a～46 h, 46 j に用いられる LED の発光輝度情報を表示用ランプ制御回路 47 に送信する。この表示用ランプ制御回路が図 6 に示した接続構成であるとして説明すると、表示用ランプ 46 a～46 h, 46 j の全ての LED の発光制御を行う LED 制御回路 LC 1～LC 5 が発光輝度制御を行うための演出制御情報を、まず 1 段目の LED 制御回路 LC 1 に送信する。この演出制御情報は、3 線シリアルインターフェイスを用いて、制御装置 CD から 1 段目の LED 制御回路 LC 1 に送信する。40

#### 【0084】

3 線シリアルインターフェイスではイネーブル信号線、クロック信号線、データ信号線50

の3種類の信号線が使用される。イネーブル信号線はクロック信号線、データ信号線に有効な信号が入力されることを示す信号である。具体的には、図7に図示するように、イネーブル信号線にロー信号のイネーブル信号が送信されている間、クロック信号線、データ信号線に有効なクロック信号、データ信号が送信されていることを示す。演出制御情報はデータ信号線上に1ビットずつ送信される。図7に図示した例では、第1バイトを構成する8ビットのデータがbit7からbit0の順で送信され、続いて、第2バイトを構成する8ビットのデータが送信され、最終バイトのbit0までのデータ信号が送信される。クロック信号線上にはロー信号とハイ信号が一定のクロック周期で繰り返すクロック信号が送信される。クロック信号がロー信号からハイ信号に変化する立ち上がりエッジの時間における、データ信号線上で送信されているデータ信号の状態がデータ信号としてLED制御回路の中でラッチされる。すなわち、データ信号線がハイ信号であれば、データ1として、データ信号線がロー信号であればデータ0としてLED制御回路の中でラッチされる。なお、データ信号線上で送信される演出制御情報の詳細は後段で説明する。

#### 【0085】

制御装置CDからの3線シリアルインターフェイスのイネーブル信号線、クロック信号線、データ信号線は、図3に図示するLED制御回路LCの入力端子DCI1, DCI2, DDI1からイネーブル信号入力端子SEN、クロック信号入力端子SCLK、データ信号入力端子SDに接続されている。イネーブル信号入力端子SENのイネーブル信号がハイ信号からロー信号に変化すると、入力回路IC2を経由してシフトレジスタSR2のイネーブル信号端子がロー信号に設定される。シフトレジスタSR2はイネーブル信号端子がロー信号に設定されると、クロック信号入力端子SCLK、データ信号入力端子SDに入力されたクロック信号、データ信号のそれぞれは、入力回路IC1、IC3のそれぞれを経由してシフトレジスタSR2のクロック信号端子、データ信号端子に入力される。ここで、シフトレジスタSR2のクロック信号端子のクロック信号の立ち上がりエッジのタイミングにおけるシフトレジスタSR2のデータ信号端子のデータ信号がデータ信号としてシフトレジスタSR2に取り込まれる。このように、シフトレジスタSR2にデータ信号が入力されて取り込まれることを、データ信号をラッチすると表現する。

#### 【0086】

##### <LVDSインターフェイス>

図8を用いてLVDSインターフェイスの入力端子の信号入力を説明する。上述のように、制御装置CDから1段目のLED制御回路LC1に3線シリアルインターフェイスを用いて、遊技機内の全てのLED制御回路LCが制御するLEDの演出制御情報が送信される。1段目のLED制御回路LC1はモード指定端子MODEをハイ信号として第1変換機能(3線シリアル-LVDS変換機能)を発揮するようにして用いられるようになっており、1段目のLED制御回路LC1から2段目以降の下位のLED制御回路LC2、LC3、等に対してLVDSインターフェイスを用いて、制御装置CDが送信した演出制御情報が順次送信される。LVDSインターフェイスでは、それぞれ2線の差動クロック信号線、差動データ信号線を用いてそれぞれ差動クロック信号、差動データ信号が送信される。

#### 【0087】

これを図3のLED制御回路LCを参照して説明すると、第1変換機能(3線シリアル-LVDS変換機能)を発揮する1段目のLED制御回路LC1の場合には、入力端子DCI1, DCI2, DDI1に入力された3線シリアル信号がここでLVDS信号に変換され、差動クロック信号出力端子DCO1、DCO2と差動データ信号出力端子DDO1、DDO2からLVDSインターフェイスの差動クロック信号線、差動データ信号線にLVDS信号となった演出制御情報が出力される。第2変換機能(LVDS-LVDS変換機能)を発揮する2段目のLED制御回路LC2においては、上記の差動クロック信号線、差動データ信号線が、図3のLED制御回路LCの差動クロック信号入力端子DCI1、DCI2および差動データ信号入力端子DDI1、DDI2に接続されている。LVDSインターフェイスは低電圧差動信号であるため、差動クロック信号線、差動データ信号

10

20

30

40

50

線のそれぞれの 2 線の信号線の間の差動電圧が有効な差動クロック信号、差動データ信号となる。

#### 【 0 0 8 8 】

図 8 は差動クロック信号線、差動データ信号線の 2 本の信号線の間の差動電圧を示す。L V D S インターフェイスでは、3 線シリアルインターフェイスと異なりイネーブル信号が使用されない。このため、有効なクロック信号、データ信号が送信される時間を示すために、ヘッダ条件と最終クロック信号を示す信号が使用される。ヘッダ条件は、差動クロック信号入力端子 D C I 1、D C I 2 がハイ信号の状態において、差動データ信号入力端子 D D I 1、D D I 2 がハイ信号からロー信号に変化する信号である。ヘッダ条件に続いて、差動クロック信号、差動データ信号が入力される。演出制御情報は差動データ信号線上に 1 ビットずつ送信される。図 8 に図示した例では、第 1 バイトを構成する 8 ビットのデータが b i t 7 から b i t 0 の順で送信され、続いて、第 2 バイトを構成する 8 ビットのデータが送信され、最終バイトの b i t 0 までのデータ信号が送信される。差動クロック信号線上にはロー信号とハイ信号が一定のクロック周期で繰り返すクロック信号が送信される。3 線シリアルインターフェイスの入力端子から入力された差動クロック信号と差動データ信号は、前述のように、シフトレジスタ S R 2 のクロック信号端子、データ信号端子に入力され、クロック信号がロー信号からハイ信号に変化する立ち上がりエッジの時間におけるデータ信号の状態が、データ信号としてシフトレジスタ S R 1 においてラッチされる。

#### 【 0 0 8 9 】

有効な差動クロック信号、差動データ信号が終了すると、上位の L E D 制御回路 L C から L V D S インターフェイスを用いて最終クロック信号が入力される。最終クロック信号は、差動クロック信号入力端子 D C I 1、D C I 2 をハイ信号の状態にすることで、最終クロック信号であることを示す。図 3、図 8 を用いて上位の L E D 制御回路 L C から L V D S インターフェイスを用いて L E D 制御回路 L C の入力端子に入力される差動クロック信号と差動データ信号の信号入力を説明したが、図 3 の L E D 制御回路から下位の L E D 制御回路に L V D S インターフェイスの差動クロック信号出力端子 D C O 1、D C O 2、差動データ信号出力端子 D D O 1、D D O 2 から差動クロック信号、差動データ信号を出力する場合の信号出力も同様である。

#### 【 0 0 9 0 】

##### < 3 線 2 線ブリッジ機能 >

図 9 を用いて、第 1 変換機能を発揮する 1 段目の L E D 制御回路 L C 1 において、3 線シリアルインターフェイスを用いて入力されたイネーブル信号、クロック信号、データ信号が、L V D S インターフェイスの差動クロック信号、差動データ信号に変換されて信号出力する、3 線 2 線ブリッジ機能を説明する。

#### 【 0 0 9 1 】

3 線 2 線ブリッジ機能では、モード指定端子 M O D E がハイ信号に設定されることで、3 線シリアルインターフェイスの入力信号が L E D 制御回路 L C に取り込まれる。< 3 線シリアルインターフェイス > の箇所で説明したように、入力されたクロック信号とデータ信号が、入力回路 I C 1、I C 2、続いてシフトレジスタ S R 2 のクロック端子、データ端子にラッチされて、セレクタ S E L 1、S E L 2 に入力される。セレクタ S E L 1、S E L 2 に入力されたクロック信号、データ信号は差動出力回路 D O C 1、D O C 2 の入力端子に入力される。ここで、3 線シリアルインターフェイスのイネーブル信号のハイ信号からロー信号への変化は、クロック信号、データ信号に有効信号が入力されることを示す信号であり、3 線シリアルインターフェイスのイネーブル信号のハイ信号からロー信号への変化に伴って、L V D S インターフェイスからヘッダ条件を出力する。すなわち、差動出力回路 D O C 1 の差動クロック信号出力端子 D C O 1、D C O 2 にハイ信号の状態の差動クロック信号を出力し、差動出力回路 D O C 2 の差動データ信号出力端子 D D O 1、D D O 2 にハイ信号からロー信号に変化する差動データ信号を出力することでヘッダ条件を出力する。

10

20

30

40

50

**【0092】**

続いて、3線シリアルインターフェイスのクロック信号、データ信号の入力は前述の<3線シリアルインターフェイス>の箇所で説明した通りとなり、シフトレジスタSR2のクロック信号端子とデータ信号端子に入力されて、データ信号がシフトレジスタSR2においてラッチされる。ここで、モード指定端子MODEがハイ信号であることから、シフトレジスタSR2に入力されたクロック信号とシフトレジスタSR2にラッチされたデータ信号は、順次、セレクタSEL1, SEL2に入力される。

**【0093】**

セレクタSEL1に入力されたクロック信号は、セレクタSEL1から差動出回路DOC1に入力され、セレクタSEL2に入力されたデータ信号は、セレクタSEL2から差動出回路DOC2にデータ信号が入力される。差動出回路DOC1、差動出回路DOC2の出力がLVDSインターフェイスの出力端子から、差動クロック信号と差動データ信号として出力される。LVDS信号の差動クロック信号と差動データ信号の送信タイミングは以下のようになる。3線シリアルインターフェイスのクロック信号入力端子SCLKのクロック信号の立ち上がりエッジのタイミングでLVDSインターフェイスの差動データ信号出力端子DDO1、DDO2から差動データ信号の送出が開始される。差動データ信号は3線シリアルインターフェイスから入力されたデータ信号と同様に第1バイトのbit7からbit0、第2バイトと続いて、最終バイトのbit0までのデータである。また、差動クロック信号出力端子DCO1、DCO2からの差動クロック信号の送出タイミングは、差動クロック信号の立ち上がりエッジのタイミングが差動データ信号のデータが安定しているタイミングとなるように送出される。

**【0094】**

制御装置CDから3線シリアルインターフェイスを用いて演出制御情報を送信し終わる、すなわち、全てのデータ信号の送出が終わると、3線シリアルインターフェイスのイネーブル信号入力端子SENはロー信号からハイ信号に変化する。イネーブル信号がハイ信号に変化したことで、LVDSインターフェイスでは最終クロック信号を送信する。最終クロック信号は、LVDSインターフェイスの出力端子の差動クロック信号出力端子DCO1、DCO2がハイ信号状態に変化する信号である。このようにして、3線シリアルインターフェイスを用いて入力されたイネーブル信号、クロック信号、および、演出制御情報を送信するデータ信号は、第1変換機能を発揮する3線 2線ブリッジ機能によってLVDSインターフェイスの差動クロック信号、差動データ信号に変換されて、下位のLED制御回路LCにLVDSインターフェイスを用いて送信される。なお、このように構成されているため、仮に3線シリアルインターフェイスのイネーブル信号線、クロック信号線、データ信号線のそれぞれの単線上に誘導ノイズが重畠したとしても、下位のLED制御回路LCに送信されるLVDSインターフェイスの差動クロック信号線、差動データ信号線上的信号波形は、誘導ノイズが重畠されていない波形整形された信号波形となる。

**【0095】**

<2線 2線リピート機能>

図10を用いて第2変換機能を発揮する2段目以降のLED制御回路LCにおいて、LVDSインターフェイスの信号で入力された差動クロック信号、差動データ信号が、LVDSインターフェイスの出力信号としてリピートされて、下位のLED制御回路LCに送信される、2線 2線リピート機能を説明する。

**【0096】**

2線 2線ブリッジ機能では、モード指定端子がロー信号に設定されることで、LVDSインターフェイスの入力信号がLED制御回路LCに取り込まれる。その動作は前述の<LVDSインターフェイス>の箇所で説明した通りであり、入力された差動クロック信号と差動データ信号が、差動入回路DIC11, DIC2、続いてシフトレジスタSR1のクロック端子、データ端子にラッチされて、セレクタSEL1, SEL2に入力される。セレクタSEL1、SEL2に入力されたクロック信号、データ信号は差動出回路DOC1、DOC2の入力端子に入力される。

10

20

30

40

50

## 【0097】

ここで、LVDSインターフェイスの入力端子から入力されたヘッダ条件に基づいて、LVDSインターフェイスの出力端子からヘッダ条件を出力する。ヘッダ条件に続いて、差動クロック信号入力端子DCI1、DCI2、差動データ信号入力端子DDI1、DDI2に有効な差動クロック信号、差動データ信号が入力される。差動データ信号は第1バイトのbit7から、最終バイトのbit0までの信号である。差動データ信号と共に、差動クロック信号が入力されて、シフトレジスタSR1のクロック端子、データ端子にそれぞれ入力される。差動データ信号は差動クロック信号の立ち上がりエッジのタイミングでシフトレジスタSR1に入力されて、ラッチされる。シフトレジスタSR1に入力されたクロック信号、およびデータ信号は、モード指定端子MODEがロー信号に設定されていることから、シフトレジスタSR1のクロック信号とデータ信号出力が選択されてセレクタSEL1、SEL2に入力される。

10

## 【0098】

セレクタSEL1に入力されたクロック信号は、セレクタSEL1から差動出力回路DOC1に入力される。セレクタSEL2に入力されたデータ信号は差動出力回路DOC2に入力される。続いて、差動出力回路DOC1、差動出力回路DOC2からLVDSインターフェイスの差動クロック信号と差動データ信号が出力される。LVDSインターフェイスの差動クロック信号入力端子DCI1、DCI2のクロック信号の立ち上がりエッジのタイミングでLVDSインターフェイスの差動データ信号出力端子DDO1、DDO2から差動データ信号の送出が開始される。差動クロック信号出力端子DCO1、DCO2からの差動クロック信号は、差動クロック信号の立ち上がりエッジのタイミングが差動データ信号のデータが安定しているタイミングとなるように、差動クロック信号出力端子DCO1、DCO2から差動クロック信号が送出される。

20

## 【0099】

差動データ信号入力端子DDI1、DDI2に演出制御情報が入力し終わると、差動クロック信号入力端子に最終クロック信号が入力される。最終クロック信号は、差動データ信号入力端子DDI1、DDI2の差動データ信号がハイ信号状態のままで差動クロック信号入力端子DCI1、DCI2の差動クロック信号がロー信号からハイ信号に立ち上がった状態となる信号である。LVDS信号の入力端子に最終クロック信号が入力されると、LVDSインターフェイスの出力端子から最終クロック信号を出力する。最終クロック信号はLVDSインターフェイスの差動データ信号出力端子DDO1、DDO2をハイ信号状態のまとし、差動クロック信号出力端子DCO1、DCO2をロー信号の状態からハイ信号の状態に変化させる信号である。このようにして、LVDSインターフェイスの入力端子に入力された差動クロック信号、差動データ信号は、2線 2線リピータ機能によって、下位のLED制御回路LCにLVDSインターフェイスの差動クロック信号、差動データ信号として送信される。このように構成されているため、仮にLVDSインターフェイスの差動クロック信号線、差動データ信号線のそれぞれの2線に同相の誘導ノイズが重畠していても、下位のLED制御回路LCに送信されるLVDSインターフェイスの差動クロック信号線、差動データ信号線のそれぞれの2線上の波形は、誘導ノイズが重畠していない波形整形された差動クロック信号、差動データ信号となる。

30

## 【0100】

図3、図7-図10を用いて説明したように、本実施形態のLED制御回路LCは第1変換機能を発揮して1段目のLED制御回路LC1として動作可能であり、3線シリアルインターフェイスの入力信号を受信すると、下位のLED制御回路LCにLVDSインターフェイスの出力信号を出力する3線 2線ブリッジ機能を有している。また、第2変換機能を発揮して2段目以降のLED制御回路LC2、LC3、等として動作可能であり、LVDSインターフェイスの入力信号を受信すると、下位のLED制御回路LCにLVDSインターフェイスの出力信号を出力する2線 2線リピータ機能を有している。3線 2線ブリッジ、2線 2線リピータ機能のいずれにおいてもLVDSインターフェイスの

40

50

出力信号の出力波形は L E D 制御回路 L C の内部で波形整形された出力波形である。このため、遊技機内に配設されている電磁部品からの誘導ノイズの影響を受けたとしても、波形整形された出力波形で下位の L E D 制御回路と接続することが可能となり、 L E D 制御回路を配設する位置の設計自由度が向上するという効果が得られる。

#### 【 0 1 0 1 】

##### < 演出制御情報 >

次に、図 3、および、図 1 1 を用いて、制御装置 C D が遊技機内の特定の L E D 制御回路 L C に演出制御情報を送信する方法を説明する。制御装置 C D はランプ制御回路 1 8 および表示用ランプ制御回路 4 7 のそれぞれについて、全ての L E D 制御回路 L C に対して、1 段目の L E D 制御回路 L C 1 から後段の L E D 制御回路を経由して演出制御情報を送信する。このため、下位の L E D 制御回路 L C の制御対象の L E D の発光輝度情報も 1 段目の L E D 制御回路 L C 1 を経由して送信される。前述のように、各 L E D 制御回路 L C が 2 4 個の L E D の発光輝度制御を可能であるが、制御装置 C D は、2 4 個 L E D の発光輝度制御を行うための発光輝度値情報を送信してもよいし、一部の L E D の発光輝度値情報を送信してもよい。このような制御を可能とするために、制御装置 C D から L E D 制御回路 L C に送信する演出制御情報は図 1 1 に図示するようなバイト構成となっている。制御装置 C D から L E D 制御回路 L C に送信する演出制御情報は第 1 バイトから第 ( 2 + p ) バイト ( p は p = 2 4 である正の整数 ) のデータ長である。

10

#### 【 0 1 0 2 】

演出制御情報の第 1 バイトの B i t 7 は後述する P W M 位相制御ビットである。 B I T 6 は L E D 制御回路 L C から出力を送信するか否かを指定する出力イネーブル指定ビットである。 B i t 5 - 0 は遊技機内に配設される複数の L E D 制御回路 L C のアドレスを指定する L E D 制御回路アドレス用ビットである。 L E D 制御回路 L C はアドレス指定を設定する 6 本のアドレス指定端子 A 5 - A 0 を有している。制御装置 C D から L E D 制御回路 L C に送信される演出制御情報の第 1 バイトの B i t 5 - 0 に含まれる L E D 制御回路アドレスはレジスタ回路 L D 1 内のレジスタ R E G 1 に入力される。レジスタ R E G 1 に記憶された B i T 5 - 0 の値と、アドレス指定端子 A 5 - A 0 から設定されたアドレスと、が一致するか否かアドレス照合を行う。例えば、図 1 の表示用ランプ 4 6 c を発光輝度制御を行うための L E D 制御回路 L C のデバイスアドレスを 3 とした場合には、アドレス指定端子 A 5 - A 0 を 0 0 0 0 1 1 と設定する。制御装置 C D は L E D 制御回路 L C に送信する演出制御情報の第 1 バイトの b i t 5 - b i t 0 を 0 0 0 0 1 1 に指定する。このようにアドレス照合を行うことで、制御装置 C D は 1 段目およびそれに続く後段の L E D 制御回路 L C 1 ~ を経由しても、演出制御情報を、指定された L E D 制御回路 L C において的確に受信することが可能である。

20

#### 【 0 1 0 3 】

アドレス照合が一致した場合には、続いて受信する第 2 バイトのデータがレジスタ回路 L D 1 のレジスタ R E G 2 に入力される。第 2 バイトのデータは続いて入力される第 3 バイトのデータを記憶するレジスタ R E G 3 のレジスタアドレスを指定する。第 3 バイト以降のデータは L E D 制御回路が制御する L E D の発光輝度値情報である。図 1 1 は、レジスタ R E G 2 に記憶される第 2 バイトのデータ値が 1 であり、レジスタアドレス 1 が指定される場合の例を示す。第 3 バイトのデータはレジスタ R E G 3 のレジスタアドレス 1 に記憶される。第 3 バイトのデータがレジスタアドレス 1 に記憶されると、レジスタ R E G 2 はレジスタアドレスを 1 だけ増加する。このため、続いて第 4 バイトのデータを受信すると、受信した第 4 バイトのデータはレジスタ R E G 3 のレジスタアドレス 2 に記憶される。このようにして、演出制御情報の最終バイトが第 ( 2 + p ) バイトである場合には、レジスタ R E G 2 はレジスタアドレス p を指定し、最終バイトの第 ( 2 + p ) バイトのデータはレジスタ R E G 3 のレジスタアドレス p に記憶される。このようにして、演出制御情報の第 3 バイトから第 ( 2 + p ) バイトまでのデータは第 2 バイトが順次指定するレジスタアドレス 1 からレジスタアドレス p に記憶される。

30

#### 【 0 1 0 4 】

40

50

図11では、制御装置CDが、例えば、24個のLEDの発光輝度制御が可能なLED制御回路に対して、p個のLEDの発光輝度制御を行うための発光輝度値情報を送信する例を示している。1つのLED制御回路は、例えば、24個のLEDの発光輝度制御を行うことが可能であり、レジスタREG3のレジスタアドレスはレジスタアドレス1からレジスタアドレス24まである。制御装置CDは1度の演出制御情報の送信で、24個のLEDの発光輝度値情報を送信することも可能である。

#### 【0105】

レジスタREG3はレジスタアドレス1からレジスタアドレス24までの24個のレジスタアドレスを有し、レジスタアドレス1 - レジスタアドレス24のそれぞれはLED制御回路LCの制御対象の24個のLEDの発光輝度値情報を記憶する。発光輝度値情報は8ビットのデータ値である。レジスタアドレス1はLED駆動端子LOUT1から駆動するLEDの256段階の発光輝度値を記憶し、レジスタアドレス2はLED駆動端子LOUT2から駆動するLEDの256段階の発光輝度値を記憶する。以下順に、レジスタアドレス24はLED駆動端子LOUT24から駆動するLEDの256段階の発光輝度値を記憶する。

#### 【0106】

##### < LEDの演出制御 >

図12を用いて、24個のLEDの256段階の発光輝度値制御を説明する。レジスタREG3のレジスタアドレス1からレジスタアドレス24にはLED駆動端子LOUT1 ~ LOUT24から出力する256段階の発光輝度値情報が記憶される。LED制御回路LCはPWM制御回路LD2を有し、レジスタREG3に記憶されている発光輝度値情報に基づいてLED駆動端子LOUT1 - LOUT24から出力するPWM信号のパルス幅を256段階のパルス幅で制御する。PWM制御回路LD2はレジスタREG3のレジスタアドレス1からレジスタアドレス24に記憶されている発光輝度値情報に基づいて、例えば、290μs周期毎にPWM制御を行う。発光輝度情報の発光輝度値が255である場合には、PWMパルスのオン信号期間が、例えば、255 / 256のデューティ比のPWMパルスとして、LED駆動端子LOUT1 - LOUT24から出力する。発光輝度値が254である場合には、254 / 256のデューティ比のPWMパルスとして、LED駆動端子LOUT1 - LOUT24から出力する。以下、発光輝度値が小さくなれば、PWMパルスのオン信号期間は短くなり、発光輝度値が0の場合にはLED駆動端子LOUT1 - LOUT24からのPWMパルス出力はオフとなり、LEDは消灯する。

#### 【0107】

図12を用いて説明したように、LED制御回路LCは256段階のPWMパルスのデューティ比でそれぞれのLED制御回路LCの制御対象のLEDの発光輝度制御を行う。ここで、例えば、図1の上パネルアセンブリ10に配設されている演出ランプ12を多彩な色調で演出制御する例を説明する。演出ランプ12を構成する複数のLEDには、例えば、光の三原色発光を行う3つのLEDを組み合わせた複数個のカラー発光LEDで構成されているものとする。遊技機のサブメインCPU71は、遊技機の遊技状態に応じて、これらの複数個のカラー発光LEDのそれぞれを異なる色調で発光させるものとする。例えば、演出ランプ12の左側部分を緑色発光で明るさが変化するように発光させ、演出ランプ12の右側部分を青色発光で明るさが変化するように発光させる演出を行うものとする。図12を用いて説明したように、LED制御回路LCのPWM制御回路LD2は制御対象の24個のLEDのそれぞれを290μsの周期で発光輝度制御する構成となっている。24個のLED駆動端子LOUT1 ~ LOUT3の3本のLED駆動端子は、演出ランプ12の左側部分のカラー発光LEDの三原色LED、すなわち、赤色LED、緑色LED、青色LEDのそれに対応し、LED駆動端子LOUT22 ~ LOUT24の3本のLED駆動端子は演出ランプ12の右側部分のカラー発光LEDの三原色LED、すなわち、赤色LED、緑色LED、青色LEDのそれに対応するものとする。このように構成した場合には、LED駆動端子LOUT1 ~ LOUT3の3本のLED駆動端子において、LOUT2の緑色LEDを駆動するためのPWMパルスのデューティ比を、L

10

20

30

40

50

ED 駆動端子 L OUT 1、L OUT 3 に対応する赤色 LED、青色 LED を駆動するための PWM パルスのデューティ比よりも高いデューティ比で  $290 \mu s$  の周期で発光輝度値情報を変化させて制御すれば、演出制御ランプ 12 の左側部分は緑色発光して明るさが変化するように発光輝度制御を行うことができる。同様にして、演出ランプ 12 の右側部分を制御する L OUT 22 ~ L OUT 24 の 3 本の LED 駆動端子においては、赤色 LED を駆動するための L OUT 22 の PWM パルスのデューティ比を緑色 LED、青色 LED を駆動するための PWM パルスのデューティ比よりも高いデューティ比で  $290 \mu s$  の周期で変化させて制御すれば、演出ランプ 12 の右側部分は赤色発光して明るさが変化するように発光輝度制御を行うことができる。

## 【0108】

10

以上の説明ではカラー三原色 LED を用いて、色調が緑色、赤色のままで、明るさを変化させる制御例を説明した。当初は緑色の色調で、時間が経過とともに赤色を帯びた色調に変化するように制御することも可能である。あるいは、単色 LED を用いて明るさを制御するように制御することも可能である。図 3 に図示した LED 制御回路 LC を用いて LED の発光輝度制御を行うことで、遊技者の興趣を高めるように、遊技機において多様な演出制御を行うことが可能となる。

## 【0109】

## &lt;LED の個別制御、グループ制御 &gt;

本実施形態の LED 制御回路は、例えば、24 個 LED の発光輝度制御を行うが、これらの 24 個の LED の発光輝度制御を行う際に個別制御、または、グループ制御が可能なように構成されている。1つの LED 制御回路 LC が駆動制御する 24 個の LED に対して同じタイミングで PWM パルスをオン制御すると、1 個の LED を駆動制御する場合と比較して一度に 24 倍という大きな電流変化が発生する。このため、周辺回路にスイッチングノイズが発生し、周辺回路の誤動作の原因となる可能性が高い。このため、本実施形態の LED 制御回路 LC では 24 個の LED のそれぞれを異なる位相タイミングで駆動制御可能に構成する。あるいは、3 個の LED 毎にグループを構成し、グループ毎に異なる位相タイミングで LED を駆動制御可能に構成する。このため、演出制御情報の第 1 バイトの bit 7 は LED 駆動端子 L OUT 1 - L OUT 24 のそれぞれを異なる位相タイミングで個別制御するのか、3 本の LED 駆動端子毎にグループ分けしてグループ制御するのかを指定する PWM 位相制御用ビットである。

20

## 【0110】

30

図 13 を用いて、24 個の LED のそれぞれの PWM 位相の個別制御を説明する。演出制御情報の第 1 バイトの bit 7 が 0 に設定されて個別制御を行う場合には、LED 駆動端子 L OUT 1 での PWM パルスのオン信号送出開始タイミング、LED 駆動端子 L OUT 2 のオン信号送出開始タイミング、LED 駆動端子 L OUT 3 のオン信号送出開始タイミングは、それぞれ固定遅延時間だけ異なるタイミングとする。以下、同様に LED 駆動端子 L OUT 24 まで、PWM パルスのオン信号送出開始タイミングを固定遅延時間だけずれて送信する。従って、LED 駆動端子 L OUT 1 - L OUT 24 のそれぞれは固定遅延時間だけ異なる PWM 位相で 24 個の LED を駆動制御する。

## 【0111】

40

図 14、図 15 を用いて、24 個の LED のグループ制御を説明する。演出制御情報の第 1 バイトの bit 7 を 1 に設定してグループ制御を行う。24 個の LED 駆動端子 L OUT 1 - L OUT 24 を、3 本の LED 駆動端子毎のグループに分け、それぞれのグループは、それぞれ固定遅延時間だけ異なるタイミングでオン信号の送出を開始する。図 14 では、LED 駆動端子 L OUT 1 - L OUT 3 で構成されるグループ 1 と、LED 駆動端子 L OUT 4 - L OUT 6 で構成されるグループ 2 とは、固定遅延時間だけ異なるタイミングでオン信号の送出を開始する。

## 【0112】

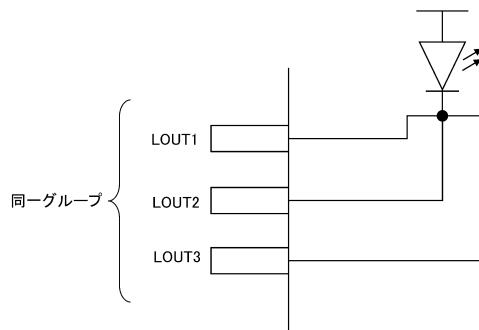

図 15 に図示するように、1 つのグループの 3 本の LED 駆動端子 L OUT 1 - L OUT 3 を並列に接続して 1 つの LED を駆動制御する。このように構成することで、1 つの L

50

LEDは3本のLED駆動端子によって定電流駆動される。従って、該LEDに流れる電流値は1個のLEDを1本のLED駆動端子から駆動制御した場合の3倍の電流値となる。このようにグループ制御することで、個別制御の場合の3倍の発光輝度でLEDを発光制御することが可能となる。図15に図示した例とは異なり、1つのグループの3本のLED駆動端子のそれぞれから、別のLEDを駆動制御してもよい。あるいは2本のLED駆動端子を並列にして1つのLEDを駆動制御し、残りの1本のLED駆動端子から他のLEDを駆動制御するように構成してもよい。

#### 【0113】

<LED制御回路の初期化>

遊技店では、毎日、開店前に遊技機に電源を投入する。電源投入時に前日の演出制御情報がLED制御回路LCのレジスタ回路LD1に記憶されたまま残っている可能性がある。この場合、電源投入時にLED制御回路LCが記憶している前日の演出制御情報に基づいて、遊技機のLEDが発光輝度制御される可能性がある。従って、電源投入時において、LED制御回路LCに記憶されている可能性のある前日の演出制御情報を初期化することが好ましい。

#### 【0114】

図16を用いて、遊技機の電源投入時に、制御装置から遊技機内の全てのLED制御回路LCに既に記憶されている演出制御情報を初期化する方法を説明する。LED制御回路LC内の演出制御情報を初期化するために、制御装置CDから1段目のLED制御回路LC1に初期化パターンを送出する。初期化パターンを送出する方法は2つある。

#### 【0115】

図16(A)を用いて初期化パターン1を説明する。1段目のLED制御回路LC1は制御装置CDからイネーブル信号がActive-Lowであるパルス信号を受信する。Active-Lowであるパルス信号はハイ信号からロー信号に変化し、その後最小200μsのタイミングでハイ信号に変化するパルス信号である。このActive-Lowのパルス信号を受信すると、1段目のLED制御回路LC1は制御装置CDから初期化信号を受信したと判断する。具体的には、1段目のLED制御回路LC1は制御装置CDから3線シリアルインターフェイスのイネーブル信号入力端子SENがハイ信号の状態からロー信号に変化するイネーブル信号を受信する。イネーブル信号入力端子SENがハイ信号からロー信号へ変化した段階で、LVDSインターフェイスの差動データ信号出力端子DDO1、DDO2がハイ信号からロー信号に変化する信号を出力する。3線シリアルインターフェイスのクロック信号入力端子SCLK、データ信号入力端子SDはハイ信号のままで変化しないため、LVDSインターフェイスの差動クロック信号出力端子DCO1、DCO2はハイ信号のまま変化しない。この3線シリアルインターフェイスで使用される信号からLVDSインターフェイスで使用される信号への信号変換は、3線→2線ブリッジ機能におけるヘッダ条件の送出と同じである。

#### 【0116】

続いて、イネーブル信号入力端子SENは最小200μsのタイミングでロー信号からハイ信号に変化するため、1段目のLED制御回路LC1はこのActive-Lowパルスを初期化信号と判断する。LVDSインターフェイスでは初期化パターンを送信する前に、差動データ信号出力端子DDO1、DDO2の差動データ信号をロー信号からハイ信号に変化させ、差動クロック信号出力端子DCO1、DCO2の差動クロック信号をハイ信号から所定の時間だけロー信号に変化させる。続いて、LVDSインターフェイスの出力端子から初期化パターンを送信する。初期化パターンは、差動データ信号出力端子DDO1、DDO2がハイ信号の状態において、差動クロック出力端子DCO1、DCO2がロー信号の状態からハイ信号の状態に変化する信号パターンである。このようにして、1段目のLED制御回路LC1は制御装置CDから受信した初期化信号に基づいて、下位の2段目のLED制御回路LC2にLVDSインターフェイスでの初期化パターンを送信するように構成されている。

#### 【0117】

10

20

30

40

50

初期化パターン1を用いて、制御装置CDからLED制御回路LCを初期化することが可能である。しかし、初期化パターン1はイネーブル信号として最小200μsのActi<sub>v</sub>e-Low信号を送信する信号である。3線シリアルインターフェイスのイネーブル信号線は単線であることから、遊技機内の電磁部品等から誘導ノイズが重畠される可能性があり、この誘導ノイズをActi<sub>v</sub>e-Low信号であると誤受信する可能性がある。このため、初期化パターン1より誘導ノイズの影響で誤動作する可能性が低い初期化パターン2を送出することが考えられる。

#### 【0118】

図16(B)を用いて初期化パターン2を説明する。1段目のLED制御回路LC1は制御装置CDから、8個のクロック信号と、全てのデータ値がハイ信号である第1バイトのみを受信する。1段目のLED制御回路はこの全てがハイ信号である第1バイトのみを受信することで、制御装置から初期化信号を受信したと判断する。具体的には、3線シリアルインターフェイスのイネーブル信号入力端子SENがハイ信号の状態からロー信号に変化するイネーブル信号を受信すると、3線2線ブリッジ機能におけるヘッダ条件の送出と同様にLVDSインターフェイスの差動データ信号出力端子DDO1、DDO2はハイ信号からロー信号に変化するデータ信号を出力する。初期化パターン2では、続いて、全てのデータ値がハイ信号である第1バイトのみを受信する。すなわち、3線シリアルインターフェイスのクロック信号入力端子SCLKから8個のクロック信号を受信し、データ信号入力端子SDはハイ信号のままである。8個のクロック信号を受信した後で、イネーブル信号入力端子SENはロー信号の状態からハイ信号の状態に変化する。このため、1段目のLED制御回路LC1は全てのデータ値がハイ信号である第1バイトのみを受信したと判断可能となる。

#### 【0119】

3線シリアルインターフェイスの入力端子から第1バイトを受信すると、LVDSインターフェイスの差動クロック信号出力端子DCO1、DCO2、および、差動データ出力端子DDO1、DDO2から受信した第1バイトのデータを出力する。この第1バイトのデータの送受信のタイムチャートは、図8に図示した3線2線ブリッジのタイムチャートと同じである。第1バイトを受信したタイミングで、イネーブル信号入力端子SENがロー信号からハイ信号に変化する、このため、1段目のLED制御回路1は第1バイトのデータ値が全てハイ信号を受信したことから初期化信号を受信したと判断し、LVDSインターフェイスから初期化パターンの送信を以下のように送信する。LVDSインターフェイスの出力端子から初期化パターンを送信する前に、差動クロック信号出力端子DCO1、DCO2の差動クロック信号をハイ信号から所定の時間だけロー信号に変化させる。続いて、初期化パターンを送信する。初期化パターンは、差動データ信号出力端子DDO1、DDO2がハイ信号の状態において、差動クロック出力端子DCO1、DCO2がロー信号の状態からハイ信号の状態に変化する信号パターンである。このようにして、1段目のLED制御回路LC1は制御装置CDから受信した初期化信号に基づいて、下位の2段目のLED制御回路LC2にLVDSインターフェイスでの初期化パターンを送信するように構成されている。

#### 【0120】

2段目以降のLED制御回路LCでは上位のLED制御回路LCからLVDSインターフェイスでの初期化パターンを受信すると、LVDSインターフェイスの出力端子から下位のLED制御回路LCに対して、初期化パターンを送出する。このようにして、制御装置CDから1段目のLED制御回路LC1に送信された初期化パターンは、2段目のLED制御回路LC2、続いて、3段目の演出制御手LC3へと、順次、下位のLED制御回路LCに送信される。このように構成されているため、制御装置から1段目のLED制御回路LC1に初期化信号が送信されると、遊技機内の全てのLED制御回路LCに初期化パターンが送信され、全てのLED制御回路LCを初期化することが可能な構成となっている。

#### 【0121】

10

20

30

40

50

## [第2実施形態]

次に、本発明に関わる遊技機の第2の実施形態としてのぱちんこ遊技機PMの全体構成について概要説明する。

### 【0122】

#### <ぱちんこ遊技機の基本構成>

まず図17を参照しながら、ぱちんこ遊技機PMの正面側の基本構造を説明する。ぱちんこ遊技機PM（単に「遊技機PM」とも称する）は、図17に示すように、外郭方形枠サイズに構成された縦向きの固定保持枠をなす外枠101の開口前面に、これに合わせた方形枠サイズに構成されて開閉搭載枠をなす前枠102が互いの正面左側縁部に配設された上下のヒンジ機構103により横開き開閉および着脱が可能に取り付けられて構成される。前枠102は、正面右側縁部に設けられたダブル錠と称される施錠装置4を利用して常には外枠101と係合連結された閉鎖状態に保持される。10

### 【0123】

前枠102には、この前枠102の上部前面域に合わせた方形状のガラス枠105が上下のヒンジ機構103を利用して横開き開閉および着脱可能に組み付けられている。ガラス枠105は、施錠装置104を利用して常に前枠102の前面を覆う閉鎖状態に保持される。前枠102には、遊技盤120が着脱可能にセット保持され、閉鎖保持されるガラス枠105の複層ガラスを通して遊技盤120の正面の遊技領域PAを視認可能に臨ませるようになっている。

### 【0124】

ガラス枠105の前面側には、遊技の展開状況に応じて発光する枠ランプ（LEDランプ）110や、遊技の展開状況に応じて効果音を発生するスピーカ111が設けられている。ガラス枠105の下部には遊技球を貯留する上下の球皿（上球皿108及び下球皿109）が設けられており、上球皿108の正面中央には遊技者によって押圧操作される演出ボタン（演出スイッチ）115が設けられ、下球皿109の正面右側には遊技球の発射操作を行う発射ハンドル112が設けられている。以下においては、演出用の操作入力手段を「演出ボタン115」と称するが、本例における演出ボタン（演出スイッチ）115とは、オン／オフ操作式のボタン型のスイッチ、操作入力の方向に応じた出力を行う十字型のスイッチ（十字キー、十字ボタン）、傾動操作式のレバー型のスイッチ、回転操作式のダイヤルスイッチ、遊技者の手が近付いたとき又は接触したときに出力を行う近接スイッチ、タッチセンサ、タッチパネルなど、あらゆる操作入力手段を含む。20

### 【0125】

遊技盤120は、例えばアクリル樹脂やポリカーボネート樹脂、ABS樹脂等の合成樹脂材料を用いて矩形平板状に形成された基板をベースとして構成されている。遊技盤120の前面には、外レール141及び内レール142が円弧状に固設されて遊技球が転動可能な略円形の遊技領域PAが区画形成されている。外レール141と内レール142とにより遊技球を遊技領域PAへ案内するための案内通路（図示せず）が形成され、この案内通路における遊技球の出口開口の近傍位置（内レール142の先端部に）、該出口開口から遊技領域PA内へ放出された遊技球が再び案内通路へ逆戻りするのを防止する球戻り防止弁143が配設されている。この遊技領域PAには、風車や多数本の遊技釘とともに、第1始動口151、第2始動口152、作動ゲート153、大入賞口154、一般入賞口161, 162, 163, 164などの各種入賞口の他、第1特別図柄表示装置171、第2特別図柄表示装置172、第1特図保留ランプ173、第2特図保留ランプ174、普通図柄表示装置175、普図保留ランプ176などの各種表示装置が設けられている。遊技領域PAの略中央にはセンター飾り121が配設されており、このセンター飾り121の中央開口を通して演出表示装置170の画面が視認可能に設けられている。遊技領域PAは、略中央のセンター飾り121を基準として、センター飾り121の左側の領域（左打ちに対応した盤面領域）である左側領域PA1と、センター飾り121の右側の領域（右打ちに対応した盤面領域）である右側領域PA2とに区画される。センター飾り121の上部には、外レール141と略上下方向に対向する天板部122が一体形成されてお304050

り、上記の案内通路の延長上において、天板部 122 と外レール 141 との間で遊技球が右側領域 PA2 へ通過可能な導入通路 144 が形成されている。遊技領域 PA の下端には各入賞口に入球せずに転動流下した遊技球を遊技盤 120 の裏側へ排出するアウトロ 129 が設けられている。以下、遊技盤 120 に設けられた各構成要素を順番に説明する。

#### 【 0 1 2 6 】

第 1 始動口 151 は、第 1 特別図柄遊技に対応する始動入賞口として設けられており、遊技球の入球を検出するための第 1 始動口スイッチ 511 を備えている。第 1 始動口 151 への遊技球の入球は、第 1 特別図柄抽選の契機となる。

#### 【 0 1 2 7 】

第 2 始動口 152 は、第 2 特別図柄遊技に対応する始動入賞口として設けられており、遊技球の入球を検出するための第 2 始動口スイッチ 521 を備えている。第 2 始動口 152 への遊技球の入球は、第 2 特別図柄抽選の契機となる。第 2 始動口 152 は、普通電動役物 522 と、この普通電動役物 522 を開閉駆動させるための普通電動役物ソレノイド 523 とを備える。普通電動役物 522 は、第 2 始動口 152 へ遊技球が入球し難い閉鎖状態と該状態よりも遊技球が入球し易い開放状態とに可変する。ここで、第 2 始動口 152 は、普通電動役物 522 が開放されなければ、遊技球が入球し難い構造となっている。一方、普通電動役物 522 が開放されると、第 2 始動口 152 への入球容易性が高まる。

#### 【 0 1 2 8 】

作動ゲート 153 は、普通図柄遊技に対応する始動入賞口として設けられており、遊技球の通過を検出するための作動ゲートスイッチ 531 を備えている。作動ゲート 153 への遊技球の通過は、第 2 始動口 152 の普通電動役物 522 を拡開させるか否かを決定するための普通図柄抽選の契機となる。

#### 【 0 1 2 9 】

大入賞口 154 は、第 1 特別図柄又は第 2 特別図柄の当否抽選で大当たり又は小当たりとなつた場合に開放状態となる横長方形形状をなす入賞口として形成される。大入賞口 154 は、遊技球の入球を検出するための大入賞口スイッチ 541 を備えるとともに、いわゆるアタッカー装置と称される特別電動役物 542 と、この特別電動役物 542 を開閉駆動させるための大入賞口ソレノイド 543 とを備えている。特別電動役物 542 は、大入賞口 154 に遊技球が入球不能又は入球困難な通常状態と遊技球が入球可能又は入球容易な開放状態とに可変する。本例において大入賞口 154 は、遊技領域 PA における右側領域 PA2 に設けられている。そのため、特別遊技状態（大当たり遊技状態）においては、遊技領域 PA へ向けて遊技球を発射する際に、右側領域 PA2 を狙って打つ、いわゆる右打ちを行うことで、大入賞口 154 への入球が容易となっている。

#### 【 0 1 3 0 】

一般入賞口 161 ~ 163 は、左打ちに対応した盤面領域である左側領域 PA1 に配設され、左側領域 PA1 を流下した遊技球が入球可能である。一般入賞口 161 ~ 163 は、遊技球の入球を検出するための左側一般入賞口スイッチ 611 を備えている。この左側一般入賞口スイッチ 611 は、コスト低減等の観点から、三つの一般入賞口 161 ~ 163 の共通センサ（シングルセンサ）として構成されており、いずれの一般入賞口 161 ~ 163 への遊技球の入球も検出が可能である。一般入賞口 164 は、右打ちに対応した盤面領域である右側領域 PA2 に配設され、右側領域 PA2 を流下した遊技球が入球可能である。一般入賞口 164 は、遊技球の入球を検出するための右側一般入賞口スイッチ 641 を備えている。各一般入賞口 161 ~ 164 への遊技球の入球は特別図柄又は普通図柄の抽選の契機とはならないが、他の入賞口（作動ゲート 153 を除く）と同様に賞球獲得の契機となる。

#### 【 0 1 3 1 】

第 1 特別図柄表示装置 171 は、遊技球が第 1 始動口 151 に入球したことを契機として、第 1 特別図柄の変動表示および確定表示を行う。この第 1 特別図柄表示装置 171 は、外部から視認される第 1 特別図柄を表示するランプ表示部と、その裏面に設けられた LED から構成される LED ランプ構成であり、LED の点滅パターン制御によってランプ

10

20

30

40

50

表示部において第1特別図柄の変動表示を行い、LEDの点灯表示によって第1特別図柄の確定表示を行う。

**【0132】**

第2特別図柄表示装置172は、遊技球が第2始動口152に入球したことを契機として、第2特別図柄の変動表示および確定表示を行う。この第2特別図柄表示装置172は、外部から視認される第2特別図柄を表示するランプ表示部と、その裏面に設けられたLEDから構成されるLEDランプ構成であり、LEDの点滅パターン制御によってランプ表示部において第2特別図柄の変動表示を行い、LEDの点灯表示によって第2特別図柄の確定表示を行う。

**【0133】**

第1特図保留ランプ173および第2特図保留ランプ174は、ランプ表示部と、その裏面に設けられた複数個のLEDから構成されるLEDランプ構成であり、それぞれのLEDランプのLEDの点灯・点滅表示によって第1特別図柄および第2特別図柄の作動保留球数（最大4個）を表現する。第1特別図柄の作動保留球数は、第1特別図柄又は第2特別図柄の変動中あるいは特別遊技の実行中に、第1始動口151への入球に基づき取得した乱数値に係る数であり、当該取得した乱数値を保留する、すなわち、当該取得した乱数値について当否判定許可条件（変動開始条件）を充足するまで当否判定が一旦保留されることになった数を示している。同様に、第2特別図柄の作動保留球数は、第1特別図柄又は第2特別図柄の変動中あるいは特別遊技の実行中に、第2始動口152への入球に基づき取得した乱数値に係る数であり、当該取得した乱数値を保留する、すなわち、当該取得した乱数値について当否判定許可条件（変動開始条件）を充足するまで当否判定が一旦保留されることになった数を示している。

10

**【0134】**

普通図柄表示装置175は、ランプ表示部と、その裏面に設けられた複数個のLEDから構成されるLEDランプ構成であり、普通図柄の変動表示及び確定表示を行う。普図保留ランプ176は、ランプ表示部と、その裏面に設けられた複数個のLEDから構成されるLEDランプ構成であり、当該ランプの点灯個数が普通図柄変動の保留数（まだ実行されていない普通図柄変動の数）に相当する。普通図柄表示装置175の左側には、特別遊技におけるラウンド遊技（単位遊技）の回数（ラウンド数：特別電動役物542が連続して作動する回数）を表示するラウンド表示器177が設けられている。

20

**【0135】**

演出表示装置170は、主として、第1特別図柄又は第2特別図柄と連動して変動表示・変動停止する装飾図柄や大当たりの期待度を予告的に示唆又は報知する予告演出を含む演出画像を表示するとともに、第1特別図柄および第2特別図柄の保留表示を行う。具体的には、演出表示装置170の画面上に、装飾図柄の変動表示や予告演出表示などが実行される装飾図柄表示部700と、第1特図保留ランプ173と同期して第1特別図柄の保留表示が実行される第1特図保留表示部701と、第2特図保留ランプ174と同期して第2特別図柄の保留表示が実行される第2特図保留表示部702とが設けられている。本実施形態では、演出表示装置170として、液晶表示装置を採用している。装飾図柄表示部700には、所定の有効ライン（不図示）上に、装飾図柄の変動表示領域となる三列の表示領域（左表示領域Z1、中表示領域Z2、右表示領域Z3）が設けられており、左表示領域Z1に対応して装飾図柄の左図柄、中表示領域Z2に対応して装飾図柄の中図柄、右表示領域Z3に対応して装飾図柄の右図柄がそれぞれ停止表示されるようになっている。特図保留表示部701、702には、通常の表示態様では、特別図柄の作動保留球が生起されると白丸印の保留画像が表示される一方、当該作動保留球が消化されると対応する保留画像が消失される。この保留画像は、特別図柄の作動保留球の発生順（入球順）に従つて順番に表示され、各保留表示部701、702に最大で4個ずつ表示が可能である。

30

**【0136】**

センター飾り121は、演出表示装置170の周囲に設置され、遊技球の流路、演出表示装置170の画面の保護、装飾等の機能を有する。センター飾り121には、遊技の展

40

50

開状況に応じた演出動作を実行する可動役物 124 が設けられている。可動役物 124 は、駆動源としてモータ M ( 例えは、ステッピングモータ ) を備えて構成されている。遊技盤 120 には、遊技の展開状況に応じて発光する盤ランプ ( LED ランプ ) 180 が設けられている。この盤ランプ 180 には、一般入賞口 161 ~ 163 の近傍に配置された稻妻形の入賞報知ランプ 181 ~ 183 や、一般入賞口 164 の近傍に配置された星形の入賞報知ランプ 184 などが含まれる。以下の説明では、便宜上、枠ランプ 110 および盤ランプ 180 ( 入賞報知ランプ 181 ~ 184 を含む ) を総称して「演出ランプ LP 」とも称する。演出ランプ LP は外部から視認されるランプ表示部と、その裏面に設けられた LED から構成される LED ランプ構成であり、 LED の発光制御を行うことで、盤ランプ 180 では遊技機の展開状況に応じて発光演出を行い、入賞報知ランプ 181 ~ 184 では入賞報知を行う。

#### 【 0137 】

続いて、図 18 を参照しながら、ぱちんこ遊技機 PM の背面側の基本構造を説明する。前枠 102 の背面側には、中央に前後連通する窓口を有して前枠 102 よりも幾分小型の矩形枠状に形成された基枠体をベースとしてなる裏セット盤 130 が、上下のヒンジ機構 103 を介して前枠 102 後方に横開き開閉及び着脱が可能に連結されている。この裏セット盤 130 には、前面開放の矩形箱状をなす裏セットカバー 130C が着脱自在に装着されており、常には前枠 102 に取り付けられた遊技盤 120 の裏面側を覆って配設されている ( これにより後述する主制御基板 200 、演出制御基板 300 、画像制御基板 400 が裏セットカバー 130C により覆われる ) 。

#### 【 0138 】

裏セット盤 130 の各部には、多数個の遊技球を貯留する貯留タンク 131 、貯留タンク 131 から右方に緩やかな下り傾斜を有して延びるタンクレール 132 、タンクレール 132 の右端部に繋がり下方に延びる球供給通路部 133 、球供給通路部 133 により導かれた遊技球を払い出す賞球払出ユニット 134 、賞球払出ユニット 134 から払い出された遊技球を上球皿 106 に導くための賞球通路部 135 などが設けられている。

#### 【 0139 】

遊技盤 110 の背面側には、ぱちんこ遊技機 PM の作動を統括的に制御する主制御基板 200 や、演出全般の制御を行う演出制御基板 300 、遊技展開に応じた画像表示、効果音の制御を行う画像制御基板 400 、などが取り付けられている。これに対して、裏セット盤 130 の背面側には、遊技球の発射及び払い出しに関する制御を行う払出制御基板 500 や、遊技施設側から受電して各種制御基板や電気・電子部品に電力を供給する電源基板 600 などが取り付けられている。これらの制御基板は、不正改造防止のため、カシメ構造及び封印シール構造を有する透明樹脂製の基板ケースに収容されたアッセンブリ状態で遊技盤 120 背面又は裏セット盤 130 背面の所定位置にそれぞれ配設される。これらの制御基板とぱちんこ遊技機 PM 各部の電気・電子部品とがハーネス ( コネクタケーブル ) を介して相互に接続されて、ぱちんこ遊技機 PM が作動可能に構成されている。

#### 【 0140 】

##### < ぱちんこ遊技機の制御構成 >

次に、図 19 を追加参照して、本実施形態に係るぱちんこ遊技機 PM に搭載された各制御基板について説明する。図 19 は、ぱちんこ遊技機 PM の制御構成を示す制御ブロック図である。

#### 【 0141 】

主制御基板 200 は、遊技に関する各種の演算処理を行うメイン CPU 201 と、制御プログラムや各種データ等を記憶した ROM 202 と、一時記憶領域となるワークエリアやバッファメモリとして機能する RAM 203 と、周辺基板や各デバイスとの間の信号を入出力する I/O ポート回路 204 とを備えて構成された主制御マイコン ( ワンチップマイコン ) 210 を搭載しており、メイン CPU 201 が ROM 202 に記憶された制御プログラムに従って遊技進行に係る主要な制御を実行するように構成されている。その他、主制御基板 200 には、図示省略するが、水晶発振器からのクロック信号を分周して内部

システムクロックを生成するクロック回路、メインC P U 2 0 1が誤動作や暴走状態となつたときにリセットをかけて正常な状態に復帰させるW D T回路、リアルタイム割込みの発生や時間計測を可能とするC T C回路、メインC P U 2 0 1によるプログラム処理（ソフトウェア乱数）とは別系統として動作して所定の乱数（内蔵乱数）を生成する乱数生成回路などが搭載されており、これらが内部バスを介して相互に接続されている。

#### 【0142】

メインC P U 2 0 1は、各スイッチからの検出情報などに基づき、R O M 2 0 2に格納された各種の制御プログラムを読み出して演算処理を行うことで、遊技の主制御に係る各種処理を実行する。R A M 2 0 3は、電源基板6 0 0において生成されるバックアップ電源によってバックアップされる不揮発性記憶手段としてのバックアップR A Mである。R A M 1 0 3のバックアップ領域は、電源断が生じた場合、当該電源断時に保持していたスタックポインタや各レジスタ等のデータを記憶しておくためのエリアとなっており、電源投入時（電源断復帰時）には当該バックアップ領域の情報に基づいて遊技機の状態が電源断前の状態に復帰されるようになっている。

#### 【0143】

主制御基板2 0 0は、第1始動口スイッチ5 1 1、第2始動口スイッチ5 2 1、作動ゲートスイッチ5 3 1、大入賞口スイッチ5 4 1、左側一般入賞口スイッチ6 1 1、右側一般入賞口スイッチ6 4 1などと電気的に接続されており、I / Oポート回路2 0 4を介して、各種スイッチからの検出信号をメインC P U 2 0 1に入力する。主制御基板2 0 0は、第1特別図柄表示装置1 7 1、第2特別図柄表示装置1 7 2、第1特図保留ランプ1 7 3、第2特図保留ランプ1 7 4、普通図柄表示装置1 7 5および普図保留ランプ1 7 6に電気的に接続されるとともに、普通電動役物ソレノイド5 2 3および特別電動役物ソレノイド5 4 3に電気的に接続されており、I / Oポート回路2 0 4を介して、メインC P U 2 0 1からの制御信号を各種表示手段および各種ソレノイドに送信する。

#### 【0144】

主制御基板2 0 0と演出制御基板3 0 0との間は、8本のパラレル信号線および1本のストローブ線で接続されており、主制御基板2 0 0から演出制御基板3 0 0へと向かう單一方向のみで通信可能に接続され、主制御基板2 0 0から演出制御基板3 0 0へ各種の演出制御コマンドが送信される。演出制御基板3 0 0から主制御基板2 0 0へデータを送信することはできず、主制御基板2 0 0に対してデータの送信を要求することはできないようになっている。なお、主制御基板2 0 0と演出制御基板3 0 0との接続は8本のパラレル信号線と1本のストローブ線の接続に限定されない。3線シリアルインターフェイスによって接続されてもよい。

#### 【0145】

演出制御基板3 0 0は、主制御基板2 0 0からの演出制御コマンドに基づき遊技演出に関する各種の演算処理を行うサブメインC P U 3 0 1、演出制御プログラムや各種データ等を記憶したR O M 3 0 2、一時記憶領域となるワークエリアやバッファメモリとして機能するR A M 3 0 3と、周辺基板や各デバイスとの間の信号を入出力するI / Oポート回路3 0 4とを備えて構成された演出制御マイコン（ワンチップマイコン）3 1 0を搭載しており、サブメインC P U 3 0 1がR O M 3 0 2に記憶された制御プログラムに従って遊技演出に係る主要な制御を実行するように構成されている。その他、演出制御基板3 0 0には、図示省略するが、水晶発振器からのクロック信号を分周して内部システムクロックを生成するクロック回路、サブメインC P U 3 0 1が誤動作や暴走状態となつたときにリセットをかけて正常な状態に復帰させるW D T回路、システムクロックに基づき各種信号を出力するT P U回路、T P U回路からの信号などに基づきタイマ割込み等の各種割込みを起動させる割込みコントローラ、シリアルデータを入出力するためのシリアル通信回路などが搭載されており、これらが内部バスを介して相互に接続されている。

#### 【0146】

演出制御基板3 0 0は、主制御基板2 0 0からの演出制御コマンドに基づく演出制御処理にて、画像制御基板4 0 0へ画像および音響を指示する画像制御コマンド、ランプ接続

10

20

30

40

50

基板 191 を制御するためのランプ制御信号（ランプデータ）、モータドライバ 192 を制御するための駆動制御信号（駆動データ）などを生成する。演出制御基板 300 は、画像制御基板 400 と双方向通信が可能に接続されており、画像および音響に関する画像制御コマンドが演出制御基板 300 から画像制御基板 400 へ送信される一方、その応答として、この画像制御コマンドを正常に受信できた旨を示す応答コマンド（ACK コマンド）が画像制御基板 400 から演出制御基板 300 へ送信される。

#### 【0147】

演出制御基板 300 は、複数の LED を発光制御するための演出出力制御手段を搭載したランプ接続基板 191 と電気接続されており、シリアル通信回路を介して、ランプ接続基板 191 を制御するためのランプ制御信号（ランプデータ）を送信する。本例では、演出制御基板 300 とランプ接続基板 191 とは、クロック同期式のシリアル通信が採用されており、ランプデータ伝送用のデータ線とは別の信号線（クロック線）で送信されるクロック信号に同期して、ランプ制御信号が当該データ線を介して 1 ビットずつ送信される。ランプ接続基板 191 は、演出制御基板 300 から送信される LED 駆動用のランプ制御信号を受けて機能する LED ドライバを内蔵しており、このランプ制御信号に基づき回路内のスイッチをオン／オフ切り替えることにより、演出ランプ LP に対して駆動電流を供給又は遮断して、演出ランプ LP を点灯又は消灯させる制御を行う。

#### 【0148】

さらに、演出制御基板 300 は、複数のモータドライバ 192 と電気接続されており、I/O ポート回路 304 を介して、モータドライバ 192 を制御するための駆動制御信号（駆動データ）をモータドライバ 192 へ送信する。モータドライバ 192 は、演出制御基板 300 から送信される役物駆動用の駆動制御信号に基づき回路内のスイッチをオン／オフ切り替えることにより、各可動役物 124 のステッピングモータに対して駆動電流を供給又は遮断して、各可動役物 124 を動作させる制御を行う。モータドライバ 192 へのデータ送信はパラレル通信方式が採用されている。

#### 【0149】

画像制御基板 400 は、演出制御基板 300 からの画像制御コマンドに基づき画像演出に関する各種の演算処理を行うサブサブ CPU 401 と、画像制御プログラムや各種データ等を記憶した ROM 402 と、一時記憶領域となるワークエリアやバッファメモリとして機能する RAM 403 と、周辺基板や各デバイスとの間の信号を入出力する I/O ポート回路 404 とを備えて構成された画像制御マイコン（ワンチップマイコン）410 を搭載しており、サブサブ CPU 401 が ROM 402 に記憶された制御プログラムに従って画像演出に係る主要な制御を実行するように構成されている。その他、画像制御基板 400 には、図示省略するが、サブサブ CPU 401 から取得した制御信号に基づき演出内容に沿った画像データを生成する VDP と、サブサブ CPU 401 から取得した制御信号に基づき演出内容に沿った音響データを生成する音源 IC とを搭載している。VDP は、いわゆる画像プロセッサであり、サブサブ CPU 401 からの指示に応じて画像 ROM に記憶された画像データを読み込み、これを画像処理して生成した映像信号（画像データ）を演出表示装置 170 に送信する。この VDP には、画像 ROM から読み出された画像データの展開・加工に使用される高速の VRAM が接続されている。音源 IC は、サブサブ CPU 401 からの指示に応じて音声 ROM に記憶された音響データを読み込み、これを合成処理して生成した音響データを増幅器（デジタルアンプ）を介してスピーカ 111 に出力する。

#### 【0150】

払出制御基板 500 は、払出 CPU 501、ROM 502 および RAM 503 を主体として構成されている。払出制御基板 500 は、主制御基板 200 と双方向通信可能に接続されており、主制御基板 200 からの払出制御コマンドに基づいて賞球払出ユニット 134 を駆動させて賞球を払い出すための制御を実行するとともに、発射ハンドル 112 の操作量に基づき球送り機構 113 と発射機構 114 とを同期的に駆動させて遊技球の発射の制御を実行する。

10

20

30

40

50

## 【0151】

電源基板600は、詳細図示を省略するが、遊技島の電源設備から供給される一次電源を基に、各制御基板で使用される通常時の電源を生成するための通常電源回路と、バックアップ電源を生成するためのバックアップ電源回路と、電圧低下による電源断を監視するための電源断監視回路と、を具備して構成され、各制御基板や遊技用機器等の電子・電気部品に必要な電源を供給する。電源基板600には、電源回路を起動させるための電源スイッチが接続されており、遊技島の電源装置から1次電源が供給されていることを前提として、該電源スイッチがオンになると、電源基板600の通常電源回路から各制御基板などに所定の電源が供給される。電源基板600は、遊技島の電源装置からの電源供給が遮断されたことを検出可能に構成されており、電源断の検出時にはその旨を報知する電源断信号（NMI信号）を主制御基板200、演出制御基板300、払出制御基板500に送信する。バックアップ電源回路は、遊技島の電源装置からぱちんこ遊技機PMに電源が供給されているときに充電される仕組みとなっている。電源基板600には、ぱちんこ遊技機PMの電源投入時に、主制御基板200のRAM203の一時記憶内容を一旦消去して初期値を設定するためのRAMクリアスイッチ（図示せず）が接続されている。RAMクリアスイッチは、電源基板600ではなく、例えば主制御基板200に接続される構成であってもよい。

10

## 【0152】

<制御基板によるランプ制御回路の演出制御>

次に、主制御基板200からの第1特別図柄表示装置171、第2特別図柄表示装置172、普通図柄表示装置175、第1特図保留ランプ173、第2特図保留ランプ174、普図保留ランプ176のランプ演出制御を説明する。主制御基板200にはメインCPU201、ROM202、RAM203が配設され、メインCPU201は、ROM202に記憶されているソフトウェアを動作させ、遊技機の遊技状態に応じて基づいて、第1特別図柄表示装置171、第2特別図柄表示装置172、普通図柄表示装置175、第1特図保留ランプ173、第2特図保留ランプ174、普図保留ランプ176のそれぞれのLEDランプのLEDの発光輝度制御を行うための演出制御内容を決定し、第1特別図柄表示装置171、第2特別図柄表示装置172、普通図柄表示装置175、第1特図保留ランプ173、第2特図保留ランプ174、普図保留ランプ176のそれぞれのLED制御回路に演出制御情報を送信する。

20

30

## 【0153】

第1特別図柄表示装置171、第2特別図柄表示装置172、普通図柄表示装置175、第1特図保留ランプ173、第2特図保留ランプ174、普図保留ランプ176のそれぞれランプ表示部（演出表示部材）およびその裏側に設けられたLEDから構成されるLEDランプ構成であり、それぞれのLEDランプにはLED制御回路が配設されている。LEDとしては、単色で発光する単色LEDあるいは三原色のLED素子から構成されるカラーLEDがあり、第1特図保留ランプ173、第2特図保留ランプ174、普図保留ランプ176はそれぞれその大きさに応じて一つもしくは複数のLEDが用いられる。単色LEDは赤色LED、緑色LED、青色LEDがあり、それぞれ発光輝度制御を行つてその明るさが変化する演出制御を行う。主制御基板200は各LEDランプの演出制御の内容を決定して、演出制御情報として第1特別図柄表示装置171、第2特別図柄表示装置172、普通図柄表示装置175、第1特図保留ランプ173、第2特図保留ランプ174、普図保留ランプ176に送信し、これらの各装置は主制御基板200からの演出制御情報に基づいて各装置の表示ランプを構成するLEDの発光輝度制御を行う。図19においては、第1特別図柄表示装置171、第2特別図柄表示装置172、普通図柄表示装置175、第1特図保留ランプ173、第2特図保留ランプ174、普図保留ランプ176のそれぞれは1つの装置として示されているが。これらの各装置のそれぞれには多数のLEDが用いられており、これらの発光輝度制御を行うために、これらの各装置において、複数個のLED制御回路が表示ランプに対応する位置に設けられている。

40

## 【0154】

50

また、演出制御基板 300 からのランプ接続基板 191、演出ランプ LP のランプ演出制御を説明する。ランプ制御基板 191 には LED 制御回路が配設され、遊技機の遊技状態に応じて主制御基板 200 が演出制御内容を決定して、演出制御基板 300 に演出制御コマンドが送信される。演出制御基板 300 では、主制御基板 200 から受信した演出制御コマンドに基づいて、LED の発光輝度制御を行うための演出制御情報を作成する。演出制御基板 300 は、LED 制御回路であるランプ接続基板 191 に演出制御情報を送信し、ランプ接続基板 191 は演出ランプ LP の発光輝度制御を行う。ここで、演出ランプ LP は LED ランプであり、複数個の単色 LED、あるいは、複数個の三原色 LED が使用されている。単色 LED を発光輝度制御を行うことで単色 LED ランプの白色の明るさが変化する演出制御を行うことができる。三原色 LED が使用されている場合は、赤色 LED、緑色 LED、青色 LED のそれぞれの発光輝度値を周期的に変化させて発光輝度制御を行うことで、多様な演出制御を行うことができる。また、演出ランプ LP は図 17 を用いて説明したように、センター飾り 121 の周囲の様々な位置に離れて配設されている。このため、ランプ接続基板 191 は複数個の LED 制御回路で構成し、演出ランプ LP を構成する LED のそれぞれの近傍に配設することが好ましい。

#### 【0155】

##### <制御基板の接続インターフェイス>

遊技機の遊技状態を示す情報が RAM 203 上に記憶され、メイン CPU 201 上で動作するソフトウェアは、これらの遊技機の遊技状態を示す情報を契機に、制御対象となる第 1 特別図柄表示装置 171、第 2 特別図柄表示装置 172、普通図柄表示装置 175、第 1 特図保留ランプ 173、第 2 特図保留ランプ 174、普図保留ランプ 176 の演出制御情報を ROM 202 より読み出す。主制御基板 200 上ではメイン CPU 201 と ROM 202、RAM 203 とは、一般に、8 ビットパラレルバスによって接続されている。後述するように、主制御基板 200 と周辺回路との接続は 8 ビットパラレルバスではなく、シリアルインターフェイスで接続される。主制御基板 200 には 8 ビットパラレルバスのインターフェイスをシリアルインターフェイスに変換する I/O ポート回路 204 が配設されて、主制御基板 200 と周辺回路とはシリアルインターフェイスを用いて接続される。8 ビットパラレルバスのインターフェイスでは 1 個のクロック信号の時間で 8 ビットの信号を 8 本の信号線を用いて同時に送受信するが、シリアルインターフェイスでは 1 個のクロック信号の時間で 1 本の信号線に 1 ビットの信号を送信し、8 個のクロック信号の時間で 8 ビットの信号を送受信する。ROM 202 から 8 ビットパラレルバスを介して読み出された演出制御情報は、シリアルインターフェイスのデータ信号に変換されて、各 LED 制御回路（第 1 特別図柄表示装置 171、第 2 特別図柄表示装置 172、普通図柄表示装置 175、第 1 特図保留ランプ 173、第 2 特図保留ランプ 174、普図保留ランプ 176）に送信される。

#### 【0156】

メイン CPU 201 上で動作するソフトウェアが演出ランプ LP の演出内容を決定すると、主制御基板 200 から演出制御基板 300 に 8 ビットパラレルバスを介して演出コマンドを送信する。演出制御基板 300 には、主に演出の管理に関する各種の演算処理を行うサブメイン CPU 301 と、制御プログラム等を記憶した読み出し専用の記憶装置である ROM 302 と、情報の書き込み及び読み出しが可能な記憶装置である RAM 303 とが配設されており、ROM 302 に記憶された制御プログラムに従って各駆動回路が動作することにより、画像演出や音声演出の管理に関する制御、LED ランプ演出に関する制御等が行われるようになっている。LED ランプ演出に関する演出制御情報は、8 ビットパラレルバスに接続された ROM 302 から演出制御基板 300 内で I/O ポート回路 304 によってシリアルインターフェイスの信号に変換されて、ランプ制御基板 191 に送信される。なお、前述のように主制御基板 200 と演出制御基板 300 とは 8 ビットパラレルの接続に限定されないことから、主制御基板 200 から演出制御基板 300 に 3 線シリアルインターフェイスを介して演出コマンドを送信してもよい。

#### 【0157】

10

20

30

40

50

主制御基板 200、演出制御基板 300 上の CPU と ROM、RAM の間は CPU の入出力処理ビット数に一致する 8 ビットパラレルバスが使用される。しかし、8 ビットパラレルバスのまま CPU を実装する制御基板と周辺回路との間で各種情報を送受信すると、膨大なインターフェイス線が必要となる。このため、第 1 実施形態のスロットマシンで説明したのと同様に、主制御基板 200、および、演出制御基板 300 内において、シリアルインターフェイスに変換して制御基板から周辺回路に各種制御情報を送信する。シリアルインターフェイスとしては I2C バスおよび 3 線シリアルインターフェイスが標準シリアルインターフェイスとして標準化されている。以下の本実施形態の説明では 3 線シリアルインターフェイスを用いて説明する。しかし、本実施形態は 3 線シリアルインターフェイスに限定するものではなく、I2C バスを用いても良い。3 線シリアルインターフェイス、I2C バス以外の他のシリアルインターフェイスであっても良い。10

#### 【0158】

本実施形態の以下の説明では、主制御基板 200（メイン CPU 201）は ROM 202 に記憶されているソフトウェアによって抽選を行い、演出制御基板 300（サブメイン CPU 301）は ROM 302 に記憶されているソフトウェアが抽選結果に基づいて演出制御情報を決定するが、以下の説明ではこれらの主制御基板 200（メイン CPU 201）、演出制御基板 300（サブメイン CPU 301）を単に「制御装置」と称する。第 1 特別図柄表示装置 171、第 2 特別図柄表示装置 172、普通図柄表示装置 175、第 1 特図保留ランプ 173、第 2 特図保留ランプ 174、普図保留ランプ 176 はそれぞれの LED ランプを構成する LED 素子の発光輝度制御を行うための LED 制御回路を備えている。また、ランプ接続基板 191 は LED 制御回路であり、これらを総称して「LED 制御回路」と称する。また、第 1 特別図柄表示装置 171、第 2 特別図柄表示装置 172、普通図柄表示装置 175、第 1 特図保留ランプ 173、第 2 特図保留ランプ 174、普図保留ランプ 176、演出ランプ LP のそれぞれの LED ランプは複数の LED 素子で構成され、以下の説明ではこれらの LED 素子を単に「LED」と称する。主制御基板 200、および、演出制御基板 300 のメイン CPU 201 とサブメイン CPU 301 を単に「CPU」と称する。20

#### 【0159】

上記説明から分かるように、本実施形態では、演出制御情報は、制御装置から 3 線シリアルインターフェイスを経由して LED 制御回路に送信される。30

#### 【0160】

##### <制御装置と LED 制御回路の接続インターフェイス>

第 1 実施形態と同様に、本実施形態においても、遊技機には、多数の表示用、演出用の LED が取り付けられている。遊技機において LED の数は数百個の LED が使用され、LED 制御回路の数は数十個から百個以上となる。従来は、制御装置と各 LED 制御回路との接続、あるいは、複数の LED 制御回路相互の接続は、I2C シリアルインターフェイス、または、3 線シリアルインターフェイス等の標準シリアルインターフェイスを用いて接続されていた。

#### 【0161】

第 1 実施形態と同様に、多数の LED 制御回路の全てを制御装置と直接 3 線シリアルインターフェイスを用いて接続すると、制御装置には膨大な数の 3 線シリアルインターフェイスの接続線が必要となる。従って、1 つあるいは数個の LED 制御回路を 1 段目の LED 制御回路として制御装置と直接接続し、残りの LED 制御回路を順次接続する。例えば、2 段目の LED 制御回路を 1 段目の LED 制御回路に、3 段目の LED 制御回路を 2 段目の LED 制御回路に接続するというように、順次接続する構成することが一般的である。このような接続構成とすることで、制御装置に設ける 3 線シリアルインターフェイスの接続線の数を抑制することが可能となる。40

#### 【0162】

制御装置と周辺回路との接続は標準シリアルインターフェイスである 3 線シリアルインターフェイスが用いられる。第 1 実施形態での説明から分かるように、制御装置と周辺回50

路との接続、すなわち、図19に図示した主制御基板200と各種の周辺回路との接続、演出制御基板300と各種の周辺回路との接続を行うLED制御回路を1段目のLED制御回路と、2段目以降のLED制御回路の2種類のLED制御回路としている。具体的には、1段目のLED制御回路と制御装置との接続に3線シリアルインターフェイスを用い、1段目のLED制御回路から2段目以降のLED制御回路の接続には、外部からの誘導ノイズの影響を受け難いLVDSインターフェイスを用いている。

#### 【0163】

このとき第1実施形態と同様に、1段目のLED制御回路および2段目以降のLED制御回路の全てに、図3に示した制御回路LCを用いている。前述のように、図3に図示したLED制御回路LCは、入力端子から3線シリアルインターフェイスの信号およびLVDSインターフェイスの信号のいずれの信号も受信可能で、受信した信号をLVDSインターフェイスの信号として出力端子から出力するので、このような使用が可能である。10

#### 【0164】

具体的には、図17に示すように、第1特別図柄表示装置171、第2特別図柄表示装置172、普通図柄表示装置175、第1特図保留ランプ173、第2特図保留ランプ174、普図保留ランプ176、演出ランプLP、および、演出ランプLPを構成する入賞報知ランプ181～183、入賞報知ランプ184を含む盤ランプ180、枠ランプ110が遊技機内に配置されているが、これらそれぞれ対応して複数のLED制御回路LCが設けられている。これら複数のLED制御回路が、図4～図6に示すような、マルチ接続、カスケード接続されている。20

#### 【0165】

これらLED制御回路による各ランプに用いられる多数のLED制御や、図7～図16を用いて説明した内容は、ぱちんこ機においても同一であるので、これらの説明は重複するため、省略する。

#### 【0166】

以上説明した第1および第2の実施形態についての効果を記載する。

##### <本実施形態の第1の効果>

本実施形態によれば、副制御手段(サブメインCPU)は第1の通信形態(3線シリアルインターフェイス)の信号によって複数の演出出力制御手段(LED制御回路)に演出制御情報を送信可能であり、演出出力制御手段(LED制御回路)は第1の通信形態の信号を受信する第1の入力手段と、第2の通信形態(LVDSインターフェイス)の信号を受信する第2の入力手段を切り替えるように構成されている。このため、同じ構成の演出出力制御手段(LED制御回路LC)を1段目の演出出力制御手段(LED制御回路LC1)として動作させることも、2段目以降の演出出力制御手段(LED制御回路LC2、LC3、等)として動作させて、遊技機内の多様な位置に配設することが可能となる。それぞれの配設位置に適した通信形態の信号で通信可能であるという効果が得られる。30

#### 【0167】

演出制御情報は複数のLEDに対して、LEDを複数の発光輝度値で制御する発光輝度値情報を含むのが好ましい。演出出力制御手段(LED制御回路LC)は複数段階の発光輝度値情報に基づいて多様な演出制御が可能となり、遊技機の興奮を高める制御を行うことが可能であるという効果が得られる。40

#### 【0168】

演出制御情報は演出出力制御手段(LED制御回路LC)を指定するアドレス情報と、複数個のLEDの発光輝度値情報を含むのが好ましい。副制御手段(サブメインCPU)と直接接続されていない演出出力制御手段(LED制御回路)に対しても、LEDを発光輝度制御するための演出制御情報を送信可能であるという効果が得られる。

#### 【0169】

第2の通信形態はLVDSインターフェイスであるのが好ましい。遊技機内に誘導ノイズの発生源が存在しても、副制御手段から遊技機内の様々な位置に配設されている演出出力制御手段(LED制御回路LC)に対して、誘導ノイズの影響を受けることなく演出制50

御情報を送信することが可能であるという効果が得られる。

#### 【0170】

##### <本実施形態の第2の効果>

本実施形態によれば、演出出力制御手段（LED制御回路LC）は、第1の通信形態（3線シリアルインターフェイス）の信号を受信して第2の通信形態（LVDSインターフェイス）の信号に変換して出力する第1の演出出力制御手段（LED制御回路LC1）、または、第2の通信形態の信号を受信して受信した入力波形を整形して第2の通信形態の信号で出力する第2の演出出力制御手段（LED制御回路LC2、LC3、等）として動作する。副制御手段（サブメインCPU）は第1の通信形態を用いて他装置と接続するよう設計されているが、従来の副制御手段を使用したままで、誘導ノイズに強い第2の通信形態の信号を用いる演出出力制御手段（LED制御回路）に対して波形整形した信号を用いて接続されることから、演出出力制御手段（LED制御回路）の接続段数が増加しても信号波形が弱まる、あるいは、信号波形が乱れることがないという効果が得られる。10

#### 【0171】

入力波形の整形は、入力端子のクロック信号に同期してデータ信号の演出制御情報を受信し、出力端子のクロック信号に同期してデータ信号の演出制御情報を送信するのが好ましい。1段目の演出出力制御手段（LED制御回路LC1）から最終段の演出出力制御手段（LED制御回路LC）までの接続段数が増加しても、下位の演出出力制御手段（LED制御回路LC）にきれいに波形整形された信号を送信することが可能であるという効果が得られる。20

#### 【0172】

##### <本実施形態の第3の効果>

本実施形態によれば、遊技機の副制御手段（サブメインCPU）から演出制御情報を受信する演出出力制御手段（LED制御回路LC）は、3線シリアルインターフェイスの信号の通信形態の信号を受信して、LVDSインターフェイスの通信形態の信号に変換して下位の演出出力制御手段（LED制御回路LC）に送信するブリッジ機能を有することが好ましい。3線シリアルインターフェイスの通信形態によって周辺回路と通信する従来の副制御手段をそのまま使用して、演出出力制御手段（LED制御回路）に接続することができるという効果が得られる。30

#### 【0173】