(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2014-512688

(P2014-512688A)

(43) 公表日 平成26年5月22日(2014.5.22)

(51) Int.Cl.

**H01L 25/065** (2006.01)

**H01L 25/07** (2006.01)

**H01L 25/18** (2006.01)

F 1

H O 1 L 25/08

テーマコード (参考)

E

審査請求 未請求 予備審査請求 未請求 (全 35 頁)

(21) 出願番号 特願2014-506450 (P2014-506450)

(86) (22) 出願日 平成24年4月11日 (2012.4.11)

(85) 翻訳文提出日 平成25年12月18日 (2013.12.18)

(86) 國際出願番号 PCT/US2012/032997

(87) 國際公開番号 WO2012/145201

(87) 國際公開日 平成24年10月26日 (2012.10.26)

(31) 優先権主張番号 13/306,099

(32) 優先日 平成23年11月29日 (2011.11.29)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 61/477,967

(32) 優先日 平成23年4月21日 (2011.4.21)

(33) 優先権主張国 米国(US)

(71) 出願人 504142411

テッセラ、インコーポレイテッド

アメリカ合衆国 カリフォルニア州 95

134, サン・ノゼ, オーチャード・

パークウェイ 3025

(74) 代理人 100099623

弁理士 奥山 尚一

(74) 代理人 100096769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

(74) 代理人 100114591

弁理士 河村 英文

(74) 代理人 100125380

弁理士 中村 純子

最終頁に続く

(54) 【発明の名称】フリップチップ、フェイスアップおよびフェイスタウンセンター・ボンドメモリ・ワイヤ・ボンドアセンブリ

## (57) 【要約】

超小型電子アセンブリ10は、第1および第2の表面34, 58と、それらの間に延在する開口39と、端子36とを有する基板30を備えている。アセンブリ10は、第1の表面34と向き合う前面16を有する第1の超小型電子素子12と、第1の超小型電子素子の縁29を超えて突出する前面22を有する第2の超小型電子素子14と、超小型電子素子の接点20, 52を端子に電気的に接続する第1および第2のリード70, 76と、第1および第2の超小型電子素子の接点を電気的に相互接続する第3のリード73と、をさらに備えている。第1の超小型電子12の接点20は、縁29に隣接して配置されている。第2の超小型電子素子14の接点26は、その前面の中央領域19に配置されている。リード70, 76, 99は、開口39と真っ直ぐ並んだ部分を有している。

**【特許請求の範囲】****【請求項 1】**

超小型電子アセンブリにおいて、

互いに反対側を向く第1および第2の表面および前記第1および第2の表面間に延在する開口を有する基板であって、前記基板の前記第2の表面に露出した第1の端子を有している、基板と、

前記基板の前記第1の表面と向き合う前面、そこから遠く離れた裏面、および前記前面と前記裏面との間に延在する縁を有する第1の超小型電子素子であって、前記第1の超小型電子素子の前記縁に隣接してその前記前面に露出した複数の接点を有している、第1の超小型電子素子と、

互いに向き合った第1および第2の縁、前記第1および第2の縁間に延在する前面、および前記第1および第2の縁から遠く離れたその前記前面の中央領域に配置された複数の接点を有する第2の超小型電子素子であって、前記第2の超小型電子素子の前記前面は、前記第1の超小型電子素子と向き合っており、前記第1の超小型電子素子の前記縁を超えて突出している、第2の超小型電子素子と、

前記第1の超小型電子素子の前記接点を前記第1の端子に電気的に接続する第1のリードと、

前記第2の超小型電子素子の前記接点を前記第1の端子に接続する第2のリードであって、前記第1および第2のリードは、前記開口と真っ直ぐに並んだ部分を有している、第2のリードと、

前記基板の前記第2の表面と反対側の前記超小型電子アセンブリの表面に露出した第2の端子であって、前記第2の端子の少なくともいくつかは、前記超小型電子素子の少なくとも1つの上に重なっている、第2の端子と、

を備えている、ことを特徴とする超小型電子アセンブリ。

**【請求項 2】**

前記第2の端子の少なくともいくつかは、ワイヤボンドによって、前記基板の前記第1の表面に露出した導電要素に電気的に接続されている、ことを特徴とする請求項1に記載の超小型電子アセンブリ。

**【請求項 3】**

前記第1および第2の超小型電子素子および前記ワイヤボンドの少なくとも一部を少なくとも部分的に覆う封止材をさらに備えており、前記第2の端子が露出している前記超小型電子アセンブリの前記表面は、前記封止材の表面である、ことを特徴とする請求項2に記載の超小型電子アセンブリ。

**【請求項 4】**

前記ワイヤボンドは、前記導電要素に取り付けられた基部および前記導電要素から遠く離れた未封止端面を有しており、縁面が、前記基部と前記未封止端面との間に延在しており、前記未封止端面は、前記封止材によって被覆されておらず、前記第2の端子は、前記未封止端面に電気的に接続されている、ことを特徴とする請求項3に記載の超小型電子アセンブリ。

**【請求項 5】**

前記ワイヤボンドの少なくとも1つの縁面の少なくとも一部は、封止されておらず、前記第2の端子の少なくとも1つは、前記ワイヤボンドの前記少なくとも1つの前記封止されていない縁面および前記未封止端面に電気的に接続されている、ことを特徴とする請求項4に記載の超小型電子アセンブリ。

**【請求項 6】**

前記ワイヤボンドは、前記導電要素に取り付けられた前記ワイヤボンドの基部と前記導電要素から遠く離れた前記ワイヤボンドの端との間に未封止縁面を有しており、前記第2の端子は、前記未封止縁面に電気的に接続されている、ことを特徴とする請求項3に記載の超小型電子アセンブリ。

**【請求項 7】**

10

20

30

40

50

前記超小型電子素子の少なくとも1つは、揮発性ランダム・アクセス・メモリ(ＲＡＭ)を含んでおり、前記超小型電子素子の少なくとも1つは、不揮発性フラッシュメモリを含んでいる、ことを特徴とする請求項1に記載の超小型電子アセンブリ。

【請求項8】

前記第1の超小型電子素子の前記接点を前記第2の超小型電子素子の前記接点に電気的に相互接続する第3のリードをさらに備えており、前記第1，第2，および第3のリードは、前記開口と真っ直ぐに並んだ部分を有している、ことを特徴とする請求項1に記載の超小型電子アセンブリ。

【請求項9】

前記第1または第2のリードの少なくとも1つは、前記第1または第2の超小型電子素子の少なくとも1つの前記接点から延在するワイヤボンドを含んでいる、ことを特徴とする請求項1に記載の超小型電子アセンブリ。 10

【請求項10】

前記開口と真っ直ぐに並んだ前記第1のリードおよび前記第2のリードの少なくとも1つの前記部分は、前記基板に沿って前記端子に延在する第2の部分を有する一体化導電要素の一部である、ことを特徴とする請求項1に記載の超小型電子アセンブリ。

【請求項11】

前記第2の超小型電子素子の前記前面と前記基板の前記第1の表面との間にスペーサ要素をさらに備えている、ことを特徴とする請求項1に記載の超小型電子アセンブリ。

【請求項12】

前記第1の超小型電子素子は、論理機能を主に果たすように構成されたチップを含んでいる、ことを特徴とする請求項1に記載の超小型電子アセンブリ。 20

【請求項13】

前記第2の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している、ことを特徴とする請求項1に記載の超小型電子アセンブリ。

【請求項14】

前記第1の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している、ことを特徴とする請求項1に記載の超小型電子アセンブリ。 30

【請求項15】

前記第1の超小型電子素子の前記接点を前記端子に電気的に接続する第3のリードをさらに備えており、前記第1のリードおよび前記第3のリードは、前記開口の両側の前記端子に接続されており、前記第1，第2，および第3のリードは、前記開口と真っ直ぐに並んだ部分を有している、ことを特徴とする請求項1に記載の超小型電子アセンブリ。

【請求項16】

前記基板の前記第1の表面と前記第2の超小型電子素子の前記前面との間に配置された第3の超小型電子素子であって、前記第3の超小型電子素子は、互いに向き合った第1および第2の縁と、前記第1および第2の縁間に延在する前面と、前記第3の超小型電子素子の前記第1の縁に隣接してその前記前面上に配置された複数の接点と、を有しており、前記第3の超小型電子素子の前記前面は、前記基板の前記第1の表面と向き合っている、第3の超小型電子素子と、 40

前記第3の超小型電子素子の前記接点を前記端子に電気的に接続する第3のリードと、

前記第1および第3の超小型電子素子の前記接点を電気的に相互接続する第4のリードであって、前記第1および第3の超小型電子素子の前記接点は、前記開口の両側に位置しており、前記第1，第2，第3，および第4のリードは、前記開口と真っ直ぐに並んだ部分を有している、第4のリードと、

をさらに備えている、ことを特徴とする請求項1に記載の超小型電子アセンブリ。

【請求項17】

前記第1および第2の超小型電子素子の前記接点を電気的に相互接続する第5のリード

10

20

30

40

50

をさらに備えている、ことを特徴とする請求項 1 6 に記載の超小型電子アセンブリ。

【請求項 1 8】

前記第 2 および第 3 の超小型電子素子の前記接点を電気的に相互接続する第 6 のリードをさらに備えている、ことを特徴とする請求項 1 7 に記載の超小型電子アセンブリ。

【請求項 1 9】

各々が請求項 1 に記載されているような第 1 および第 2 の超小型アセンブリを備える超小型電子コンポーネントにおいて、前記第 1 の超小型電子アセンブリは、前記第 2 の超小型電子アセンブリの上に少なくとも部分的に重なっており、前記第 1 の超小型電子アセンブリの前記第 1 の端子は、前記第 2 の超小型電子アセンブリの前記第 2 の端子に接合されている、ことを特徴とする超小型電子コンポーネント。

10

【請求項 2 0】

前記第 1 の超小型電子素子の少なくとも 1 つは、論理機能を果たすように主に構成されており、前記第 2 の超小型電子素子の少なくとも 1 つは、任意の他の機能よりもメモリ記憶アレイ機能をもたらすように構成された極めて多数の能動素子を有している、ことを特徴とする請求項 1 9 に記載の超小型電子コンポーネント。

【請求項 2 1】

前記第 1 の超小型電子アセンブリの前記第 1 の端子の少なくともいくつかおよび前記第 2 の超小型電子アセンブリの前記第 2 の端子の少なくともいくつは、エリアアレイで配置されており、前記第 1 および第 2 の超小型電子アセンブリは、接合金属の導電塊である接合ユニットによって、互いに接合されている、ことを特徴とする請求項 1 9 に記載の超小型電子コンポーネント。

20

【請求項 2 2】

前記超小型電子アセンブリは、前記超小型電子コンポーネントの周辺に隣接して配置された接合ユニットを介して互いに電気的に接続されている、ことを特徴とする請求項 1 9 に記載の超小型電子コンポーネント。

【請求項 2 3】

前記接合ユニットは、前記超小型電子コンポーネントの過疎中央領域の外側に配置されている、ことを特徴とする請求項 2 2 に記載の超小型電子コンポーネント。

【請求項 2 4】

請求項 1 に記載の超小型電子アセンブリと、前記超小型電子アセンブリに電気的に接続された 1 つまたは複数の他の電子コンポーネントと、を備えるシステム。

30

【請求項 2 5】

前記端子の少なくともいくつかが、回路パネルに電気的に接続されている、ことを特徴とする請求項 2 4 に記載のシステム。

【請求項 2 6】

ハウジングをさらに備えており、前記超小型電子アセンブリおよび前記他の電子コンポーネントは、前記ハウジングに実装されている、ことを特徴とする請求項 2 5 に記載のシステム。

【請求項 2 7】

超小型電子アセンブリにおいて、

40

互いに反対側を向く第 1 および第 2 の表面および前記第 1 および第 2 の表面間に延在する開口を有する基板であって、端子を有している、基板と、

前記基板の前記第 1 の表面と向き合う前面、そこから遠く離れた裏面、および前記前面と前記裏面との間に延在する縁を有する第 1 の超小型電子素子であって、前記第 1 の超小型電子素子の前記縁に隣接してその前記前面に露出した複数の接点を有している、第 1 の超小型電子素子と、

互いに向き合った第 1 および第 2 の縁、前記第 1 および第 2 の縁間に延在する前面、および前記第 1 および第 2 の縁から遠く離れたその前記前面の中央領域に配置された複数の接点を有する第 2 の超小型電子素子であって、前記第 2 の超小型電子素子の前記前面は、前記第 1 の超小型電子素子と向き合っており、前記第 1 の超小型電子素子の前記縁を超えて

50

て突出している、第2の超小型電子素子と、

前記第1の超小型電子素子の前記接点を前記端子に電気的に接続する第1のリードと、

前記第2の超小型電子素子の前記接点を前記端子に電気的に接続する第2のリードと、

前記第1の超小型電子素子の前記接点を前記第2の超小型電子素子の前記接点に電気的に相互接続する第3のリードであって、前記第1、第2、および第3のリードは、前記開口と真っ直ぐに並ぶ部分を有している、第3のリードと、

を備えている、ことを特徴とする超小型電子アセンブリ。

#### 【請求項28】

前記第1または第2のリードの少なくとも1つは、前記第1または第2の超小型電子素子の少なくとも1つの接点から延在するワイヤボンドを含んでいる、ことを特徴とする請求項27に記載の超小型電子アセンブリ。 10

#### 【請求項29】

前記開口と真っ直ぐに並んだ前記第1のリードおよび前記第2のリードの少なくとも1つの前記部分は、前記基板に沿って前記端子に延在する第2の部分を有する一体化導電要素の一部である、ことを特徴とする請求項27に記載の超小型電子アセンブリ。

#### 【請求項30】

前記第2の超小型電子素子の前記前面と前記基板の前記第1の表面との間にスペーサ要素をさらに備えている、ことを特徴とする請求項27に記載の超小型電子アセンブリ。 20

#### 【請求項31】

前記第1の超小型電子素子は、論理機能を主に果たすように構成されたチップを含んでいる、ことを特徴とする請求項27に記載の超小型電子アセンブリ。 20

#### 【請求項32】

前記第2の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している、ことを特徴とする請求項27に記載の超小型電子アセンブリ。 20

#### 【請求項33】

前記第1の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している、ことを特徴とする請求項27に記載の超小型電子アセンブリ。 20

#### 【請求項34】

請求項27に記載の超小型電子アセンブリと、前記超小型電子アセンブリに電気的に接続された1つまたは複数の他の電子コンポーネントと、を備えるシステム。 30

#### 【請求項35】

前記端子が回路パネルに電気的に接続されている、ことを特徴とする請求項34に記載のシステム。

#### 【請求項36】

ハウジングをさらに備えており、前記超小型電子アセンブリおよび前記他の電子コンポーネントは、前記ハウジングに実装されている、ことを特徴とする請求項35に記載のシステム。

#### 【請求項37】

各々が請求項27に記載されているような第1および第2の超小型電子アセンブリを備える超小型電子コンポーネントにおいて、前記第1の超小型電子アセンブリは、前記第2の超小型電子アセンブリに電気的に接続されており、前記第2の超小型電子アセンブリの上に少なくとも部分的に重なっている、ことを特徴とする超小型電子コンポーネント。 40

#### 【請求項38】

前記超小型電子アセンブリは、前記超小型電子コンポーネントの周辺に隣接して配置された接合ユニットを介して互いに電気的に接続されている、ことを特徴とする請求項37に記載の超小型電子コンポーネント。

#### 【請求項39】

前記接合ユニットは、前記超小型電子コンポーネントの過疎中央領域の外側に配置され 50

ている、ことを特徴とする請求項 3 8 に記載の超小型電子コンポーネント。

【請求項 4 0】

前記超小型電子素子のいくつかは、揮発性ランダム・アクセス・メモリ( R A M )を含んでおり、前記超小型電子素子のいくつかは、不揮発性フラッシュメモリを含んでいる、ことを特徴とする請求項 3 7 に記載の超小型電子コンポーネント。

【請求項 4 1】

前記第 1 の超小型電子素子の少なくとも 1 つは、論理機能を果たすように主に構成されており、前記第 2 の超小型電子素子の少なくとも 1 つは、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している、ことを特徴とする請求項 3 7 に記載の超小型電子コンポーネント。

10

【請求項 4 2】

互いに反対側を向く第 1 および第 2 の表面および前記第 1 および第 2 の表面間に延在する開口を有する基板であって、端子を有している、基板と、

前記基板の前記第 1 の表面と向き合う前面、そこから遠く離れた裏面、および前記前面と前記裏面との間に延在する縁を有する第 1 の超小型電子素子であって、前記第 1 の超小型電子素子の前記縁に隣接してその前記前面に露出した複数の接点を有している、第 1 の超小型電子素子と、

互いに向き合った第 1 および第 2 の縁、前記第 1 および第 2 の縁間に延在する前面、および前記第 1 および第 2 の縁から遠く離れたその前記前面の中央領域に配置された複数の接点を有する第 2 の超小型電子素子であって、前記第 2 の超小型電子素子の前記前面は、前記第 1 の超小型電子素子と向き合っており、前記第 1 の超小型電子素子の前記縁を超えて突出している、第 2 の超小型電子素子と、

20

前記第 1 の超小型電子素子の前記接点を前記端子に電気的に接続する第 1 のリードと、前記第 2 の超小型電子素子の前記接点を前記端子に電気的に接続する第 2 のリードと、前記第 1 の超小型電子素子の前記接点を前記端子に電気的に接続する第 3 のリードであって、前記第 1 のリードおよび前記第 3 のリードは、前記開口の両側の端子に接続されており、前記第 1 , 第 2 , および第 3 のリードは、前記開口と真っ直ぐに並んだ部分を有している、第 3 のリードと、

を備えている、ことを特徴とする超小型電子アセンブリ。

30

【請求項 4 3】

前記第 1 の超小型電子素子は、論理機能を主に果たすように構成されたチップを含んでいる、ことを特徴とする請求項 4 2 に記載の超小型電子アセンブリ。

【請求項 4 4】

前記第 2 の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している、ことを特徴とする請求項 4 2 に記載の超小型電子アセンブリ。

40

【請求項 4 5】

前記第 1 の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している、ことを特徴とする請求項 4 2 に記載の超小型電子アセンブリ。

【請求項 4 6】

互いに反対側を向く第 1 および第 2 の表面および前記第 1 および第 2 の表面間に延在する開口を有する基板であって、端子を有している、基板と、

前記基板の前記第 1 の表面と向き合う前面、そこから遠く離れた裏面、および前記前面と前記裏面との間に延在する縁を有する第 1 の超小型電子素子であって、前記第 1 の超小型電子素子の前記縁に隣接してその前記前面に露出した複数の接点を有している、第 1 の超小型電子素子と、

互いに向き合った第 1 および第 2 の縁、前記第 1 および第 2 の縁間に延在する前面、および前記第 1 および第 2 の縁から遠く離れたその前記前面の中央領域に配置された複数の接点を有する第 2 の超小型電子素子であって、前記第 2 の超小型電子素子の前記前面は、

50

前記第1の超小型電子素子と向き合っており、前記第1の超小型電子素子の前記縁を超えて突出している、第2の超小型電子素子と、

前記基板の前記第1の表面と前記第2の超小型電子素子の前記前面との間に配置された第3の超小型電子素子であって、前記第3の超小型電子素子は、互いに向き合った第1および第2の縁、前記第1および第2の縁間に延在する前面、および前記第3の超小型電子素子の前記第1の縁に隣接してその前記前面に配置された複数の接点を有しており、前記第3の超小型電子素子の前記前面は、前記基板の前記第1の表面と向き合っている、第3の超小型電子素子と、

前記第1の超小型電子素子の前記接点を前記端子に電気的に接続する第1のリードと、前記第2の超小型電子素子の前記接点を前記端子に電気的に接続する第2のリードと、前記第3の超小型電子素子の前記接点を前記端子に電気的に接続する第3のリードと、前記第1および第3の超小型電子素子の前記接点を電気的に相互接続する第4のリードであって、前記第1および第3の超小型電子素子の前記接点は、前記開口の両側に位置しており、前記第1、第2、第3、および第4のリードは、前記開口と真っ直ぐに並んだ部分を有している、第4のリードと、

を備えている、ことを特徴とする超小型電子アセンブリ。

#### 【請求項 4 7】

前記第1および第2の超小型電子素子の前記接点を電気的に相互接続する第5のリードをさらに備えている、ことを特徴とする請求項4 6に記載の超小型電子アセンブリ。

#### 【請求項 4 8】

前記第2および第3の超小型電子素子の前記接点を電気的に相互接続する第6のリードをさらに備えている、ことを特徴とする請求項4 7に記載の超小型電子アセンブリ。

#### 【請求項 4 9】

前記第1の超小型電子素子は、論理機能を主に果たすように構成されたチップを含んでいる、ことを特徴とする請求項4 6に記載の超小型電子アセンブリ。

#### 【請求項 5 0】

前記第2の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している、ことを特徴とする請求項4 6に記載の超小型電子アセンブリ。

#### 【請求項 5 1】

前記第1の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している、ことを特徴とする請求項4 6に記載の超小型電子アセンブリ。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

##### [関連出願の相互参照]

本願は、2011年4月21日に出願された米国仮特許出願第61/477,967号および2011年11月29日に出願された米国特許出願第13/306,099号の出願日の利得を主張するものであり、これらの開示内容は、参照することによって、ここに含まれるものとする。以下の本願の譲渡人に譲渡された出願：いずれも2011年4月21日に出願された米国仮特許出願第61/477,820号、第61/477,877号、および第61/477,883号も、参照することによって、ここに含まれるものとする。

##### 【0 0 0 2】

##### [発明の分野]

本発明は、積層超小型電子アセンブリ、このようなアセンブリを製造する方法、およびこのようなアセンブリに有用な構成要素に関する。

##### 【背景技術】

10

20

30

40

50

## 【0003】

半導体チップは、一般的に、個々の予めパッケージ化されたユニットとして供給されている。標準的なチップは、チップの内部回路に接続された接点を有する大きな前面を備える平坦な矩形体を有している。各チップは、典型的には、パッケージ内に実装され、該パッケージが、印刷回路基板のような回路パネルに実装され、チップの接点が回路パネルの導体に接続されることになる。多くの従来設計では、チップパッケージは、チップ自体の面積よりも著しく大きい回路パネルの面積を占めている。本開示において前面を有する平坦なチップに関して用いられる「チップの面積」という用語は、前面の面積を指すと理解されたい。「フリップチップ」設計では、チップの前面は、パッケージ基板、すなわち、チップキャリアの面と向き合っており、チップの接点は、半田ボールまたは他の接続要素によって、チップキャリアの接点に直接接合されるようになっている。次いで、このチップキャリアは、チップの前面の上に位置する端子を介して回路パネルに接合されることになる。「フリップチップ」設計は、比較的コンパクトな配置をもたらし、各チップは、例えば、本願の譲渡人に譲渡された特許文献1，2，3のいくつかの実施形態に開示されているように、チップの前面の面積と等しいかまたはいくらか大きい回路パネルの面積を占めることになる。なお、これらの文献の開示内容は、参照することによって、それらの全体がここに含まれるものとする。

10

## 【0004】

いくつかの革新的な実装技術が、従来のフリップチップボンディングのコンパクト性に近いかまたは等しいコンパクト性をもたらしている。単一チップをチップ自体の面積と等しいかまたはいくらか大きい回路パネルの面積内に収容するパッケージは、一般的に、「チップサイズパッケージ」と呼ばれている。

20

## 【0005】

超小型電子アセンブリによって占有される回路パネルの平面面積を最小化することに加えて、回路パネルの全高さ、すなわち、回路パネルの面と直交する全寸法を短縮するチップパッケージを製造することも望まれている。このような薄い超小型電子パッケージによって、パッケージが実装された回路パネルを隣接する構造体に近接して配置し、これによって、該回路パネルを含む製品の全体の寸法を短縮することができる。単一パッケージまたは単一モジュール内に複数のチップを実装する種々の提案がなされてきている。従来の「マルチチップモジュール」では、チップは、単一パッケージ基板上に並んで実装され、次いで、該パッケージ基板が回路パネルに実装されるようになっている。しかし、この手法では、チップによって占有される回路パネルの総面積の縮小に限りがある。総面積は、依然として、モジュール内の個々のチップの全表面積よりも大きくなっている。

30

## 【0006】

複数のチップを「積層」配置に、すなわち、複数のチップを上下に重ねる配置にパッケージ化することも提案されてきている。積層配置では、いくつかのチップをこれらのチップの全面積よりも小さい回路パネルの面積内に実装することができる。いくつかの積層チップ配置が、例えば、特許文献1，3，4のいくつかの実施形態に開示されている。これらの開示内容は、参照することによって、それらの全体がここに含まれるものとする。特許文献5は、チップを上下に積層し、チップに付随して設けられた、所謂、「配線フィルム」の導体によって、チップを相互接続するようになっている装置を開示している。この開示内容も、参照することによって、ここに含まれるものとする。

40

## 【先行技術文献】

## 【特許文献】

## 【0007】

【特許文献1】米国特許第5,148,265号明細書

【特許文献2】米国特許第5,148,266号明細書

【特許文献3】米国特許第5,679,977号明細書

【特許文献4】米国特許第5,347,159号明細書

【特許文献5】米国特許第4,941,033号明細書

50

**【発明の概要】****【発明が解決しようとする課題】****【0008】**

当技術分野におけるこれらの努力にも関わらず、チップの中央領域に実質的に配置された接点を有するチップに対するマルチチップパッケージにおけるさらなる改良が望まれている。いくつかの半導体チップ、例えば、いくつかのメモリチップは、一般的に、チップの中心軸に実質的に沿って配置された1列または2列の接点を有するものとして作製されている。

**【課題を解決するための手段】****【0009】**

10

本開示は、超小型電子アセンブリおよび該超小型電子アセンブリを製造する方法に関する。本発明の一態様によれば、超小型電子アセンブリは、互いに反対側を向く第1および第2の表面および第1および第2の表面間に延在する開口を有する基板と、基板の第1の表面と向き合う前面を有する第1の超小型電子素子と、第1の超小型電子素子と向き合う前面を有する第2の超小型電子素子と、を備えている。基板は、その第2の表面に露出した第1の端子を有しているとよい。第1の超小型電子素子は、前面から遠く離れた裏面、および前面と裏面との間に延在する縁も有しているとよい。第1の超小型電子素子は、第1の超小型電子素子の縁に隣接してその前面に露出した複数の接点を有しているとよい。第2の超小型電子素子は、互いに向き合った第1および第2の縁を有しているとよい。第2の超小型電子素子の前面は、第1および第2の縁間に延在しているとよい。

20

**【0010】**

第2の超小型電子素子は、第1および第2の縁から遠く離れたその前面の中央領域に配置された複数の接点を有しているとよい。第2の超小型電子素子の前面は、第1の超小型電子素子の縁を超えて突出しているとよい。超小型電子アセンブリは、第1の超小型電子素子の接点を第1の端子に電気的に接続する第1のリード、および第2の超小型電子素子の接点を第1の端子に接続する第2のリードも備えているとよい。第1および第2のリードは、開口と真っ直ぐに並んだ部分を有しているとよい。超小型電子アセンブリは、基板の第2の表面と反対側の超小型電子アセンブリの表面に露出した第2の端子も備えているとよい。第2の端子の少なくともいくつかは、超小型電子素子の少なくとも1つの上に重なっているとよい。

30

**【0011】**

一実施形態では、第2の端子の少なくともいくつかは、ワイヤボンドによって、基板の第1の表面に露出した導電要素に電気的に接続されている。特定の例では、超小型電子アセンブリは、第1および第2の超小型電子素子およびワイヤボンドの少なくとも一部を少なくとも部分的に覆う封止材もさらに備えている。第2の端子が露出している超小型電子アセンブリの表面は、封止材の表面であるとよい。一例では、ワイヤボンドは、導電要素に取り付けられた基部および導電要素から遠く離れた未封止端面を有しており、縁面が、基部と未封止端面との間に延在している。未封止端面は、封止材によって被覆されていないとよい。第2の端子は、未封止端面に電気的に接続されているとよい。例示的な実施形態では、ワイヤボンドの少なくとも1つの縁面の少なくとも一部は、封止されておらず、

40

第2の端子の少なくとも1つは、ワイヤボンドの少なくとも1つの封止されていない縁面および未封止端面に電気的に接続されている。

**【0012】**

特定の実施形態では、ワイヤボンドは、導電要素に取り付けられたワイヤボンドの基部と導電要素から遠く離れたワイヤボンドの端との間に未封止縁面を有している。第2の端子は、未封止縁面に電気的に接続されるようになっていてもよい。一実施形態では、超小型電子素子の少なくとも1つは、揮発性ランダム・アクセス・メモリ(RAM)を含んでおり、超小型電子素子の少なくとも1つは、不揮発性フラッシュメモリを含んでいる。例示的な実施形態では、超小型電子アセンブリは、第1の超小型電子素子の接点を第2の超小型電子素子の接点に電気的に相互接続する第3のリードをさらに備えている。第1、第

50

2，および第3のリードは、開口と真っ直ぐに並んだ部分を有しているとよい。一例では、第1または第2のリードの少なくとも1つは、第1または第2の超小型電子素子の少なくとも1つの接点から延在するワイヤボンドを含んでいる。

#### 【0013】

特定の例では、開口と真っ直ぐに並んだ第1のリードおよび第2のリードの少なくとも1つの部分は、基板に沿って端子に延在する第2の部分を有する一体化導電要素の一部である。例示的な実施形態では、超小型電子アセンブリは、第2の超小型電子素子の前面と基板の第1の表面との間にスペーサ要素も備えている。一例では、第1の超小型電子素子は、論理機能を主に果たすように構成されたチップを含んでいる。特定の実施形態では、第2の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している。一実施形態では、第1の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している。例示的な実施形態では、超小型電子アセンブリは、第1の超小型電子素子の接点を端子に電気的に接続する第3のリードも備えている。第1のリードおよび第3のリードは、開口の両側の端子に接続されているとよい。第1，第2，および第3のリードは、開口と真っ直ぐに並んだ部分を有しているとよい。

#### 【0014】

一例では、超小型電子アセンブリは、基板の第1の表面と第2の超小型電子素子の前面との間に配置された第3の超小型電子素子と、第3の超小型電子素子の接点を端子に電気的に接続する第3のリードと、第1および第3の超小型電子素子の接点を電気的に相互接続する第4のリードと、をさらに備えている。第3の超小型電子素子は、互いに向き合った第1および第2の縁と、第1および第2の縁間に延在する前面と、第3の超小型電子素子の第1の縁に隣接してその前面上に配置された複数の接点と、を有しているとよい。第3の超小型電子素子の前面は、基板の前記第1の表面と向き合っているとよい。第1および第3の超小型電子素子の接点は、開口の両側に位置しているとよい。第1，第2，第3，および第4のリードは、開口と真っ直ぐに並んだ部分を有しているとよい。例示的な実施形態では、超小型電子アセンブリは、第1および第2の超小型電子素子の接点を電気的に相互接続する第5のリードをさらに備えている。特定の実施形態では、超小型電子アセンブリは、第2および第3の超小型電子素子の接点を電気的に相互接続する第6のリードをさらに備えている。

#### 【0015】

一実施形態では、超小型電子コンポーネントは、前述の第1および第2の超小型電子アセンブリを備えている。第1の超小型電子アセンブリは、第2の超小型電子アセンブリの上に少なくとも部分的に重なっているとよい。第1の超小型電子アセンブリの第1の端子は、第2の超小型電子アセンブリの第2の端子に接合されているとよい。例示的な実施形態では、第1の超小型電子素子の少なくとも1つは、論理機能を果たすように主に構成されている。第2の超小型電子素子の少なくとも1つは、任意の他の機能よりもメモリ記憶アレイ機能をもたらすように構成された極めて多数の能動素子を有しているとよい。特定の実施形態では、第1の超小型電子アセンブリの第1の端子の少なくともいくつかおよび第2の超小型電子アセンブリの第2の端子の少なくともいくつかは、エリアアレイで配置されている。第1および第2の超小型電子アセンブリは、接合金属の導電塊である接合ユニットによって、互いに接合されているとよい。

#### 【0016】

例示的な実施形態では、超小型電子アセンブリは、超小型電子コンポーネントの周辺に隣接して配置された接合ユニットを介して互いに電気的に接続されている。一例では、接合ユニットは、超小型電子コンポーネントの過疎中央領域の外側に配置されている。特定の例では、システムは、前述の超小型電子アセンブリと、該超小型電子アセンブリに電気的に接続された1つまたは複数の他の電子コンポーネントと、を備えている。特定の実施形態では、端子の少なくともいくつかが、回路パネルに電気的に接続されている。一例では、システムは、ハウジングも備えており、超小型電子アセンブリおよび他の電子コン

ポーネントは、ハウジングに実装されている。

【0017】

本発明の他の態様によれば、超小型電子アセンブリは、互いに反対側を向く第1および第2の表面および第1および第2の表面間に延在する開口を有する基板と、基板の第1の表面と向き合う前面を有する第1の超小型電子素子と、第1の超小型電子素子と向き合う前面を有する第2の超小型電子素子と、を備えている。基板は、端子を有しているとよい。第1の超小型電子素子は、前面から遠く離れた裏面、および前面と裏面との間に延在する縁を有しているとよい。第1の超小型電子素子は、第1の超小型電子素子の縁に隣接してその前面に露出した複数の接点を有しているとよい。第2の超小型電子素子は、互いに向き合った第1および第2の縁を有しているとよい。第2の超小型電子素子の前面は、第1および第2の縁間に延在しているとよい。

10

【0018】

第2の超小型電子素子は、第1および第2の縁から遠く離れたその前面の中央領域に配置された複数の接点を有しているとよい。第2の超小型電子素子の前面は、第1の超小型電子素子の縁を超えて突出しているとよい。超小型電子アセンブリは、第1の超小型電子素子の接点を端子に電気的に接続する第1のリードと、第2の超小型電子素子の接点を端子に接続する第2のリードと、第1の超小型電子素子の接点を第2の超小型電子素子の接点に電気的に相互接続する第3のリードと、をさらに備えているとよい。第1、第2、および第3のリードは、開口と真っ直ぐに並ぶ部分を有しているとよい。

20

【0019】

例示的な実施形態では、第1または第2のリードの少なくとも1つは、第1または第2の超小型電子素子の少なくとも1つの接点から延在するワイヤボンドを含んでいる。一実施形態では、開口と真っ直ぐに並んだ第1のリードおよび第2のリードの少なくとも1つの部分は、基板に沿って端子に延在する第2の部分を有する一体化導電要素の一部である。特定の実施形態では、超小型電子アセンブリは、第2の超小型電子素子の前面と基板の第1の表面との間にスペーサ要素も備えている。特定の実施形態では、第1の超小型電子素子は、論理機能を主に果たすように構成されたチップを含んでいる。例示的な実施形態では、第2の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している。一実施形態では、第1の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している。

30

【0020】

本発明のさらに他の態様は、本発明の前述の態様による超小型電子アセンブリを該超小型電子アセンブリに電気的に接続された他の電子コンポーネントと連結させて組み入れるシステムを提供している。例えば、端子が回路パネルに電気的に接続されているとよい。他の例では、システムは、携帯ハウジングとすることができる単一ハウジングに配置され、および／または実装されるようになっているとよい。本発明のこの態様における好ましい実施形態によるシステムは、同等の従来システムよりも小形化することができる。

【0021】

一実施形態では、超小型電子コンポーネントは、前述の第1および第2の超小型電子アセンブリを備えている。第1の超小型電子アセンブリは、第2の超小型電子アセンブリに電気的に接続されており、第2の超小型電子アセンブリの上に少なくとも部分的に重なっているとよい。例示的な実施形態では、超小型電子アセンブリは、超小型電子コンポーネントの周辺に隣接して配置された接合ユニットを介して互いに電気的に接続されている。特定の実施形態では、接合ユニットは、超小型電子コンポーネントの過疎中央領域の外側に配置されている。一実施形態では、超小型電子素子のいくつかは、揮発性ランダム・アクセス・メモリ（RAM）を含んでおり、超小型電子素子のいくつかは、不揮発性フラッシュメモリを含んでいる。特定の実施形態では、第1の超小型電子素子の少なくとも1つは、論理機能を果たすように主に構成されており、第2の超小型電子素子の少なくとも1つは、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多

40

50

数の能動素子を有している。

【0022】

本発明のさらに他の態様によれば、超小型電子アセンブリは、互いに反対側を向く第1および第2の表面および第1および第2の表面間に延在する開口を有する基板と、基板の第1の表面と向き合う前面を有する第1の超小型電子素子と、第1の超小型電子素子と向き合う前面を有する第2の超小型電子素子と、を備えている。基板は、端子を有しているとよい。第1の超小型電子素子は、前面から遠く離れた裏面、および前面と裏面との間に延在する縁も備えているとよい。第1の超小型電子素子は、第1の超小型電子素子の縁に隣接してその前面に露出した複数の接点を有しているとよい。第2の超小型電子素子は、互いに向き合った第1および第2の縁を有しているとよい。第2の超小型電子素子の前面は、第1および第2の縁間に延在しているとよい。

10

【0023】

第2の超小型電子素子は、第1および第2の縁から遠く離れたその前面の中央領域に配置された複数の接点を有しているとよい。第2の超小型電子素子の前面は、第1の超小型電子素子の縁を超えて突出しているとよい。超小型電子アセンブリは、第1の超小型電子素子の接点を端子に電気的に接続する第1のリードと、第2の超小型電子素子の接点を端子に接続する第2のリードと、第1の超小型電子素子の接点を端子に電気的に接続する第3のリードと、をさらに備えているとよい。第1のリードおよび第3のリードは、開口の両側の端子に接続されているとよい。第1、第2、および第3のリードは、開口と真っ直ぐに並んだ部分を有しているとよい。

20

【0024】

特定の実施形態では、第1の超小型電子素子は、論理機能を主に果たすように構成されたチップを含んでいる。例示的な実施形態では、第2の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している。一実施形態では、第1の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している。

30

【0025】

本発明のさらに他の態様によれば、超小型電子アセンブリは、互いに反対側を向く第1および第2の表面および第1および第2の表面間に延在する開口を有する基板と、基板の第1の表面と向き合う前面を有する第1の超小型電子素子と、第1の超小型電子素子と向き合う前面を有する第2の超小型電子素子と、基板の第1の表面と第2の超小型電子素子の前面との間に配置された第3の超小型電子素子と、を備えている。基板は、端子を備えているとよい。

30

【0026】

第1の超小型電子素子は、前面から遠く離れた裏面、および前面と裏面との間に延在する縁も有しているとよい。第1の超小型電子素子は、第1の超小型電子素子の縁に隣接してその前面に露出した複数の接点を有しているとよい。第2の超小型電子素子は、互いに向き合った第1および第2の縁を有しているとよい。第2の超小型電子素子の前面は、第1および第2の縁間に延在しているとよい。第2の超小型電子素子は、第1および第2の縁から遠く離れたその前面の中央領域に配置された複数の接点を有しているとよい。第2の超小型電子素子の前面は、第1の超小型電子素子の縁を超えて突出しているとよい。第3の超小型電子素子は、互いに向き合った第1および第2の縁、第1および第2の縁間に延在する前面、および第3の超小型電子素子の第1の縁に隣接してその前面に配置された複数の接点を有しているとよい。第3の超小型電子素子の前面は、基板の第1の表面と向き合っているとよい。

40

【0027】

超小型電子アセンブリは、第1の超小型電子素子の接点を端子に電気的に接続する第1のリードと、第2の超小型電子素子の接点を端子に電気的に接続する第2のリードと、第3の超小型電子素子の接点を前記端子に電気的に接続する第3のリードと、第1および第3の超小型電子素子の接点を電気的に相互接続する第4のリードと、をさらに備えている

50

とよい。第1および第3の超小型電子素子の接点は、開口の両側に位置しているとよい。第1，第2，第3、および第4のリードは、開口と真っ直ぐに並んだ部分を有しているとよい。

#### 【0028】

一実施形態では、超小型電子アセンブリは、第1および第2の超小型電子素子の接点を電気的に相互接続する第5のリードも備えている。特定の実施形態では、超小型電子アセンブリは、第2および第3の超小型電子素子の接点を電気的に相互接続する第6のリードも備えている。特定の実施形態では、第1の超小型電子素子は、論理機能を主に果たすように構成されたチップを含んでいる。例示的な実施形態では、第2の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している。一実施形態では、第1の超小型電子素子は、任意の他の機能よりもメモリ機能アレイ機能をもたらすように構成された極めて多数の能動素子を有している。

10

#### 【0029】

以下、添付の図面を参照して、本発明の種々の実施形態について説明する。これらの図面は、本発明のいくつかの実施形態しか示しておらず、それ故、本発明の範囲を制限するとみなされるべきではないことを理解されたい。

#### 【図面の簡単な説明】

#### 【0030】

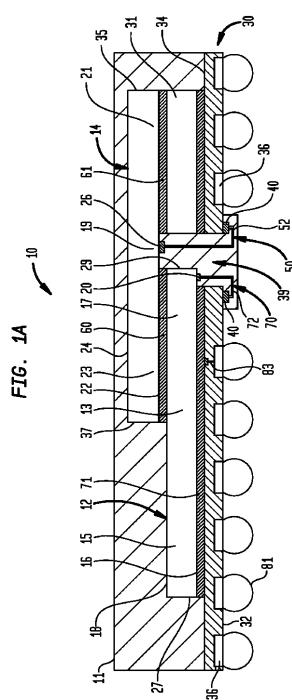

【図1A】本発明の一実施形態による積層超小型電子アセンブリの略横断立面図である。

20

【図1B】本発明の一実施形態による積層超小型電子アセンブリの略横断立面図である。

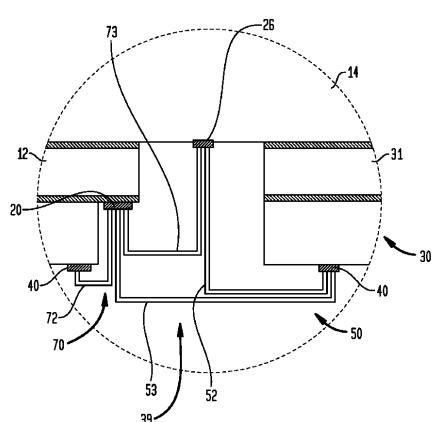

【図1C】本発明の一実施形態による積層超小型電子アセンブリの部分断面図である。

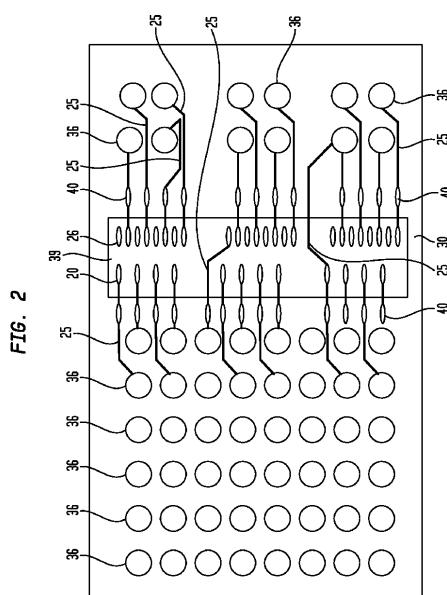

【図2】図1Aに示されている超小型電子アセンブリの平面図である。

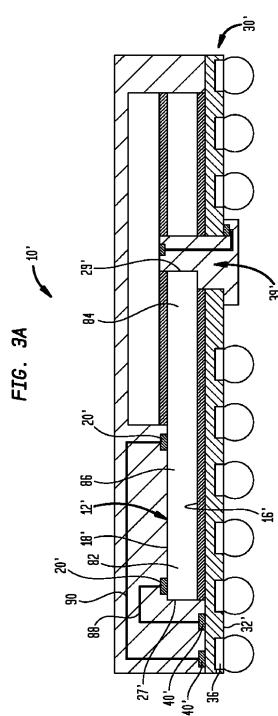

【図3A】本発明の他の実施形態による積層超小型電子アセンブリの略横断立面図である。

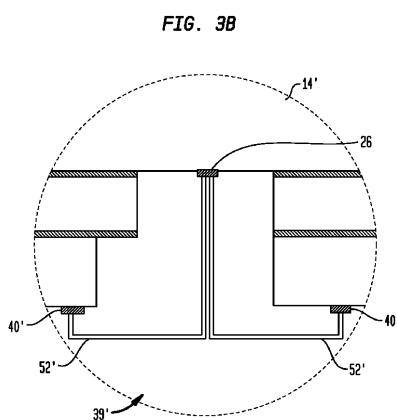

【図3B】図3Aに示されている実施形態をさらに示す部分断面図である。

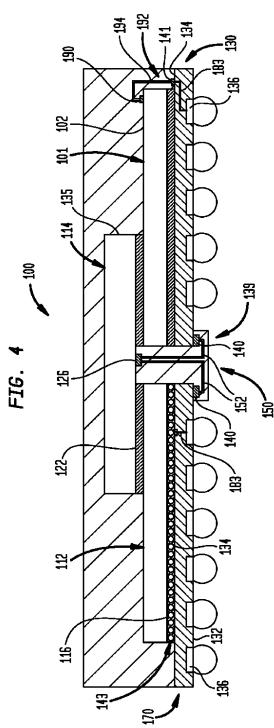

【図4】本発明のさらに他の実施形態による積層超小型電子アセンブリの略横断立面図である。

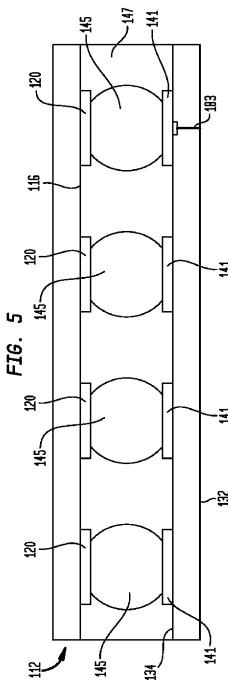

【図5】図4に示されている積層超小型電子アセンブリの一部を示す断面図である。

30

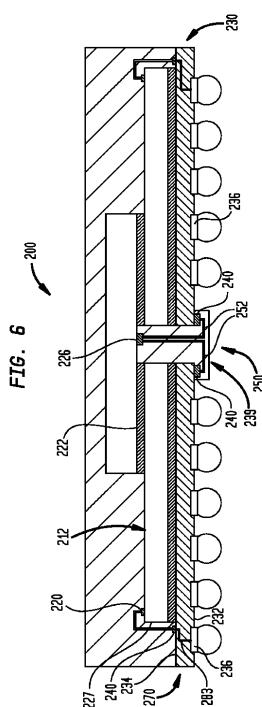

【図6】本発明の一実施形態による積層超小型電子アセンブリの略横断立面図である。

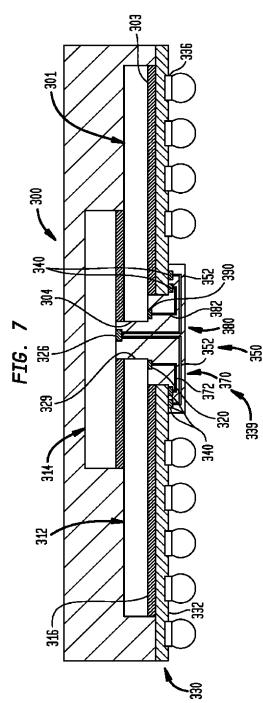

【図7】本発明の他の実施形態による積層超小型電子アセンブリの略横断立面図である。

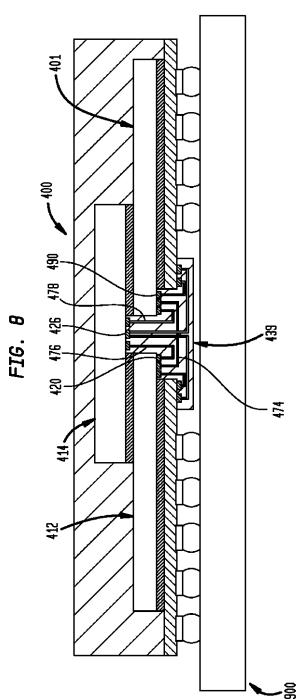

【図8】本発明のさらに他の実施形態による積層超小型電子アセンブリの略横断立面図である。

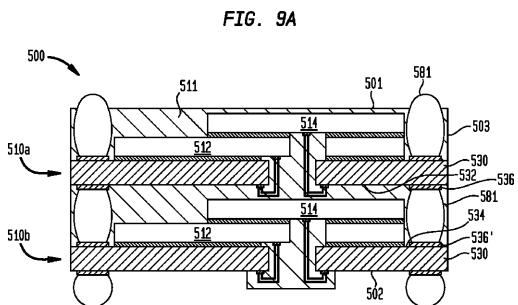

【図9A】本発明の他の実施形態による積層超小型電子アセンブリの略横断立面図である。

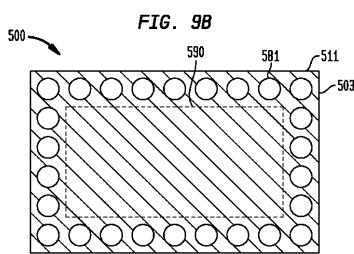

【図9B】図9Aに示されている積層超小型電子アセンブリの平面図である。

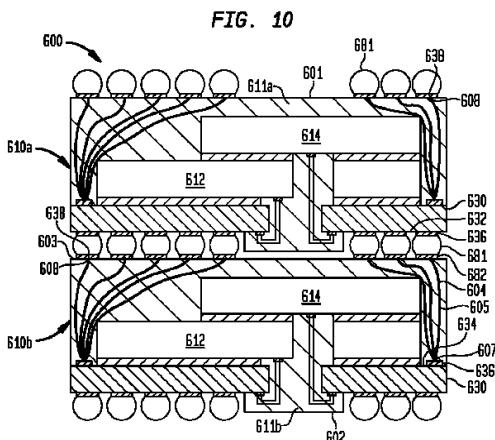

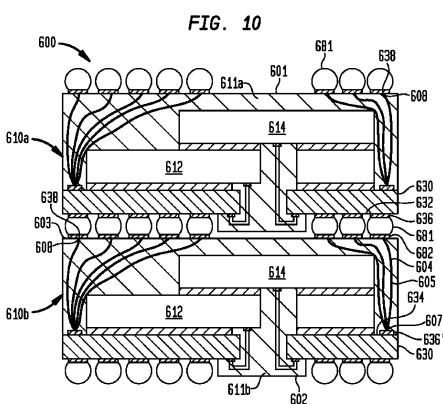

【図10】本発明のさらに他の実施形態による積層超小型電子アセンブリの略横断立面図である。

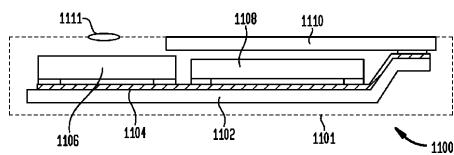

【図11】本発明の一実施形態によるシステムの概略図である。

#### 【発明を実施するための形態】

#### 【0031】

図1A，2を参照すると、本発明の一実施形態による積層超小型電子アセンブリ10は、基板30と向き合うフェイスダウン位置にある第1の超小型電子素子12および第1の超小型電子素子12の少なくとも一部の上に重なるフェイスダウン位置にある第2の超小型電子素子14を備えている。いくつかの実施形態では、第1および第2の超小型電子素子12，14は、その前面16に接点を有する半導体チップまたは半導体チップを含む素子であるとよい。半導体チップは、シリコンまたはガリウムヒ素のような半導体材料の薄い平板であり、個々の予めパッケージ化されたユニットとして供給されるようになっている。半導体チップは、シリコンまたはガリウムヒ素のような半導体材料の薄い平板であり、個々の予めパッケージ化されたユニットとして供給されるようになっている。半導体チップは、能動回路素子、とりわけ、トランジスタまたはダイオード、または受動回路素子

40

50

、とりわけ、レジスタ、キャパシタ、またはインダクタ、または能動回路素子と受動回路素子との組合せから構成されているとよい。「能動」半導体チップでは、各超小型電子素子における能動回路素子は、典型的には、互いに電気的に接続されており、1つまたは複数の「集積回路」をもたらしている。第1および第2の超小型電子素子は、いずれも、以下に詳細に説明するように、基板30に電気的に接続されている。次いで、この基板30が、その表面の端子36を介して、印刷回路基板のような回路パネルに電気的に接続されることになる。特定の実施形態では、超小型電子アセンブリ10は、回路パネル、とりわけ、印刷回路基板の面上の対応する接点に電気的に接続されるように構成された端子を有する超小型電子「パッケージ」であるとよい。

## 【0032】

特定の実施形態では、基板は、例えば、ポリマー材料またはセラミックまたはガラスのような無機材料からなる種々の構造の誘電体要素とすることができます。基板は、その上に端子のような導電要素、トレースおよび基板接点のような導電要素、または端子に電気的に接続される他の導電要素を有している。他の例では、基板は、シリコンのような半導体材料から本質的になっていてもよいし、または代替的に、半導体材料の層および1つまたは複数の誘電体層を含んでいてもよい。このような基板は、1 当たり7 パーツ・パー・ミリオン(7 ppm / )未満の熱膨張係数を有しているとよい。さらに他の実施形態では、基板は、リードフィンガーを有するリードフレームであってもよく、この場合、端子がリードフィンガーの一部、例えば、リードの端部分であってもよい。さらに他の実施形態では、基板は、リードフィンガーを有するリードフレームであってもよく、この場合、端子がリードフィンガーの一部、例えば、リードの端部分であってもよい。

10

20

30

40

## 【0033】

第1の超小型電子素子12は、論理機能を果たすように主に構成された半導体チップ、とりわけ、マイクロプロセッサ、特定用途向け集積回路(A S I C)、現場プログラム可能ゲートアレイ(F P G A)、または他の論理チップを含むことができる。特定の実施形態では、超小型電子素子12は、論理機能を主にもたらすとともに、メモリ記憶アレイも含むコントローラまたはチップオンシステム(S O C)とすることができます。他の例では、第1の超小型電子素子12は、フラッシュ(N O R またはN A N D)メモリチップ、ダイナミックランダムアクセスメモリ(D R A M)チップ、または静态ランダムアクセスメモリ(S R A M)チップのようなメモリチップを含むことができ、またはそのようなチップであってもよく、またはいくつかの他の機能を果たすように主に構成されていてもよい。このようなメモリチップは、メモリ記憶アレイを含んでいるとよく、典型的には、極めて多数の能動回路要素、例えば、チップの他の要素よりもメモリ記憶アレイ機能をもたらすように構成されたトランジスタのような能動素子を有している。第1の超小型電子素子12は、前面16、そこから遠く離れた裏面18、および前面と裏面との間に延在する第1および第2の縁27、29を有している。電気接点20が、第2の縁29に隣接して第1の超小型電子素子12の前面16に露出している。この開示に用いられる「導電要素が構造体の表面に「露出している(exposed)」」という記述は、該導電要素が、構造体の外側から表面に向かって該表面と直交する方向に移動する理論点との接触に利用できることを示している。従って、構造体の表面に露出した端子または他の導電要素は、このような表面から突出していてもよいし、このような表面と同一面をなしていてもよいし、またはこのような表面に対して窪んでいるが、構造体の孔または凹みを通して露出していてもよい。電気接点20は、ボンドパッド、またはバンプ、ポストなどのような導電構造を含んでいる。ボンドパッドは、銅、ニッケル、金、アルミニウムのような一種または複数種の金属から構成されているとよく、約0.5 μmの厚みを有しているとよい。ボンドパッドの大きさは、デバイスの形式によって変更可能であるが、典型的には、片側において10 μm - 100 μmの大きさを有している。

50

## 【0034】

第2の超小型電子素子14は、前面22、そこから遠く離れた裏面24、前面と裏面との間に延在する第1および第2の縁35、37、および前面22に露出した接点26を有

50

している。図1Aに示されているように、第1および第2の超小型電子素子12，14は、第2の超小型電子素子14の少なくとも一部が第1の超小型電子素子12の少なくとも一部に重なるように、互いに積層されている。図1Aに示されているような特定の実施形態では、第2の超小型電子素子14の前面22は、第1および第2の端領域21、23および第1および第2の端領域21、23間に延在する中央領域19を備えている。第1の端領域21は、中央領域19と第1の縁35との間に延在しており、第2の端領域23は、中央領域19と第2の縁37との間に延在している。中央領域は、第2の超小型電子素子14の第1および第2の端領域35、37間の距離の3分の1にわたって延在しており、第1および第2の端領域も、各々、これらの縁35、37間の距離の3分の1にわたって延在している。電気接点26が、第2の超小型電子素子14の前面22に露出している。例えば、接点26は、第1の表面22の中心に隣接して1列または互いに平行の2列に配置されている。第2の超小型電子素子14は、DRAMチップを含んでいてもよいし、またはDRAMチップであってもよい。このようなDRAMチップは、メモリ記憶アレイを含んでいるとよく、典型的には、極めて多数の能動回路要素、例えば、他の要素よりもメモリ記憶アレイ機能をもたらすように構成されたトランジスタのような能動素子を有している。第2の超小型電子素子14の中央領域19の少なくとも一部は、第2の超小型電子素子の接点26が第1の超小型電子素子12の第2の縁29を超えて露出するように、第1の超小型電子素子12の第2の縁29を超えて突出している。前述したように、一実施形態では、基板30は、互いに反対側を向く第1および第2の表面34、32を有する誘導体要素を含んでいる。1つまたは複数の導電要素または端子36が、基板30の第2の表面32に露出している。特定の実施形態では、端子36のいくつかまたは全てが、第1および/または第2の超小型電子素子12、14に対して移動可能になっているとよい。

10

20

30

30

### 【0035】

基板30は、その互いに向き合った第1および第2の表面間、例えば、誘電体要素30の互に反対側を向いた第1および第2の表面間に延在する1つまたは複数の開口をさらに備えている。図1Aに示されている実施形態では、基板30は、開口39を備えており、少なくともいくつかの接点26が基板30の開口39と真っ直ぐに並んでいる。複数のリードが、第2の超小型電子素子の接点26を超小型電子アセンブリの端子36に電気的に接続している。リードは、開口39と真っ直ぐに並んだ部分を有している。例えば、リードは、基板接点に接合されたワイヤボンド50を含んでおり、該基板接点は、半導体素子または誘電体要素30に沿って延在する金属トレースのようなリードの他の一部を介して、端子36に接続されており、またはもし基板がリードフレームから構成されているなら、リードは、そのリードフィンガーの一部であってもよい。

### 【0036】

誘電体要素30の第1の表面34は、第1の超小型電子素子12の前面16と並置されているとよい。図1Aに示されているように、基板30は、第1の超小型電子素子12の第1の縁27および第2の超小型電子素子14の第2の縁35を超えて延在している。一例では、誘電体材料を含む基板は、「誘電体要素」30と呼ばれることもあり、どのような適切な誘電体材料から部分的または全体的に作製されていてもよい。基板30は、どのような適切な誘電体材料から部分的または全体的に作製されていてもよい。例えば、基板30は、柔軟材料の層、例えば、ポリイミド、BT樹脂、またはテープ自動ポンディング(TAB)テープを作製するのに一般的に用いられる他の誘電体材料の層から構成されているとよい。代替的に、基板30は、纖維強化工ポキシの厚い層のような比較的剛性のボード状材料、例えば、Fr-4またはFr-5ボードから構成されていてもよい。用いられる材料に関わらず、基板30は、単層から構成されていてもよいし、または複層から構成されていてもよい。

40

### 【0037】

図1Aに戻ると、スペーサ要素または支持要素31が、第2の超小型電子素子14の第1の端領域21と誘電体要素30の一部との間に配置されている。スペーサ要素31は、

50

第2の超小型電子素子を基板30の上方に支持するのを助長するものである。このようなスペーサ要素31は、例えば、二酸化珪素などの誘電体材料、シリコンのような半導体材料、または1つまたは複数の層からなる接着剤または他のポリマー材料から作製されているとよい。特定の実施形態では、スペーサ要素は、金属を含んでいてもよいし、または金属から作製されていてもよい。もしスペーサ要素が接着剤を含んでいるなら、該接着剤は、第2の超小型電子素子14を基板30に接続することができる。一実施形態では、スペーサ要素31は、基板の第1の表面34と実質的に直交する垂直方向において、第1の超小型電子素子12の前面16と裏面18との間の厚みと実質的に同じ厚みを有している。もしスペーサ要素31が接着剤を含んでいるなら、該接着剤は、第2の超小型電子素子14を誘電体要素30に接続することができる。

10

## 【0038】

図1A, 2に示されているように、基板30は、第2の表面32に露出した導電要素または基板接点40および導電トレース25を備えている。導電トレース25は、基板接点40を端子36に電気的に連結するものである。トレース25および基板接点40は、本願の譲渡人に譲渡された米国特許出願公開第2005/0181544号に示されている方法を用いて作製することができる。この開示内容は、参照することによって、その全体がここに含まれるものとする。

## 【0039】

図1に戻ると、接着層のようなスペーサ要素または支持要素31が、第2の超小型電子素子14の第1の端領域21と基板30の一部との間に配置されている。もしスペーサ要素31が接着剤を含んでいるなら、該接着剤は、第2の超小型電子素子14を基板30に接続することができる。図1Aに示されているように、第2の超小型電子素子14の第2の端領域23は、熱伝導性を有する接着剤のような接合材料60によって、第1の超小型電子素子12の第2の端領域17に接合されている。同様に、接合材料61、例えば、任意選択的に熱伝導性を有する接着剤が、第2の超小型電子素子の第1の端領域をスペーサ要素31に接合している。接合材料71が、第1の超小型電子素子の前面16のかなりの部分と基板30の第1の表面34の一部との間に配置されていてもよい。特定の実施形態では、接合材料60, 61および/または71は、ダイ取付け接着剤から部分的または全体的に作製されているとよく、特定の例では、シリコーンエラストマーのような低弾性係数材料から構成されているとよい。しかし、特定の実施形態では、接合材料60, 61および/または71は、もし2つの超小型電子素子12, 14が同一の材料から形成された従来の半導体チップであるなら、高弾性係数接着剤または半田から全体的または部分的に作製されていてもよい。何故なら、これらの超小型電子素子は、温度変化に応じて、均一に膨張および収縮する傾向にあるからである。用いられる材料に関わらず、スペーサ要素31は、単層から構成されていてもよいし、または複層から構成されていてもよい。図4-8に関連して以下に詳細に説明するように、スペーサ要素31は、1つまたは複数の超小型電子素子と置き換えられてもよい。

20

## 【0040】

図1A, 2を参照すると、超小型電子アセンブリは、リード70を備えている。リード70は、第1の超小型電子素子の接点20を少なくともいくつかの端子36に電気的に接続するものである。リード70は、基板の30の開口39と真っ直ぐに並んだ部分を有している。一実施形態では、リードは、ワイヤボンドのようなボンド要素70を含んでおり、ボンド要素70は、開口39内を通って延在し、超小型電子素子の接点20および基板の接点40に接続されるようになっている。トレース(図示せず)が、基板に沿って、接点40と端子36との間に延在しているとよい。一変形態では、ボンドワイヤ70は、開口39内に延在し、基板接点40に電気的に接続されるワイヤボンド72を含んでいる。ワイヤボンド72の各々は、接点20を基板30の対応する基板接点40に電気的に連絡している。ワイヤボンド70は、「熱特性が改良された中央接点を有する拡張された積層超小型電子アセンブリ」と題して2010年10月19日に出願された米国特許出願第12/907,522号に記載されているような多重ワイヤボンド構造を含んでいてもよ

30

40

50

い。この開示内容は、参照することによって、その全体がここに含まれるものとする。前述したように、また図2に示されているように、トレース25は、基板接点40を端子36に電気的に接続している。従って、リード50は、ワイヤボンド52、少なくともいくつかの基板接点40、および少なくともいくつかのトレース25を含んでいることになる。これらの要素の全てが、第1の超小型電子素子12の接点20と端子36との間に電気的接続をもたらすのに貢献することになる。

#### 【0041】

図1Bに示されているように、代替的または付加的に、リードボンド76のようなリードが、図示されているように基板30の第1の表面に沿って、または第2の表面に沿って、開口39内に延在し、接点20に接続されるようになっているとよい。リードボンド76は、第1の表面34から基板30の第2の表面32の1つまたは複数の端子36に延在するビア83または任意の他の種類の導電要素に電気的に接続されるようになっているとよい。従って、リード70は、リードボンド76およびビア83を含むことになる。図1Bにさらに示されているように、超小型電子アセンブリ10は、リードボンド85を備えていてもよい。リードボンド85は、第2の超小型電子素子14の接点26を基板の第2の表面32の基板接点40に電気的に相互接続するものである。

10

#### 【0042】

超小型電子アセンブリ10は、第2の超小型電子素子14の接点26を基板30の第2の表面32の少なくともいくつかの端子36に電気的に接続するリード50をさらに備えている。リード50は、開口39と真っ直ぐに並んだ部分を有しており、第2の超小型電子素子14の接点26を基板30の第2の表面32の基板接点40に電気的に接続する多重ワイヤボンド52を含んでいるとよい。これらのワイヤボンド52は、開口39を通って延在しているとよい。ワイヤボンド52の各々は、接点26を基板30の対応する基板接点40に電気的に接続している。リード50は、「熱特性が改良された中央接点を有する拡張された積層超小型電子アセンブリ」と題して2010年10月19日に出願された米国特許出願第12/907,522号に記載されているような多重ワイヤボンド構造を含んでいてもよい。この開示内容は、参照することによって、その全体がここに含まれるものとする。図2に示されているように、トレース25が、基板接点40を端子36に電気的に接続している。従って、リード50は、ワイヤボンド52、少なくともいくつかの基板接点40、および少なくともいくつかのトレース25を含んでいることになる。これらの要素の全てが、第2の超小型電子素子14の接点26と端子36との間に電気接続をもたらすのに貢献することになる。代替的または付加的に、リード50は、接点26を基板30の第1の表面34または基板の第2の表面32のいくつかの基板接点に電気的に連結するリードボンドを含んでいてもよい。リードボンドは、必ずしも、基板30の開口39を貫通する必要がなく、開口と少なくとも部分的に真っ直ぐに並んでいてもよい。

20

30

#### 【0043】

超小型電子アセンブリ10は、少なくとも第1の超小型電子素子12および第2の超小型電子素子14を覆うオーバモールド材または封止材11をさらに備えているとよい。図A1に示されているように、オーバモールド材11は、第1の超小型電子素子12の第1の縁27および第2の超小型電子素子14の第1の縁35を超えて延在する基板30の部分も覆っているとよい。その結果、オーバモールド材11は、少なくとも第1の超小型電子素子12の第1の縁27、第2の超小型電子素子14の第1の縁35、および基板30の第1の表面34に接触している。オーバモールド材11は、エポキシなどを含むどのような適切な材料から作製されていてもよい。

40

#### 【0044】

超小型電子アセンブリ10は、「熱特性が改良された中央接点を有する拡張された積層超小型電子アセンブリ」と題して2010年10月19日に出願された米国特許出願第12/907,522号に記載されているような、第1または第2の超小型電子素子12,14の1つまたは複数の裏面に取り付けられたヒートスプレッダまたはヒートシンクを追加的に備えていてもよい。なお、この開示内容は、参照することによって、その全体がこ

50

こに含まれるものとする。いくつかの実施形態では、超小型電子アセンブリ 10 は、第 1 および / または第 2 の超小型電子素子 12 , 14 の 1 つまたは複数の裏面 18 , 24 および可能であれば、端領域 27 , 35 , 37 に熱的に連結されたヒーツプレッダを備えている。ヒーツプレッダは、図 1A に示されているオーバモールド材 11 によって占められた領域の一部を占めることになる。

#### 【 0045 】

加えて、超小型電子アセンブリ 10 は、誘電体要素 30 の第 2 の表面 32 上の端子 36 に取り付けられた接合ユニット 81 をさらに備えている。接合ユニット 81 は、半田ボールであってもよいし、または他の金属、例えば、錫、インジウム、またはその組合せの塊であってもよく、超小型電子アセンブリ 10 を印刷回路基板のような回路パネルに接合し、電気的に接続するように適合されている。10

#### 【 0046 】

図 1C に示されているように、超小型電子アセンブリ 10 のリード 50 は、付加的または代替的に、第 1 の超小型電子素子 12 の少なくともいくつかの接点 20 を開口 39 の両側に配置された少なくともいくつかの基板接点 40 に電気的に接続するワイヤボンド 53 を含んでいてもよい。従って、ワイヤボンド 53 は、基板 30 の開口に跨っていることになる。加えて、リード 70 は、代替的にまたは付加的に、第 1 の超小型電子素子 12 の接点 20 の少なくともいくつかを第 2 の超小型電子素子 14 の接点 26 の少なくともいくつかに電気的に接続するワイヤボンド 73 を含んでいてもよい。20

#### 【 0047 】

図 3A は、図 1A に示されている超小型電子アセンブリ 10 の変更形態 10' を示している。この変更形態では、表面 16' の接点 20 に代わって（または加えて）、第 1 の超小型電子素子 12' は、基板 30' から離れる方を向く表面 18' に接点 20' を備えている。このような表面 18' は、第 1 の超小型電子素子 12' の前面とすることができます。表面 18' は、第 1 の超小型電子素子 12' の第 1 の縁 27' に隣接する第 1 の端部分 82、第 2 の縁 29' に隣接する第 2 の端部分 84、および第 1 および第 2 の端部分 82, 84 間の中央部分 86 を有している。接点 20' は、第 1 の縁 27' に隣接する表面 18' の第 1 の端部分 82 内、表面 18' の中央部分 86 内、または第 1 の端部分および中央部分の両方内に配置されているとよい。一実施形態では、接点 20' は、表面 18' の中央部分 86 に 1 列または互いに平行の 2 列に配置されている。30

#### 【 0048 】

超小型電子アセンブリ 10' は、表面 18' の接点 20' および端子 36 に電気的に接続されたリード 88 を備えることができる。一例では、ワイヤボンドのようなリード 88 の部分は、第 1 の超小型電子素子 12' の第 1 の縁 27 を超えて、接点 40' に延在し、該接点 40' が、例えば、トレース（図示せず）または他の導電要素を介して、端子に接続されるようになっている。リード 88 は、接点 20' から第 1 の超小型電子素子の第 1 の縁 27' を超えて、基板 30' の第 1 の表面 34' の接点 40' に延在するワイヤボンド 90 を含んでいるとよく、該接点と端子 36 との間に導電トレースのような基板の他の導電構造を含んでいるとよい。図 3B に示されているように、リード部分 52' 、例えば、ワイヤボンドが、超小型電子素子 14' の接点 26 を開口 39' の片側または両側の接点 40' に接続することができる。40

#### 【 0049 】

図 4, 5 は、図 1A に示されている超小型電子アセンブリ 10 の変更形態を示している。図 1A に示されている超小型電子アセンブリ 100 は、フェイスアップ位置にある第 1 の超小型電子素子 101 を有する点において、図 3A に示されている超小型電子アセンブリ 10 に類似している。この変更形態では、フリップチップ位置にある第 3 の超小型電子素子 112 が、スペーサ要素 31 に代わって設けられている。しかし、図示されている特定の例では、第 1 の超小型電子素子 101 は、図の右側に位置しており、第 3 の超小型電子素子 112 は、図の左側に位置している。第 3 の超小型電子素子 112 は、その前面 116 に複数の接点 120 を備えている。第 3 の超小型電子素子 112 の接点 120 は、基50

板 130 の第 2 の表面 132 に少なくともいくつかの端子 136 に接続されている。

【0050】

フリップチップ接続部 143 は、金属のバンプ、例えば、半田のような接合金属を介して、第 1 の超小型電子素子 112 の前面 116 の電気接点 120 を基板 30 の第 1 の表面 134 の少なくともいくつかの接点 141 に電気的に接続している。次いで、この超小型電子素子は、反転され、これによって、金属バンプは、超小型電子素子の接点（例えば、ボンドパッド）と基板との間の電気経路をもたらすと共に、基板に対する超小型電子素子の機械的な取付けをもたらすことになる。フリップチッププロセスには多くの変更形態があるが、一般的な一構成では、半田が金属バンプとして用いられ、この場合、半田をボンドパッドおよび基板に固定するための方法として、該半田を熔融させようになっている。熔融すると、半田は、流動し、切頭球を形成することになる。

10

【0051】

フリップチップ相互接続部は、ワイヤボンドを介して誘電体要素に接続された他の超小型電子素子と比較して、第 1 の超小型電子素子 112 に極めて多数の（入力 / 出力）I / O をもたらすことになる。加えて、フリップチップ相互接続部は、第 2 の超小型電子素子 114 と基板 130 との間のワイヤボンド経路を最小限にし、これによって、ワイヤボンドのインピーダンスを低減させることができる。

20

【0052】

図 4, 5 に示されている実施形態では、フリップチップ相互接続部 143 は、第 1 の超小型電子素子 112 と基板 130 との間に配置された半田ボールのような複数の固体金属バンプ 145 を備えている。各金属バンプ 145 は、導電球または導電ポストとすることができます。各固体金属バンプ 145 は、第 1 の超小型電子素子 112 の接点 120 と基板 130 の基板接点 141 との間に配置され（かつ接触し）、これによって、電気接点 120 と導電要素 141 との間に電気接続をもたらすことになる。金属バンプ 145 は、接合金属または任意の他の適切な接合材料から本質的になっている。

20

【0053】

アンダーフィル 147 が、第 1 の超小型電子素子 112 を基板 130 に付着させるために固体金属バンプ 145 を包囲している。アンダーフィル 147 は、特に、第 1 の超小型電子素子 112 を基板 130 に連結するために、第 1 の超小型電子素子 112 の前面 116 と基板 130 の第 1 の表面 134 との間に配置されている。例えば、アンダーフィル 147 は、エポキシ樹脂のようなポリマー接着剤から全体的または部分的に作製されているとい。しかし、いくつかの実施形態では、アンダーフィル 147 が全体的に省略されている。

30

【0054】

図 6 は、図 4 に示されている超小型電子アセンブリ 100 の変更形態を示している。超小型電子アセンブリ 200 は、超小型電子アセンブリ 100 に類似しているが、第 1 の超小型電子を基板接点に電気的に接続するフリップチップ接続部を備えていない。代わって、第 1 の超小型電子素子 212 は、フェイスアップ配置されており、その第 1 の縁 227 に隣接して一列または複数列の接点 220 を備えている。リード 270 が、接点 220 を基板 230 の第 2 の表面 232 上の端子 236 に電気的に接続している。

40

【0055】

リード 270 は、接点 220 から、第 1 の超小型電子素子 212 の第 1 の縁 227 を超えて、基板 230 の第 2 の表面 232 の基板接点 230 に延在するワイヤボンド 272 を含んでいる。加えて、リード 270 は、基板接点 240 を少なくともいくつかの端子 236 に電気的に接続するビア 283 または任意の他の適切な導電要素を含んでいる。ビア 283 は、基板 230 の第 1 の表面 234 から第 2 の表面 232 に向かって、基板 230 を貫通している。

【0056】

超小型電子アセンブリ 200 は、第 2 の超小型電子素子 214 の前面 222 の接点 226 を少なくともいくつかの端子 236 に電気的に接続するリード 250 をさらに備えてい

50

る。リード 250 の一部は、基板 230 の開口 239 と真っ直ぐに並んでいる。この変更形態では、リード 250 は、接点 226 から開口 239 内に延在する多重ワイヤボンド 252 を含んでいる。ワイヤボンド 252 は、基板 230 の第 2 の表面 232 において開口 239 の両側に配置された基板接点 240 に電気的に接続されるようになっている。

#### 【0057】

図 7 は、図 6 に示されている超小型電子アセンブリ 200 の変更形態を示している。図 7 に示されている超小型電子アセンブリ 300 は、スペーサ要素 31 に置き換えられた第 3 の超小型電子素子 301 を有していることを除けば、図 1A, 1B に示されている超小型電子アセンブリ 200 と実質的に同様である。第 3 の超小型電子素子は、第 1 の超小型電子素子 12 (図 1A) と同様の基板に対する電気的相互接続部を有している。

10

#### 【0058】

図 8 は、図 7 に示されている超小型電子アセンブリ 300 の変更形態を示している。この変更形態では、図示されている超小型電子アセンブリ 400 は、回路パネル 900、例えば、印刷回路基板のような外部コンポーネントに実装されており、付加的な電気接続部またはリードを備えている。図 8 は、印刷回路基板のような回路パネルに電気的に実装された 1 つの超小型電子アセンブリしか示していないが、本明細書に記載された超小型電子アセンブリのいずれが、超小型電子アセンブリの外部の回路パネルまたは他のコンポーネントに実装されてもよい。

#### 【0059】

超小型電子アセンブリ 400 は、電気接続部またはリード 474 を備えている。リード 474 は、開口 439 を横切って延在し、第 1 の超小型電子素子 412 の接点 420 を第 3 の超小型電子素子 401 の接点 490 に電気的に接続している。リード 474 は、ワイヤボンドおよび / またはリードボンドを含んでいる。他の組の電気接続部またはリード 476 が、基板 430 の開口 439 と少なくとも部分的に真っ直ぐに並んでおり、第 1 の超小型電子素子 412 の少なくともいくつかの接点 420 を第 2 の超小型電子素子 414 の少なくともいくつかの接点 426 に電気的に接続している。リード 476 は、ワイヤボンドおよび / またはリードボンドを含んでいる。さらに他の組の電気接続部またはリード 478 が、基板 430 の開口 439 と少なくとも部分的に真っ直ぐに並んでおり、第 2 の超小型電子素子 414 の少なくともいくつかの接点 426 を第 3 の超小型電子素子 401 の少なくともいくつかの接点 490 に電気的に接続している。リード 478 は、ワイヤボンドおよび / またはリードボンドを含んでいる。

20

#### 【0060】

図 9A は、図 1A に示されている略側断面図を積層した変更形態を示している。超小型電子コンポーネント 500 は、積層された第 1 および第 2 の超小型電子アセンブリ 510a, 510b (総称的に、超小型電子アセンブリ 510) を有している。これらの超小型電子アセンブリ 510 は、各々、図 1A - 8 を参照して前述した超小型電子アセンブリのいずれであってもよく、これらの超小型電子アセンブリは、互いに同じであってもよいしまたは異なっていてもよい。スタック内にどのような数の超小型電子アセンブリ 510、例えば、図 9A に示されているように、2 つの超小型電子アセンブリ 510a, 510b が含まれていてもよい。

30

#### 【0061】

半田ボールのような接合ユニット 581 が、第 1 および第 2 の超小型電子アセンブリ 510a, 510b を互いに接合し、かつ互いに電気的に連結している。このような接合ユニット 581 は、第 1 の超小型電子アセンブリ 510a の基板 530 の第 2 の表面 532 に露出した端子 536 と、第 2 の超小型電子アセンブリ 510b の基板 530 の第 1 の表面 534 に露出した端子 536' とに取り付けられている。積層超小型電子アセンブリ 510 を備える超小型電子コンポーネント 500 は、超小型電子コンポーネント 500 の上面 501 または底面 502 に露出した接合ユニット 581 を用いて、印刷回路基板のような回路パネルに取り付けられるようになっている。

40

#### 【0062】

50

図 9 B に示されているように、超小型電子コンポーネント 500 は、超小型電子コンポーネントの周辺 503 に隣接して配置された接合ユニット 581 を備えている。接合ユニット 581 は、超小型電子コンポーネント 500 の過疎 (depopulated) 中央領域 590 の外側に配置されている。このような実施形態では、接合ユニット 581 は、超小型電子アセンブリ 510 の第 1 および第 2 の超小型電子要素 512, 514 の上に重ならないよう、配置されている。このような実施形態によって、超小型電子コンポーネント 500 が中央領域 590 内に接合ユニット 581 を含む場合よりも、複数の超小型電子アセンブリ 510 が互いに接合されたときの積層高さを小さくすることができる。

#### 【0063】

図 9 A に示されているように、超小型電子コンポーネント 500 は、超小型電子アセンブリ 510 の第 1 および第 2 の超小型電子素子 512, 514 を少なくとも部分的に覆う単一の封止材 511 を有している。このような実施形態では、これらの超小型電子アセンブリ 510 は、封止されることなく、互いに接合され、次いで、接合された超小型電子コンポーネント内のそれぞれの超小型電子素子を覆う単一の封止材 511 が施されることになる。封止材 511 は、超小型電子コンポーネントの以下の部分、すなわち、超小型電子コンポーネントの外部の 1 つまたは複数のコンポーネントに電気的に接続されるように構成されていない部分を覆うようになっている。

#### 【0064】

代替的実施形態では、超小型電子アセンブリ 510 の各々は、図 10 に示されている実施形態と同じように、個別に形成され、それぞれ、封止材が施されるようになっていてよい。各超小型電子アセンブリ 510 に対して個別に施された封止材を有するこのような実施形態では、このように封止された超小型電子アセンブリは、例えば、図 10 に示されているような形態で互いに積層され、かつ互いに接合され、それらの間に電気的連通をもたらすようになっている。

#### 【0065】

特定の例では、超小型電子コンポーネント 500 は、例えば、スマートフォン用途用の非均質メモリとして機能するように構成されているとよい。このような例では、超小型電子アセンブリ 510 内の超小型電子素子 512, 514 のいくつかは、揮発性 RAM のようなメモリ記憶素子を含むことができ、超小型電子素子 512, 514 のいくつか、不揮発性フラッシュメモリのようなメモリ記憶素子を含むことができる。

#### 【0066】

図 10 は、図 1 A に示されている略側断面図を積層した変更形態を示している。超小型電子コンポーネント 600 は、積層された第 1 および第 2 の超小型電子アセンブリ 610 a, 610 b (総称的に、超小型電子アセンブリ 610) を有している。超小型電子アセンブリ 610 は、各々、図 1 A - 8 を参照して前述した超小型電子アセンブリのいずれでもよく、これらの超小型電子アセンブリは、互いに同じであってもよいし、または異なっていてもよい。スタック内にどのような数の超小型電子アセンブリ 610、例えば、図 10 A に示されているように、2つの超小型電子アセンブリ 610 a, 610 b が含まれていてもよい。

#### 【0067】

超小型電子コンポーネント 600 は、以下の点、すなわち、接合ユニット 681 の少なくともいくつかが超小型電子素子 612, 614 の上に重なるように、かつ超小型電子アセンブリ 610 a, 610 b の各々が、個別に形成され、それぞれ、封止材 611 a, 610 b が施される点を除けば、図 9 A, 9 B に示されている超小型電子コンポーネント 500 と同じである。代替的な実施形態では、超小型電子コンポーネント 600 は、図 9 A に示されている単一の封止材 511 と同じように、超小型電子アセンブリ 610 の第 1 および第 2 の超小型電子素子 612, 614 を少なくとも部分的に覆う単一の封止材を有していてもよい。

#### 【0068】

図 10 に示されているように、接合ユニット 681 が、これらの超小型電子アセンブリ

10

20

30

40

50

610を互いに接合し、かつ電気的に連結するようになっている。このような接合ユニット681は、第1の超小型電子アセンブリ610aの基板630の第2の表面632に露出した端子636と、第2の超小型電子アセンブリ610bの封止材611bの上面603に露出した端子682とに取り付けられている。端子682は、ワイヤボンド604によって、基板630の第1の表面634に露出した導電要素636'に電気的に接続されている。封止材611aまたは611bの上面603に露出した端子682のいくつかは、超小型電子素子612, 614の少なくとも1つの上に重なっている。超小型電子素子612, 614の少なくとも1つの上に重なる端子682を備える超小型電子アセンブリ610を有するこのような超小型電子コンポーネント600では、各超小型電子アセンブリ610の端子682, 636は、超小型電子アセンブリ610のエリアアレイ積層を可能とするエリアアレイに配置されることになる。

10

## 【0069】

封止材611aまたは611bの上面603に露出した端子682は、上面の上方に延在していてもよいし、上面と同じ平面をなしていてもよいし、または上面の下方に凹んでもよい。このような端子682は、どのような形状、例えば、パッド状またはボール状であってもよい。端子682およびワイヤボンド604の形状および構成の他の例は、2011年5月3日に出願された同時係属中の共有に係る韓国特許出願第10-2011-0041843号に図示され、かつ記載されている。この開示内容は、参照することによって、ここに含まれるものとする。

20

## 【0070】

ワイヤボンド604は、その基部607において導電要素636'に接合され、基部607および基板630から遠く離れた自由端608に延在している。ワイヤボンド604の自由端608は、超小型電子素子612, 614または(超小型電子素子612, 614に接続される)超小型電子アセンブリ610a内の任意の他の導電特徴部に電気的に接続または接合されないという点において、自由な端として特徴付けられている。換言すれば、自由端608は、半田ボールまたは本明細書において検討した他の特徴部を介して、超小型電子アセンブリ610aの外部の導電特徴部に直接的または間接的に電気的に接続されることが可能になっている。自由端608は、例えば、封止材611aによって所定位置に保持されてもよいし、または他の導電特徴部に電気的に接続されてもよいという事実は、このような任意の特徴部が超小型電子素子612, 614に電気的に接続されていない限り、該自由端608は、ここに述べたように「自由」ではないことを意味するものではない。逆に、基部607は、ここで述べたように、超小型電子素子612, 614に直接または間接的に接続されることになるので、自由ではない。

30

## 【0071】

ワイヤボンド604は、銅、金、ニッケル、半田、アルミニウム、などのような導電材料から形成されているとよい。付加的に、ワイヤボンド604は、例えば、銅またはアルミニウムのような導電材料のコアに皮膜が施された組合せ材料から作製されていてもよい。この皮膜は、アルミニウム、ニッケル、などのような第2の導電材料であるとよい。代替的に、皮膜は、絶縁材料、例えば、絶縁被覆であってもよい。一実施形態では、ワイヤボンド604を形成するために用いられるワイヤは、約15μmから150μmの間の厚み、例えば、ワイヤ長さを横断する寸法を有することができる。

40

## 【0072】

ワイヤボンド604の自由端608は、端面638を有している。端面638は、複数のワイヤボンド604のそれぞれの端面638によって形成されたアレイにおける接点の少なくとも一部を形成している。ワイヤボンド604の(未封止部分とも呼ばれる)一部は、封止材611aによって覆われておらず、これによって、ワイヤボンドを封止材の外側に位置する特徴部または要素に対する電気接続に利用することが可能になる。一実施形態では、ワイヤボンド604の端面638は、封止材611aによって覆われておらず、該封止材の上面603に露出している。端面638が封止材によって覆われていない構成に加えて、またはそれに代わって、ワイヤボンド604の縁面605の一部が封止材611

50

1aによって覆われないようになっている実施形態も可能である。換言すれば、封止材611aは、ワイヤボンド604の一部、例えば、端面638、縁面605、またはこれらの組合せを除けば、第1の表面634の上方の超小型電子アセンブリ610aの全てを覆っているとよい。

#### 【0073】

一実施形態では、端面638と縁面605の一部とが、封止材611aによって被覆されないようになっている。このような構成によって、半田ボールなどによって、他の導電要素への接続が可能になる。具体的には、半田が縁面605に沿って濡れることによって、端面638への接合に加えて、縁面605への接合が可能にする。図示されている実施形態では、封止材611aの上面603のような表面が、超小型電子素子612, 614を覆うのに十分な距離だけ、基板630の第1の表面634から離間しているとよい。従って、ワイヤボンド604の端638が上面603と同一平面になっている超小型電子アセンブリ610aの実施形態は、超小型電子素子612, 614よりも基板630の上方に高く延在するワイヤボンド604を備えているとよい。

10

#### 【0074】

積層超小型電子アセンブリ610を備える超小型電子コンポーネント600は、超小型電子コンポーネント600の上面601または底面602に露出した接合ユニット681によって、印刷回路基板のような回路パネルに取り付けられることになる。

#### 【0075】

特定の例では、超小型電子コンポーネント600は、例えば、スマートフォン用途用の非均質メモリとして機能するように構成されている。このような例では、超小型電子アセンブリ610内の超小型電子アセンブリ612, 614のいくつかは、揮発性RAMのようなメモリ記憶要素を含むことができ、超小型電子要素612, 614のいくつかは、不揮発性フラッシュメモリのようなメモリ記憶要素を含むことができる。

20

#### 【0076】

図9A, 9B, 10は、ワイヤボンドを介して基板の接点に電気的に接続された超小型電子要素を示しているが、他の実施形態では、このような超小型電子要素は、他の接続構成、例えば、基板の接点への1つまたは複数の超小型電子要素のリードボンド実装およびフリップチップ実装を介して、基板の接点に電気的に接続されてもよい。

30

#### 【0077】

前述した超小型電子アセンブリは、図11に示されるような種々の電子システムの構築に利用可能である。例えば、本発明のさらに他の実施形態によるシステム1100は、前述の超小型電子アセンブリ1106を他の電子コンポーネント1108, 1110と併用することができる。図示されている例では、コンポーネント1108は、半導体チップであり、コンポーネント1110は、ディスプレイスクリーンであるが、どのような他のコンポーネントが用いられてもよい。もちろん、説明を明瞭にするために、図11には2つの付加的なコンポーネントしか示されていないが、システムは、どのような数のこのようなコンポーネントを備えていてもよい。超小型電子アセンブリ1106は、前述したアセンブリのいずれであってもよい。さらに他の変更形態では、どのような数のこのような超小型電子アセンブリが用いられてもよい。

40

#### 【0078】

超小型電子アセンブリ1106およびコンポーネント1108, 1110は、破線によって概略的に描かれている共通ハウジング1101内に実装されており、必要に応じて、互いに電気的に相互接続され、所望の回路を形成するようになっている。図示されている例示的なシステムでは、システムは、柔軟な印刷回路基板のような回路パネル1102を含んでおり、回路パネルは、コンポーネントを互いに相互接続する多数の導体1104を備えている。これらの回路の1つのみが図11に示されている。しかし、これは単なる例示にすぎず、電気的接続をなすどのような適切な構造が用いられてもよい。ハウジング1101は、例えば、携帯電話または携帯情報端末に用いられる形式の携帯ハウジングとして描かれており、スクリーン1110がこのハウジングの表面に露出している。構造体1

50

106が撮像チップのような光感応要素を含んでいる場合、レンズ1111または他の光学素子が光を構造体に導くために設けられてもよい。ここでも、図11に示されている簡素化されたシステムは、単なる例示にすぎず、例えば、前述の構造体を用いて、他のシステム、例えば、デスクトップコンピュータ、ルーターなどのような定置構造と一般的に見なされるシステムを作製することも可能である。

#### 【0079】

本発明をここでは特定の実施形態を参照して説明してきたが、これらの実施形態は、本発明の原理および用途の単なる例示にすぎないことを理解されたい。従って、例示的な実施形態に対して多くの修正がなされてもよいこと、および添付の請求項に記載される本発明の精神および範囲から逸脱することなく、他の構成が考案されてもよいことを理解されたい。

10

#### 【0080】

種々の従属請求項およびそこに記載される特徴は、元の請求項に記載されるのと異なる方法によって組み合わされてもよいことを理解されたい。また、個々の実施形態に関連して記載された特徴は、記載された実施形態の他の特徴と共有されてもよいことを理解されたい。

【図1A】

【図 1 C】

FIG. 1C

【図 2】

【図 3 A】

【図 3 B】

【 义 4 】

【 図 5 】

【図6】

【 図 7 】

【図8】

【図 9 A】

【図9B】

【図10】

【 図 1 1 】

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      | International application No<br>PCT/US2012/032997 |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------|------------------------------------------------------------------------------------|-----------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---|----------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>INV. H01L25/10 H01L25/065 H01L23/31<br>ADD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                      |                                                   |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                      |                                                   |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>H01L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                      |                                                   |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                      |                                                   |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>EPO-Internal, WPI Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                      |                                                   |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="text-align: left; padding: 2px;">Category*</th> <th style="text-align: left; padding: 2px;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="text-align: left; padding: 2px;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td style="padding: 2px;">Y</td> <td style="padding: 2px;">US 6 703 713 B1 (TSENG WEI-CHENG [TW] ET AL) 9 March 2004 (2004-03-09)<br/>column 4, lines 51-65; figures 1-3<br/>column 5, line 15 - line 20<br/>-----</td> <td style="padding: 2px;">1-3,9,<br/>24-26</td> </tr> <tr> <td style="padding: 2px;">Y</td> <td style="padding: 2px;">US 2007/218689 A1 (HA JONG-WOO [KR] ET AL) 20 September 2007 (2007-09-20)<br/>paragraph [0040] - paragraph [0043];<br/>figure 5<br/>-----</td> <td style="padding: 2px;">1-3,9,<br/>24-26</td> </tr> </tbody> </table> |                                                                                                                                                      |                                                   | Category* | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | Y | US 6 703 713 B1 (TSENG WEI-CHENG [TW] ET AL) 9 March 2004 (2004-03-09)<br>column 4, lines 51-65; figures 1-3<br>column 5, line 15 - line 20<br>----- | 1-3,9,<br>24-26 | Y | US 2007/218689 A1 (HA JONG-WOO [KR] ET AL) 20 September 2007 (2007-09-20)<br>paragraph [0040] - paragraph [0043];<br>figure 5<br>----- | 1-3,9,<br>24-26 |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Citation of document, with indication, where appropriate, of the relevant passages                                                                   | Relevant to claim No.                             |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | US 6 703 713 B1 (TSENG WEI-CHENG [TW] ET AL) 9 March 2004 (2004-03-09)<br>column 4, lines 51-65; figures 1-3<br>column 5, line 15 - line 20<br>----- | 1-3,9,<br>24-26                                   |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | US 2007/218689 A1 (HA JONG-WOO [KR] ET AL) 20 September 2007 (2007-09-20)<br>paragraph [0040] - paragraph [0043];<br>figure 5<br>-----               | 1-3,9,<br>24-26                                   |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input checked="" type="checkbox"/> See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                      |                                                   |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

| * Special categories of cited documents :<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |                                                   |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

| *T* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>*X* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>*Y* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art<br>"&" document member of the same patent family                                                                                                                                                                                                                                                                                                             |                                                                                                                                                      |                                                   |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

| Date of the actual completion of the international search<br><br>20 June 2012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Date of mailing of the international search report<br><br>07/08/2012                                                                                 |                                                   |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

| Name and mailing address of the ISA/<br>European Patent Office, P.O. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel: (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Authorized officer<br><br>Manook, Rhoda                                                                                                              |                                                   |           |                                                                                    |                       |   |                                                                                                                                                      |                 |   |                                                                                                                                        |                 |

**INTERNATIONAL SEARCH REPORT**

International application No.

PCT/US2012/032997

**Box No. II Observations where certain claims were found unsearchable (Continuation of Item 2 of first sheet)**

This international search report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:

1.  Claims Nos.: because they relate to subject matter not required to be searched by this Authority, namely:

2.  Claims Nos.: because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful international search can be carried out, specifically:

3.  Claims Nos.: because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).

**Box No. III Observations where unity of invention is lacking (Continuation of Item 3 of first sheet)**

This International Searching Authority found multiple inventions in this international application, as follows:

see additional sheet

1.  As all required additional search fees were timely paid by the applicant, this international search report covers all searchable claims.

2.  As all searchable claims could be searched without effort justifying an additional fees, this Authority did not invite payment of additional fees.

3.  As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:

4.  No required additional search fees were timely paid by the applicant. Consequently, this international search report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.:

1-6, 9, 24-26

**Remark on Protest**

- The additional search fees were accompanied by the applicant's protest and, where applicable, the payment of a protest fee.

- The additional search fees were accompanied by the applicant's protest but the applicable protest fee was not paid within the time limit specified in the invitation.

- No protest accompanied the payment of additional search fees.

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2012/032997

| Patent document cited in search report | Publication date | Patent family member(s) | Publication date         |

|----------------------------------------|------------------|-------------------------|--------------------------|

| US 6703713 B1 09-03-2004               | TW US            | 557556 B<br>6703713 B1  | 11-10-2003<br>09-03-2004 |

| US 2007218689 A1 20-09-2007            | NONE             |                         |                          |

International Application No. PCT/ US2012/ 032997

FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210

This International Searching Authority found multiple (groups of) inventions in this international application, as follows:

1. claims: 1-6

Re. cl. 2 the special technical feature with respect to the not inventive subject matter of claim 1 (according to documents US6703713 (D1) with US 2007/218689 (D2)) is that at least some of the second terminals are electrically connected with conductive elements exposed at the first surface of the substrate with wire bonds.

Thus the objective problem of claim 2 to be solved can be construed as: how to connect the internal connections of the single microelectronic assembly to the external connections of the single microelectronic assembly and simultaneously be heat conducting.

1.1. claims: 9, 24-26

Although the special technical features of the dependent claims 9 and 24-26 are not the same, they could be searched without any additional effort and thus are included in the first searched group of claims Ia.

---

2. claims: 7, 12-14

Re. cl. 7 the special technical feature with respect to the not inventive subject matter of claim 1 is that at least one of the microelectronic elements includes a volatile random access memory (RAM), and at least one of the microelectronic elements includes nonvolatile flash memory.

Re. cl. 12 the special technical feature with respect to the not inventive subject matter of claim 1 is that the first microelectronic element includes a chip configured to predominantly perform a logic function.

Re. cl. 13 the special technical feature with respect to the not inventive subject matter of claim 1 is that the second microelectronic element has a greater number of active devices configured to provide memory storage array function than any other function.

Re. cl. 14 the special technical feature with respect to the not inventive subject matter of claim 1 is that the first microelectronic element has a greater number of active devices configured to provide memory storage array function than any other function.

Thus the objective problem of claims 7,12,13 and 14 to be solved can be construed as: Enabling the microelectronic assembly to perform multiple functions.

---

3. claim: 8

Re. cl. 8 the special technical feature with respect to the not inventive subject matter of claim 1 is that third leads

International Application No. PCT/ US2012/ 032997

FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210

electrically interconnecting the contacts of the first microelectronic element with the contacts of the second microelectronic element, the first, second, and third leads having portions aligned with the aperture.

Thus the objective problem of claim 8 to be solved can be construed as: How to ensure the first and second microelectronic elements can operate with each other, whilst ensuring minimal interconnect resistance is maintained.

---

4. claim: 10

Re. cl. 10 the special technical feature with respect to the not inventive subject matter of claim 1 is that the portions of at least one of the first leads and the second leads aligned with the aperture are portions of monolithic conductive elements having second portions extending along the substrate to the terminals.

Thus the objective problem of claim 10 to be solved can be construed as: ensuring the fabrication of the leads can be minimised, whilst simultaneously avoiding resistive loss at the connecting points.

---

5. claim: 11

Re. cl. 11 the special technical feature with respect to the not inventive subject matter of claim 1 is that there is a spacing element between the front surface of the second microelectronic element and the first surface of the substrate.

Thus the objective problem of claim 11 to be solved can be construed as: controlling CTE mismatching between the second microelectronic element and the substrate (see app. par. 52)

---

6. claim: 15

Re. cl. 15 the special technical feature with respect to the not inventive subject matter of claim 1 is that there are third leads electrically connecting the contacts of the first microelectronic element to the terminals, the first leads and third leads being connected to terminals on opposite sides of the aperture, the first, second and third leads having portions aligned with the aperture.

Thus the objective problem of claim 15 to be solved can be construed as: Ensuring the first microelectronic element is connected to opposite sides of the aperture thus solving the problem of being able to connect to substrates having different electrical layouts.

---

7. claims: 16-18

Re. cl. 16 the special technical feature with respect to the

International Application No. PCT/ US2012/ 032997

**FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210**

not inventive subject matter of claim 1 is that there is a third microelectronic element disposed between the first surface of the substrate and the front surface of the second microelectronic element, the third microelectronic element having first and second opposed edges, a front surface extending between the first and second edges, and a plurality of contacts disposed on the front surface thereof adjacent the first edge thereof, the front surface of the third microelectronic element facing the first surface of the substrate; third leads electrically connecting the contacts of the third microelectronic element to the terminals; and fourth leads electrically interconnecting the contacts of the first and third microelectronic elements, the contacts of the first and third microelectronic elements being located on opposite sides of the aperture, the first, second, and third leads having portions aligned with the aperture.

Thus the objective problem of claim 16 to be solved can be construed as: Protecting a multitude of chips within the same package whilst ensuring ease of manufacturing.

---

**8. claims: 19-23**

Re. cl. 19 the special technical feature with respect to the not inventive subject matter of claim 1 is that including first and second microelectronic assemblies, each microelectronic assembly as claimed in claim 1, the first microelectronic assembly at least partially overlying the second microelectronic assembly and the first terminals of the first microelectronic assembly being joined with the second terminals of the second microelectronic assembly.

Thus the objective problem of claim 19 to be solved can be construed as: Increasing the density of the microelectronic assembly whilst maintaining the same footprint.

---

**9. claims: 27-41**

The surplus technical features of claim 27 are that third leads electrically interconnecting the contacts of the first microelectronic element with the contacts of the second microelectronic element, the third lead having portions aligned with the aperture.

Thus the objective problem of claim 27 to be solved can be construed as: How to ensure the first and second microelectronic elements can operate with each other, whilst ensuring minimal interconnect resistance is maintained.

---

**10. claims: 42-45**

The surplus technical features of claim 42 are that of third leads electrically connecting the contacts of the first microelectronic element to the terminals, the first leads

International Application No. PCT/ US2012/ 032997

FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210

and third leads being connected to terminals on opposite sides of the aperture, the third lead having portions aligned with the aperture.