(43) International Publication Date

17 September 2015 (17.09.2015)(51) International Patent Classification:

**H01L 29/49** (2006.01)    **H01L 29/78** (2006.01)

**H01L 29/66** (2006.01)(21) International Application Number:

PCT/US2015/018806(22) International Filing Date:

4 March 2015 (04.03.2015)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

61/950,681    10 March 2014 (10.03.2014)    US

14/341,568    25 July 2014 (25.07.2014)    US(71) Applicant: **QUALCOMM INCORPORATED** [US/US];

5775 Morehouse Drive, San Diego, California 92121-1714

(US).(72) Inventors: **XU, Jeffrey Junhao**; 5775 Morehouse Drive,

San Diego, California 92121 (US). **RIM, Kern**; 5775Morehouse Drive, San Diego, California 92121 (US).

**ZHU, John Jianhong**; 5775 Morehouse Drive, San Diego, California 92121 (US). **SONG, Stanley Seungchul**; 5775 Morehouse Drive, San Diego, California 92121 (US).

**BADAROGLU, Mustafa**; 5775 Morehouse Drive, San Diego, California 92121 (US). **MACHKAOUTSAN, Vladimir**; 5775 Morehouse Drive, San Diego, California 92121 (US). **YANG, Da**; 5775 Morehouse Drive, San Diego, California 92121 (US). **YEAP, Choh Fei**; 5775 Morehouse Drive, San Diego, California 92121 (US).(74) Agent: **TOLER, Jeffrey G.**; 8500 Bluffstone Cove, Suite A201, Austin, Texas 78759 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG,

[Continued on next page]

(54) Title: SEMICONDUCTOR DEVICE HAVING A GAP DEFINED THEREIN

FIG. 1A

**(57) Abstract:** In a particular embodiment, a method includes forming a first spacer structure on a dummy gate of a semiconductor device and forming a sacrificial spacer on the first spacer structure. The method also includes etching a structure of the semiconductor device to create an opening, removing the sacrificial spacer via the opening, and depositing a material to close to define a gap.

FIG. 1B

MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) **Designated States** (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

**Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

**Published:**

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

**SEMICONDUCTOR DEVICE HAVING A GAP DEFINED THEREIN*****I. Claim of Priority***

[0001] The present application claims priority from commonly owned U.S. Provisional Pat. App. No. 61/950,681 filed March 10, 2014, and U.S. Non-Provisional Patent Application No. 14/341,568 filed July 25, 2014, the contents of which are expressly incorporated herein by reference in their entirety..

***II. Field***

[0002] The present disclosure is generally related to a semiconductor device having a gap defined therein.

***III. Description of Related Art***

[0003] Advances in technology have resulted in smaller apparatuses and more powerful computing devices. For example, there currently exist a variety of portable personal computing devices, including wireless computing devices, such as portable wireless telephones, personal digital assistants (PDAs), and paging devices that are small, lightweight, and easily carried by users. More specifically, portable wireless telephones, such as cellular telephones and internet protocol (IP) telephones, can communicate voice and data packets over wireless networks. Further, many such wireless telephones include other types of devices that are incorporated therein. For example, a wireless telephone can also include a digital still camera, a digital video camera, a digital recorder, and an audio file player. Also, such wireless telephones can process executable instructions, including software applications, such as a web browser application, that can be used to access the Internet. As such, these wireless telephones can include significant computing capabilities.

[0004] Portable personal computing devices, such as wireless computing devices, may include a semiconductor device, such as a fin field-effect transistor (FinFET) device. The FinFET device may be formed with one or more fins. When a FinFET device includes a single fin, a shape of the fin may limit a drive strength (e.g., a current, such as an alternating current) of the FinFET to a relatively low level. To enable higher drive strengths, a FinFET device may be formed with multiple fins. However, the multiple

- 2 -

fins may introduce parasitic capacitances that restrict (e.g., limit) alternating current performance of the FinFET device.

#### ***IV. Summary***

**[0005]** The present disclosure provides a semiconductor device having a gap (e.g., an air gap and/or a vacuum gap) defined therein. For example, a source/drain region of the semiconductor device may define the gap. A method of forming the semiconductor device, such as a FinFET device, may include depositing a first spacer material on a dummy gate (e.g., a sidewall of the dummy gate) of the semiconductor device. The method may also include depositing a sacrificial spacer on the first spacer material and depositing a second spacer material on the sacrificial spacer. The second spacer material may be in contact with the first spacer material. The method may further include removing the sacrificial spacer between the first spacer material and the second spacer material to create a cavity (having an opening) between the first spacer material and the second spacer material. For example, the sacrificial spacer material may be removed (e.g., etched) through the opening. The method may include filling the opening to establish a gap that is defined by a portion of the first spacer material and by a portion of the second spacer material. The opening may be filled (e.g., closed) with a third spacer material (e.g., a spacer cap) or a source/drain region material. The gap may be defined by a source/drain region of the semiconductor device. Additionally, the gap may be defined by the first spacer material, the second spacer material, the third spacer material, a substrate (e.g., a fin) of the semiconductor device, or a combination thereof, as illustrative, non-limiting examples. A height of the gap may be less than a height of a gate of the semiconductor device. The gap may enable a reduced parasitic capacitance and may increase a drive strength of the semiconductor device as compared to semiconductor devices that do not include a gap.

**[0006]** In a particular embodiment, a method includes forming a first spacer structure on a dummy gate of a semiconductor device and forming a sacrificial spacer on the first spacer structure. The method also includes etching a structure of the semiconductor device to create an opening, removing the sacrificial spacer through the opening and depositing a material to close the opening to define a gap.

**[0007]** In another particular embodiment, a semiconductor device includes a gate, a

- 3 -

contact, and a source/drain region. The source/drain region is electrically coupled to the contact and defines a gap positioned between the gate and the contact. A height of the gap is less than a height of the gate.

[0008] In another particular embodiment, a non-transitory computer-readable medium includes instructions that, when executed by a processor, cause the processor to initiate formation of a semiconductor device. The semiconductor device formed by forming a first spacer structure on a dummy gate of a semiconductor device and by forming a sacrificial spacer on the first spacer structure. The semiconductor device is further formed by etching a structure to create an opening. The semiconductor device is further formed by removing the sacrificial spacer through the opening and by depositing a material to close the opening to define a gap.

[0009] In another particular embodiment, an apparatus includes means for activating a channel region of a semiconductor device. The channel region is coupled to a source/drain region of the semiconductor device. The apparatus further includes means for conducting current, the means for conducting coupled to the source/drain region. The source/drain region defines a gap positioned between the means for activating and the means for conducting. A height of the gap is less than a height of the means for activating the channel region.

[0010] One particular advantage provided by at least one of the disclosed embodiments is reduced parasitic capacitance (e.g., a gate capacitance) and an AC performance improvement as compared to devices (e.g., FinFETs) that do not have a defined gap. Another particular advantage provided by at least one of the disclosed embodiments is that a FinFET transistor delay time may be reduced and/or a switch energy may be reduced as compared to FinFET devices that do not have a defined gap.

[0011] Other aspects, advantages, and features of the present disclosure will become apparent after review of the entire application, including the following sections: Brief Description of the Drawings, Detailed Description, and the Claims.

#### ***V. Brief Description of the Drawings***

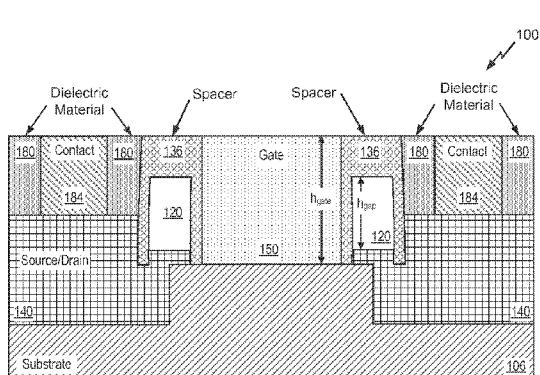

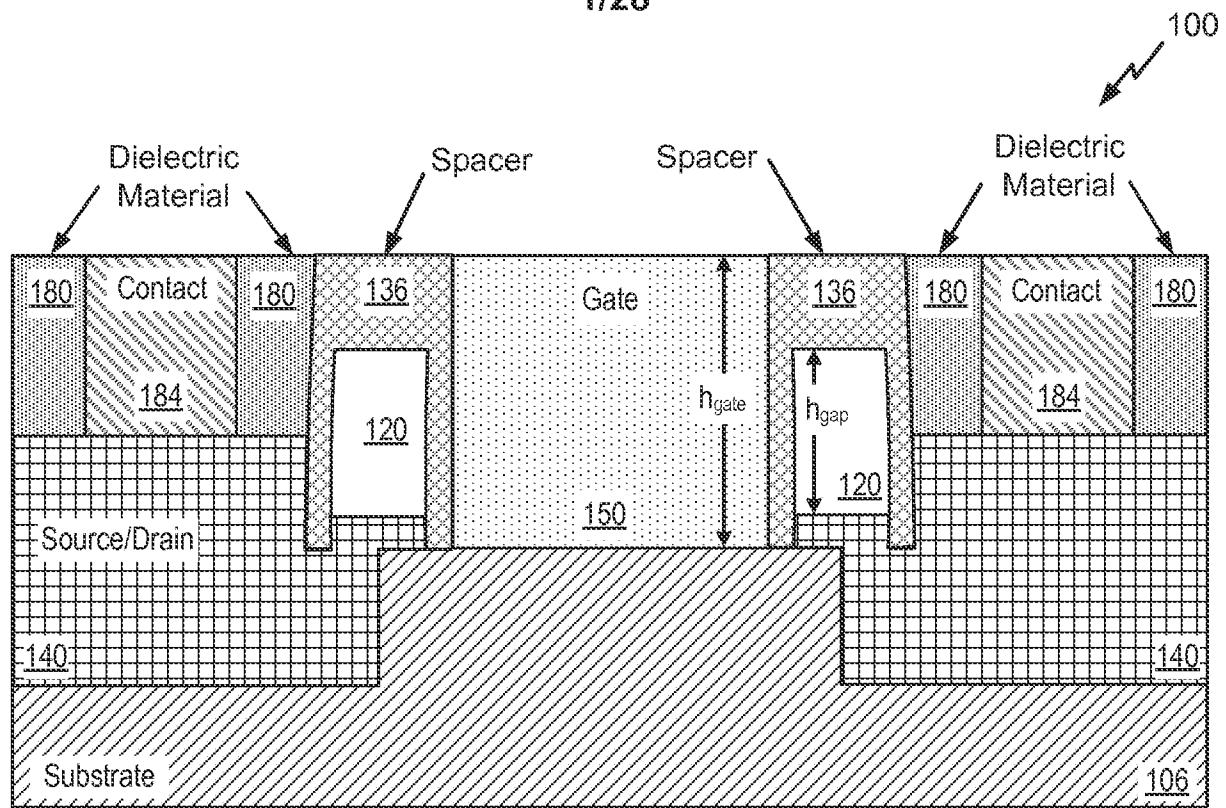

[0012] FIG. 1A is a diagram of a partial view of a first semiconductor device including a source/drain region that defines a gap;

- 4 -

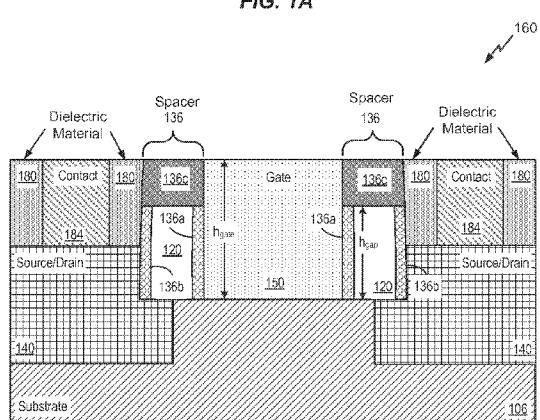

[0013] FIG. 1B is a diagram of a partial view of a second semiconductor device including a source/drain region that defines a gap;

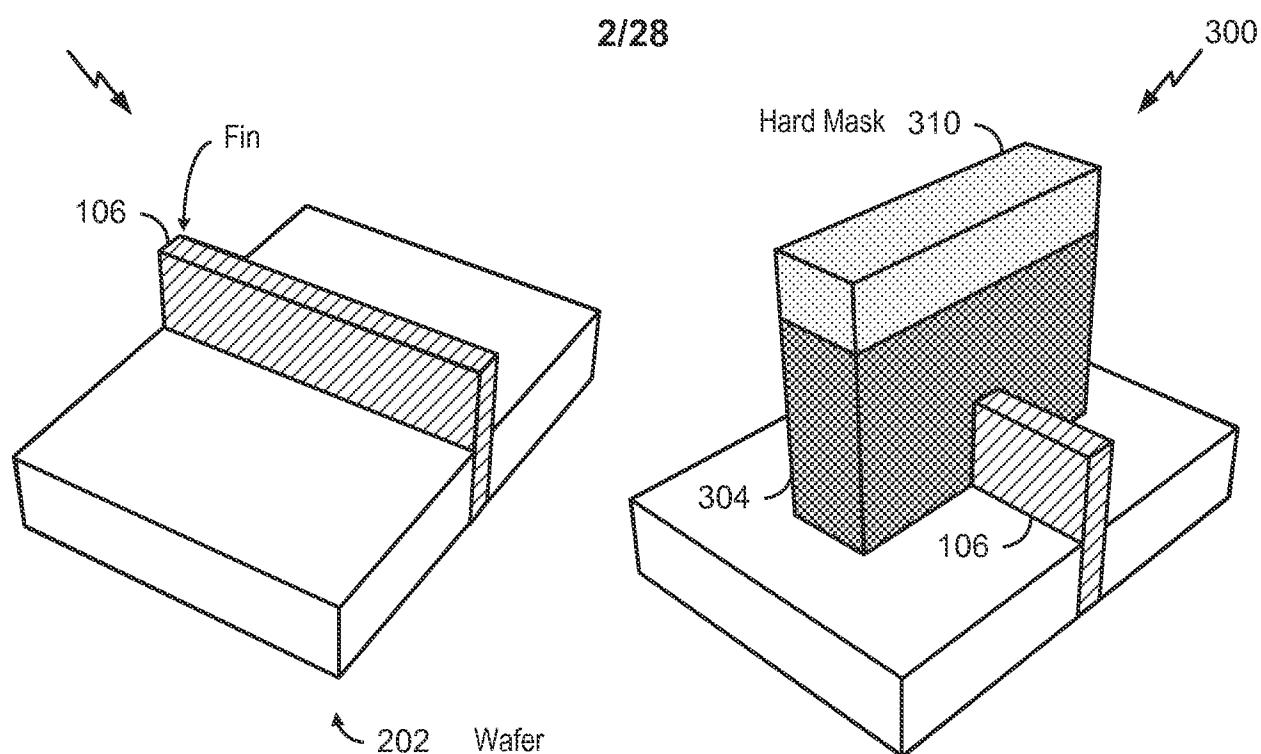

[0014] FIG. 2 is a first illustrative diagram of at least one stage of a first process of fabricating a semiconductor device including a source/drain region that defines a gap;

[0015] FIG. 3 is a second illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a hardmask on a dummy gate;

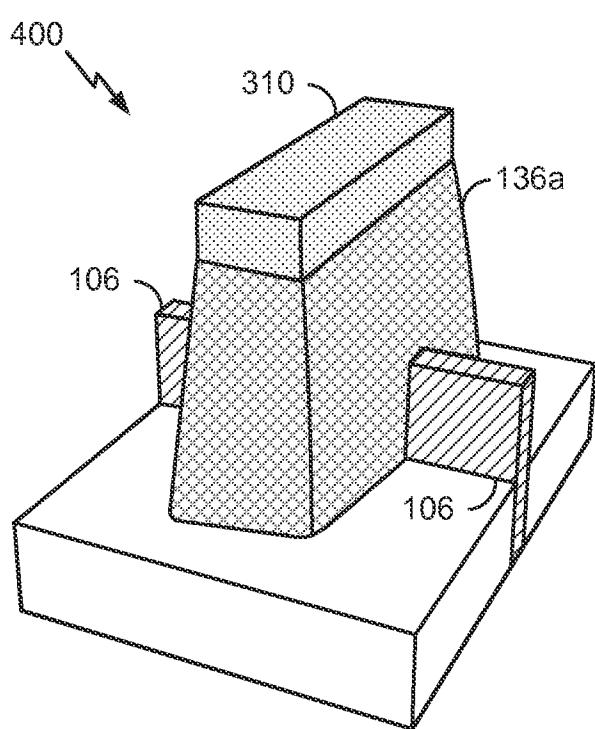

[0016] FIG. 4 is a third illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a first spacer structure;

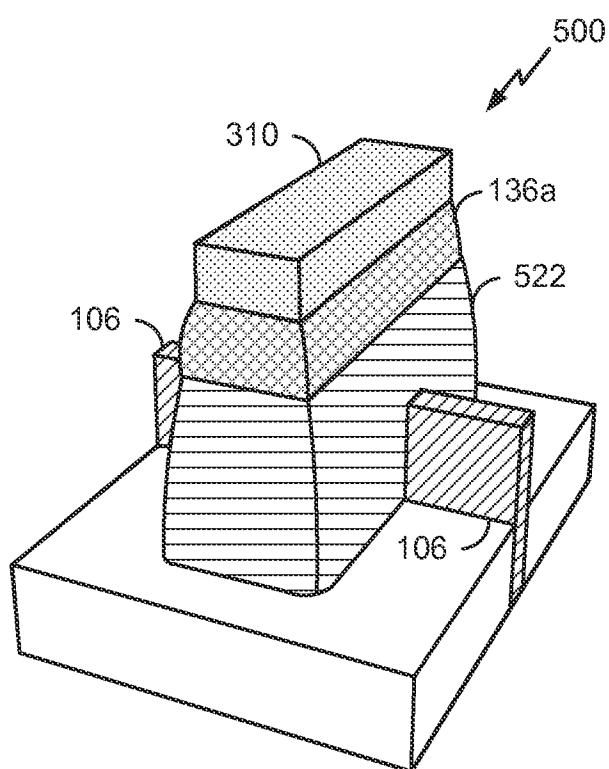

[0017] FIG. 5 is a fourth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a sacrificial spacer;

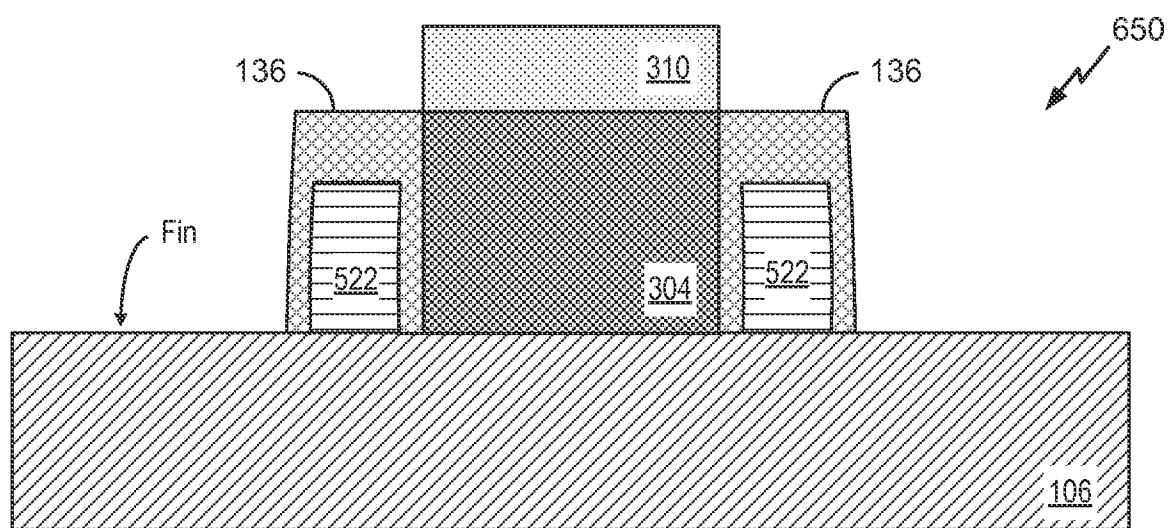

[0018] FIG. 6 is a fifth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a second spacer structure;

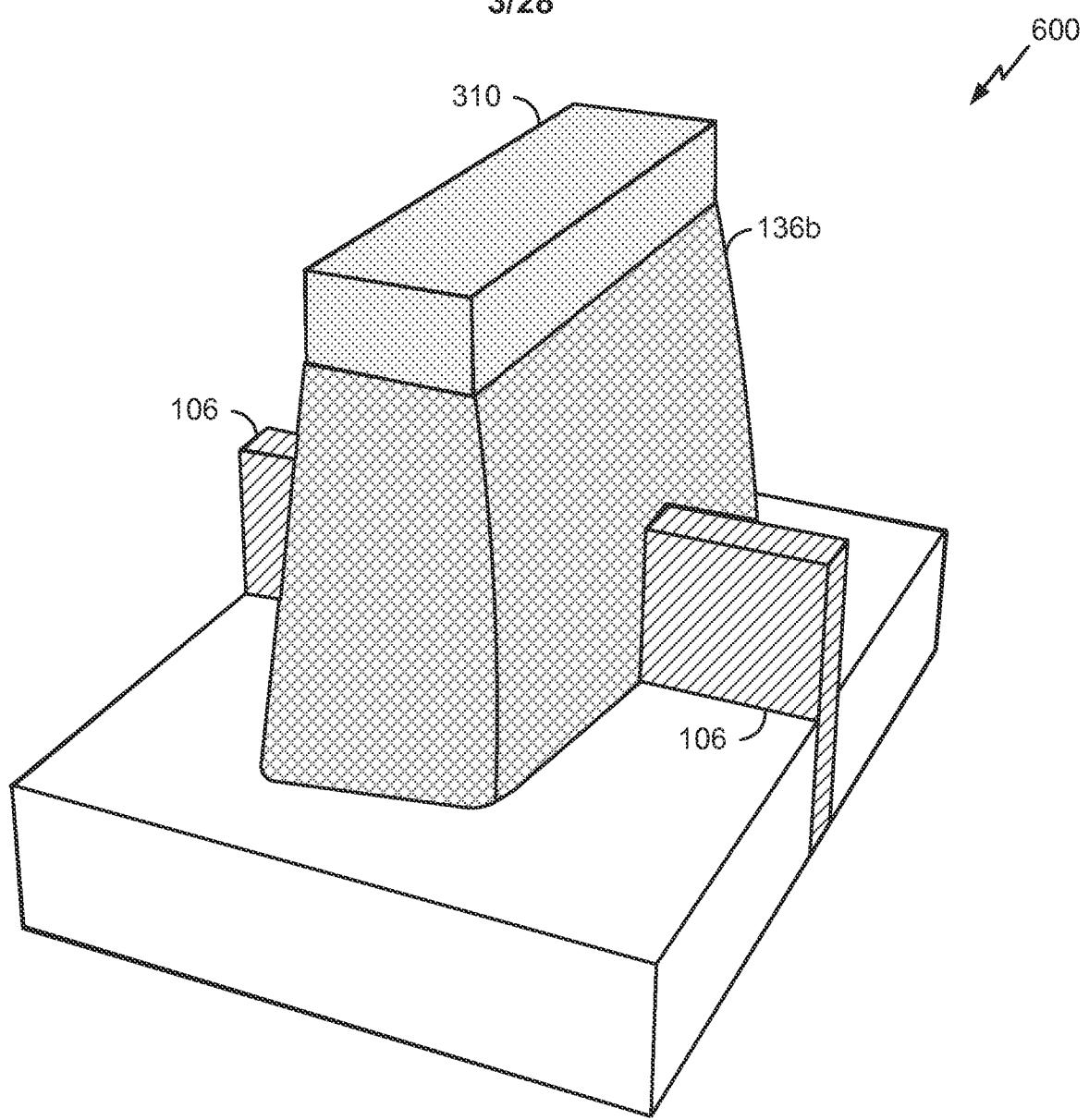

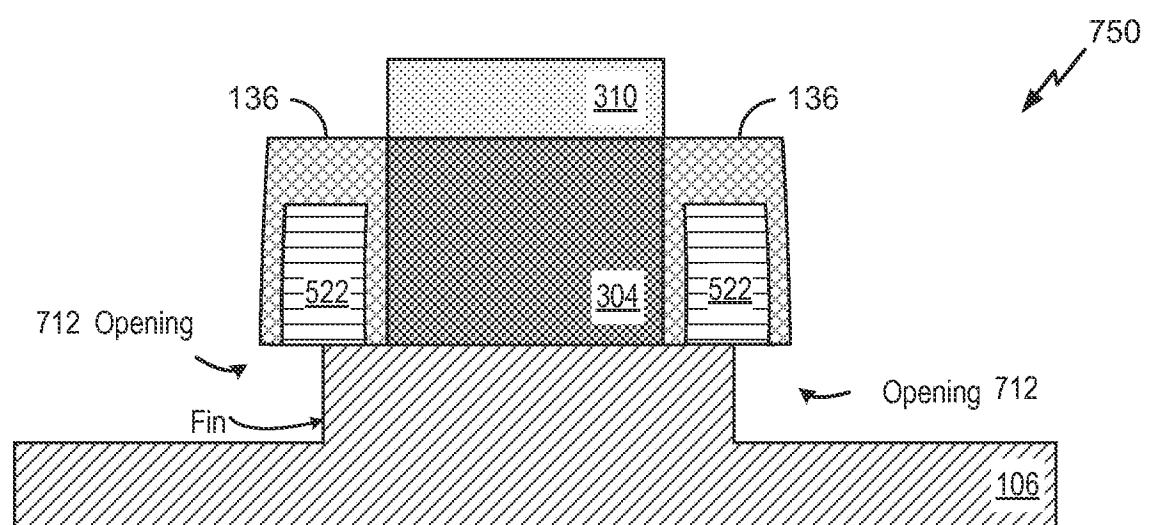

[0019] FIG. 7 is a sixth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after removing a portion of a fin of the semiconductor device;

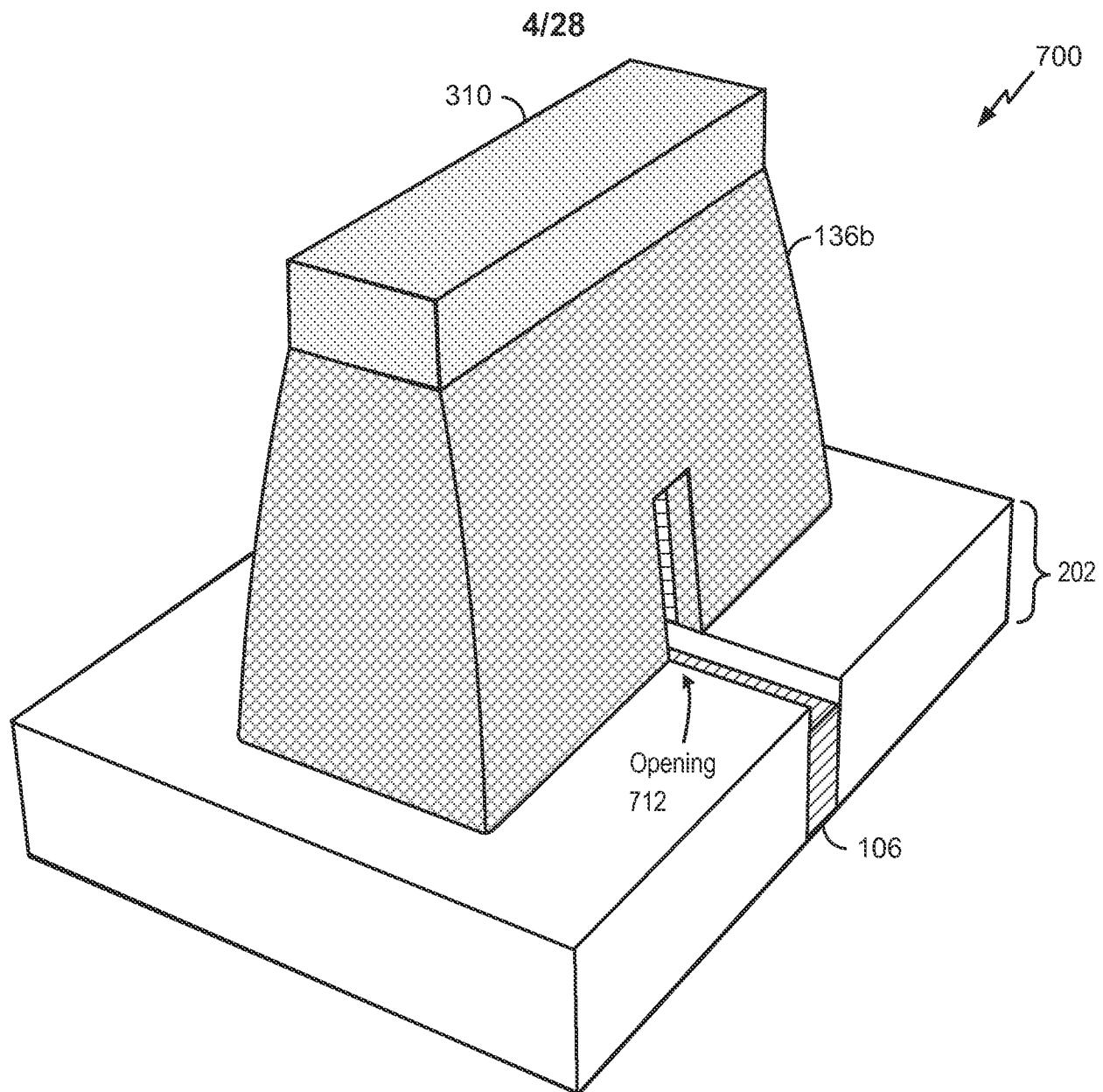

[0020] FIG. 8 is a seventh illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after removing the sacrificial spacer;

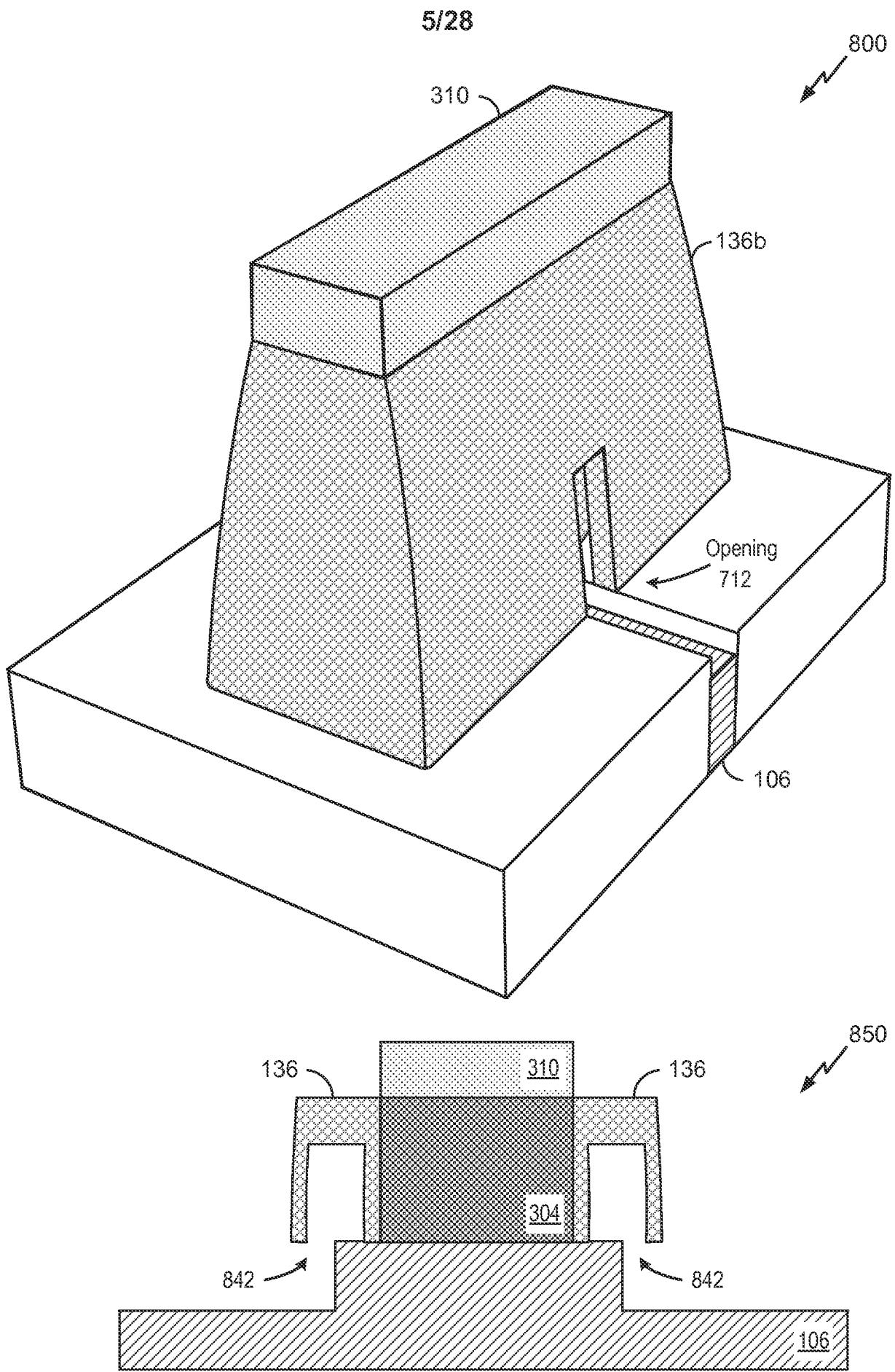

[0021] FIG. 9 is an eighth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a source/drain region;

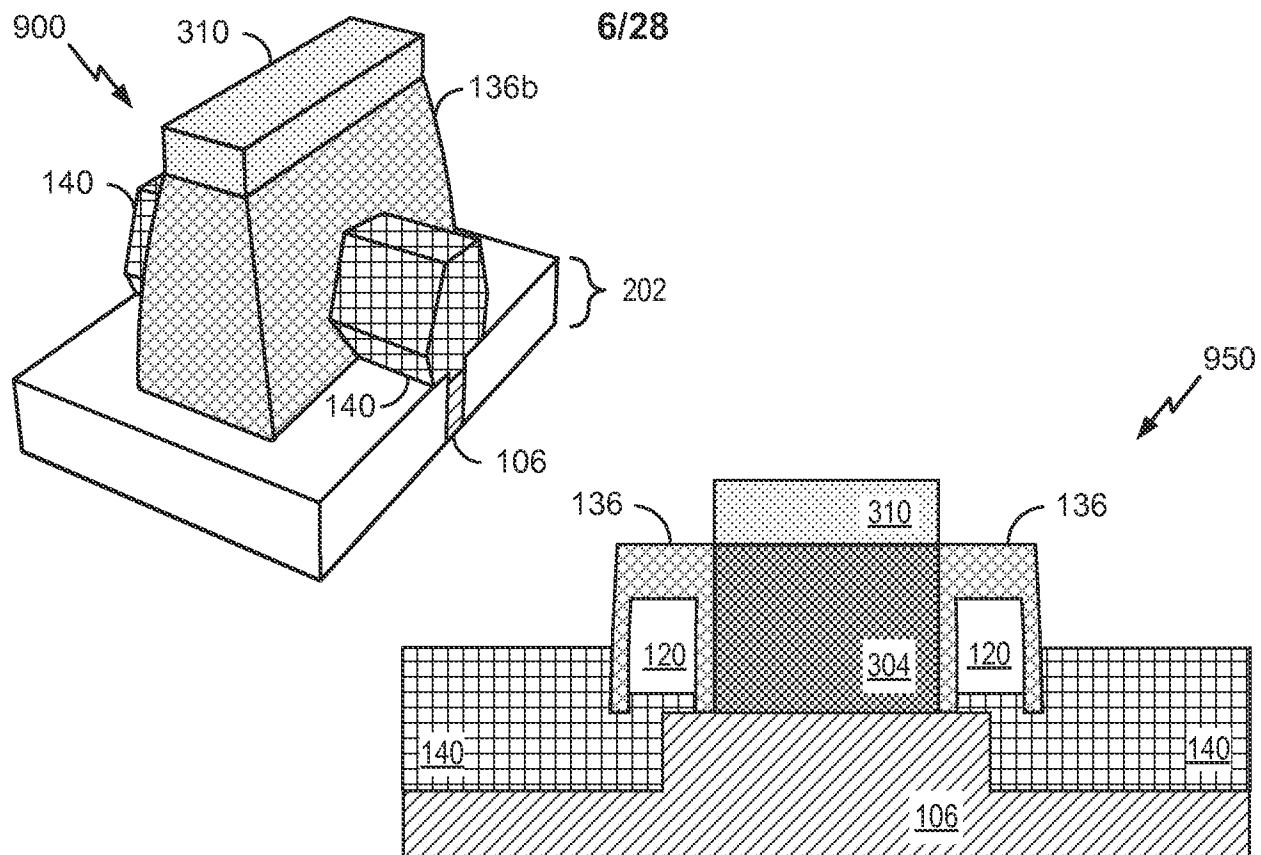

[0022] FIG. 10 is a ninth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after a dielectric material is deposited and after planarization is performed;

[0023] FIG. 11 is a tenth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after the dummy gate is removed;

[0024] FIG. 12 is an eleventh illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a gate;

- 5 -

[0025] FIG. 13 is a twelfth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a cavity;

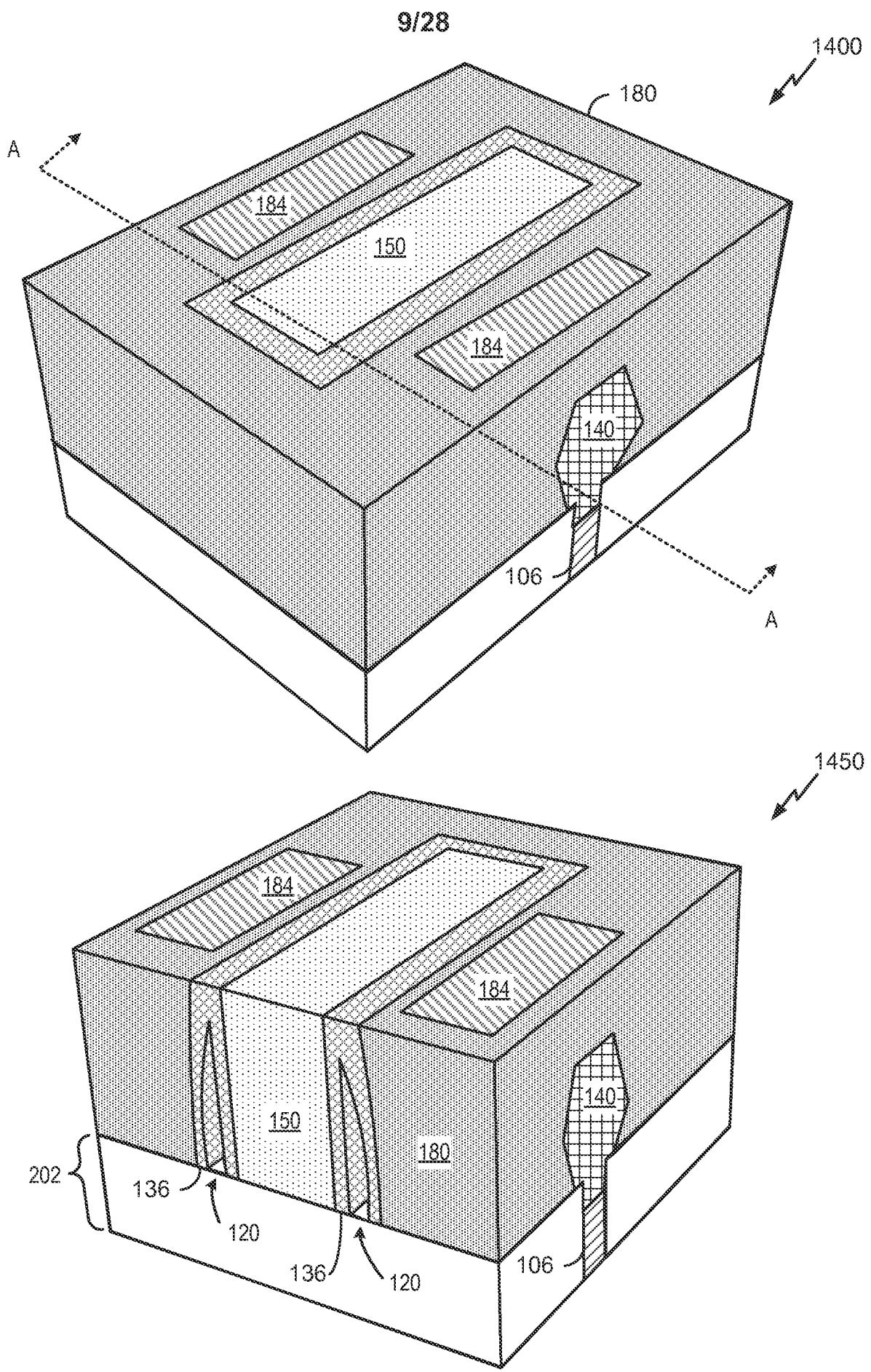

[0026] FIG. 14 is a thirteenth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a contact;

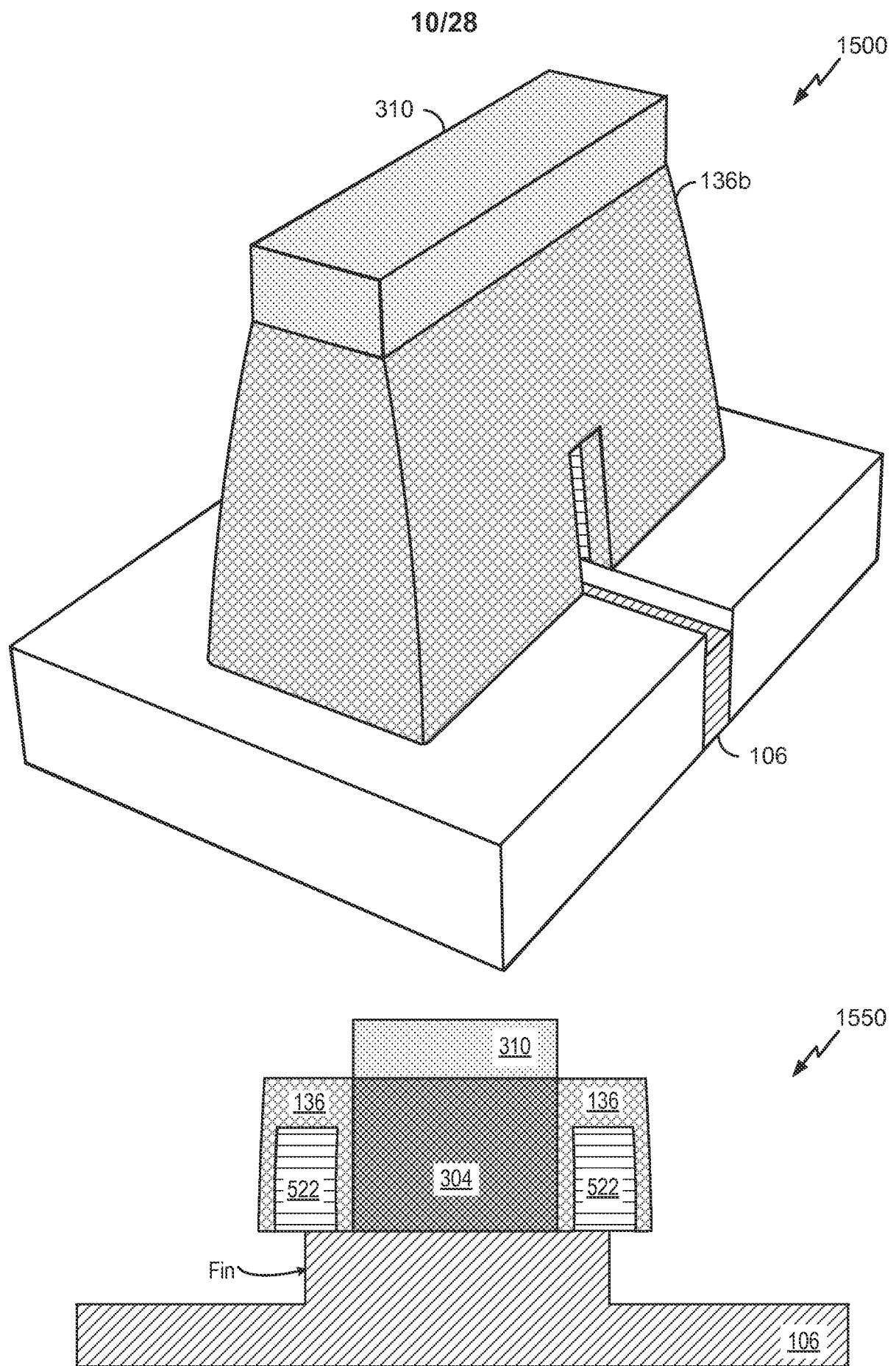

[0027] FIG. 15 is a first illustrative diagram of at least one stage of the second process of fabricating a semiconductor device after removing a portion of a fin of the semiconductor device;

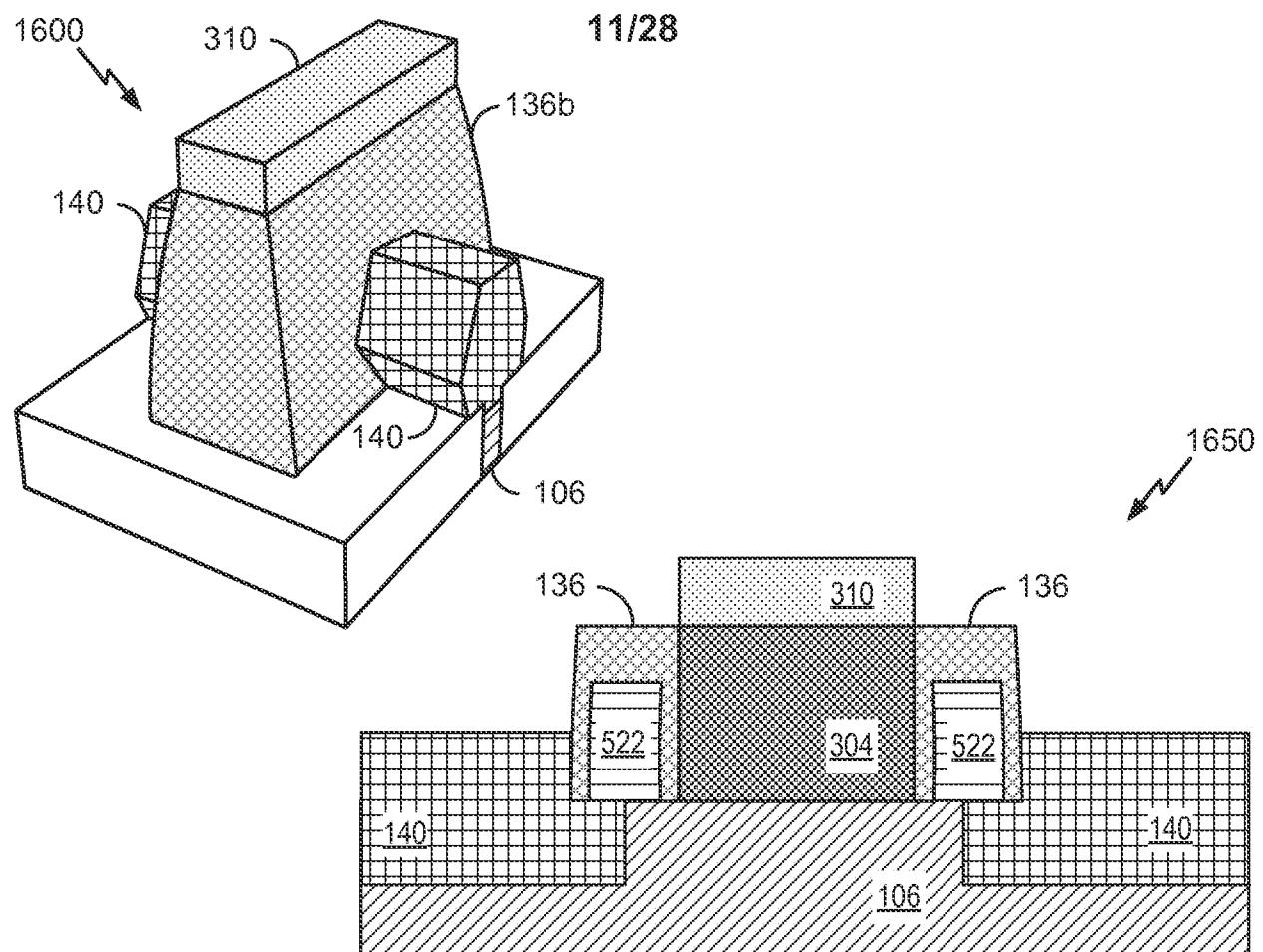

[0028] FIG. 16 is a second illustrative diagram of at least one stage of the second process of fabricating a semiconductor device after forming a source/drain region;

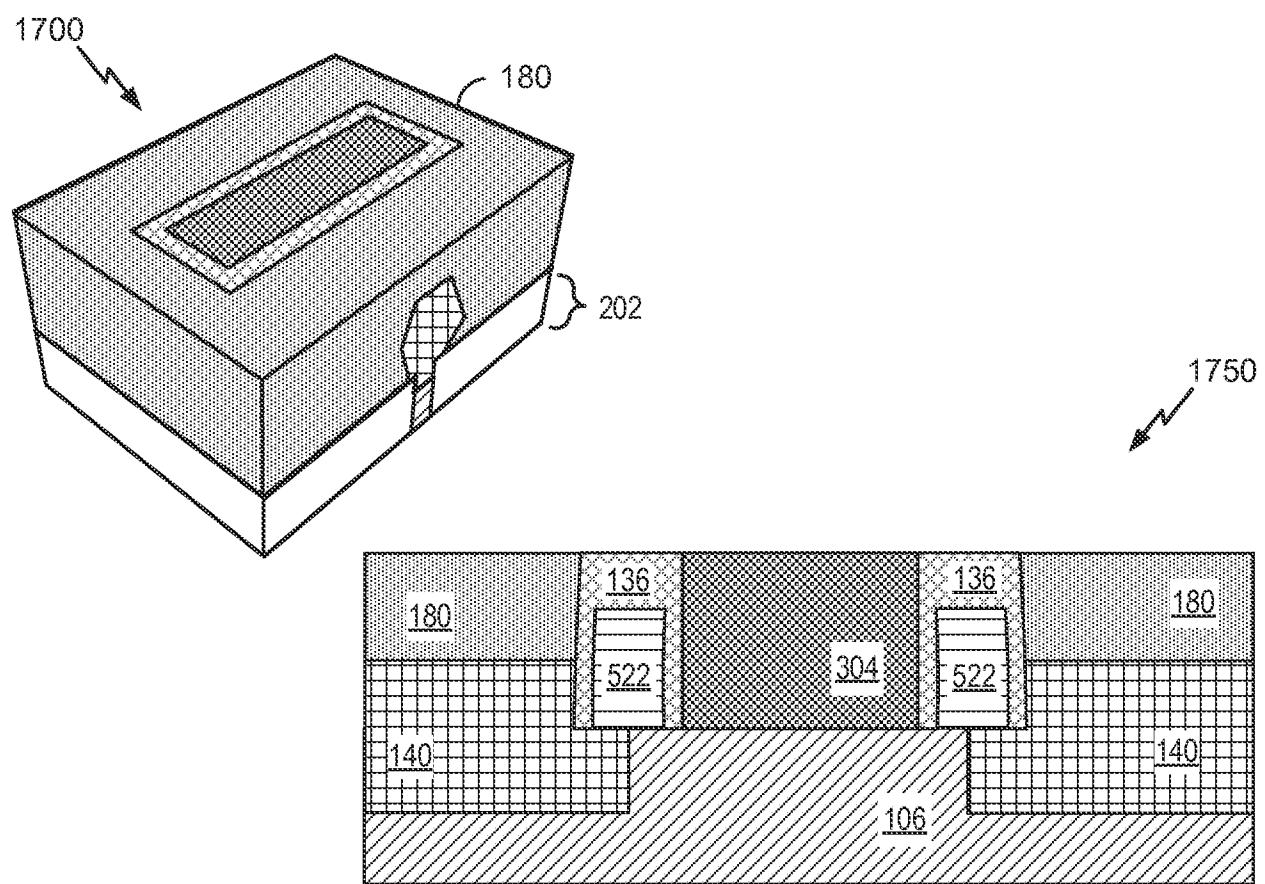

[0029] FIG. 17 is a third illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after a dielectric material is deposited and after planarization is performed;

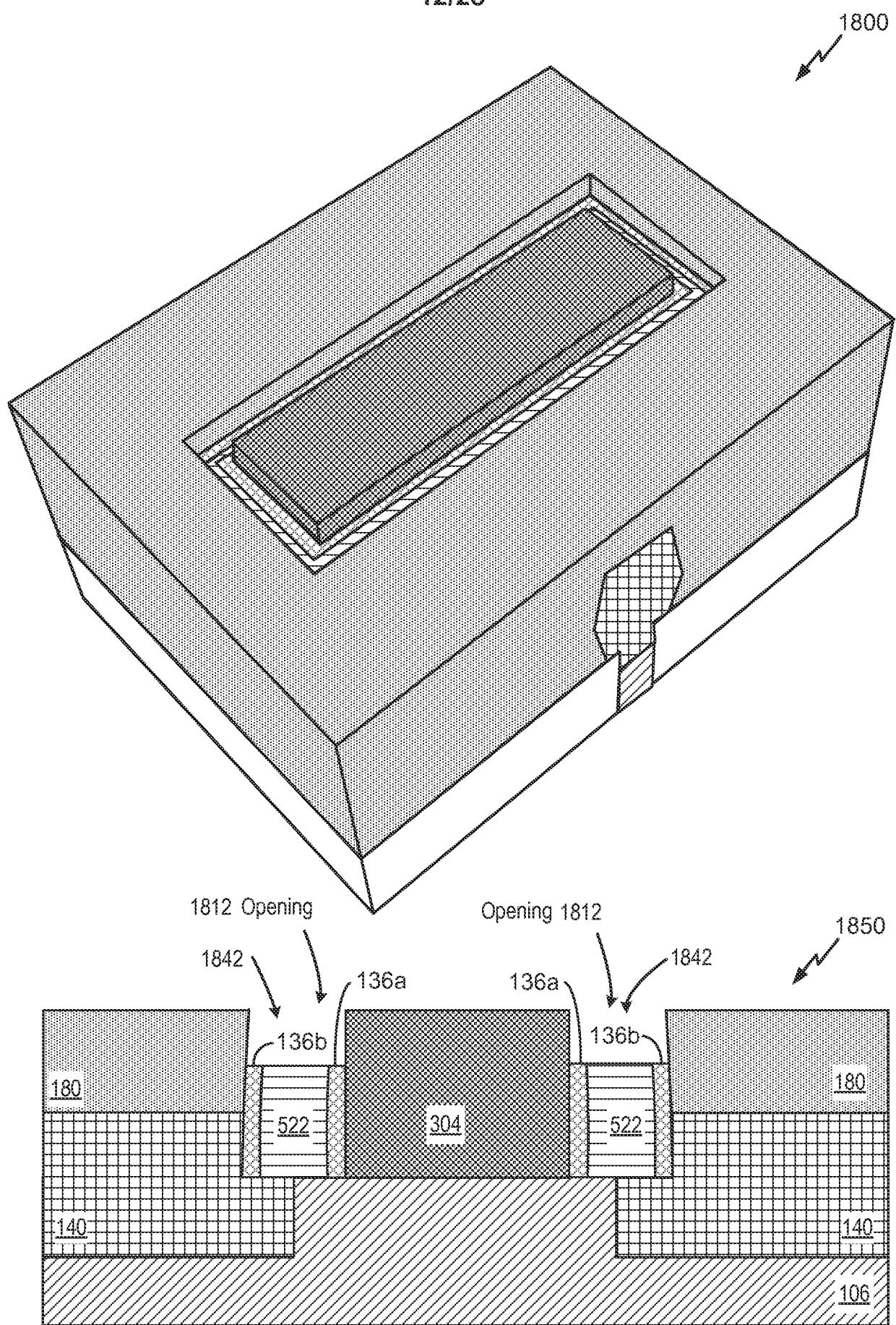

[0030] FIG. 18 is a fourth illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after exposing a portion of a sacrificial spacer;

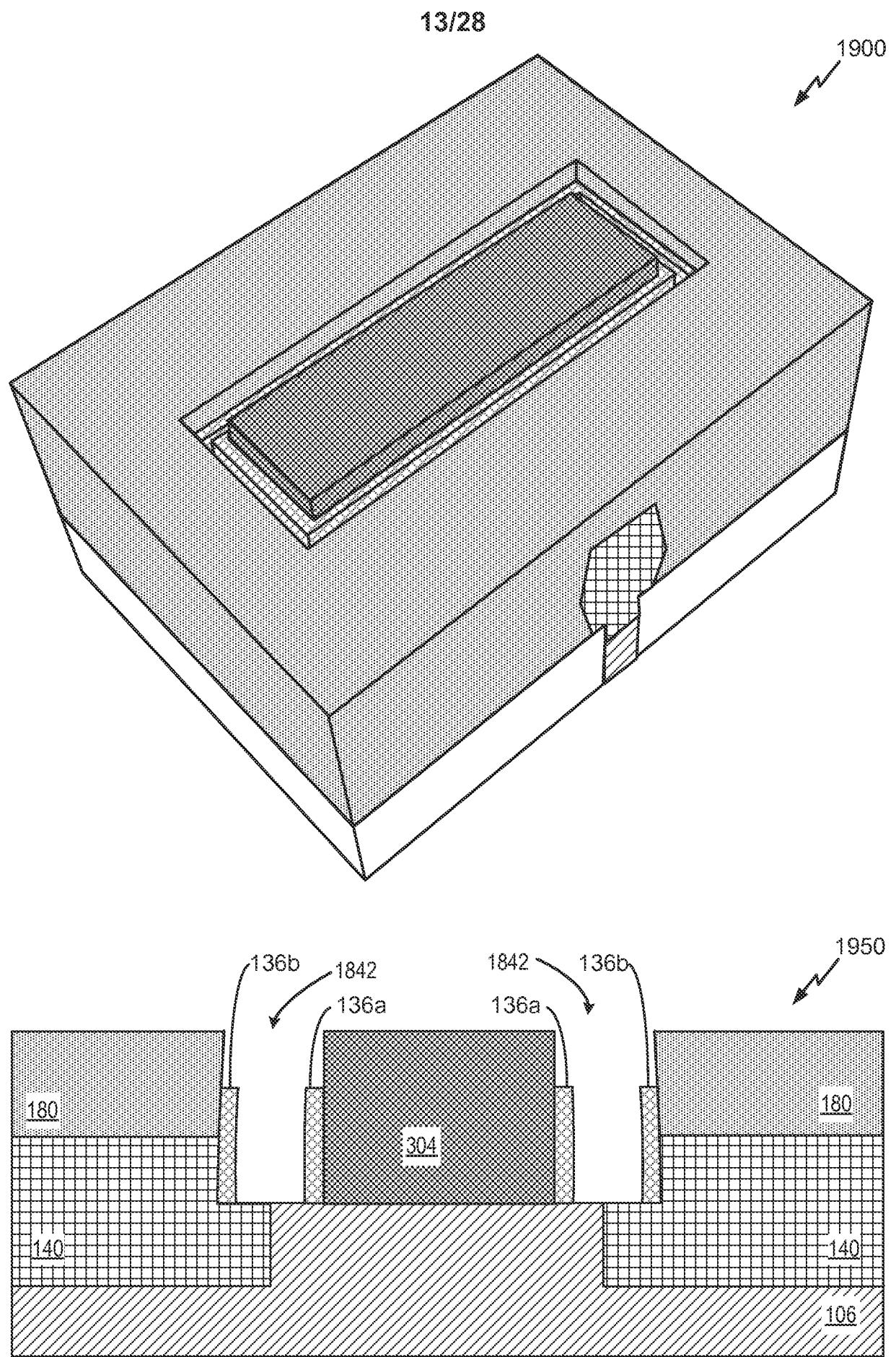

[0031] FIG. 19 is a fifth illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after removing a sacrificial spacer;

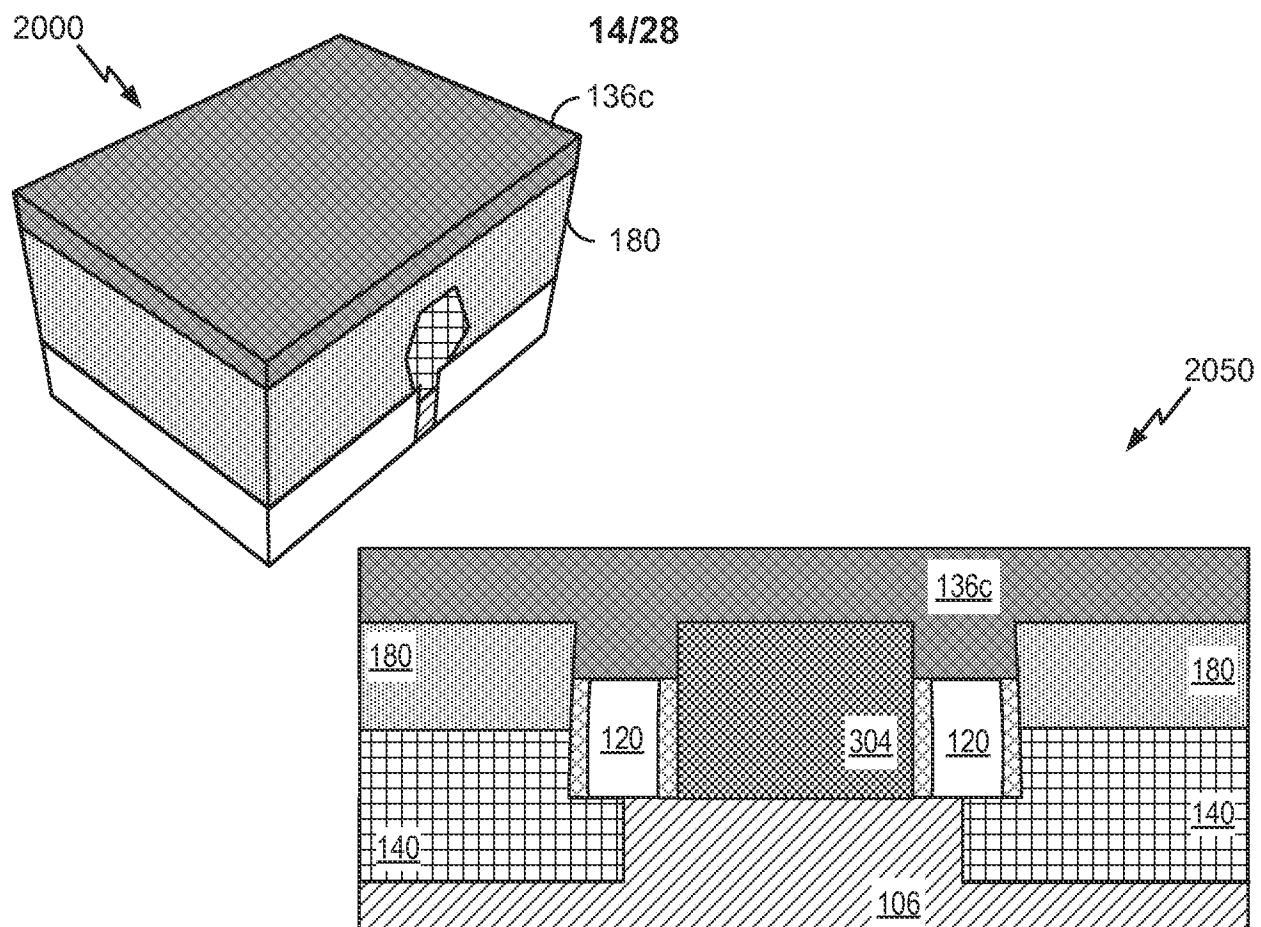

[0032] FIG. 20 is a sixth illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after forming a third spacer material;

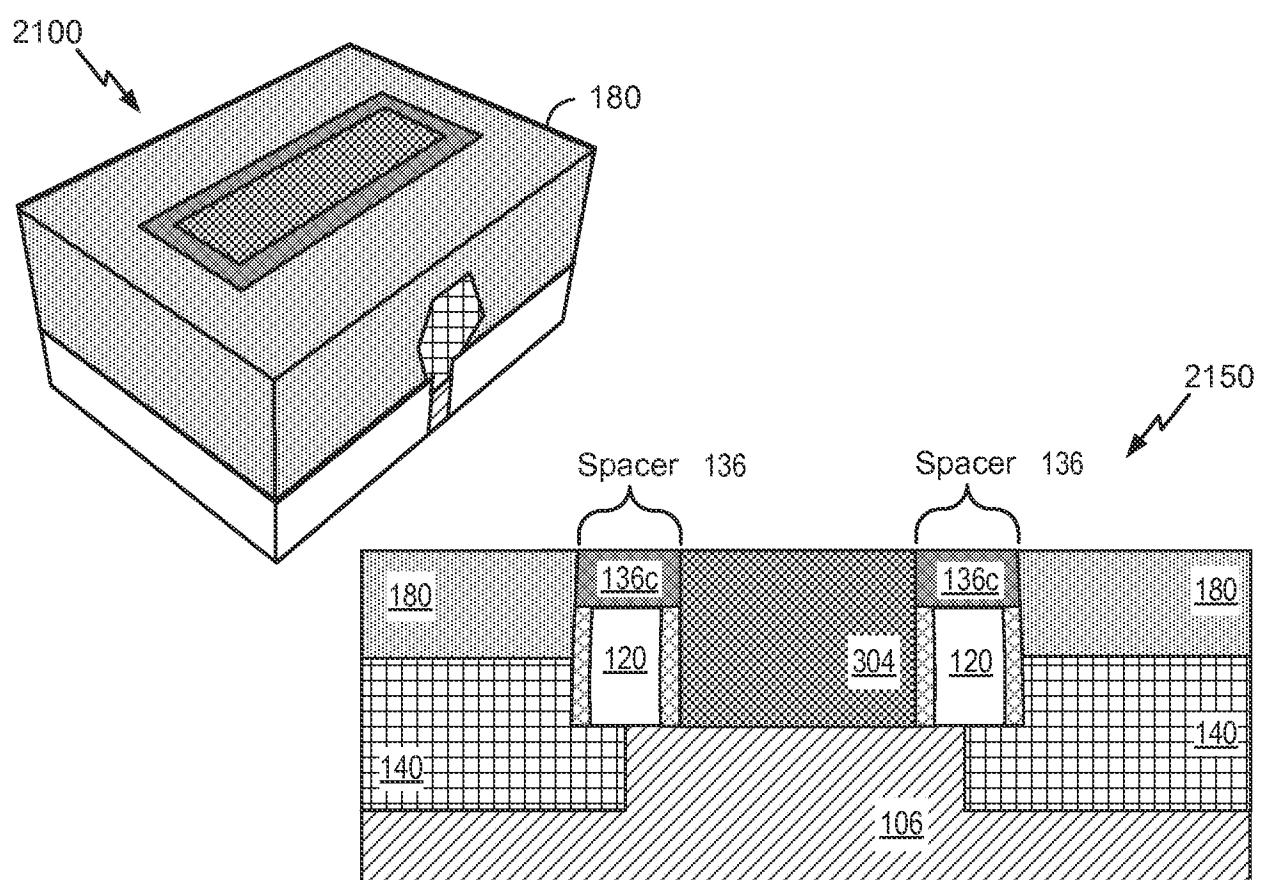

[0033] FIG. 21 is a seventh illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after planarization is performed;

[0034] FIG. 22 is an eighth illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after a dummy gate is removed;

[0035] FIG. 23 is a ninth illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after forming a gate;

[0036] FIG. 24 is a tenth illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after forming a cavity;

- 6 -

[0037] FIG. 25 is an eleventh illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after forming a contact;

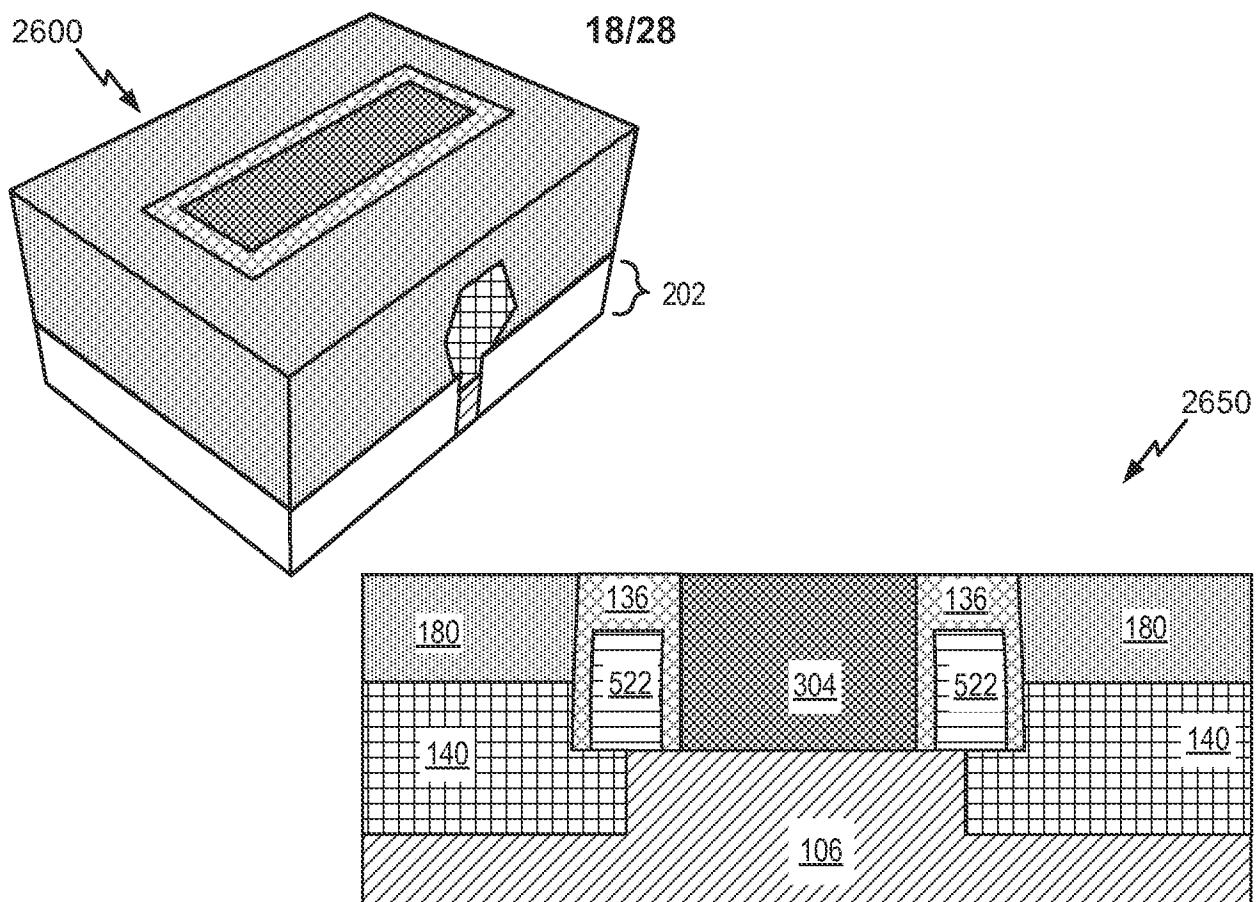

[0038] FIG. 26 is a first illustrative diagram of at least one stage of a third process of fabricating a semiconductor device that includes a source/drain region that defines a gap;

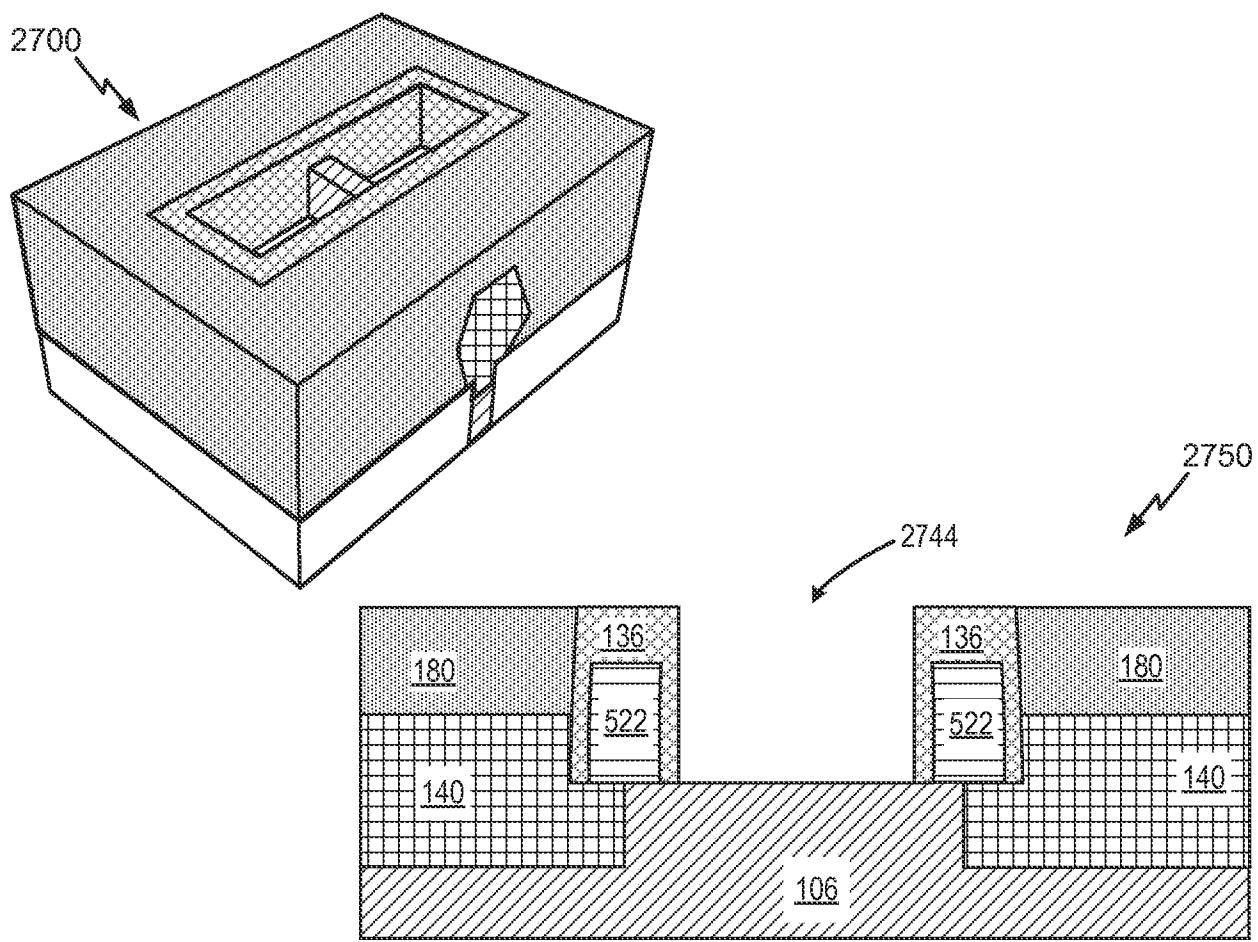

[0039] FIG. 27 is a second illustrative diagram of at least one stage of the third process of fabricating the semiconductor device after a dummy gate is removed;

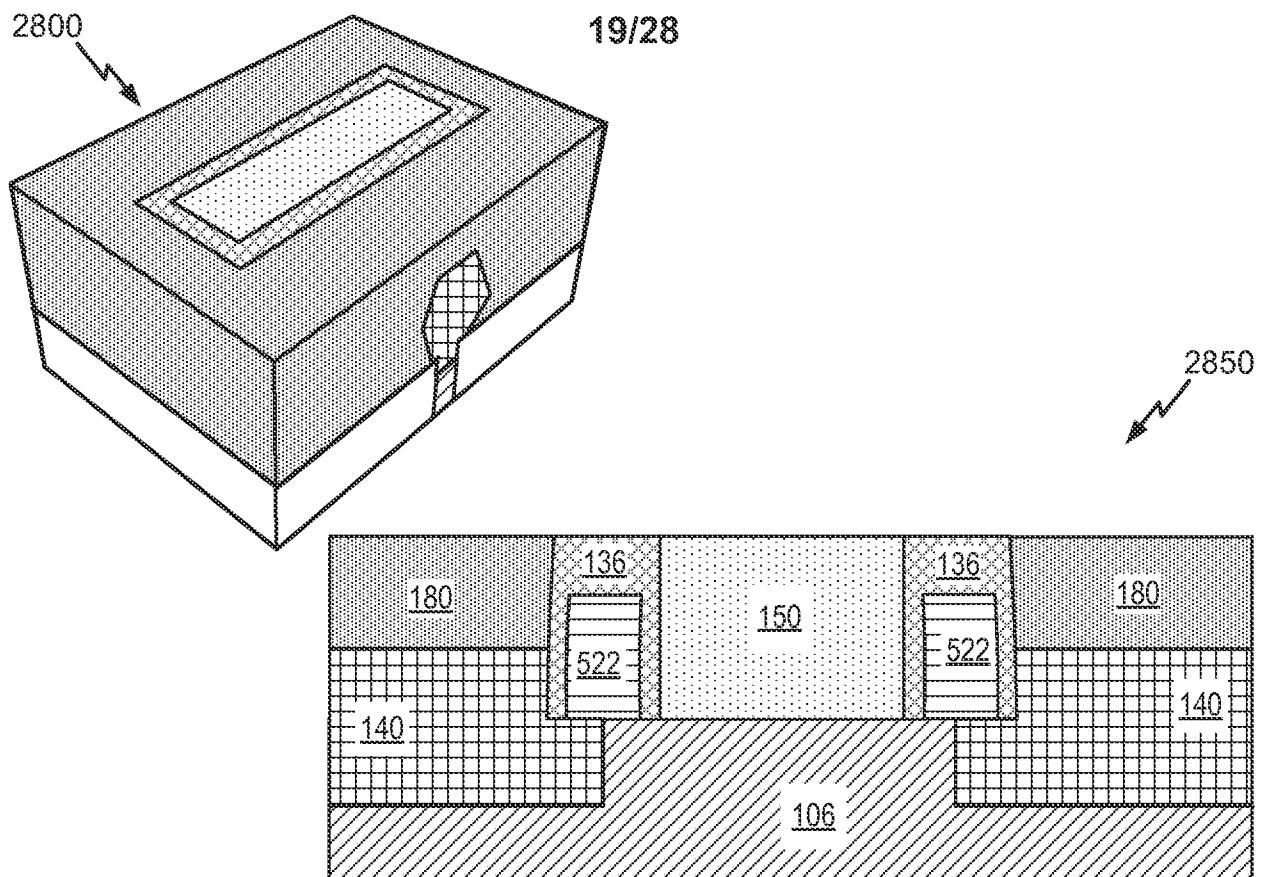

[0040] FIG. 28 is a third illustrative diagram of at least one stage of the third process of fabricating the semiconductor device after forming a gate;

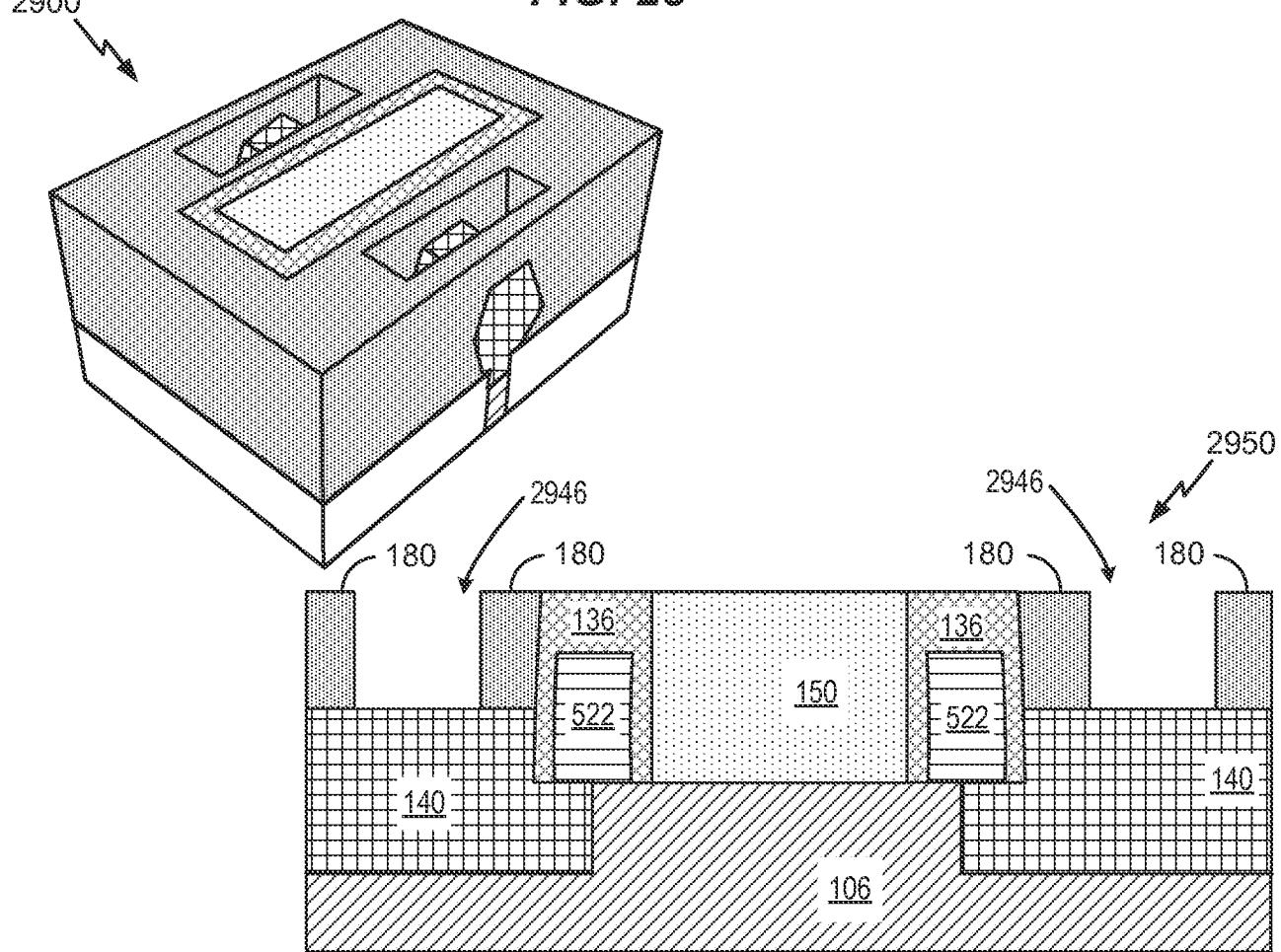

[0041] FIG. 29 is a fourth illustrative diagram of at least one stage of the third process of fabricating the semiconductor device after forming a cavity;

[0042] FIG. 30 is a fifth illustrative diagram of at least one stage of the third process of fabricating the semiconductor device after forming a contact;

[0043] FIG. 31 is a sixth illustrative diagram of at least one stage of the third process of fabricating the semiconductor device after exposing a portion of a sacrificial spacer;

[0044] FIG. 32 is a seventh illustrative diagram of at least one stage of the third process of fabricating the semiconductor device after removing the sacrificial spacer;

[0045] FIG. 33 is an eighth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a third spacer material and after planarization is performed;

[0046] FIG. 34 is a flow diagram of an illustrative embodiment of a method of forming the semiconductor device of FIGS. 1A-B;

[0047] FIG. 35 is a flow diagram of a first illustrative embodiment of a method of forming the semiconductor device of FIG. 1B;

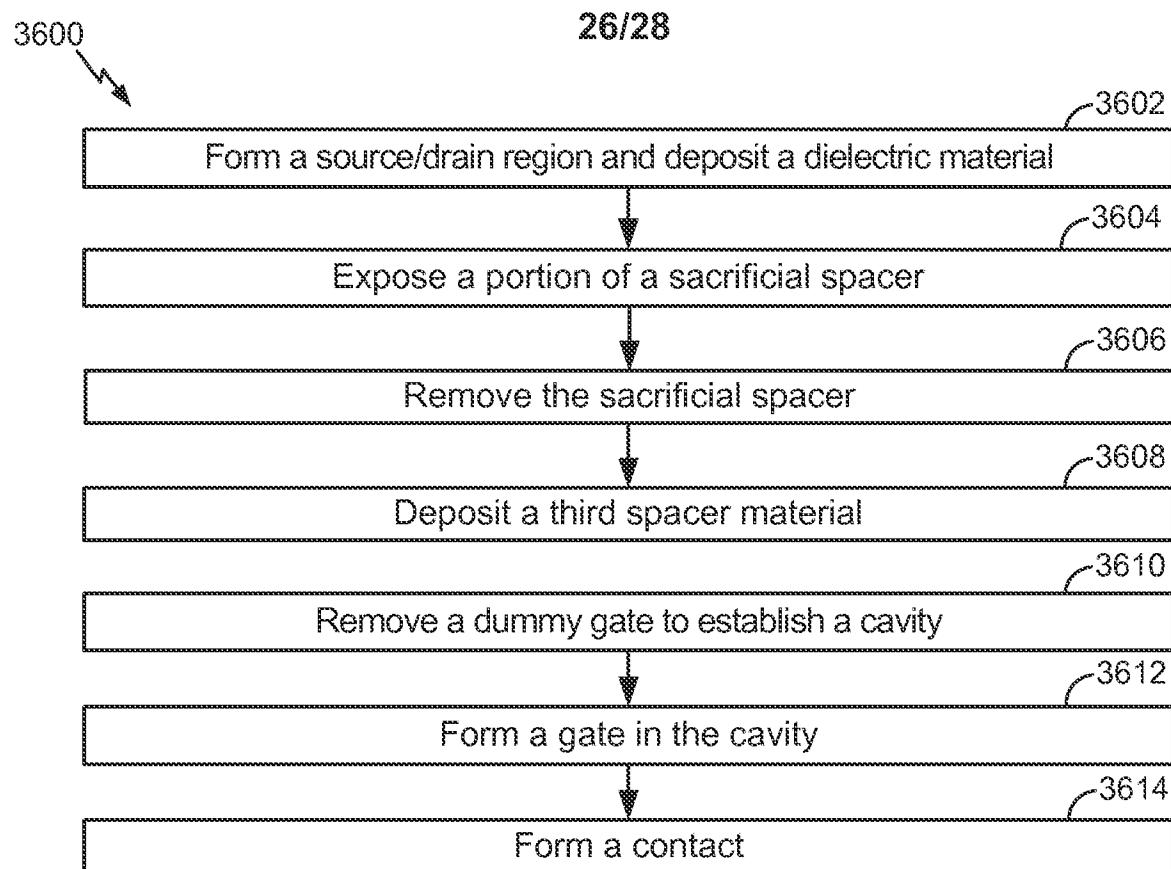

[0048] FIG. 36 is a flow diagram of a second illustrative embodiment of a method of forming the semiconductor device of FIG. 1B;

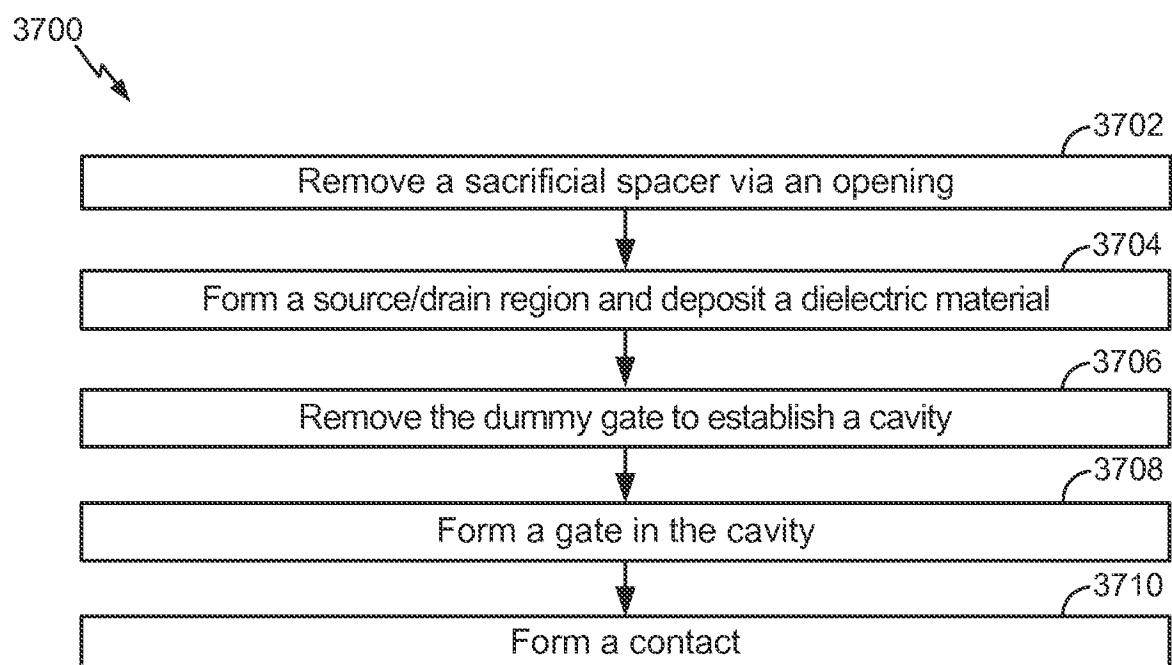

[0049] FIG. 37 is a flow diagram of an illustrative embodiment of a method of forming the semiconductor device of FIG. 1A;

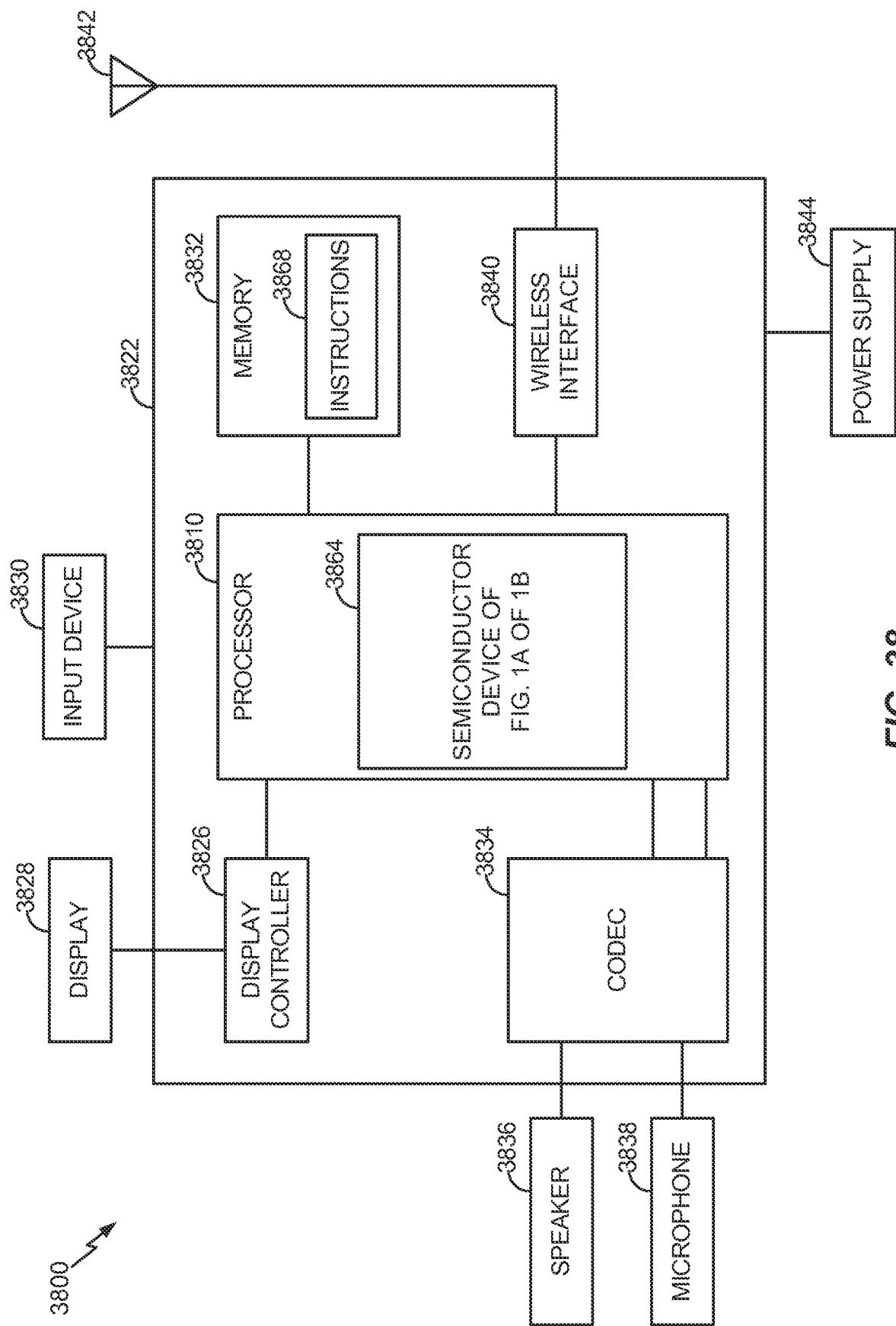

[0050] FIG. 38 is a block diagram of a device including the semiconductor device of FIG. 1A or FIG. 1B; and

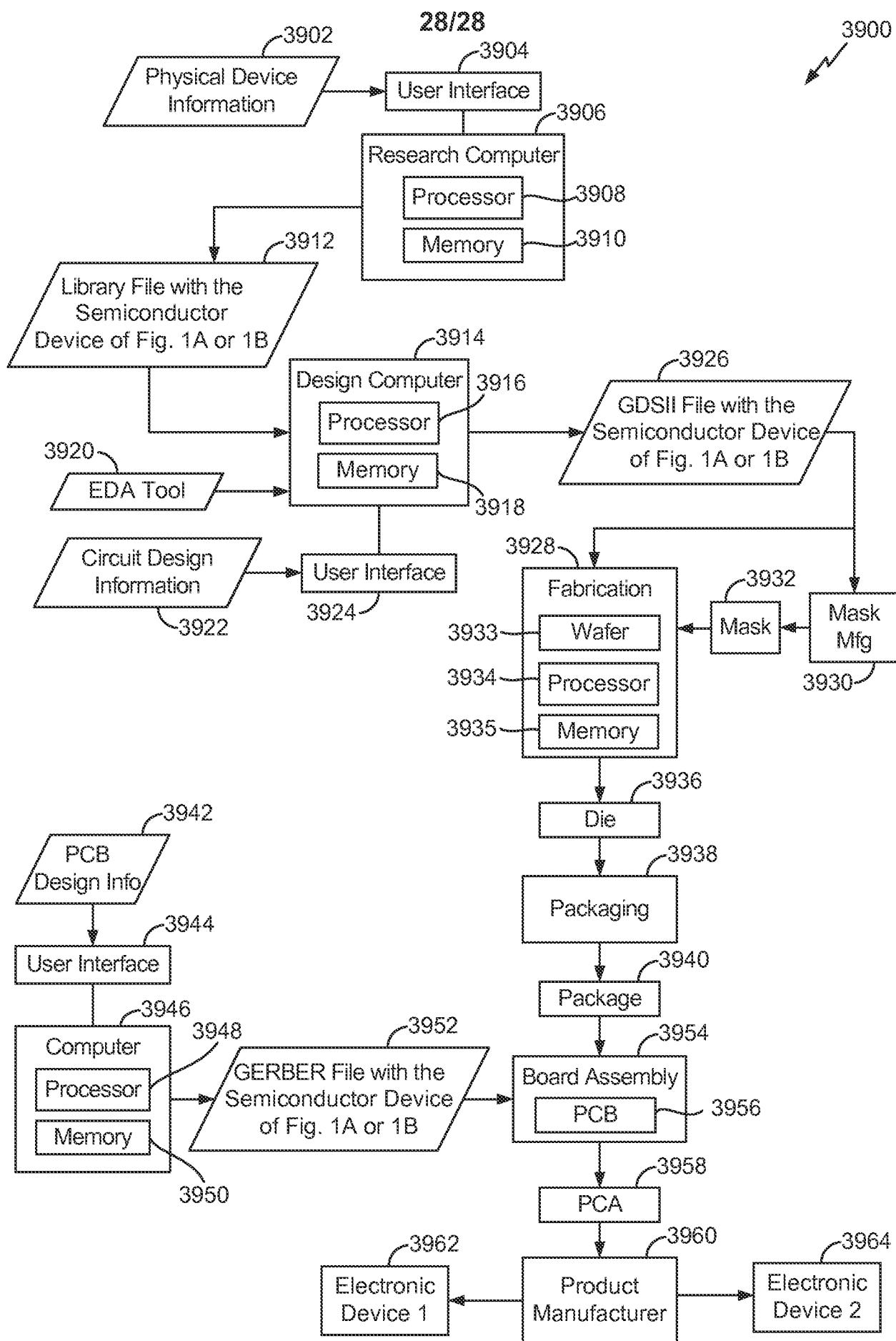

[0051] FIG. 39 is a data flow diagram of an illustrative embodiment of a manufacturing process to fabricate a device including the semiconductor device of FIG. 1A or FIG. 1B.

## ***VI. Detailed Description***

[0052] Particular embodiments of the present disclosure are described below with reference to the drawings. In the description, common features are designated by common reference numbers throughout the drawings.

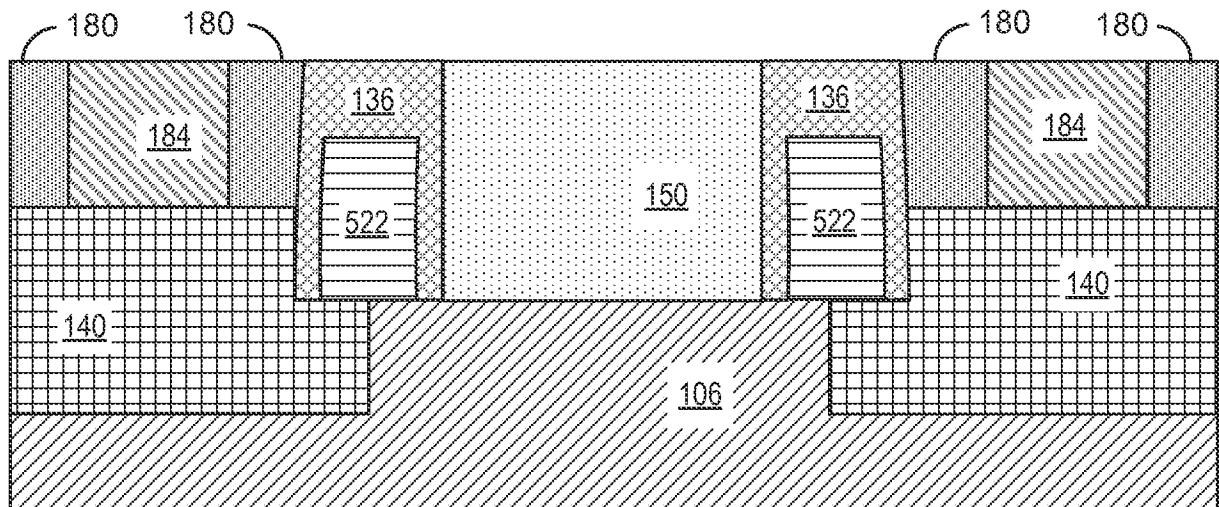

[0053] Referring to FIG. 1A, a diagram of a semiconductor device 100 having a gap defined therein is shown. The semiconductor device 100 may include or correspond to a field-effect transistor (FET) device, such as a FinFET device that includes one or more fins, a metal-oxide semiconductor (MOS) device, such as p-type metal-oxide-semiconductor (pMOS) device or an n-type metal-oxide-semiconductor (nMOS) device, as illustrative, non-limiting examples.

[0054] The semiconductor device 100 may include a substrate 106, one or more source/drain regions 140, dielectric material 180 (e.g. a dielectric layer), one or more contacts 184, a spacer 136, and a gate 150. The substrate 106 may be associated with and/or formed from a wafer, such as a silicon wafer, as an illustrative, non-limiting example. The substrate 106 may include a silicon (Si) substrate. The substrate 106 may include a fin portion that is associated with a channel region of the semiconductor device 100.

[0055] The gate 150 may be coupled to (e.g., in contact with) the substrate 106, such as coupled to the fin portion of the substrate 106. The gate 150 may include a conformal oxide layer (e.g., a high K (HiK) material), gate material (e.g., a metal), or a combination thereof. The gate 150 may have a height  $h_{gate}$ . The height  $h_{gate}$  of the gate 150 may be determined relative to a surface of the substrate 106. For example, the height  $h_{gate}$  of the gate 150 may be determined based on a distance from a top surface

- 8 -

of the gate 150 to a bottom surface of the gate 150. The bottom surface of the gate 150 may be in contact with a surface of the substrate 106, such as a surface of a channel region of the substrate 106.

**[0056]** Although the semiconductor device 100 is illustrated as having two source/drain (S/D) regions 140, one of the source/drain regions 140 may be designated as a source region and the other source/drain region 140 may be designated as a drain region. Each of the source/drain regions 140 may be coupled to a corresponding contact 184. The contact 184 may include a metal. Each contact 184 may be in contact with a corresponding source/drain region 140. Alternatively or additionally, each contact 184 may be electrically coupled to a corresponding source/drain region 140 through one or more structures, such as through a silicide.

**[0057]** A spacer 136 may be positioned between the gate 150 and the contact 184. Although the spacer 136 is illustrated as a single spacer structure, the spacer 136 may include one or more sub-structures, as described further herein with reference to FIG. 1B. The spacer 136 may include one or more materials, such as an oxide or a nitride (e.g., a nitride including silicon (Si), carbon (C), boron (B), or a combination thereof), as illustrative, non-limiting examples.

**[0058]** One or more components (e.g., one or more structures) of the semiconductor device 100 may define the gap 120. For example, as illustrated in FIG. 1A, the spacer 136 and one or more source/drain regions 140 define the gap 120. Additionally, as illustrated in FIG. 1B, the substrate 106 may also define the gap 120. The gap 120 may have a height  $h_{gap}$ . The height  $h_{gap}$  of the gap 120 may be determined based on a distance from a top boundary of the gap 120 to a bottom boundary of the gap 120. The top boundary of the gap 120 may be established by a surface of the spacer 136. The bottom boundary of the gap 120 may be established by a surface of the source/drain region 140. The height  $h_{gap}$  of the gap 120 is less than the height  $h_{gate}$  of the gate 150.

**[0059]** During operation of the semiconductor device 100, the gate 150 and the contact 184 (e.g., source/drain electrodes) of the semiconductor device 100 may be biased in accordance with operation of the semiconductor device 100. When the semiconductor device 100 is in an on state, the gate 150 may activate a channel region to enable a

carrier path from a first source/drain region 140 (e.g., a source region) to a second source/drain region 140 (e.g., the drain region), such as a carrier path through the substrate 106 (e.g., through a fin of the semiconductor device 100). When the semiconductor device 100 is in an off state, the gate 150 may not activate the channel region and the carrier path may not be enabled (e.g., the carrier path is disabled in a subthreshold regime of operation).

[0060] By having the gap 120, such as an air-filled gap or a vacuum gap, the semiconductor device 100 may advantageously include a reduced parasitic capacitance (e.g., a gate capacitance) and an AC performance improvement as compared to FinFET devices that have multiple fins and do not have a defined gap. Additionally, a FinFET transistor delay time and/or a switch energy associated with the semiconductor device 100 may advantageously be reduced.

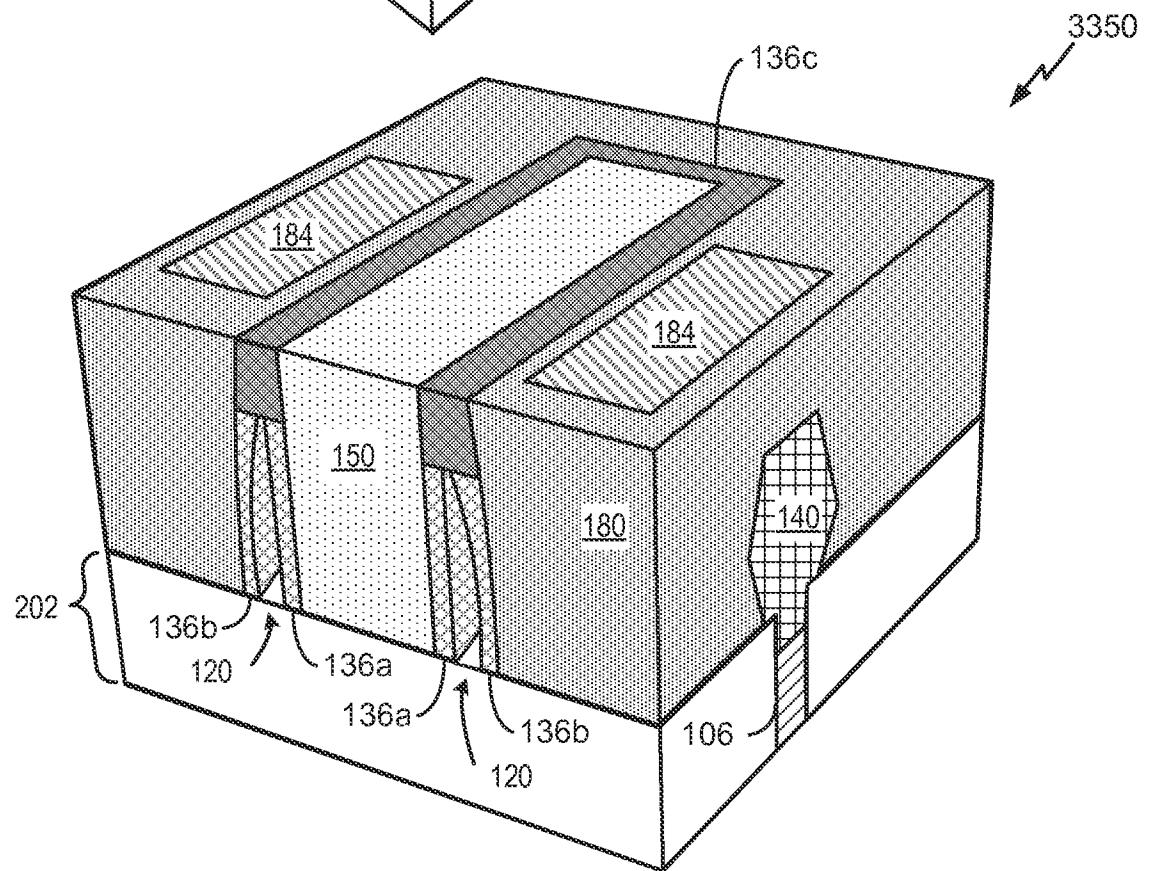

[0061] Referring to FIG. 1B, a diagram of a semiconductor device 100 having a gap defined therein is shown. The semiconductor device 160 may include or correspond to the semiconductor device 100 of FIG. 1A. For example, the semiconductor device 100 may include or correspond to a field-effect transistor (FET) device, such as a FinFET device.

[0062] The spacer 136 may include one or more sub-structures, such a first spacer structure 136a, a second spacer structure 136b, and a third spacer structure 136c. Although the spacer 136 is illustrated as including three sub-structures, the spacer 136 may include less than three sub-structures or more than three sub-structures.

[0063] The first spacer structure 136a may include an oxide or silicon nitride and the second spacer structure 136b may include an oxide or silicon nitride, as illustrative, non-limiting examples. A first spacer material of the first spacer structure 136a and a second spacer material of the second spacer structure 136b may be the same material or may be different materials. The third spacer structure 136 may include a third spacer material, such as a nitride (e.g., a nitride including silicon (Si), carbon (C), boron (B), or a combination thereof), as illustrative, non-limiting examples.

[0064] The height  $h_{gap}$  of the gap 120 may be determined based on a distance from a top boundary of the gap 120 to a bottom boundary of the gap 120. The top boundary of

- 10 -

the gap 120 may be established by a surface of the spacer 136, such as a surface of the third spacer structure 136c. The bottom boundary of the gap 120 may be established by a surface of the source/drain region 140 and/or a surface of the substrate 106 (e.g., a surface of a channel region of the substrate 106). The height  $h_{gap}$  of the gap 120 is less than the height  $h_{gate}$  of the gate 150.

**[0065]** The semiconductor device 160 may operate in a similar manner as the semiconductor device 100. The semiconductor device 160 may advantageously include a reduced parasitic capacitance (e.g., a gate capacitance) and an AC performance improvement as compared to FinFET devices that have multiple fins and that do not have a defined gap. Additionally, a FinFET transistor delay time and/or a switch energy associated with the semiconductor device 160 may advantageously be reduced.

**[0066]** Referring to FIG. 2, a first illustrative diagram of at least one stage of a first process of fabricating a semiconductor device that includes a source/drain region that defines a gap is depicted and generally designated 200. The semiconductor device, such as a FinFET device, may correspond to the semiconductor device 100 of FIG. 1A. A wafer 202 as depicted in FIG. 2 is illustrated after performing shallow trench isolation (STI) on the wafer 202 to form a fin. For example, the wafer 202 may be etched during the STI to form the fin. The wafer 202 may include a substrate 106, such as a silicon (Si) substrate, as an illustrative, non-limiting example. Accordingly, the fin may include silicon (Si). Although a single fin is illustrated, the substrate 106 may include more than one fin.

**[0067]** Referring to FIG. 3, a second illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a hardmask on a dummy gate is depicted and generally designated 300. A dummy gate 304 may be formed above the wafer 202 (e.g., above the substrate 106). For example, the dummy gate 304 may be formed on at least a portion of the fin. To illustrate, the dummy gate 304 may be deposited on the wafer 202 and on the substrate 106. The dummy gate 304 may include amorphous silicon (a-Si) or polysilicon, as illustrative, non-limiting examples. A hardmask 310 may be formed above the dummy gate 304. For example, the hardmask 310 may be deposited on a surface (e.g., a top) of the dummy gate 304. The

hardmask 310 may include an oxide.

[0068] Referring to FIG. 4, a third illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a first spacer material is depicted and generally designated 400. A first spacer structure 136a may be formed on the dummy gate 304. For example, the first spacer structure 136a may be formed by depositing a first spacer material on the dummy gate 304. The first spacer structure 136a may be deposited on a sidewall of the dummy gate 304, such that the first spacer structure 136a is in contact with the dummy gate 304. The first spacer structure 136a may be formed above the wafer 202 and above the substrate 106. The first spacer structure 136a (e.g., the first spacer material) may include silicon nitride (SiN) or an oxide. Etching may be performed as part of or in addition to formation of the first spacer structure 136a.

[0069] Referring to FIG. 5, a third illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a sacrificial spacer is depicted and generally designated 500. A sacrificial spacer 522 may be conformally formed on at least a portion of the first spacer structure 136a. The sacrificial spacer 522 may be formed above the wafer 202 and above the substrate 106. The sacrificial spacer 522 may include a material that includes carbon. A cross sectional thickness of the sacrificial spacer 522 may be greater than a cross sectional thickness of the first spacer structure 136a.

[0070] Etching may be performed as part of or in addition to formation of the sacrificial spacer 522. For example, the sacrificial spacer 522 may be etched to expose a portion of a surface of the first spacer structure 136a. Alternatively, after etching the sacrificial spacer 522, the sacrificial spacer 522 may cover an entirety of the first spacer structure 136a.

[0071] Referring to FIG. 6, a fifth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a second spacer material is depicted and generally designated 600. FIG. 6 also includes a cross section 650 through the fin of the semiconductor device. A second spacer structure 136b may be formed on first spacer structure 136a and/or the sacrificial spacer 522. For example, a second spacer material of the second spacer structure 136b may be deposited on the first

spacer structure 136a and the sacrificial spacer 522, such that the second spacer structure 136b is in contact with a portion of a surface of the first spacer structure 136a and at least a portion of a surface of the sacrificial spacer 522. When the second spacer structure 136b and the first spacer structure 136a are in contact, the first spacer structure 136a and the second spacer structure 136b may be referred to collectively as a spacer 136. The second spacer structure 136b may be formed above the wafer 202 and above the substrate 106. Accordingly, the sacrificial spacer 522 may be positioned between the first spacer structure 136a and the second spacer structure 136b.

[0072] The second spacer material of the second spacer structure 136b may include the same material as the first spacer material of the first spacer structure 136a or may be a different material than the first spacer material. For example, the second spacer material may include silicon nitride (SiN) or an oxide. Etching may be performed as part of or in addition to formation of the second spacer structure 136b. A cross sectional thickness of the second spacer structure 136b may be less than a cross sectional thickness of the sacrificial spacer 522.

[0073] Referring to FIG. 7, a sixth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after removing a portion of a fin of the semiconductor device is depicted and generally designated 700. FIG. 7 also includes a cross section 750 through the fin of the semiconductor device. A portion of the substrate 106, such as a portion of the fin, associated with a source/drain (S/D) region may be removed. For example, the portion of the substrate 106 (e.g., the fin) may be etched (e.g., recessed) that is associated with one or more S/D regions while another portion of the substrate 106 associated with a channel region is not removed. After the portion of the substrate 106 is etched, a surface of the portion of the substrate 106 may be lower than a surface of the wafer 202. The removal of the portion of the substrate 106 may include removing a particular portion of the fin that is in contact with the second spacer structure 136b. The removal of the particular portion of the fin that is in contact with the second spacer structure 136b may expose a portion of the sacrificial spacer 522. Additionally, another particular portion of the fin that is in contact with the sacrificial spacer 522 may also be etched. The removal of the portion of the substrate may establish an opening 712 through which the sacrificial spacer 522 may be removed.

**[0074]** Referring to FIG. 8, a seventh illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after removing the sacrificial spacer is depicted and generally designated 800. FIG. 8 also illustrates a cross section 850 through the fin of the semiconductor device. The sacrificial spacer 522 may be removed using a chemical or reactive gas chemistry. For example, a hydrogen reaction or a standard clean 1 type may be used to remove the sacrificial spacer 522 without performing an etch operation. Removal of the sacrificial spacer 522 may not affect (e.g., may not remove) the first spacer structure 136a or the second spacer structure 136b. Removal of the sacrificial spacer 522 may create a cavity 842 that is defined by the first spacer structure 136a and the second spacer structure 136b. The cavity 842 may also be defined by the substrate 106 (e.g., the fin) and/or the wafer 202.

**[0075]** Referring to FIG. 9, an eighth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a source/drain region is depicted and generally designated 900. FIG. 9 also illustrates a cross section 950 through the fin of the semiconductor device. A source/drain (SD) region 140 may be formed (e.g., raised) above a recessed portion of the substrate 106 (e.g., the fin) and/or above the wafer 202. For example, the source/drain (SD) region 140 may be epitaxially deposited (e.g., epitaxially grown) on the portion of the substrate 106 (e.g., the fin). The S/D region 140 may extend at least part way into the cavity 842 of FIG. 8 and may block (e.g., close) the opening 712 through which the sacrificial spacer 522 was removed. By closing the opening 712 through which the sacrificial spacer 522 was removed, a gap 120 (e.g., an air-gap or a vacuum gap) may be defined by at least a portion of the spacer 136 (e.g., the first spacer structure 136a and the second spacer structure 136b). The gap 120 may further be defined by the wafer 202 and/or the S/D region 140. Additionally or alternatively, the gap 120 may further be defined by the substrate 106 (e.g., the fin).

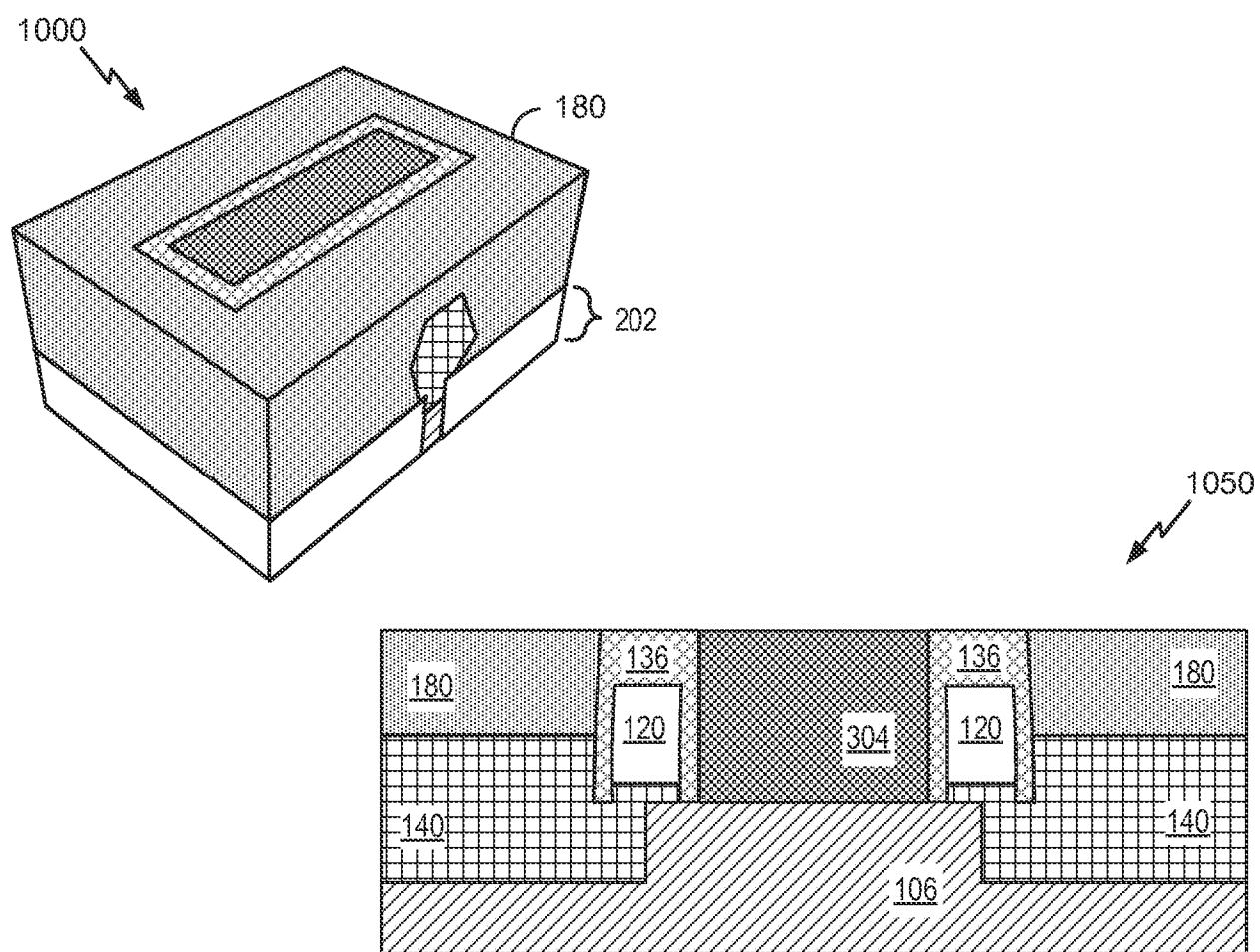

**[0076]** Referring to FIG. 10, a ninth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after a dielectric material is deposited and after planarization is performed is depicted and generally designated 1000. FIG. 10 also illustrates a cross section 1050 through the fin of the semiconductor device. A dielectric material 180 may be deposited above the wafer 202. For example, the dielectric material 180 may include a silicon-containing material. After the dielectric

- 14 -

material 180 is deposited, a chemical mechanical planarization (CMP) (e.g., a chemical mechanical polish) may be performed to remove a portion of the dielectric material 180 and the hardmask 310. By removing the hardmask 310, the CMP may expose the dummy gate 304, such as a top surface of the dummy gate 304.

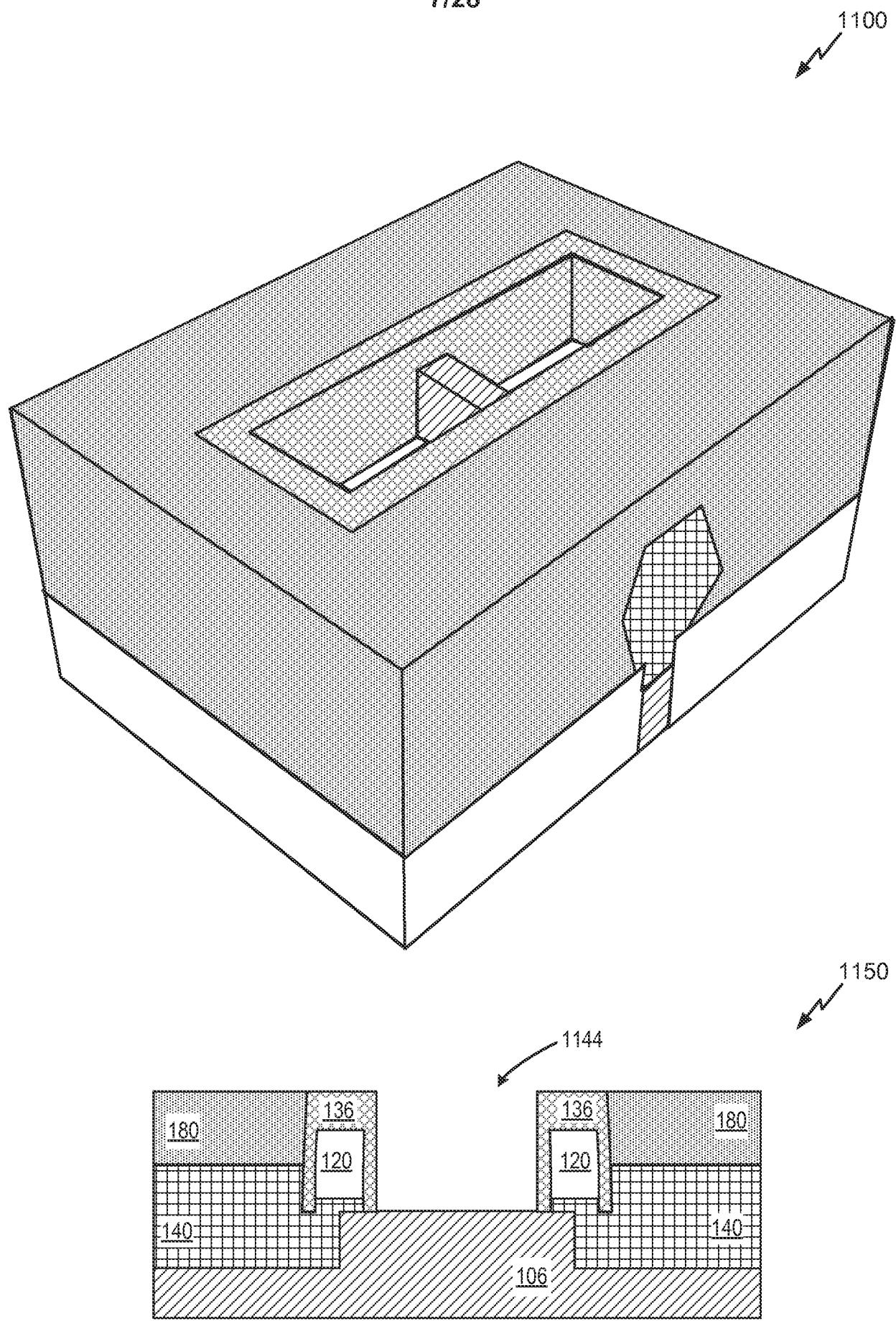

[0077] Referring to FIG. 11, a tenth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after the dummy gate is removed is depicted and generally designated 1100. FIG. 11 also illustrates a cross section 1150 through the fin of the semiconductor device. The dummy gate 304 may be removed to establish (e.g., form) a cavity 1144. For example, the dummy gate 304 may be etched out to expose at least a portion of the substrate 106 (e.g., the fin) associated with a channel region. The dummy gate 304 may be removed using a dry etch, a wet etch, or a combination thereof.

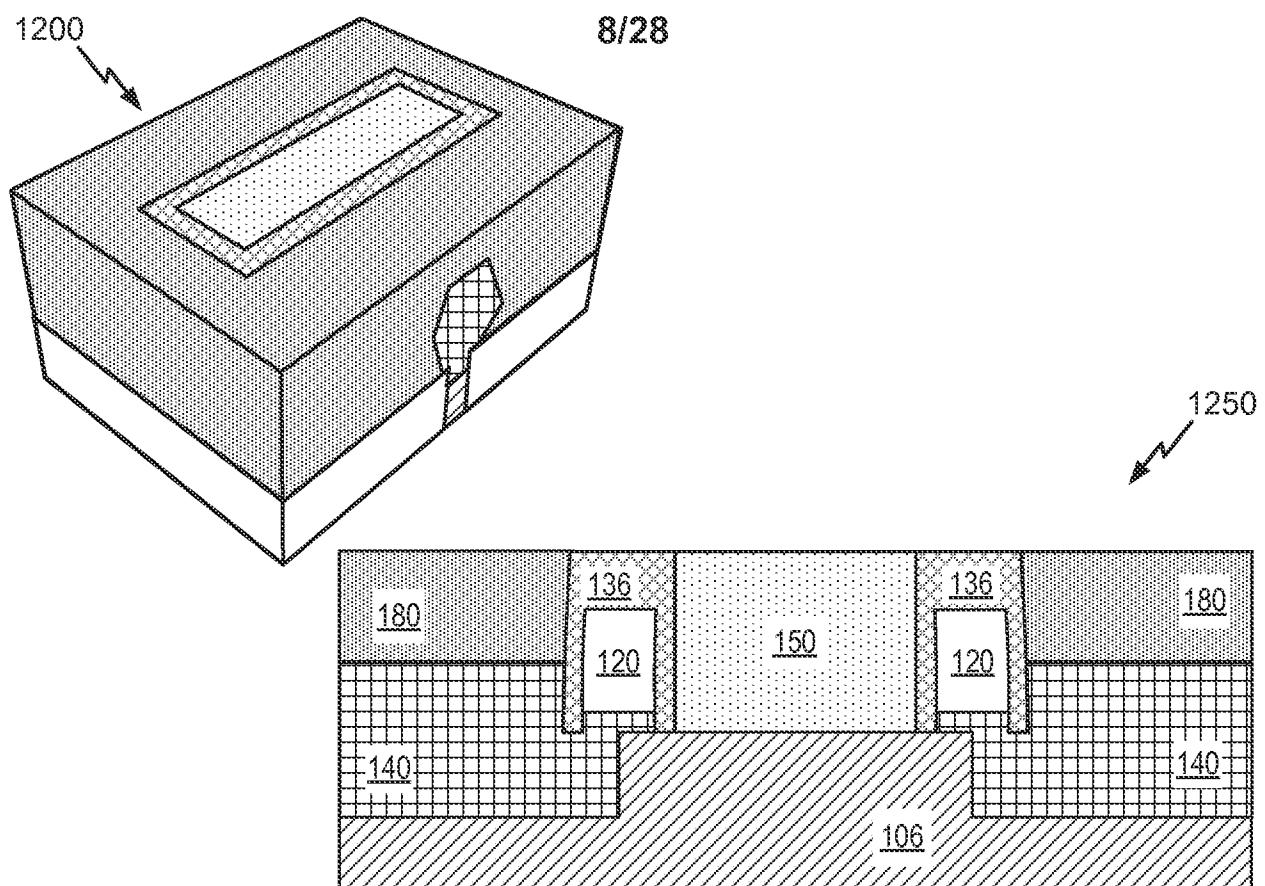

[0078] Referring to FIG. 12, an eleventh illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a gate is depicted and generally designated 1200. FIG. 12 also illustrates a cross section 1250 through the fin of the semiconductor device. A gate 150 may be formed (e.g., deposited) in the cavity 1144 of FIG. 11. For example, the gate 150 may be formed on (e.g., over) a portion of the substrate 106 (e.g., the fin) that is exposed in the cavity 1144 of FIG. 11. The gate 150 may include a high-k material. Although illustrated as a single material layer, the gate 150 may include one or more layers (e.g., one or more materials), such as an oxide layer, a high-k gate dielectric, and/or a metal gate layer (e.g., a metal gate material), as illustrative, non-limiting embodiments.

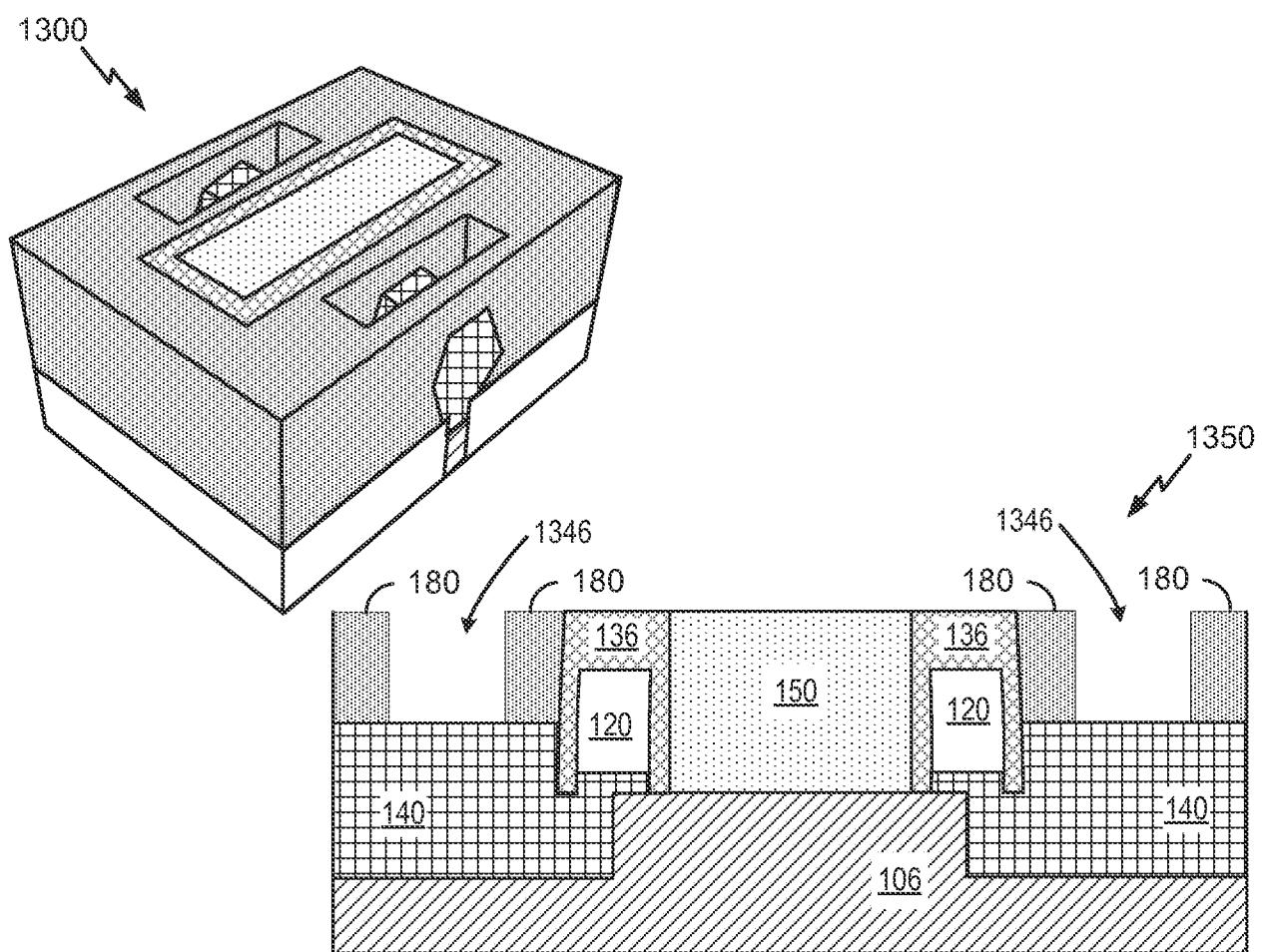

[0079] Referring to FIG. 13, a twelfth illustrative diagram of at least one stage of the first process of fabricating the semiconductor device after forming a cavity is depicted and generally designated 1300. FIG. 13 also illustrates a cross section 1350 through the fin of the semiconductor device. Contact patterning may be performed to create a cavity 1346. For example, an etch process may be used to create the cavity 1346 (e.g., a trench) and to expose a portion (e.g. a surface) of the S/D region 140. The cavity 1346 may not expose a portion of the spacer 136, such as a surface of the second spacer structure 136b.

[0080] Referring to FIG. 14, a thirteenth illustrative diagram of at least one stage of the

- 15 -

first process of fabricating the semiconductor device after forming a contact is depicted and generally designated 1400. FIG. 14 also illustrates a cross section 1450 through a line A-A of the semiconductor device. A contact 184 may be formed in the cavity 1346 of FIG. 13. In a particular embodiment, the contact 184 does not touch the spacer 136. The contact 184 may include a metal material. The semiconductor device of FIG. 14 may include or correspond to the semiconductor device 100 of FIG. 1A.

**[0081]** The semiconductor device may advantageously include the spacer 136 that defines the gap 120. The gap 120 may reduce a parasitic capacitance (e.g., a gate capacitance, such as a capacitance between the gate 150 and the contact 184). Additionally, the gap 120 may provide an AC performance improvement as compared to FinFET devices that do not have a defined gap.

**[0082]** Referring to FIG. 15, a first illustrative diagram of at least one stage of a second process of fabricating a semiconductor device after removing a portion of a fin of the semiconductor device is depicted and generally designated 1500. FIG. 15 also illustrates a cross section 1550 through a fin of the semiconductor device. A portion of the substrate 106 (e.g., a portion of the fin) associated with a source/drain (S/D) region may be removed. For example, the portion of the substrate 106 may be etched (e.g., recessed) that is associated with one or more S/D regions while another portion of the fin associated with a channel region is not removed. After the portion of the substrate 106 is etched, a portion of a second spacer structure 136b and a portion of a sacrificial spacer 522 may be exposed. The semiconductor device of FIG. 15 may include or correspond to the semiconductor device as illustrated in FIG. 7. For example, the diagram 1500 of at least one stage of the second process may be preceded by one or more stages, such as one or more stages of a process as illustrated with reference to FIGS. 2-6.

**[0083]** Referring to FIG. 16, a second illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after forming a source/drain region is performed is depicted and generally designated 1600. FIG. 16 also illustrates a cross section 1650 through the fin of the semiconductor device. A source/drain (SD) region 140 may be formed (e.g., raised) above a recessed portion of the substrate 106 and/or above the wafer 202. For example, the source/drain (SD) region 140 may be

- 16 -

epitaxially deposited (e.g., epitaxially grown) on the portion of the substrate 106. The S/D region 140 may be in contact with the sacrificial spacer 522 and/or the spacer 136 (e.g., a second spacer structure 136b).

**[0084]** Referring to FIG. 17, a third illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after a dielectric material is deposited and after planarization is performed is depicted and generally designated 1700. FIG. 17 also illustrates a cross section 1750 through the fin of the semiconductor device. A dielectric material 180 may be deposited above the wafer 202. For example, the dielectric material 180 may include a silicon-containing material. After the dielectric material 180 is deposited, a chemical mechanical planarization (CMP) (e.g., a chemical mechanical polish) may be performed to remove a portion of the dielectric material 180 and the hardmask 310. By removing the hardmask 310, the CMP may expose the dummy gate 304, such as a surface of the dummy gate 304. Additionally or alternatively, the CMP may expose a surface of the spacer 136 (e.g., a first spacer structure 136a and/or a second spacer structure 136b).

**[0085]** Referring to FIG. 18, a fourth illustrative diagram of at least one stage of the second process of fabricating the semiconductor after exposing a portion of the sacrificial spacer is depicted and generally designated 1800. FIG. 18 also illustrates a cross section 1850 through the fin of the semiconductor device. A portion of the spacer 136 (including the first spacer structure 136a and/or the second spacer structure 136b) may be removed to expose a portion of the sacrificial spacer 522. For example, the portion of the spacer 136 may be etched to expose a surface of the sacrificial spacer 522. Removing the portion of the spacer 136 may create a cavity 1842. The cavity 1842 may be defined by the dummy gate 304, the first spacer structure 136a, the sacrificial spacer 522, the second spacer structure 136b, the dielectric material 180, or a combination thereof. After the portion of the spacer 136 is removed to expose the sacrificial spacer 522, a portion of the first spacer structure 136a that is positioned between the sacrificial spacer 522 and the dummy gate 304 may be exposed. Additionally, after the portion of the spacer 136 is removed to expose the sacrificial spacer 522, a portion of the second spacer structure 136b that is positioned between the sacrificial spacer 522 and the dielectric material 180 may be exposed. The cavity 1842 may have an opening 1812 through which the sacrificial spacer 522 may be removed.

**[0086]** Referring to FIG. 19, a fifth illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after removing a sacrificial spacer is depicted and generally designated 1900. FIG. 19 also illustrates a cross section 1950 through the fin of the semiconductor device. The sacrificial spacer 522 may be removed using a chemical or reactive gas chemistry. For example, a hydrogen reaction or a standard clean 1 type may be used to remove the sacrificial spacer 522 without performing an etch operation. The sacrificial spacer 522 may be removed through the opening 1812 of FIG. 18. Removal of the sacrificial spacer 522 may not affect (e.g., may not remove) the first spacer structure 136a or the second spacer structure 136b. Removal of the sacrificial spacer 522 may extend the cavity 1842 such that the cavity 1842 is defined by the substrate 106 (e.g., the fin) and/or the S/D region 140.

**[0087]** Referring to FIG. 20, a sixth illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after forming a third spacer material is depicted and generally designated 2000. FIG. 20 also includes a cross section 2050 through the fin of the semiconductor device. A third spacer structure 136c may be formed on the semiconductor device. For example, the third spacer structure 136c may be non-conformally deposited on the semiconductor device. The third spacer structure 136c may extend at least part way into the cavity 1842 of FIG. 19 and may block (e.g., close) the opening 1812 through which the sacrificial spacer 522 was removed. By closing the opening 1812 through which the sacrificial spacer 522 was removed, a gap 120 (e.g., an air-gap or a vacuum gap) may be defined by at least a portion of the third spacer structure 136c, the first spacer structure 136a, and/or the second spacer structure 136b. The gap 120 may further be defined by the wafer 202, the substrate 106, and/or the S/D region 140. Additionally or alternatively, the gap 120 may further be defined by the fin.

**[0088]** The third spacer structure 136c may include a third spacer material, such as silicon nitride or another nitride, such as a nitride that includes carbon (C) or boron (B), as illustrative, non-limiting examples. The third spacer material may be the same material or a different material than the first spacer material of the first spacer structure 136a and/or the second spacer material of the second spacer structure 136b. The third spacer structure 136c may be configured to operate as a cap or a seal to establish and

define the gap 120.

[0089] Referring to FIG. 21, a seventh illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after planarization is performed is depicted and generally designated 2100. FIG. 21 also illustrates a cross section 2150 through the fin of the semiconductor device. A chemical mechanical planarization (CMP) (e.g., a chemical mechanical polish) may be performed to remove a portion of the third spacer structure 136c and thus establish the spacer 136 which includes the first spacer structure 136a, the second spacer structure 136b, and the third spacer structure 136c. By removing the portion of the third spacer structure 136c, the CMP may expose the dummy gate 304, such as a surface of the dummy gate 304. Additionally or alternatively, by removing the portion of the third spacer structure 136c, the CMP may expose a surface of the dielectric material.

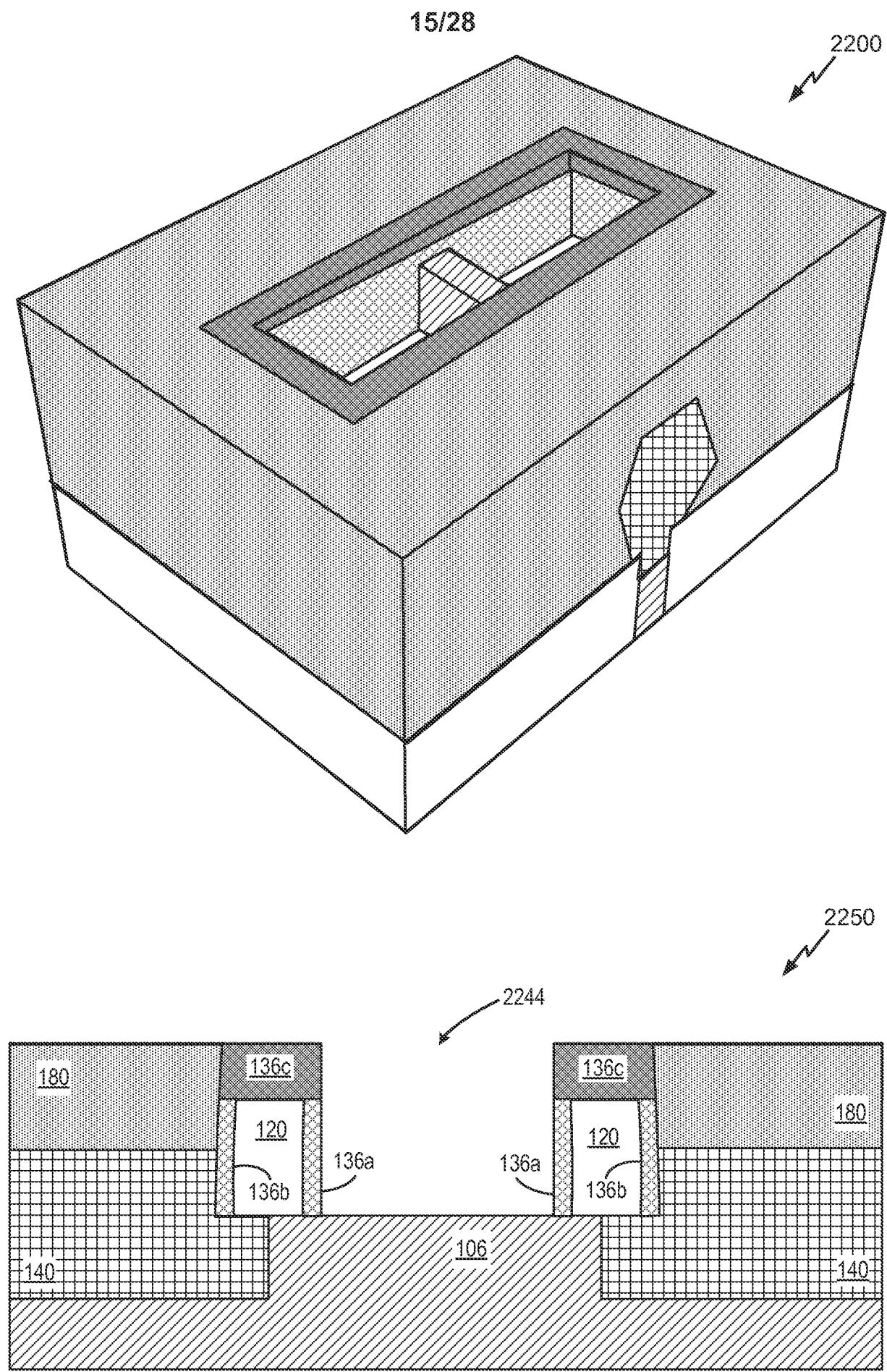

[0090] Referring to FIG. 22, an eighth illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after a dummy gate is removed is depicted and generally designated 2200. FIG. 22 also illustrates a cross section 2250 through the fin of the semiconductor device. The dummy gate 304 may be removed to establish a cavity 2244. For example, the dummy gate 304 may be etched out to expose at least a portion of the substrate 106 (e.g., the fin) associated with a channel region. The dummy gate 304 may be removed using a dry etch, a wet etch, or a combination thereof.

[0091] Referring to FIG. 23, a ninth illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after forming a gate is depicted and generally designated 2300. FIG. 23 also illustrates a cross section 2350 through the fin of the semiconductor device. A gate 150 may be formed (e.g., deposited) in the cavity 2244 of FIG. 22. For example, the gate 150 may be formed on (e.g., over) a portion of the substrate 106 (e.g., the fin) that is exposed in the cavity 2244 of FIG. 22. The gate 150 may include a high-k material. The gate 150 may include one or more layers (e.g., one or more materials), such as an oxide layer, a high-k gate dielectric, and/or a metal gate layer (e.g., a metal gate material), as illustrative, non-limiting embodiments.

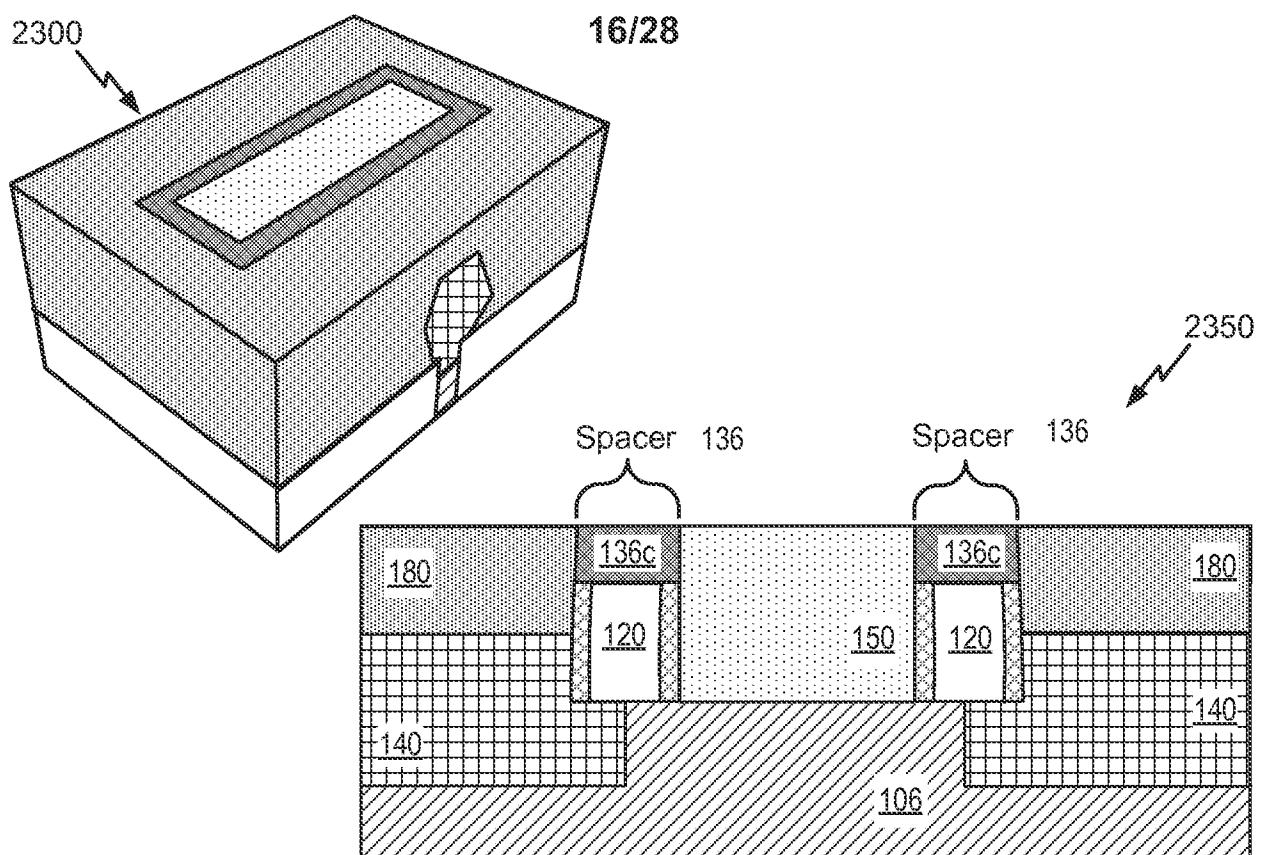

[0092] Referring to FIG. 24, a tenth illustrative diagram of at least one stage of the

second process of fabricating the semiconductor device after forming a cavity is depicted and generally designated 2400. FIG. 24 also illustrates a cross section 2450 through the fin of the semiconductor device. Contact patterning may be performed to create a cavity 2446. For example, an etch process may be used to create the cavity 2446 (e.g., a trench) and to expose a portion (e.g. a surface) of the S/D region 140. In a particular embodiment, the cavity 2446 does not expose a portion of the spacer 136, such as a surface of the second spacer structure 136b or the third spacer structure 136c.

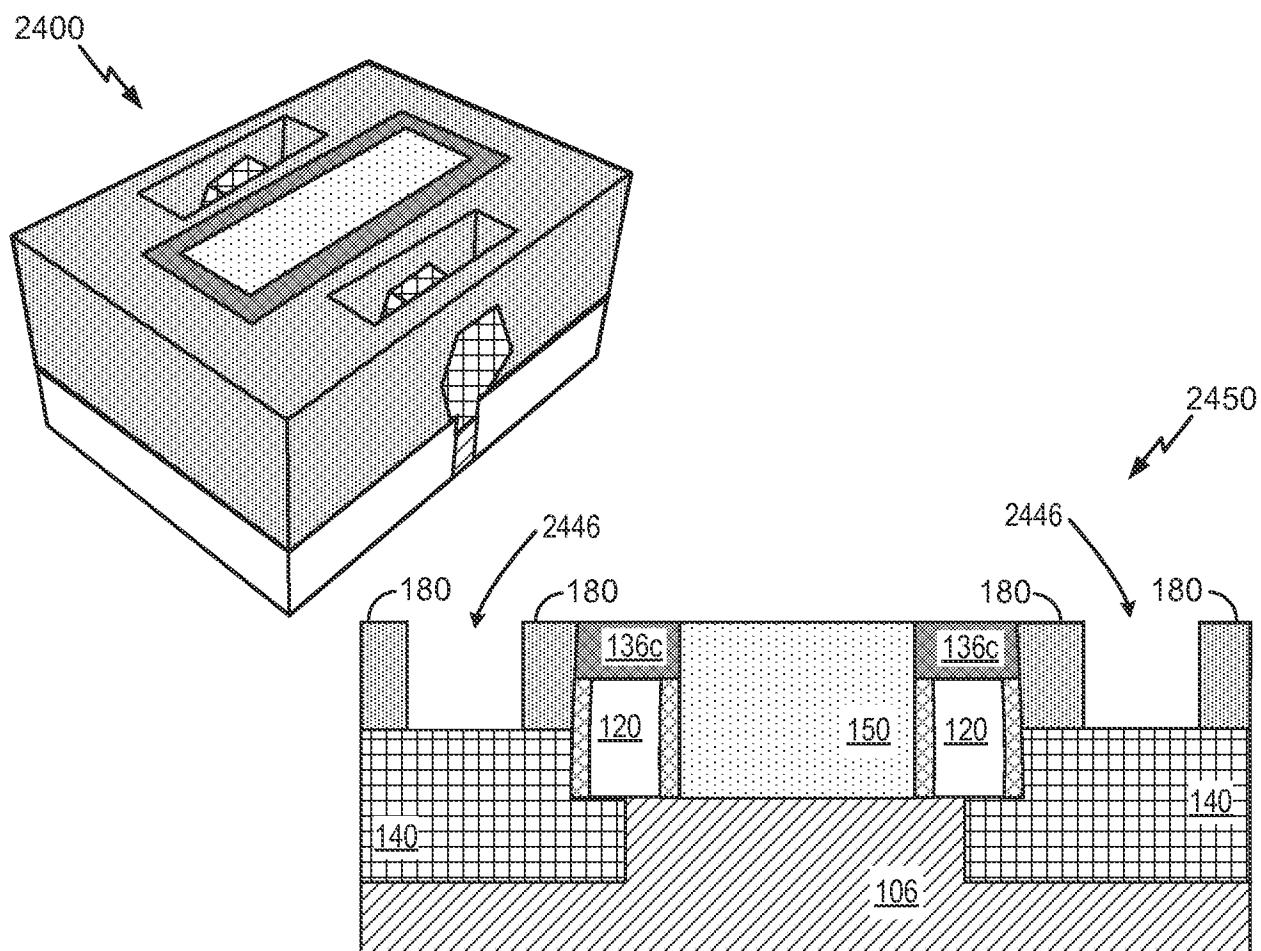

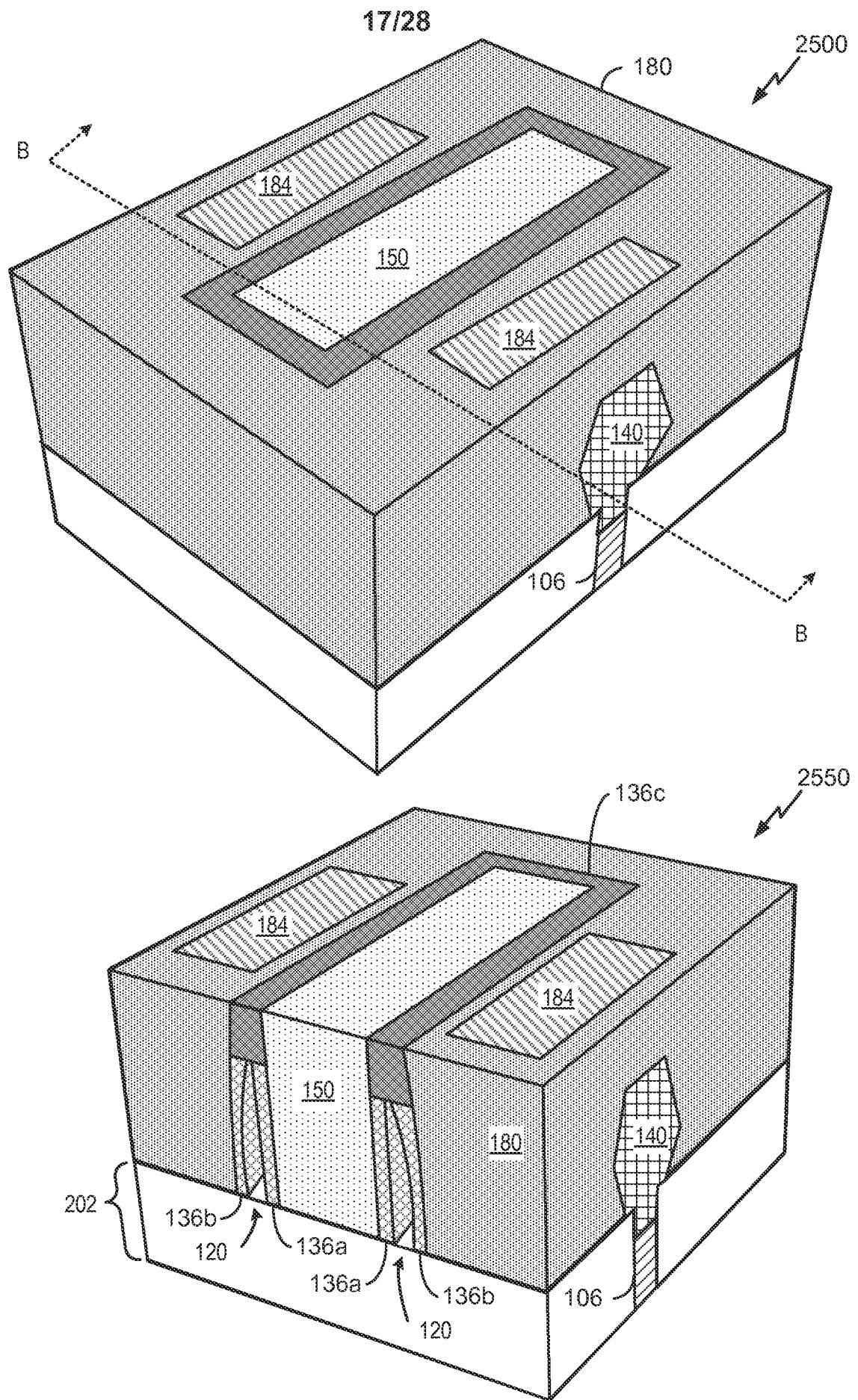

**[0093]** Referring to FIG. 25, an eleventh illustrative diagram of at least one stage of the second process of fabricating the semiconductor device after forming a contact is depicted and generally designated 2500. FIG. 25 also illustrates a cross section 2550 through a line B-B of the semiconductor device. A contact 184 may be formed in the cavity 2446 of FIG. 24. The contact 184 may not touch the spacer 136. The contact 184 may be a metal material. The semiconductor device of FIG. 25 may include or correspond to the semiconductor device 160 of FIG. 1B.

**[0094]** The semiconductor device may advantageously include the spacer 136 that defines the gap 120. The gap 120 may reduce a parasitic capacitance (e.g., a gate capacitance, such as a capacitance between the gate 150 and the contact 184). Additionally, the gap 120 may provide an AC performance improvement as compared to FinFET devices that do not have a defined gap.

**[0095]** Referring to FIG. 26, a first illustrative diagram of at least one stage of a third process of fabricating a semiconductor device after a dielectric material is deposited and after planarization is performed is depicted and generally designated 2600. FIG. 26 also illustrates a cross section 2650 through a fin of the semiconductor device. A dielectric material 180 may be deposited above the wafer 202. For example, the dielectric material 180 may include a silicon-containing material. After the dielectric material 180 is deposited, a chemical mechanical planarization (CMP) (e.g., a chemical mechanical polish) may be performed to remove a portion of the dielectric material 180 and the hardmask 310. By removing the hardmask 310, the CMP may expose the dummy gate 304, such as a surface of the dummy gate 304. Additionally or alternatively, the CMP may expose a surface of the spacer 136 (e.g., a first spacer structure 136a and/or a second spacer structure 136b).

- 20 -

**[0096]** Referring to FIG. 27, a second illustrative diagram of at least one stage of the third process of fabricating the semiconductor device after a dummy gate is removed is depicted and generally designated 2700. FIG. 27 also illustrates a cross section 2750 through the fin of the semiconductor device. The dummy gate 304 may be removed to establish a cavity 2744. For example, the dummy gate 304 may be etched out to expose at least a portion of the substrate 106 (e.g., the fin) associated with a channel region. The dummy gate 304 may be removed using a dry etch, a wet etch, or a combination thereof.

**[0097]** Referring to FIG. 28, a third illustrative diagram of at least one stage of the third process of fabricating the semiconductor device after forming a gate is depicted and generally designated 2800. FIG. 28 also illustrates a cross section 2850 through the fin of the semiconductor device. A gate 150 may be formed (e.g., deposited) in the cavity 2744 of FIG. 27. For example, the gate 150 may be formed on (e.g., over) a portion of the substrate 106 (e.g., the fin) that is exposed in the cavity 2744 of FIG. 27. The gate 150 may include a high-k material. The gate 150 may include one or more layers (e.g., one or more materials), such as an oxide layer, a high-k gate dielectric, and/or a metal gate layer (e.g., a metal gate material), as illustrative, non-limiting embodiments.

**[0098]** Referring to FIG. 29, a third illustrative diagram of at least one stage of the third process of fabricating the semiconductor after forming a cavity is depicted and generally designated 2900. FIG. 29 also illustrates a cross section 2950 through the fin of the semiconductor device. Contact patterning may be performed to create a cavity 2946. For example, an etch process may be used to create the cavity 2946 (e.g., a trench) and to expose a portion (e.g. a surface) of the S/D region 140. In a particular embodiment, the cavity 2946 does not expose a portion of the spacer 136, such as a surface of the second spacer structure 136b.

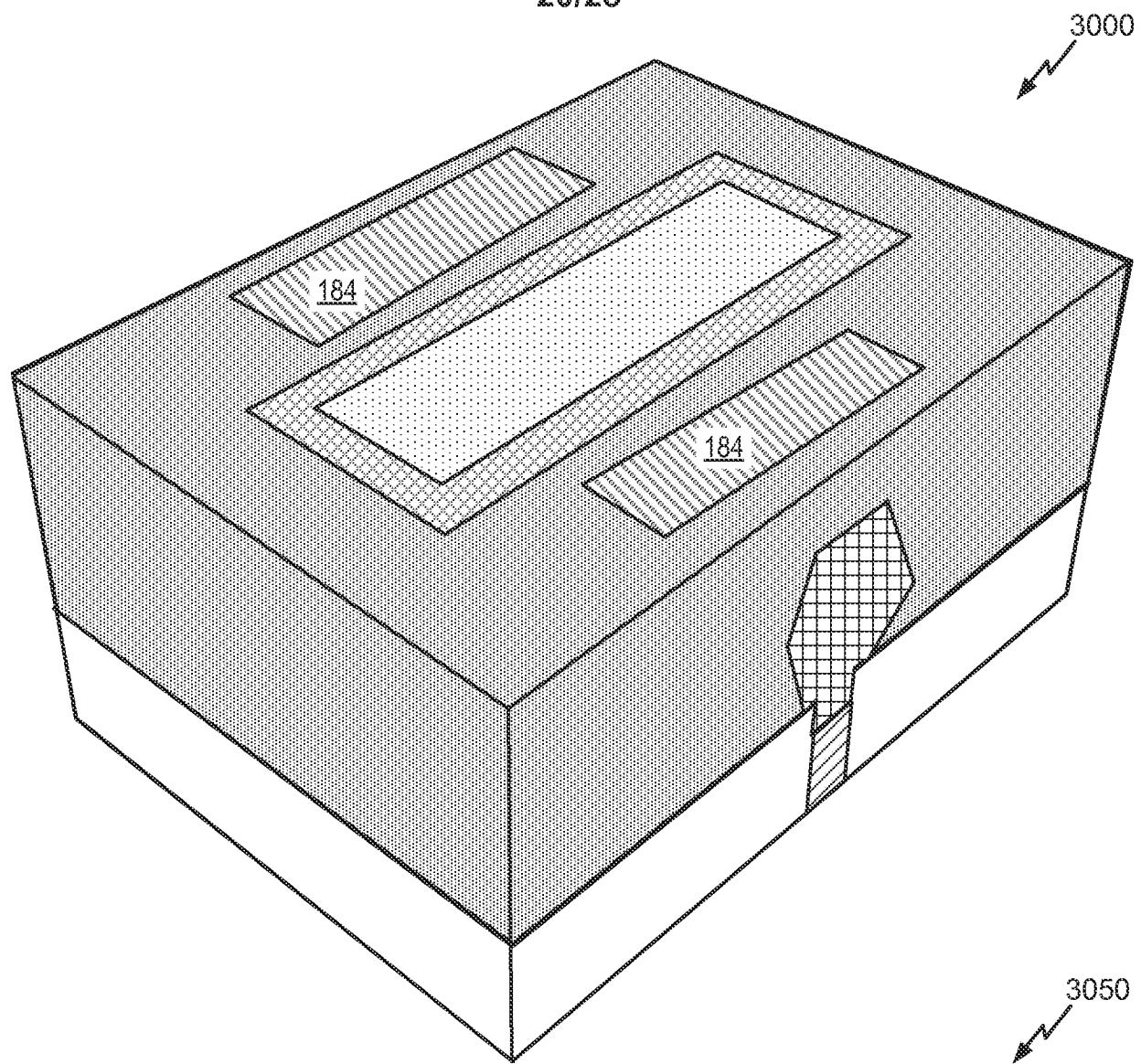

**[0099]** Referring to FIG. 30, a fifth illustrative diagram of at least one stage of the third process of fabricating the semiconductor device forming a contact is depicted and generally designated 3000. FIG. 30 also illustrates a cross section 3050 through the fin of the semiconductor device. A contact 184 may be formed in the cavity 2946 of FIG. 29. In a particular embodiment, the contact 184 does not touch the spacer 136. The contact 184 may be a metal material.

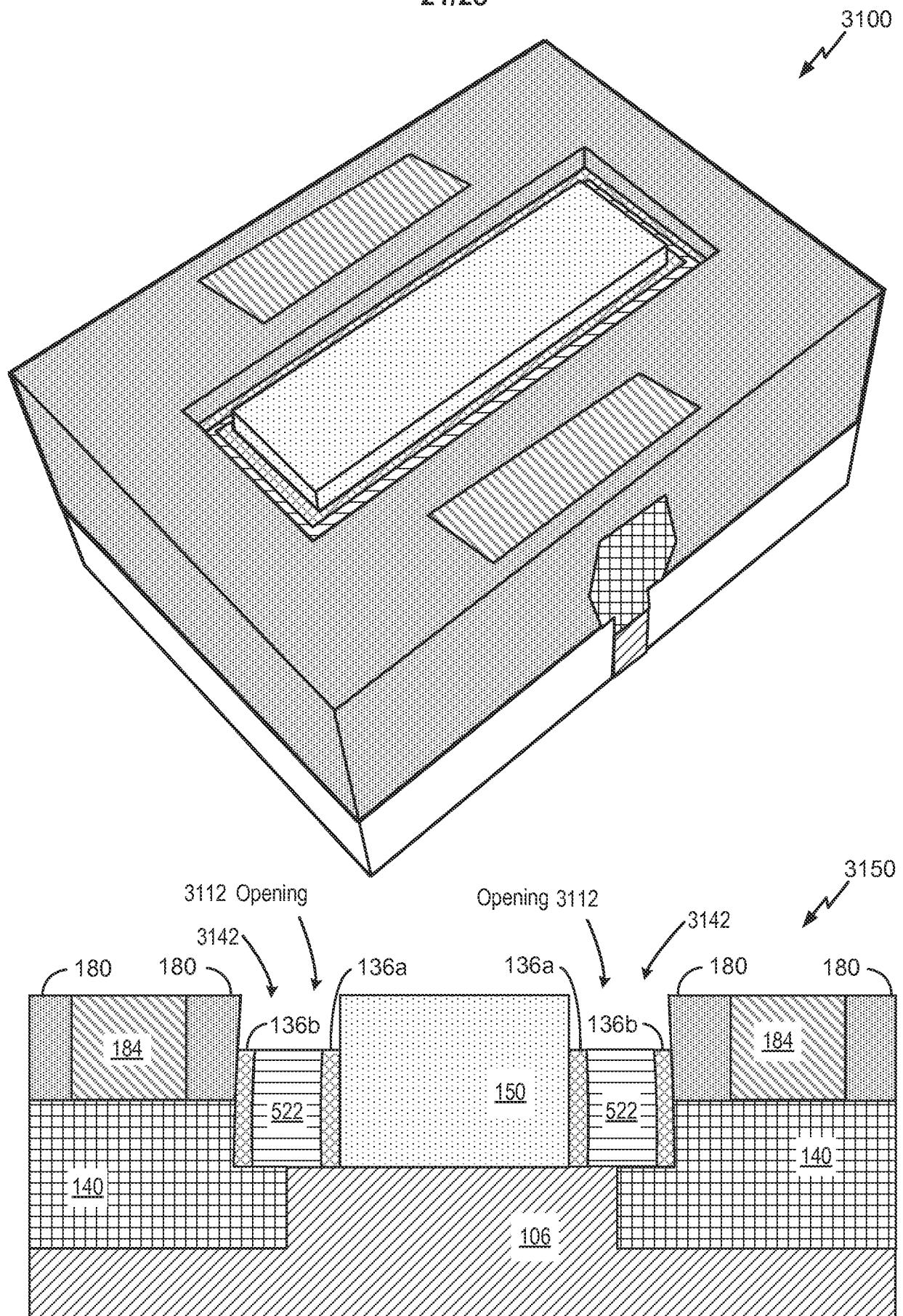

**[00100]** Referring to FIG. 31, a sixth illustrative diagram of at least one stage of the third process of fabricating the semiconductor device after exposing a portion of the sacrificial spacer is depicted and generally designated 3100. FIG. 31 also includes a cross section 3150 through the fin of the semiconductor device. A portion of the spacer 136 (including the first spacer structure 136a and the second spacer structure 136b) may be removed to expose a portion of the sacrificial spacer 522. For example, the portion of the spacer 136 may be etched to expose a surface of the sacrificial spacer 522. Removing the portion of the spacer 136 may create a cavity 3142. The cavity 1842 may be defined by the gate 150, the first spacer structure 136a, the sacrificial spacer 522, the second spacer structure 136b, the dielectric material 180, or a combination thereof. After the portion of the spacer 136 is removed to expose the sacrificial spacer 522, a portion of the first spacer structure 136a that is positioned between the sacrificial spacer 522 and the gate 150 may be exposed. Additionally, after the portion of the spacer 136 is removed to expose the sacrificial spacer 522, a portion of the second spacer structure 136b that is positioned between the sacrificial spacer 522 and the dielectric material 180 may be exposed. The cavity 3142 may be associated with an opening 3112 through which the sacrificial spacer 522 may be removed.

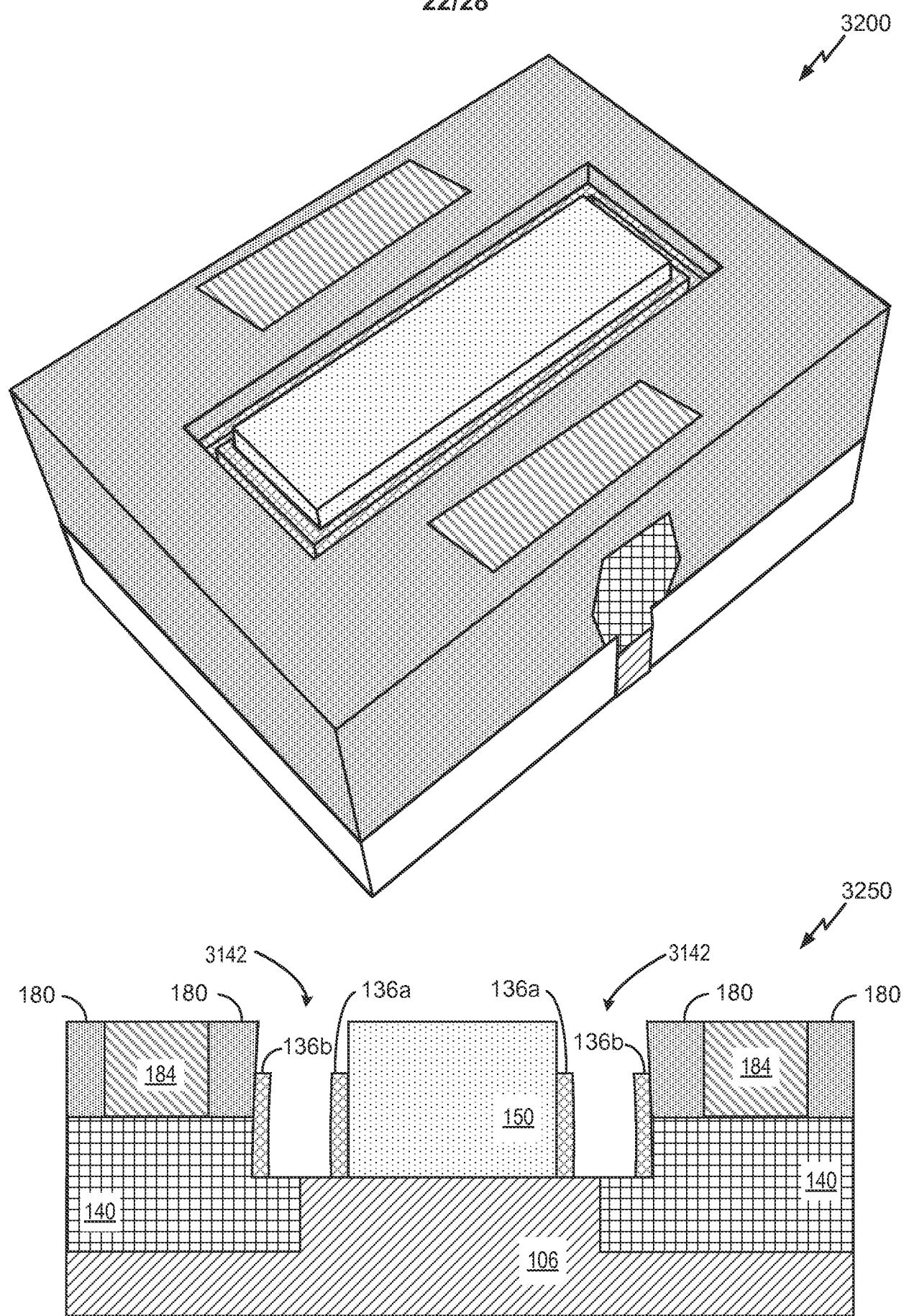

**[00101]** Referring to FIG. 32, a seventh illustrative diagram of at least one stage of the third process of fabricating the semiconductor device after removing a sacrificial spacer is depicted and generally designated 3200. FIG. 32 also illustrates a cross section 3250 through the fin of the semiconductor device. The sacrificial spacer 522 may be removed using a chemical or reactive gas chemistry. For example, a hydrogen reaction or a standard clean 1 type may be used to remove the sacrificial spacer 522 without performing an etch operation. Removal of the sacrificial spacer 522 may not affect (e.g., remove) the first spacer structure 136a or the second spacer structure 136b. Removal of the sacrificial spacer 522 may extend the cavity 3142 such that the cavity 3142 is defined by the substrate 106 (e.g., the fin) and/or the S/D region 140.

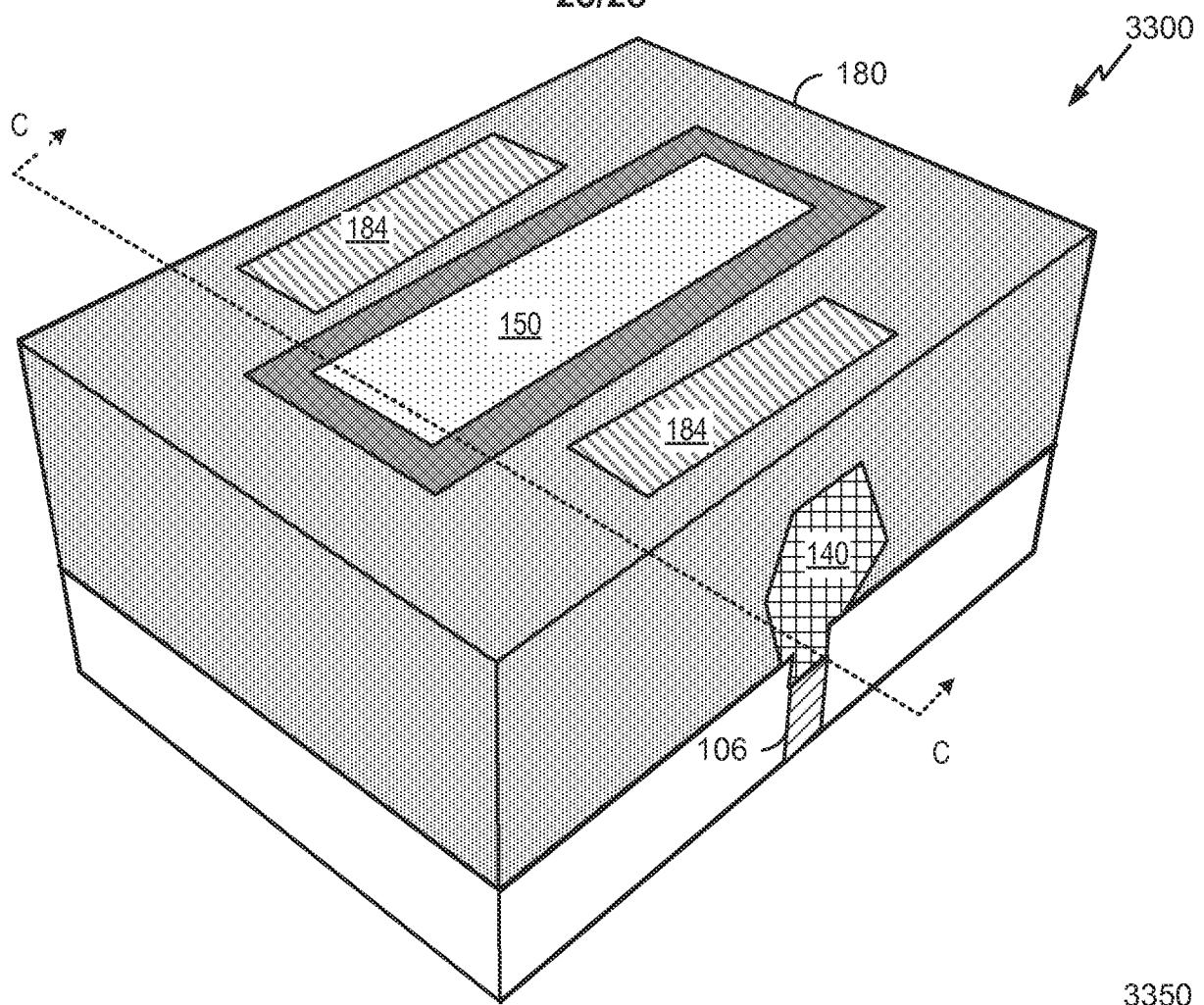

**[00102]** Referring to FIG. 33, an eighth illustrative diagram of at least one stage of the third process of fabricating the semiconductor device after forming a third spacer material and after planarization is performed is depicted and generally designated 3300. FIG. 33 also illustrates a cross section 3350 through a line C-C of the semiconductor device. A third spacer structure 136c may be formed on the semiconductor device. For

example, the third spacer structure 136c may be non-conformally deposited on the semiconductor device. The third spacer structure 136c may extend at least part way into the cavity 3142 of FIG. 32 and may block (e.g., close) the opening 3112 through which the sacrificial spacer 522 was removed. By closing the opening 3112, a gap 120 (e.g., an air-gap or a vacuum gap) may be defined by the third spacer structure 136c, the first spacer structure 136a, and/or the second spacer structure 136b. The gap 120 may further be defined by the wafer 202, the substrate 106, and/or the S/D region 140. Additionally or alternatively, the gap 120 may further be defined by the fin.

**[00103]** In a particular embodiment, the third spacer structure 136c includes silicon nitride or another nitride, such as a nitride that includes carbon or boron. The third spacer structure 136c may be the same material or a different material than the first spacer structure 136a and/or the second spacer structure 136b. The third spacer structure 136c may be configured to operate as a cap or a seal to establish and define the gap 120. The semiconductor device of FIG. 32 may include or correspond to the semiconductor device 160 of FIG. 1B.

**[00104]** The semiconductor device may advantageously include the spacer 136 that defines the gap 120. The gap 120 may reduce a parasitic capacitance (e.g., a gate capacitance, such as a capacitance between the gate 150 and the contact 184). Additionally, the gap 120 may provide an AC performance improvement as compared to FinFET devices that do not have a defined gap.

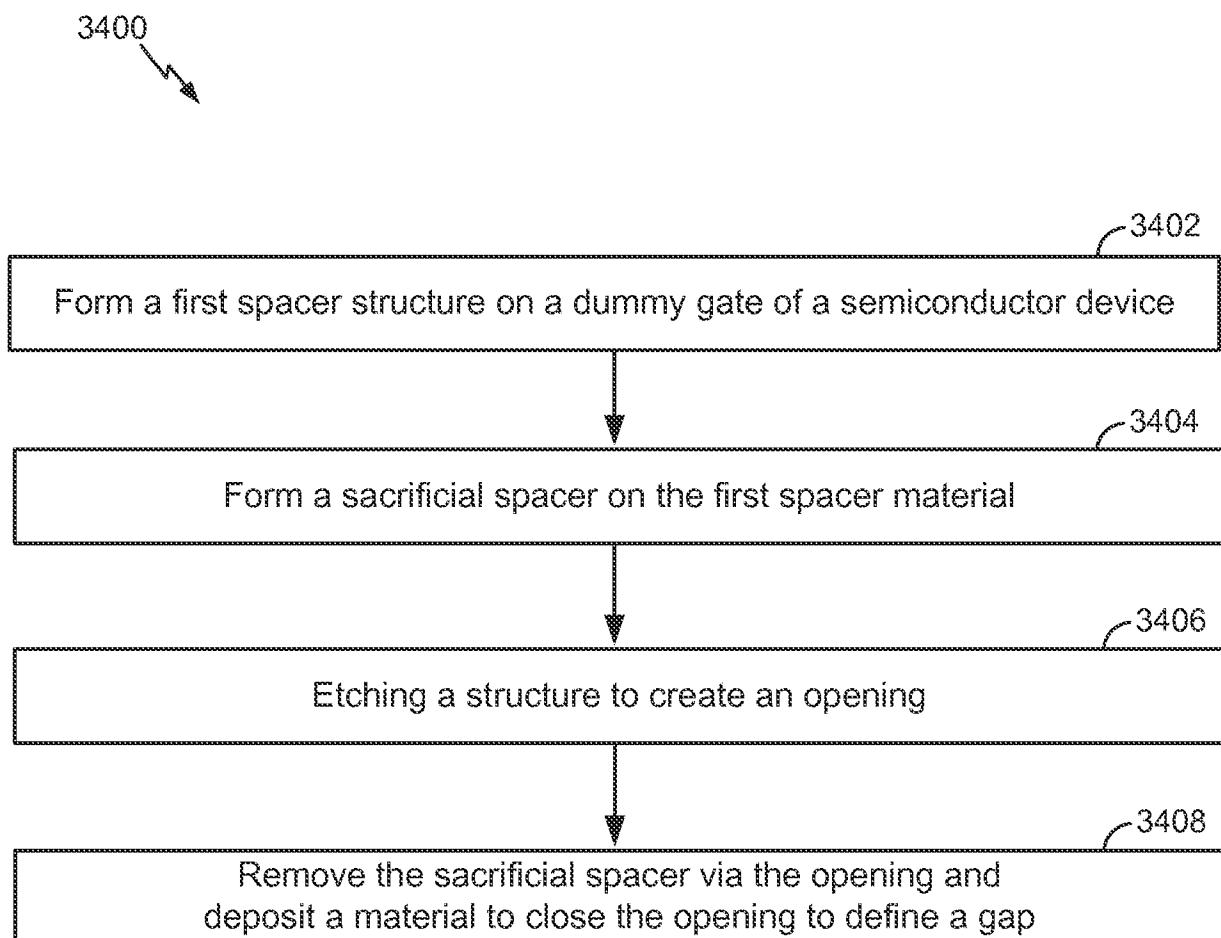

**[00105]** Referring to FIG. 34, a flow diagram of a first illustrative embodiment of a method 3400 of forming a semiconductor device is depicted. The semiconductor may include a field-effect transistor (FET), such as a FinFET that includes one or more fins, or a metal-oxide-semiconductor (MOS), such as a p-type metal-oxide-semiconductor (pMOS) or an n-type metal-oxide-semiconductor (nMOS) device, as illustrative, non-limiting examples. For example, the semiconductor device may include the semiconductor device 100 of FIG. 1A, the semiconductor device 160 of FIG. 1B, a semiconductor device formed according to the process illustrated by FIGS. 2-14, a semiconductor device formed according to the process illustrated by FIGS. 15-25, or a semiconductor device formed according to the process illustrated by FIGS. 26-33.

**[00106]** The method 3400 includes forming a first spacer structure on a dummy gate of a

- 23 -

semiconductor device, at 3402. The first spacer structure may include an oxide or a nitride. The dummy gate may be formed on a substrate of the semiconductor device. For example, the first spacer structure may include or correspond to the spacer 136 of FIGS. 1A-1B or the first spacer structure 136a of FIG. 1B and FIG. 4, or a combination thereof. The dummy gate may include or correspond to the dummy gate 304 of FIG. 3.

**[00107]** The method 3400 further includes forming a sacrificial spacer on the first spacer material, at 3404. The sacrificial spacer may include or correspond to the sacrificial spacer 522 of FIG. 5.

**[00108]** The method 3400 further includes etching a structure to create an opening, at 3406. The structure may be in contact with (e.g., adjacent to) the sacrificial spacer. Etching the structure may expose a portion of the sacrificial spacer. The structure may include a substrate (e.g., a fin portion of the substrate), such as the substrate 106 of FIGS. 1A-1B, or the structure may include the first spacer structure and/or a second spacer structure. The second spacer structure may include or correspond to the spacer 136 of FIGS. 1A-1B or the second spacer structure 136b of FIG. 1B and FIG. 6, or a combination thereof. The opening may correspond to the opening 712 of FIG. 7, the opening 1812 of FIG. 18, or the opening 3112 of FIG. 31.

**[00109]** The method 3400 further includes removing the sacrificial spacer via the opening and depositing a material to close the opening to define a gap, at 3408. The sacrificial spacer 522 may be removed using a chemical or reactive gas chemistry. For example, a hydrogen reaction or a standard clean 1 type may be used to remove the sacrificial spacer 522 without performing an etch operation. The material may be deposited by being epitaxially grown, such as epitaxially grown on a substrate. The material may include a source/drain material of the source/drain region 140 of FIGS. 1A-B or a material of a third spacer structure 136c of FIG. 1B. The gap may include or correspond to the gap 120 of FIGS. 1A-B. The gap may be defined by a portion of a source/drain region of the semiconductor device, such as the source/drain region 140 of FIGS. 1A-B. The gap may be positioned between a gate of the semiconductor device and a contact coupled to the source/drain region. The gap may reduce a parasitic capacitance associated with the semiconductor device.

**[00110]** In a particular embodiment, a second spacer structure may be formed on the

sacrificial spacer. For example, the second spacer structure may be formed on a portion of the first spacer structure. A spacer (e.g., the spacer 136 of FIG. 1B) of the semiconductor device comprises at least the first spacer structure and the second spacer structure. The first spacer structure and the second spacer structure may include the same material. A portion of the material may be positioned between the first spacer structure and the second spacer structure. The first spacer structure and the second spacer structure may define the gap.

**[00111]** In another particular embodiment, the method 3400 may include establishing the opening. The opening may be created by removing a portion of a substrate, such as a portion of a fin of the semiconductor device (e.g., the opening 712 of FIG. 7). Alternatively, the opening may be created by removing a portion the first spacer structure, a portion of a second spacer structure, a portion of the sacrificial spacer, or a combination thereof (e.g., the opening 1812 of FIG. 18 or the opening 3112 of FIG. 31). For example, the opening by be defined by the first spacer structure, a second spacer structure, a dielectric layer, the dummy gate, or a combination thereof. As another example, the opening may be defined by the first spacer structure, a second spacer structure, a dielectric layer, a gate, or a combination thereof.

**[00112]** In another particular embodiment, the dummy gate may be removed to create a cavity, such as the cavity 1144 of FIG. 11, the cavity 2244 of FIG. 22, or the cavity 2744 of FIG. 27. For example, the dummy gate may be removed prior to removing the sacrificial spacer. As another example, the sacrificial spacer may be removed prior to removing the dummy gate. A gate may be formed in the cavity, such as the gate 150 of FIGS. 1A-B. The gate may be coupled to a channel region of the substrate, such as a channel included in a fin of the semiconductor device. The gate may include a high K material. A contact, such as the contact 148 of FIGS. 1A-B, may be formed subsequent to forming the gate. The contact may be electrically coupled to a source/drain region of the semiconductor device.

**[00113]** In a particular embodiment, the source/drain region is formed on a substrate of the semiconductor device and a dielectric layer, such as the dielectric material 180 of FIGS. 1A-B, is deposited on the source/drain region. A portion of the dielectric layer may be removed to create a cavity, such as the cavity 1346 of FIG. 13, the cavity 2446

of FIG. 24, or the cavity 2946 of FIG. 29, and the contact may be formed in the cavity. For example, the contact may be formed prior to removing the sacrificial spacer. As another example, the contact may be formed prior to removing the sacrificial spacer.

**[00114]** The method 3400 may be used to define a gap positioned between a gate and contact of a semiconductor device. The gap may reduce a parasitic capacitance (e.g., a gate capacitance, such as a capacitance between the gate and the contact). Additionally, the gap may provide an AC performance improvement as compared to a semiconductor device that does not have a defined gap.

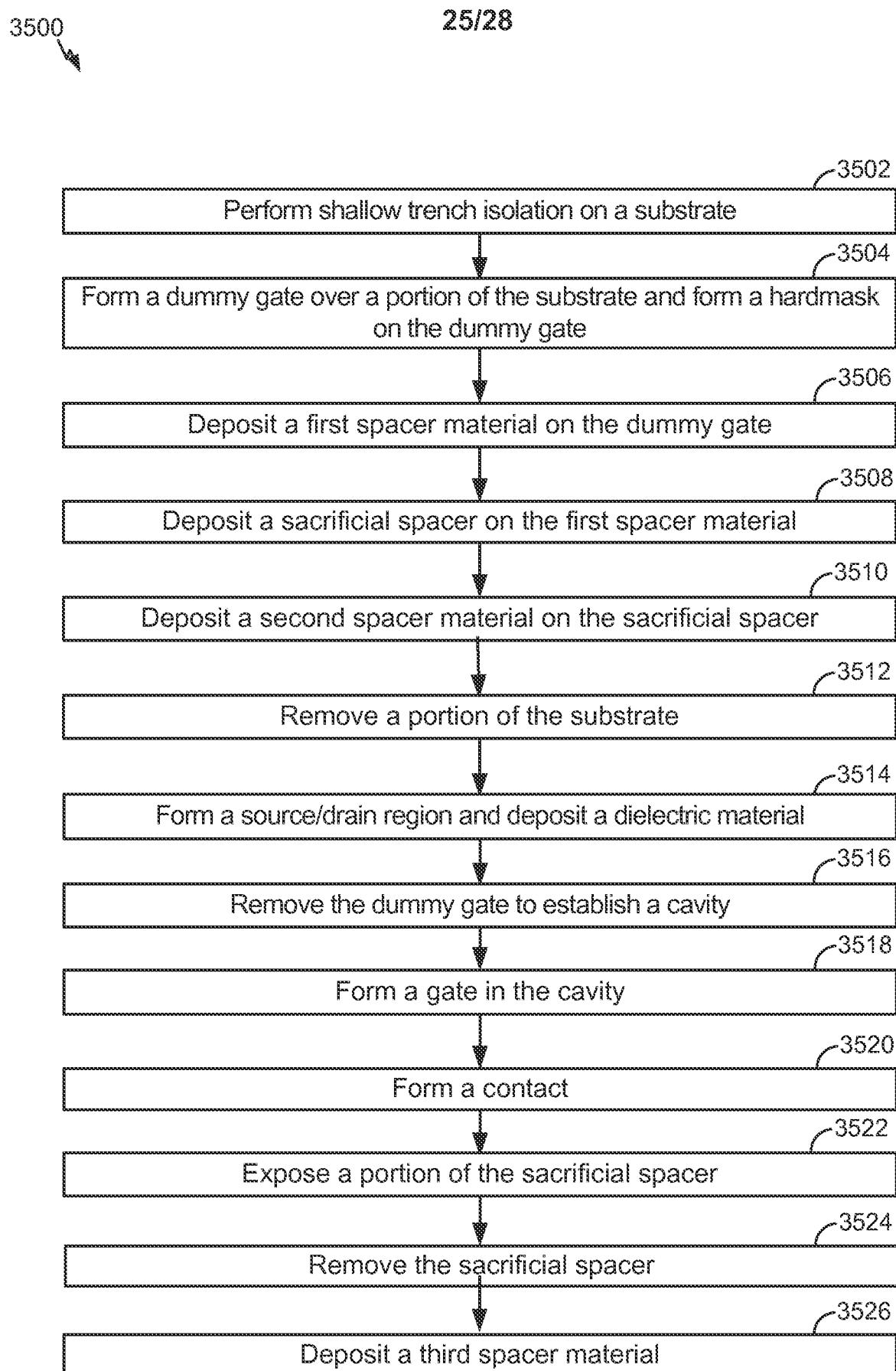

**[00115]** Referring to FIG. 35, a flow diagram of an illustrative embodiment of a method 3500 of forming a semiconductor device. For example, the semiconductor device may include the semiconductor device 160 of FIG. 1B or a semiconductor device formed according to the process illustrated by FIGS. 26-33.

**[00116]** The method 3500 may include performing shallow trench isolation on a substrate, at 3502. For example, the substrate may include or correspond to the substrate 106 of FIG. 1B, the wafer 202 of FIG. 2, or a combination thereof.

**[00117]** The method 3500 may further include forming a dummy gate over a portion of the substrate and forming a hardmask on the dummy gate, at 3504. The dummy gate and the hardmask may include or correspond to the dummy gate 304 and the hardmask 310 of FIG. 3, respectively.

**[00118]** The method 3500 may also include depositing a first spacer material on the dummy gate, at 3506. The first spacer material may be deposited directly on and/or may be in contact with the dummy gate. The first spacer material may include or correspond to the spacer 136 (e.g., the first spacer structure 136a) of FIG. 1B.

**[00119]** The method 3500 may further include depositing a sacrificial spacer on the first spacer material, at 3508. The sacrificial spacer may be deposited directly on and/or may be in contact with the first spacer material. The sacrificial spacer may include or correspond to the sacrificial spacer 522 of FIG. 5.

**[00120]** The method 3500 may also include depositing a second spacer material on the sacrificial spacer, at 3510. The second spacer may be deposited directly on and/or may

be in contact with the first spacer material, the sacrificial spacer, or a combination thereof. The second spacer may include or correspond to the spacer 136 (e.g., the second spacer structure 136b) of FIG. 1B. An etch process may be performed after the second spacer material is deposited.

**[00121]** The method 3500 may further include removing a portion of the substrate, at 3512. The portion of the substrate that is removed may correspond to a source/drain region of the semiconductor device. Additionally or alternatively, the portion of the substrate that is removed may include or correspond to a portion of a fin of the substrate.

**[00122]** The method 3500 may also include forming a source/drain region and depositing a dielectric material, at 3514. The source/drain region and the dielectric material may include or correspond to the source/drain region 140 of FIG. 1B and the dielectric material 180 of FIG. 1B, respectively. After the dielectric material is deposited, a chemical mechanical planarization (CMP) process (e.g., a chemical mechanical polish) may be performed to remove a portion of the dielectric material and the hardmask. By removing the hardmask, the CMP may expose the dummy gate, such as a surface of the dummy gate.

**[00123]** The method 3500 may further include removing the dummy gate to establish a cavity, at 3516, and forming a gate in the cavity, at 3518. The cavity may include or correspond to the cavity 2744 of FIG. 27. The gate may include or correspond to the gate 150 of FIG. 1B.

**[00124]** The method 3500 may also include forming a contact, at 3520. To form the contact, a portion of the dielectric material may be removed to form a cavity (e.g., a trench), such as the cavity 2946 of FIG. 29, and the contact may be formed in the cavity. The contact may include or correspond to the contact 184 of FIG. 1B.

**[00125]** The method 3500 may further include exposing a portion of the sacrificial spacer, at 3522, and removing the sacrificial spacer, at 3524. The sacrificial spacer may be exposed by removing a portion of a spacer (including the first spacer material and the second spacer material). For example, removing the portion of the spacer may include removing a portion of the first spacer material, a portion of the second spacer material,

or a combination thereof. Removal of the portion of the spacer may establish an opening, such as the opening 3112 of FIG. 31, through which the sacrificial spacer may be removed.

**[00126]** The method 3500 may also include depositing a third spacer material, at 3526. The third spacer material may be deposited to close (e.g., fill) the opening. Closing the opening may define a gap, such as an air-gap or a vacuum gap. The gap may include or correspond to the gap 120 of FIG. 1B. The third spacer material may include or correspond to the third spacer structure 136c. After the third spacer material is deposited, a CMP process may be performed to remove a portion of the third spacer material.

**[00127]** The method 3500 may be used to define a gap positioned between a gate and contact of a semiconductor device. The gap may reduce a parasitic capacitance (e.g., a gate capacitance, such as a capacitance between the gate and the contact). Additionally, the gap may provide an AC performance improvement as compared to a semiconductor device that does not have a defined gap.

**[00128]** Referring to FIG. 36, a flow diagram of an illustrative embodiment of a method 3600 of forming a semiconductor device is depicted. For example, the semiconductor device may include the semiconductor device 160 of FIG. 1B or a semiconductor device formed according to the process illustrated by FIGS. 15-25.

**[00129]** The method 3600 may include forming a source/drain region and depositing a dielectric material, at 3602. The source/drain region and the dielectric material may include or correspond to the source/drain region 140 of FIG. 1B and the dielectric material 180 of FIG. 1B, respectively. After the dielectric material is deposited, a chemical mechanical planarization (CMP) process (e.g., a chemical mechanical polish) may be performed to remove a portion of the dielectric material and the hardmask. By removing the hardmask, the CMP may expose a dummy gate, such as a surface of the dummy gate. Alternatively or additionally, the CMP process may expose a spacer, such as a surface of a spacer formed by a first spacer material and a second spacer material. The first spacer material and the second spacer material may include or correspond to the first spacer structure 136a and the second spacer structure 136b of FIG. 1B, respectively.

**[00130]** The method 3600 may further include exposing a portion of a sacrificial spacer, at 3604, and removing the sacrificial spacer, at 3606. The sacrificial spacer may be exposed by removing a portion of a spacer (including the first spacer material and second spacer material). For example, removing the portion of the spacer may include removing a portion of the first spacer material, a portion of the second spacer material, or a combination thereof. Removal of the portion of the spacer may establish an opening, such as the opening 1812 of FIG. 18, through which the sacrificial spacer may be removed.

**[00131]** The method 3600 may also include depositing a third spacer material, at 3608. The third spacer material may be deposited to close (e.g., fill) the opening. Closing the opening may define a gap, such as an air-gap or a vacuum gap. The gap may include or correspond to the gap 120 of FIG. 1B. The third spacer material may include or correspond to the third spacer structure 136c of FIG. 1B. After the third spacer material is deposited, a CMP process may be performed to remove a portion of the third spacer material.

**[00132]** The method 3600 may also include removing a dummy gate to establish a cavity, at 3610, and forming a gate in the cavity, at 3612. The cavity may include or correspond to the cavity 2244 of FIG. 22. The gate may include or correspond to the gate 150 of FIG. 1B.

**[00133]** The method 3600 may further include forming a contact, at 3614. To form the contact, a portion of the dielectric material may be removed to form a cavity (e.g., a trench), such as the cavity 2446 of FIG. 24, and the contact may be formed in the cavity. The contact may include or correspond to the contact 184 of FIG. 1B.

**[00134]** The method 3600 may be used to define a gap positioned between a gate and contact of a semiconductor device. The gap may reduce a parasitic capacitance (e.g., a gate capacitance, such as a capacitance between the gate and the contact). Additionally, the gap may provide an AC performance improvement as compare to a semiconductor device that does not have a defined gap.

**[00135]** Referring to FIG. 37, a flow diagram of an illustrative embodiment of a method 3700 of forming a semiconductor device is depicted. For example, the semiconductor

device may include the semiconductor device 100 of FIG. 1A or a semiconductor device formed according to the process illustrated by FIGS. 2-14.

**[00136]** The method 3700 may include removing a sacrificial spacer via an opening, at 3702. The sacrificial spacer may include or correspond to the sacrificial spacer 522 of FIG. 5. The opening may include or correspond to the opening 712 of FIG. 7.

**[00137]** The method 3700 may further include forming a source/drain region and depositing a dielectric material, at 3704. The source/drain region may be formed by epitaxially growing a source/drain material. Forming the source/drain region may close the opening and define a gap, such as an air-gap or a vacuum gap. The source/drain region and the dielectric material may include or correspond to the source/drain region 140 of FIG. 1A and the dielectric material 180 of FIG. 1A, respectively. After the dielectric material is deposited, a chemical mechanical planarization (CMP) process (e.g., a chemical mechanical polish) may be performed to remove a portion of the dielectric material and the hardmask. By removing the hardmask, the CMP may expose the dummy gate, such as a surface of the dummy gate.

**[00138]** The method 3700 may also include removing a dummy gate to establish a cavity, at 3706, and forming a gate in the cavity, at 3708. The cavity may include or correspond to the cavity 1144 of FIG. 11. The gate may include or correspond to the gate 150 of FIG. 1A.

**[00139]** The method 3700 may further include forming a contact, at 3710. To form the contact, a portion of the dielectric material may be removed to form a cavity (e.g., a trench), such as the cavity 1346 of FIG. 13, and the contact may be formed in the cavity. The contact may include or correspond to the contact 184 of FIG. 1A.

**[00140]** The method 3700 may be used to define a gap positioned between a gate and contact of a semiconductor device. The gap may reduce a parasitic capacitance (e.g., a gate capacitance, such as a capacitance between the gate and the contact). Additionally, the gap may provide an AC performance improvement as compared to a semiconductor device that does not have a defined gap.

**[00141]** The methods of FIGS. 34-37 may be implemented by a field-programmable gate

- 30 -

array (FPGA) device, an application-specific integrated circuit (ASIC), a processing unit such as a central processing unit (CPU), a digital signal processor (DSP), a controller, another hardware device, firmware device, or any combination thereof. As an example, the methods of FIG. 34-37 can be performed by one or more processors that execute instructions to control fabrication equipment.

**[00142]** Referring to FIG. 38, a block diagram of a particular illustrative embodiment of a wireless communication device 3800 is depicted. The device 3800 may include the semiconductor device 100 of FIG. 1A, the semiconductor device 160 of FIG. 1B, a semiconductor device formed according to the process illustrated by FIGS. 2-14, a semiconductor device formed according to the process illustrated by FIGS. 15-25, a semiconductor device formed according to the process illustrated by FIGS. 26-33, a semiconductor device formed using at least one of the methods of FIGS. 34-37, or a combination thereof.

**[00143]** The device 3800 includes a processor 3810, such as a digital signal processor (DSP), coupled to a memory 3832. The processor 3810 may include a semiconductor device 3864. For example, the semiconductor device 3864 may be the semiconductor device 100 of FIG. 1A, the semiconductor device 160 of FIG. 1B, a semiconductor device formed according to the process illustrated by FIGS. 2-14, a semiconductor device formed according to the process illustrated by FIGS. 15-25, a semiconductor device formed according to the process illustrated by FIGS. 26-33, a semiconductor device formed using at least one of the methods of FIGS. 34-37, or a combination thereof.

**[00144]** The memory 3832 includes instructions 3868 (e.g., executable instructions) such as computer-readable instructions or processor-readable instructions. The instructions 3868 may include one or more instructions that are executable by a computer, such as the processor 3810.

**[00145]** FIG. 38 also shows a display controller 3826 that is coupled to the processor 3810 and to a display 3828. A coder/decoder (CODEC) 3834 can also be coupled to the processor 3810. A speaker 3836 and a microphone 3838 can be coupled to the CODEC 3834.

**[00146]** FIG. 38 also indicates that a wireless interface 3840, such as a wireless controller, can be coupled to the processor 3810 and to an antenna 3842. In a particular embodiment, the processor 3810, the display controller 3826, the memory 3832, the CODEC 3834, and the wireless interface 3840 are included in a system-in-package or system-on-chip device 3822. In a particular embodiment, an input device 3830 and a power supply 3844 are coupled to the system-on-chip device 3822. Moreover, in a particular embodiment, as illustrated in FIG. 38, the display 3828, the input device 3830, the speaker 3836, the microphone 3838, the antenna 3842, and the power supply 3844 are external to the system-on-chip device 3822. However, each of the display 3828, the input device 3830, the speaker 3836, the microphone 3838, the antenna 3842, and the power supply 3844 can be coupled to a component of the system-on-chip device 3822, such as an interface or a controller. Although the semiconductor device 3864 is depicted as being included in the processor 3810, the semiconductor device 3864 may be included in another component of the device 3800 or a component coupled to the device 3800. For example, the semiconductor device 3864 may be included in the memory 3832, the wireless interface 3840, the power supply 3844, the input device 3830, the display 3828, the display controller 3826, the CODEC 3834, the speaker 3836, or the microphone 3838.

**[00147]** In conjunction with one or more of the described embodiments of FIGS. 1-38, an apparatus is disclosed that may include means for activating a channel region of a semiconductor device. The channel region may be coupled to a source/drain region of the semiconductor device. The means for activating may correspond to the gate 150 of FIGS. 1A-1B, one or more other structures, devices, or circuits configured to activate the channel region, or any combination thereof.

**[00148]** The apparatus may also include means for conducting current. The means for conducting may be coupled to the source/drain region. The source/drain region may define a gap positioned between the means for activating and the means for conducting. A height of the gap is less than a height of the means for activating the channel region. The means for conducting may correspond to the contact 184 of FIG. 1A-B, one or more other, structures, devices, or circuits configured to conduct current, or any combination thereof.

**[00149]** In conjunction with the described embodiments of FIGS. 1-38, a method is disclosed that may include a first step for forming a first spacer structure on a dummy gate of a semiconductor device, such as described by the method 3400 of FIG. 34 at 3402 or the method 3500 of FIG. 35 at 3506, or by depositing a first spacer material of the first spacer structure on the dummy gate, by epitaxial growth of a first spacer material of the first spacer structure on the dummy gate, by one or more other processes configured to form the first spacer structure on the dummy gate of the semiconductor device, or any combination thereof.