(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4158564号

(P4158564)

(45) 発行日 平成20年10月1日(2008.10.1)

(24) 登録日 平成20年7月25日(2008.7.25)

|              |              |

|--------------|--------------|

| (51) Int.Cl. | F 1          |

| H04L 7/04    | (2006.01)    |

| G06F 13/42   | (2006.01)    |

| H04B 10/00   | (2006.01)    |

| H04L 25/03   | (2006.01)    |

|              | HO 4 L 7/04  |

|              | G0 6 F 13/42 |

|              | HO 4 B 9/00  |

|              | HO 4 L 25/03 |

|              | B            |

|              | 3 4 O A      |

|              | B            |

|              | Z            |

請求項の数 8 (全 10 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2003-69938 (P2003-69938)    |

| (22) 出願日  | 平成15年3月14日 (2003.3.14)        |

| (65) 公開番号 | 特開2004-282330 (P2004-282330A) |

| (43) 公開日  | 平成16年10月7日 (2004.10.7)        |

| 審査請求日     | 平成18年2月21日 (2006.2.21)        |

|           |                                                     |

|-----------|-----------------------------------------------------|

| (73) 特許権者 | 000005496<br>富士ゼロックス株式会社<br>東京都港区赤坂九丁目7番3号          |

| (74) 代理人  | 100090583<br>弁理士 田中 清                               |

| (74) 代理人  | 100098110<br>弁理士 村山 みどり                             |

| (72) 発明者  | 上村 健<br>神奈川県足柄上郡中井町境430 グリー<br>ンテクなかい 富士ゼロックス株式会社内  |

| (72) 発明者  | 舟田 雅夫<br>神奈川県足柄上郡中井町境430 グリー<br>ンテクなかい 富士ゼロックス株式会社内 |

最終頁に続く

(54) 【発明の名称】同期伝送システム

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のクロック信号の出力手段とデータ信号の入力手段および/または出力手段を備える第1のノードと、第2のクロック信号の入力手段とデータ信号の入力手段および/または出力手段を備える第2のノードとの間で伝送路を介して信号伝送を行うための同期伝送システムであって、前記第1のノードおよび/または前記第2のノードが前記第1のクロック信号および/または前記第2のクロック信号のデューティ比を調整信号に従って変更するデューティ調整回路を備えたことを特徴とする同期伝送システム。

## 【請求項 2】

前記調整信号は、前記第1のノードから前記第2のノードへの信号伝送時間と、前記第2のノードから前記第1のノードへの信号伝送時間と、前記第2のノードにおけるデータ信号の入力から出力に至るまでの処理時間とに基づいて生成されることを特徴とする、請求項1に記載の同期伝送システム。 10

## 【請求項 3】

複数の前記第1のノードおよび/または複数の前記第2のノードを備えたことを特徴とする、請求項1または2に記載の同期伝送システム。

## 【請求項 4】

前記調整信号は、前記各第1のノードから前記各第2のノードへの信号伝送時間の最大値と、前記各第2のノードから前記各第1のノードへの信号伝送時間の最大値と、前記各第2のノードにおけるデータ信号の入力から出力に至るまでの処理時間の最大値とに基づい 20

て生成されることを特徴とする、請求項 3 に記載の同期伝送システム。

【請求項 5】

前記第 1 のノードはテスト信号を前記第 2 のノードへ送信し、前記第 2 のノードは前記テスト信号を前記第 1 のノードに返信し、前記テスト信号と前記返信されたテスト信号との時間差より前記信号伝送時間を算出することを特徴とする、請求項 2 ~ 4 のいずれかに記載の同期伝送システム。

【請求項 6】

前記テスト信号は、システムの電源投入直後および / または前記伝送路の未使用時間に送信されることを特徴とする、請求項 5 に記載の同期伝送システム。

【請求項 7】

前記出力手段は電気信号を光信号に変換する電気光変換手段を備え、前記入力手段は光信号を電気信号に変換する光電気変換手段を備え、前記電気光変換手段と前記光電気変換手段との間を光伝送路により光学的に接続したことを特徴とする、請求項 1 ~ 6 のいずれかに記載の同期伝送システム。

【請求項 8】

前記信号伝送時間は、前記電気光変換手段における電気光変換時間および前記光電気変換手段における光電気変換時間を含むことを特徴とする請求項 7 に記載の同期伝送システム。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、C P U メモリバスのような高速かつ低レンテンシを要求される伝送路を介して複数のノード間で信号伝送を行うための同期伝送システムに関する。

【0002】

【従来の技術】

C P U の動作周波数は半導体技術の進歩により向上してきたが、C P U の動作周波数に比べると、C P U メモリ間の信号伝送周波数は一桁低く、C P U メモリシステム全体の性能ボトルネックとなっている。一般には伝送路の帯域を向上する方法として、シリアル伝送が知られている。これは複数の信号を並列直列変換により速度変換した後に送信し、受信側にて直列並列変換を施して元の複数の信号を得る方法である。

【0003】

しかし C P U メモリ間のデータ転送においては、帯域向上だけでなく両者間のデータ転送遅延時間、いわゆるレイテンシの低減が必要である。上述のシリアル伝送は従来方法に加えて並列直列変換、および直列並列変換に要する時間分のレイテンシが増大する問題があった。

【0004】

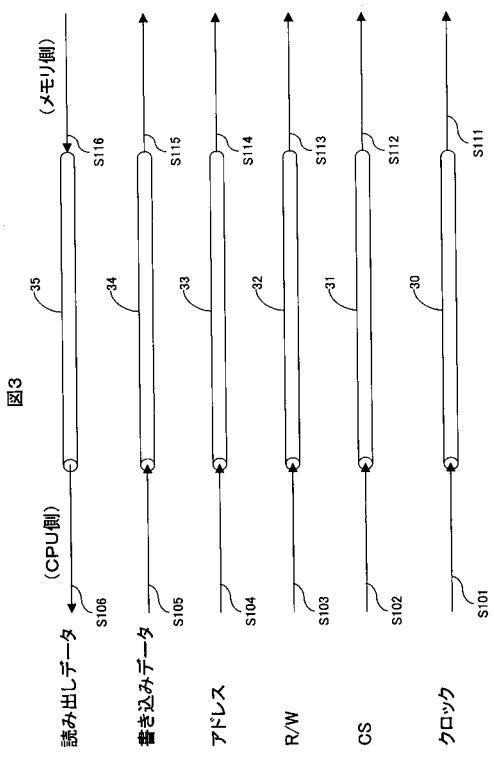

図 3 は、従来の同期伝送システムの一例を示す図である。このシステムは、1 つの C P U と 1 つのメモリ間を伝送路 3 0 ~ 3 5 で接続したものである。図示のように、C P U 側からクロック信号 S 1 0 1 、チップセレクト ( C S ) 信号 S 1 0 2 、書き込み / 読み出し ( R / W ) 信号 S 1 0 3 、アドレス信号 S 1 0 4 、および書き込みデータ信号 S 1 0 5 が、伝送路 3 0 ~ 3 4 を介して伝送され、メモリ側でそれぞれ対応する信号 S 1 1 1 、 S 1 1 2 、 S 1 1 3 、 S 1 1 4 、 S 1 1 5 として受信される。一方、メモリ側からは、読み出しデータ信号 S 1 1 6 が伝送路 3 5 を介して伝送され、C P U 側で信号 S 1 0 6 として受信される。

【0005】

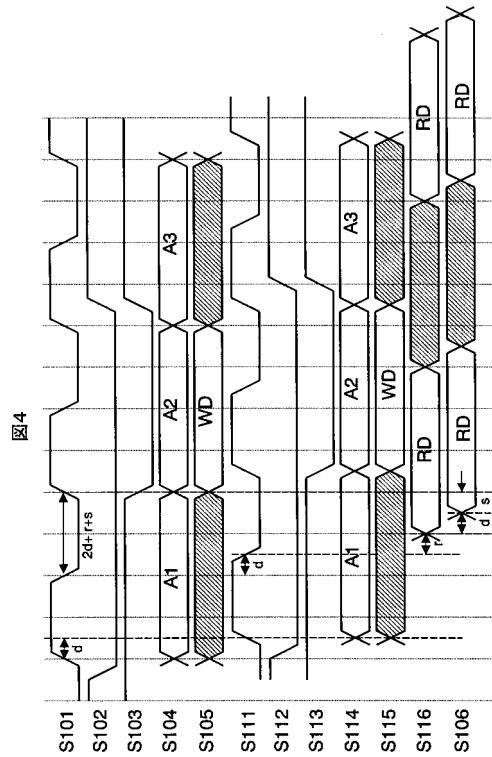

図 4 は、図 3 のシステムにおけるタイミングチャートを示す図である。図のように、C P U から出力される信号 S 1 0 2 ~ S 1 0 5 は、いずれもデューティ 5 0 % であるクロック信号 S 1 0 1 の立ち上がりエッジに同期して出力される。R / W 信号 S 1 0 3 は、値 " 1 " が読み出し、値 " 0 " が書き込み指示を表す。C S 信号 S 1 0 2 は、値 " 0 " が有効とする。図 4 中の記号 d は C P U とメモリ間の信号伝送時間を表す。以下では信号伝送時間

10

20

30

40

50

$d$  は、あるノードから他のノードへの信号伝送に要する時間を表し、ノード間に存在する伝送路や回路部品の伝播遅延時間、更にラッチ回路を通過する際に生じる同期信号の待ち時間等を全て含む。但し図 4 における  $d$  は伝送路 30 ~ 35 の伝播遅延時間に相当する。図 4 の最初の一周期は読み出し動作を表し、メモリアドレス A1 からデータ RD を読み出す。ここではメモリ側で受信するクロック信号 S111 の立下りエッジから、時間  $r$  だけ経過後に読み出しデータ信号 S116 が確定するものとする。図中の記号  $s$  は CPU 側のデータ信号のセットアップ時間を示す。このシステムの場合、レイテンシの下限 L0 と動作周波数の上限 F0 は以下のようになる。

$$L_0 = \max(d, 2d + r + s) \times 2 = 4d + 2r + 2s, F_0 = 1 / L_0$$

【0006】

10

なお、入力クロック信号に基づき所望のデューティを持つクロック信号を生成するクロック生成回路および当該クロック生成回路により生成されたクロック信号で動作タイミングを制御する半導体記憶装置が特許文献 1 に記載されているが、この技術はメモリ内における異なる動作間の衝突を回避するためのものであり、CPU メモリバス等におけるレイテンシの問題を解決するものではない。

【特許文献 1】

特開 2000 - 99194 号公報

【0007】

20

【発明が解決しようとする課題】

従って本発明の目的は、データ転送におけるレイテンシを低減し、かつ伝送帯域を向上し得る同期伝送システムを提供することにある。

【0008】

【課題を解決するための手段】

上記目的は、第 1 のクロック信号の出力手段とデータ信号の入力手段および / または出力手段を備える第 1 のノードと、第 2 のクロック信号の入力手段とデータ信号の入力手段および / または出力手段を備える第 2 のノードとの間で伝送路を介して信号伝送を行うための同期伝送システムであって、前記第 1 のノードおよび / または前記第 2 のノードが前記第 1 のクロック信号および / または前記第 2 のクロック信号のデューティ比を調整信号に従って変更するデューティ調整回路を備えた同期伝送システムにより、達成される。

【0009】

30

ここで、前記調整信号は、前記第 1 のノードから前記第 2 のノードへの信号伝送時間と、前記第 2 のノードから前記第 1 のノードへの信号伝送時間と、前記第 2 のノードにおけるデータ信号の入力から出力に至るまでの処理時間とに基づいて生成することができる。また、本同期伝送システムは、複数の前記第 1 のノードおよび / または複数の前記第 2 のノードを備えることができる。この場合、前記調整信号は、前記各第 1 のノードから前記各第 2 のノードへの信号伝送時間の最大値と、前記各第 2 のノードから前記各第 1 のノードへの信号伝送時間の最大値と、前記各第 2 のノードにおけるデータ信号の入力から出力に至るまでの処理時間の最大値とに基づいて生成することができる。

【0010】

40

また、前記第 1 のノードはテスト信号を前記第 2 のノードへ送信し、前記第 2 のノードは前記テスト信号を前記第 1 のノードに返信し、前記テスト信号と前記返信されたテスト信号との時間差より前記信号伝送時間を算出することができる。前記テスト信号は、システムの電源投入直後および / または前記伝送路の未使用時間に送信することができる。

【0011】

さらに、前記出力手段は電気信号を光信号に変換する電気光変換手段を備え、前記入力手段は光信号を電気信号に変換する光電気変換手段を備え、前記電気光変換手段と前記光電気変換手段との間を光伝送路により光学的に接続することができる。前記信号伝送時間は、前記電気光変換手段における電気光変換時間および前記光電気変換手段における光電気変換時間を含むことができる。

このように構成することにより、データ転送におけるレイテンシを低減し、かつ伝送帯域

50

向上することができる。

#### 【0012】

##### 【発明の実施の形態】

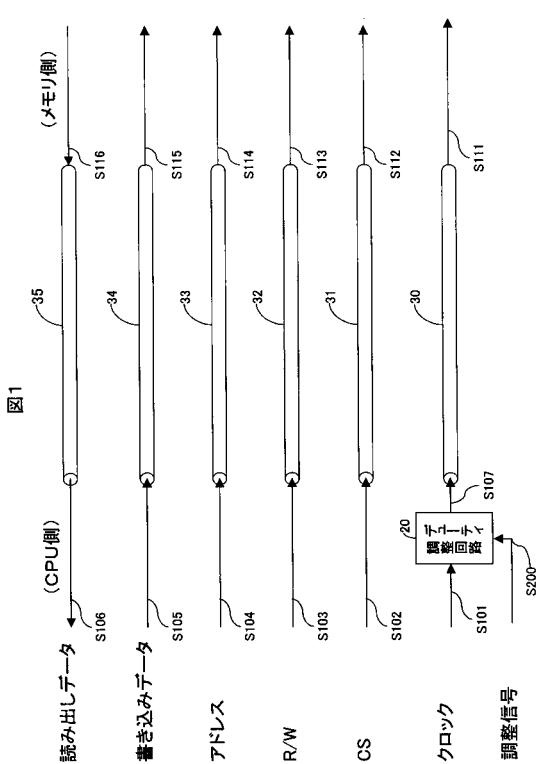

図1は、本発明に係る同期伝送システムの一実施例を示す図である。本実施例は、1つのCPUと1つのメモリ間を伝送路30～35で接続した例を示しており、CPU側に調整信号S200によりクロック信号のデューティ比を変更可能なデューティ調整回路20を備える。この調整信号S200は、例えば、CPUからメモリへの信号伝送時間と、メモリからCPUへの信号伝送時間と、メモリにおけるデータ信号の入力から出力に至るまでの処理時間とに基づいて生成することができる。調整信号の生成の仕方については後述する。

10

#### 【0013】

図1において、CPU側のクロック信号S101は、デューティ調整回路20でデューティ比が変更されて信号S107となり、伝送路30を介して伝送され、メモリ側で信号S111として受信される。また、チップセレクト(CS)信号S102、書き込み/読み出し(R/W)信号S103、アドレス信号S104、および書き込みデータ信号S105は、伝送路31～34を介して伝送され、メモリ側でそれぞれ対応する信号S112、S113、S114、S115として受信される。一方、メモリ側からは、読み出しデータ信号S116が伝送路35を介して伝送され、CPU側で信号S106として受信される。

20

#### 【0014】

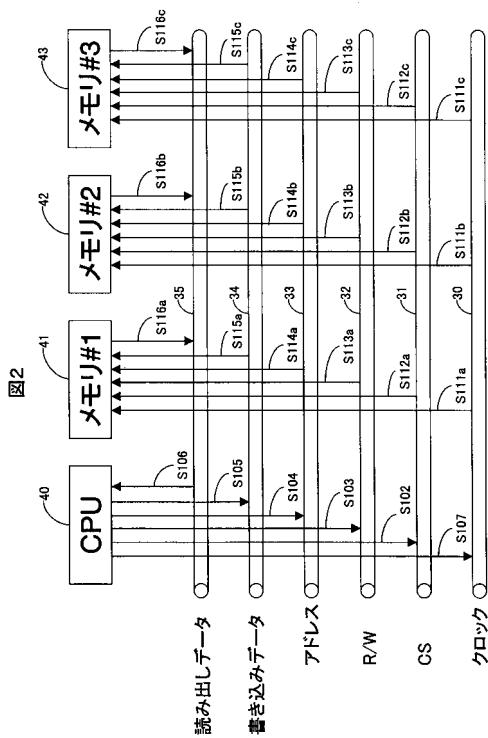

図2は、図1の本発明に係る同期伝送システムを用いて構成されるCPUメモリバスの一例を示すブロック図である。本CPUメモリバスは、1つのCPU40と複数のメモリ41～43とを備える。CPU40は、信号S107、S102～S105を伝送路30～34を介して送信し、伝送路35を介して信号S106を受信する。一方、メモリ41～43は、伝送路30～34を介して、それぞれ信号S111a～c、S112a～c、S113a～c、S114a～c、S115a～cを受信し、それぞれ信号S116a～cを伝送路35を介して伝送する。

30

#### 【0015】

図2のCPUメモリバスは、1つのCPUと複数のメモリとで構成されているが、複数のCPUと1つのメモリ、または、複数のCPUと複数のメモリとで構成することもできる。この場合、デューティ比を調整するための調整信号は、各CPUから各メモリへの信号伝送時間の最大値と、各メモリから各CPUへの信号伝送時間の最大値と、各メモリにおけるデータ信号の入力から出力に至るまでの処理時間の最大値とに基づいて生成することができる。すなわち、最も遅いものに合わせるのである。調整信号の生成の仕方については後述する。また、CPU側には図示しないがデューティ調整回路が備えられている。このデューティ調整回路は、CPU側でなくメモリ側に備えることもでき、また、CPU側およびメモリ側の両方に備えることもできる。

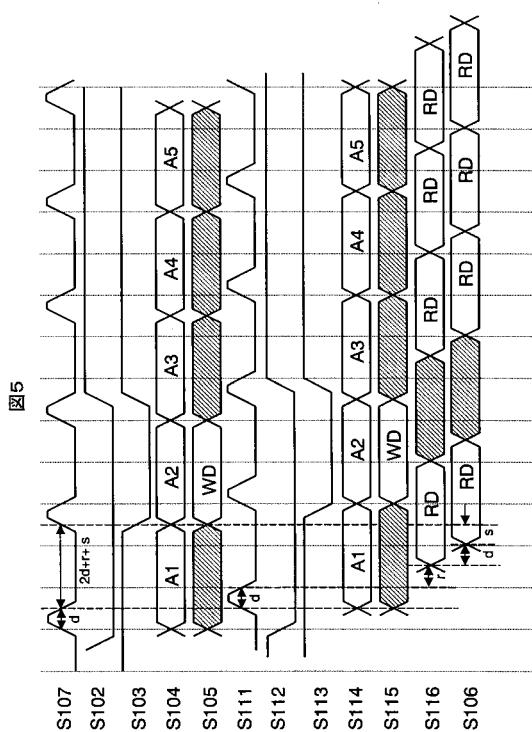

#### 【0016】

図5は、図1のシステムにおけるタイミングチャートを示す図である。図1のシステムは、クロック信号のデューティ調整回路20を含み構成されている。デューティ調整回路20は調整信号S200に従って動作し、デューティ比を $d / (3d + r + s)$ となるように調整した信号をクロック信号S107として出力する。ここで記号dは図4と同様にノード間の信号伝送時間を表す。図5の最初の一周期は読み出し動作を表し、メモリアドレスA1からデータRDを読み出す。ここではメモリ側で受信するクロック信号S111の立下りエッジから、時間rだけ経過後に読み出しデータ信号S116が確定するものとする。すなわち、時間rはメモリにおけるデータ信号の入力から出力に至るまでの処理時間である。また、記号sはCPU側のデータ信号のセットアップ時間を示す。この結果、タイミングチャートは図示のようになり、レイテンシの下限L1と動作周波数の上限F1は以下のようになる。

40

$$L1 = 3d + r + s, F1 = 1 / L1$$

50

例えば  $d = 10 \text{ ns}$ 、 $r = 10 \text{ ns}$ 、 $s = 5 \text{ ns}$  の場合、図 4 で説明した従来技術では  $F_0 = 14.3 \text{ MHz}$  であるのに対し、本実施例では  $F_1 = 22.2 \text{ MHz}$  となる。

#### 【0017】

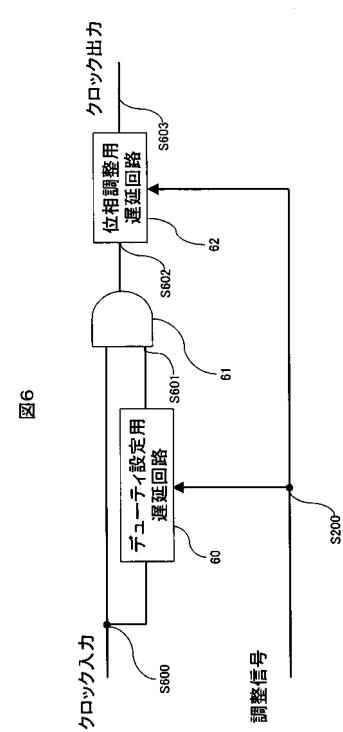

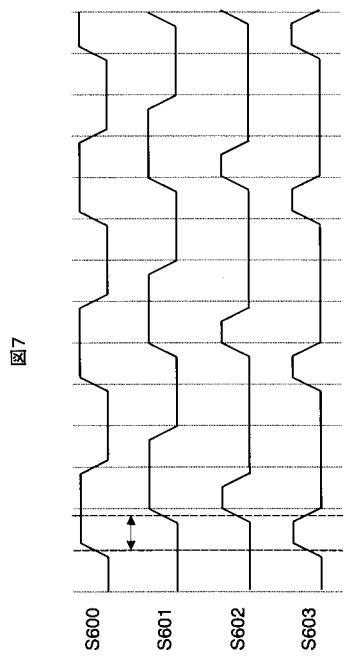

図 6 は、本発明に用いるデューティ調整回路の一実施例を示すブロック図である。本例のデューティ調整回路 20 は、デューティ設定用遅延回路 60、論理積回路 61、および位相調整用遅延回路 62 を備えて構成される。図 7 は、図 6 のデューティ調整回路におけるタイミングチャートである。以下、このタイミングチャートを用いてデューティ調整回路 20 の動作を説明する。まず、デューティ設定用遅延回路 60 は調整信号 S200 に従い、クロック信号 S600 のデューティ比が  $d / (3d + r + s)$  となるように、遅延された信号 S601 を出力する。論理積回路 61 は、信号 S600 と信号 S601 の論理積を信号 S602 として出力する。ここで、信号 S602 と信号 S600 とでは位相がずれているため、位相調整用遅延回路 62 は両信号の立上りエッジが同期するように遅延を設定し、クロック出力として信号 S603 を出力する。

#### 【0018】

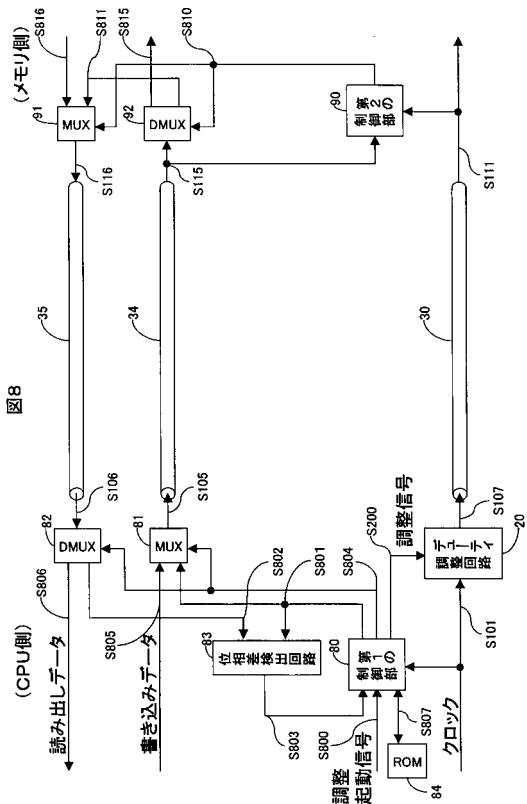

図 8 は、デューティ調整回路に入力される調整信号の生成方法の一例を示すブロック図である。図示のように、第 1 のノードである C P U 側には、伝送路 30 に対して設けられたデューティ調整回路 20 と、調整起動信号を入力し調整信号を出力する第 1 の制御部 80 と、伝送路 34、35 に対してそれぞれ設けられたマルチプレクサ ( MUX ) 81 およびデマルチプレクサ ( DMUX ) 82 と、位相差を検出する位相差検出回路 83 と、記憶装置である R O M 84 とが備えられている。また、第 2 のノードであるメモリ側には、伝送路 34 を介して信号を入力する第 1 の制御部 90 と、伝送路 35、34 に対してそれぞれ設けられたマルチプレクサ ( MUX ) 91 およびデマルチプレクサ ( DMUX ) 92 とが備えられている。

#### 【0019】

以下、図 8 を参照しながらデューティ調整信号 S200 の生成方法について説明する。まず、デューティ調整信号 S200 の算出に必要となる信号伝送時間  $d$ 、メモリの読み出し時間  $r$ 、C P U のセットアップ時間  $s$  のうち、メモリの読み出し時間  $r$  と C P U のセットアップ時間  $s$  はシステム固有の値であるため、予め算出し信号 S807 により R O M 84 に格納する。信号伝送時間  $d$  は伝送路の長さ等で変動するため、これを次のようにして算出する。第 1 の制御部 80 は、調整起動信号 S800 により起動され、信号 S804 によりマルチプレクサ 81 とデマルチプレクサ 82 に選択を指示し、各々信号 S801 と信号 S802 を選択する。そして、信号 S801 を伝送路 34 を介して伝送し、メモリ側に設けられた第 2 の制御部 90 に対して調整起動を指示する。第 2 の制御部 90 は調整起動を受けて、信号 S810 によりマルチプレクサ 91 とデマルチプレクサ 92 に選択を指示し、いずれも信号 S811 を選択する。なお、図中、信号 S805、S815 は書き込みデータ信号、信号 S806、S816 は読み込みデータ信号である。

#### 【0020】

次に、第 1 の制御部 80 は信号 S801 としてテスト信号を出力する。テスト信号はマルチプレクサ 81 および伝送路 34 を介してメモリ側へ伝送され、デマルチプレクサ 92、マルチプレクサ 91、および伝送路 35 を介して C P U 側へ戻る。位相差検出回路 83 は、元のテスト信号である信号 S801 と、戻された信号 S802 の位相差（時間差）を検出し、その検出結果を信号 S803 として第 1 の制御部 80 に出力する。信号 S803 は C P U 側とメモリ側の往復に要する伝送時間に相当し、この半分の値を上記の信号伝送時間  $d$  とする。第 1 の制御部 80 は、この算出された信号伝送時間  $d$  および予め算出されたメモリの読み出し時間  $r$  と C P U のセットアップ時間  $s$  の値に基づいて、調整信号 S200 を生成し、デューティ調整回路 20 に出力する。

#### 【0021】

本例は C P U とメモリが 1 対 1 で設けられている場合であるが、複数の C P U と複数のメモリを有するシステムの場合は、この調整信号は、各 C P U から各メモリへの信号伝送時間の最大値と、各メモリから各 C P U への信号伝送時間の最大値と、各メモリにおけるデ

10

20

30

40

50

ータ信号の入力から出力に至るまでの処理時間の最大値に基づいて生成することができる。また、第1の制御部80から出力されるテスト信号は、本システムの電源投入直後および／または伝送路の未使用時間に送信することができる。特にシステムを取り巻く環境、例えば温度や湿度、または電源電圧の変動などが生じたときは、それをセンサ等によって検出し、必要に応じてテスト信号を出力し、クロック信号のデューティ比を変更することが好ましい。

#### 【0022】

ここで、CPUメモリバスは光伝送路で構成することができる。この場合、CPUとメモリに設けられる各出力手段は電気信号を光信号に変換する半導体レーザ等の発光素子を有する電気光変換手段を備える。一方、入力手段は光信号を電気信号に変換する発光ダイオード等の受光素子を有する光電気変換手段を備える。この電気光変換手段と光電気変換手段との間は光伝送路により光学的に接続される。この場合の信号伝送時間は、電気光変換手段における電気光変換時間および光電気変換手段における光電気変換時間を含むものである。10

#### 【0023】

以下に関しては本実施例における一つの実現例であり、本発明を制約するものではない。

(1) 各信号は正論理であっても負論理であってもよい。(2) 図1、図2、図3、図8においては、読み出しデータ信号、書き込みデータ信号、アドレス信号、R/W信号、CS信号、クロック信号が全て異なる伝送路により伝送されているが、全ての信号もしくはこれらのうち一部の信号を同じ伝送路により伝送する方式でもよい。(3) 図4、図5においては、メモリの読み出しがメモリの受信クロック信号S111の立下りエッジから開始しているが、例えばCS信号、R/W信号およびアドレス信号が確定してからメモリの読み出しが開始され、読み出しデータが内部で確定後の信号S111の立下りエッジにて信号S116がラッチ出力される方式でもよい。この場合はメモリ読み出し時間をr'、ラッチ出力時間をr"とするとき、デューティ比は $(d + r') / (3d + r' + r'' + s)$ となるように調整を行う。このとき、従来方式でのレイテンシは $L_0' = \max(d + r', 2d + r'' + s) \times 2$ 、本発明でのレイテンシは $L_1' = 3d + r' + r'' + s$ となり、改善がなされる。20

#### 【0024】

このように本発明では、CPUにおけるデータ送信、データ受信、メモリアクセスの各所要時間から同期伝送クロックのデューティ比を決めるこことにより、CPUとメモリの待ち時間が削減され、CPUメモリアクセスにおけるレイテンシ削減と伝送帯域の向上を同時に実現することができる。よってシステム全体の性能向上を図ることができる。30

#### 【0025】

##### 【発明の効果】

本発明によれば、データ転送におけるレイテンシを低減し、かつ伝送帯域を向上し得る同期伝送システムを提供することができる。

##### 【図面の簡単な説明】

【図1】本発明に係る同期伝送システムの一実施例を示す図である。

【図2】本発明に係る同期伝送システムを用いて構成されるCPUメモリバスの一例を示すブロック図である。40

【図3】従来の同期伝送システムの一例を示す図である。

【図4】図3のシステムにおけるタイミングチャートを示す図である。

【図5】図1のシステムにおけるタイミングチャートを示す図である。

【図6】本発明に用いるデューティ調整回路の一実施例を示すブロック図である。

【図7】図6のデューティ調整回路におけるタイミングチャートである。

【図8】デューティ調整回路に入力される調整信号の生成方法の一例を示すブロック図である。

##### 【符号の説明】

## 30 ~ 35 伝送路

- S101、S107、S111 クロック信号

S102、S112 CS信号

S103、S113 R/W信号

S104、S114 アドレス信号

S105、S115 書き込みデータ信号

S106、S116 読み出しデータ信号

S200 調整信号

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 义 8 】

---

フロントページの続き

(72)発明者 小林 健一

神奈川県足柄上郡中井町境430 グリーンテクなかい 富士ゼロックス株式会社内

(72)発明者 山田 秀則

神奈川県足柄上郡中井町境430 グリーンテクなかい 富士ゼロックス株式会社内

(72)発明者 佐藤 嘉秀

神奈川県足柄上郡中井町境430 グリーンテクなかい 富士ゼロックス株式会社内

(72)発明者 上野 修

神奈川県足柄上郡中井町境430 グリーンテクなかい 富士ゼロックス株式会社内

(72)発明者 逆井 一宏

神奈川県足柄上郡中井町境430 グリーンテクなかい 富士ゼロックス株式会社内

(72)発明者 鈴木 一広

神奈川県足柄上郡中井町境430 グリーンテクなかい 富士ゼロックス株式会社内

(72)発明者 馬場 智夫

神奈川県足柄上郡中井町境430 グリーンテクなかい 富士ゼロックス株式会社内

(72)発明者 小関 忍

神奈川県足柄上郡中井町境430 グリーンテクなかい 富士ゼロックス株式会社内

(72)発明者 木島 勝

神奈川県足柄上郡中井町境430 グリーンテクなかい 富士ゼロックス株式会社内

(72)発明者 三浦 昌明

神奈川県足柄上郡中井町境430 グリーンテクなかい 富士ゼロックス株式会社内

審査官 矢頭 尚之

(56)参考文献 特開2001-144590(JP,A)

特表2004-501554(JP,A)

特開2000-099194(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04L 7/04

G06F 13/42

H04L 25/03

H04L 29/00