(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5930353号

(P5930353)

(45) 発行日 平成28年6月8日(2016.6.8)

(24) 登録日 平成28年5月13日(2016.5.13)

(51) Int.Cl.

G06F 17/50 (2006.01)

F 1

G06F 17/50 652A

G06F 17/50 654M

請求項の数 19 (全 17 頁)

(21) 出願番号 特願2015-530177 (P2015-530177)

(86) (22) 出願日 平成26年2月27日 (2014.2.27)

(65) 公表番号 特表2015-528607 (P2015-528607A)

(43) 公表日 平成27年9月28日 (2015.9.28)

(86) 國際出願番号 PCT/US2014/019106

(87) 國際公開番号 WO2014/149507

(87) 國際公開日 平成26年9月25日 (2014.9.25)

審査請求日 平成27年2月27日 (2015.2.27)

(31) 優先権主張番号 61/802,114

(32) 優先日 平成25年3月15日 (2013.3.15)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 13/939,763

(32) 優先日 平成25年7月11日 (2013.7.11)

(33) 優先権主張国 米国(US)

(73) 特許権者 514326649

レゾナント インコーポレイテッド

RESONANT INC.

アメリカ合衆国 カリフォルニア州 93

117, サンタバーバラ, カスティリアン

ドライブ 110, スイート 100

(74) 代理人 110001302

特許業務法人北青山インターナショナル

(72) 発明者 フェンジー, ニール

アメリカ合衆国 カリフォルニア州 93

111, サンタバーバラ, パーティスト

リート 650

最終頁に続く

(54) 【発明の名称】マイクロ波フィルタの要素除去設計

## (57) 【特許請求の範囲】

## 【請求項 1】

コンピュータ化されたフィルタ最適化装置(300)を使用してマイクロ波フィルタを設計するための方法において：

(a) 複数の共振要素(202)を有する複数の回路要素と1つ以上の非共振要素(204)とを備える、処理中のフィルタ回路設計(DIP)(200)を生成し(ステップ102)；

(b) DIP(200)をコンピュータ化されたフィルタ最適化装置(300)に入力することによって、DIP(200)を最適化し(ステップ104)；

(c) DIP(200)が最適化された後、DIP(200)中の複数の回路要素の1つが重要でないものと決定し(ステップ106、114)； 10

(d) DIP(200)から1つの重要でない回路要素を除去し(ステップ110)；

(e) DIP(200)から最終フィルタ回路設計を引き出し(ステップ118)；そして、

(f) 最終フィルタ回路設計に基づきマイクロ波フィルタを製造する(ステップ120)；

ことを特徴とする方法。

## 【請求項 2】

1つの重要でない回路要素が最初はインダクタンスおよびキャパシタンスのいずれかを備える非共振要素(204)である方法であって、その方法が、非共振要素の除去の前に

、さらに：

1つの重要でない回路要素をインダクタンスおよびキャパシタンスの一方からインダクタンスおよびキャパシタンスの他方へ変更することによって、変更されたフィルタ回路設計を生成し（ステップ112）；

変更されたフィルタ回路設計をコンピュータ化されたフィルタ最適化装置（300）に入力することによって、DIP（200）を再び最適化し（ステップ104）；そして、

DIP（200）中の1つの重要でない回路要素が重要でないことを確認する（ステップ106）；

ことを特徴とする請求項1に記載の方法。

【請求項3】

1つの重要でない回路要素が最初は共振要素（202）である方法であって、その方法が、1つの重要でない回路要素の除去の前に、さらに：

1つの重要でない回路要素を共振要素（202）から静キャパシタンスへ変更することによって、変更されたフィルタ回路設計を生成し（ステップ116）；

変更されたフィルタ回路設計をコンピュータ化されたフィルタ最適化装置（300）に入力することによって、DIP（200）を再び最適化し；そして、

DIP（200）中の1つの重要でない回路要素が重要でないことを確認する（ステップ106）；

ことを特徴とする請求項1に記載の方法。

【請求項4】

DIP（200）からの1つの重要な回路要素の除去が、減少した数のフィルタ回路設計をもたらす方法であって、その方法が、さらに：

（g）減少した数のフィルタ回路設計をコンピュータ化されたフィルタ最適化装置（300）に入力することによって、DIP（200）を再び最適化し（ステップ104）；

（h）DIP（200）が最適化された後、DIP（200）中の複数の回路要素のうちの他の1つが重要でないものと決定し（ステップ106、114）；そして

（i）DIP（200）から他の1つの重要でない回路要素を除去する（ステップ110）；

ことを特徴とする請求項1に記載の方法。

【請求項5】

1つの重要でない回路要素が非共振要素（204）であり、他の重要でない回路要素が共振要素（202）であることを特徴とする請求項4に記載の方法。

【請求項6】

さらに、DIP（200）中の回路要素のいずれもが重要でないと決定されなくなるまでステップ（g）-（i）を繰り返すことにより、少なくとも1つの付加的な減少した数のフィルタ回路設計を生成し、ここで最終フィルタ回路設計が最終的に最適化されたDIP（200）と同じであることを特徴とする請求項4に記載の方法。

【請求項7】

1つの回路要素が非共振要素（204）であることを特徴とする請求項1に記載の方法。

【請求項8】

非共振要素が重要でないかどうかを決定することが、非共振要素（204）の値をしきい値と比較することを備えることを特徴とする請求項7に記載の方法。

【請求項9】

非共振要素（204）の値が成分値であることを特徴とする請求項8に記載の方法。

【請求項10】

非共振要素（204）が、成分値がしきい値未満の場合重要でないと決定される、直列インダクタまたはシャントキャパシタのいずれかであることを特徴とする請求項9に記載の方法。

【請求項11】

10

20

30

40

50

非共振要素(204)が、成分値がしきい値より大きい場合重要でないと決定される、シャントインダクタまたは直列キャパシタのいずれかであることを特徴とする請求項9に記載の方法。

【請求項12】

非共振要素(204)の値が相対値であることを特徴とする請求項7に記載の方法。

【請求項13】

非共振要素(204)が直列回路要素であり、相対値が、DIP中(200)の、直列回路要素の絶対値の他の直列回路要素の絶対値に対するパーセントであり、直列回路要素が、相対値がしきい値未満である場合、重要でないと決定されることを特徴とする請求項12に記載の方法。

10

【請求項14】

非共振要素(204)がシャント回路要素であり、相対値が、DIP(200)中の、シャント回路要素の絶対値の他のシャント回路要素の絶対値に対するパーセントであり、シャント回路要素が、相対値がしきい値未満である場合、重要でないと決定されることを特徴とする請求項12に記載の方法。

【請求項15】

非共振要素(204)が直列回路要素であり、相対値が、直列回路要素の絶対値の直列回路要素からいずれかの方向に見えるインピーダンスに対するパーセントであり、直列回路要素が、相対値がしきい値未満である場合、重要でないと決定されることを特徴とする請求項12に記載の方法。

20

【請求項16】

非共振要素(204)がシャント回路要素であり、相対値がシャント回路要素の絶対値のシャント回路要素からいずれかの方向に見えるサセプタンスに対するパーセントであり、シャント回路要素が、相対値がしきい値未満である場合、重要でないと決定されることを特徴とする請求項12に記載の方法。

【請求項17】

非共振要素(204)が重要でないかどうかを決定することが、最適化された回路設計から非共振要素を除去し、非共振要素(204)なしで最適化された回路設計における性能パラメータの値と非共振要素(204)ありで最適化された回路設計における性能パラメータの値とを比較することを備えることを特徴とする請求項7に記載の方法。

30

【請求項18】

1つの回路要素が共振要素(202)であることを特徴とする請求項1に記載の方法。

【請求項19】

DIP(200)がパスバンドおよびストップバンドの一方あるいは両方を有する周波数応答であり、共振要素(202)が重要でないかどうかを決定することが、共振要素に関連する伝達零点とパスバンドおよびストップバンドの一方あるいは両方のエッジ周波数とを比較することを備えることを特徴とする請求項18に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

40

本発明は、一般的にマイクロ波フィルタに関するものであり、特に、狭帯域の用途のために設計された音響波のマイクロ波フィルタに関するものである。

【背景技術】

【0002】

電気フィルタは長い間電気信号の処理に使用してきた。特に、そのような電気フィルタは、望ましい信号周波数を通過することによって入力信号から望ましい電気信号周波数を選択し、一方、他の望ましくない電気信号周波数をロックまたは減衰するために使用される。フィルタは、そのフィルタによって選択的に通過される周波数のタイプを示す、ローパスフィルタ、ハイパスフィルタ、バンドパスフィルタ、および、バンドストップフィルタを含むいくつかの一般的なカテゴリーに分類される。さらに、フィルタは、バンド形周波

50

数応答（周波数カットオフ特性）のタイプを示す、バターワース、チェビシェフ、逆チェビシェフ、および、エリフティックなどのタイプによって分類される。

【0003】

使用されるフィルタのタイプは、しばしば、使用目的に依存する。通信用途において、バンドパスフィルタおよびバンドストップフィルタは、セルラ基地局、携帯電話機、および、R F 信号の全部あるいは1つ以上の予め定義したバンドを除去するかブロックするための他の電気通信装置において、従来から使用されている。約 500 - 3, 500 MHz の周波数範囲が、最も重要である。

【0004】

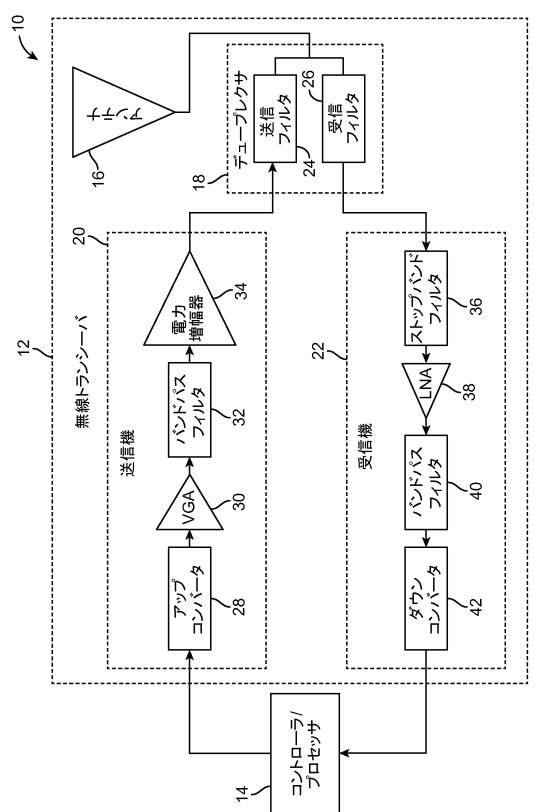

図1を参照すると、先行技術の電気通信システム10は、無線信号を送信および受信することができるトランシーバ12、および、トランシーバ12の機能を制御することができるコントローラ／プロセッサ14、を含むことができる。

10

【0005】

トランシーバ12は、一般的に、プロードバンドアンテナ16、送信フィルタ24および受信フィルタ26を有するディープレクサ18、ディープレクサ18の送信フィルタ24を介してアンテナ16と結合している送信機20、および、ディープレクサ18の受信フィルタ26を介してアンテナ16に結合している受信機22、を備えている。

【0006】

送信機20は、コントローラ／プロセッサ14によって提供されたベースバンド信号をラジオ周波数（R F）信号に変換するよう構成されたアップコンバータ28、R F信号を増幅するよう構成された可変利得増幅器（VGA）30、コントローラ／プロセッサ14によって選択された動作周波数でR F信号を出力するよう構成されたバンドパスフィルタ32、および、フィルタを通過したR F信号を増幅し、次にディープレクサ18の送信フィルタ24を介してアンテナ16に供給されるよう構成された電力増幅器34を含んでいる。

20

【0007】

受信機22は、受信フィルタ26を介してアンテナ16から入力されたR F信号から送信信号干渉を排除するよう構成されたノッチまたはストップバンドフィルタ36、比較的低ノイズのストップバンドフィルタ36からのR F信号を増幅するよう構成された低ノイズ増幅器（LNA）38、コントローラ／プロセッサ14によって選択された周波数で増幅されたR F信号を出力するよう構成された波長の調整が可能なバンドパスフィルタ40、および、R F信号をコントローラ／プロセッサ14に供給されるベースバンド信号へダウンコンバートするよう構成されたダウンコンバータ42を含んでいる。また、ストップバンドフィルタ36によって実行された送信信号干渉を排除する機能は、ディープレクサ18によって代わりに実行することもできる。あるいは、送信機20の電力増幅器34が送信信号干渉を低減するよう設計することもできる。

30

【0008】

図1に示されたブロック図は実際には機能的であり、いくつかの機能が1つの電子部品によって実行でき、あるいは、1つの機能がいくつかの電子部品によって実行される、ことは理解されるべきである。例えば、アップコンバータ28、VGA30、バンドパスフィルタ40、ダウンコンバータ42、および、コントローラ／プロセッサ14によって実行された機能は、しばしば、単一のトランシーバチップによって実行される。バンドパスフィルタ32の機能は、電力増幅器34およびディープレクサ18の送信フィルタ24にすることができる。

40

【0009】

マイクロ波フィルタは、一般的に、2つのサーキット構築ブロック：共振周波数（基本共振周波数  $f_0$  または種々の高次共振周波数  $f_1 - f_n$  のいずれか）でエネルギーを大変効率的に蓄積する、複数の共振器；および、広域スペクトルレスポンスを提供する多重反射零点を形成するために共振器間の電磁エネルギーを結合するカップリング；を使用して構築される。例えば、4つの共振器からなるフィルタは、4つの反射零点を含むことができる。

50

きる。本明細書の目的のために、反射零点は、インダクタンスとキャパシタンスとがキャンセルされて最小量のパワーが反射される、フィルタの反射機能のルートを参照することができる。所定のカップリング強度は、そのリアクタンス（すなわち、インダクタンスおよび／またはキャパシタンス）によって決定される。カップリングの相対強度は、フィルタの形状を決定し、カップリングのトポロジーは、フィルタがバンドパスとして機能するのかバンドストップとして機能するのかを決定する。共振周波数  $f_0$  は、主として、各共振器のインダクタンスおよびキャパシタンスによって決定される。従来のフィルタ設計では、フィルタが動作する周波数はフィルタを構成する共振器の共振周波数によって決定される。各共振器は、上述の理由のため、フィルタレスポンスがシャープで高度に選択的となるように、大変低い内部抵抗を有しなければならない。低抵抗のこの要求は、与えられた技術のために共振器のサイズとコストを駆動する傾向がある。10

#### 【 0 0 1 0 】

フロントエンドの受信フィルタ（例えば、図 1 に示された受信フィルタ 26）は、希望の受信した信号周波数近辺の周波数における強力な干渉信号に起因する種々の悪影響を除去するために、シャープな特性を有するバンドパスフィルタの形をとることが好ましい。アンテナ入力側でのフロントエンド受信フィルタの位置のため、挿入損失は、雑音指数を低下させないように、大変低くしなければならない。ほとんどのフィルタ技術において、低い挿入損失を達成することは、フィルタの急峻性または選択性において相応の譲歩を必要とする。実際に、携帯電話機の多くのフィルタは、表面弹性波（S A W）、バルク超音波（B A W）、および、フィルムバルク音響共振器（F B A R）の技術のような音響共振器技術を使用して構成される。そのような音響共振フィルタは、同等のインダクターおよびキャパシター共振器と比較して、低挿入損失、コンパクトサイズおよび低コストの有利性を有している。20

#### 【 0 0 1 1 】

実際のマイクロ波フィルタの設計は、例えば、イメージ設計やネットワーク合成設計を使用する初期の回路設計から始まる。通常、これらのアプローチは、最初から、考えられる最も少ない数の回路要素を有する回路のみを検討する。これは、通常、最終フィルタにおける損失を最小限とする希望から実行され、すべてのタイプのマイクロ波フィルタ設計において一般的な方法である。初期設計は、通常、最終フィルタを作製するために使用された実回路要素の損失や他の望ましくない特性を無視した、単純化されて理想化された回路要素モデルを使用して行われる。コンピュータによる最適化は、実際のマイクロ波フィルタの設計において、重要で必要なステップである。数ある中でも、アジレントのアドバンスト・デザイン・システム（A D S）を含む設計ツールは、「初期回路設計」を改良するためにモンテカルロ法、グラディエント法などの数値最適化方法を使用できる。コンピュータによる最適化ステップは、ますます、現実的で正確な回路要素モデルを使用でき、最終的なフィルタ設計に従って製造されるものに対する回路要素の値を限定したものとする。最適化は、希望するフィルタレスポンスに最もマッチする回路要素の値の組み合わせを検索することで行われる。このタイプのコンピュータによる最適化は、しばしば、マイクロ波フィルタ設計において使用される。最適化は、通常、実回路要素で実現されるであろうかなり改良された設計を生産するが、それは、通常、初期の回路設計における回転要素の数から、最終的な回路設計における回転要素の数を減少させるものではなく、回路要素の 1 つのタイプを他のタイプに変更させたものでもない。30

#### 【 0 0 1 2 】

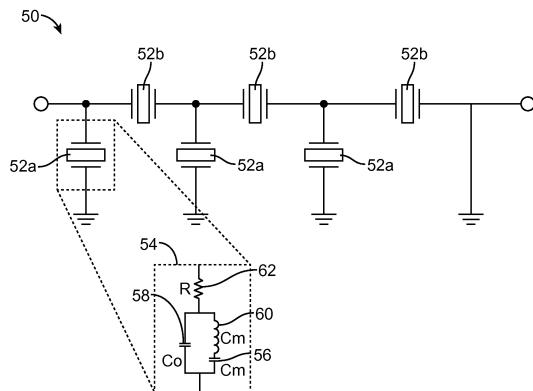

例えば、音波バンドパスフィルタの設計において通常使用されている初期回路はラダーフィルタ 50 であり、図 2 に示されているように、複数の並列シャント共振器 52a と著列共振器 52b とを備えている。フィルタ 50 は、N 共振ラダートポロジー（すなわち、N は共振器の数と同じであり、この例では 6 である）を考慮する。この明細書の目的のため、音響ラダーフィルタは、交代級数で分路した音波共振器を備える、メーソンタイプの音波ダラー回路構造を使用する 1 つあるいはそれ以上のフィルタを参照する。40

#### 【 0 0 1 3 】

10

20

30

40

50

音響共振器 5 2 の各々は、変形バダーワース・ファンダイク (MBVD) モデル 5 4 によって記載される。MBVD モデル 5 4 は、また、SAW 共振器を記載しており、結晶性石英、ニオブ酸リチウム (LiNbO<sub>3</sub>)、タンタル酸リチウム (LiTaO<sub>3</sub>) 結晶、または、BAW 共振器などの、圧電基板上にインター・デジタル変換器 (IDTs) を配置することによって製造される。各 MBVD モデル 5 4 は、動キャパシタンス  $C_m$  5 6、静キャパシタンス  $C_0$  5 8、動インダクタンス  $L_m$  6 0、および、抵抗  $R$  6 2 を含んでいる。動キャパシタンス  $C_m$  5 6 および動インダクタンス  $L_m$  6 0 は、電気的および音響的な動作の相互作用に起因しており、そのため、MBVD モデル 5 4 の動アームとして参照される。静キャパシタンス  $C_0$  5 8 は、この構造の固有キャパシタンスに起因しており、そのため、MBVD モデル 5 4 の静(非動的)キャパシタンスとして参照される。抵抗  $R$  6 2 は、音響共振器 5 2 の電気抵抗に起因している。パラメータは以下の等式によって関係付けられる：

【数 1】

$$[1] \quad \frac{1}{\omega_R} = \frac{1}{\sqrt{L_m C_m}},$$

【数 2】

$$[2] \quad \frac{\omega_A}{\omega_R} = \sqrt{1 + \frac{1}{\gamma}},$$

ここで、 $\omega_R$  および  $\omega_A$  は、それぞれ、与えられた音響共振器に対する共振周波数と反共振周波数であり、 $\gamma$  は材料の特性に依存し、更に以下のように定義されている：

【数 3】

$$[3] \quad \frac{C_0}{C_m} = \gamma.$$

典型的な  $\gamma$  の値は、42度XYカットのLiTaO<sub>3</sub>に対し約12から約18の範囲である。

【0014】

等式(1)から、音響共振器 5 2 の各々の共振周波数が MBVD モデル 5 4 の動アームに依存することが理解され、一方で、フィルタ特性(例えばバンド幅)は等式 2 の  $\gamma$  によって決定される。音響共振器 5 2 に対する品質係数 (Q) は、フィルタ内の要素の損失に関して、音響フィルタ設計における重要な性能指数である。回路要素の Q は、サイクル毎に蓄積されるエネルギーのサイクル毎に失ったエネルギーに対する比率を示している。Q 係数は、各音響共振器 5 2 における実際の損失をモデル化しており、通常、1つ以上の Q 係数が音響共振器 5 2 の損失を表すために要求される。Q 係数は、フィルタの例に対し、以下のように定義される。動キャパシタンス  $C_m$  5 6 は  $Q C_m = 1.0 \times 10^8$  として定義される関連 Q を有しており；静キャパシタンス  $C_0$  5 8 は  $Q C_0 = 200$  として定義される関連 Q を有しており；動インダクタンス  $L_m$  6 0 は  $Q L_m = 1000$  として定義される関連 Q を有している。回路設計者は、通常、SAW 共振器を、共振周波数  $\omega_R$ 、静キャパシタンス  $C_0$ 、 $\gamma$  および品質係数  $Q L_m$  によって特徴付ける。商用アプリケーションにおいて、 $Q L_m$  は、SAW 共振器であり約 1000 であり、BAW 共振器で約 3000 である。

【0015】

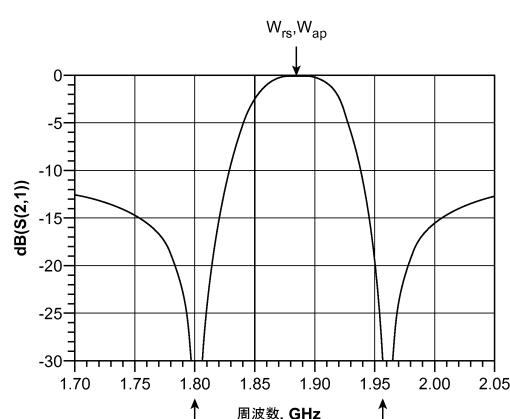

フィルタ 5 0 に対する周波数応答は図 3 に示されており、図 3 は、デシベル (dB) 対周波数  $f$  の対数単位で、フィルタレスポンスとして散乱行列  $[S21]^2$  (挿入損失) および  $[S11]^2$  (リターン損失) を示している。シャント共振器 5 2 a の各々の共振周波数と反共振周波数とを、それぞれ、 $\omega_{rp}$  と  $\omega_{ap}$  として指定し、直列共振器 5 2 b の各々の共振周波数と反共振周波数とを、それぞれ、 $\omega_{rs}$  と  $\omega_{as}$  として指定する。 $\omega_{rs}$  と  $\omega_{ap}$  とが互いにほぼ同じとき、図 3 のフィルタレスポンスで示されているように、

10

20

30

40

50

$r_s$ 、 $a_p$  近傍を中心とするパスバンドが生成され、パスバンドエッジを定義する  $r_p$ 、 $a_s$  で伝達零点が生成される。この明細書の目的のために、伝達零点は、パワーの最大量が反射するフィルタの伝達関数のルートを参照する。パスバンドの中心周波数  $\omega_p$  から遠く離れた周波数で、共振器はほぼキャパシタとして動作し、帯域外抑制を提供し、大きい  $|S_21|$  に対し漸近的に一定となるウイングを形成する、 $|S_21|^2$  のフィルタレスポンスとなる。

#### 【0016】

バンドパスフィルタのレスポンスは、リターン損失（すなわち、中心パスバンド周波数  $\omega_p$  での  $|S_{11}|^2$  の値）、挿入口ス（すなわち、中心パスバンド周波数  $\omega_p$  での  $|S_{21}|^2$  の値）、パスバンド幅（PBW）、および、帯域外抑制（すなわち、大きい  $|S_{21}|$  での  $1/|S_{21}|$ ）によって特徴付けられる。バンドパスラダーフィルタは、材料パラメータ値 および共振器の数（フィルタオーダーと称する）に依存する範囲において、これらのパラメータの制限された利用可能な範囲に亘って設計されている。SAWフィルタおよびBAWフィルタの現在広く使用されている材料に対する材料パラメータ値は 12 - 14 の範囲であり、共振周波数および反共振周波数をパスバンド中心周波数  $\omega_p$  に近づけ、 $|S_{21}|^2$  フィルタレスポンスにおいて比較的狭いパスバンドを生成する。材料パラメータ値が 4 の材料は現在開発中である。より小さい材料パラメータ値は、よりワイドなパスバンド幅 PBW を可能とし、リターン損失 RL を減少し、または、帯域外抑制を向上する。

#### 【0017】

固定されたパスバンド幅 PBW に対し、帯域外抑制が増えると、リターン損失 RL は減少する。場合によっては、受動回路要素が、フィルタ性能を改善するために、ラダー構造に結合される。例えば、インダクタを追加することは、効果的な材料パラメータ値を低減でき、そのことは、パスバンド幅 PBW を増加させ、リターン損失 RL を低減し、または、帯域外抑制を向上させる。しかしながら、インダクタの追加による利点は、挿入損失、サイズおよびコストの増加を犠牲にして成り立つ。バンドパスフィルタのパラメータは、システム応用に従って決まるパラメータと要求とのドレードオフで、性能を最大限にするために、利用可能な範囲の限界までブッシュされる。より高次のフィルタは、与えられたパスバンドのリターン損失 RL およびパスバンド幅 PBW でより大きな帯域外抑制を達成する。

#### 【0018】

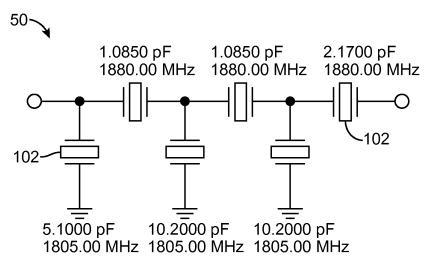

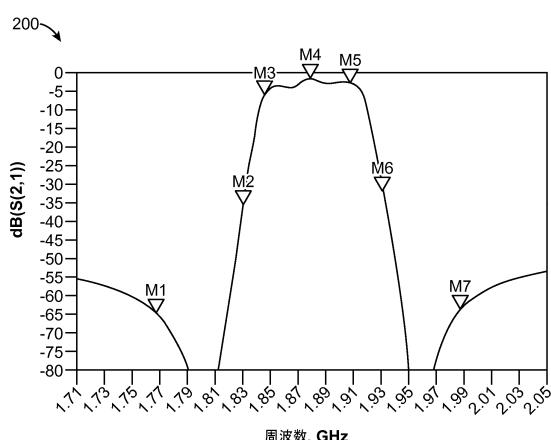

ここまでで簡単に議論したように、フィルタ 50 は初期の回路設計を有しており、最終的な回路設計を形成するために、それは適切なコンピュータ最適化技術（例えば、アジレント ADS ソフトウェア）を介して最適化される。例えば、フィルタ 50 は、最初、図 4 a に示された各共振器 52 に対し共振周波数  $\omega_R$  および静キャパシタンス  $C_R$  で設計されており、シミュレートすると、図 4 b に示された周波数応答となる。この周波数応答は、以下のマーカーによって特徴付けられて示されている：周波数 = 1.770 GHz で  $\text{Mag } S_{21} = -65.71 \text{ dB}$  の M1；周波数 = 1.830 GHz で  $\text{Mag } S_{21} = -36.735 \text{ dB}$  の M2；周波数 = 1.850 GHz で  $\text{Mag } S_{21} = -4.367 \text{ dB}$  の M3；周波数 = 1.879 GHz で  $\text{Mag } S_{21} = -1.444 \text{ dB}$  の M4；周波数 = 1.910 GHz で  $\text{Mag } S_{21} = -2.680 \text{ dB}$  の M5；周波数 = 1.930 GHz で  $\text{Mag } S_{21} = -30.118 \text{ dB}$  の M6；および、周波数 = 1.990 GHz で  $\text{Mag } S_{21} = -62.874 \text{ dB}$  の M7。

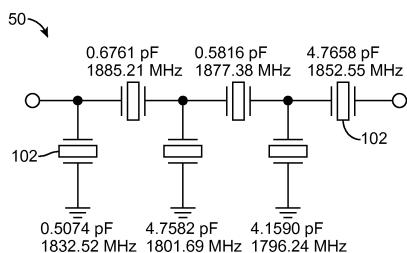

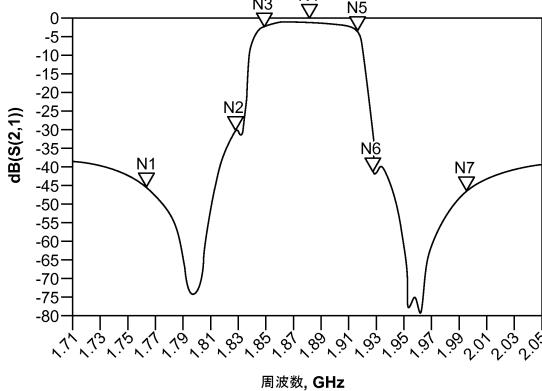

#### 【0019】

最適化の後、図 5 a に示した各共振器 52 に対し共振周波数  $\omega_R$  および静キャパシタンス  $C_R$  を有しており、シミュレートすると、図 5 b に示された周波数応答となる。この周波数応答は、以下のマーカーによって特徴付けられて示されている：周波数 = 1.770 GHz で  $\text{Mag } S_{21} = -46.943 \text{ dB}$  の N1；周波数 = 1.829 GHz で  $\text{Mag } S_{21} = -29.865 \text{ dB}$  の N2；周波数 = 1.851 GHz で  $\text{Mag } S_{21} = -1.479 \text{ dB}$  の N3；周波数 = 1.875 GHz で  $\text{Mag } S_{21} = -0.833 \text{ dB}$  の N4

10

20

30

40

50

；周波数 = 1.910 GHz で Mag S21 = -1.898 dB の N5；周波数 = 1.929 GHz で Mag S21 = -41.977 dB の N6；および、周波数 = 1.990 GHz で Mag S21 = -47.182 dB の N7。

#### 【0020】

前述のことから理解されるように、共振器 52 に対する MBVD モデル 54 の値は、周波数応答の改善のための最適化で変更される。しかしながら、回路要素のタイプおよび数は変わらずに残り、最終回路の設置面積およびコストを減少しない。そのため、一般的にマイクロ波フィルタに対し、特に、受動要素を含み、および / または、より複雑なセクションを有する近代ネットワーク理論やイメージ理論のような、複雑な設計技術を使用する、フィルタ設計に対し、改善された最適化方法が必要である。

10

#### 【図面の簡単な説明】

#### 【0021】

図面は本発明の好ましい実施例の設計および有用性を示しており、同様の要素は共通の参照番号によって参照される。本発明の上述したおよび他の有用性および目的がどのようにして得られたかをより良く理解できるように、簡単に上で説明した本発明のより特別な記載は、その具体的な実施例の参照によって与えられ、それは図面を伴って示される。これらの図面は、本発明の典型的な実施例を示したものであり、そのためその範囲を限定すると考えてはならないことを理解したうえで、本発明は、以下のような図面の使用を介して付加的で具体的かつ詳細に記載され理解される：

【図 1】図 1 は、先行技術の無線通信システムのブロック図である。

20

【図 2】図 2 は、先行技術の無線通信システムで使用される先行技術の音響ラダーフィルタの線図である。

【図 3】図 3 は、図 2 の先行技術の音響ラダーフィルタの周波数応答プロットである。

【図 4】図 4 a は、従来のフィルタ最適化技術を用いて最適化した図 2 の音響ラダーフィルタの初期回路設計の線図である。図 4 b は、図 4 a の初期回路設計の周波数応答プロットである。

【図 5】図 5 a は、従来のフィルタ最適化技術を使用した図 4 a の初期回路設計の最適化の結果として得られる図 2 の音響ラダーフィルタの最適化された最終回路設計の線図である。図 5 b は、図 5 a の最終回路設計の周波数応答プロットである。

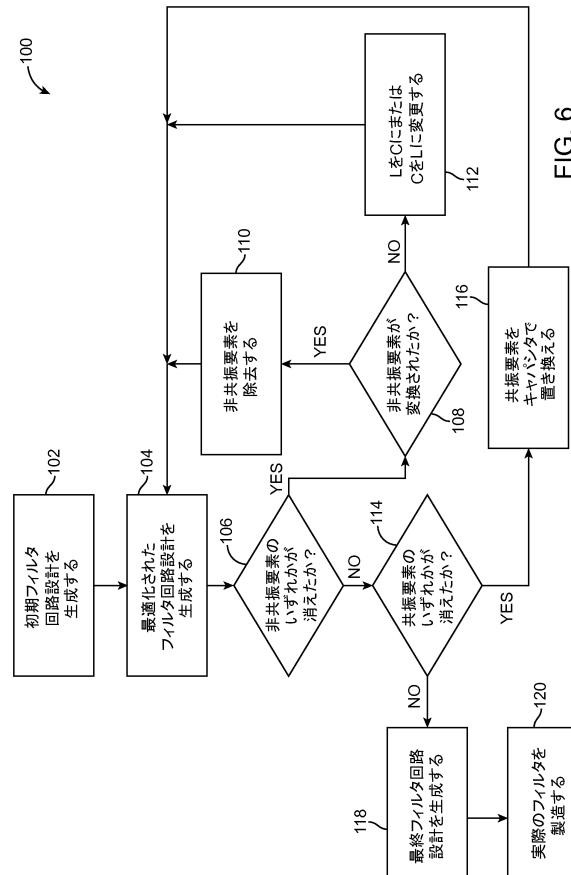

【図 6】図 6 は、本発明の一方法に従って音響ラダーフィルタを最適化するために使用された要素除去設計 (ERD) 技術を示すフローダイアグラムである。

30

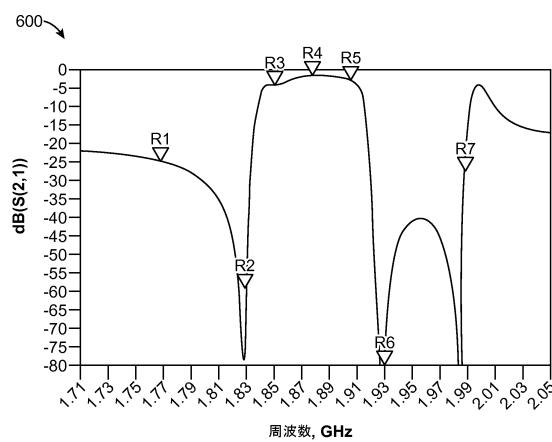

【図 7 a】図 7 a は、図 6 の ERD 技術を使用して最適化された音響ラダーフィルタの初期回路設計の線図である。

【図 7 b】図 7 b は、図 7 a の初期回路設計の周波数応答プロットである。

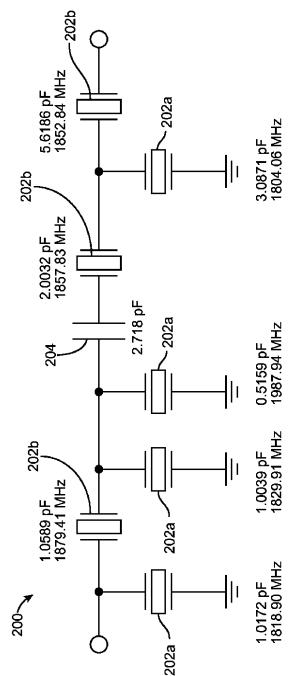

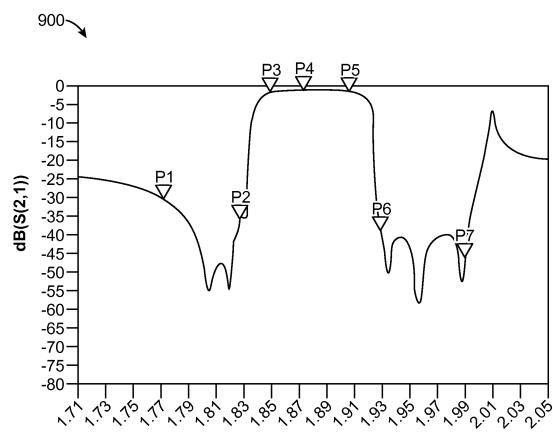

【図 8 a】図 8 a は、図 6 の ERD 技術を使用した図 7 の初期フィルタ回路設計の最適化から得られた最適化された最終回路設計の線図である。

【図 8 b】図 8 b は、図 8 a の最終回路設計の周波数応答プロットである。

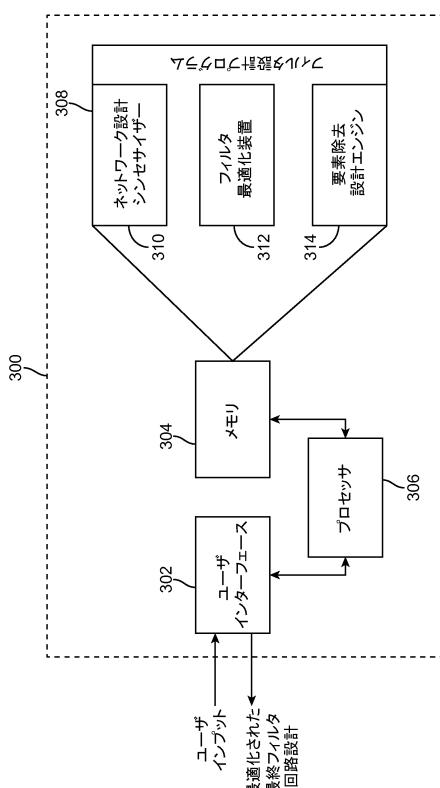

【図 9】図 9 は、図 6 の ERD 技術のコンピュータ化されたステップを実行するコンピュータ化されたフィルタ回路システムのブロック図である。

#### 【発明を実施するための形態】

#### 【0022】

マイクロ波フィルタ設計の最適化技術は、回路要素の値を変更すること、回路要素のタイプを変更すること、および / または、余分あるいは不要な回路要素を個別的に除去することによって、音波 (AW) マイクロ波フィルタ (表面弹性波 (SAW)、バルク弹性波 (BAW)、薄層バルク弹性波 (FBAR) のフィルタのような) を最適化する。これらの要素は、インダクタ、キャパシタおよび音響共振器 (例えば変形バダーワース・ファンダイク (MBVD) モデルを使用してモデル化された) を含む。

#### 【0023】

この最適化技術は、先行技術で可能なものよりも初期回路設計におけるより複雑な回路の改良された最適化を可能とするために、いくつかの伝統的なコンピュータ最適化方法を

40

50

を利用する。これらの初期フィルタ回路設計は、例えばイメージ設計やネットワーク合成設計などの設計方法を使用して生成される。この最適化技術は、初期フィルタ回路設計と比べて要素の数を削減した最終フィルタ回路設計の結果となり、一方同時に、フィルタの周波数応答を向上させる。本明細書の目的のために、周波数応答の向上は、フィルタの望ましいマイクロ波性能（例えば、より低い挿入損失、より急峻な抑制スロープ、より高い対域外抑制、より低いノード電圧、より直線的なグループ遅延など）における向上を参照する。そのため、より小さい占有面積、より低いコスト、より低い挿入損失およびより大きな選択性を有するフィルタは、伝統的な製造プロセスやインフラの使用により、達成される。

## 【0024】

10

マイクロ波フィルタ設計の最適化技術は、ここに、AWフィルタを参照して記載されるが、この技術は、共振要素がMBVDモデルが有する精度のあるレベルでモデル化される、他のタイプのマイクロ波フィルタとともに利用されること、を理解すべきである。最適化技術は、また、複雑な共振器要素（例えば、マルチモード誘電体共振器およびその他の同様な技術）を有する他の技術に適用される。

## 【0025】

図6を参照すると、音響波フィルタを設計するために使用される要素除去設計（ERD）技術100が記載されている。ERD技術100の実装時には、プロセスの設計（DIP）が改善され、最終的な設計に初期設計から変更される。この方法は、ステップにおいて、回路要素の数を減少させて性能の有効性を改善するようDIPを個別に改良するために、コンピュータによる最適化および決定を使用する。

20

## 【0026】

この目的のため、ERD技術100は、最初に、中心パスバンド周波数、パスバンド幅、リターン損失などの性能仕様に基づいた初期フィルタ回路設計を作成し、帯域外抑制が、イメージフィルタ技術やネットワーク同期技術を使用して発生する（ステップ102）。本明細書の目的のために、回路要素は、回路相互接続のネットワーク内における、インダクタ、キャパシタ、共振器、スイッチまたは抵抗を参照する。

## 【0027】

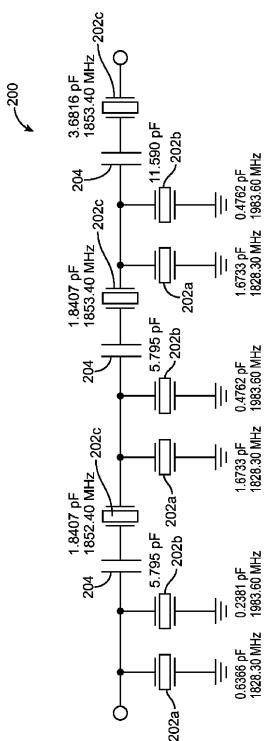

例えば、図7aに示すように、初期フィルタ回路設計は、複数の並列シャント共振要素202aおよび202bと直列共振要素202cとを備える、バンドパスラダー200である。図示した実施例において、ラダーフィルタ200の各シャント足は、異なる周波数で共振する2つ並列シャント共振要素202aおよび202bを含んでいる。共振要素202の各々は、図2に示されたMBVDモデル54でモデル化されている。ラダーフィルタ200は、また、それが直列共振要素202cと関連したキャパシタの形態の複数の非共振要素204を備えている。本明細書の目的のために、非共振要素は回路中受動部品を参照する。非共振要素の例は、インダクタ、キャパシタ、スイッチまたは抵抗を含む。非共振要素は注目する周波数から遠く離れた共振を有する。例えば、インダクタは、パスバンド周波数の50%以上の共振を有する。そのため、フィルタ200は9つの共振要素と3つの非共振要素を含む。

30

## 【0028】

40

フィルタ200は、最初、図7aに示された各共振器202に対し共振周波数<sub>R</sub>および静キャパシタンスC<sub>0</sub>で設計されており、シミュレートすると、図7bに示された周波数応答となる。この周波数応答は、以下のマーカーによって特徴付けられて示されている：周波数=1.770GHzでMagS21=-24.627dBのR1；周波数=1.830GHzでMagS21=-64.652dBのR2；周波数=1.850GHzでMagS21=-0.987dBのR3；周波数=1.881GHzでMagS21=-3.039dBのR4；周波数=1.910GHzでMagS21=-87.468dBのR5；周波数=1.930GHzでMagS21=-87.468dBのR6；および、周波数=1.990GHzでMagS21=-28.429dBのR7。初期フィルタ回路設計200の回路要素は以下のパラメータ：ガンマ=12、QC<sub>0</sub>=200、Qca

50

$p = 200$ 、 $Q L_m = 1000$ 、および、 $R_s = 0.5$ 、を有するものと仮定する。

#### 【0029】

次に、E RD 技術 100 は、DIP (この場合初期フィルタ設計) をコンピュータ化されたフィルタ最適化装置 (例えば、アシリエントの ADS) に入力する (ステップ 104)。本明細書の目的のために、DIP のコンピュータ最適化は、コンピュータに基づく回路シミュレータ中の回路要素の値を変えることによって、周波数応答を向上させることを参考する。回路シミュレータは、望ましい結果に対してシミュレートした応答を比較するために、ゴールを使用する。コンピュータで最適化されるべき DIP はこの点で初期回路設計であり、E RD 技術 100 がフィルタ設計プロセスのいかなる点においても DIP を改善するために実行されること、を理解すべきである。いずれのイベントでも、結果として得られる DIP は、入力された DIP における回路要素の数と同じ数の回路要素を有している。

10

#### 【0030】

E RD 技術 100 は、次に、DIP 中の非共振要素 204 のいずれが重要でなくなるのか (「消える」) どうかを決定する (ステップ 106)。本明細書の目的のために、回路要素は、直列要素リアクタンス値および / またはシャント要素サセプタンス値がステップ 104 でのコンピュータ最適化中に大変少なくなる場合、および / または、回路要素がフィルタ性能において重要なインパクトなしにフィルタ設計から除去される場合、消える傾向にある。非共振要素 204 はその種類およびフィルタ回路設計内の配置に従って消える傾向にある。

20

#### 【0031】

例えば、非共振要素 204 が直列インダクタまたはシャントキャパシタである場合、その成分値が例えば  $0.1 \text{ nH}$  (インダクタ) または  $0.1 \text{ pF}$  (キャパシタ) 未満と小さくなるため、それは消える傾向にある。この場合、非共振要素 204 は、その成分値がしきい値未満である場合、重要でないと決定される。これに対し、非共振要素 204 がシャントインダクタまたは直列キャパシタである場合、その成分値が例えば  $100 \text{ nH}$  (インダクタ) または  $50 \text{ pF}$  (キャパシタ) 以上と大きくなるため、それは消える傾向にある。この場合、非共振要素 204 がその成分値がしきい値以上である場合、重要でないと決定される。

#### 【0032】

30

他の例として、非共振要素 204 は、その相対値 (インピーダンスまたはサセプタンス) がそれらに接続されている同じタイプ (直列またはシャント) の他の回路要素と比較して小さい (例えば 10% 未満) となるため、消える傾向にある。そのため、非共振要素 204 が直列回路要素である場合、それは、DIP 内のほかの直列非共振要素 204 の絶対値に対するその絶対値がしきい値未満の場合、重要でないと決定される。同様に、非共振要素 204 がシャント回路要素である場合、DIP 中のほかのシャント非共振要素 204 の絶対値に対するその絶対値がしきい値未満の場合、重要でないと決定される。

#### 【0033】

さらに他の例として、非共振要素 204 が直列回路要素である場合、そのインピーダンスが非共振要素 204 からいずれかの方向に見えるインピーダンスのパーセント (例えば 10%) 未満であるため、消える傾向にある。このとき、非共振要素 204 は、非共振要素 204 からいずれかの方向に見えるインピーダンスに対する非共振要素 204 の絶対インピーダンス値のパーセントがしきい値未満である場合、重要でないと決定される。これに対し、非共振要素 204 がシャント回路要素である場合、そのサセプタンスが非共振要素 204 からいずれかの方向に見えるサセプタンスのパーセント (例えば 10%) 未満であるため、消える傾向にある。このとき、非共振要素 204 からいずれかの方向に見えるサセプタンスに対する非共振要素 204 の絶対サセプタンス値のパーセントがしきい値未満である場合、非共振要素 204 は重要でないと決定される。

40

#### 【0034】

さらに他の例において、非共振要素 204 は、それを除去することがフィルタ回路の性

50

能パラメータ（例えば、挿入損失、抑制勾配、帯域外抑制、ノード電圧、グループ遅延平滑性など）においてパーセント劣化の変更（例えば10%）の結果となるとき、消える傾向にある。このとき、非共振要素204は、非共振要素204の性能パラメータの値の非共振要素204外の性能パラメータに対する劣化がしきい値未満である場合、DIPから非共振要素204を除去することによって、重要でないと決定される。

【0035】

DIP中の非共振要素204の一つがステップ106で重要でないと決定された場合、ERD技術100が、重要でない非共振要素204のサインが前回と変わったかどうか（すなわち、非共振要素204がインダクタンスからキャパシタンスあるいはキャパシタンスからインダクタンスに変換されたかどうか）を決定する（ステップ108）。もちろん、DIPが最初に生成される場合は、そのような前回の変更は存在しない。とりわけ、ERD技術100は、重要でない非共振要素204の除去が非共振要素204の変更より好ましいことを確認するためにこの問い合わせを行う。

10

【0036】

重要でない非共振要素204が前回ステップ108で変換された（非共振要素204がキャパシタおよびインダクタの両者として消えたことを示す）場合、ERD技術100はDIPから重要でない非共振要素204を除去することによって減少したフィルタ回路設計を生成する（ステップ110）。非共振要素204が前回ステップ108で変換されていない（非共振要素204がキャパシタンスおよびインダクタンスの一方として消えたが、キャパシタンスおよびインダクタンスの他方としてまだ消えていないことを示す）場合、ERD技術100は非共振要素204のサインを変えることで（すなわち、それをキャパシタンスからインダクタンスへ（非共振要素204が最初キャパシタンスである場合）、または、インダクタンスからキャパシタンスへ（非共振要素204が最初インダクタンスである場合）変えることで）DIPを変更する（ステップ112）。

20

【0037】

ERD技術100は次にステップ104に戻り、再び、ステップ110で発生した減少したフィルタ回路設計またはステップ112で発生した変更されたフィルタ回路設計のいずれかをコンピュータ化されたフィルタ最適化装置へ入力することによってDIPを最適化し、DIPに残っている非共振要素204がステップ108において重要でないとなっているかどうかを決定する。DIP中の非共振要素204の一つが重要でなくなったと決定された場合は、ERD技術は、再び、重要でない非共振要素204が前回ステップ108で変更されたかを決定する。重要でない非共振要素204が前回変換されていた場合、次に、重要でない非共振要素204は前回のDIPから除去されるべきだと判断し、そのためそれはステップ110で除去される。重要でない非共振要素204が前回変換されていない場合は、次に、ERD技術100はステップ112においてそれを変更する。

30

【0038】

DIP中の非共振要素204のいずれもが（それがDIPで最初に発生されたものであってもその後発生されたものであっても）ステップ106で重要でないと決定された場合、ERD技術は、次に、DIP中の共振要素202のいずれかが重要でなくなったかどうか（「消えたかどうか」）を決定する（ステップ114）。共振要素202は、共振要素202に関する伝達零点が相対的に全てのバスバンドおよびストップバンドから遠いとき；例えば、等式[1]および[2]で得られるように、共振周波数<sub>R</sub>および反共振周波数<sub>A</sub>が最も近いバスバンドまたはストップバンドのエッジ周波数から10%以上移動しているとき、消える傾向にある。

40

【0039】

DIP中の共振要素202の一つがステップ114で重要でないと決定された場合、ERD技術は、好ましくは重要でない共振要素202の静キャパシタンスの値と同じ値を有する、静キャパシタンスC<sub>0</sub>に重要でない共振要素202を置き換えることによって、DIPを変換する（ステップ116）。特に、重要でなくなる共振要素202は、その静キャパシタンスのために回路に悪影響を与え、そのため除去するよりはキャパシタに置き換

50

えることが好ましい。

【0040】

E R D 技術 1 0 0 は次にステップ 1 0 4 に戻り、再び D I P を最適化し、次に、 D I P 中の非共振要素 2 0 4 のいずれか（重要でない共振要素 2 0 2 から変換されたいずれの静キャパシタンス C<sub>0</sub> をも含む）がステップ 1 0 6 で重要でなくなったかどうかを再び決定する。

【0041】

D I P 中の非共振要素 2 0 4 の一つが重要でなくなったと決定された場合、 E R D 技術は、再び、重要でない非共振要素 2 0 4 が前回ステップ 1 0 8 で変換されたかどうかを決定し、上述したように実行する。重要でない非共振要素 2 0 4 が重要でない共振要素 2 0 2 を置き換えた静キャパシタンス C<sub>0</sub> である場合、次に、重要でない回路要素（前回共振要素 2 0 2 であったが、現在は非共振要素 2 0 4 である）は完全に除去されるべきであり、そのためステップ 1 1 0 で除去される。

【0042】

ステップ 1 0 6 において、 D I P 中の非共振要素 2 0 4 のいずれもが重要でなくなっていると決定された場合、 E R D 技術 1 0 0 は、再び、 D I P 中の共振要素 2 0 2 のいずれかがステップ 1 1 4 で重要でなくなったかどうかを決定する。 D I P 中の共振要素 2 0 2 の一つが重要でなくなったと決定された場合、 E R D 技術は、ステップ 1 1 6 で、重要でない共振要素 2 0 2 を静キャパシタンス C<sub>0</sub> に置き換える。

【0043】

D I P 中の共振要素 2 0 2 のいずれもが重要でなくなっていると決定された場合、 E R D 技術は、 D I P が、典型的な実施例において、シミュレートすると図 8 b に示された周波数応答の結果となる、図 8 a に示された、残っている共振要素 2 0 2 および非共振要素 2 0 4 に対し共振周波数  $f_R$  および静キャパシタンス C<sub>0</sub> を有する、改良された最終フィルタ回路設計となるべきだと判断する（ステップ 1 1 8 ）。この周波数応答は、以下のマーカーによって特徴付けられて示されている：周波数 = 1.770 GHz で Mag S 2 1 = -30.080 dB の P 1 ；周波数 = 1.830 GHz で Mag S 2 1 = -34.193 dB の P 2 ；周波数 = 1.850 GHz で Mag S 2 1 = -1.394 dB の P 3 ；周波数 = 1.872 GHz で Mag S 2 1 = -0.761 dB の P 4 ；周波数 = 1.910 GHz で Mag S 2 1 = -1.406 dB の P 5 ；周波数 = 1.930 GHz で Mag S 2 1 = -45.227 dB の P 6 ；および、周波数 = 1.990 GHz で Mag S 2 1 = -45.227 dB の P 7 。

【0044】

図 7 a と図 8 a との間の比較から判るように、改良された最終フィルタ回路設計は、より少ない数の回路要素、特に、2つ少ない共振要素 2 0 2 および1つ少ない非共振要素 2 0 4 、を含む。図 8 a と図 8 b との比較から判るように、最終フィルタ回路設計は、平坦な周波数応答およびパスバンドでの損失をもたらす。また、従来の最適化技術（すなわち、回路要素を除去しない）が図 7 a に示された初期のフィルタ回路 2 0 0 で実行されても、図 8 b に示された E R T 技術によってもたらされた周波数応答性能ほど良くない周波数応答性能を有する最終フィルタ回路の結果となること、に注意すべきである。そのため、従来の見解とは反し、 E R T 技術を使用する回路要素の除去は、マイクロ波フィルタのコストおよびサイズを減少するだけでなく、それはより多くの回路要素を有する先行技術のマイクロ波フィルタを超えてマイクロ波フィルタの周波数応答性能を向上させる。

【0045】

特に、 E R D 技術 1 0 0 は、前回のステップが取り消されるべきかやり直されるべきかを決定するために、ステップ 1 0 4 に起因する D I P の周波数応答を解析できる。

【0046】

例えば、 D I P の周波数応答性能が初期のフィルタ回路設計の周波数応答性能より良くない場合、これは初期のフィルタ回路設計が受け入れられないことを意味し、そのため、異なる初期フィルタ回路設計が考慮され、次にステップ 1 0 4 でコンピュータ化されたフ

10

20

30

40

50

イルタ最適化装置に入力される。

【0047】

他の例として、非共振要素204が変換された（キャパシタンスからインダクタンスへまたはインダクタンスからキャパシタンスへ）後のDIPの周波数応答性能が、非共振要素204が変換される前のDIPの周波数応答性能に関連するしきい値量だけ悪い場合、ERD技術100は単純に前回のDIPに戻ることができ、その設計から非共振要素204を除去することができる。

【0048】

更に他の例として、共振要素202が静キャパシタンスC<sub>0</sub>に変換された後のDIPの周波数応答性能が、共振要素202が変換される前のDIPの周波数応答性能に関連するしきい値量だけ悪い場合、ERD技術は単純に前回のDIPに戻ることができ、その設計に戻って共振要素204を元に戻ることができる。

10

【0049】

改良された最終フィルタ回路設計が達成された時点で、ERD技術100は、最終フィルタ回路設計に基づいた実際のマイクロ波フィルタを製造する（ステップ120）。好ましくは、実際のマイクロ波フィルタの回路要素の値は、改良された最終フィルタ回路設計における対応する回路要素の値と一致する。

【0050】

図9をまず第1に参照すると、コンピュータ化されたフィルタ設計システム300が、ERD技術100を使用してマイクロ波フィルタを設計するために使用されている。コンピュータ化されたフィルタ設計システム300は、通常、ユーザからの情報およびデータ（例えば、パラメータ値やフィルタ仕様）を受け取り、ユーザに最適化した回路設計を出力するよう構成されたユーザインターフェース302；ユーザインターフェース302を介してユーザから入力された情報およびデータとともに、特定の機能または特定の要約データタイプの実装を実行する、（ルーティン、プログラム、オブジェクト、部品、データ構造、手順、モジュール、機能などを限定しないが含むことができ、ソフトウェアインストラクションの形態をとることができる）、フィルタ設計ソフトウェア308を記憶するよう構成されたメモリ304；および、フィルタ設計ソフトウェアを実行するよう構成されたプロセッサ306を備える。フィルタ設計ソフトウェアプログラム308は、サブプログラム、特に、従来のネットワーク設計シンセサイザー310（ステップ102で初期のフィルタ回路設計を生成するために使用される）、従来のフィルタ最適化装置312（ステップ104でDIPを生成するために使用される）、および、最適化された最終回路設計を生成するために、ERD技術100のフィルタ回路設計に従ってネットワーク設計シンセサイザー88およびフィルタ最適化装置90をコントロールする要素除去設計エンジン314、に分割される。

20

【0051】

本発明の特定の実施例が示されて記載されているが、上述した議論は本発明をそれらの実施例に限定することを意図していないことを理解すべきである。当業者にとって、各種の変更や変形が本発明の精神および範囲を逸脱しない限り可能であることは自明である。例えば、本発明は単一の入力および出力を有するフィルタを十分超える応用を有しており、本発明の特定の実施例は、低損失の選択回路が使用される、デュープレクサ、マルチブレクサ、チャンネライザ、リアクティブスイッチなどを形成するために使用される。そのため、本発明は、クレームで定義されているように、本発明の精神および範囲内の代替例、変形例および同等例をカバーすることを意図している。

30

40

【図1】

FIG. 1

(先行技術)

【図2】

FIG. 2

(先行技術)

【図3】

FIG. 3

(先行技術)

【図4】

FIG. 4a

(先行技術)FIG. 4b

(先行技術)

【 図 5 】

FIG. 5a

(先行技術)

FIG. 5b

(先行技術)

【図7a】

FIG. 7a

【 図 6 】

FIG. 6

【図 7 b】

FIG. 7b

【図 8 a】

FIG. 8a

【図 8 b】

FIG. 8b

【図 9】

FIG. 9

---

フロントページの続き

(72)発明者 ライン , カート

アメリカ合衆国 カリフォルニア州 93117 , ゴレタ , キャノングリーンドライブ 487 ,

アパートメント ジー .

審査官 早川 学

(56)参考文献 特表2010-532147 (JP, A)

梅川光晴 , 高周波回路解析を体験する Agilent Technologies 社の高周波

回路設計ツール「Eagl eware GENESYS」, Design Wave MAGA

ZINE 第13巻 第2号 , CQ出版株式会社 , 2008年 2月 1日 , 第13巻 , 第2号 , p

p.119~127

(58)調査した分野(Int.Cl. , DB名)

G 06 F 17 / 50