19 RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

⑪ N° de publication :

3 017 261

(à n'utiliser que pour les commandes de reproduction)

(21) N° d'enregistrement national :

15 50755

51 Int Cl<sup>8</sup> : **H 03 K 17/16** (2013.01), H 01 L 27/02

12

## DEMANDE DE BREVET D'INVENTION

A1

22 Date de dépôt : 30.01.15.

(30) Priorité : 04.02.14 US 14/172,727.

④ Date de mise à la disposition du public de la demande : 07 08 15 Bulletin 15/32

**56** **Liste des documents cités dans le rapport de recherche préliminaire : Ce dernier n'a pas été établi à la date de publication de la demande.**

**60 Références à d'autres documents nationaux apparentés :**

Demande(s) d'extension :

(71) **Demandeur(s) :** TRIQUINT SEMICONDUCTOR, INC.

— U.S.

72 Inventeur(s) : NOHBA GEORGE

73) Titulaire(s) : TBIQUINT SEMICONDUCTOR INC

74) Mandataire(s) : CABINET PLASSEBAUD.

54 CIRCUIT DE COMMUTATION DE TRANSISTOR A EFFET DE CHAMP

57 Des modes de réalisation comprennent un appareil, un système et un procédé connexes à un circuit de commutation. Dans certains modes de réalisation, le circuit de commutation peut comprendre un premier commutateur incluant un transistor à canal n à effet de champ (FET) dans le trajet de signal. Le circuit de commutation peut en outre comprendre un deuxième commutateur en shunt au premier commutateur. Le deuxième commutateur peut comprendre un transistor de décharge (132) pour fournir un trajet de décharge pour un corps (120) d'un transistor en commutation (104).

## CIRCUIT DE COMMUTATION DE TRANSISTOR A EFFET DE CHAMP

Des modes de réalisation de la présente invention concernent généralement le domaine de circuits, et plus particulièrement des circuits de commutation.

- Les transistors à effet de champ (FET) peuvent être utilisés pour des dispositifs commutateurs à radiofréquence (RF) à faible puissance, particulièrement

- 5 dans des applications mobiles où le prix, les performances, et la consommation d'énergie sont des éléments clefs. Cependant, des FET peuvent présenter des difficultés lorsqu'ils traitent des signaux plus grands. En particulier, les performances sous grands signaux dans des FET servant de commutateurs peuvent être affectées par accumulation de charge dans une région quasi-neutre du corps des FET.

- 10 L'accumulation de charge peut entraîner une accumulation de porteur chaud, des fuites de drain induites par grille (GIDL) excessive, une transconductance négative, une perte de commande de grille, etc. Ces problèmes peuvent être généralement appelés effet de corps flottant (FBE).

Dans certaines applications, certaines applications peuvent nécessiter des

15 commutateurs ultra-rapides, et à ultra-basse perte/haute isolation. Dans certains cas, un commutateur à faible perte peut nécessiter un générateur de tension négative (NVG) qui peut être utilisé pour obtenir la faible perte et l'isolation requises, et également pour satisfaire aux conditions de grands signaux. Cependant, l'utilisation d'un NVG peut entraîner un commutateur plus lent, ainsi que de forts coûts indirects

20 en ce qui concerne la superficie de circuit. En outre, l'utilisation du NVG peut entraîner un courant de fuite dans le mode de sommeil, à savoir lorsque le circuit ne transfère pas activement un signal. Dans certains cas, des condensateurs de blocage peuvent être utilisés dans les commutateurs pour aborder les problèmes décrits ci-dessus, cependant l'utilisation de condensateurs de blocage peut entraîner une grande

25 superficie de circuit et également réduire les performances de circuit. Par exemple, le circuit peut subir une mauvaise perte d'insertion, une mauvaise linéarité, et/ou une mauvaise isolation.

Selon un premier aspect, l'invention concerne un circuit de commutation comprenant :

- 30 un premier commutateur incluant un transistor à canal n ; et

un deuxième commutateur couplé au premier commutateur, le deuxième commutateur incluant :

un premier transistor à canal p incluant un premier contact de source, un premier contact de drain, un premier contact de grille, et un premier contact de corps ;

5 un deuxième transistor à canal p couplé au premier transistor à canal p, le deuxième transistor à canal p incluant un second contact de source, un second contact de drain, un second contact de grille, et un second contact de corps, dans lequel le premier contact de grille est couplé au second contact de drain, et le premier 10 contact de corps est couplé au second contact de source ; et

une première résistance et une seconde résistance toutes les deux couplées au second contact de grille.

Avantageusement, un ou plusieurs des agencements suivants peuvent être utilisés dans ce premier aspect de l'invention :

15 - la première résistance ou la seconde résistance est une résistance à haute densité ;

- le premier transistor à canal p possède une épaisseur de 1 millimètre (mm) ;

- le deuxième transistor à canal p possède une épaisseur de 3 micromètres (μm) ;

20 - le premier contact de source est couplé à un troisième commutateur qui inclut au moins un troisième transistor à canal p et un quatrième transistor à canal p ;

- le premier contact de grille est couplé à une source d'entrée de tension à courant continu (CC) ;

25 - le premier commutateur est couplé au deuxième commutateur de sorte que le premier transistor à canal p soit directement couplé au premier commutateur et le premier transistor à canal p soit entre le premier commutateur et un contact de terre du circuit de commutation.

Selon un deuxième aspect, l'invention concerne un procédé comprenant :

le couplage d'un contact de grille d'un premier transistor à canal p à effet de champ (FET) à un contact de drain d'un deuxième FET à canal p ;

le couplage d'un contact de corps du premier FET à canal p à un contact de source du deuxième FET à canal p ;

le couplage d'un contact de grille du deuxième FET à canal p à une première résistance et à une seconde résistance ; et

le couplage d'un contact de drain du premier FET à canal p et de la première résistance à un FET à canal n de sorte que le premier FET à canal p soit 5 électriquement positionné entre le FET à canal n et une terre.

Avantageusement, un ou plusieurs des agencements suivants peuvent être utilisés dans ce deuxième aspect de l'invention :

- la première résistance ou la seconde résistance est une résistance à haute densité ;

10 - le premier FET à canal p possède une épaisseur de 1 millimètre (mm) ;

- le deuxième FET à canal p possède une épaisseur de 3 micromètres ( $\mu\text{m}$ ) ;

15 - le premier FET à canal p, le deuxième FET à canal p, la première résistance, et la seconde résistance sont un premier commutateur, et un contact de source du premier FET à canal p est couplé à un deuxième commutateur qui inclut un troisième FET à canal p.

Selon un troisième aspect, l'invention concerne un système comprenant :

une entrée de signal ;

20 un premier commutateur électriquement positionné entre l'entrée de signal et une sortie de signal, le premier commutateur incluant un transistor à canal n à effet de champ (FET) ; et

un deuxième commutateur électriquement couplé entre l'entrée de signal et une terre, et électriquement couplé entre le premier commutateur et la terre, dans lequel le deuxième commutateur inclut :

un premier FET à canal p ;

25 un deuxième FET à canal p couplé au premier FET à canal p, le deuxième FET à canal p incluant un contact de drain couplé à un contact de grille du premier FET à canal p, et un contact de source couplé à un contact de corps du premier FET à canal p ; et

une première résistance et une seconde résistance toutes les deux couplées à 30 un contact de grille du deuxième FET à canal p.

Avantageusement, un ou plusieurs des agencements suivants peuvent être utilisés dans ce troisième aspect de l'invention :

- la première résistance ou la seconde résistance sont une résistance à haute densité ;

- le premier FET à canal p possède une épaisseur de 1 millimètre (mm) ;

- le deuxième FET à canal p possède une épaisseur de 3 micromètres ( $\mu\text{m}$ ) ;

5 - le système comprend en outre un troisième commutateur qui inclut un troisième FET à canal p et un quatrième FET à canal p, dans lequel un contact de source du premier FET à canal p est couplé à un contact de drain du troisième FET à canal p.

Des modes de réalisation sont illustrés à titre d'exemple et non à titre de 10 limitation sur les figures des dessins joints, sur lesquels des références identiques indiquent des éléments similaires et sur lesquels :

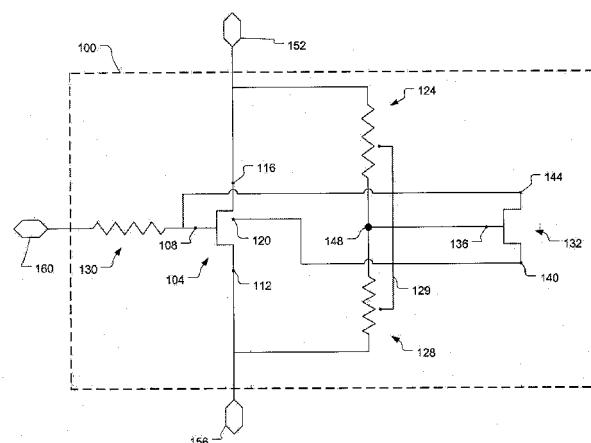

la figure 1 illustre un commutateur à transistor à effet de champ (FET), conformément à divers modes de réalisation.

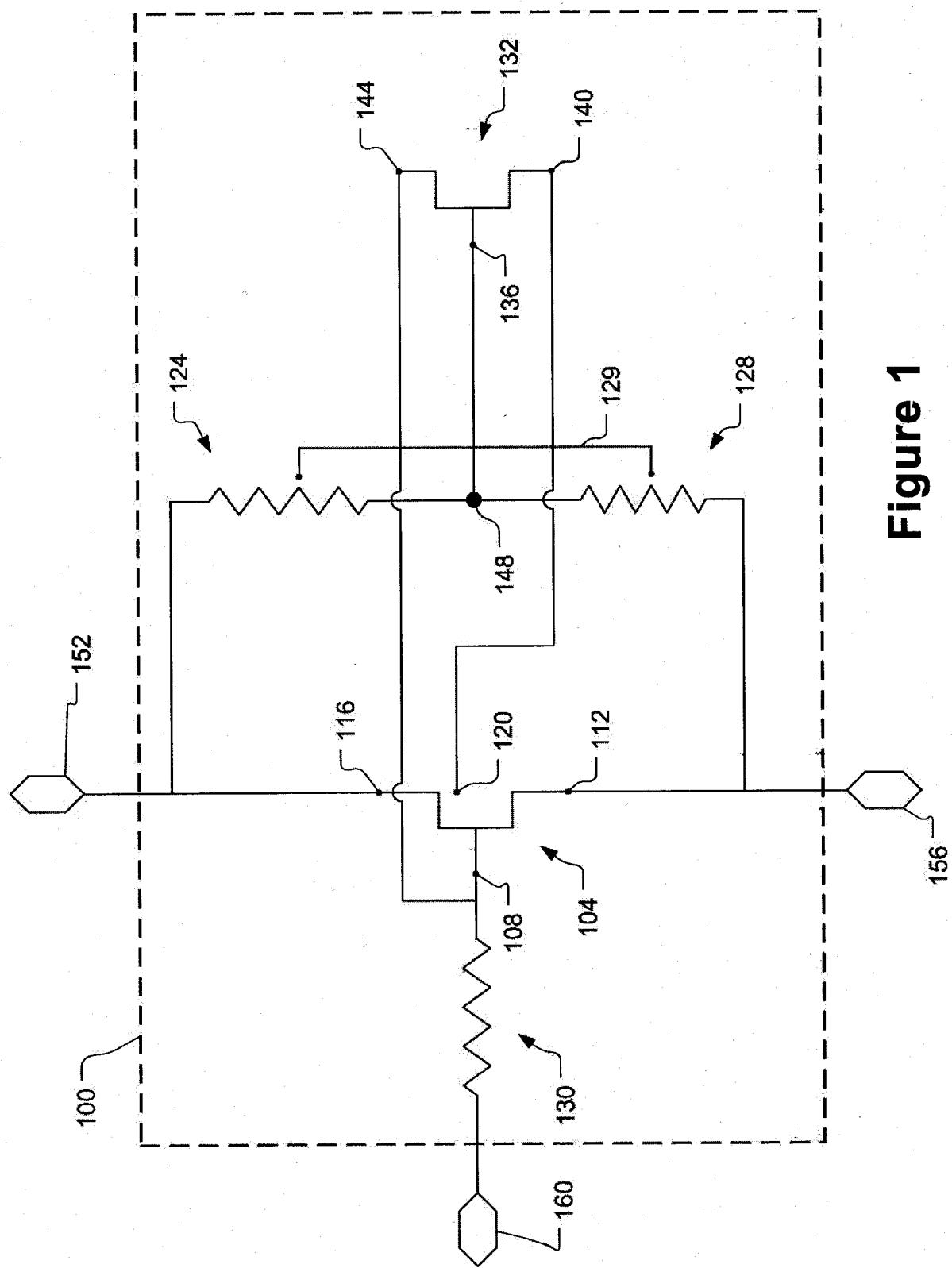

15 la figure 2 illustre un circuit de commutation incorporant une pluralité de commutateurs, conformément à divers modes de réalisation.

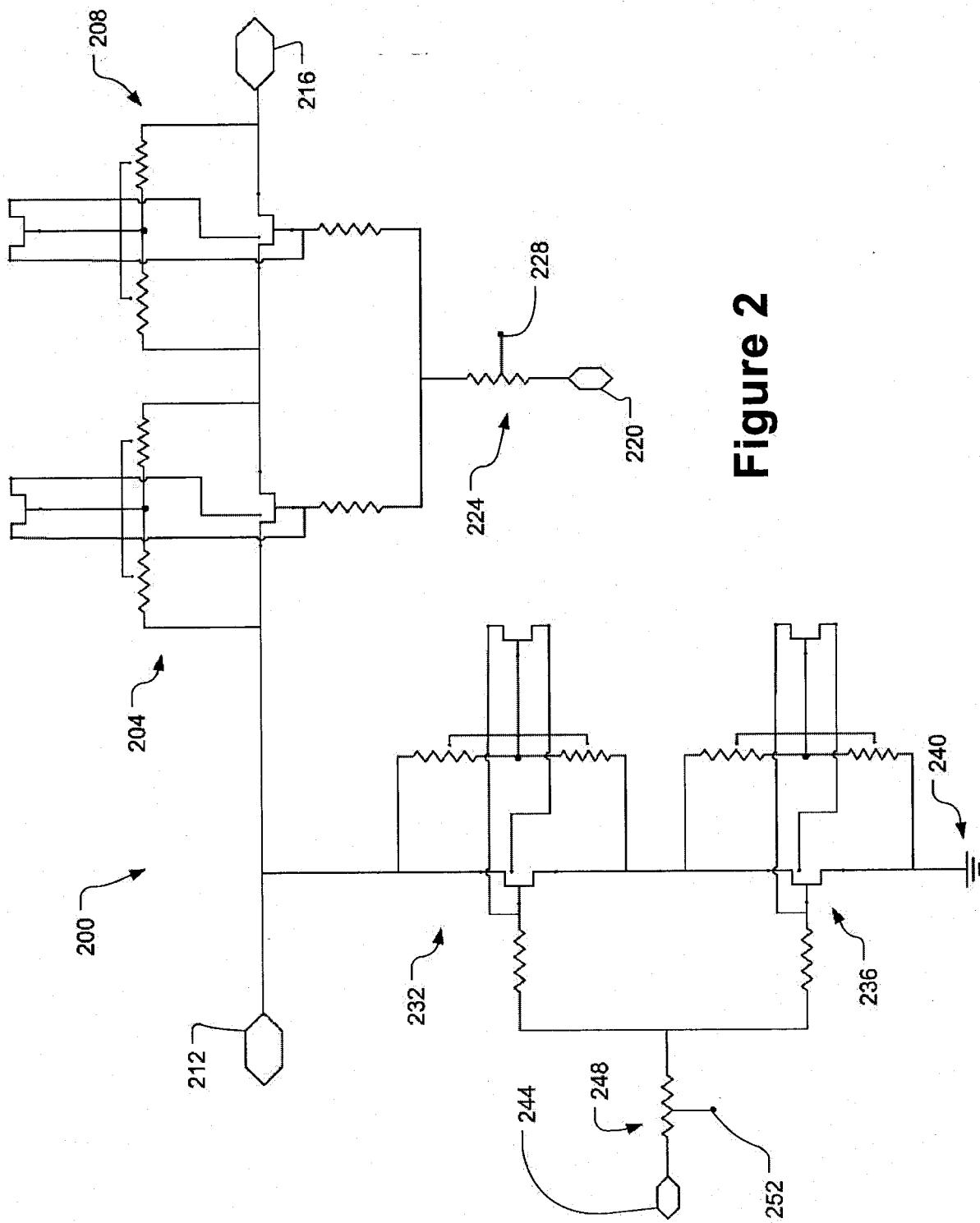

la figure 3 illustre un procédé illustratif de construction d'un circuit de commutation, conformément à divers modes de réalisation.

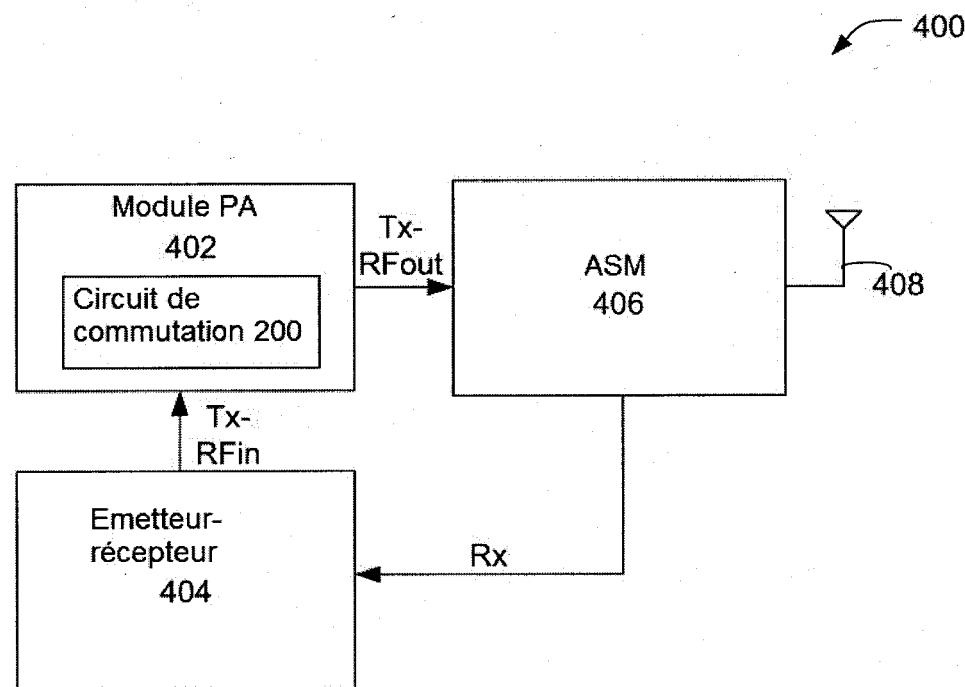

la figure 4 est un schéma de principe d'un dispositif de communication sans fil illustratif, conformément à divers modes de réalisation.

20 Des modes de réalisation comprennent un circuit de commutation. Dans certains modes de réalisation, le circuit de commutation peut comprendre un premier commutateur qui inclut un transistor en commutation à canal n dans le trajet de signal. Le transistor en commutation à canal n peut être un transistor à canal n à effet de champ (FET). Le circuit de commutation peut en outre comprendre un deuxième 25 commutateur en shunt au premier commutateur. Le deuxième commutateur peut comprendre un transistor en commutation et un transistor de décharge pour fournir un trajet de décharge pour un corps du transistor en commutation. Le transistor en commutation et le transistor de décharge peuvent être des transistors à canal p, et plus spécifiquement, des FET à canal p. A fois le transistor à canal n et les transistors à canal p peuvent être couplés à une source de tension configurée pour fournir une tension positive aux commutateurs. Lorsque la source de tension fournit la tension positive, le commutateur qui inclut le transistor en commutation à canal n peut s'allumer de sorte que le commutateur puisse permettre à un signal à radiofréquence 30

(RF) de se propager à travers le commutateur. En même temps, le commutateur qui inclut les transistors à canal p peut s'éteindre en raison de la tension positive. La tension positive peut alors être éliminée, ou une tension négative peut être appliquée, et le commutateur qui inclut le transistor à canal n peut s'éteindre alors que le 5 commutateur qui inclut les transistors à canal p s'allume. D'autres modes de réalisation peuvent être décrits et revendiqués.

Divers aspects des modes de réalisation illustratifs vont être décrits en utilisant des termes couramment utilisés par l'homme du métier pour communiquer la substance de son travail à un autre homme du métier. Cependant, il sera évident, 10 pour l'homme du métier, que d'autres modes de réalisation peuvent être pratiqués avec seulement certains des aspects décrits. Dans des buts explicatifs, des dispositifs et configurations spécifiques sont présentés afin de fournir une compréhension approfondie des modes de réalisation illustratifs. Cependant, il sera évident, pour l'homme du métier, que d'autres modes de réalisation peuvent être pratiqués sans 15 détails spécifiques. Dans d'autres cas, des caractéristiques bien connues sont omises ou simplifiées afin de ne pas compliquer les modes de réalisation illustratifs.

En outre, diverses opérations vont être décrites sous forme de multiples opérations distinctes, tour à tour, d'une manière qui est la plus utile dans la compréhension de la présente invention ; cependant, l'ordre de description ne doit 20 pas être interprété comme impliquant que ces opérations sont nécessairement dépendantes. En particulier, ces opérations n'ont pas besoin d'être réalisées dans l'ordre de présentation.

L'expression « dans un mode de réalisation » est utilisée à plusieurs reprises. L'expression ne fait généralement pas référence au même mode de réalisation ; 25 cependant, elle le peut. Les termes « comprenant », « comportant » et « incluant » sont synonymes, sauf indication contraire du contexte.

Pour fournir un contexte de clarification au langage qui peut être utilisé en association avec divers modes de réalisation, les expressions « A/B » et « A et/ou B » signifient (A), (B), ou (A et B) ; et l'expression « A, B, et/ou C » signifie (A), (B), 30 (C), (A et B), (A et C), (B et C) ou (A, B et C).

Le terme « couplé à », conjointement avec ses dérivés, peut être utilisé dans les présentes. « Couplé » peut signifier un ou plusieurs de ce qui suit. « Couplé » peut signifier que deux, ou plus, éléments sont en contact physiques ou électrique

direct. Cependant, « couplé » peut également signifier que deux, ou plus, éléments entrent indirectement en contact, et cependant coopèrent ou interagissent toujours, et peut signifier qu'un ou plusieurs autres éléments sont couplés ou connectés entre les éléments qui sont dits être couplés les uns aux autres.

5 La figure 1 illustre un commutateur 100 conformément à divers modes de réalisation. Le commutateur 100 peut être un dispositif à silicium sur isolant (SOI) comportant une couche de silicium disposée sur une couche isolante, qui peut également être appelée couche d'oxyde enterré (BOX). Dans certains modes de réalisation, une couche de silicium supplémentaire peut être disposée sous la couche 10 isolante.

15 Dans divers modes de réalisation, la couche de silicium supérieure peut mesurer approximativement 50 à 90 nanomètres (nm) d'épaisseur et la couche isolante, qui peut être une couche de dioxyde de silicium ou de saphir, peut mesurer approximativement 100 à 200 nm d'épaisseur. Dans certains modes de réalisation, le commutateur 100 peut être un dispositif SOI partiellement appauvri (PD-SOI) dans lequel le silicium sous une couche dopée est partiellement appauvri en porteurs de charge libres. La zone partiellement appauvrie peut être appelée région quasi-neutre.

20 Le commutateur 100 peut comprendre un transistor en commutation 104. Dans certains modes de réalisation, le transistor en commutation 104 peut être un transistor à effet de champ (FET). Dans certains modes de réalisation, le transistor en commutation 104 peut présenter une tendance à accumuler des charges dans la région quasi-neutre, comme cela est décrit ci-dessus. Des modes de réalisation décrits dans les présentes permettent la décharge de ces charges accumulées tout en réduisant au moins certains des problèmes identifiés ci-dessus connexes à d'autres 25 techniques conçues pour aborder les problèmes de FBE.

Le transistor en commutation 104 peut comprendre un contact de grille 108, un contact de source 112, un contact de drain 116, et un contact de corps 120. Le commutateur 100 peut en outre comprendre des résistances 124 et 128 couplées en série l'une avec l'autre et en outre couplées aux, et entre les, contact de source 112 et 30 contact de drain 116, comme cela est représenté. Les résistances 124 et 128 peuvent être de taille égale dans certains modes de réalisation. Dans certains modes de réalisation, les résistances 124 et 128 peuvent être des résistances à haute densité. Dans certains modes de réalisation, les résistances 124 et 128 peuvent être couplées

par une ligne de commande 129. Le commutateur 100 peut en outre comprendre une résistance 130 couplée au contact de grille 108.

Le commutateur 100 peut en outre comprendre un transistor de décharge 132.

Dans certains modes de réalisation, le transistor de décharge 132 peut être un FET.

- 5 Le transistor de décharge 132 peut fonctionner pour créer un trajet de décharge pour décharger des charges qui s'accumulent dans la région quasi-neutre du transistor en commutation 104. Le transistor de décharge 132 peut comprendre un contact de grille 136, un contact de source 140, et un contact de drain 144. Le contact de grille 136 peut être couplé à un nœud 148 qui est situé entre les résistances 124

- 10 et 128 ; le contact de source 140 peut être couplé au corps contact 120 ; et le contact de drain 144 peut être couplé au contact de grille 108.

Les résistances 124 et 128 peuvent fournir une terre virtuelle, par exemple, un potentiel fixe, au niveau du nœud 148 et, donc, au niveau du contact de grille 136. L'utilisation du transistor de décharge 132 pour attacher le corps contact 120, le contact de drain 116, et le contact de source 112 au potentiel fixe du nœud 148 peut faciliter l'élimination de la différence de potentiel entre le contact de grille 108 et le corps contact 120 et, donc, décharger des charges de la région quasi-neutre.

Dans certains modes de réalisation, le contact de drain 116 peut être couplé directement ou indirectement avec une borne d'entrée de signal à radiofréquence (RF) 152 par l'intermédiaire de laquelle le commutateur 100 peut recevoir un signal RF. Le contact de source 112 peut être couplé directement ou indirectement avec une borne de sortie de signal RF 156 à partir de laquelle le signal RF peut être envoyé par le commutateur 100. Le contact de grille 108 et/ou le contact de drain 144 peuvent être couplés directement ou indirectement avec une source de tension 160, qui peut fournir une tension de commande pour allumer ou éteindre le transistor en commutation 104 et le transistor de décharge 132, comme cela est décrit ci-dessous.

Dans des modes de réalisation, le commutateur 100 peut fonctionner comme suit. Il faut noter que la description ci-dessous suppose que le transistor en commutation 104 et le transistor de décharge 132 sont tous les deux des FET à canal n. Cependant, comme cela est décrit de façon plus détaillée ci-dessous, dans certains modes de réalisation, le transistor en commutation 104 et le transistor de décharge 132 peuvent tous les deux être des FET à canal p, auquel cas le fonctionnement peut être inversé.

Initialement, le commutateur 100 peut être allumé en allumant le transistor en commutation 104 pour faire passer un signal, par exemple, le signal à radiofréquence (RF) reçu à partir de la borne d'entrée de signal RF 152, du contact de drain 116 au contact de source 112. Dans certains modes de réalisation, le transistor en commutation 104 peut être allumé par application d'une tension continue positive, par exemple, 2,5 volts (V), sur le contact de grille 108 du transistor en commutation 132, par exemple par application de la tension continue positive à partir de la source de tension 160. Le contact de drain 144 du transistor de décharge 132 connaîtra également la tension continue positive. Le contact de grille 136 du transistor de décharge 132 peut connaître une tension 0 à la terre virtuelle. Ceci peut entraîner une tension grille-source,  $V_{gs}$ , de -2,5 V au niveau du transistor de décharge 132. Ceci éteindra le transistor de décharge 132 et, en fait, éliminera le transistor de décharge 132 du commutateur circuit.

Dans certains modes de réalisation, le commutateur 100 peut être éteint pour fournir un trajet de décharge entre le contact de grille 108 et le corps contact 120 du transistor en commutation 104. Dans certains modes de réalisation, le commutateur 100 peut être éteint en éteignant le transistor en commutation 104 pour empêcher le passage d'un signal, par exemple, le signal RF reçu à partir de la borne d'entrée de signal RF 152, du contact de drain 116 au contact de source 112. Dans certains modes de réalisation, le transistor en commutation 104 peut être éteint par application de tension continue nulle ou d'une tension continue négative, par exemple, 0 V ou -2,5 V, sur le contact de grille 108 du transistor en commutation 104. Le contact de drain 144 du transistor de décharge 132 peut également connaître la tension continue négative. Ceci peut entraîner une  $V_{gs}$  positive, par exemple 2,5 V, au niveau du transistor de décharge 132. Ceci peut allumer le transistor de décharge 132, créant ainsi un trajet de décharge par le couplage du contact de grille 108 du transistor en commutation 104 au corps contact 120 du transistor en commutation 104. Ceci peut être réalisé sans devoir fournir une marge de sécurité de tension car il n'y aura aucune chute de tension de seuil.

Bien que le fonctionnement du commutateur 100 soit généralement décrit en termes de l'utilisation d'un FET à canal n en tant que transistor en commutation 104 (également appelé « commutateur NMOS » ou « transistor NMOS »), des modes de

réalisation utilisant un transistor à canal p tel qu'un FET à canal p en tant que transistor en commutation 104 (également appelé « commutateur PMOS » ou « transistor PMOS ») et le transistor de décharge 132 peuvent être utilisés. Dans des modes de réalisation où le transistor en commutation 104 et le transistor de décharge 132 sont des transistors à canal p, l'application d'une tension positive peut faire en sorte que les transistors à canal p s'éteignent alors que l'application d'une tension négative ou d'une tension nulle peut faire en sorte que les transistors à canal n s'allument.

La fourniture d'un trajet de décharge en utilisant le commutateur 100 tel qu'il est décrit ci-dessus peut ne pas entraîner la même pénalité connexe à une marge de sécurité de seuil de tension qui est associée à un circuit de commutateur FET connecté par diode. Des simulations illustratives ont montré que, en ce qui concerne un circuit de commutateur FET connecté par diode, le commutateur 100 peut être associé à une amélioration de 3 dB par rapport à l'IMD, une amélioration de 2,5 dB par rapport à des harmoniques de troisième ordre, et une amélioration de 1,5 dB par rapport à des harmoniques de deuxième ordre.

La fourniture d'un trajet de décharge en utilisant le commutateur 100, comme cela est décrit ci-dessus, peut également entraîner la même pénalité connexe à une perte d'insertion qui est associée à un circuit de commutation à contact de corps (BC) résistif. Des simulations illustratives ont montré que, par rapport à un circuit de commutation BC résistif, le commutateur 100 peut être associé à une amélioration de 40 millidécibels (mdB) ou plus par rapport à la perte d'insertion, une amélioration de 1 dB par rapport à l'IMD, une amélioration de 3,5 dB par rapport à des harmoniques de deuxième ordre, et une amélioration de 0,5 dB par rapport à des harmoniques de troisième ordre.

Le commutateur 100 peut être un amplificateur à grille commune et peut être incorporé dans un grand nombre d'applications y compris, sans toutefois y être limitées, des commutateurs à semi-conducteur à oxyde de métal complémentaire (CMOS), des amplificateurs de puissance, des amplificateurs à faible bruit (LNA), des circuits tampons, des duplexeurs, etc.

Dans certains modes de réalisation, une pluralité de commutateurs 100 peuvent être incorporés dans une conception à circuit unique. La figure 2 illustre un exemple d'un circuit de commutation 200 incorporant un ou plusieurs commutateurs,

qui peuvent chacun être similaires au commutateur 100 décrit ci-dessus. Spécifiquement, le circuit de commutation 200 peut comprendre des commutateurs 204 et 208. Les commutateurs 204 et 208 peuvent être couplés à, et généralement positionnés entre, une entrée de signal RF 212 et une sortie de signal RF 216, qui peuvent être respectivement similaires à l'entrée de signal RF 152 et la sortie de signal RF 156. Les commutateurs 204 et 208 peuvent être respectivement similaires au commutateur 100 décrit ci-dessus, et à la fois les transistors en commutation et les transistors à décharge des commutateurs 204 et 208 peuvent être des transistors à canal n, et plus spécifiquement des FET à canal n, comme cela est décrit ci-dessus. Comme cela est représenté sur la figure 2, les commutateurs 204 et 208 peuvent être couplés l'un à l'autre en série de sorte que le contact de source du transistor en commutation du commutateur 204 soit couplé au contact de drain du transistor en commutation du commutateur 208.

Dans des modes de réalisation, les commutateurs 204 et 208 peuvent être couplés à une source de tension 220 configurée pour fournir une tension positive, par exemple 2,5 V. Dans certains modes de réalisation, une résistance 224 peut être positionnée généralement entre la source de tension 220 et les commutateurs 204 et 208. Dans certains modes de réalisation, la résistance 224 peut comprendre une ligne de commande 228. Dans des modes de réalisation, la source de tension 220 peut être similaire à la source de tension 160, décrite ci-dessus.

Le circuit de commutation 200 peut comprendre des commutateurs supplémentaires 232 et 236. Les commutateurs 232 et 236 peuvent être généralement positionnés entre l'entrée de signal RF 212 et la terre 240. Spécifiquement, on peut dire que les commutateurs 232 et 236 sont en shunt du circuit de commutation 200. Dans des modes de réalisation, les commutateurs 232 et 236 peuvent être couplés à une source de tension 244 configurée pour fournir une tension positive, par exemple 2,5 V. Dans certains modes de réalisation, la source de tension 244 et la source de tension 220 peuvent être la même source de tension, ou autrement être couplées l'une à l'autre. Dans certains modes de réalisation, une résistance 248 peut être positionnée généralement entre la source de tension 244 et les commutateurs 232 et 236. Dans certains modes de réalisation, la résistance 248 peut comprendre une ligne de commande 252.

Les commutateurs 232 et 236 peuvent être respectivement similaires au commutateur 100 décrit ci-dessus, et à la fois les transistors en commutation et les transistors à décharge des commutateurs 232 et 236 peuvent être des transistors à canal p et, plus spécifiquement, des FET à canal p, comme cela est décrit ci-dessus.

- 5 Comme cela est représenté sur la figure 2, les commutateurs 232 et 236 peuvent être couplés l'un à l'autre en série de sorte que le contact de source du transistor en commutation du commutateur 232 soit couplé au contact de drain du transistor en commutation du commutateur 236.

Bien que le circuit de commutation 200 soit décrit avec deux 10 commutateurs 204 et 208 avec les transistors à canal n, et deux commutateurs 232 et 236 avec les transistors à canal p, dans d'autres modes de réalisation, le circuit de commutation peut présenter plus ou moins de commutateurs. Dans certains modes de réalisation, les commutateurs 204 et 208 peuvent comporter des transistors à canal p et les commutateurs 232 et 236 peuvent comporter des transistors à canal n, et la 15 source de tensions 220 et 224 peut être configurée pour fournir une tension négative.

En fonctionnement, le circuit de commutation 200 peut fonctionner comme suit. Un signal RF peut être fourni au niveau de l'entrée de signal RF 212. Une tension positive peut être fournie au niveau des sources de tension 220 et 244. Comme cela est décrit ci-dessus, les commutateurs 204 et 208 peuvent comprendre 20 des FET à canal n. Lorsque les commutateurs 204 et 208 reçoivent la tension positive à partir de la source de tension 220, les transistors de décharge de chacun des commutateurs 204 et 208 peuvent s'éteindre. En outre, les transistors en commutateur peuvent s'allumer de sorte que le signal RF puisse se propager à travers le circuit de commutation 200 de l'entrée de signal RF 212 à la sortie de signal 25 RF 216.

De façon similaire, les commutateurs 232 et 236 peuvent recevoir une tension positive à partir de la source de tension 244. Comme cela est décrit ci-dessus, les commutateurs 232 et 236 peuvent comprendre des FET à canal p. Donc, la tension positive reçue à partir de la source de tension 244 peut faire en sorte que les 30 transistors en commutateur des commutateurs 232 et 236 s'éteignent. Lorsque les transistors en commutateur des commutateurs 232 et 236 sont éteints, un signal peut ne pas pouvoir se propager de l'entrée de signal RF 212 à la terre 240. Donc, la partie en shunt du circuit de commutation 200 peut en réalité être fermée par l'application

d'une tension positive, alors que cette partie de signal du circuit de commutation 200 peut être ouverte par la tension positive.

Par contre, l'application de tension nulle, ou d'une tension de terre, à partir des sources de tension 244 et 220 peut faire en sorte que le circuit de commutation 200 fonctionne d'une manière opposée à la manière décrite ci-dessus. Spécifiquement, l'application de la tension de terre à partir de la source de tension 220 peut faire en sorte que les transistors de décharge de commutateurs 204 et 208 soient allumés, de sorte que des signaux puissent passer à la terre 240. Par exemple, le bruit à partir de l'entrée de signal RF 212 peut être shunté à la terre 240. 10 En même temps, les transistors en commutation des commutateurs 204 et 208 peuvent être éteints pour que le bruit à partir de l'entrée de signal RF 212 puisse ne pas se propager vers la sortie de signal RF 216.

Le circuit de commutation décrit ci-dessus 200 peut profiter de plusieurs avantages. Spécifiquement, le circuit de commutation 200 peut présenter une perte 15 d'insertion améliorée, et une isolation et des performances générales plus importantes, tout en résidant toujours dans une zone relativement compacte. Par exemple, dans certains modes de réalisation, un transistor en commutation d'un commutateur peut présenter une épaisseur d'approximativement 1 millimètre (mm). Un transistor de décharge d'un commutateur peut présenter une épaisseur 20 d'approximativement 1 micron ( $\mu\text{m}$ ). En outre, la vitesse de commutation du circuit de commutation 200 peut être considérée être très rapide. En outre, le circuit de commutation 200 peut être mis en œuvre en utilisant seulement des sources de tension positive, telles que les sources de tension 220 et 244, qui, dans certains modes de réalisation, peuvent être combinées en une seule source de tension positive. 25 Donc, le circuit de commutation 200 peut ne pas nécessiter de condensateurs de blocage ou de générateur de tension négative.

La figure 3 illustre un procédé illustratif pour construire un circuit de commutation, tel que le circuit de commutation 200. Initialement, le contact de grille d'un premier transistor peut être couplé au contact de drain d'un second transistor 30 à 304. Spécifiquement, le contact de grille d'un transistor en commutation, tel que le transistor en commutation 104 d'un commutateur 100 dans un commutateur, tel que le commutateur 232, peut être couplé au contact de drain d'un transistor de décharge, tel que le transistor de décharge 132 dans le commutateur 232.

5 Ensuite, un contact de corps du premier transistor peut être couplé à un contact de source du second transistor à 308. Spécifiquement, le corps contact du transistor en commutation 104 d'un commutateur 100 dans le commutateur 232 peut être couplé au contact de source du transistor de décharge 132 dans le commutateur 232.

10 Ensuite, le contact de grille du second transistor peut être couplé à une première résistance et une seconde résistance à 312. Spécifiquement, le contact de grille du transistor de décharge 132 dans le commutateur 232 peut être couplé à des résistances, telles que les résistances 124 et 128, de sorte que le contact de grille 136 connaisse une terre virtuelle.

15 Enfin, le contact de drain du premier transistor peut être couplé à un deuxième commutateur. Par exemple, le contact de drain du transistor en commutation 104 d'un commutateur 100 dans le commutateur 232 peut être couplé à un autre commutateur, tel que le commutateur 204. Spécifiquement, le contact de drain du transistor en commutation 104 dans le commutateur 232 peut être couplé au contact de drain du transistor en commutation dans le commutateur 204. Comme cela est noté ci-dessus, le transistor de décharge et le transistor en commutation du commutateur 232 peuvent être des FET à canal p, alors que le transistor en commutation du commutateur 204 peut être un FET à canal n.

20 Le commutateur 200 peut être incorporé dans une variété de systèmes. Un schéma de principe d'un système illustratif 400 est illustré sur la figure 4. Comme cela est illustré, le système 400 inclut un module d'amplificateur de puissance (PA) 402, qui peut être un module PA à radiofréquence (RF) dans certains modes de réalisation. Le système 400 peut comprendre un émetteur-récepteur 404 couplé au module PA 402, comme cela est illustré. Le module PA 402 peut comprendre le circuit de commutation 200 pour réaliser une quelconque d'une variété d'opérations telles que l'amplification, la commutation, le mélange, etc. Dans divers modes de réalisation, le circuit de commutation 200 peut en outre/en variante être inclus dans l'émetteur-récepteur 404 pour fournir, par exemple, une conversion ascendante, ou 25 dans un module de commutateur d'antenne (ASM) 406 pour fournir diverses fonctions de commutation.

30 Le module PA 402 peut recevoir un signal d'entrée RF, RFin, à partir de l'émetteur-récepteur 404. Le module PA 402 peut amplifier le signal d'entrée RF,

RFin, pour fournir le signal de sortie RF, RFout. Le signal d'entrée RF, RFin, et le signal de sortie RF, RFout, peuvent tous les deux faire partie d'une chaîne de transmission, respectivement notée par Tx - RFin et Tx - RFout sur la figure 4.

Le signal de sortie RF amplifié, RFout, peut être fourni à l'ASM 406, qui 5 effectue une transmission par liaison radio (OTA) du signal de sortie RF, RFout, par l'intermédiaire d'une structure d'antenne 408. L'ASM 406 peut également recevoir des signaux RF par l'intermédiaire de la structure d'antenne 408 et coupler les signaux RF reçus, Rx, à l'émetteur-récepteur 404 le long d'une chaîne de réception.

Dans divers modes de réalisation, la structure d'antenne 408 peut comprendre 10 une ou plusieurs antennes directionnelles et/ou omnidirectionnelles, y compris, par exemple, une antenne dipôle, une antenne monopôle, une antenne à plaque, une antenne à boucle, une antenne à microruban ou tout autre type d'antenne approprié pour la transmission/réception OTA de signaux RF.

Le système 400 peut être un quelconque système incluant une amplification 15 de puissance. Dans divers modes de réalisation, l'inclusion du circuit de commutation 200 dans le système 400 pour commuter le signal RF peut être particulièrement utile lorsque le système 400 est utilisé pour l'amplification de puissance à hautes puissances et fréquence RF. Par exemple, l'inclusion du circuit de commutation 200 dans le système 400 peut être particulièrement avantageuse pour la 20 transmission de signaux de système mondial de communication avec les mobiles (GSM) avec une puissance d'approximativement 32 dBm ou plus et une fréquence d'approximativement 1800 mégahertz (MHz) ou plus, ainsi que des signaux GSM à bande plus basse, par exemple, 800 MHz à 915 MHz, possédant une puissance d'approximativement 34 dBm ou plus.

25 Le système 400 peut être approprié pour un ou plusieurs quelconques de communications terrestres et satellites, de systèmes radars, et éventuellement dans diverses applications industrielles et médicales. Plus spécifiquement, dans divers modes de réalisation, le système 400 peut être un sélectionné parmi un dispositif radar, un dispositif de communication satellite, un dispositif informatique mobile 30 (par exemple, un téléphone, une tablette, un ordinateur portatif, etc.), une station de base, une radio de diffusion, ou un système d'amplificateur de télévision.

Bien que la présente invention ait été décrite en ce qui concerne les modes de réalisation illustrés ci-dessus, l'homme du métier ordinaire appréciera qu'une grande

variété de mises en œuvres autres et/ou équivalentes, calculées pour obtenir les mêmes objectifs, peuvent être substituées aux modes de réalisation spécifiques présentés et décrits, sans s'éloigner de la portée de la présente invention. L'homme du métier appréciera facilement que les enseignements de la présente invention peuvent être mis en œuvre dans une grande variété de modes de réalisation. La présente description est prévue pour être considérée comme illustrative et non comme restrictive.

REVENDICATIONS

1. Circuit de commutation (200), comprenant :

un premier commutateur (204, 208) incluant un transistor à canal n ; et

un deuxième commutateur (204, 208) couplé au premier commutateur (204, 208), le deuxième commutateur (204, 208) incluant :

- 5 un premier transistor à canal p (104) incluant un premier contact de source (112), un premier contact de drain (116), un premier contact de grille (108), et un premier contact de corps (120) ;

un deuxième transistor à canal p (132) couplé au premier transistor à canal p (104), le deuxième transistor à canal p (132) incluant un second contact de source (140), un second contact de drain (144), un second contact de grille (136), et un second contact de corps, dans lequel le premier contact de grille (108) est couplé au second contact de drain (144), et le premier contact de corps (120) est couplé au second contact de source (140) ; et

une première résistance (124) et une seconde résistance (128) toutes les deux 10 couplées au second contact de grille (136).

- 15 2. Circuit de commutation (200) selon la revendication 1, dans lequel la première résistance (124) ou la seconde résistance (128) est une résistance à haute densité.

- 20 3. Circuit de commutation (200) selon la revendication 1, dans lequel le premier transistor à canal p (104) possède une épaisseur de 1 millimètre (mm).

4. Circuit de commutation (200) selon la revendication 1, dans lequel le deuxième transistor à canal p (132) possède une épaisseur de 3 micromètres ( $\mu\text{m}$ ).

- 25 5. Circuit de commutation (200) selon la revendication 1, dans lequel le premier contact de source (112) est couplé à un troisième commutateur (232, 236) qui inclut au moins un troisième transistor à canal p et un quatrième transistor à canal p.

6. Circuit de commutation (200) selon la revendication 1, dans lequel le premier contact de grille (108) est couplé à une source d'entrée de tension à courant continu (CC) (160).

- 5 7. Circuit de commutation (200) selon la revendication 1, dans lequel le premier commutateur (204, 208) est couplé au deuxième commutateur (204, 208) de sorte que le premier transistor à canal p (104) soit directement couplé au premier commutateur (204, 208) et le premier transistor à canal p (104) soit entre le premier commutateur (204, 208) et un contact de terre du circuit de commutation (200).

- 10 8. Procédé (300), comprenant :

le couplage (304) d'un contact de grille (108) d'un premier transistor à canal p à effet de champ (FET - 104) à un contact de drain (144) d'un deuxième FET à canal p (132) ;

15 le couplage (308) d'un contact de corps (120) du premier FET à canal p (104) à un contact de source (140) du deuxième FET à canal p (132) ;

le couplage (312) d'un contact de grille (136) du deuxième FET à canal p (132) à une première résistance (124) et une seconde résistance (128) ; et

le couplage (316) d'un contact de drain (116) du premier FET à canal p (104) et de la 20 première résistance (124) à un FET à canal n de sorte que le premier FET à canal p (104) soit électriquement positionné entre le FET à canal n et une terre.

9. Procédé selon la revendication 8, dans lequel la première résistance (124) ou la seconde résistance (128) est une résistance à haute densité.

- 25 10. Procédé selon la revendication 8, dans lequel le premier FET à canal p (104) possède une épaisseur de 1 millimètre (mm).

11. Procédé selon la revendication 8, dans lequel le deuxième FET à canal p (132) 30 possède une épaisseur de 3 micromètres ( $\mu\text{m}$ ).

12. Procédé selon la revendication 8, dans lequel le premier FET à canal p (104), le deuxième FET à canal p (132), la première résistance (124), et la seconde

résistance (128) sont un premier commutateur, et un contact de source (112) du premier FET à canal p (104) est couplé à un deuxième commutateur qui inclut un troisième FET à canal p.

- 5 13. Système (400), comprenant :

une entrée de signal (RFin) ;

un premier commutateur électriquement positionné entre l'entrée de signal (RFin) et une sortie de signal (RFout), le premier commutateur incluant un transistor à canal n à effet de champ (FET) ; et

- 10 un deuxième commutateur électriquement couplé entre l'entrée de signal (RFin) et une terre, et électriquement couplé entre le premier commutateur et la terre, dans lequel le deuxième commutateur inclut :

un premier FET à canal p (104) ;

un deuxième FET à canal p (132) couplé au premier FET à canal p (104), le

- 15 deuxième FET à canal p (132) incluant un contact de drain (144) couplé à un contact de grille (108) du premier FET à canal p (104), et un contact de source (140) couplé à un contact de corps (120) du premier FET à canal p (104) ; et

une première résistance (124) et une seconde résistance (128) toutes les deux couplées à un contact de grille (136) du deuxième FET à canal p (132).

- 20 14. Système selon la revendication 13, dans lequel la première résistance (124) ou la seconde résistance (128) sont une résistance à haute densité.

- 25 15. Système selon la revendication 13, dans lequel le premier FET à canal p (104) possède une épaisseur de 1 millimètre (mm).

16. Système selon la revendication 13, dans lequel le deuxième FET à canal p (132) possède une épaisseur de 3 micromètres ( $\mu\text{m}$ ).

- 30 17. Système selon la revendication 13, comprenant en outre un troisième commutateur qui inclut un troisième FET à canal p et un quatrième FET à canal p, dans lequel un contact de source (112) du premier FET à canal p (104) est couplé à un contact de drain du troisième FET à canal p.

1/4

**Figure 1**

2/4

**Figure 2**

3/4

300

**Figure 3**

4/4

**Figure 4**