#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

### (19) World Intellectual Property Organization International Bureau

(43) International Publication Date 13 February 2003 (13.02.2003)

**PCT**

## (10) International Publication Number WO 03/013048 A2

- (51) International Patent Classification<sup>7</sup>: **H04L 1/00**, 5/15, G06F 7/556, H04L 5/02, H04M 11/06

- (21) International Application Number: PCT/US02/24401

- (22) International Filing Date: 31 July 2002 (31.07.2002)

- (25) Filing Language: English

- (26) Publication Language: English

- (71) Applicant: GLOBESPAN VIRATA INCORPORATED [US/US]; 100 Schultz Drive, Red Bank, NJ 07701 (US).

- (72) Inventors: GRAZIANO, Michael, J.; 970 Bluebonnet Drive, Sunnyvale, CA 94086 (US). CHEN, Tsung-Liang; 3121 McKinley Drive, Santa Clara, CA 95051 (US). CHARI, Sujai; 10 Avocet Drive, #204, Redwood City, CA 94065 (US). LUK-PAT, Gerard, T.; 1153 W. Washington Avenue, Sunnyvale, CA 94086 (US). LEUNG, Eric, Tsing-Ho; 1295 Starglo Place, San Jose, CA 95131 (US).

- (74) Agents: DUNCAN, Kevin, T. et al.; Intellectual Property Dept., Hunton & Williams, Suite 1200, 1900 K Street, N.W., Washington, DC 20006-1109 (US).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH,

[Continued on next page]

(30) Priority Data:

60/308,587 31 July 2001 (31.07.2001) US 10/050,129 18 January 2002 (18.01.2002) US 10/050,128 18 January 2002 (18.01.2002) US 10/050.532 18 January 2002 (18.01.2002) US 10/050,533 18 January 2002 (18.01.2002) US 10/050,529 18 January 2002 (18.01.2002) US

**(54) Title:** METHOD AND SYSTEM FOR DETERMINING MAXIMUM POWER BACKOFF USING FREQUENCY DOMAIN GEOMETRIC SIGNAL TO NOISE RATIO

(57) Abstract: The present invention is directed to methods and systems for determining maximum power backoff for modems operating according to G.SHDSL and other standards using frequency domain geometric signal to noise ratio (SNR). In one example, a G.SHDSL standard may specify a minimum power back off (PBO) that may be required for modem implementation. Although the standard specifies the minimum back off, it is desirable to be able to increase the POB beyond this level. The reasons for this may include reduced power consumption and reduced crosstalk generated by a modem. The present invention discloses a method and system for determining an absolute maximum power PBO that may be tolerated and still meet bit error rate (BER) and/or other requirements. The present invention implements a geometric mean to compute SNR in a frequency domain over a pass-band of a transmit spectrum.

WO 03/013048 A2

GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK,

TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

# METHOD AND SYSTEM FOR DETERMINING MAXIMUM POWER BACKOFF USING FREQUENCY DOMAIN GEOMETRIC SIGNAL TO NOISE RATIO

#### 5 FIELD OF THE INVENTION

10

20

25

30

The present invention relates generally to communication systems providing duplex symmetric transmission, more particularly, to determining maximum power backoff for G.SHDSL modem using frequency domain geometric signal-to-noise ratio (SNR); to determining an optimal G.SHDSL data rate using sub-band capacity; to varying G.SHDSL echo canceller filter length based on data rate; to determining an efficient estimation of a base-2 logarithm of a number; and to optimizing performance of non-DMT-based DSL by shaping transmitted power spectral density according to line conditions.

#### 15 BACKGROUND OF THE INVENTION

Traditionally, a modem converts data between the analog form, used for communicating over telephone lines, and the digital form, used on computers for the purposes of computer processing and computer-to-computer communication. Generally, standard modems may transmit data at a maximum rate of 56,000 bits per second (bps) or 56kbps. However, inherent limitations of phone systems may translate to lower modem speeds and other limitations. Modems at a transmitting end modulate the digital data of computers into analog signals to send over telephone lines, such as Plain Old Telephone System (POTS). Then, modems at a destination receiving site demodulate the analog signals back into digital signals to be read by a destination computer on the other end. There are standards to ensure that modems made by different manufacturers can communicate with each other. For example, modems communicating with each other may be required to use the same speed and comply with other requirements.

More recently, modems for cable and Digital Subscriber Line (DSL) service have come to be known as digital modems while those used for traditional dial-up networking are referred to as analog modems. DSL technology provides high-speed,

broadband network connections to homes, businesses and other users. DSL utilizes the same cabling used for normal telephones, while offering higher data rates and other advantages through the use of digital modern technology.

5

10

15

20

25

30

G.SHDSL is a standard that enables manufacturers and other entities to develop Central Office (CO) loop access equipment and Customer Premises Equipment (CPE) around a single standard, thereby increasing market share and decreasing component costs. As a symmetric multi-rate DSL, G.SHDSL can operate over a single pair of copper wires. For speed versatility, the technology can also be deployed over dual copper pairs. G.SHDSL has associated with it a global standard developed by the International Telecommunications Union's (ITU) Telecommunications Standards Sector based in Geneva. Higher bit rate and longer copper transmission line (or loop) are additional factors that strengthen G.SHDSL.

G.hs (handshake) protocol negotiates the highest achievable data rate given the loop conditions. Using the G.hs protocol during pre-activation, service type may be negotiated during start-up (e.g., training). With this protocol, the most efficient framing type may be negotiated to avoid unnecessary overhead and latency on the DSL link.

Optimization of various factors, such as power back off, determination of data rates, filter lengths, transmit power spectral density, and other factors, may affect modem and system performance.

Traditional methods for determining power back off (PBO) are generally computed in the time domain. Similarly, current methods for determining an optimal data rate involve calculating SNR in the time domain and providing an estimate of the capacity. Traditional methods for dynamically adapting the length of a filter result in higher costs and power consumption. Estimation of a base-2 logarithm of a number generally involves a separate polynomial for each range of input numbers or an expansion requiring a large number of terms, which are oftentimes complicated and difficult to implement.

Therefore, there is a need in the art of modem systems for a more efficient method and system for providing efficient communication between modems.

3

#### SUMMARY OF THE INVENTION

5

10

15

20

25

30

Aspects of the present invention overcome the problems noted above, and realize additional advantages. One such inventive aspect provides methods and systems for providing an accurate estimate of the SNR that may be calculated using a frequency domain approach. A maximum amount of PBO may be utilized by a G.SHDSL modem using a geometric SNR.

According to an aspect of the present invention, a method for determining a power backoff value for a first modem comprises the steps of: receiving a signal from a second modem; determining from the signal, information concerning line conditions on a communications channel between the first modem and the second modem; and calculating a signal to noise ratio using a geometric mean for a subband of a total frequency band for a plurality of rates.

Other features of the present invention further include the step of determining a power backoff value for each of the plurality of rates based on the calculated signal to noise ratio; wherein the power backoff value comprises an amount of power backoff in decibels for an estimated line loss; wherein the signal comprises a transmit signal and a noise signal and further comprising a step of determining a first power spectrum of a transmit signal; further comprising a step of determining a second power spectrum of a noise signal; wherein the steps of determining a first power spectrum and a second power spectrum further comprises the steps of computing a discrete Fourier transform of the transmit signal plus the noise signal; and computing a discrete Fourier transform of the noise signal; further comprising the step of using the sub-band to optimally shape a spectrum for determining a power backoff value; wherein the power backoff value satisfies a bit error rate requirement; wherein the steps are performed during a line probe session between a plurality of pre-activation handshaking sessions between a plurality of modems; wherein the step of calculating a signal to noise ratio further comprises the steps of sampling a noise signal; computing a discrete Fourier transform of the noise signal; and estimating a noise power spectral density for the noise signal; further comprising the steps of sampling a transmit signal; computing a discrete Fourier transform of the transmit signal; and estimating a signal and noise power spectral density; further comprising the steps of computing a signal to noise ratio of a

5

10

15

20

25

30

frequency sub-band; and summing a plurality of sub-bands with signal to noise ratio values greater than a predetermined value; wherein the step of determining a power backoff value further comprises the step of shaping a spectrum such that at least one frequency with a signal to noise ratio value above a predetermined value is increasingly attenuated; wherein the step of determining a power backoff value further comprises the step of shaping a spectrum such that at least one frequency associated with a signal to noise ratio value approximately equal to a predetermined threshold is minimally cut back; further comprising the step of shaping a spectrum such that transmitted power is gradually increased with increasing frequency wherein signal to noise ratio is maintained substantially constant through a passband; wherein at least one of the first and second modem operate according to the G.SHDSL standard; wherein the power backoff value comprises a maximum power backoff value for a given bit error rate; wherein the steps are performed at a customer premise equipment; and wherein the steps are performed at a central office.

According to another aspect of the present invention, a system for determining a power backoff value for a first modem comprises a receiving module for receiving a signal from a second modem; a line condition determination module for determining from the signal, information concerning line conditions on a communications channel between the first modem and the second modem; and a calculation module for calculating a signal to noise ratio using a geometric mean for a sub-band of a total frequency band for a plurality of rates.

Other features of the present invention include a power backoff determination module for determining a power backoff value for each of the plurality of rates based on the calculated signal to noise ratio; wherein the power backoff value comprises an amount of power backoff in decibels for an estimated line loss; wherein the signal comprises a transmit signal and a noise signal and further comprising a first power spectrum determination module for determining a first power spectrum of a transmit signal; a second power spectrum determination module for determining a second power spectrum of a noise signal; a first computing module for computing a discrete Fourier transform of the transmit signal plus the noise signal; and a second computing module for computing a discrete Fourier

5

transform of the noise signal; wherein the sub-band is used to optimally shape a spectrum for determining a power backoff value; wherein the power backoff value satisfies a bit error rate requirement; wherein the power backoff value is determined during a line probe session between a plurality of pre-activation handshaking sessions between a plurality of modems; wherein the calculation module further comprises a noise sampling module for sampling a noise signal; a noise transform module for computing a discrete Fourier transform of the noise signal; and a noise estimating module for estimating a noise power spectral density for the noise signal; a transmit sampling module for sampling a transmit signal; a transmit transform module for computing a discrete Fourier transform of the transmit signal; and a signal estimating module for estimating a signal and noise power spectral density; a frequency sub- band computing module for computing a signal to noise ratio of a frequency sub-band and a summing module for summing a plurality of sub-bands with signal to noise ratio values greater than a predetermined value; wherein a spectrum is shaped such that at least one frequency with a signal to noise ratio value above a predetermined value is increasingly attenuated; wherein a spectrum is shaped such that at least one frequency associated with a signal to noise ratio value approximately equal to a predetermined threshold is minimally cut back; wherein a spectrum is shaped such that transmitted power is gradually increased with increasing frequency wherein signal to noise ratio is maintained substantially constant through a passband; wherein at least one of the first and second modem operate according to the G.SHDSL standard; wherein the power backoff value comprises a maximum power backoff value for a given bit error rate; wherein the system is located at a customer premise equipment; and wherein the system is located at a central office.

According to another aspect of the present invention, a method for determining a maximum power backoff value comprises the step of calculating the signal to noise ratio by

$$SNR_{dB} = \frac{10}{\beta - \alpha + 1} \left( \sum_{k=\alpha}^{\beta} D_k \right)$$

5

10

15

20

25

5

10

15

20

25

30

where

$$0 < \alpha < \beta < N-1$$

;  $D_k = \begin{cases} D'_k & D'_k > 0 \\ 0 & otherwise \end{cases}$ ;  $D'_k = \log_{10} \left[ \frac{|\hat{S}(k)|^2}{|W(k)|^2} \right]$ ;

where  $\hat{S}(k)$  represents an estimate of  $k^{th}$  frequency sub-band of a received signal spectrum;  $\hat{W}(k)$  represents an estimate of  $k^{th}$  frequency sub-band of a received noise spectrum;  $\alpha$  represents a starting sub-band;  $\beta$  represents an ending sub-band;  $D_k$  represents one or more sub-bands with SNR greater than zero; and  $D'_k$  represents SNR for  $k^{th}$  sub-band.

Another inventive aspect provides methods and systems for providing an accurate estimate of the channel capacity that may be performed for each symbol rate tested during line probe. In addition, an optimal symbol rate under a set of conditions may be determined using the capacities for each tested symbol rate.

According to an aspect of the present invention, a method for determining a data rate using sub-band capacity in a communication network having a first modem in communication with a second modem over a communication channel comprises the steps of receiving a signal from a first modem; determining from the signal, information concerning line conditions on a communications channel associated with the first modem; calculating an estimate of channel capacity using a geometric mean of capacities of a plurality of frequency domain sub-bands; and determining a data rate based on the estimate of channel capacity.

Other features of the present invention include determining a signal power for each sub-band; determining a noise power for each sub-band; wherein each sub-band is determined with a discrete Fourier transform; wherein each sub-band is sufficiently small such that noise within the sub-band is approximately additive white and gaussian noise; wherein the steps are performed during a line probe session between pre-activation handshaking sessions between a plurality of modems to evaluate performance of a plurality of data rates across a communication channel; wherein the step of calculating further comprises the steps of sampling a noise signal, computing a discrete Fourier transform of the noise signal, and estimating a noise power spectral density for the noise signal; further comprising the steps of sampling a transmit signal, computing a discrete Fourier transform of the transmit signal, and estimating a signal and noise power spectral density; comprising the

5

10

15

20

25

30

7

PCT/US02/24401

steps of computing capacity of each frequency sub-band and summing the capacity of each frequency sub-band to generate a total capacity; wherein at least one of the first modem and the second modem operate according to the G.SHDSL standard for spectral compatibility; wherein the step of determining a data rate, further comprises the step of comparing the estimate of channel capacity for a plurality of rates of interest; wherein the steps are performed at a customer premise equipment; and wherein the steps are performed at a central office.

According to another aspect of the present invention, in a communication network having a first modem in communication with a second modem over a communication channel, a system for conducting symbol rate negotiation and determining a preferred rate comprises a receiving module for receiving a signal from a first modem; a line condition determining module for determining from the signal, information concerning line conditions on a communications channel associated with the first modem; a calculating module for calculating an estimate of channel capacity using a geometric mean of capacities of a plurality of frequency domain sub-bands; and a data rate determining module for determining a data rate based on the estimate of channel capacity.

Other features of the present invention include wherein a signal power is determined for each sub-band; wherein a noise power is determined for each sub-band; wherein each sub-band is determined with a discrete Fourier transform; wherein each sub-band is sufficiently small such that noise within the sub-band is approximately additive white and gaussian noise; wherein the system operates during a line probe session between pre-activation handshaking sessions between a plurality of modems to evaluate performance of a plurality of data rates across a communication channel; a noise sampling module for sampling a noise signal, a noise transform computing module for computing a discrete Fourier transform of the noise signal, and a noise estimating module for estimating a noise power spectral density for the noise signal; a transmit sampling module for computing a discrete Fourier transform of the transmit signal, and a transmit estimating module for estimating a signal and noise power spectral density; a capacity computing module for computing capacity of each frequency sub-band, and a capacity summer for summing the

capacity of each frequency sub-band to generate a total capacity; wherein at least one of the first modem and the second modem operate according to the G.SHDSL standard for spectral compatibility; wherein the estimate of channel capacity is compared for a plurality of rates of interest; wherein the system is located at a customer premise equipment; and wherein the system is located at a central office.

According to another aspect of the present invention, a method for calculating the estimate of channel capacity comprises:

$$C = B_{s} \left( \sum_{k=\alpha}^{\beta} \log_{2} \left( |\hat{W}(k)|^{2} 10^{\frac{(\Gamma - G + \gamma + \delta)}{10}} + |\hat{S}(k)|^{2} \right) - \sum_{k=\alpha}^{\beta} \log_{2} \left( |\hat{W}(k)|^{2} 10^{\frac{(\Gamma - G + \gamma + \delta)}{10}} \right) \right)$$

10

15

20

25

5

where

$$B_s = \frac{B}{(\beta - \alpha + 1)}$$

;  $0 < \alpha < \beta < N-1$ ;  $B_s$  represents a sub-band width in

Hz;  $\hat{S}(k)$  represents an estimated power spectrum of signal;  $\hat{W}(k)$  represents an estimated power spectrum of noise;  $\Gamma$  represents a gap from a theoretical channel capacity for PAM signals in dB; G represents a coding gain of a Trellis decoder in dB;  $\gamma$  represents a required margin in dB;  $\delta$  represents an implementation loss in dB,  $\alpha$  represents an index of a first sub-band and  $\beta$  represents an index of a last sub-band.

Another inventive aspect provides methods and systems for providing efficient use of available CPU cycles that may be achieved by reducing the length of the echo canceller filter. In addition, an echo canceller's adaptive algorithm may be implemented to reach a lower mean squared error (MSE) due to increased training time allowed by cycle reduction. Further, total power consumption of a processor may be reduced by reducing the number of multiplications (and/or other operations) that may be performed by an echo canceller filter for each time iteration. This may be achieved by not performing multiplications on taps that are not being used. In addition, for higher rates, a shorter echo canceller filter may be implemented by transmitting less energy at low frequencies. As a result, the temporal length of the echo channel may be shortened thereby reducing the total number of taps needed to model the channel. According to another embodiment of the present invention, the

5

10

15

20

25

30

present invention may involve increasing performance by reducing CPU cycles per iteration and allowing for more echo canceller training time or the ability to track faster changes in the echo channel by allowing a faster update rate. The present invention provides a static adjustment that may occur before a single echo canceller training session.

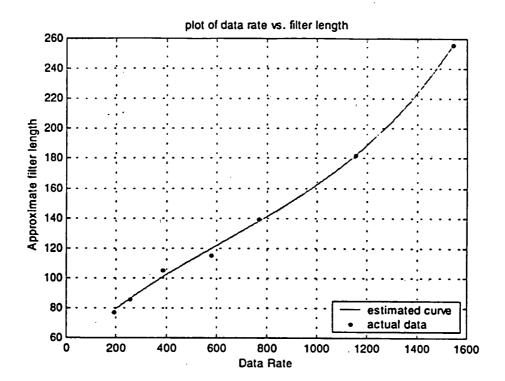

According to an aspect of the present invention, a method for adapting a filter length of an echo canceller filter based on data rate comprises the steps of measuring a plurality of approximate filter lengths at a plurality of data rates; fitting a polynomial to a curve representing the approximate filter lengths at the plurality of data rates; inputting a selected data rate to a function of the polynomial for generating an approximate number of filter taps for modeling an echo channel for the selected data rate; and adjusting the number of filter taps based on the selected data rate; wherein a mean square error associated with the echo canceller filter is reduced.

Other features of the present invention include wherein a number of CPU cycles per filter coefficient update is reduced; wherein a number of echo canceller coefficient updates is increased by a reduction in CPU cycles; wherein the step of adjusting is a static adjustment; wherein the step of adjusting is prior to an echo canceller training session; wherein the curve is a linear curve; wherein training time of the echo canceller filter at lower rates is extended; wherein the filter length comprises a number of filter taps for modeling an echo channel; further comprising the step of determining an echo tail wherein the echo tail comprises a point where at least one filter coefficient decays to a value below a predetermined value towards an end of a filter; further comprising the step of varying the number of filter taps for compensating for the echo tail; wherein the value is approximately equal to one least significant bit; wherein the at least one filter coefficient approaches a noise floor; further comprising the step of detecting an analog delay, wherein the analog delay is a delay in time of an echo; further comprising the step of determining a section of filter taps towards a beginning of a filter, the section of filter taps approaching a quantization noise floor; further comprising the step of varying the number of filter taps for compensating for the analog delay; and wherein the modem operates according to the G.SHDSL standard.

According to another aspect of the present invention, in a communication network having a first modem in communication with a second modem over a communication channel, a system for adapting a filter length of an echo canceller filter based on data rate comprises a measuring module for measuring a plurality of approximate filter lengths at a plurality of data rates; a fitting module for fitting a polynomial to a curve representing the approximate filter lengths at the plurality of data rates; an input module for inputting a selected data rate to a function of the polynomial for generating an approximate number of filter taps for modeling an echo channel for the selected data rate; and an adjusting module for adjusting the number of filter taps based on the selected data rate; wherein a mean square error associated with the echo canceller filter is reduced.

5

10

15

20

25

30

Other features of the present invention include wherein a number of CPU cycles per filter coefficient update is reduced; wherein a number of echo canceller coefficient updates is increased by a reduction in CPU cycles; wherein the adjusting module performs static adjustment; wherein the adjusting module performs an adjustment prior to an echo canceller training session; wherein the curve is a linear curve; wherein training time of the echo canceller filter at lower rates is extended; wherein the filter length comprises a number of filter taps for modeling an echo channel; an echo tail determining module for determining an echo tail wherein the echo tail comprises a point where at least one filter coefficient decays to a value below a predetermined value towards an end of a filter; a varying module for varying the number of filter taps for compensating for the echo tail; wherein the value is approximately equal to one least significant bit; wherein the at least one filter coefficient approaches a noise floor; a detecting module for detecting an analog delay, wherein the analog delay is a delay in time of an echo; a filter tap determining module for determining a section of filter taps towards a beginning of a filter, the section of filter taps approaching a quantization noise floor; a varying module for varying the number of filter taps for compensating for the analog delay; and wherein the modem operates according to the G.SHDSL standard.

According to another aspect of the present invention, a method for adapting a filter length of an echo canceller filter based on data rate comprises the steps of initiating a line probe session; performing an abbreviated echo canceller training

during the line probe session for determining a length of an echo tail; estimating a number of taps for the echo canceller filter based on the abbreviated echo canceller training; and adjusting the number of taps; wherein a mean square error associated with the echo canceller filter is reduced.

Other features of the present invention include the step of calculating a mean filter wherein

$$y_k = \frac{1}{10} \sum_{i=0}^{9} w_{k-i} \quad k = 0, 1 \cdots M - 1$$

where M represents a maximum length in taps of the echo canceller filter and w represents filter coefficients, determining whether  $y_k$  drops below a predetermined threshold, and truncating the echo canceller filter by discarding one or more remaining taps below the predetermined threshold; and wherein the predetermined threshold is determined by

$$20\log_{10}\left(\frac{T}{2^{15}}\right) = -80$$

where

$$T = 2^{15}10^{\frac{-80}{20}} = 3.2768$$

.

5

10

15

20

According to another aspect of the present invention, in a communication network having a first modem in communication with a second modem over a communication channel, a system for adapting a filter length of an echo canceller filter based on data rate comprises a line probe module for initiating a line probe session; a training module for performing an abbreviated echo canceller training during the line probe session for determining a length of an echo tail; an estimating module for estimating a number of taps for the echo canceller filter based on the abbreviated echo canceller training; and an adjusting module for adjusting the number of taps; wherein a mean square error associated with the echo canceller filter is reduced.

Other features of the present invention include a calculating module for calculating a mean filter wherein

$$y_k = \frac{1}{10} \sum_{i=0}^{9} w_{k-i}$$

$k = 0,1 \cdots M-1$

5

10

15

20

25

30

where M represents a maximum length in taps of the echo canceller filter and w represents filter coefficients, a determining module for determining whether  $y_k$  drops below a predetermined threshold, and a truncating module for truncating the echo canceller filter by discarding one or more remaining taps below the predetermined threshold; and wherein the predetermined threshold is determined by

$$20\log_{10}\left(\frac{T}{2^{15}}\right) = -80$$

where

$$T = 2^{15}10^{\frac{-80}{20}} = 3.2768$$

.

Another inventive aspect provides methods and systems for estimating the log base-2 of a fixed point binary number using a single polynomial for an entire possible range of input numbers. This would allow for an accurate computation of SNR in dB, transmit power in dB, BER, and other operations involving a log base-2 calculation.

According to an aspect of the present invention, a system for estimating a logarithm of a number comprises an integer module for determining an integer part of a logarithm of a number; a linear approximation module for determining a linear approximation of a fractional part of the logarithm of the number; and an implementation module for implementing the linear approximation in a single polynomial function for estimating the fractional part; wherein the single polynomial function is used for a range of input values. Other features of the present invention include wherein the single polynomial function is a second order polynomial.

According to another aspect of the present invention, a method for estimating a logarithm of a number comprises the steps of determining an integer part of a logarithm of a number; determining a linear approximation of a fractional part of the logarithm of the number; and implementing the linear approximation in a single polynomial function for estimating the fractional part; wherein the single polynomial function is used for a range of input values. Other features of the present invention include wherein the single polynomial function is a second order polynomial.

According to another aspect of the present invention, a circuit for generating an integer part and an estimate of a fractional part of a logarithm comprises a shift register for loading a valid input data and for generating an estimate of a fractional

5

10

15

20

25

30

part; and a counter for loading a total number of bits in an input data and for generating an integer part; wherein the circuit implements a single polynomial for generating an improved estimate of the fractional part.

Other features of the present invention include wherein the shift register left shifts data by one bit when a most significant bit of the shift register is substantially equal to zero, wherein the shift register left shifts until the most significant bit equals one; and wherein the counter decrements by one when a most significant bit of the shift register is substantially equal to zero, wherein the counter decrements until the most significant bit equals one.

According to another aspect of the present invention, a method for generating an integer part and an estimate of a fractional part of a logarithm comprises steps of loading a valid input data; generating an estimate of a fractional part; loading a total number of bits in an input data; and generating an integer part; wherein a single polynomial is implemented for generating an improved estimate of the fractional part.

Other features of the present invention include wherein the shift register left shifts data by one bit when a most significant bit of the shift register is substantially equal to zero, wherein the shift register left shifts until the most significant bit equals one; and wherein the counter decrements by one when a most significant bit of the shift register is substantially equal to zero, wherein the counter decrements until the most significant bit equals one.

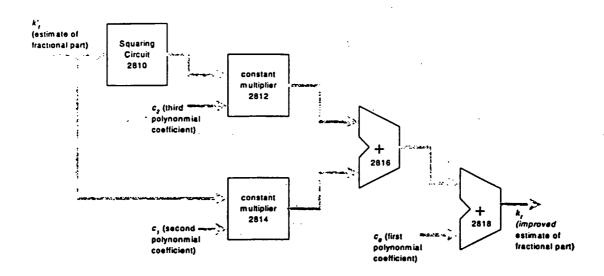

According to another aspect of the present invention, a digital circuit for implementing a polynomial for estimating a fractional part of a logarithm of a number comprises a function circuit for receiving an estimate of a fractional part and for generating a function of the estimate, wherein the function corresponds to an order of the polynomial; a first constant multiplier for multiplying the estimate of a fractional part and a second polynomial coefficient and for generating a first output; a second constant multiplier for multiplying the function of the estimate and a third polynomial coefficient and for generating a second output; a first adder for adding the first output of the first constant multiplier and the second output of the second constant multiplier and for generating a first sum; and a second adder for adding the

5

10

15

20

25

30

14

PCT/US02/24401

first sum and a first polynomial coefficient and for generating an improved estimate of the fractional part.

Other features of the present invention include wherein the order of the polynomial is two; wherein the function circuit is a squaring circuit; and wherein the order of the polynomial is greater than two.

According to another aspect of the present invention, a method for implementing a polynomial for estimating a fractional part of a logarithm of a number comprises the steps of receiving an estimate of a fractional part; generating a function of the estimate, wherein the function corresponds to an order of the polynomial; multiplying the estimate of a fractional part and a second polynomial coefficient, wherein a first output is generated; multiplying the function of the estimate and a third polynomial coefficient, wherein a second output is generated; adding the first output of the first constant multiplier and the second output of the second constant multiplier, wherein a first sum is generated; and adding the first sum and a first polynomial coefficient, wherein an improved estimate of the fractional part is generated.

Other features of the present invention include wherein the order of the polynomial is two; wherein the function circuit is a squaring circuit; and wherein the order of the polynomial is greater than two.

According to another aspect of the present invention, a method for estimating a logarithm of a number comprises the steps of determining an integer part of a logarithm of a number; determining a linear approximation of a fractional part of the logarithm of the number; wherein the linear approximation comprises a fraction minus a constant one wherein a numerator of the fraction is a variable and a denominator of the fraction is two to a power of the integer part; raising the linear approximation to a predetermined power, for generating a fraction estimate; multiplying the fraction estimate by a variable, for generating a product; and summing the product over a predetermined range for generating a polynomial approximation of the fractional part.

Other features of the present invention include wherein the steps are performed to calculate one or more of signal to noise ratio, bit error rate, and power in dB; wherein the system is applied to one or more of ADSL, DSL, and G.SHDSL

15

applications; and wherein the system is applied to one or more of central office, customer premise equipment, and wireless applications.

Another inventive aspect provides methods and systems for improving the performance of a pair of non-DMT-based DSL modems by choosing transmitted PSD's according to the line conditions. In addition, the signal-to-noise ratio (SNR) of both modems may be above some minimum SNR needed for the target bit error rate (BER). Further, the margin levels specified in the respective standard are satisfied.

5

10

15

20

25

30

According to an aspect of the present invention, a method for shaping transmitted power spectral density based on line condition data comprises the steps of determining first line condition data associated with a first modem; determining second line condition data associated with a second modem; exchanging, respectively, the first and second line condition data between the first modem and the second modem; and shaping a transmit spectrum for each of the first modem and the second modem in response thereto.

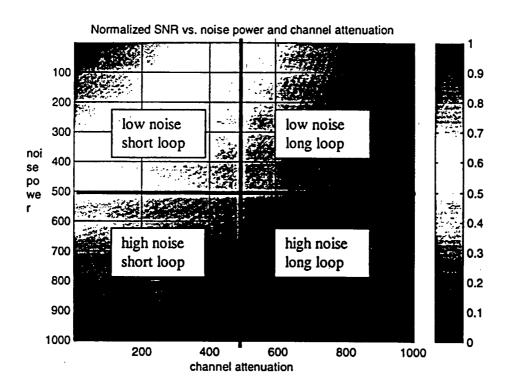

Other features of the present invention include wherein the transmit spectrum of the first modem and the transmit spectrum of the second modem are shaped differently; wherein the transmit spectrum of the first modem and the transmit spectrum of the second modem are shaped substantially the same; further comprising the step of identifying one or more interfering signals that interfere with data received by each of the first modem and the second modem where the interfering signals comprises one or more of noise and echo; wherein the steps are performed prior to a step of modem training; wherein the steps of determining line condition data further comprise the steps of determining a plurality of signal power values associated with at least one of the first modem and the second modem, determining a plurality of noise power values associated with at least one of the local modem and the remote modem, and determining a plurality of signal to noise ratio values associated with at least one of the local modem and the remote modem; wherein line condition data comprises noise data and loop data; wherein noise data occupy a range of values between high noise and low noise and wherein loop data occupy a range of values between short loop and long loop; further comprising the

5

10

15

20

25

30

step of reducing transmitted power for a predetermined plurality of frequencies for reducing uncancelled echo power at a first modem wherein the first modem is a local modem; wherein a maximum loop length is extended for which a signal to noise ratio is maintained above a minimum signal to noise ratio; wherein a noise margin is increased on a loop for which the uncancelled echo power reduces the noise margin, wherein the noise margin comprises an amount of noise that is added after at least one of a first modem and a second modem achieves steady-state while maintaining a signal to noise ratio above a minimum signal to noise ratio; wherein the uncancelled echo power is reduced because of a reduction in one or more effects of a nonlinear echo channel producing noise at frequencies other than a transmitted frequency; wherein the uncancelled echo power is reduced because of a reduction in a required number of echo canceller filter taps; further comprising the step of increasing transmitted power for a predetermined plurality of frequencies for increasing a signal received at the second modem, the second modem being a remote modem, wherein the received signal at the remote modem is determined by the signal transmitted by the first modem, the first modem being a local modem, and loop attenuation; further comprising the step of minimizing a number of transmit filters to be stored by using at least one transmit filter with a plurality of normalized parameters that are normalized to a data rate; wherein the normalized parameters comprise a cutoff frequency of the transmit filter; further comprising the steps of implementing a first power spectral density for optimizing noise performance and implementing a second power spectral density for optimizing reach performance; further comprising the step of interpolating between the first power spectral density and the second power spectral density; wherein the first line condition data and the second line condition data are from a common line; wherein the first line condition data and the second line condition data are from different lines; wherein one or more of the first line condition data and the second line condition data are derived from cross talk; wherein one or more of the first line condition data and the second line condition data comprise a frequency-independent reduction in power determined by calculating a signal to noise ratio using a geometric mean for a sub-band of a total frequency band for a plurality of rates further comprising the step of choosing a transmitted power for a predetermined plurality of frequencies to simultaneously

5

10

15

20

25

30

balance reducing the uncancelled echo power at the local modem while increasing a received signal at the second modem, the second modem being a remote modem; and further comprising the step of choosing a transmitted power for a predetermined plurality of frequencies to simultaneously balance reducing uncancelled echo power at the first modem, the first modem being a local modem, while increasing a received signal at the second modem, the second modem being a remote modem.

17

PCT/US02/24401

According to another aspect of the present invention, a system for shaping transmitted power spectral density based on line condition data comprises a first determining module for determining first line condition data associated with a first modem; a second determining module for determining second line condition data associated with a second modem; an exchanging module for exchanging, respectively, the first and second line condition data between the first modem and the second modem; and a shaping module for shaping a transmit spectrum for each of the first modem and the second modem in response thereto.

Other features of the present invention include wherein the transmit spectrum of the first modem and the transmit spectrum of the second modem are shaped differently; wherein the transmit spectrum of the first modem and the transmit spectrum of the second modern are shaped substantially the same; an identifying module for identifying one or more interfering signals that interfere with data received by each of the first modem and the second modem where the interfering signals comprises one or more of noise and echo; wherein the system is operated prior to modem training; a signal power determining module for determining a plurality of signal power values associated with at least one of the first modem and the second modem, a noise power determining module for determining a plurality of noise power values associated with at least one of the local modem and the remote modem, and a signal to noise ratio determining module for determining a plurality of signal to noise ratio values associated with at least one of the local modem and the remote modem; wherein line condition data comprises noise data and loop data; wherein noise data occupy a range of values between high noise and low noise and wherein loop data occupy a range of values between short loop and long loop; a reducing power module for reducing transmitted power for a predetermined plurality of frequencies for reducing uncancelled echo power at a first modem wherein the

5

10

15

20

25

30

first modem is a local modem; wherein a maximum loop length is extended for which a signal to noise ratio is maintained above a minimum signal to noise ratio; wherein a noise margin is increased on a loop for which the uncancelled echo power reduces the noise margin, wherein the noise margin comprises an amount of noise that is added after at least one of a first modem and a second modem achieves steady-state while maintaining a signal to noise ratio above a minimum signal to noise ratio; wherein the uncancelled echo power is reduced because of a reduction in one or more effects of a nonlinear echo channel producing noise at frequencies other than a transmitted frequency; wherein the uncancelled echo power is reduced because of a reduction in a required number of echo canceller filter taps; an increasing power module for increasing transmitted power for a predetermined plurality of frequencies for increasing a signal received at the second modem, the second modem being a remote modem, wherein the received signal at the remote modem is determined by the signal transmitted by the first modem, the first modem being a local modem, and loop attenuation; a minimizing module for minimizing a number of transmit filters to be stored by using at least one transmit filter with a plurality of normalized parameters that are normalized to a data rate; wherein the normalized parameters comprise a cutoff frequency of the transmit filter; wherein a first power spectral density is implemented for optimizing noise performance; and a second power spectral density is implemented for optimizing reach performance; an interpolating module for interpolating between the first power spectral density and the second power spectral density; wherein the first line condition data and the second line condition data are from a common line; wherein the first line condition data and the second line condition data are from different lines; wherein one or more of the first line condition data and the second line condition data are derived from cross talk; wherein one or more of the first line condition data and the second line condition data comprise a frequency-independent reduction in power determined by calculating a signal to noise ratio using a geometric mean for a sub-band of a total frequency band for a plurality of rates; a selecting module for choosing a transmitted power for a predetermined plurality of frequencies to simultaneously balance reducing the uncancelled echo power at the local modem while increasing a received signal at the second modem, the second modem being a remote modem; and a

selecting module for choosing a transmitted power for a predetermined plurality of frequencies to simultaneously balance reducing uncancelled echo power at the first modem, the first modem being a local modem, while increasing a received signal at the second modem, the second modem being a remote modem.

The accompanying drawings, which are incorporated in and constitute a part of this specification, illustrate various embodiments of the invention and, together with the description, serve to explain the principles of the invention.

#### BRIEF DESCRIPTION OF THE DRAWINGS

5

- The present invention can be understood more completely by reading the following Detailed Description of the Invention, in conjunction with the accompanying drawings, in which:

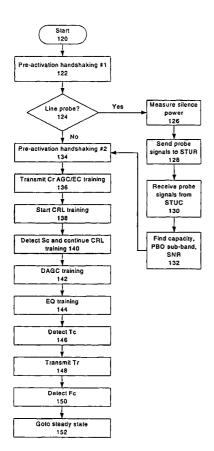

- FIG. 1a is a block diagram illustrating an example of a line probe session, according to an embodiment of a first aspect of the present invention.

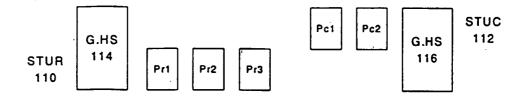

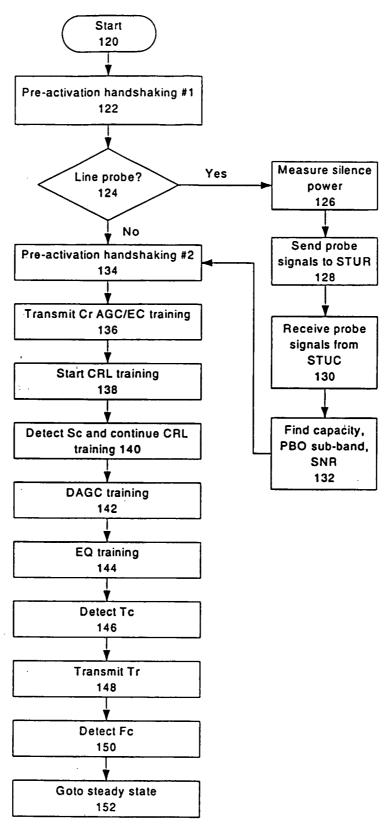

- FIG. 1b is a flowchart illustrating a line probe session for STUR, according to an embodiment of a first aspect of the present invention.

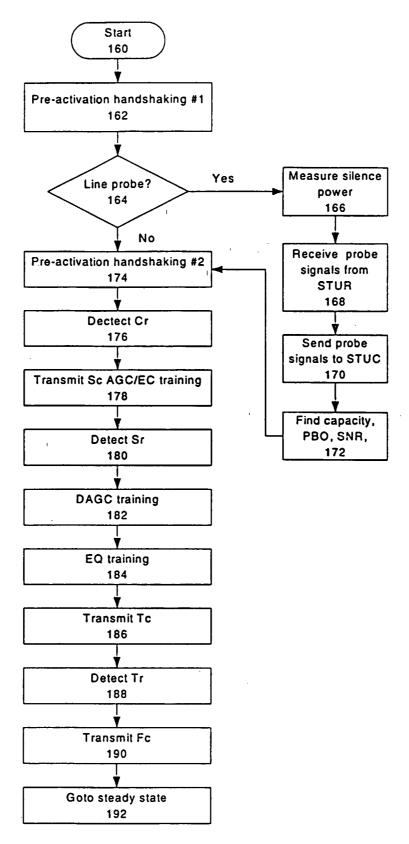

- FIG. 1c is a flowchart illustrating a line probe session for STUC, according to an embodiment of a first aspect of the present invention.

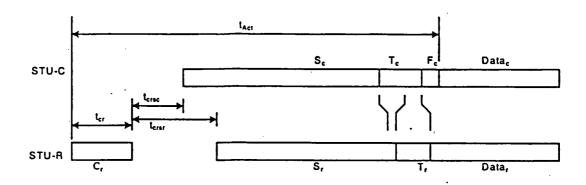

- FIG. 1d is timing diagram, according to an embodiment of a first aspect of the present invention.

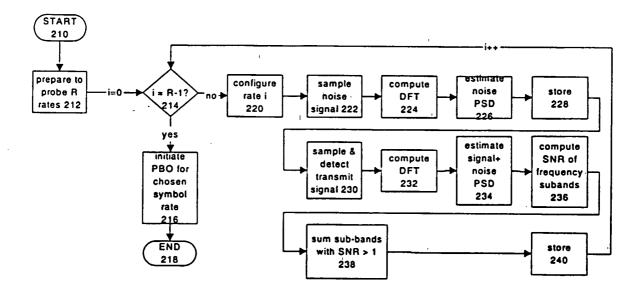

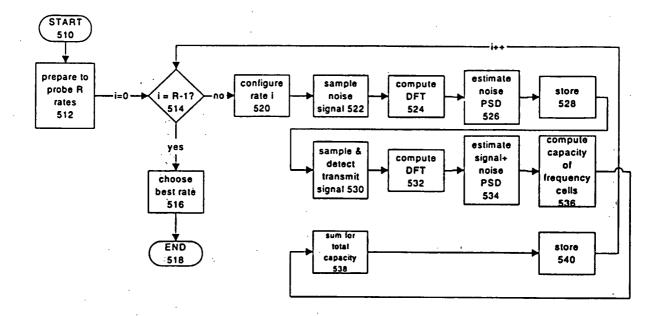

- FIG. 2 is a flowchart illustrating a line probe session with a sub-band SNR calculation, according to an embodiment of the first aspect of the present invention.

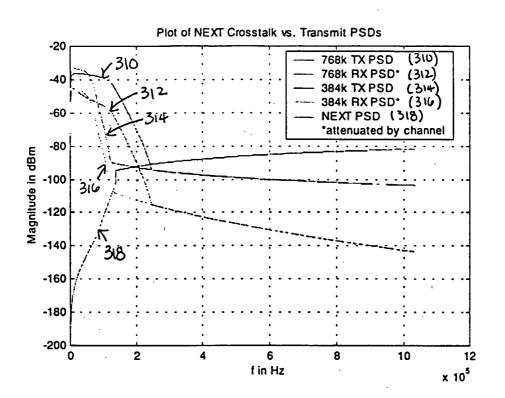

- FIG. 3a is a chart illustrating a noise scenario, according to an embodiment of the first aspect of the present invention.

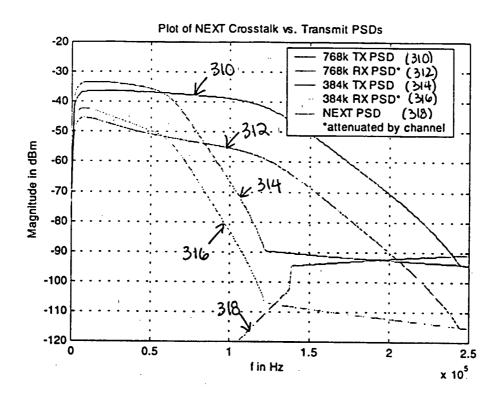

- 25 FIG. 3b is a chart illustrating a noise scenario, according to an embodiment of the first aspect of the present invention.

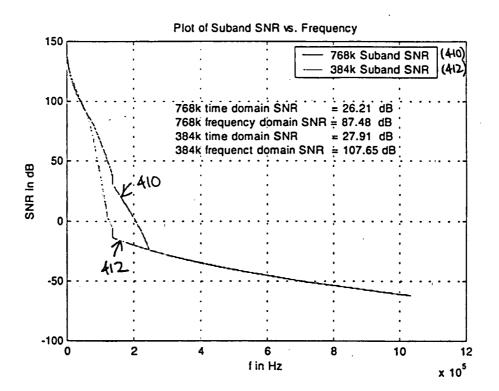

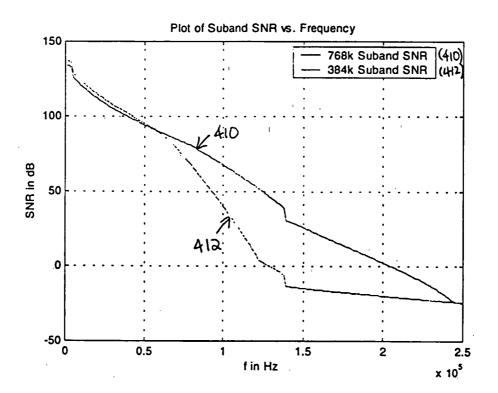

- FIG. 4a is a chart illustrating a sub-band SNR, according to an embodiment of the first aspect of the present invention.

- FIG. 4b is a chart illustrating a sub-band SNR, according to an embodiment of the first aspect of the present invention.

- FIG. 5 is a flowchart illustrating a line probe session with a sub-band capacity calculation, according to an embodiment of a second aspect of the present invention.

5

25

- FIG. 6 is a plot representing normalized SNR vs. noise power and channel attenuation, according to an embodiment of a fifth aspect of the present invention.

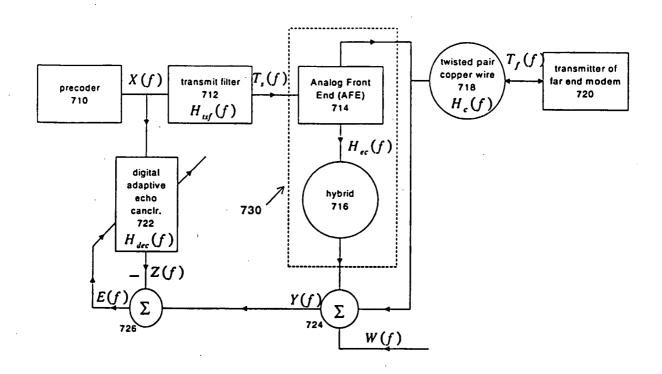

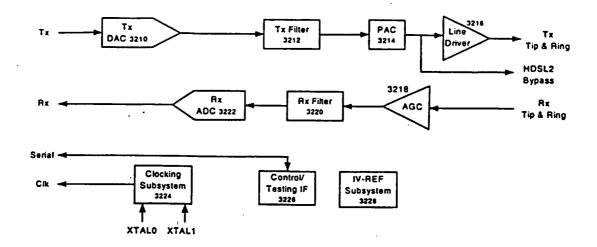

- FIG. 7 is a block diagram of a G.SHDSL system, according to an embodiment of the fifth aspect of the present invention.

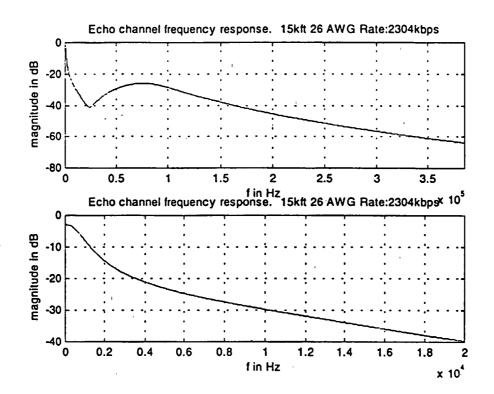

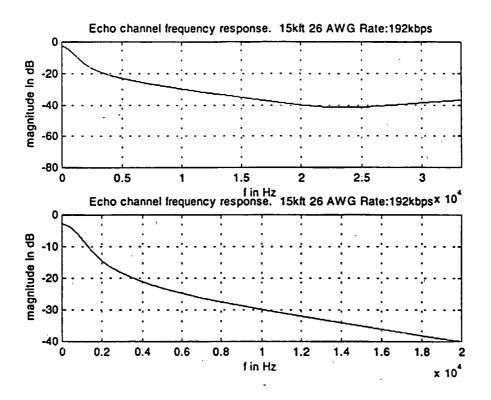

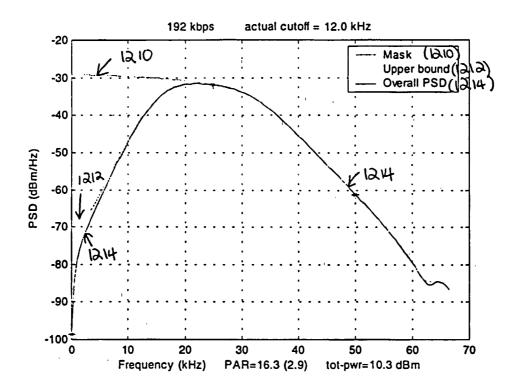

- FIGs. 8-11 are charts illustrating echo channel frequency responses, according to an embodiment of the fifth aspect of the present invention.

- FIG. 12 is a chart illustrating transmit PSD that reduces nonlinear effects at lower frequencies, according to an embodiment of the fifth aspect of the present invention.

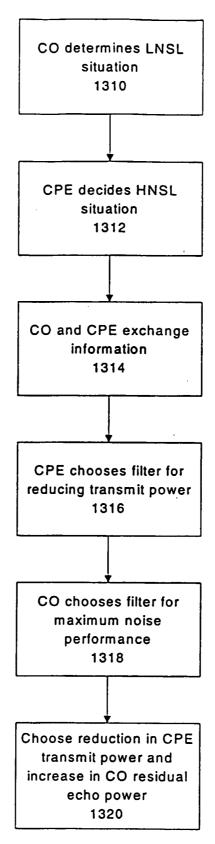

- FIG. 13 is a flowchart illustrating a filter selection method, according to an embodiment of the fifth aspect of the present invention.

- FIG. 14 is a system diagram of a communication network, according to an embodiment of the present invention.

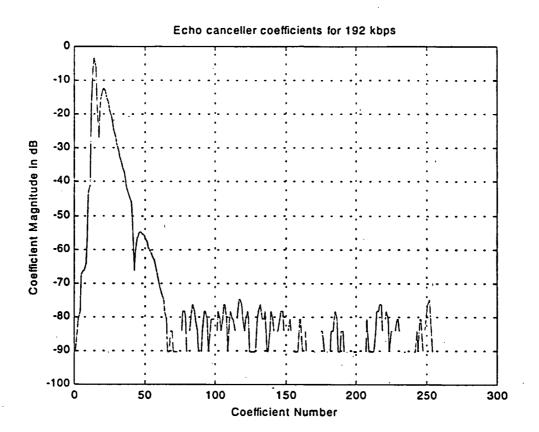

- FIG. 15 is a chart illustrating echo canceller filter taps, according to an embodiment of a third aspect of the present invention.

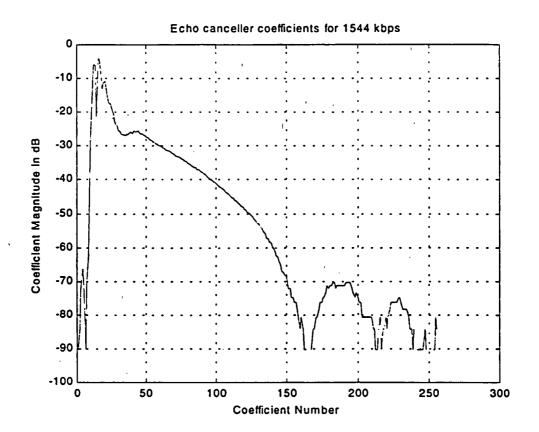

- FIG. 16 is a chart illustrating echo canceller filter taps, according to an embodiment of the third aspect of the present invention.

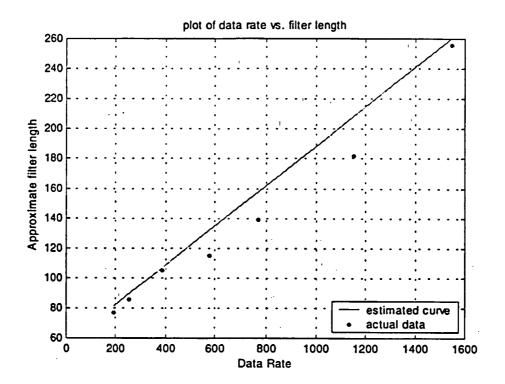

- FIG. 17 is a chart illustrating a polynomial curve used to approximate echo channel length, according to an embodiment of the third aspect of the present invention.

- FIG. 18 is a chart illustrating a linear curve used to approximate echo channel length, according to an embodiment of the third aspect of the present invention.

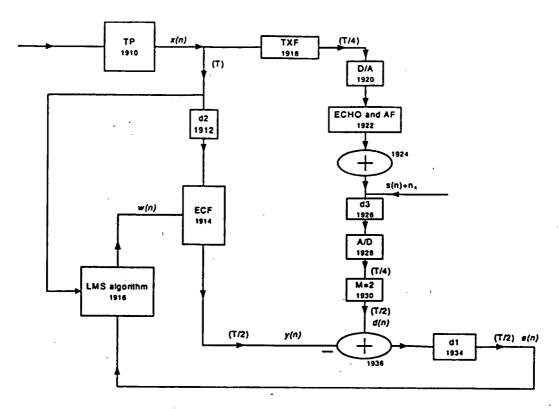

FIG. 19 is a block diagram illustrating basic operations of an echo canceller, according to an embodiment of the third aspect of the present invention.

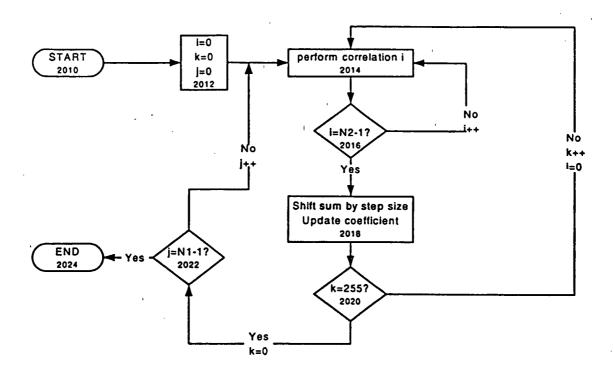

- FIG. 20 is a flowchart illustrating a software algorithm, according to an embodiment of the third aspect of the present invention

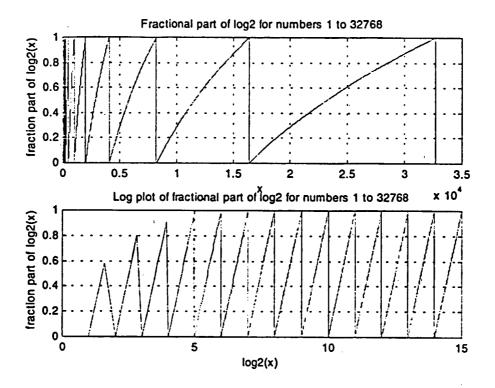

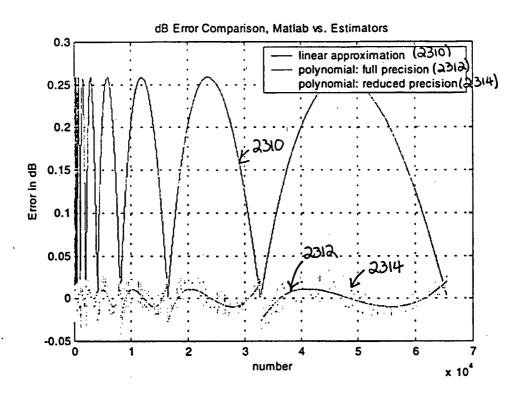

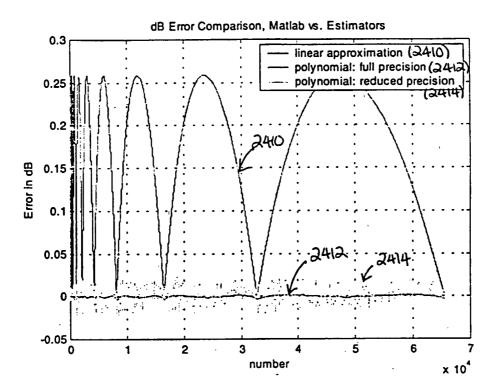

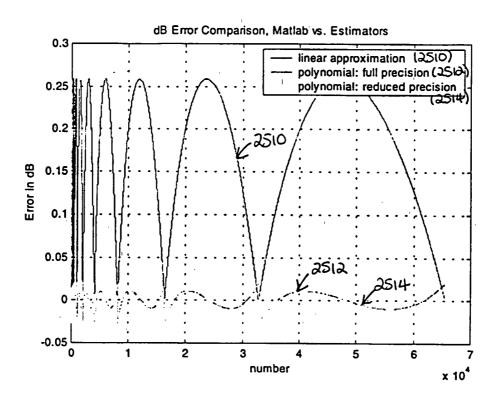

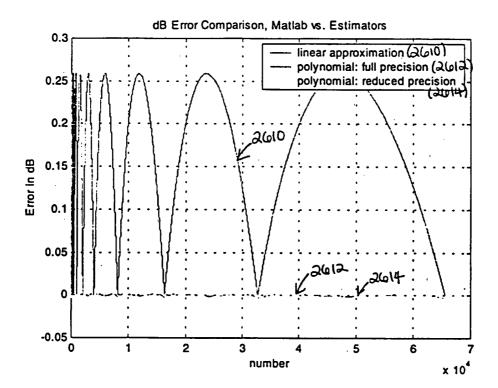

- FIGs. 21 and 22 are charts illustrating a fractional part of a log, according to an embodiment of a fourth aspect of the present invention.

- FIGs. 23-26 are charts illustrating errors of different approximations in terms of dB, according to an embodiment of the fourth aspect of the present invention.

- FIG. 27 is a block diagram of a digital circuit to generate an integer part and estimate of a fractional part of Log-2, according to an embodiment of the fourth aspect of the present invention.

- FIG. 28 is a block diagram of a digital circuit to implement a second order polynomial, according to an embodiment of the fourth aspect of the present invention.

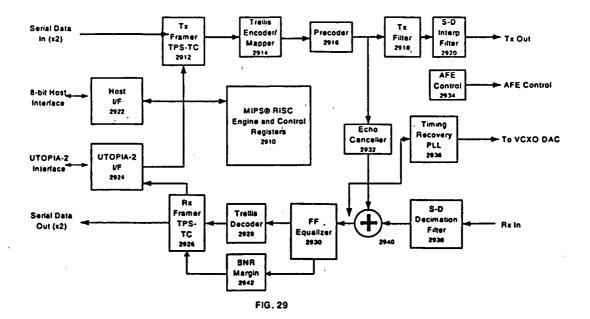

- FIG. 29 is a schematic diagram of a hardware architecture in which the inventive aspects of the present invention may be incorporated.

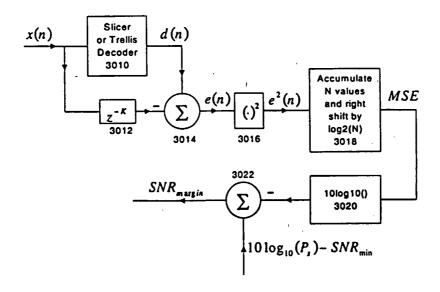

- FIG. 30 is a block diagram illustrating details of SNR margin, according to an embodiment of the present invention.

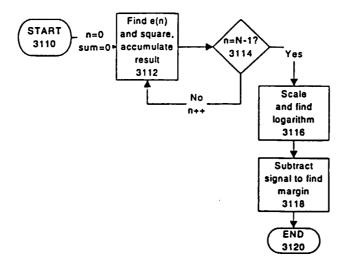

- FIG. 31 illustrates a flowchart describing hardware algorithm for SNR margin, according to an embodiment of the present invention.

- FIG. 32 is a schematic diagram of a hardware architecture in which the inventive aspects of the present invention may be incorporated.

#### LIST OF ACRONYMS

- ADC Analog Digital Converter

- AFE Analog Front End

- AGC Automatic Gain Control

- ANSI American National Standard Institute

- AR autoregressive

22

- ARMA autoregressive moving average

- ATM Asynchronous Transfer Mode

- AWG American Wire Gauge

- AWGN additive white and gaussian

- 5 bps bits per second

- BER bit error rate

- CO- Central Office

- CPE Customer Premises Equipment

- CPU central processing unit

- CRL clock recovery loop

- DAC Digital Analog Converter

- DAGC Digital automatic gain control

- DAV Digital Audio Video

- DFT discrete Fourier transform

- DMT Discrete Multi-Tone

- DSL Digital Subscriber Line

- DSLAMs DSL Access Multiplexers

- EC echo canceller

- EPL estimated power loss

- 20 EQ Equalizer

- ETSI European Telecommunications Standard Institute

- FF Feed Forward

- FIR Finite Impulse Response

- FFT Fast Fourier Transform

- G.hs handshake

- HDSL High Speed Digital Subscriber Line

- IAD Integrated Access Devices

- ITU International Telecommunications Union

- IV-REF Current and Voltage Reference Generator

- LA loop attenuation

- LP line probe

- LSB least significant bit

- MA moving average

- MIPS Million Instructions Per Second

- MMSE Minimum Mean Squared Error

- MSB most significant bit

- MSE mean squared error

- NEXT near end cross talk

- NEXT PSD near end cross talk power spectral density

- PAC programmable attenuation control

- PAR peak-to-average ratio

- PBO power back off

- PGA programmable gain amplifier

- PHY Physical Layer Device

- 15 PLL Phase Locked Loop

- POTS Plain Old Telephone System

- PSD power spectral density

- QMF quadrature mirror filter

- RISC Reduced Instruction Set Computing

- 20 ROI rate of interest

- Rx Receive

- S-D Sigma-Delta

- SDSL Synchronous Digital Subscriber Line

- SNMP Simple Network Management Protocol

- SNR signal to noise ratio

- SOHO small office/home office

- STM Synchronous Transfer Mode

- STUC SHDSL Transceiver Unit Central Office

- STUR SHDSL Transceiver Unit Remote End

- TPS-TC Transmission Protocol Specific Transmission Convergence

Tx - Transmit

WO 03/013048

- USB Universal Serial Bus

- VCXO DAC Volt Controlled Oscillator Digital Analog Converter

5

10

15

20

25

30

#### DETAILED DESCRIPTION OF THE INVENTION

The following description is intended to convey a thorough understanding of the invention by providing a number of specific embodiments and details involving modems applications. It is understood, however, that the invention is not limited to these specific embodiments and details, which are exemplary only. It is further understood that one possessing ordinary skill in the art, in light of known systems and methods, would appreciate the use of the invention for its intended purposes and benefits in any number of alternative embodiments, depending upon specific design and other needs.

24

PCT/US02/24401

An embodiment of the present invention is directed to determining maximum power backoff for a G.SHDSL modem using frequency domain geometric signal to noise ratio (SNR). A G.SHDSL standard may specify a minimum power back off (PBO) for modem implementation. Power back-off may be specified as an amount of PBO in dB for an estimated line loss. Although the standard specifies a minimum back off, it is desirable to be able to increase the PBO beyond the minimum. The reasons for this may include reduced power consumption and reduced crosstalk generated by a modem. An aspect of the present invention discloses a method and system for determining an absolute maximum power PBO that may be tolerated and still meet bit error rate (BER) and/or other requirements. According to another embodiment, the present invention implements a geometric mean to compute SNR in a frequency domain over a pass-band of a transmit spectrum.

During a line probe session, a G.SHDSL modem may determine, among other things, the level of PBO that the modem may support given the line conditions. FIG. 1a illustrates a line probe (LP) session for G.HS (e.g., 114, 116) between SHDSL Transceiver Unit-Central Office (STUR) 110 and SHDSL Transceiver Unit-

Remote End (STUC) 112, which may last a maximum of approximately 10 seconds, for example.

During the transmission of each probe signal, represented by Prx (e.g., Pr1, Pr2, Pr3) and Pcx (e.g., Pc1, Pc2) in FIG. 1a, the modem transmitting the probe may train an associated automatic gain control (AGC) and echo canceller (EC). It may then measure a residual echo signal and use this signal as an estimate of the noise spectrum. In addition, the modem may measure a silence power spectrum during segments where no signals are transmitted. This measurement may be used for a noise spectrum estimate. The modem receiving the probe signal may measure its received signal and noise spectrum. One modem may transmit a probe signal at any given time.

5

10

15

20

25

30

When the modems are not measuring received signals, the modems may calculate a sub-band SNR for each rate using the methods described below and assign a PBO value for the given rate.

FIG. 1b is a flowchart illustrating a line probe session for STUR and FIG. 1c is a flowchart illustrating a line probe session for STUC.

In FIG. 1b, a line probe session for STUR may be initiated at start 120. At step 122, a first pre-activation handshaking may be performed. At step 124, a line probe may be initiated. If the line probe is initiated, silence power may be measured, at step 126. Probe signals may be sent to STUC, at step 128. Probe signals may be received from STUC, at step 130. Capacity, Power back off (PBO) sub-band and signal-to-noise (SNR) may be determined, at step 132. Other calculations and/or factors may be determined as well. A second pre-activation handshaking may be performed at step 134. Cr (which represents a remote unit training signal) Automatic Gain Control (AGC)/echo canceller (EC) training may be transmitted, at step 136. Clock recovery loop (CRL) training may be initiated at step 138. Sc (which represents a central office unit training signal) may be detected and CRL training may continue, at step 140. Digital automatic gain control (DAGC) training may be performed, at step 142. Equalizer (EQ) training may be performed, at step 144. Tc (which represents a central office unit training signal) may be detected, at step 146. Tr (which represents a remote unit training signal) may be

5

10

15

20

25

transmitted, at step 148. Fc (which represents a central office unit training signal) may be detected, at step 150. At step 152, steady state may be achieved.

In FIG. 1c, a line probe session for STUC may be initiated, at start 160. At step 162, a first pre-activation handshaking may be performed. At step 164, a line probe may be initiated. If the line probe is initiated, silence power may be measured, at step 166. Probe signals may be received from STUR, at step 168. Probe signals may be sent to STUR, at step 170. Capacity, PBO, and SNR may be determined, at step 172. Other calculations and/or factors may be determined as well. A second pre-activation handshaking may be performed, at step 174. Cr may be detected, at step 176. Sc AGC/EC training may be transmitted, at step 178. Sc may be detected, at step 180. DAGC training may be performed, at step 182. Equalizer (EQ) training may be performed, at step 184. Tc may be transmitted, at step 186. Tr may be detected, at step 188. Fc may be transmitted, at step 190. At step 192, steady state may be achieved.

FIG. 1d is an example of a timing diagram of an activation sequence. As illustrated, STUR may initiate Cr, lasting a duration of  $t_{\rm cr}$ , which has a nominal value of 1 second with  $\pm$  20 millisecond tolerance. Time from the end of Cr to a beginning of Sc is represented by  $t_{\rm crsc}$ , which has a nominal value of 500 millisecond with  $\pm$  20 millisecond tolerance. After a time  $t_{\rm crsc}$ , STUC may initiate Sc. Time from the end of Cr to a beginning of Sr is represented by  $t_{\rm crsr}$ , which has a nominal value of 1.5 second with  $\pm$  20 millisecond tolerance. After a time  $t_{\rm crsr}$ , STUR may initiate Sr. After Sc, STUC may initiate Tc. After Sr, STUR may initiate Tr. After Tc, STUC may initiate Fc. At approximately the same time, Data<sub>c</sub> and Data<sub>r</sub> may be initiated by STUC and STUR, respectively. Time from the beginning of Cr to the beginning of Data<sub>r</sub> is represented by  $t_{\rm Actdata}$ , which has a nominal value of 15 seconds.

If the SNR is calculated in the time domain, one method to determine PBO is according to the equations shown below.

$$SNR_{dB} = 10log_{10} \left( \frac{P_{signal+noise}}{P_{noise}} \right) = 10log_{10} \left( \frac{\sum_{n=0}^{M-1} |[s(n) + w(n)]|^2}{\sum_{n=0}^{M-1} |w(n)|^2} \right)$$

$$PBO_{dB} = SNR_{dB} - (\gamma + \delta + SNR_{min})$$

(2)

$s(n) = n^{th}$  sample of the received signal

$w(n) = n^{th}$  sample of the received noise

M = window length in samples used to compute average

$P_{signal+noise} =$ power of signal + noise

$P_{noise}$  = power of noise only

5

10

15

20

25

where  $\gamma$  represents a required margin in dB ( $\geq$  0 dB, example: G.SHDSL Annex B margin is 6 dB); SNR<sub>min</sub> represents a minimum SNR in dB needed to obtain the specified BER, and  $\delta$  represents an implementation loss in dB.

A problem with this estimate is not being localized in frequency. Finding the noise and signal powers as shown in (1) and (2) above may be the equivalent of integrating under the entire frequency domain PSD. For a sub-band of the total frequency band, this estimate may not produce the desired results.

According to an embodiment of the present invention, PBO selection may be based on a sub-band SNR calculation. FIG. 2 illustrates a flowchart for a line probe session with a sub-band SNR calculation, according to an embodiment of the present invention. At step 210, a line probe session may be initiated. At step 212, a process for preparing to probe R rates may be initiated. At step 214, it may be determined whether i = R-1, where i represents an index for the rate. If so, PBO may be initiated for a chosen symbol rate, at step 216. The line probe session may be terminated at step 218. If i does not equal R - 1, rate i may be configured, at step 220. At step 222, a noise signal may be sampled. At step 224, a discrete Fourier transform (DFT) may be computed for the noise signal. At step 226, noise power spectral density (PSD) may be estimated for the noise signal may be sampled and detected. At step 232, a DFT may be computed for the transmit signal. At step 234, a signal and noise PSD may be estimated. At step 236, a SNR of frequency sub-

28

bands may be computed. At step 238, sub-bands satisfying a condition (e.g., SNR > 1) may be summed. At step 240, relevant information may be stored. Following step 240, the process may return to step 214 to again determine whether i = R-1, where the variable i has been increased by a predetermined value (as shown by i++). For verification of a symbol rate with the new PBO value, the line probe can be restarted with a new PBO.

According to an embodiment of the present invention, to compute the SNR based on frequency domain data, power spectrums of the signal and noise may be determined, as shown in the equations below.

10

5

$$Y(k) = \frac{1}{N} \sum_{n=0}^{N-1} [s(n) + w(n)] \exp\left(\frac{-2 \cdot \pi \cdot j \cdot k \cdot n}{N}\right) = S(k) + W(k)$$

(3)

$$W(k) = \frac{1}{N} \sum_{n=0}^{N-1} w(n) \exp\left(\frac{-2 \cdot \pi \cdot j \cdot k \cdot n}{N}\right)$$

(4)

$s(n) = n^{th}$  time sample of the received signal  $w(n) = n^{th}$  time sample of the received noise N = window length in time samples used to compute spectrum  $S(k) = k^{th}$  frequency suband of the received signal spectrum  $W(k) = k^{th}$  frequency suband of the received noise spectrum  $Y(k) = k^{th}$  frequency suband of signal plus noise spectrum  $j = \sqrt{-1}$

where S(k) represents a DFT of the signal; W(k) represents a DFT of noise; Y(k) represents a DFT of signal-plus-noise; s(n) represents a transmit signal; w(n) represents a noise signal.

According to an embodiment of the present invention, these transforms may be computed with Fast Fourier Transform (FFT). A real 2N input sequence may be packed into an N point complex sequence as shown below. According to an embodiment of the present invention, transform weights may be computed on the fly using the method shown below. Frequency cells may be estimated using a number of methods other than a conventional DFT, such as autoregressive (AR), moving

average (MA), autoregressive moving average (ARMA), quadrature mirror filter (QMF) filter bank, and other methods.

To illustrate a geometric SNR, a geometric mean may be defined as follows:

$$mean_{geometric} = \left(\prod_{i=0}^{M-1} a_i\right)^{\frac{1}{M}} \tag{5}$$

$a_i = i^{th}$  sample used for average

M = window size in samples used for average

Using the geometric mean, a SNR of the channel may be computed using the following:

$$SNR \cong \left[ \left[ \prod_{k=\alpha}^{\beta} \frac{|Y(k) - \hat{W}(k)|^2}{|W(k)|^2} \right]^{\frac{1}{\beta - \alpha + 1}} \right]$$

(6)

10

5

$$SNR \cong 10\log_{10} \left[ \left[ \prod_{k=\alpha}^{\beta} \frac{|Y(k) - \hat{W}(k)|^2}{|W(k)|^2} \right]^{\frac{1}{\beta - \alpha + 1}} \right] = \frac{10}{\beta - \alpha + 1} \sum_{k=\alpha}^{\beta} \log_{10} \left[ \frac{|\hat{S}(k)|^2}{|W(k)|^2} \right] (7)$$

which may be rewritten in the following manner to filter cells with negative or zero SNR

15

$$D'_k = \log_{10} \left[ \frac{|\hat{S}(k)|^2}{|W(k)|^2} \right]$$

(8)

$$D_{k} = \begin{cases} D'_{k} & D'_{k} > 0\\ 0 & otherwise \end{cases}$$

(9)

$$SNR_{dB} = \frac{10}{\beta - \alpha + 1} \left( \sum_{k=\alpha}^{\beta} D_k \right)$$

(10)

5

10

15

20

25

30

30

where  $0 < a < \beta < N-1$ ;  $\hat{S}(k)$  represents an estimate of  $k^{th}$  frequency sub-band of a received signal spectrum;  $\hat{W}(k)$  represents an estimate of  $k^{th}$  frequency sub-band of a received noise spectrum; Y(k) represents a  $k^{th}$  frequency sub-band of signal plus noise spectrum;  $\alpha$  represents a starting sub-band;  $\beta$  represents an ending sub-band;  $D_k$  represents one or more sub-bands with SNR greater than zero;  $D'_k$  represents SNR for  $k^{th}$  sub-band.

The following example illustrates a sub-band SNR calculation where the sub-band approach may be used to optimally shape a spectrum for maximum power back off. The FIGs. 3a, 3b, 4a and 4b illustrate two data rates, 768,000 bps and 384,000 bps. FIGs. 3a and 3b show the transmitted and received spectrums as well as the near-end crosstalk power spectral density (NEXT PSD), which is essentially the received noise spectrum.

FIGs. 3a and 3b illustrate a noise scenario including 30 NEXT disturbers of ADSL downstream with a loop length of 5000 feet of 26 AWG twisted-pair, which is the noise spectrum generated by 30 twisted pair ADSL modems in the same wire bundle as the modem being simulated, according to an embodiment of the present invention. As can be seen by these plots, most of the noise energy is concentrated outside of the transmission band of the modem. More specifically, plot 310 represents 768k TX PSD, plot 312 represents 768k RX PSD, plot 314 represents 384k TX PSD, plot 316 represents 384 RX PSD, and plot 318 represents NEXT PSD wherein RX plots 312 and 316 may be attenuated by the channel. When the SNR is computed in the time domain, some or all of out of band noise may be averaged in a SNR estimate. The SNR estimate may be considered conservative as much of the out of band noise may be removed with a receive filter and equalizer, for example. If the power cutback is based on this time domain SNR, it may also be considered conservative. Thus, using the sub-band SNR, in accordance with the present invention, provides the ability to back off the power more aggressively.

FIGs. 4a and 4b illustrate a sub-band SNR, according to an embodiment of the present invention. As illustrated, frequency domain SNR for certain frequencies may be significantly higher than time domain numbers included on the plot. Plot 410 represents 768k sub-band SNR and plot 412 represents 384k sub-band SNR, as

shown in FIGs. 4a and 4b. For example, if the required SNR to achieve the minimum BER is 24 dB, the time domain SNR for 768k may suggest a maximum of approximately 2 dB PBO. However, looking at the frequency domain SNR computed with the geometric mean across a transmission band, with an average SNR of 87.48 dB, the PBO may be significantly more. For example, 26.21 (SNR time) minus 24 (min BER) equals 2.21 dB while 87.48 minus 24.00 equals 63.48 dB.

One way to achieve a maximum (or optimal) PBO involves shaping the spectrum such that frequencies with the highest SNR are attenuated the most and frequencies where the SNR is close to the threshold are not cutback or minimally cutback. For example, as shown in FIGs. 4a and 4b, the SNR may increase as frequency decreases. The filter's spectral shape may gradually increase the transmitted power with increasing frequency, maintaining an approximately constant SNR throughout the passband.

The following equations illustrate a method for packing a 2N-point real input signal into an N-point complex input for efficient computation of the FFT.

$$y(n) = s(2n) + js(2n+1) = h(n) + jg(n)$$

(11)

where n = 0, 1 N - 1

5

10

25

$$Y(k) = \frac{1}{N} \sum_{n=0}^{N-1} y(n) \exp\left(\frac{-2 \cdot \pi \cdot j \cdot k \cdot n}{N}\right) = R(k) + jI(k)$$

(12)

20

$$S_R(k) = \frac{1}{2} [R(k) + R(N-k)] + \frac{1}{2} \cos\left(\frac{\pi k}{N}\right) [I(k) + I(N-k)] - \frac{1}{2} \sin\left(\frac{\pi k}{N}\right) [R(k) - R(N-k)]$$

$$(k)$$

$$S_{I}(k) = \frac{1}{2} \left[ I(k) - I(N - k) \right] + \frac{1}{2} \sin \left( \frac{\pi k}{N} \right) \left[ I(k) + I(N - k) \right] - \frac{1}{2} \cos \left( \frac{\pi k}{N} \right) \left[ R(k) - R(N - k) \right]$$

(14)

Equations (11) to (14) are described in "The Fast Fourier Transforms and it's Applications" by E. Oran Brigham –1988 – Figure 9.15, page 193.

A recursive calculation of FFT weights may be implemented to save storage space until FFT is performed.

$$\exp\left(-\frac{2\cdot\pi\cdot j\cdot n\cdot k}{N}\right) = \cos\left(\frac{2\cdot\pi\cdot n\cdot k}{N}\right) - j\sin\left(\frac{2\cdot\pi\cdot n\cdot k}{N}\right)$$

(15)

Equation (15) is described in "The Fast Fourier Transforms and it's Applications" by E. Oran Brigham –1988 – equation 6.16, page 97.

5 The first cosine and sine terms may be found using the equations below.

$$R_0 = \cos\left(\frac{4\pi}{N_{real}}\right) \tag{16}$$

$$I_0 = -\sin\left(\frac{4\pi}{N_{real}}\right) \tag{17}$$

where

WO 03/013048

$N_{real}$  = real FFT size

$R_0 = \text{zero}^{\text{th}}$  sample of real part of exponential weight

$I_0 = zero^{th}$  sample of imaginary part of exponential weight

10

20

The equations to recursively compute the transform weights are given below:

$$R_{m} = R_{0} \cdot R_{m-1} - I_{0} \cdot I_{m-1} \tag{18}$$

$$I_{m} = I_{0} \cdot R_{m-1} + R_{0} \cdot I_{m-1} \tag{19}$$

15 where m = 1, 2,

$$\cdots \frac{N_{real}}{4}$$

$R_m = m^{\text{th}}$  sample of real part of exponential weight

$I_m = m^{th}$  sample of imaginary part of exponential weight

Since the input to the FFT is real, it may be more efficient to form a complex input to the FFT and then unpack the results to obtain the spectrum of the original real signal. This may involve the computation of additional weights as shown in equations (20) and (21).

$$R_{p} = \cos\left(\frac{2 \cdot \pi \cdot p}{N_{real}}\right) \tag{20}$$

$$I_{p} = \sin\left(\frac{2 \cdot \pi \cdot p}{N_{real}}\right) \tag{21}$$

where

$$p=1,2\cdots\frac{N_{real}}{2}$$

$R_n = p^{th}$  sample of cosine recombination weights

$I_p = p^{th}$  sample of sine recombination weights

To avoid calling the sine and cosine function for each weight, the identity for computing the weights recursively may be derived as in equations (18) and (19) above.

Starting with the trigonometric identities below, a recursive equation may be used to find the terms in (20) and (21).

$$\cos(A \pm B) = \cos(A)\cos(B) \mp \sin(A)\sin(B) \tag{22}$$

$$10 \quad \sin(A \pm B) = \sin(A)\cos(B) \pm \cos(A)\sin(B) \tag{23}$$

$$R_{p} = \cos\left(\frac{2 \cdot \pi \cdot p}{N_{real}}\right) = \cos\left(\frac{2 \cdot \pi}{N_{real}} + \frac{2 \cdot \pi \cdot (p-1)}{N_{real}}\right) =$$

$$\cos\left(\frac{2 \cdot \pi}{N_{real}}\right) \cos\left(\frac{2 \cdot \pi \cdot (p-1)}{N_{real}}\right) - \sin\left(\frac{2 \cdot \pi}{N_{real}}\right) \sin\left(\frac{2 \cdot \pi \cdot (p-1)}{N_{real}}\right)$$

$$I_{p} = \sin\left(\frac{2 \cdot \pi \cdot p}{N_{real}}\right) = \sin\left(\frac{2 \cdot \pi}{N_{real}} + \frac{2 \cdot \pi \cdot (p-1)}{N_{real}}\right) =$$

$$15 \quad \sin\left(\frac{2 \cdot \pi}{N_{real}}\right) \cos\left(\frac{2 \cdot \pi \cdot (p-1)}{N_{real}}\right) + \cos\left(\frac{2 \cdot \pi}{N_{real}}\right) \sin\left(\frac{2 \cdot \pi \cdot (p-1)}{N_{real}}\right)$$

$$(25)$$

This gives a recursion similar to that in equations (16), (17), (18) and (19) above. This is further illustrated in equations (26) and (27) below.

$$20 R_0 = \cos\left(\frac{2 \cdot \pi}{N_{real}}\right) (26)$$

$$I_0 = \sin\left(\frac{2 \cdot \pi}{N_{real}}\right) \tag{27}$$

where

$N_{real}$  = real FFT size

5 Equations (18) and (19) may be modified slightly and then used with the above initializers to compute the new weights.

$$R_{m} = R_{0} \cdot R_{m-1} - I_{0} \cdot I_{m-1} \tag{28}$$

$$I_{m} = I_{0} \cdot R_{m-1} + R_{0} \cdot I_{m-1} \tag{29}$$

10

15

20

where m = 1, 2,

$$\cdots \frac{N_{real}}{2}$$

Another embodiment of the present invention may be directed to determining an optimal G.SHDSL data rate using sub-band capacity. In the G.SHDSL standard, provisions may be made for rate negotiation to take place between two communicating modems after a line probe (LP) session. During LP, a first modem transmits a signal while a second modem samples a received signal to determine effects of line conditions on a communications channel. For example, performing a signal-to-noise-ratio (SNR) calculation in the time-domain gives an indication of an amount of signal power above that of the background noise. A problem may arise when this SNR value is used to compute the capacity of the channel since the capacity theorem, as described below, makes an assumption that the noise is additive white and gaussian (AWGN). When residue echo and NEXT noise are taken into consideration, the noise is no longer AWGN. In fact, the noise may not have been true AWGN.

The present invention provides an approach to rate negotiation that implements a geometric frequency domain approximation of channel capacity. The capacity for a plurality of M frequency sub-bands may be computed to find an overall capacity for a rate of interest (ROI). The sub-bands may be any segment of a total N frequency bands found with a discrete Fourier transform (DFT) or other method of spectrum estimation, such as an autoregressive (AR), moving average

(MA), autoregressive-moving average (ARMA), quadrature mirror filter bank (QMF), and other methods. This geometric capacity may allow for a more accurate capacity calculation if the sub-band width is sufficiently small such that the noise within that band is approximately AWGN.

As shown in FIG. 1a, during a line probe session, the G.SHDSL modem may determine which rates the modem may support given the line conditions. FIG. 1a illustrates the line probe (LP) session for G.HS (e.g., 114, 116) between STUR 110 and STUC 112, which lasts a maximum of approximately 10 seconds, for example.

During the transmission of each probe signal, represented by Prx (e.g., Pr1, Pr2, Pr3) and Pcx (e.g., Pc1, Pc2) in FIG. 1a, a modem transmitting the probe may train associated automatic gain control (AGC) and echo canceller (EC). The modem may then measure the residual echo signal and use this measurement as an estimate of the noise spectrum. In addition, the modem may measure a silence power spectrum during the segments where no signals are transmitted and use this measurement as a noise spectrum estimate. The modem receiving the probe signal may measure a received signal and noise spectrum. One modem may transmit a probe signal at any given time.

When the modems are not measuring received signals, the modems may calculate sub-band capacity for each rate using the methods described.

If the SNR is calculated in the time domain, a method to compute the capacity may include measuring the silence power (noise),  $P_{\text{noise}}$ , and then the received power (signal + noise),  $P_{\text{signal+noise}}$ , and finding the capacity, C, using the equation below.

25

20

5

10

15

$$C = Blog_2 \left( 1 + \frac{P_{signal}}{P_{noise} 10^{\frac{(\Gamma - G + \gamma + \delta)}{10}}} \right) = Blog_2 \left( 1 + \frac{SNR}{10^{\frac{(\Gamma - G + \gamma + \delta)}{10}}} \right) \frac{bits}{\sec ond}$$

(30)

where  $\Gamma$  represents a gap from a theoretical channel capacity for PAM signals, in dB; G represents a coding gain of a Trellis decoder in dB; B represents a transition

5

10

15

20

25

30

bandwidth;  $\gamma$  represents a required margin in dB (e.g., G.SHDSL Annex B margin is approximately 6 dB); and  $\delta$  represents an implementation loss in dB.