## (12) 发明专利

(10) 授权公告号 CN 108363669 B

(45) 授权公告日 2021. 10. 22

(21) 申请号 201810062812.7

(51) Int.Cl.

(22) 申请日 2018.01.23

G06F 13/16 (2006.01)

(65) 同一申请的已公布的文献号

G06F 13/28 (2006.01)

申请公布号 CN 108363669 A

(13) 申請公布日 2018.08.03

### 3) 对比文件

### (30) 优先权数据

US 2015101078 A1, 2015-06-25

2017-012541 2017-01-36 1B

US 2015181078 A1, 2015.06.25

### (72) 专利权人/功能性条款

审查员 彭莉

地址 日本国东京都大田

2

(72) 发明人 今田淳一 新藤泰士

（六）有利代理机构、北京检察院知识库

公司 11203

权利要求书2页 说明书14页 附图20页

(54) 发明名称

# 存储器访问系统、其控制方法、存储介质及图像形成装置

## (57) 摘要

本发明涉及存储器访问系统、其控制方法、存储介质及图像形成装置。为了实现本发明，该存储器访问系统监视表示在存储器与多个主设备之间使用的总的存储带宽的使用存储带宽，并且确定使用存储带宽是否大于等于第一阈值。基于上述确定结果，该存储器访问系统还限制多个主设备当中的低优先级的主设备对存储器的访问。

1. 一种存储器访问系统,所述存储器访问系统包括:

存储器;

访问存储器的多个主设备;

处理器,其监视多个存储带宽的数据量,其包括每个预定时间在多个主设备中包括的第一主设备和存储器之间使用的数据量、每个预定时间在多个主设备中包括的第二主设备和存储器之间使用的数据量,并且计算所监视的多个存储带宽的数据总量;以及

存储器控制器,其在满足关于所计算的由处理器监视的所述多个存储带宽的数据总量的预定条件的情况下,减少所述多个被监视的主设备当中的比第一主设备的优先级低的第二主设备对存储器的访问,而不减少第一主设备对存储器的访问。

2. 根据权利要求1所述的存储器访问系统,其中,所述存储器控制器通过使比第一主设备的优先级低的第二主设备停止访问存储器来减少访问。

3. 根据权利要求1所述的存储器访问系统,其中,所述存储器控制器通过使比第一主设备的优先级低的第二主设备缩短在比第一主设备的优先级低的第二主设备访问存储器时的突发长度来减少访问。

4. 根据权利要求1所述的存储器访问系统,其中,所述比第一主设备的优先级低的第二主设备通过以非实时方式访问存储器来执行数据传输,并且

高优先级的第一主设备通过以实时方式访问存储器来执行数据传输。

5. 根据权利要求1所述的存储器访问系统,其中,存储器控制器是直接存储器访问控制器。

6. 一种存储器访问系统,所述存储器访问系统包括:

存储器;

访问存储器的多个主设备;

处理器,其监视多个存储带宽的数据量,包括每个预定时间在多个主设备中包括的第一主设备和存储器之间使用的数据量、每个预定时间在多个主设备中包括的第二主设备和存储器之间使用的数据量,并且计算所监视的多个存储带宽的数据总量,其中,多个第一主设备具有比多个第二主设备更高的优先级;以及

存储器控制器,其在满足关于所计算的由处理器监视的所述多个存储带宽的数据总量的预定条件的情况下,减少第二主设备对存储器的访问,而不减少第一主设备对存储器的访问,以及在不满足所述预定条件的情况下,不减少第一主设备和第二主设备对存储器的访问。

7. 一种存储器访问系统的控制方法,所述存储器访问系统包括存储器和访问存储器的多个主设备,所述控制方法包括执行以下步骤:

监视多个存储带宽的数据量,其包括每个预定时间在多个主设备中包括的第一主设备和存储器之间使用的数据量,还包括每个预定时间在多个主设备中包括的第二主设备和存储器之间使用的数据量;

计算所监视的多个存储带宽的数据总量;以及

在满足关于所计算的被监视的所述多个存储带宽的数据总量的预定条件的情况下,减少所述多个被监视的主设备当中的比第一主设备的优先级低的第二主设备对存储器的访问,而不减少第一主设备对存储器的访问。

8. 一种计算机可读存储介质,其存储有使计算机执行存储器访问系统的控制方法中的各步骤的计算机程序,所述存储器访问系统包括存储器和访问存储器的多个主设备,

其中,所述控制方法包括执行以下步骤:

监视多个存储带宽的数据量,其包括每个预定时间在多个主设备中包括的第一主设备和存储器之间使用的数据量,还包括每个预定时间在多个主设备中包括的第二主设备和存储器之间使用的数据量;

计算所监视的多个存储带宽的数据总量;以及

在满足关于所计算的被监视的所述多个存储带宽的数据总量的预定条件的情况下,减少所述多个被监视的主设备当中的比第一主设备的优先级低的第二主设备对存储器的访问,而不减少第一主设备对存储器的访问。

9. 一种图像形成装置,所述图像形成装置包括:

在权利要求1至6中的任一项中限定的存储器访问系统;

执行图像处理的图像处理单元;

从原稿读取图像的扫描器;以及

在记录介质上形成图像的打印机。

10. 根据权利要求9所述的图像形成装置,其中,与图像处理单元有关的处理通过以非实时的方式访问存储器来执行数据传输,并且

与扫描器和打印机有关的处理通过以实时方式访问存储器来执行数据传输。

## 存储器访问系统、其控制方法、存储介质及图像形成装置

### 技术领域

[0001] 本发明涉及存储器访问系统、其控制方法、计算机可读存储介质以及图像形成装置。

### 背景技术

[0002] 各自包括存储器访问系统的现有图像形成装置，包括具有诸如扫描器功能、打印机功能、复印功能、网络功能和FAX发送/接收功能等各种功能的数字多功能外围设备。数字多功能外围设备中的功能操作通常由被称为控制器的图像输入/输出控制单元来控制。

[0003] 在这样的控制器中，为了实现成本降低，将CPU和实现上述功能的多个功能处理单元集成在一个芯片中。CPU的工作存储器和用于进行图像数据传输、实现上述功能的主存储器被进一步集成，极大地增加了对主存储器的数据访问量。扫描性能和打印性能的速度提高也是增加主存储器的数据访问量的一个因素。特别是，诸如扫描和打印等的处理需要如下的实时特性，一旦开始操作，至少在直到处理中的页面的输入/输出完成之前不能停止操作。也就是说，期望的是：在对于需要实时处理的图像处理一直保证对主存储器的访问的恒定传输带宽的同时，控制器也尽可能并行地操作非实时处理功能。换句话说，控制器需要进行控制，以不引起对于需要实时处理的图像处理不能保证对主存储器的访问的传输带宽的情形。因此，需要使用即使所有功能都被操作也能够充分保证存储器传输性能的、具有高频/多位宽度的存储器，以确保足够的存储器传输性能。

[0004] 然而，使用高频存储器导致存储器的成本和电力消耗增加，并且使用具有多位宽度的存储器通过增加芯片的引脚数量导致芯片单位价格的成本增加。为了解决这个问题，有一项发明，该发明监测主存储器与实时处理功能单元或非实时处理功能单元之间的传输带宽，并控制存储器访问，以确保实时处理功能的主存储器的传输带宽，同时限制存储器具有高频和多位。

[0005] 例如，日本特开2014-160341号公报提出了一种控制技术以在预设的几乎超过传输带宽的情况下，不接受来自非实时处理功能单元的访问。这使得可以通过控制来抑制带宽，以在所有实时处理单元操作的状态下不接受非实时处理单元的传输，并且增加主存储器的使用存储带宽(use-memory-bandwidth)，并保证实时处理的传输带宽。

[0006] 此外，日本特开2009-75942号公报提出了如下的一种技术，使实时处理功能单元和非实时处理功能单元中的各个的数据传输单位缩短，并且释放根据传输带宽从各个处理功能单元用于访问的缩短的各个数据传输单位的总线使用权。这使得即使同时发生实时处理单元的传输操作和非实时处理单元的传输操作，也可以保证实时处理的传输带宽。

[0007] 然而，上述现有技术存在以下问题。例如，在上述相关技术中，即使在主存储器未被集中访问的状态下，如果非实时处理单元的传输带宽几乎超过给定阈值，则传输带宽也被抑制。此外，即使在主存储器未被集中访问的状态下，也释放短数据传输单位的总线使用权。在这些情况下，可能无法完全使用主存储器的存储器传输性能。

[0008] 由SDRAM等代表的存储器通过只指定一个地址连续地传输后续地址的数据的突发

传输 (burst transfer) 来实现到存储器的高速数据传输,使得可以通过延长突发长度 (burst length) 来提高存储器传输性能。然而,如果延长访问主存储器的所有处理单元的突发长度,则传输到主存储器的数据量和各个处理单元占据主存储器的时间段增加。

## 发明内容

[0009] 本发明的一个方面使得能够实现一种控制机制,以在监视存储器所使用的使用存储带宽并利用存储器的传输性能的同时,确保实时处理单元所需的带宽。

[0010] 本发明的一方面提供了一种存储器访问系统,其包括:存储器;访问存储器的多个主设备;处理器,其监视表示在存储器与多个主设备之间使用的总的存储器带宽的使用存储带宽,并且确定所监视的使用存储带宽是否不小于第一阈值;以及存储器控制器,其在处理器确定使用存储带宽不小于第一阈值的情况下限制多个主设备当中的具有低优先级的主设备对存储器的访问。

[0011] 本发明的另一方面提供了一种存储器访问系统,其包括:存储器;访问存储器的多个主设备;处理器,其监视表示在存储器与多个主设备之间使用的总的存储器带宽的使用存储带宽并且确定监视的使用存储带宽是否不小于第一阈值;以及存储器控制器,其确定处理器监视的使用存储带宽是否不小于第一阈值,并且在确定使用存储带宽不小于所述第一阈值的情况下,限制所述多个主设备当中的低优先级的主设备对存储器的访问。

[0012] 本发明的又一方面提供了一种存储器访问系统的控制方法,该存储器访问系统包括存储器和访问存储器的多个主设备,该控制方法包括执行以下步骤:监视表示在存储器与所述多个主设备之间使用的总的存储带宽的使用存储带宽;确定在监视步骤中监视的使用存储带宽是否不小于第一阈值;以及在确定步骤中确定使用存储带宽不小于第一阈值的情况下,进行限制所述多个主设备当中的低优先级的主设备对存储器的访问的存储器访问控制。

[0013] 本发明的又一方面提供了一种计算机可读存储介质,其存储有使计算机执行存储器访问系统的控制方法中的各步骤的计算机程序,所述存储器访问系统包括存储器和访问存储器的多个主设备,其中,所述控制方法包括执行以下步骤:监视表示在存储器与所述多个主设备之间使用的总的存储带宽的使用存储带宽;确定在监视步骤中监视的使用存储带宽是否不小于第一阈值;以及在确定步骤中确定使用存储带宽不小于第一阈值的情况下,进行限制所述多个主设备当中的低优先级的主设备对存储器的访问的存储器访问控制。

[0014] 根据下面(参照附图)对示例性实施例的描述,本发明的其他特征将变得清楚。

## 附图说明

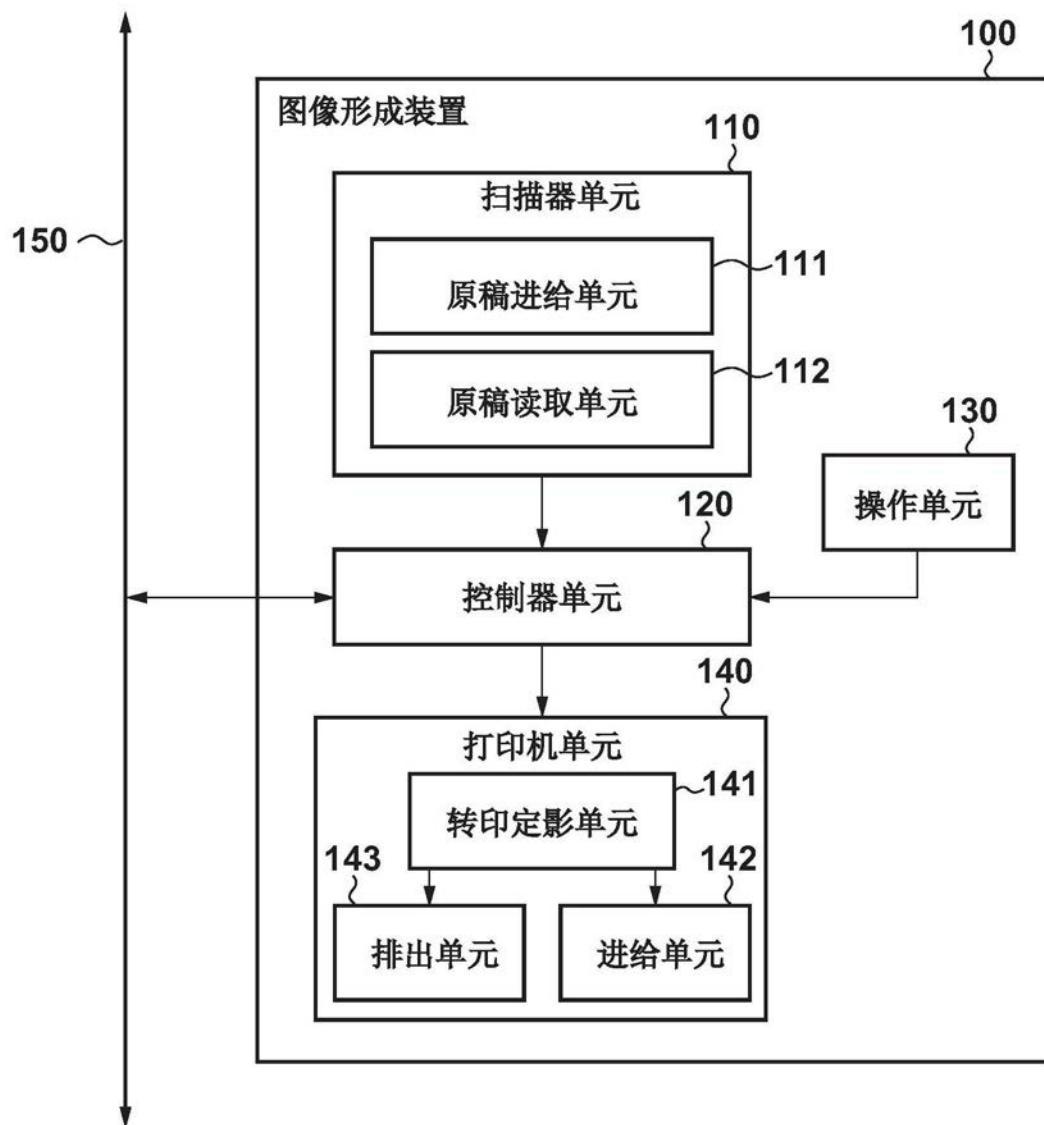

[0015] 图1是示出根据实施例的图像形成装置的框图;

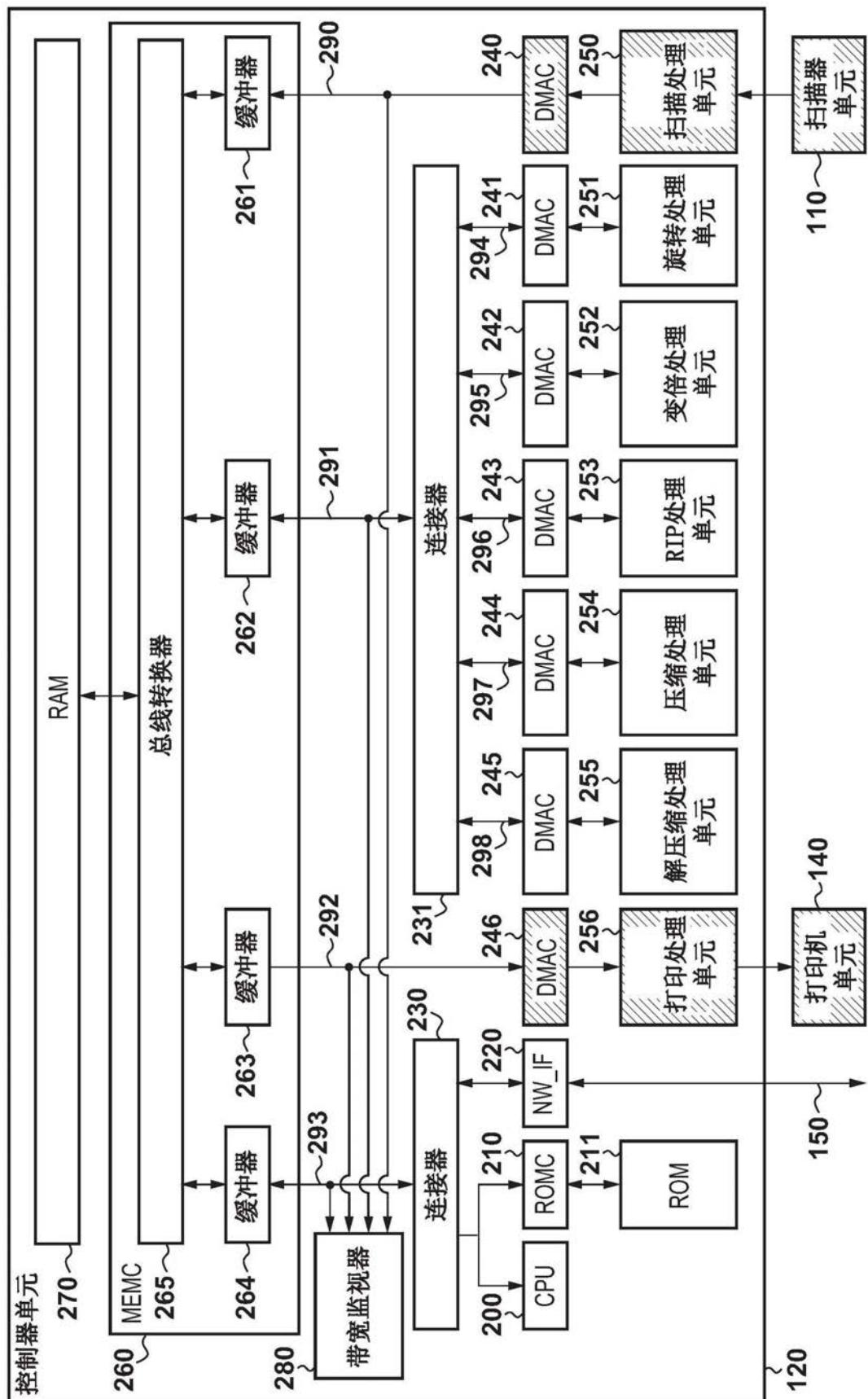

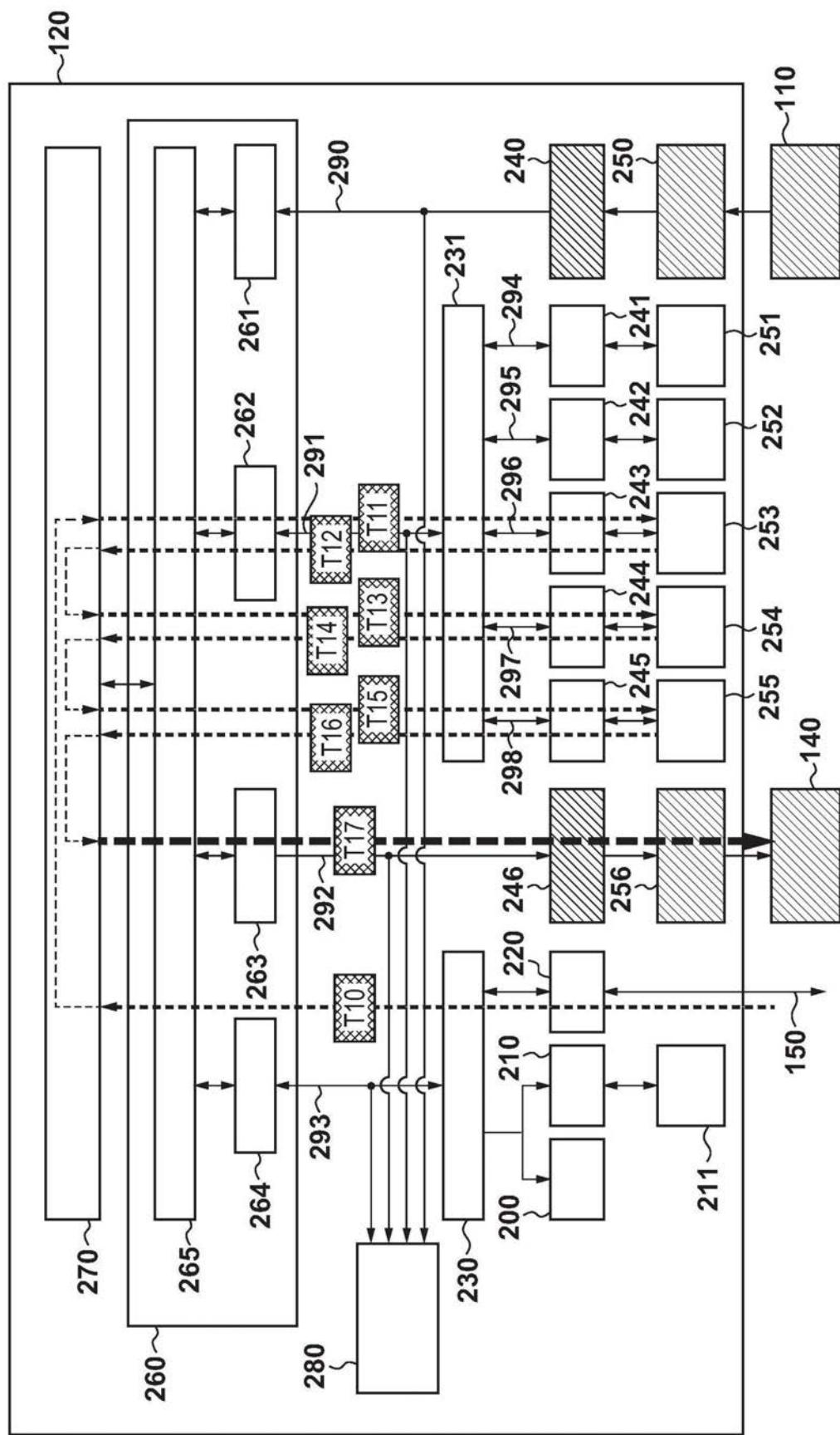

[0016] 图2是示出根据实施例的控制器单元的框图;

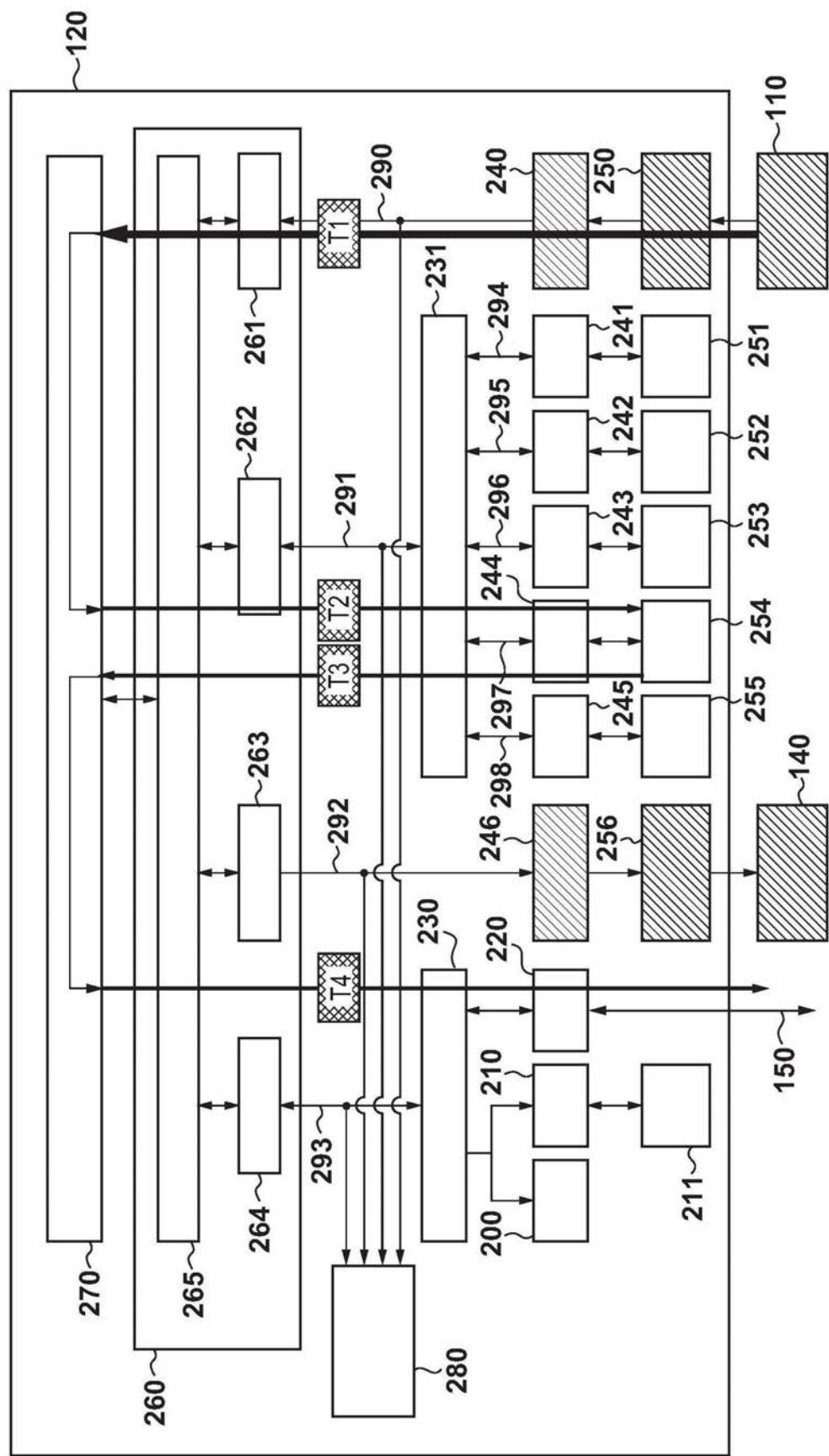

[0017] 图3A至图3E示出了显示根据实施例的控制器单元的图像路径控制的图;

[0018] 图4A至图4C示出了显示根据实施例的带宽示例的表;

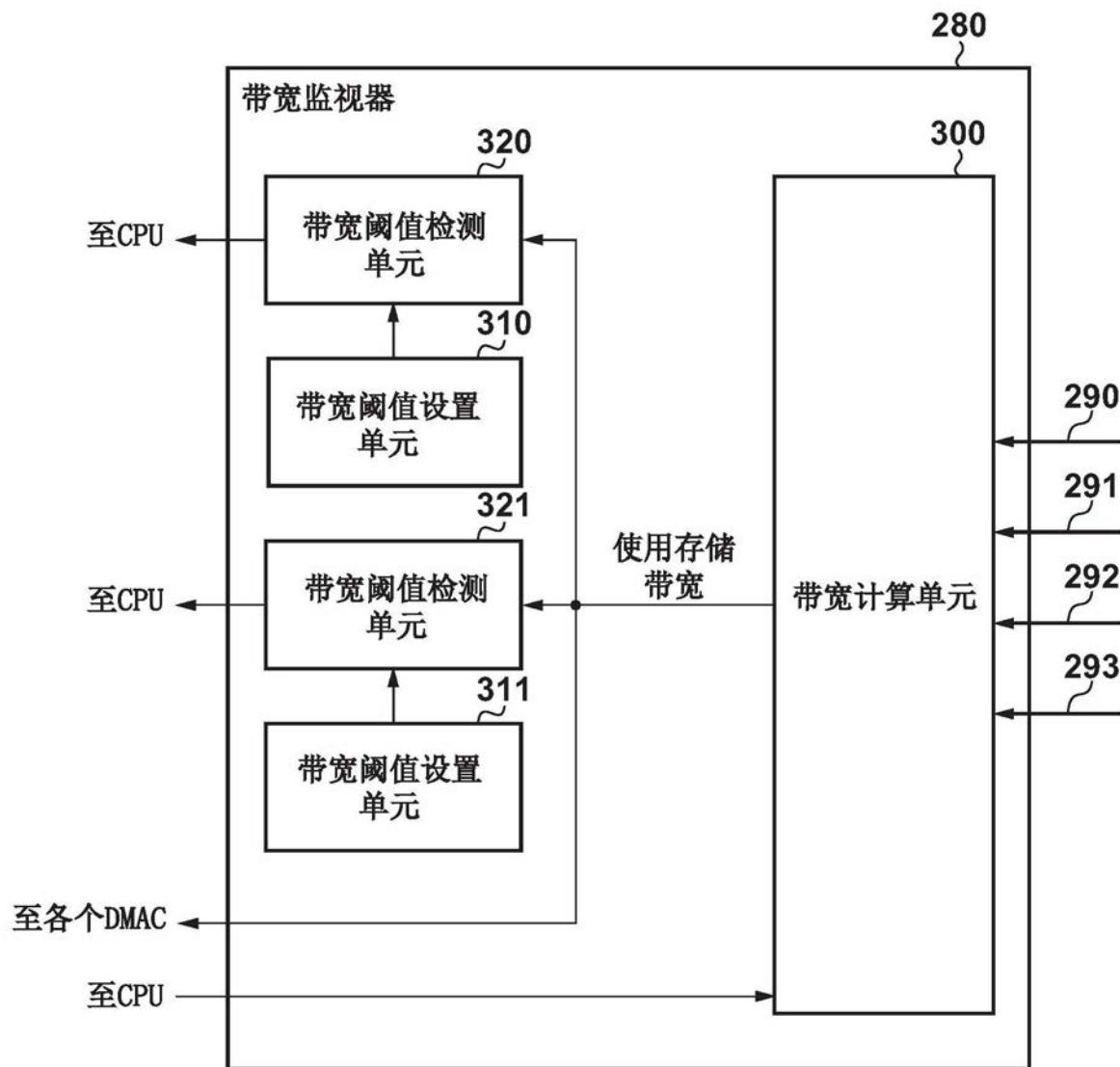

[0019] 图5是示出根据实施例的带宽监视器的框图;

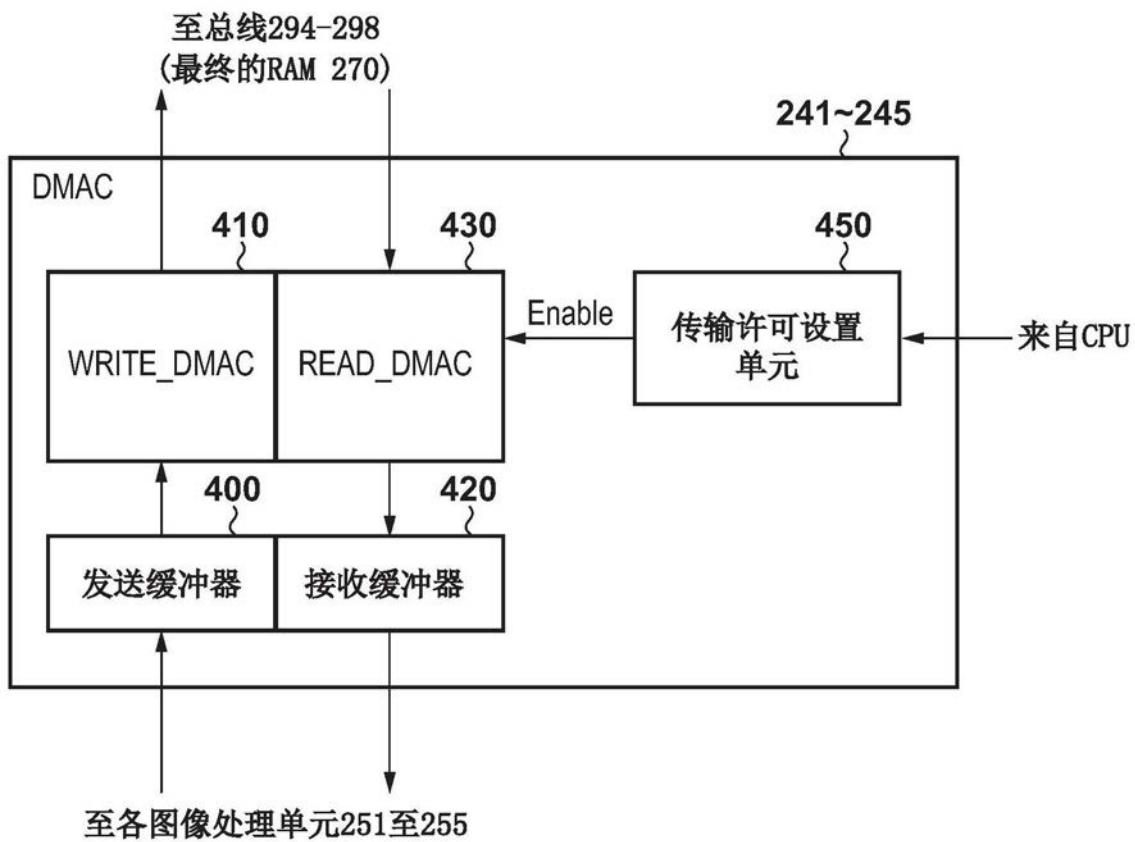

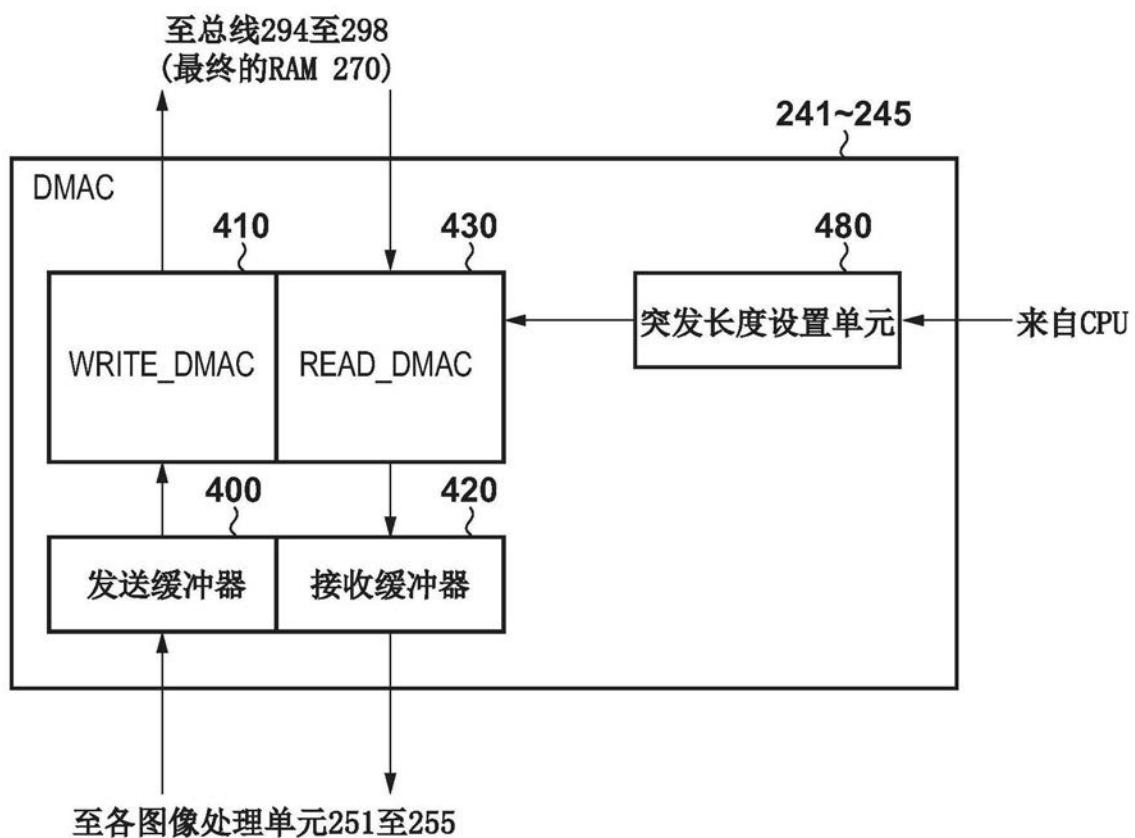

[0020] 图6是示出根据实施例的DMAC的框图;

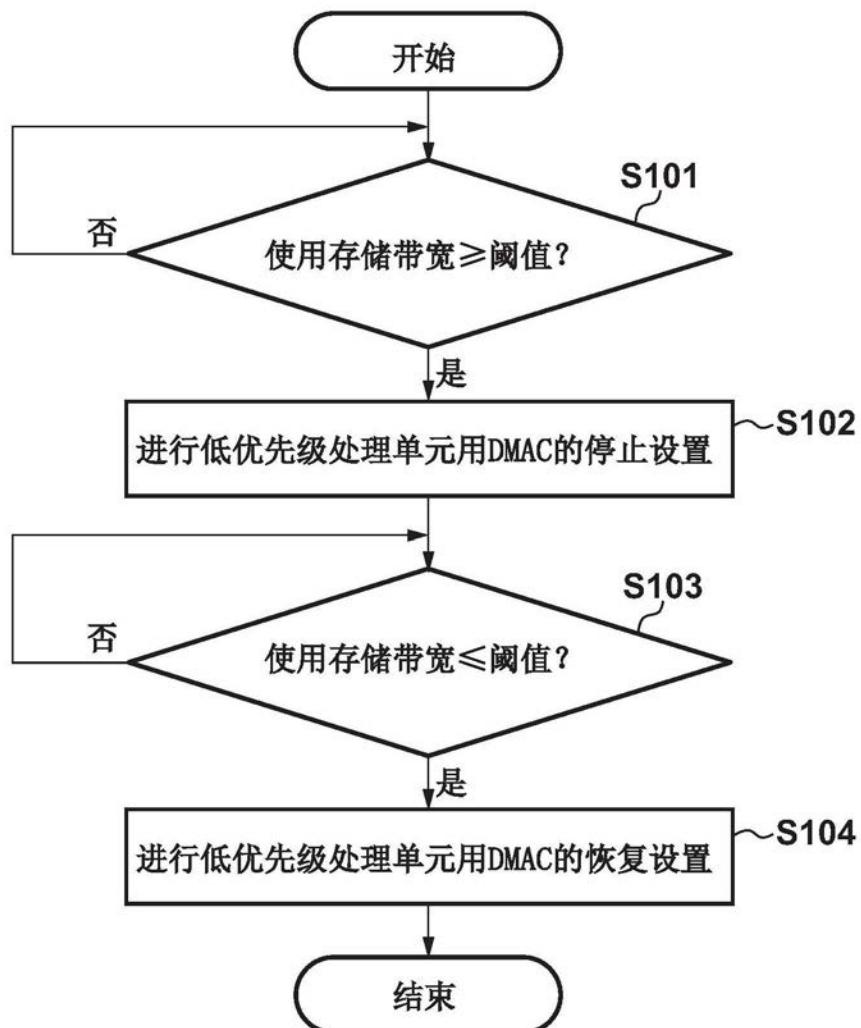

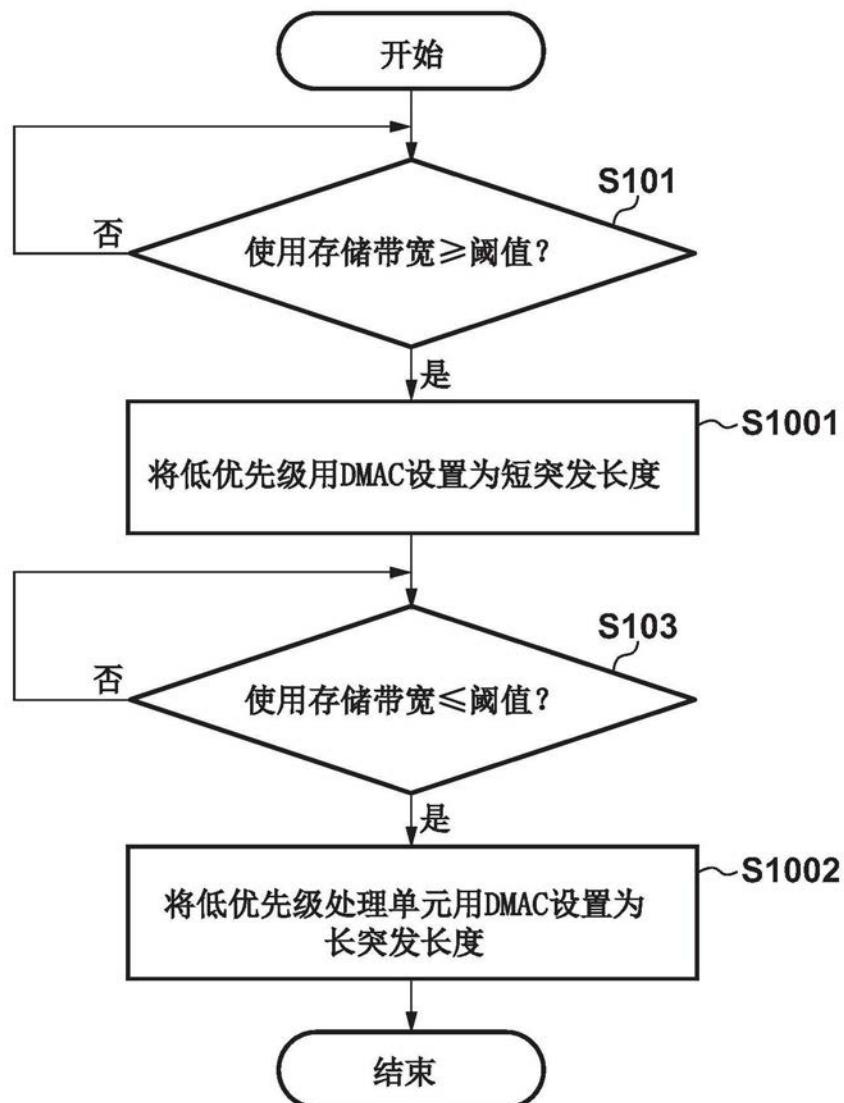

[0021] 图7是根据实施例的带宽控制的控制流程图;

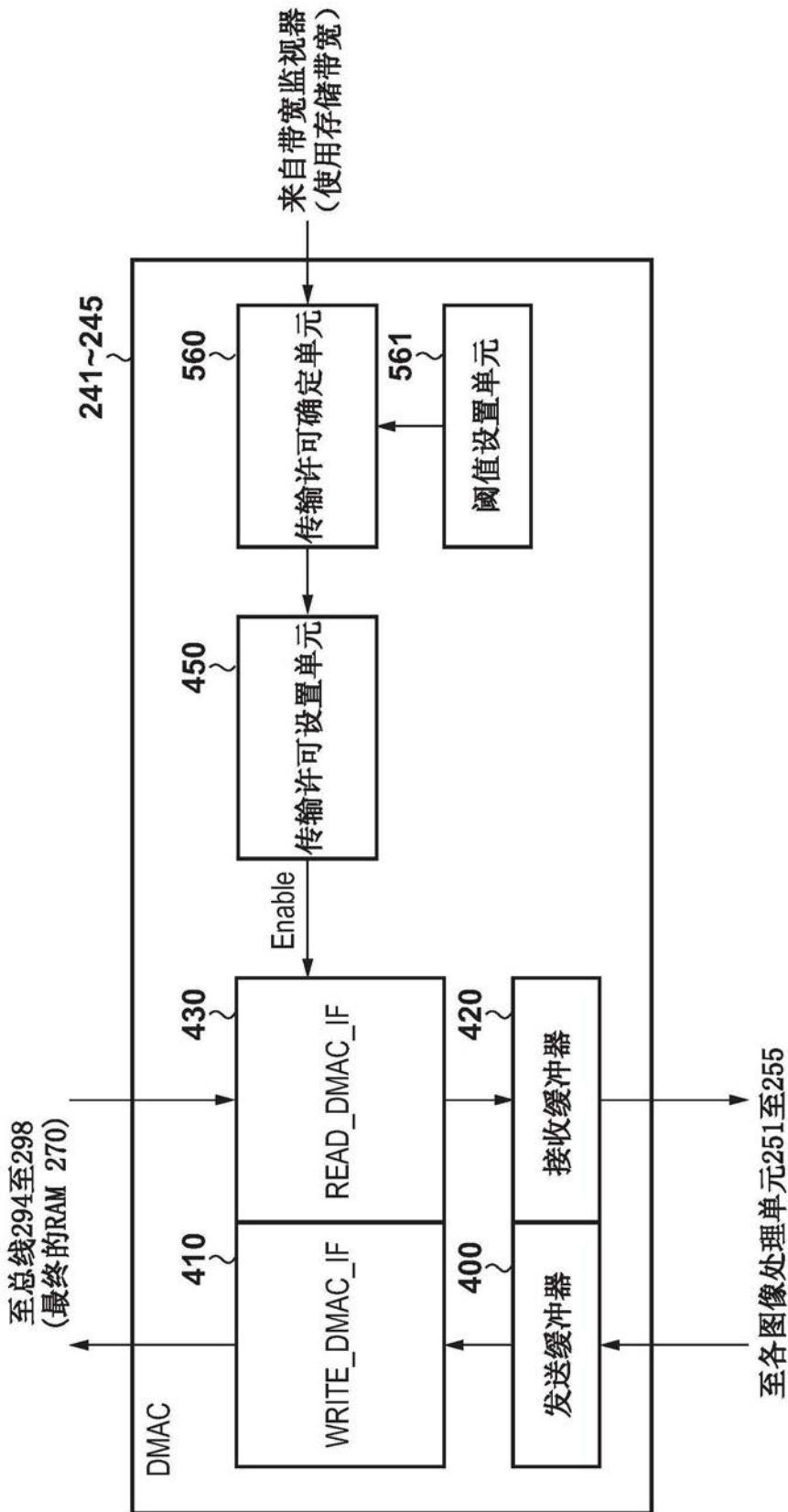

- [0022] 图8是示出根据实施例的DMAC的框图；

- [0023] 图9是示出根据实施例的DMAC的框图；

- [0024] 图10是根据本实施例的带宽控制的控制流程图；

- [0025] 图11A-1和图11A-2是根据实施例的关于RAM控制的时序图；以及

- [0026] 图11B-1和图11B-2是根据实施例的关于RAM控制的时序图。

## 具体实施方式

[0027] 现在将参照附图详细描述本发明的优选实施例。应该注意的是，除非另有具体说明，否则在这些实施例中阐述的部件的相对构造、数字表达式和数值不限制本发明的范围。

- [0028] <第一实施例>

- [0029] <图像形成装置的构造>

[0030] 下面将描述本发明的第一实施例。首先，将参照图1描述根据本实施例的图像形成装置100的构造的示例。注意，在本实施例中，通过将图像形成装置作为存储器访问系统的示例给出描述。注意，本发明不限于图像形成装置。也就是说，本发明可应用于包括将在下面描述的特征在于存储器访问系统的任何装置。

[0031] 图像形成装置100包括扫描器单元110、控制器单元120、操作单元130和打印机单元140。扫描器单元110光学读取原稿图像并将原稿图像转换为图像数据。此外，扫描器单元110包括具有读取原稿的功能的原稿读取单元112和具有输送原稿片材的功能的原稿进给单元111。打印机单元140输送记录纸，将图像数据打印在纸张上作为可见图像，并将打印的图像排出到装置外部。打印机单元140包括：包括多种类型的记录纸盒的进给单元142，具有将图像数据转印并定影到记录纸上的功能的转印定影单元141，以及具有将经历了打印的记录纸分类并装订然后将记录纸输出到装置外部的功能的排出单元143。

[0032] 控制器单元120电连接到扫描器单元110和打印机单元140，并进一步连接到诸如LAN、ISDN、因特网/内联网等的网络150。控制器单元120提供控制扫描器单元110读取原稿图像数据并控制打印机单元140将图像数据输出到记录片材的复印功能。

[0033] 控制器单元120还提供将从扫描器单元110读取的图像数据转换成代码数据，并经由网络150将其发送到主机计算机(未示出)的扫描器功能。控制器单元120还提供将经由网络150从主机计算机接收的代码数据转换成图像数据并将其输出到打印机单元140的打印机功能。控制器单元120还提供从ISDN接收数据以进行打印的传真接收功能和将扫描的数据发送到ISDN的传真发送功能。扫描、打印和传真发送/接收的这些处理将被称为作业，并且图像形成装置100根据来自操作者的指令来控制/处理这些作业。操作单元130连接到由液晶触摸面板形成的控制器单元120，并且提供用于操作图像形成装置100的用户接口(user interface)。

- [0034] <控制器单元的构造>

[0035] 接下来将参照图2描述根据本实施例的控制器单元120的构造的示例。将详细描述控制器单元120的各内部块。

[0036] 控制器单元120包括CPU 200、ROMC 210、ROM 211、网络IF (NW\_IF) 220、连接器(interconnect) 230和231、DMAC 240至246、扫描处理单元250、旋转处理单元251、变倍处理单元252、RIP处理单元253、压缩处理单元254、解压缩处理单元255、打印处理单元256、MEMC

260、RAM 270和带宽监视器280。CPU(中央处理单元)200是控制整个系统的处理器。

[0037] CPU 200根据OS或加载到RAM 270中的控制程序来总体控制与打印处理的作业和扫描处理的作业有关的处理。ROMC 210是用于对存储系统的引导程序的ROM 211进行访问的控制模块(ROM控制器)。当图像形成装置100被开启时,CPU 200经由ROM控制器210访问ROM 211并引导系统。RAM 270是用于操作CPU 200的系统工作存储器,也是用于临时存储图像数据的图像存储器。在本实施例中,作为示例,RAM 270由SDRAM形成。

[0038] MEMC 260是用于访问存储系统的控制程序和图像数据的RAM 270的控制模块(存储器控制器)。MEMC 260包括用于设置或控制RAM 270的寄存器,并且该寄存器可以从CPU 200访问。稍后将描述MEMC 260的详细构造。

[0039] 网络IF 220是连接到网络150并将信息(例如图像数据)输入到外部主机计算机/从外部主机计算机输出的处理单元。连接器230和231将CPU 200和各处理单元与MEMC 260连接。

[0040] DMAC 240至246中的各个用作存储器访问控制单元,并且是充当经由MEMC 260访问RAM 270的存储器访问主设备的DMA(直接存储器访问)控制器。DMAC 240至246进行各处理单元250至256与RAM 270之间的稍后将描述的数据传输。DMAC 240至246中的各个由CPU 200控制,并且具有控制针对特定存储器地址的读取/写入操作和进行DMA传输的定时的功能。DMAC 240至246中的各个具有控制功能,以不通过来自CPU 200的设置向存储器发出图像传输请求,稍后将在本实施例中描述其细节。

[0041] CPU 200还总体控制将在下面描述的扫描处理单元250、旋转处理单元251、变倍处理单元252、RIP处理单元253、压缩处理单元254、解压缩处理单元255和打印处理单元256。在各个处理单元的描述中,图像数据是指未压缩的图像,并且压缩的图像数据是指通过一些压缩方法压缩的图像。

[0042] 根据由CPU 200设置的设置,扫描处理单元250对从扫描器单元110输入的图像数据进行诸如阴影校正处理、MTF校正处理、输入伽马校正或滤波处理等的图像处理,并将图像数据输出到DMAC 240。根据由CPU 200设置的设置,旋转处理单元251对从DMAC 241输入的图像数据进行90°、180°或者270°的旋转处理,并将图像数据输出到DMAC 241。根据由CPU 200设置的设置,变倍处理单元252将从DMAC 242输入的图像数据变倍诸如1/2或1/4等的任意倍率,并将图像数据输出到DMAC 242。根据由CPU 200设置的设置,RIP处理单元253对从DMAC 243输入的PDL图像数据进行渲染处理,并将图像数据输出到DMAC 243。

[0043] 根据由CPU 200设置的设置,压缩处理单元254对从DMAC 244输入的图像数据进行诸如JPEG或JBIG等的图像压缩处理,并将压缩的图像数据输出到DMAC 244。根据由CPU 200设置的设置,解压缩处理单元255对从DMAC 245输入的JPEG或JBIG压缩的图像数据进行解压缩处理,并将解压缩的图像数据输出到DMAC 245。根据由CPU 200设置的设置,打印处理单元256对从DMAC 246输入的图像数据进行诸如颜色空间转换处理、滤波处理或半色调处理等的图像处理,并将图像数据输出到打印机单元140。

[0044] 在到目前为止描述的MEMC、DMAC与连接器之间的总线290到298由作为标准总线的AXI\_BUS等连接。

[0045] 接下来将描述MEMC 260的内部构造。缓冲器261到264暂时地缓冲发送到各DMAC和连接器的数据/从各DMAC和连接器接收到的数据。缓冲器261至264中的各个至少具有能够

由总线290至293进行一次突发传输的缓冲器大小。当总线290至293的操作频率与总线转换器的操作频率不同时,缓冲器261至264中的各个还充当异步缓冲器。总线转换器265具有以循环方式仲裁缓冲器261至264的访问权的仲裁功能,并且进行到用于访问RAM 270的协议的转换。

[0046] 带宽监视器280监视总线290至293的传输数据量,并计算传输数据的总带宽。总带宽是指用于RAM 270的使用存储带宽。所计算的使用存储带宽可以从CPU 200中读出。可以从CPU 200设置带宽阈值,并且也可以检测使用存储带宽是否大于等于设置的阈值或者总带宽是否小于等于设置的阈值。稍后将参照图5中的带宽监视器280的详细框图来描述详情。

[0047] <图像路径和访问控制>

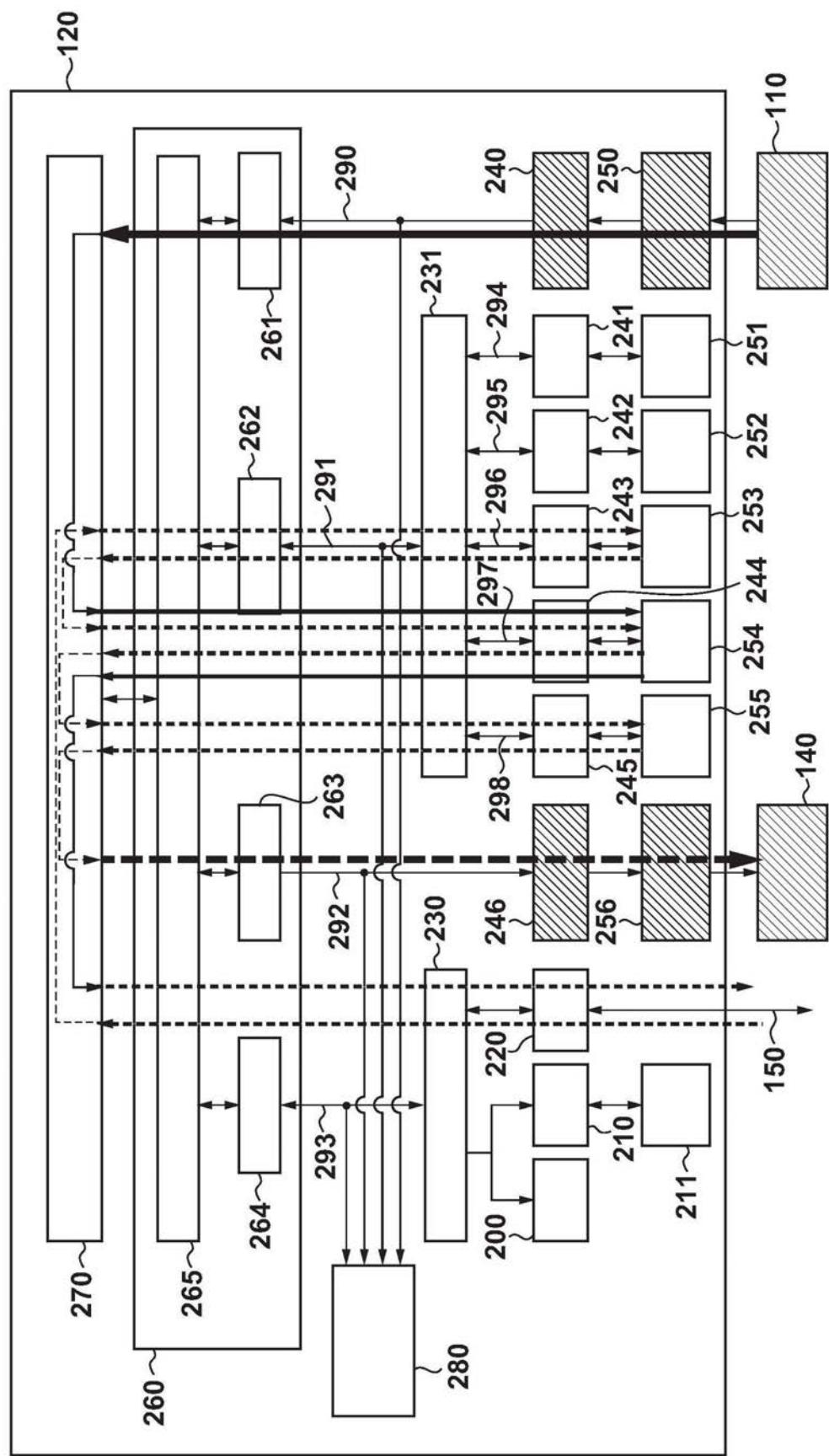

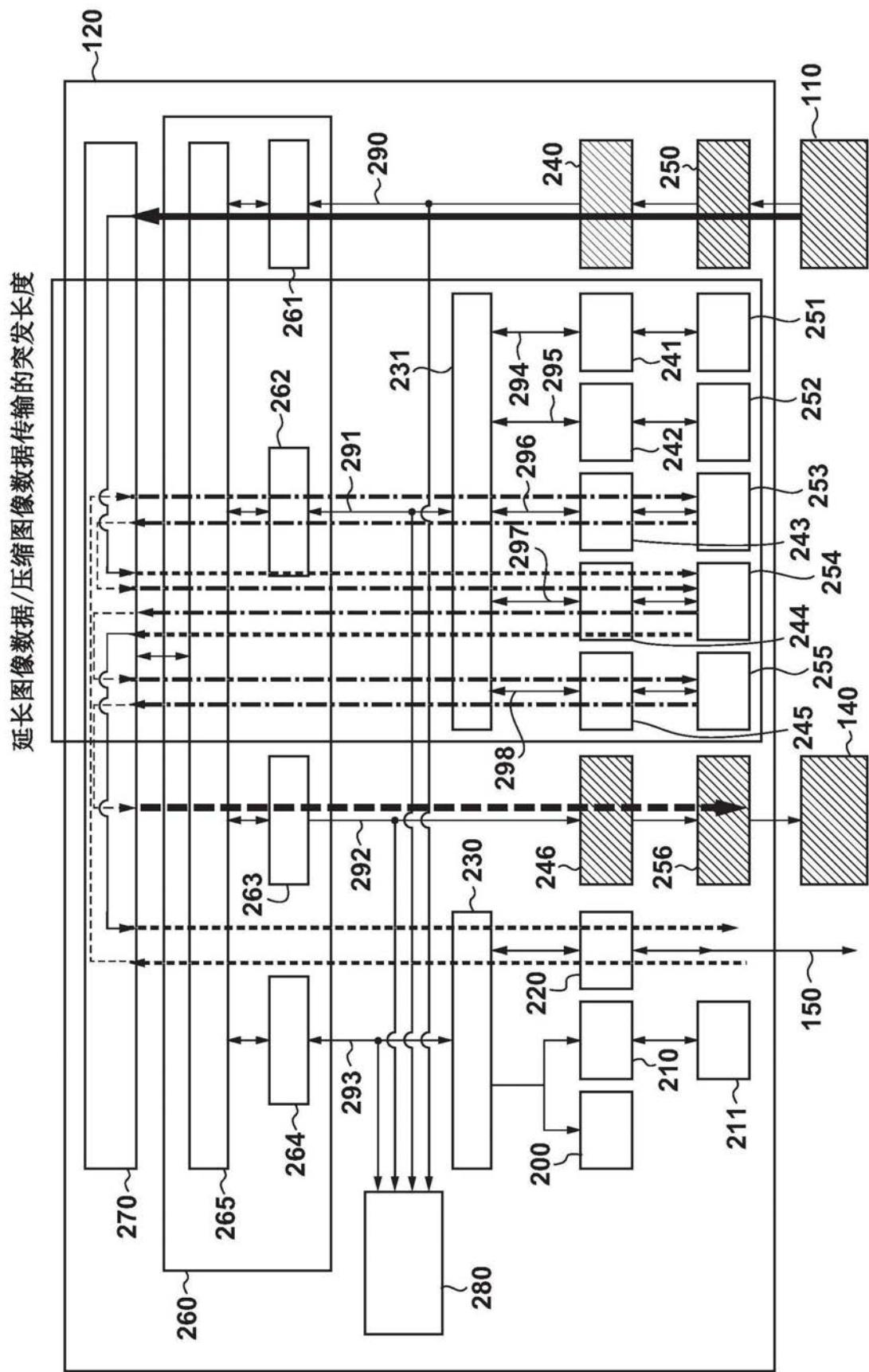

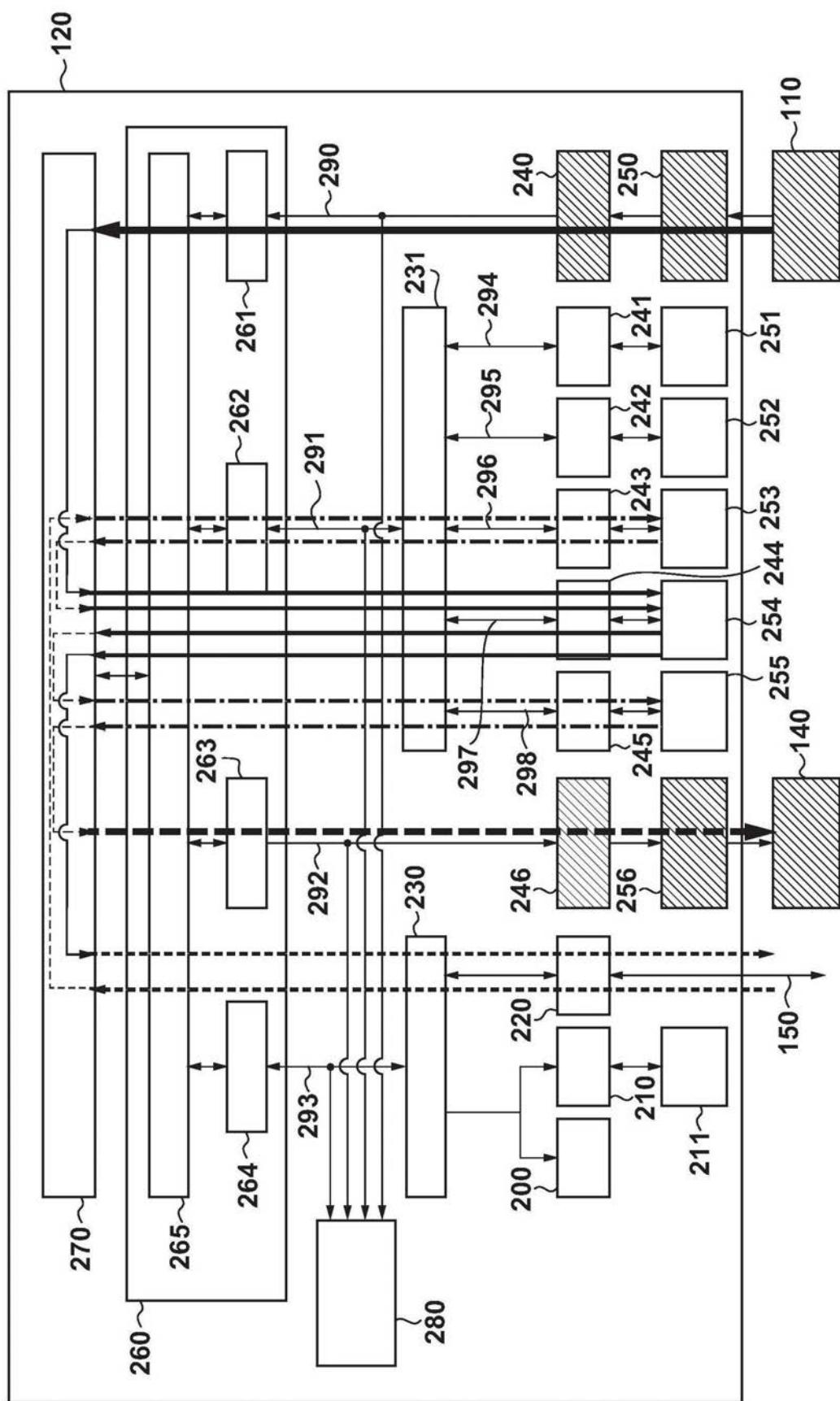

[0048] 接下来将参照图3A和图3B来描述本实施例中的图像路径以及在应用本实施例时如何抑制图像数据传输。这里,图像路径是指控制器单元120内部的图像数据流。注意,与图像数据的发送/接收和传输有关的主体是通过图3A至图3E中所示的箭头穿过的各个块。

[0049] 首先,将描述描述图3A至图3E的前提。当在各图像处理单元之间传输图像时,图像数据无一例外地经由RAM 270传输。各视图中所示的粗箭头表示需要实时处理的图像路径(以下称为实时图像路径),细箭头表示需要非实时处理的图像路径(以下称为非实时图像路径)。本实施例中的实时图像路径包括,开始将图像数据从扫描器单元110向RAM 270输入并将图像数据传输到RAM 270的路径,以及将存储在RAM 270中的图像数据传输到打印机单元140的路径。

[0050] 扫描器单元110读取原稿图像,并且因此一旦开始就不能中途停止读取。因此,当开始将图像数据从扫描器单元110向控制器单元120输入时,控制器单元120需要将预定量的图像数据连续传输到RAM 270而不能停止。另一方面,一旦开始打印,打印机单元140就不能中途停止打印。因此,当控制器单元120开始向打印机单元140输出图像数据时,必须一直从控制器单元120向RAM 270读出预定量的图像数据并将其输出到打印机单元140。如上所述,需要一直连续进行按预定时间决定的图像数据传输的路径充当实时图像路径。

[0051] 现在将参照图3A至图3E描述本实施例中的图像路径的示例以及在本实施例中的到RAM 270的数据传输访问争夺时的图像传输控制。更具体地,将描述当在数据传输访问争夺时存储器访问拥塞的时候,以及当RAM 270的使用存储带宽几乎超过RAM 270的实质传输带宽的时候,抑制图像数据传输的方法。

[0052] 图3A是执行SEND(发送)作业时的图像路径的示例,并且该路径由实箭头表示。SEND作业是压缩从扫描器单元110读取的图像数据并将其传输到连接到网络150上的PC或服务器(未示出)的作业。在T1,从扫描器单元110读取的图像数据被假脱机到RAM 270。随后,在T1假脱机的图像数据从RAM 270被传输到压缩处理单元254,并在T2经历诸如JPEG等的图像压缩,并且在T3,压缩的图像数据从压缩处理单元254被假脱机到RAM 270。随后,在T4,在T3假脱机的压缩的图像数据从RAM 270经由网络IF 220传输到网络上。

[0053] 图3B是执行PDL\_PRINT(PDL打印)作业时的图像路径的示例,并且该图像路径由虚线箭头表示。PDL\_PRINT作业是从连接到网络150上的PC(未示出)接收用于进行打印处理的打印数据并将该数据输出到打印机单元140以进行打印的作业。在T10,PDL数据经由网络IF 220从网络被接收并被假脱机到RAM 270。随后,在T10假脱机的PDL数据从RAM 270被传输到

RIP处理单元253,并在T11经历渲染处理,并且在T12,图像数据从RIP处理单元253被假脱机到RAM 270。

[0054] 然后,在T12假脱机的图像数据从RAM 270被传输到压缩处理单元254并在T13经历诸如JBIG等的图像压缩,在T14,压缩的图像数据从压缩处理单元254被假脱机到RAM 270。随后,在T14假脱机的压缩的图像数据从RAM 270被传输到解压缩处理单元255,并且在T15经历图像解压缩,并且在T16,解压缩的图像数据从解压缩处理单元255被假脱机到RAM 270。在T17,在T16假脱机的图像数据从RAM 270被读出并被输出到打印机单元140。

[0055] 图3C是当同时执行上述图3A和图3B所示的SEND作业和PDL\_PRINT作业时的图像路径的示例。参照图3A和图3B描述了图像路径,因此将省略其描述。当SEND作业和PDL\_PRINT作业由此彼此争夺时,理所应当的是,操作图像路径增加,到RAM 270的数据传输量,即,使用存储带宽增加。

[0056] 如果RAM 270的使用存储带宽增加并且超过RAM 270的可能传输带宽,则实时图像路径的扫描图像路径(T1)和打印图像路径(T17)不能满足所需的传输带宽。在这种情形下,控制器单元120作为系统发生故障。因此,为了避免这种情形,在本实施例中,进行控制以在RAM 270中的使用存储带宽几乎超过RAM 270的可能传输带宽的情况下,暂停非实时图像路径的数据传输,如图3D所示。更具体地,这通过使CPU 200使用带宽监视器280来控制DMAC 241至245而实现。这种控制保证控制器单元120不会作为系统发生故障。

[0057] 如图3E所示,如果RAM 270的可能传输带宽在一定程度上高,则也可以由CPU 200仅控制一些非实时图像路径以由RAM 270访问。在本实施例中,操作假设在保证实时图像路径所需的传输带宽的同时尽可能优先处理SEND作业的情况。然而,本发明不限于此,并且可以控制以根据装置的规格、设置等优先处理另一处理。

[0058] <传输带宽>

[0059] 接下来将参照图4A至图4C详细描述RAM 270的可能传输带宽以及参照图3A至图3E描述的扫描图像路径(T1)和打印图像路径(T17)所需的带宽。

[0060] 图4A示出了RAM 270的可能传输带宽(存储带宽)。其计算方法由下式给出:

[0061] 存储带宽[MB/s] = 存储器操作频率[MHz] \* 存储器总线宽度[位] \* 存储器效率[%] / 8... (1)

[0062] 其中,存储器操作频率是RAM 270的操作频率,存储器总线宽度是MEMC 260与RAM 270之间的数据传输信号的总线宽度的位数,并且存储器效率是MEMC 260与RAM 270之间的实际传输效率。传输效率由对RAM 270的访问模式而改变。

[0063] 图4B示出了扫描图像路径(图3A的T1)所需的带宽。其计算方法由下式给出:

[0064] (扫描图像路径所需的带宽) = (每页像素数 \* 每个分量的位宽 \* 分量数) \* (ipm/60) \* (1/1-除图像传输以外的比例) / 8... (2)

[0065] 其中,每页像素数是要被扫描的每页原稿的像素数量。例如,600[dpi]的A4尺寸的像素数量约为35[Mpixel]。将通过举例来描述分量。例如,如果由扫描处理单元250传输到RAM 270的图像数据是RGB图像,并且每种颜色的色调数量是256,则每个分量的位宽是8位宽度,并且因为有三种颜色,所以分量的数量是三。或者,如果由扫描处理单元250输出的图像数据的色调的数量是1,024,则每个分量的位宽是10位。此外,除了RGB图像数据之外,还输出诸如字符/照片等的图像识别信息,在RGB\*图像识别信息中分量的数量是4。ipm代表扫

描器单元110的读取性能,并且表示扫描器单元110每分钟可以扫描并读出的原稿的数量。除图像传输以外的比例代表当从扫描器单元110输入图像时除了实际传输图像的时间以外的时间的比例。

[0066] 图4C示出了打印图像路径所需的带宽(图3B的T17)。其计算方法由下式给出:

[0067] 打印图像路径所需的带宽=(每页像素数\*每个分量的位宽\*分量数)\*(ppm/60)\*(1/1-除图像传输以外的比例)/8... (3)

[0068] 计算方法与式(2)的差别仅为ipm与ppm,ppm代表每分钟可打印片材(记录介质)的数量。其他变量等与式(2)中的相同,因此将省略其描述。

[0069] 如上所述,RAM 270需要至少保证图像形成装置100的扫描读取速度和打印输出速度,并且选择具有至少CPU等可以操作的存储带宽的存储器。

[0070] 将假设扫描性能使用图4B中的扫描带宽示例2,并且打印性能使用图4C中的打印带宽示例4,通过使用图4A至图4C的示例给出具体描述。在这种情况下,至少需要通过将扫描处理所需的带宽233[MB/s]和打印处理所需的带宽933[MB/s]相加所获得的1,166[MB/s]作为存储带宽。更具体地,因为需要保证至少CPU 200等可以操作的带宽,所以最小需要1166+a[MB/s]作为存储带宽。a是由CPU 200使用的存储带宽。

[0071] 因此,当控制器单元120可以同时操作扫描处理和打印处理时,在图4A所示的存储带宽示例1中具有1,066[MHz]的存储器操作频率的存储器仅输出1,066[MB/s],因此不能选择。因此,在本实施例中,至少需要选择图4A中的存储带宽示例2中的具有存储器操作频率1,866[MHz],1,866[MB/s]的性能的存储器。对于非实时图像路径可以分配额外的带宽,如果选择具有高操作频率的存储器,则也增加了能够操作非实时图像路径的可能性。

[0072] 下面将详细描述用于实现图3D中的操作的构造和序列。

[0073] <带宽监视器的构造>

[0074] 下面将参照图5描述根据本实施例的带宽监视器280的构造的示例。将详细描述各个内部块。带宽监视器280包括带宽计算单元300、带宽阈值设置单元310和311以及带宽阈值检测单元320和321。

[0075] 带宽计算单元300用于测量RAM 270的使用存储带宽。更具体地,带宽计算单元300监视总线290、291、292和293的数据传输,并且计算RAM 270的当前使用存储带宽。由带宽计算单元300计算的使用存储带宽可以从CPU 200读取。带宽计算单元300还经由信号线将计算出的使用存储带宽输出到带宽阈值检测单元320和321。注意,在图5中,总线290至293由箭头概念性地表示。这表示带宽监视器280监视总线290至293并获得信息。

[0076] 此外,在图5中,从带宽计算单元300计算出的使用存储带宽被输出到各个DMAC。这是下面将要描述的第二实施例中的构造,并且因此将省略其描述。

[0077] 带宽阈值设置单元310和311可以由CPU 200设置带宽阈值。在带宽阈值设置单元310和311中设置的阈值被用于与由带宽计算单元300所测量的RAM 270的当前使用存储带宽进行比较。

[0078] 带宽阈值检测单元320和321将带宽计算单元300计算的当前使用存储带宽与带宽阈值设置单元310和311中设置的阈值进行比较,并将比较结果通知给CPU 200。可以从CPU 200设置通知条件,并且条件设置可以是如下情况中的一者:由带宽计算单元300计算出的使用存储带宽超过带宽阈值设置单元310和311中设置的阈值的情况和使用存储带宽落在

带宽阈值设置单元310和311中设置的阈值以下的情况。该带宽监视器280使得CPU 200能够知道RAM 270的当前使用存储带宽。注意,在本实施例中,仅配设了两个带宽阈值设置单元和两个带宽阈值检测单元。然而,如果要进行多个条件,则可以采用配设三个或更多个带宽阈值设置单元和三个或更多个带宽阈值检测单元的构造。

[0079] <DMAC的构造示例>

[0080] 接下来将参照图6描述根据本实施例的DMAC 241至245中的各个的构造示例。将详细描述各内部块。所有DMAC 241至245由CPU 200控制。DMAC 241至245中的各个包括发送缓冲器400、WRITE\_DMAC410、接收缓冲器420、READ\_DMAC 430以及传输许可设置单元450。

[0081] 当数据从各个图像处理单元被传输到RAM 270(写入RAM 270)时使用发送缓冲器400和WRITE\_DMAC 410。当数据从RAM 270被传输到各个图像处理单元(从RAM 270中读出)时使用接收缓冲器420和READ\_DMAC 430。

[0082] 发送缓冲器400是暂时保持从各图像处理单元输入的数据的缓冲器。WRITE\_DMAC 410是进行用于将数据写入RAM 270中的数据传输的控制器。WRITE\_DMAC 410确认包括突发传输数据的一次传输的数据是否被存储在发送缓冲器400中,并且如果数据被存储则将图像数据传输到总线294至298中。

[0083] 接收缓冲器420是暂时保存从READ\_DMAC 430输入的数据的缓冲器。当接收缓冲器420保持数据时,数据被传输到各个图像处理单元。READ\_DMAC 430确认在接收缓冲器420中是否存在用于存储包括突发传输数据的一次接收的数据的空闲空间,并且如果存在空闲空间则向总线294至298输出读出请求,并且接收图像数据。

[0084] 传输许可设置单元450是进行控制以设置能够进行WRITE\_DMAC 410和READ\_DMAC 430的数据传输或者停止数据传输的状态的设置单元,并且由CPU 200进行设置。如果由传输许可设置单元450输出的Enable(有效)信号被有效,则WRITE\_DMAC 410和READ\_DMAC 430可以做出数据传输请求。另一方面,如果Enable信号被无效,则WRITE\_DMAC 410和READ\_DMAC 430不能做出数据传输请求。例如,在本实施例中,总线294至298中的各个均为AXI\_BUS,并且因此被控制以不从写入地址信道和读出地址信道断言VALID信号。

[0085] <处理顺序>

[0086] 接下来,将参照图7来描述本实施例中的根据存储器的使用存储带宽来控制带宽抑制方法的处理序列。例如通过使CPU 200将存储在ROM 211中的控制程序加载到RAM 270中并执行该程序来实现下面将要描述的处理。

[0087] 在步骤S101中,CPU 200确定由带宽监视器280监视的使用存储带宽是否变得大于等于阈值。如果使用存储带宽没有变得大于等于阈值,则重复进行步骤S101中的确定。如果使用存储带宽变得大于等于阈值,则处理进行到步骤S102。用于确定使用存储带宽是否变得大于等于阈值的方法可以通过来自带宽监视器280中的带宽阈值检测单元320的通知来检测。该阈值是图4A所示的存储带宽,并且在带宽阈值设置单元310和311中预设。

[0088] 在步骤S102中,因为使用存储带宽变得大于等于阈值,所以CPU 200对在低优先级处理用非实时图像路径中使用的DMAC 241至245中的各个的传输许可设置单元450进行停止设置。通过停止设置,DMAC 241至245以不做出数据传输请求的方式操作,并且RAM 270的使用存储带宽减小,使得能够进行控制以不超过图4A所示的存储带宽。

[0089] 在步骤S103中,CPU 200确定由带宽监视器280监视的使用存储带宽是否变得小于

等于阈值。如果阈值为变得小于等于阈值,则重复进行步骤S103中的确定。如果使用存储带宽变得小于等于阈值,则处理进行到步骤S104。用于确定使用存储带宽是否变得小于等于阈值的方法通过来自带宽监视器280中的带宽阈值检测单元321的通知来检测。

[0090] 在步骤S104中,因为使用存储带宽变得小于等于阈值,所以CPU 200对在非实时图像路径中使用的DMAC 241至245中的各个的传输许可设置单元450进行许可设置。通过许可设置,DMAC 241至245可以做出数据传输请求。即,这里取消在步骤S102中进行的对存储器的访问限制。

[0091] 例如,在带宽阈值设置单元311中设置的值被设置为略小于图4A中描述的存储带宽的值。在这种情况下,重复如下处理:紧接在步骤S102中停止DMAC 241至245的数据传输之后,在步骤S103中使用存储带宽变为小于等于阈值,并且在步骤S104中DMAC 241至245恢复数据传输。可选地,在带宽阈值设置单元311中设置的值被设置为远小于图4A中描述的存储带宽的值。在这种情况下,不需要与在带宽阈值设置单元311中设置的值被设置为略小于图4A中描述的存储带宽的值的情况那样,频繁地进行传输许可设置单元450的设置的操作。

[0092] 本实施例仅通过两个阈值来实现。然而,如参照图5所描述,也可以配设多个带宽阈值设置单元310和带宽阈值检测单元320。通过准备多个阈值,CPU 200根据各阈值中的一个控制DMAC 241至245中的各个停止/恢复,使得能够实现图3E中描述的操作。这种修改也适用于稍后将描述的第二实施例和第三实施例。

[0093] 将通过举例给出更具体的描述。例如,配设三个带宽阈值设置单元310,并且分别设置超过1,866[MB/s]的值、低于1500[MB/s]的值和低于1200[MB/s]的值的三个阈值。在步骤S101中检测到的各DMAC 241至245的阈值共同为1866[MB/s]。另一方面,DMAC 244使用1500[MB/s],DMAC 241、242、243和245使用1200[MB/s]作为在步骤S103中检测出的阈值。

[0094] 在这种情况下,当设置图3C中的状态时,首先超过了1,866[MB/s],并且因此设置图3D中的状态以暂时停止所有DMAC 241到245。当设置这个状态时,使用存储带宽会很快降低,然后降到1500[MB/s]以下。当设置这个状态时,只有DMAC 244可以操作。当在该状态下值降到1200[MB/s]以下时,其他DMAC 241至243以及245也开始操作。当值未降到1200[MB/s]以下时,获得保持图3E的状态的情形。

[0095] 注意,作为变型例,可以包括带宽阈值设置单元310和带宽阈值检测单元320,以检测停止或恢复各个DMAC处理的存储器的使用存储带宽,并且可以设置能够针对各个DMAC进行控制的设置值。这使得各DMAC 241至245能够如同它们被赋予优先级那样操作。该变型例也适用于稍后将描述的第二实施例和第三实施例。

[0096] 如上所述,根据本实施例的存储器访问系统监视表示在存储器与多个主设备之间使用的总的存储带宽的使用存储带宽,并且确定使用存储带宽是否大于等于由CPU设置的第一阈值。另外,该存储器访问系统基于上述CPU的确定,限制多个主设备当中的低优先级的主设备访问存储器。因此,在本实施例中,监视由RAM 270使用的存储带宽,并且进行控制,以仅在几乎超过RAM 270的可能存储带宽时,不做出从非实时处理单元到RAM 270的存储器访问请求。根据本实施例,这使得可以在最大限度地使用RAM 270的可用带宽的同时保证实时处理单元的传输带宽,也就是说,确保也能够尽量使用非实时处理单元的情形。

[0097] <第二实施例>

[0098] 下面将描述本发明的第二实施例。在上述第一实施例中,当RAM 270的使用存储带

宽几乎达到存储带宽时,带宽监视器280将监视结果通知给CPU 200,并且CPU 200控制DMAC 241至245,保证实时图像路径的带宽。在上述第一实施例中,CPU 200在存储带宽达到阈值之后进行控制,花费较短的时间直到DMAC 241至245的传输许可设置单元450最终做出停止设置。在短时间期间可能超过存储带宽的阈值。因此,需要给在带宽阈值设置单元310中设置的阈值设置小的余量。

[0099] 另一方面,本实施例与上述第一实施例的不同之处在于DMAC 241至245的传输许可设置单元450不由CPU 200设置,而是用DMAC 241至245中的硬件进行控制。通过用硬件进行控制可以立即进行各个传输许可设置单元450的停止设置,使得可以将存储器传输带宽使用到存储带宽的上限。因此,如图5所示,在本实施例中,向DMAC 241至245中的各个通知由带宽计算单元300计算出的使用存储带宽。DMAC 241至245基于通知的使用存储带宽控制各个主设备对RAM 270的访问。

[0100] <DMAC的构造>

[0101] 将参照图8描述根据本实施例的DMAC 241至245中的各个的构造示例。将详细描述各内部块。所有DMAC 241至245都由CPU 200控制。如在第一实施例中描述的图6的构造中一样,DMAC 241至245中的各个包括发送缓冲器400、WRITE\_DMAC 410、接收缓冲器420、READ\_DMAC 430以及传输许可设置单元450。根据本实施例的DMAC 241至245中的各个还包括传输许可确定单元560和阈值设置单元561。

[0102] 发送缓冲器400、WRITE\_DMAC 410、接收缓冲器420以及READ\_DMAC 430具有与参照图6所描述的构造相同的构造,因此将省略其描述。下面将主要描述与图6所示的上述第一实施例的不同之处。

[0103] 用于带宽监视器280的带宽计算单元300来计算使用存储带宽的信号线连接在MEMC 260与DMAC 241至245中的各个之间。阈值设置单元561可以由CPU 200设置,并且设置要与由带宽计算单元300计算出的使用存储带宽进行比较的阈值。传输许可确定单元560将阈值设置单元561的值与由带宽计算单元300计算出的使用存储带宽进行比较,并且如果使用存储带宽大于等于在阈值设置单元561中设置的阈值,则确定进行停止设置。另一方面,如果使用存储带宽小于在阈值设置单元561中设置的阈值,则传输许可确定单元560确定进行许可设置。传输许可设置单元450被通知确定结果。

[0104] 传输许可设置单元450除了不由CPU 200控制而是根据由传输许可确定单元560的确定结果控制以外,具有与上述第一实施例相同的构造。

[0105] 在本实施例中,在阈值设置单元561中设置特定阈值,并且传输许可确定单元560根据使用存储带宽是大于等于阈值还是小于阈值来进行传输许可设置单元的停止/许可设置。然而,如在上述第一实施例中那样,可以采用如果使用存储带宽超过特定阈值则进行传输停止设置,并且如果使用存储带宽落在特定阈值以下,则进行传输许可设置的构造。

[0106] 这里将描述当采用本实施例的构造时用于进行图3C至图3E所示的操作的设置的示例。例如,将给出用于进行与图7的流程图描述的操作相同的操作的描述。

[0107] 在DMAC 241至245中的各个的阈值设置单元561中将进行停止设置的阈值设置为1,866 [MB/s]。DMAC 244的许可设置阈值被设置为1500 [MB/s],DMAC 241、242、243和245的许可设置阈值被设置为1200 [MB/s]。通过这样设置,变得可以如在上述第一实施例中那样进行图3C至图3E所示的操作。

[0108] 当然也可以使用其他设置值。例如,如果在DMAC 241、242、243和245中的各个的阈值设置单元561中将进行停止设置的阈值设置为1,500[MB/s],则当然保证DMAC 240和DMAC 246操作。另外,也可以增加要优先处理的DMAC 244的比例,尽管它是非实时图像路径操作。

[0109] 如上所述,根据本实施例的存储器访问系统监视表示在存储器与多个主设备之间使用的总的存储带宽的使用存储带宽,并且通过DMAC确定使用存储带宽是否大于等于第一阈值。基于确定结果,DMAC限制多个主设备当中的低优先级的主设备对存储器的访问。因此,在本实施例中,充当DMAC 241至245中的各个中的硬件的传输许可确定单元560进行DMAC 241至245中的各个的传输许可设置单元450。这使得CPU 200能够比传输许可设置单元450更加直接地进行传输许可设置单元450的停止设置。因此,变得可以使用存储器传输带宽达比上述第一实施例多的存储带宽的上限。

[0110] <第三实施例>

[0111] 下面将描述本发明的第三实施例。在本实施例中,如图3D所示,如果RAM 270的使用存储带宽几乎超过RAM 270的可能传输带宽(存储带宽),则进行控制以缩短突发长度以减少用于非实时图像路径的数据传输的使用存储带宽。更具体地,CPU 200使用带宽监视器280来控制DMAC 241至245,从而实现上述控制。在图3D中,由虚箭头表示各个具有缩短的突发长度的SEND作业的非实时图像路径,并且由长短交替的虚线的箭头表示各个具有缩短的突发长度的PDL\_PRINT作业的非实时图像路径由。通过如此控制,可以保证控制器单元120不会作为系统发生故障。

[0112] <DMAC的构造>

[0113] 下面将参照图9描述根据本实施例的DMAC 241至245中的各个的构造示例。将详细描述各内部块。所有DMAC 241至245都由CPU 200控制。这里将仅描述与上述第一实施例中描述的构造不同的构造。

[0114] 根据本实施例的DMAC 241至245中的各个包括突发长度设置单元480以取代图6中的传输许可设置单元450的构造。突发长度设置单元480是在WRITE\_DMCA 410和READ\_DMCA 430的数据传输时控制突发长度的设置单元,并由CPU 200设置。根据由突发长度设置单元480输出的突发长度,WRITE\_DMCA 410和READ\_DMCA 430输出发送缓冲器400的数据写入请求和接收缓冲器420的数据读出请求。

[0115] DMAC的突发长度的初始值被设置为可设置的最大突发大小。根据可以在突发长度设置单元480中设置的最大突发大小,或者可以由发送缓冲器400、接收缓冲器420和DMAC访问的缓冲器(261至264中的一个)中的各个存储的最大突发大小来决定最大突发大小。

[0116] <处理序列>

[0117] 接下来,参照图10来说明用于根据实施例中的存储器的使用存储带宽来控制带宽抑制方法的处理顺序。例如通过使CPU 200将存储在ROM 211中的控制程序加载到RAM 270中并执行该程序,来实现下面将要描述的处理。注意,这里将仅描述与上述第一实施例中描述的图7的控制不同的步骤。即,在处理序列中,执行步骤S1001和S1002来代替步骤S102和S104。

[0118] 在步骤S1001中,因为使用存储带宽大于等于阈值,所以CPU 200对在非实时图像路径中使用的DMAC 241至245中的各个的突发长度设置单元480进行缩短突发长度的改变设置。通过改变设置,DMAC 241至245中的各个以减少针对数据传输请求的数据传输量的方

式操作,并且RAM 270的使用存储带宽减小,使得可以进行控制以不超过图4A中描述的存储带宽。

[0119] 如果CPU 200在步骤S103中确定使用存储带宽变得小于等于阈值,则处理进行到步骤S1002,在步骤S1002中,CPU 200对用于非实时图像路径中的DMAC 241至245中的各个的突发长度设置单元480进行延长突发长度的改变设置。通过改变设置,DMAC 241至245中的各个以增加针对数据传输请求的数据传输量的方式操作,使得可以增加RAM 270的使用存储带宽。

[0120] 例如,在带宽阈值设置单元311中设置的值可以是略小于图4A中描述的存储带宽的值。在这种情况下,重复如下的处理:紧接在步骤S1001中在DMAC 241至245的数据传输停止之后,在步骤S103中使用存储带宽变为小于等于阈值,并且在步骤S1002中DMAC 241至245恢复数据传输。可选地,在带宽阈值设置单元311中设置的值可以是远小于图4A中描述的存储带宽的值。在这种情况下,不需要与在带宽阈值设置单元311中设置的值被设置为略小于图4A中描述的存储带宽的值的情况那样,频繁地进行突发长度设置单元480的设置的操作。

[0121] 本实施例仅通过两个阈值来实现。然而,如参照图5所描述的,也可以提供多个带宽阈值设置单元310和带宽阈值检测单元320。通过准备多个阈值,CPU 200进行控制以根据对应的阈值中的一个改变DMAC 241至245中的各个的突发长度,使得能够实现图3E中描述的操作。更具体地,配设三个带宽阈值设置单元310,并且分别设置超过1,866[MB/s]的值,低于1500[MB/s]的值和低于1200[MB/s]的值的三个阈值。各个DMAC的突发长度的初始设置值是8。在步骤S101中检测到的各DMAC 241至245中的阈值是共同的1,866[MB/s]。作为在步骤S103中检测到的阈值,DMAC 244使用1500[MB/s]和1200[MB/s],并且DMAC 241、242、243和245仅使用1200[MB/s]。

[0122] 在这种情况下,当设置图3C中的状态时,首先超过1,866[MB/s],因此设置图3D中的状态以将所有DMAC 241至245改变为短的突发长度(突发长度2)。当设置这个状态时,使用存储带宽很快降低,然后降到1500[MB/s]以下。当设置这个状态时,只有DMAC 244被改变为长突发长度(突发长度4)。当在该状态下值降到1200[MB/s]以下时,DMAC 241至245中的各个被改变为最大突发长度(突发长度8)。当该值未落在1200[MB/s]以下时,获得保持图3E的状态的情形。

[0123] 通过由此根据带宽阈值逐步改变突发长度,变得可以根据带宽来控制使用存储带宽。在本实施例中描述了示例。然而,可以配设带宽阈值设置单元310和带宽阈值检测单元320以检测改变各个DMAC的突发长度的存储器的使用存储带宽,并且可以设置针对各个DMAC进行控制的设置值。这使得各DMAC 241至245能够如同它们被赋予优先级那样操作。

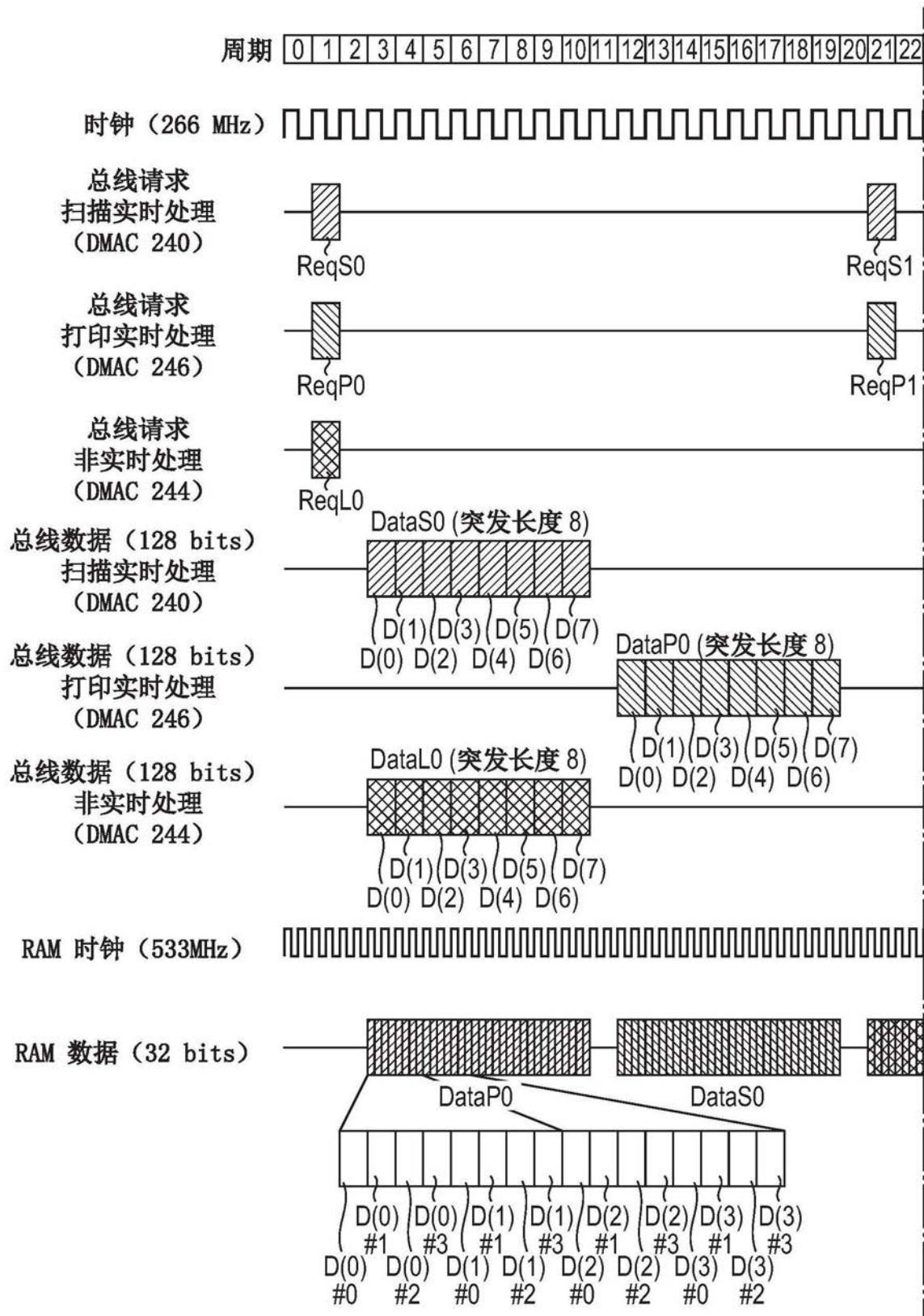

[0124] <时序图>

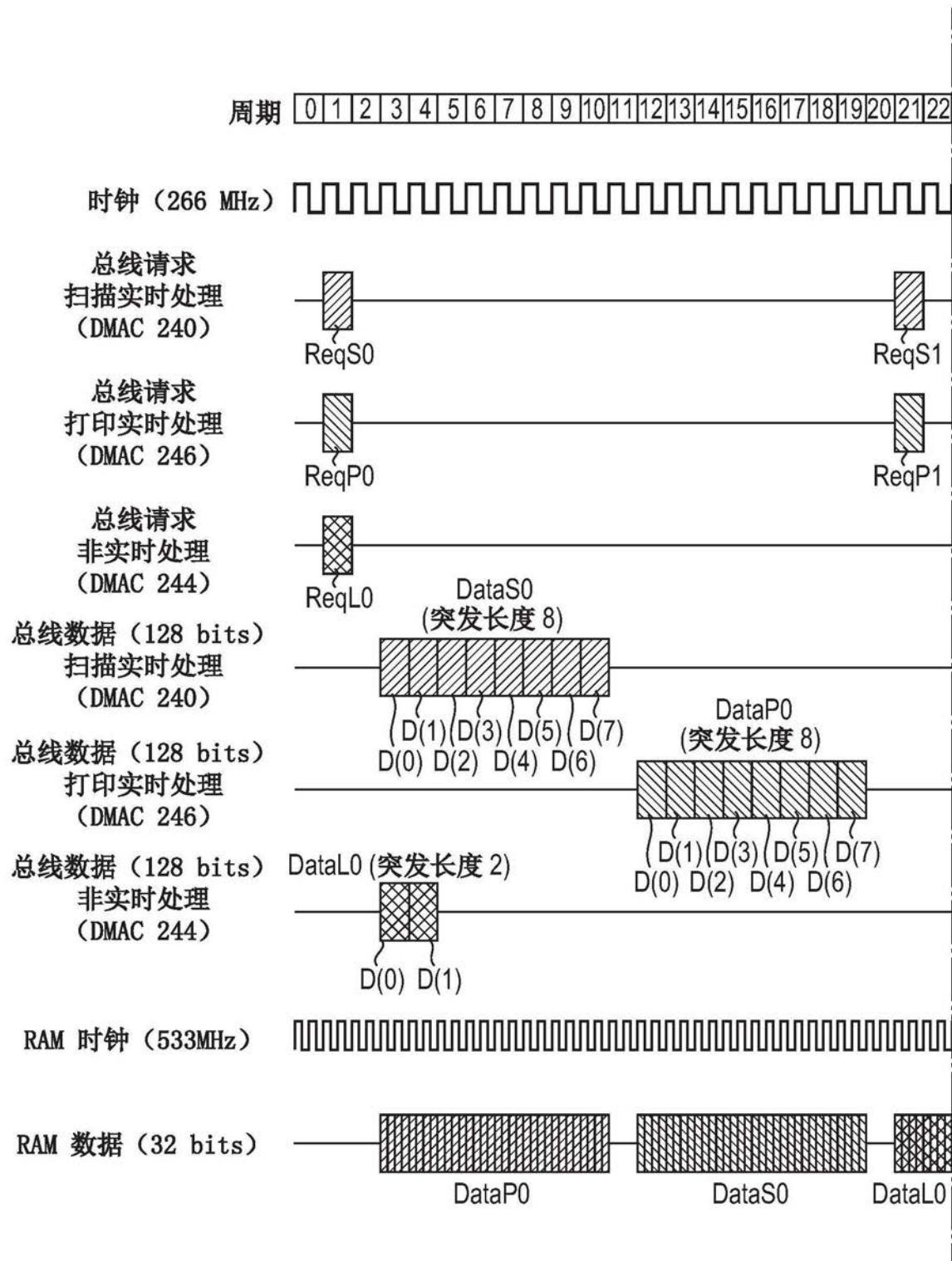

[0125] 接下来将参照图11A和图11B描述在如下情况下的操作,其中,实时处理中的SEND作业的写入图像数据传输和PDL\_PRINT作业的读出图像数据传输,以及非实时处理中的写入图像数据传输同时发生。注意,DMAC 240和246中的各个以及DMAC 244连接到以266MHz操作的128位总线宽度的总线,并且发出突发长度8的请求。RAM 270是正在它的533MHz的两个边缘进行数据传输的、具有32位总线宽度的RAM。也就是说,总线的突发长度为1的数据由RAM时钟的四个周期传输。

[0126] 下面将描述在非实时处理中的突发长度未被缩短的情况下以及在该突发长度被缩短的情况下使用存储带宽。首先,将参照图11A-1和图11A-2描述在非实时处理中的突发长度未被缩短的情况下操作。

[0127] 在周期1中,DMAC 240、246和244发出总线请求 (ReqS0、ReqP0和ReqL0)。由DMAC 240和244写入的图像数据 (DataS0和DataL0) 从周期3被传输到周期10,并写入缓冲器261和262中。另一方面,DMAC246的总线请求 (ReqP0) 是从RAM 270读出的请求,并且因此图像数据从周期3到周期10被从RAM 270读出。

[0128] 然后,从周期12到周期19,来自DMAC 240的存储在缓冲器261中的写入图像数据 (DataS0) 被传输到RAM 270。另一方面,从RAM 270读出的读出图像数据 (DataP0) 被传输到DMAC 246。

[0129] 在周期21中,由于缓冲器261的图像数据 (DataS0) 被写入RAM 270,并且缓冲器具有空闲空间,所以DMAC 240发出下一个总线请求 (ReqS1)。同样,由于针对总线请求 (ReqP0) 的读出数据 (DataP0) 的读出完成,所以DMAC 246发出下一个总线请求 (ReqP1)。

[0130] 从周期21到周期28,写入缓冲器262中的图像数据 (DataL0) 被写入。在周期30中,由于缓冲器262的图像数据 (DataL0) 被写入RAM 270,并且缓冲器具有空闲空间,所以DMAC 244发出下一个总线请求 (ReqL1)。

[0131] 如上所述,图像数据依次被传输到RAM 270。在周期46中完成了针对作为实时处理的DMAC 240和246的两个总线请求的图像数据传输。

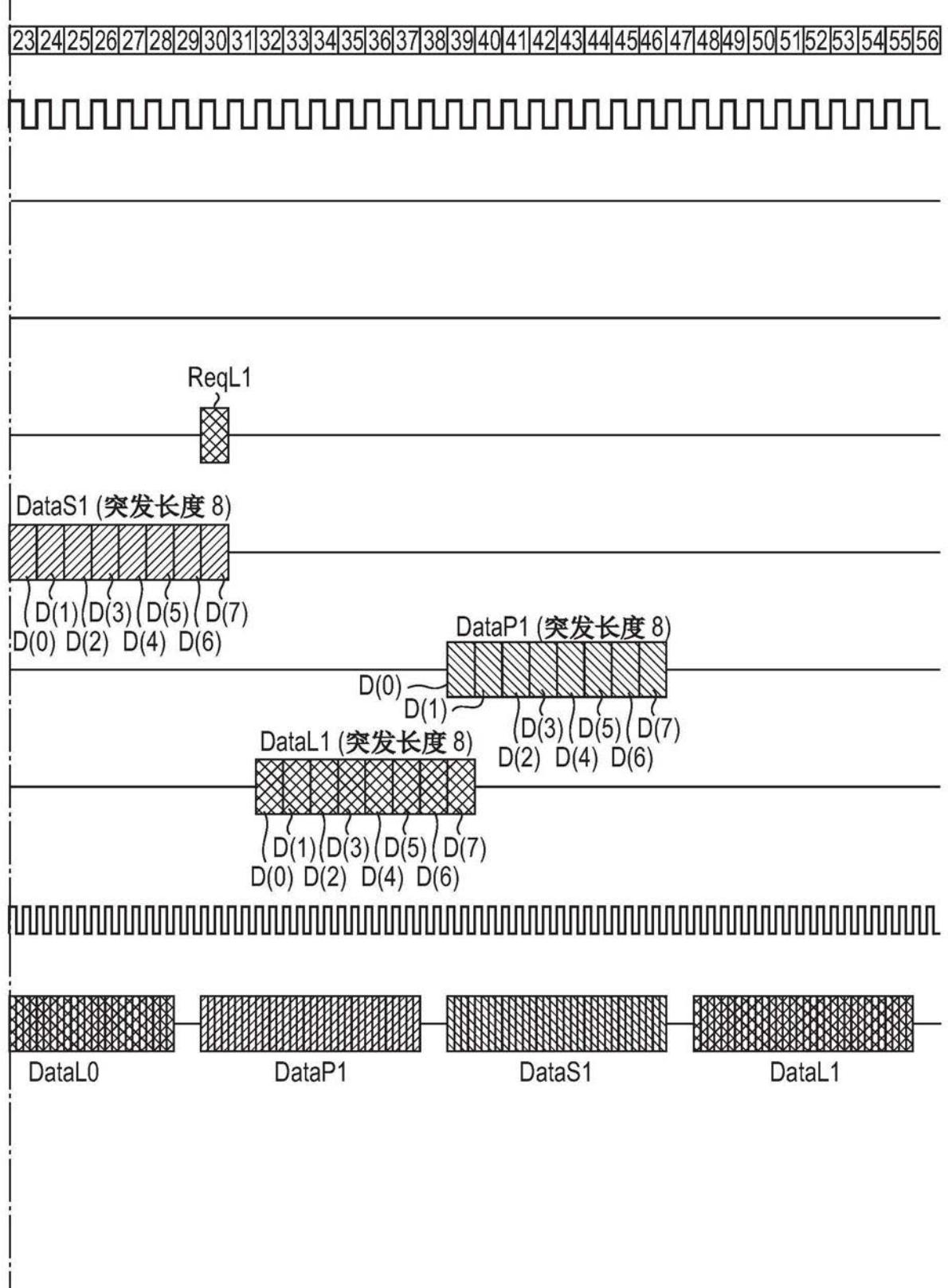

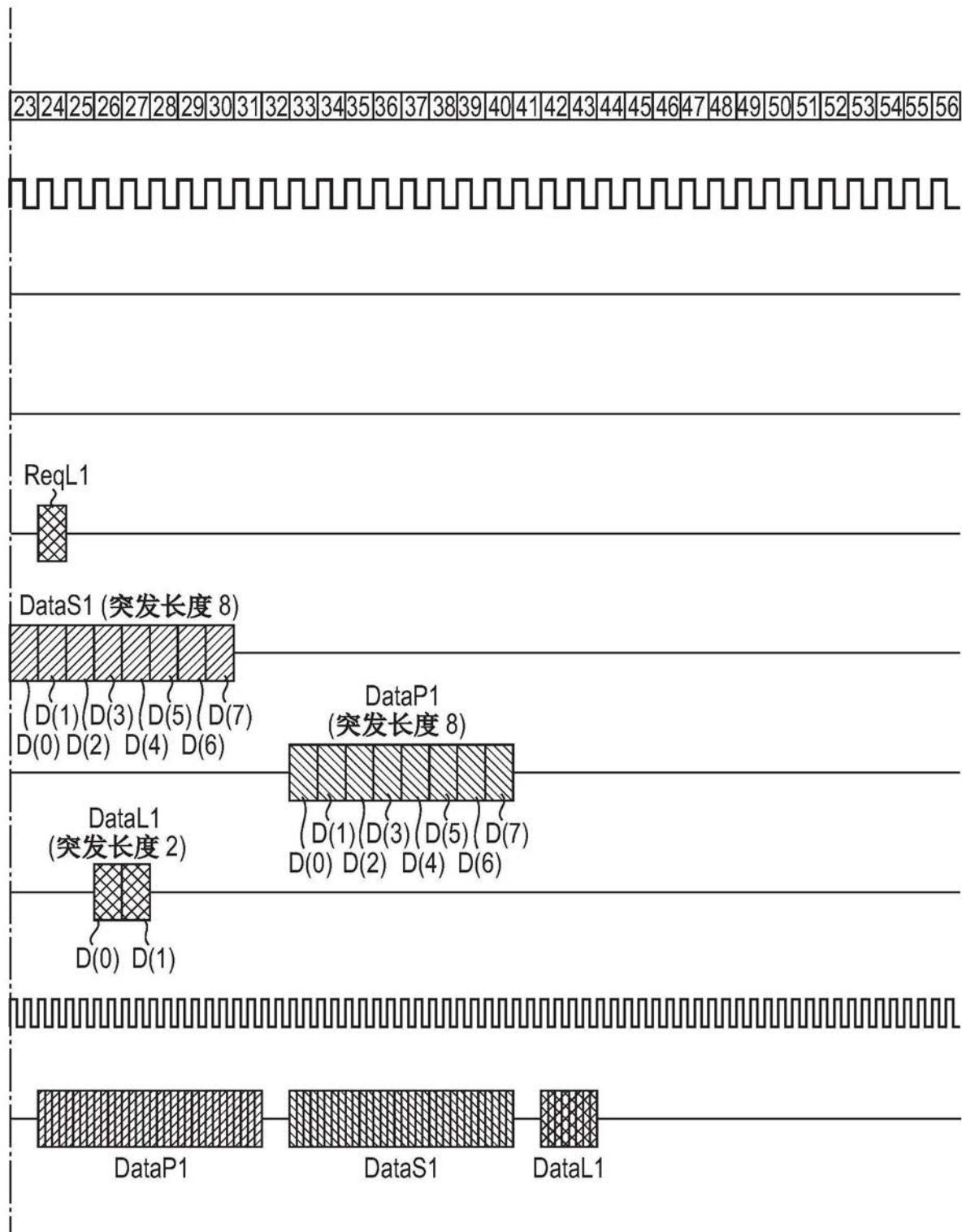

[0132] 随后,将参照图11B-1和图11B-2描述在非实时处理中突发长度被改变为突发长度2的情况下的操作。从周期1到周期21,DMAC 240和246的操作与图11A-1和图11A-2的相同,因此省略其描述。

[0133] 另一方面,DMAC 244被设置为具有突发长度2,并且因此从周期3到周期4图像数据 (DataL0) 被写入缓冲器262。从周期21到周期22,写入缓冲器262的图像数据 (DataL0) 被写入到RAM 270。

[0134] 由于来自DMAC 244的图像数据传输具有突发长度2,因此在周期22中到RAM 270的图像传输被释放。因此,从周期24到周期31在周期21中发出的总线请求 (ReqP1) 的图像数据被读出,并且从周期33到周期40,来自DMAC 240的图像数据 (DataS1) 被写入。

[0135] 如果如非实时处理那样做出将DMAC 244中的突发长度改变为突发长度2的改变,则在周期40中完成了针对作为实时处理的DMAC 240和246的两个总线请求的图像数据传输。注意,这里描述了实时处理具有突发长度8并且非实时处理具有突发长度2的示例。然而,本发明不限于此。可以通过进一步延长实时处理中的突发长度或者进一步缩短非实时处理中的突发长度来增加分配给实时处理的带宽。

[0136] 如上所述,根据本实施例,监视由RAM 270使用的使用存储带宽,并且仅在几乎超过RAM 270的可能存储带宽时,减少用于从非实时处理单元到RAM 270的存储器访问请求的使用存储带宽。这使得可以在最大限度地使用RAM 270的可用带宽的同时保证实时处理单元的传输带宽,也就是说,确保能够尽量使用非实时处理单元的情形。注意,本实施例可以与上述第一实施例和第二实施例组合应用。也就是说,CPU 200或各个DMAC可以进行降低用于存储器访问请求的使用存储带宽的确定。

[0137] 其他实施例

[0138] 还可以通过读出并执行记录在存储介质(也可更完整地称为“非暂时性计算机可读存储介质”)上的计算机可执行指令(例如,一个或更多个程序)以执行上述实施例中的一个或更多个的功能,和/或包括用于执行上述实施例中的一个或更多个的功能的一个或更多个电路(例如,专用集成电路(ASIC))的系统或装置的计算机,来实现本发明的实施例,并且,可以利用通过由系统或装置的计算机例如读出并执行来自存储介质的计算机可执行指令以执行上述实施例中的一个或更多个的功能,并且/或者控制一个或更多个电路以执行上述实施例中的一个或更多个的功能的方法,来实现本发明的实施例。计算机可以包括一个或更多个处理器(例如,中央处理单元(CPU)、微处理单元(MPU)),并且可以包括分开的计算机或分开的处理器的网络,以读出并执行计算机可执行指令。计算机可执行指令可以例如从网络或存储介质被提供给计算机。存储介质可以包括例如硬盘、随机存取存储器(RAM)、只读存储器(ROM)、分布式计算系统的存储器、光盘(诸如压缩光盘(CD)、数字通用光盘(DVD)或蓝光光盘(BD)<sup>TM</sup>)、闪存装置以及存储卡等中的一个或更多个。

[0139] 本发明的实施例还可以通过如下的方法来实现,即,通过网络或者各种存储介质将执行上述实施例的功能的软件(程序)提供给系统或装置,该系统或装置的计算机或是中央处理单元(CPU)、微处理单元(MPU)读出并执行程序的方法。

[0140] 虽然针对示例性实施例描述了本发明,但是,应该理解,本发明不限于公开的示例性实施例。权利要求的范围应当被赋予最宽的解释,以涵盖所有这类变型例以及等同的结构和功能。

图1

图2

图3A

图3B

图3C

图3D

图3E

## 存储带宽 (RAM 270可以输出的带宽)

| 示例      | 存储器工作频率<br>[MHz] | 存储器总线宽度<br>[bit] | 存储器效率 | 存储器带宽<br>[MB/s] |

|---------|------------------|------------------|-------|-----------------|

| 存储带宽示例1 | 1066             | 32               | 25%   | 1066            |

| 存储带宽示例2 | 1866             | 32               | 25%   | 1866            |

| 存储带宽示例3 | 2400             | 32               | 25%   | 2400            |

图4A

扫描图像路径所需的带宽 [在图3A的T1处的图像路径]

| 示例      | 分辨率    | 每页像素数<br>(A4) [Mpix] | 每个分量的<br>宽度 [bit] | 分量数 | ipm | 除图像传输以外的比例<br>(片材间隔等) | 扫描图像路径<br>所需的带宽<br>[MB/s] |

|---------|--------|----------------------|-------------------|-----|-----|-----------------------|---------------------------|

| 存储带宽示例1 | 600dpi | 35                   | 8                 | 3   | 30  | 25%                   | 70                        |

| 存储带宽示例2 | 600dpi | 35                   | 8                 | 3   | 100 | 25%                   | 233                       |

图4B

打印图像路径所需的带宽[在图3B的T17处的图像路径]

| 示例      | 分辨率     | 每页像素数(A4) [Mpix] | 每个分量的宽度[bit] | 分量数 | ppm | 除图像传输以外的比例(片材间隔等) | 打印图像路径所需的带宽[MB/s] |

|---------|---------|------------------|--------------|-----|-----|-------------------|-------------------|

| 存储带宽示例1 | 600dpi  | 35               | 8            | 3   | 30  | 25%               | 70                |

| 存储带宽示例2 | 600dpi  | 35               | 8            | 3   | 100 | 25%               | 233               |

| 存储带宽示例3 | 1200dpi | 140              | 8            | 3   | 30  | 25%               | 280               |

| 存储带宽示例4 | 1200dpi | 140              | 8            | 3   | 100 | 25%               | 933               |

图4C

图5

图6

图7

图8

图9

图10

图11A-1

图11A-2

图11B-1

图11B-2