# MINISTERO DELLO SVILUPPO ECONOMICO DIREZIONE GENERALE PER LA LOTTA ALLA CONTRAFFAZIONE UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA DI INVENZIONE NUMERO | 102019000016871 |

|------------------------------|-----------------|

| Data Deposito                | 20/09/2019      |

| Data Pubblicazione           | 20/03/2021      |

# Classifiche IPC

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| Н       | 03     | В           | 19     | 14          |

# Titolo

CIRCUITO ELETTRONICO PER TRIPLICARE LA FREQUENZA, IN PARTICOLARE PER APPLICAZIONI IN RADIOFREQUENZA NELL'INTERVALLO DELLE ONDE MILLIMETRICHE

### DESCRIZIONE

del brevetto per Invenzione Industriale dal titolo:

"CIRCUITO ELETTRONICO PER TRIPLICARE LA FREQUENZA, IN

PARTICOLARE PER APPLICAZIONI IN RADIOFREQUENZA

NELL'INTERVALLO DELLE ONDE MILLIMETRICHE"

di STMICROELECTRONICS S.R.L.

di nazionalità italiana,

con sede a VIA C. OLIVETTI 2, 20864 AGRATE BRIANZA (MB)

Inventori: MAHDIPOUR PIRBAZARI Mahmoud, MAZZANTI Andrea,

PALLOTTA Andrea

\*\*\*

La presente invenzione riguarda un circuito elettronico per triplicare la frequenza, in particolare per applicazioni in radiofrequenza nell'intervallo delle onde millimetriche.

Come è noto, le comunicazioni nell'intervallo delle millimetriche (onde-mm) hanno attirato molta attenzione negli ultimi anni a causa dell'ampia larghezza di banda disponibile che fornisce una elevata capacità di Quindi, gli attuali trasmissione di dati. utilizzano ricetrasmettitori che convertono i dalla frequenza base alla frequenza scambiati comunicazione selezionata e viceversa. A tal ricetrasmettitori utilizzano una circuiteria per generare un'oscillazione locale (LO). La progettazione

ricetrasmettitori di oscillazione locale è fondamentale che molti parametri contrastanti, ad esempio intervallo di frequenze, rumore di fase, potenza di uscita livelli di toni spuri, influenzano le prestazioni. A differenza di quanto cercato comunemente ad altre frequenze radio, la generazione di oscillazione locale con circuito PLL (anello ad aggancio di fase) comprendente un VCO (oscillatore a tensione controllata) alla frequenza di uscita desiderata non è fattibile nell'intervallo delle onde millimetriche. Infatti, il forte impatto strutture parassite e gli effetti sulla tecnologia del silicio e il basso fattore qualità dei componenti passivi (soprattutto, condensatori variabili) compromettono l'intervallo di frequenze e il rumore di fase ottenibili. Inoltre, i divisori di frequenza tradizionali nel PLL causano un consumo di potenza eccessivo.

Un approccio più promettente consiste nel fornire un PLL in un intervallo inferiore (ad esempio, nell'intervallo 10-20 GHz), in cui il VCO di silicio presenta massimo fattore di merito, seguito da una catena di moltiplicatori di frequenza.

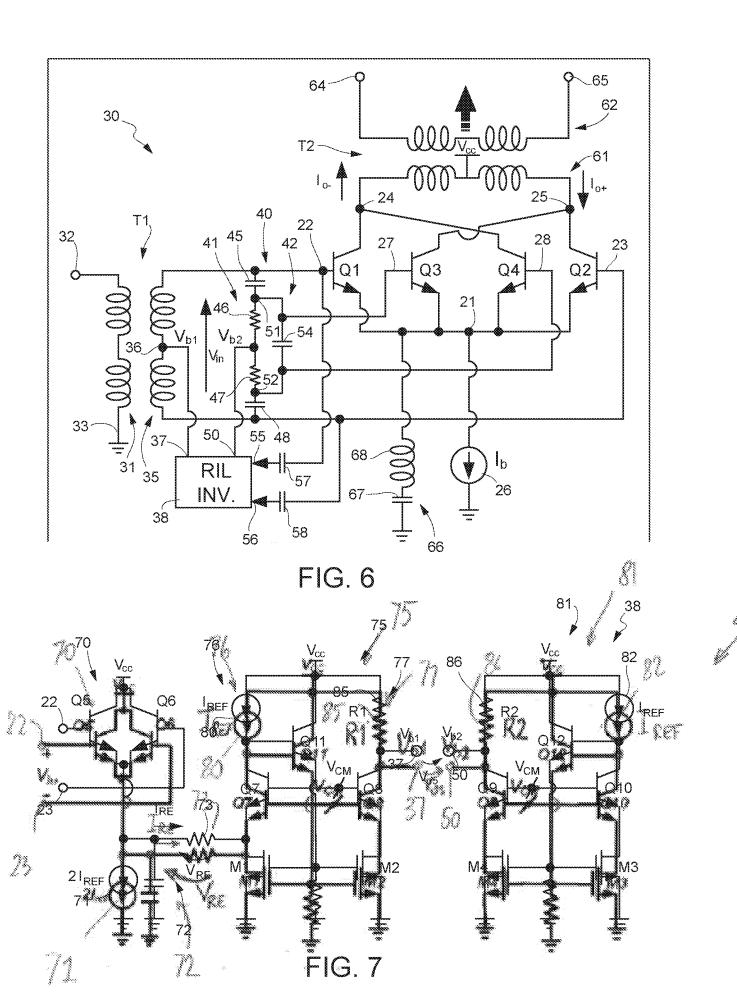

Per esempio, la figura 1 mostra un tipico sistema a moltiplicatore di frequenza 1 per ottenere una moltiplicazione per 6, per esempio per ottenere una tensione di 60 GHz da una sorgente di 10 GHz. Qui, un

generatore di tensione a bassa frequenza 2 fornisce una tensione di ingresso Vin ad una frequenza di base  $f_0$ , ad esempio a 10 GHz, ad un triplicatore di frequenza 3, che genera una tensione intermedia V1 ad una frequenza tripla  $(3f_0)$ . La tensione intermedia V1 è disponibile ad una prima uscita 01 attraverso un primo buffer 4 ed è alimentata ad un duplicatore di frequenza 5 che genera una tensione di uscita V0 alla frequenza di uscita  $6F_0$ . La tensione di uscita V0 è resa disponibile ad una seconda uscita 02 attraverso un secondo buffer 6.

sistema a moltiplicatore di frequenza 1 fornire una buona soppressione dei segnali di pilotaggio e delle armoniche indesiderate per non compromettere prestazioni di ricetrasmettitore. In particolare, sistema a moltiplicatore di frequenza 1, è desiderato che il primo stadio (triplicatore di freguenza 3) presenti massima soppressione, poiché i suoi toni spuri spostati vicino alle frequenze LO degli stadi in cascata. dall'intermodulazione Inoltre, questa problematica è più critica per moltiplicatori di ordine dispari, poiché i moltiplicatori di ordine pari (qui, i duplicatori di frequenza 5) possono sfruttare i transistori push-push per sopprimere le componenti segnale a frequenze indesiderate.

I moltiplicatori di ordine dispari, come ad esempio il

triplicatore di frequenza 3 del sistema a moltiplicatore di frequenza 1, comprendono tipicamente un transistore con basso angolo di conduzione (ad esempio, un transistore polarizzato in classe C) che genera una corrente ricca di armoniche e la componente desiderata è selezionata con un filtro passa banda o un oscillatore agganciato a iniezione.

Per esempio, la figura 2 mostra la struttura di base di un circuito triplicatore in classe C, indicato con 10. Il circuito triplicatore in classe C 10 comprende un transistore 11, qui di tipo bipolare, alimentato su un terminale di base B dalla tensione di ingresso

$Vin = A \sin(2\pi f_0 t)$

attraverso un condensatore di ingresso 12 e accoppiato ad una tensione di polarizzazione Vb attraverso un resistore 13. Il transistore 11 ha un terminale di emettitore E collegato a massa e un terminale di collettore C accoppiato ad un terminale di uscita 14 e ad una tensione di alimentazione  $V_{\rm cc}$  attraverso un circuito risonante LC 15 sintonizzato a  $3f_0$ .

In modo di per sé noto, il circuito triplicatore in classe C 10 conduce una corrente Io il cui contenuto armonico è fissato dall'angolo di conduzione  $\theta$  determinato dalla tensione di polarizzazione Vb e mostrato nelle simulazioni delle figure 3A e 3B.

Nel dettaglio, la figura 3A mostra l'andamento della

densità di corrente di uscita Jo (corrente di uscita Io normalizzata rispetto all'area A del transistore 11) per la fondamentale (IfO), la terza armonica (I3fO) e la quinta (I5f0). La figura 3B mostra l'andamento armonica If0/I3f0 (= Jf=/J3f0) delle rapporto ampiezze della normalizzata la fondamentale J£0 е terza armonica normalizzata (J3f0) in funzione dell'angolo di conduzione θ.

Come si può notare dalla figura 3A, il rapporto di reiezione armonico totale HRR è dominato dalla fondamentale JfO, ovvero dalla dispersione del segnale di pilotaggio, che sempre maggiore rispetto alla terza armonica normalizzata J3f0. In corrispondenza dell'angolo conduzione  $\theta \approx 150^{\circ}$ , l'ampiezza della terza armonica normalizzata J3f0 è massimizzata (punto M nella figura 3A), ma la fondamentale JfO è ancora 9 dB maggiore rispetto alla terza armonica J3f0 (come anche visibile nella figura 3B). Anche dimensionando il circuito risonante LC 15 in modo da massimizzare la soppressione in compromesso larghezza di banda, il circuito triplicatore di classe C 10 ha una soppressione molto debole, che non può essere aumentata sopra i 20 dB.

I circuiti triplicatori in classe C possono essere migliorati, in linea di principio, usando una topologia di filtro più complessa o mettendo in cascata molteplici stadi

di filtraggio, ma al costo di un'elevata complessità di progettazione, grande area, limitazione di larghezza di banda e maggiore consumo.

Anche la soluzione di oscillatore agganciato a iniezione (si veda, per esempio, N. Mazor et al., "A high suppression frequency tripler for 60-GHz transceivers," in 2015 IEEE MTT-S International Microwave Symposium, 2015, pp. 1-4), sebbene fornisca una migliore soppressione (fino a circa 30 dB), non risolve il problema in modo soddisfacente.

Perciò, uno scopo dell'invenzione è fornire un triplicatore di frequenza che superi gli svantaggi della tecnica nota e in particolare migliori considerevolmente la soppressione della frequenza del segnale di pilotaggio sull'uscita.

Secondo la presente invenzione, sono forniti un circuito elettronico ed un metodo per triplicare la frequenza, come definiti nelle rivendicazioni allegate.

Per la comprensione della presente invenzione, sue forme di realizzazione verranno ora descritte solo a titolo esemplificativo, con riferimento ai disegni, in cui:

la figura 1 mostra un diagramma a blocchi della struttura generale di una catena a moltiplicatore di frequenza;

la figura 2 è uno schema circuitale di un

moltiplicatore di frequenza noto;

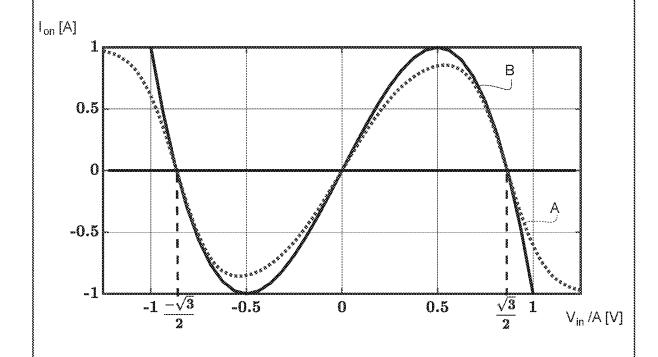

le figure 3A e 3B sono andamenti di grandezze riferite al circuito di figura 2;

la figura 4 è uno schema circuitale del presente triplicatore di frequenza;

- la figura 5 mostra l'andamento di una transcaratteristica desiderata e l'effettiva caratteristica del circuito di figura 4;

- la figura 6 è uno schema circuitale di un dispositivo triplicatore includente il circuito di figura

4:

- la figura 7 è uno schema circuitale di una forma di realizzazione di un blocco del dispositivo triplicatore di figura 6;

- la figura 8 mostra andamenti di grandezze riferite al circuito di figura 4; e

- la figura 9 mostra andamenti comparativi dello spettro di potenza ottenuto con il circuito di figura 4 e il circuito della tecnica nota di figura 1.

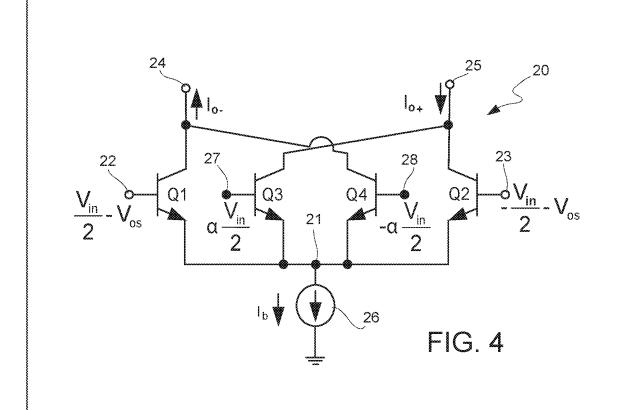

La figura 4 mostra un circuito triplicatore 20 che consente di ottenere una elevata soppressione di armoniche indesiderate.

Il circuito triplicatore 20 rappresenta una implementazione di un circuito triplicatore ideale basato su transistore avente una transcaratteristica polinomiale

f(Vin) (successivamente anche chiamata transcaratteristica polinomiale ideale) secondo la seguente equazione (1):

$$f(V_{in}) = \left(\frac{3}{A}V_{in} - \frac{4}{A^3}V_{in}^3\right)g_m \tag{1}$$

in cui  $g_m$  è la trasconduttanza del transistore nel circuito triplicatore (ad una condizione di polarizzazione in continua specifica).

In particolare, come si può dimostrare con alcuni calcoli, le transcaratteristiche ideali indicate sopra consentono a un circuito triplicatore, ricevente al suo ingresso una tensione di pilotaggio sinusoidale:

$$V_{in} = A\sin(2\pi f_0 t) = A\sin(\omega_0 t)$$

avente ampiezza A e frequenza di base  $f_{0}$  in grado di generare una corrente di uscita  $I_{0}$ :

$$I_o = f(V_{in}) = g_m \sin(3 \cdot 2\pi f_0 t) = g_m \sin(3\omega_0 t)$$

avente soltanto la terza armonica ( $3f_0$ ).

La figura 4 mostra la struttura del circuito triplicatore 20 che ha una transcaratteristica che si avvicina alla transcaratteristica polinomiale f(Vin), come discusso in seguito.

In dettaglio, in riferimento alla figura 4, il circuito triplicatore 20 comprende una prima e una seconda coppia di transistori, accoppiati tra loro in modo incrociato. In particolare, la prima coppia di transistori comprende un primo e un secondo transistore Q1, Q2, qui di tipo bipolare NPN, e la seconda coppia di transistori

comprende un terzo e un quarto transistore Q3, Q4, anche qui di tipo bipolare NPN. I transistori da Q1 a Q4 hanno gli stessi parametri, in particolare la stessa area di emettitore.

In dettaglio, il primo e il secondo transistore Q1, Q2 hanno terminali di emettitore accoppiati tra loro e ad un nodo comune 21, terminali di base accoppiati ad un primo e, rispettivamente, a un secondo nodo di ingresso 22, 23 e terminali di collettore accoppiati a un primo e, rispettivamente, a un secondo nodo di uscita 24, 25 fornenti una prima e, rispettivamente, una seconda corrente "single-ended"  $I_{o-}$  e  $I_{o+}$ .

Il terzo e il quarto transistore Q3, Q4 hanno terminali di emettitore accoppiati tra loro e ad un nodo comune 21, terminali di base accoppiati ad un terzo e, rispettivamente, a un quarto nodo di ingresso 27, 28, e terminali di collettore accoppiati al secondo e, rispettivamente, al terzo nodo di uscita 25, 24.

Un generatore di corrente di polarizzazione 26, configurato per generare una corrente di polarizzazione Ib, è accoppiato tra il nodo comune 21 e massa.

Il primo e il secondo nodo di ingresso 22, 23 ricevono ciascuno una frazione pari a 1/2 della tensione di ingresso  $V_{\rm in}$ , in controfase, entrambe ridotte di una tensione continua (tensione di offset  $V_{\rm os}$ ). Il terzo e il quarto

nodo di ingresso 27, 28 ricevono ciascuno un'attenuazione  $\alpha/2$  della tensione di ingresso, in controfase, l'attenuazione  $\alpha$  essendo selezionata in modo tale che, durante il funzionamento, a bassi valori della tensione di ingresso  $V_{in}$  e tenendo conto anche della tensione di offset  $V_{os}$ , la prima coppia di transistori Q1, Q2 sia ancora spenta, mentre la seconda coppia di transistori Q3, Q4 sia accesa, come discusso in dettaglio di seguito.

Specificamente, il primo nodo di ingresso 22 riceve la prima tensione V1:

$$V1 = V_{in}/2 - V_{os}$$

;

il secondo nodo di ingresso 22 riceve una tensione V2:

$$V2 = -V_{in}/2 - V_{os};$$

il terzo nodo di ingresso 27 riceve una tensione V3:

$$V3 = \alpha V_{in}/2;$$

e

il quarto nodo di ingresso 28 riceve una tensione V4:

$$V4 = -\alpha V_{in}/2$$

in cui  $V_{\text{os}}$  è la tensione di offset in continua e  $\alpha$  è l'attenuazione, come indicato sopra.

Il circuito triplicatore 20 di figura 4 funziona nel modo seguente. Come indicato sopra, a bassi valori della tensione di ingresso  $V_{\rm in}$ , il primo e il secondo transistore Q1, Q2 hanno basse tensioni di polarizzazione base-emettitore e sono spenti; perciò le correnti di uscita  $I_{\rm o+}$

e  $I_{o-}$  sono governate soltanto dal terzo e dal quarto transistore Q3, Q4, approssimando l'equazione (1). Quando il valore della tensione di ingresso  $V_{in}$  aumenta, il primo e il secondo transistore Q1, Q2 si accendono, sottraendo corrente dai nodi di uscita 24, 25. In particolare, dopo aver raggiunto le loro ampiezze massime, si riduce la corrente differenziale di uscita  $I_{o} = I_{o+} - I_{o+}$ , invertendo la pendenza della transcaratteristica.

La transcaratteristica del circuito triplicatore 20 di figura 4 è mostrata dalla curva A mostrata in figura 5 con linea tratteggiata come corrente di uscita normalizzata  $I_{\rm on}$  in funzione della tensione di uscita normalizzata  $V_{\rm in}/A$ . Per riferimento, la figura 5 mostra anche la transcaratteristica ideale (1) con linea continua B.

In particolare, la corrente di uscita normalizzata  $I_{on}$  è la corrente differenziale  $I_{o+}$  –  $I_{o+}$ , normalizzata rispetto alla sua ampiezza massima (uguale a  $I_b$ ).

I valori dell'attenuazione  $\alpha$  e della tensione di selezionati in modo offset  $V_{os}$ sono tale che la transcaratteristica del circuito triplicatore 20 segua la transcaratteristica polinomiale ideale dell'equazione (1), ovvero in modo tale che la transcaratteristica del circuito triplicatore 20 sia nulla a Vin = 0, poi aumenti con una pendenza simile alla transcaratteristica polinomiale ideale, e quindi diminuisca nuovamente a zero e a valori negativi, seguendo la transcaratteristiche ideali.

L'opposto succede per valori negativi di Vin.

In particolare, gli attraversamenti di zero (oltre a quello a  $V_{\rm in}=0$ ) della transcaratteristica del circuito triplicatore 20 si verificano quando la tensione sul terminale di base del terzo transistore Q3 (sul terzo nodo di ingresso 27) è uguale alla tensione sul terminale di base del primo transistore Q1 (sul primo nodo di ingresso 22) nonché quando la tensione sul terminale di base del quarto transistore Q4 (sul quarto nodo di ingresso 28) è uguale alla tensione sul terminale di base del secondo transistore Q2 (sul secondo nodo di ingresso 23), ovvero quando è soddisfatta la condizione (2):

$$\pm \frac{V_{in}}{2} - V_{OS} = \pm \alpha \frac{V_{in}}{2} \tag{2}.$$

Gli attraversamenti di zero si verificano perciò ai seguenti valori della tensione di ingresso  $V_{\text{in}}$ :

$$V_{in} = \pm \frac{2 V_{OS}}{(1 - \alpha)} \tag{3}.$$

D'altra parte, gli attraversamenti di zero della transcaratteristica (1) (oltre a quello a  $V_{\rm in}$  = 0) si verificano ai seguenti valori della tensione di ingresso  $V_{\rm in}$ :

$$V_{in} = \pm \frac{\sqrt{3}}{2} A \tag{4}.$$

Ne segue che la transcaratteristica del circuito

triplicatore 20 e la transcaratteristica ideale hanno gli stessi attraversamenti di zero quando l'attenuazione  $\alpha$  e la tensione di offset  $V_{os}$  soddisfano la seguente condizione:

$$\frac{2V_{OS}}{(1-\alpha)} = \frac{\sqrt{3}}{2}A\tag{5}.$$

L'analisi delle derivate della transcaratteristica polinomiale ideale (1) mostra che la sua pendenza corrispondenza degli attraversamenti di in corrispondenza di  $V_{in}=\pm\sqrt{3}\,A\,/2$  è  $\pm2$  volte sull'origine. Un'ulteriore analisi del circuito dimostra che è sufficiente progettare l'attenuazione  $\alpha$  = 0,2 per avere le pendenze delle due trans-caratteristiche identiche agli attraversamenti di zero, in modo tale che la forma dell'effettiva transcaratteristica del circuito triplicatore 20 si mantenga il più vicino possibile a quella ideale (si veda la figura 5). Tuttavia, l'analisi del circuito dimostra che un valore dell'attenuazione  $\alpha$ compreso nell'intervallo da 0,1 a 0,35 consente alla transcaratteristica del circuito triplicatore adattarsi bene all'andamento della transcaratteristica polinomiale ideale (1). Infatti, la variazione del valore di attenuazione  $\alpha$  può essere compensata attraverso

tensione di offset Vos, come discusso nel seguito.

Fissando il valore dell'attenuazione  $\alpha$ , il valore della tensione di offset  $V_{os}$  è ottenuto come funzione lineare dell'ampiezza A della tensione di ingresso  $V_{in}$ , in base alla condizione (5).

In questo caso, può essere impostato anche un valore non ottimale dell'attenuazione  $\alpha$ , e il rilevatore di inviluppo funziona come anello aperto in grado di compensare e mantenere la relazione lineare desiderata della condizione (5).

Per esempio, la figura 6 mostra un circuito triplicatore, indicato con 30, comprendente il triplicatore 20 di figura 5 e un rilevatore di inviluppo.

In figura 6, un trasformatore di ingresso T1 ha un primario 31 accoppiato tra un primo e un secondo ingresso circuitale 32, 33 e un avvolgimento secondario 35 accoppiato tra i nodi di ingresso 22, 23 del circuito triplicatore 20. Il secondario 35 ha una presa centrale 36 collegata ad una prima uscita 37 di un rilevatore di inviluppo 38 e posta ad una prima tensione di polarizzazione Vb1.

Un divisore di tensione 40, di tipo capacitivo, è accoppiato tra i nodi di ingresso 22, 23 del circuito triplicatore 20 e comprende un primo ramo 41 e un secondo ramo 42.

Il primo ramo 41 del divisore di tensione 40 comprende un primo condensatore 45, un primo resistore 46, un secondo resistore 47 e un secondo condensatore 48 collegati in serie. Il primo e il secondo condensatore 45, 48 hanno la stessa capacità C1; il primo e il secondo resistore 46, 47 hanno la stessa resistenza R.

La primo ramo 41 ha una presa centrale, tra il primo e il secondo resistore 46, 47, accoppiata ad una seconda uscita 50 del rilevatore di inviluppo 38, che genera una seconda tensione di polarizzazione Vb2. Il primo ramo 41 ha inoltre un primo nodo intermedio 51 tra il primo condensatore 45 e il primo resistore 46 e un secondo nodo intermedio 52 tra il secondo resistore 47 e il secondo condensatore 48. La differenza di tensione Vb2-Vb1 forma la tensione di offset Vos del triplicatore 20 di figura 5.

Il secondo ramo 42 del divisore di tensione 40 comprende un terzo condensatore 54 accoppiato tra il primo e il secondo nodo intermedio 51, 52. Il terzo condensatore 54 ha una capacità C2. Il primo e il secondo nodo intermedio 51, 52 sono inoltre accoppiati al terzo e, rispettivamente, al quarto nodo di ingresso 27, 28 del circuito triplicatore 20.

Il primo e il secondo nodo di ingresso 22, 23 del circuito triplicatore 20 sono inoltre accoppiati a un primo e, rispettivamente, a un secondo ingresso 55, 56 del

rilevatore di inviluppo 38 attraverso rispettivi condensatori 57, 58.

Il circuito triplicatore 30 comprende inoltre un trasformatore di uscita T2 avente un primario 61 accoppiato tra il primo e il secondo nodo di uscita 24, 25 del triplicatore 20 e un secondario 62 accoppiato tra una prima e una seconda uscita circuitale 64, 65; e una rete LC 66 formata da un condensatore di shunt 67 e un induttore di "tail" 68 è accoppiato tra il nodo comune 21 del triplicatore 20 e massa.

La prima e la seconda uscita circuitale 64, 65 possono essere collegate ad un buffer di uscita simile al primo buffer 4 del sistema moltiplicatore di frequenza 1 di figura 1 e/o ad un moltiplicatore di frequenza come ad esempio il duplicatore di frequenza 5 del sistema moltiplicatore di frequenza 1 di figura 1.

Nel circuito triplicatore 30 di figura 6, il primo trasformatore T1 funziona per l'adattamento di linea (come un trasformatore "balun") e genera un segnale differenziale (corrispondente alla tensione di ingresso  $V_{in}$  di figura 4 e quindi identificato con lo stesso riferimento) applicato direttamente al primo e al secondo nodo di ingresso 22, 23 del circuito triplicatore 20 (e quindi ai terminali di base del primo e del secondo transistore Q1, Q2). Il segnale differenziale  $V_{in}$  è ridotto dell'attenuazione  $\alpha$  dal

divisore capacitivo 40 e applicato al terzo e al quarto nodo di ingresso 27, 28 del circuito triplicatore 20 (e quindi ai terminali di base del terzo e del quarto transistore Q3, Q4).

L'induttore di tail 68 risuona con la capacitanza equivalente di shunt presente sul nodo comune 21 e la capacitanza di shunt 67 è dimensionata sufficientemente grande da agire come un corto in alternata alla frequenza operativa del nodo comune 21, che è 2f0. Infatti, la rete LC 66 consente alle capacità parassite di shunt sul nodo comune 21 di caricarsi-scaricarsi a frequenza elevata usando la corrente che viene scambiata con l'induttore di tail 68, quindi di non rimanere in ritardo rispetto alle tensioni di base dei transistori di ingresso Q1-Q4 quando funzionano a elevata frequenza di ingresso.

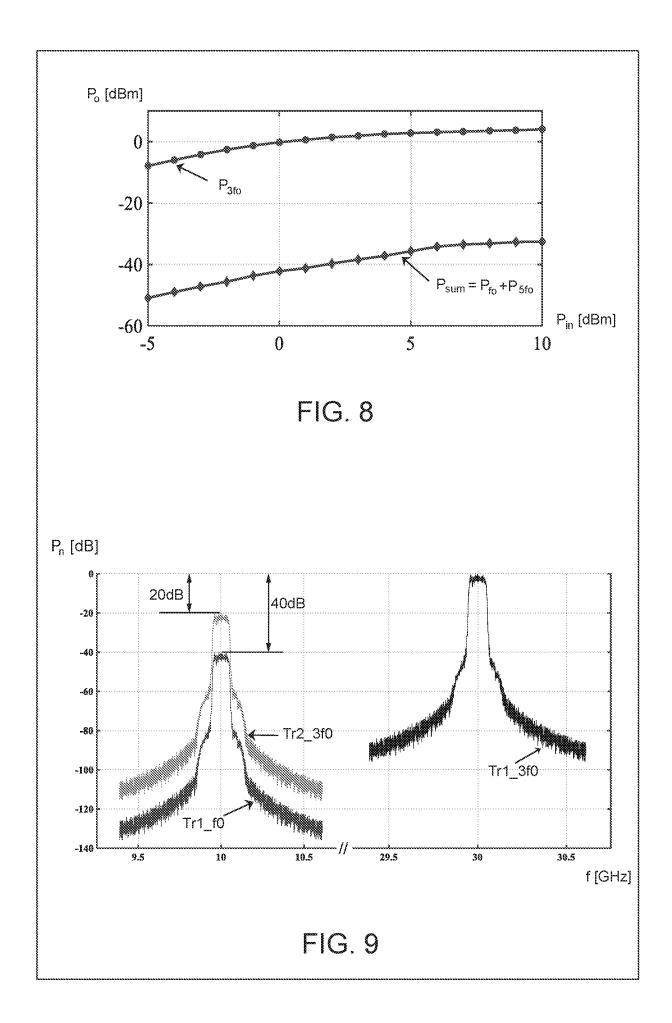

La figura 7 mostra un'implementazione esemplificativa del rilevatore di inviluppo 38 generante la tensione di offset  $V_{\rm OS}$  che soddisfa la condizione (5).

Nell'implementazione specifica mostrata in figura 6, il rilevatore di inviluppo 38 comprende una coppia differenziale di ingresso 70 formata da un quinto e da un sesto transistore Q5 e Q6 e pilotata dalla tensione di ingresso  $V_{\rm in}$ . Un generatore di corrente 71, generante una seconda corrente di riferimento  $2I_{\rm REF}$ , doppia della corrente di riferimento  $I_{\rm REF}$ , è accoppiato ai terminali di emettitore

del quinto e del sesto transistore Q5 e Q6 e ad un filtro mediatore RC 72. Il filtro mediatore RC 72 include un resistore mediatore 72 avente resistenza RE ed è accoppiato ad una prima rete di generazione tensione 75. La prima rete generazione tensione 75 comprende un primo ramo generazione corrente 76 e un primo ramo a specchio corrente 77. Il primo ramo di generazione corrente 76 include un primo generatore di corrente 80 generante una corrente di riferimento IREF e un transistore Q7; il primo ramo a specchio di corrente 77 include un transistore Q8 avente base accoppiata al transistore Q7 del primo ramo di generazione di corrente 76, ha un terminale di collettore formante la prima uscita 37 del rilevatore di inviluppo 38 e genera la prima tensione di polarizzazione Vb1. Una seconda rete di generazione di tensione 81, avente stessa struttura di base della prima rete di generazione di tensione 75, ha transistori Q9 e Q10 accoppiati e genera la seconda tensione di polarizzazione Vb2 in corrispondenza del collettore del transistore Q9 accoppiato alla seconda uscita 50 del rilevatore di inviluppo 38. La seconda rete di generazione di tensione 81 include inoltre un secondo corrente 82 generante la corrente generatore di di riferimento IREF.

Una tensione di alimentazione  $V_{\text{CC}}$  è applicata ai terminali di collettore del quinto e del sesto transistore

Q5 e Q6 e a nodi di alimentazione della prima e della seconda rete di generazione di tensione 75, 81. La tensione di alimentazione  $V_{\rm CC}$  è inoltre applicata ad una presa centrale del secondo trasformatore T2.

Tutti i transistori da Q5 a Q10 nel rilevatore di inviluppo 38 condividono una stessa tensione di polarizzazione V<sub>CM</sub>. In tal modo, i transistori Q5-Q6 (pilotati da |Vin(t)|) e Q7, fanno sì che la tensione  $V_{RE}$ sul resistore di mediatura 73 sia uguale al valore medio di |Vin(t)|. Poiché  $V_{in}(t) = A \sin(2\pi f_0 t)$ , la tensione sul resistore di mediatura 73 è  $V_{RE} = (4/\pi)A$  e la corrente attraverso di esso è  $I_{RE} = (4/\pi) A/R_E$ . I transistori MOSFET M1, M2 nella prima rete di generazione di tensione 75 specchiano la corrente  $I_{REF}$  +  $I_{RE}$  in un primo resistore di uscita 85 (accoppiato alla prima uscita 37 del rilevatore di inviluppo 38) con resistenza R1, mentre i transistori MOSFET M3, M4 nella seconda rete di generazione di tensione 81 specchiano la corrente  $I_{REF}$  in un secondo resistore di uscita 86 con resistenza R2 (accoppiato alla seconda uscita 50 del rilevatore di inviluppo 38). Quindi:

$Vb1 = V_{CC} - (I_{REF} + I_{RE}) \cdot R1$

$Vb2 = V_{CC} - I_{REF} \cdot R2$ .

Assumendo che R1=R2,

$V_{os}$  = Vb2 - Vb1 = R1 · I<sub>RE</sub> = (4/ $\pi$ ) (R1/R<sub>E</sub>)A.

Il rapporto  $R1/R_E$  è progettato in modo tale che  $V_{\rm os}$

soddisfi la condizione (5), consentendo in tal modo di mantenere una buona soppressione della componente di frequenza fondamentale indipendentemente dall'ampiezza del segnale di ingresso.

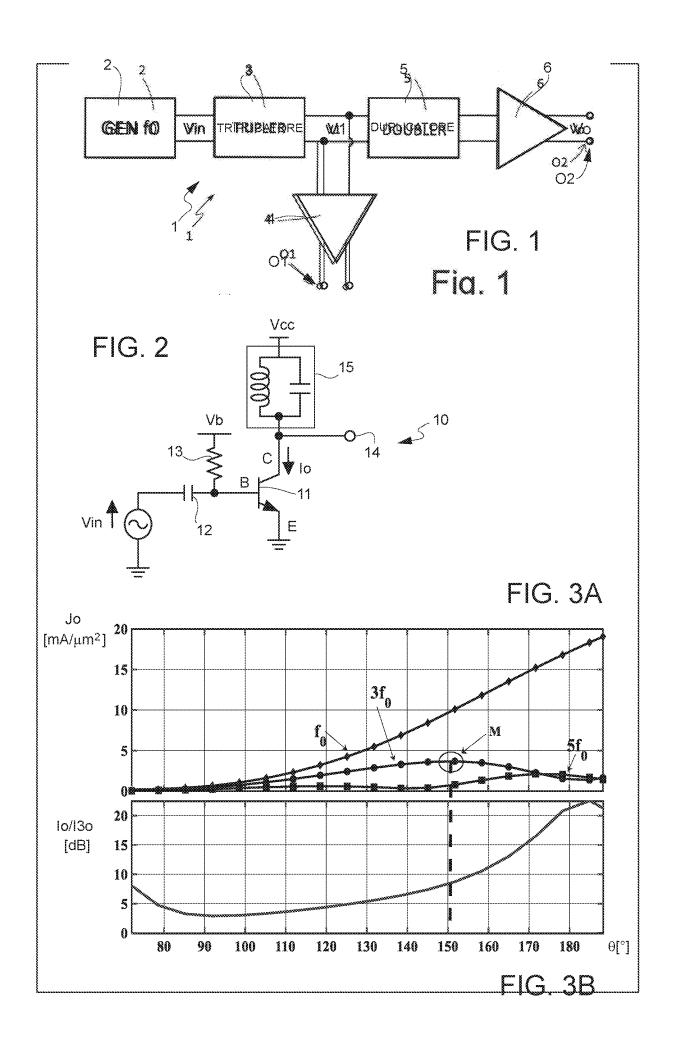

Misure effettuate dalla Richiedente confermano che il circuito triplicatore 20 sopprime quasi completamente la componente alla frequenza fondamentale fo nella corrente di uscita Io. Per esempio, la figura 8 mostra l'andamento della potenza di uscita P<sub>3f0</sub> misurata a 3f0 quando potenza di ingresso Pin è a 12.5 GHz e il tracciato della somma  $P_{sum}$  delle potenze di uscita  $P_{f0}$  (misurata a  $f_0$ ) e  $P_{5f0}$ (misurata in corrispondenza di 5f<sub>0</sub>) ottenuta con triplicatore di frequenza 20. Come si può vedere, nell'intervallo da -5dBm a 10 dBm, la potenza di uscita  $P_{3f0}$ è maggiore della potenza somma  $P_{\text{sum}}$  di circa 40 dBm in quasi l'intero intervallo di potenza di ingresso e in ogni caso mai inferiore a 36 dBm.

Il miglioramento del circuito triplicatore 20 rispetto a un triplicatore convenzionale che utilizza transistori operanti in classe C è inoltre visibile in figura 9, che mostra lo spettro di uscita ottenibile con il presente triplicatore di frequenza 20 (curva  $Tr1_3f0$ ), lo spettro di uscita indesiderato a  $f_0$  ottenibile con un triplicatore convenzionale che utilizza transistori operanti in classe C (curva  $Tr2_f0$ ) e lo spettro di uscita indesiderato a  $f_0$

ottenibile con il presente triplicatore di frequenza 20 (curva Tr1\_f0). Come visibile, la curva Tr1\_f0 è di 20 dB inferiore alla curva Tr2\_f0 e di 40 dB inferiore alla curva Tr1\_3f0.

I vantaggi della presente invenzione sono chiari da quanto sopra. In particolare, si sottolinea che il presente circuito triplicatore è in grado di sopprimere la fondamentale e le armoniche indesiderate in un modo molto migliore rispetto ai circuiti convenzionali.

Il presente circuito triplicatore funziona a bassa potenza rispetto alle soluzioni convenzionali che usano transistori e i filtri in classe C.

Infine, è chiaro che numerose variazioni e modifiche possono essere apportate al circuito elettronico di triplicazione frequenza descritto e illustrato, tutti rientranti nell'ambito di protezione dell'invenzione come definito nelle rivendicazioni allegate.

Per esempio, i transistori bipolari Q1-Q10 potrebbero essere sostituiti da transistori MOSFET; i transistori possono essere realizzati in qualsiasi tecnologia, come ad esempio di silicio, arseniuro di gallio (GaAs), fosfuro di indio (InP), ecc.; la struttura del rilevatore di inviluppo può essere qualsiasi, purché esegua le funzionalità indicate sopra, ottenendo specificatamente la relazione che soddisfa la relazione (5) Vb2 - Vb1 = Vos.

# RIVENDICAZIONI

1. Circuito per triplicare la frequenza, configurato per ricevere una tensione di ingresso ( $V_{in}$ ) avente una forma sinusoidale e una frequenza di base, il circuito comprendendo una prima e una seconda coppia di transistori (Q1-Q4) accoppiate in modo incrociato e avendo transcaratteristica  $f(V_{in})$  approssimante una transcaratteristica nominale polinomiale (1):

$$f(V_{in}) = \left(\frac{3}{A}V_{in} - \frac{4}{A^3}V_{in}^3\right)g_m \quad (1)$$

in cui  $g_{\text{m}}$  è una transconduttanza di transistori della prima e della seconda coppia di transistori.

2. Circuito secondo la rivendicazione 1, in cui:

la prima coppia di transistori comprende un primo e un secondo transistore (Q1, Q2) aventi rispettivi primi e secondi terminali di conduzione e un rispettivo terminale di controllo,

la seconda coppia di transistori comprende un terzo e un quarto transistore (Q3, Q4) aventi rispettivi primi e secondi terminali di conduzione e un rispettivo terminale di controllo;

il circuito comprende inoltre un primo, un secondo, un terzo e un quarto nodo di ingresso (22, 23, 27, 28) e una prima e una seconda uscita (24, 25),

in cui i primi terminali di conduzione del primo, del secondo, del terzo e del quarto transistore sono accoppiati

insieme,

i secondi terminali di conduzione del primo (Q1) e del quarto (Q4) transistore sono accoppiati insieme e alla prima uscita (24),

i secondi terminali di conduzione del secondo (Q2) e del terzo (Q3) transistore sono accoppiati insieme e alla seconda uscita (25),

il terminale di controllo del primo transistore (Q1) è accoppiato al primo nodo di ingresso (22) e configurato per ricevere una prima frazione (1/2) della prima tensione di ingresso ( $V_{in}$ ) diminuita di un valore di offset ( $V_{os}$ ),

il terminale di controllo del secondo transistore (Q2) è accoppiato al secondo nodo di ingresso (23) e configurato per ricevere una controfase della prima frazione della tensione di ingresso ( $V_{in}$ ) diminuita del valore di offset ( $V_{os}$ ),

il terminale di controllo del terzo transistore (Q3) è accoppiato al terzo nodo di ingresso (27) e configurato per ricevere una seconda frazione ( $\alpha$   $V_{in}/2$ ) della tensione di ingresso, e

il terminale di controllo del quarto transistore (Q4) è accoppiato al quarto nodo di ingresso (28) e configurato per ricevere una controfase della seconda frazione della tensione di ingresso.

3. Circuito secondo la rivendicazione 2, in cui la

prima frazione è ½.

- 4. Circuito secondo la rivendicazione 2 o 3, in cui la seconda frazione ( $\alpha$ ) è selezionata in modo tale che la transcaratteristica del circuito  $f(V_{in})$  e la transcaratteristica nominale polinomiale abbiano le stesse pendenze in corrispondenza degli attraversamenti di zero.

- 5. Circuito secondo una qualsiasi delle rivendicazioni 2-4, in cui la seconda frazione ( $\alpha$ ) è compresa tra 0,1 e 0,35.

- 6. Circuito secondo una qualsiasi delle rivendicazioni 2-4, in cui la seconda frazione ( $\alpha$ ) è 0,2.

- 7. Circuito secondo una qualsiasi delle rivendicazioni 2-6, in cui la tensione di offset  $(V_{\rm os})$  soddisfa la condizione:

$$\frac{2V_{OS}}{(1-\alpha)} = \frac{\sqrt{3}}{2}A$$

in cui A è l'ampiezza della tensione di ingresso.

- 8. Circuito secondo una qualsiasi delle rivendicazioni 2-7, comprendente inoltre un rilevatore di inviluppo (38) accoppiato al primo e al secondo nodo di ingresso (22, 23) e generante una tensione di offset  $(V_{\rm os})$ .

- 9. Circuito secondo una qualsiasi delle rivendicazioni 1-4, comprendente inoltre:

un trasformatore di ingresso (T1) avente un primario (31) accoppiato tra un primo e un secondo ingresso circuitale (32, 33) e un secondario (35) accoppiato tra il

primo e il secondo nodo di ingresso (22, 23), il trasformatore secondario avendo una presa centrale (36); e

una rete a divisore (40) accoppiata tra il primo e il secondo nodo di ingresso e avente una presa centrale (50),

in cui il rilevatore di inviluppo (38) comprende un primo nodo di uscita (37) accoppiato alla presa centrale (36) del secondario (35) del trasformatore di ingresso (T1) e un secondo nodo di uscita (50) accoppiato alla presa centrale della rete a divisore (40).

10. Circuito secondo la rivendicazione 9, in cui la rete a divisore (40) comprende un primo e un secondo ramo (41, 42), il primo ramo (41) della rete a divisore (40) includendo un primo e un secondo resistore (46, 47) e un primo e un secondo condensatore (45, 48), il primo condensatore (45) avendo un primo terminale accoppiato al ingresso (22) secondo terminale nodo di е un accoppiato al primo resistore (46) e al terzo nodo di ingresso (27), il secondo condensatore avendo un primo terminale accoppiato al secondo ingresso circuitale (23) e un secondo terminale accoppiato al secondo resistore (47) e al quarto nodo di ingresso (28), il primo e il secondo resistore (46, 47) essendo accoppiati insieme alla presa centrale (50) della rete a divisore (40), il secondo ramo (42) comprendendo un terzo condensatore (54) accoppiato tra il terzo e il quarto nodo di ingresso (27, 28).

11. Metodo per triplicare la frequenza, comprendente:

ricevere una tensione di ingresso ( $V_{in}$ ) avente una forma sinusoidale e una frequenza di base;

applicare la tensione di ingresso a un circuito triplicatore (20) comprendente una prima e una seconda coppia di transistori (Q1-Q4) accoppiate in modo incrociato e avente transcaratteristica  $f(V_{in})$  approssimante una transcaratteristica nominale polinomiale (1):

$$f(V_{in}) = \left(\frac{3}{A}V_{in} - \frac{4}{A^3}V_{in}^3\right)g_m \quad (1)$$

in cui  $g_m$  è una transconduttanza di transistori della prima e della seconda coppia di transistori; e

generare una corrente di uscita avente una forma sinusoidale e una frequenza di uscita che è un triplo della frequenza di base.

12. Metodo secondo la rivendicazione 11, in cui:

la prima coppia di transistori comprende un primo e un secondo transistore (Q1, Q2) aventi rispettivi primi e secondi terminali di conduzione e un rispettivo terminale di controllo, e la seconda coppia di transistori comprende un terzo e un quarto transistore (Q3, Q4) aventi rispettivi primi e secondi terminali di conduzione e un rispettivo terminale di controllo,

in cui applicare la tensione di ingresso comprende:

accoppiare il primo terminale di conduzione del primo,

del secondo, del terzo e del quarto transistore ad un nodo

# comune (21);

accoppiare il secondo terminale di conduzione del primo e del quarto transistore ad un primo nodo di uscita (25);

accoppiare un secondo terminale di conduzione del secondo e del terzo transistore ad un secondo nodo di uscita (24);

applicare una prima frazione (1/2) della tensione di ingresso diminuita di un valore di sbilanciamento ( $V_{\rm os}$ ) al terminale di controllo del primo transistore (Q1),

applicare una controfase della prima frazione della tensione di ingresso diminuita di un valore di sbilanciamento ( $V_{os}$ ) al terminale di controllo del secondo transistore (Q2);

applicare una seconda frazione ( $\alpha V_{in}/2$ ) della tensione di ingresso al terminale di controllo del terzo transistore (Q3);

applicare una controfase della seconda frazione  $(\alpha V_{\rm in}/2) \ \ \mbox{della tensione di ingresso a un terminale di controllo del quarto transistore (Q4);}$

e in cui generare una corrente di uscita comprende generare una prima corrente SINGLE-ENDED in corrispondenza del primo nodo di uscita (24) e generare una seconda corrente SINGLE ENDED in corrispondenza del secondo nodo di uscita (25).

- 13. Metodo secondo la rivendicazione 12, in cui la prima frazione è ½ e la seconda frazione ( $\alpha/2$ ) è selezionata in modo tale che le trans-caratteristiche  $f(V_{in})$  e la transcaratteristica nominale polinomiale abbiano le stesse pendenze.

- 14. Metodo secondo la rivendicazione 12 o 13, in cui la seconda frazione ( $\alpha$ ) è compresa tra 0,1 e 0,35, ed è in particolare 0,2.

- 15. Metodo secondo una qualsiasi delle rivendicazioni 12-14, in cui la tensione di offset soddisfa la condizione:

$$\frac{2\,V_{OS}}{(1-\alpha)} = \frac{\sqrt{3}}{2}\,A$$

in cui A è l'ampiezza della tensione di ingresso.

16. Metodo secondo una qualsiasi delle rivendicazioni da 12 a 15, comprendente inoltre rilevare l'ampiezza (A) della tensione di ingresso e generare la tensione di offset  $V_{\rm OS}$ .

FIG. 5