(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4187021号

(P4187021)

(45) 発行日 平成20年11月26日(2008.11.26)

(24) 登録日 平成20年9月19日(2008.9.19)

|                          |                    |

|--------------------------|--------------------|

| (51) Int.Cl.             | F 1                |

| HO 1 L 21/8246 (2006.01) | HO 1 L 27/10 4 4 7 |

| HO 1 L 27/105 (2006.01)  | HO 1 L 43/08 P     |

| HO 1 L 43/08 (2006.01)   | HO 1 L 43/08 Z     |

| HO 1 L 43/10 (2006.01)   | HO 1 L 43/10       |

| HO 1 L 29/82 (2006.01)   | HO 1 L 29/82 Z     |

請求項の数 10 (全 19 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2006-222046 (P2006-222046)  |

| (22) 出願日     | 平成18年8月16日 (2006.8.16)        |

| (65) 公開番号    | 特開2007-180487 (P2007-180487A) |

| (43) 公開日     | 平成19年7月12日 (2007.7.12)        |

| 審査請求日        | 平成18年11月30日 (2006.11.30)      |

| (31) 優先権主張番号 | 特願2005-349790 (P2005-349790)  |

| (32) 優先日     | 平成17年12月2日 (2005.12.2)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                         |

|-----------|-----------------------------------------|

| (73) 特許権者 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号  |

| (74) 代理人  | 100122884<br>弁理士 角田 芳末                  |

| (74) 代理人  | 100133824<br>弁理士 伊藤 仁恭                  |

| (72) 発明者  | 細見 政功<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内 |

| (72) 発明者  | 鹿野 博司<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内 |

最終頁に続く

(54) 【発明の名称】記憶素子及びメモリ

## (57) 【特許請求の範囲】

## 【請求項 1】

積層方向に電流を流すことにより、情報を磁性体の磁化状態により保持する記憶層の磁化の向きが変化して、前記記憶層に対して情報の記録が行われる記憶素子であって、

前記記憶層と、

中間層と、

前記記憶層に対して、前記中間層を介して設けられて、前記記憶層及び前記中間層とにより積層膜を形成する磁化固定層とを有し、

前記積層膜のうち、少なくとも前記記憶層において、平面パターンの長軸の端部の曲率半径 R が、31 nm R 90 nm を満足する

記憶素子。

## 【請求項 2】

前記中間層が酸化マグネシウムから成る請求項 1 に記載の記憶素子。

## 【請求項 3】

前記曲率半径 R と、前記平面パターンの短軸の長さ W とが、R W / 2 の関係を満足し、前記平面パターンの短軸の長さ W が 175 nm 以下である請求項 1 に記載の記憶素子。

## 【請求項 4】

前記平面パターンは、長軸の長さ L と短軸の長さ W の比であるアスペクト比が 1 . 5 以上、4 . 0 以下である請求項 1 に記載の記憶素子。

## 【請求項 5】

10

20

前記曲率半径 R と、前記平面パターンの長軸の長さ L とが、 $L / 24 \leq R$  の関係を満たす請求項 4 に記載の記憶素子。

**【請求項 6】**

互いに交差する 2 種類の配線を備え、

前記 2 種類の配線の交点付近かつ前記 2 種類の配線の間に配置され、積層方向に電流を流すことにより、情報を磁性体の磁化状態により保持する記憶層の磁化の向きが変化して、前記記憶層に対して情報の記録が行われる構成であり、前記 2 種類の配線を通じて、前記記憶素子に前記積層方向の電流が流れ、前記記憶層と、中間層と、前記記憶層に対して、前記中間層を介して設けられて、前記記憶層及び前記中間層とにより積層膜を形成する磁化固定層とを有し、前記積層膜のうち、少なくとも前記記憶層において、平面パターンの長軸の端部の曲率半径 R が、 $31 \text{ nm} \leq R \leq 90 \text{ nm}$  を満足する記憶素子を備えたメモリ。

10

**【請求項 7】**

前記記憶素子の前記中間層が酸化マグネシウムから成る請求項 6 に記載のメモリ。

**【請求項 8】**

前記記憶素子は、前記曲率半径 R と、前記平面パターンの短軸の長さ W とが、 $R \leq W / 2$  の関係を満足し、前記平面パターンの短軸の長さ W が  $175 \text{ nm}$  以下である請求項 6 に記載のメモリ。

**【請求項 9】**

記憶素子の前記平面パターンは、長軸の長さ L と短軸の長さ W の比であるアスペクト比が  $1.5$  以上、 $4.0$  以下である請求項 6 に記載のメモリ。

20

**【請求項 10】**

前記記憶素子は、前記曲率半径 R と、前記平面パターンの長軸の長さ L とが、 $L / 24 \leq R$  の関係を満たす請求項 9 に記載のメモリ。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、電流を流すことにより記憶層の磁化の向きを変化させる記憶素子及びこの記憶素子を有するメモリに係わり、不揮発性メモリに適用して好適なものである。

**【背景技術】**

30

**【0002】**

コンピュータ等の情報機器では、ランダム・アクセス・メモリとして、動作が高速で、高密度な D R A M が広く使われている。

しかし、D R A M は電源を切ると情報が消えてしまう揮発性メモリであるため、情報が消えない不揮発のメモリが望まれている。

**【0003】**

そして、不揮発メモリの候補として、磁性体の磁化で情報を記録する磁気ランダム・アクセス・メモリ (M R A M) が注目され、開発が進められている（例えば非特許文献 1 参照）。

**【0004】**

40

M R A M は、ほぼ直交する 2 種類のアドレス配線（ワード線、ビット線）にそれぞれ電流を流して、各アドレス配線から発生する電流磁場によって、アドレス配線の交点にある磁気記憶素子の磁性層の磁化を反転して情報の記録を行うものである。

また、情報の読み出には、磁気記憶素子の記憶層の磁化の向きに応じて抵抗が変化する、いわゆる磁気抵抗効果 (M R 效果) を用いる。

**【0005】**

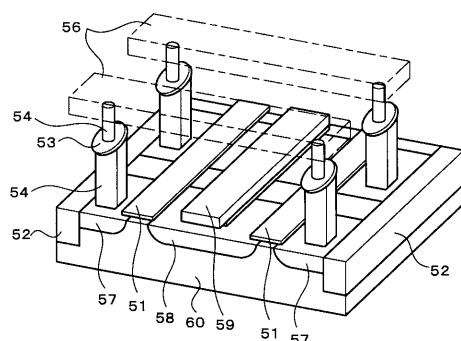

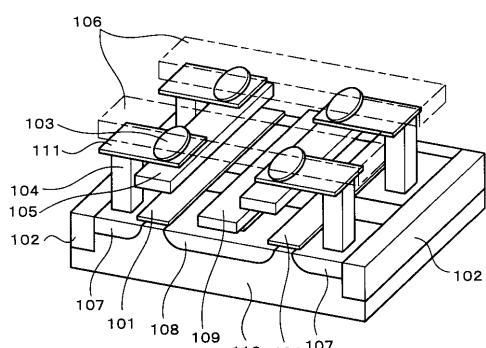

ここで、一般的な M R A M の模式図（斜視図）を、図 12 に示す。

シリコン基板等の半導体基体 110 の素子分離層 102 により分離された部分に、各メモリセルを選択するための選択用トランジスタを構成する、ドレイン領域 108、ソース領域 107、並びにゲート電極 101 が、それぞれ形成されている。

50

また、ゲート電極 101 の上方には、図中前後方向に延びるワード線 105 が設けられている。

ドレイン領域 108 は、図中左右の選択用トランジスタに共通して形成されており、このドレイン領域 108 には、配線 109 が接続されている。

そして、ワード線 105 と、上方に配置された、図中左右方向に延びるビット線 106 との間に、磁化の向きが反転する記憶層を有する磁気記憶素子 103 が配置されている。この磁気記憶素子 103 は、例えば磁気トンネル接合素子（MTJ 素子）により構成される。

さらに、磁気記憶素子 103 は、水平方向のバイパス線 111 及び上下方向のコンタクト層 104 を介して、ソース領域 107 に電気的に接続されている。

ワード線 105 及びビット線 106 にそれぞれ電流を流すことにより、電流磁界を磁気記憶素子 103 に印加して、これにより磁気記憶素子 103 の記憶層の磁化の向きを反転させて、情報の記録を行うことができる。

#### 【0006】

そして、MRAM 等の磁気メモリにおいて、記録した情報を安定に保持するためには、情報を記録する磁性層（記憶層）が、一定の保磁力を有していることが必要である。

一方、記録された情報を書き換えるためには、アドレス配線にある程度の電流を流さなければならない。

ところが、MRAM を構成する素子の微細化に従い、磁化の向きを反転させる電流値が増大する傾向を示す反面、アドレス配線も細くなるため、充分な電流が流せなくなってくる。

#### 【0007】

そこで、より少ない電流で磁化反転が可能な構成として、スピン注入による磁化反転を利用する構成の磁気メモリが注目されている（例えば、特許文献 1 参照）。

スピン注入による磁化反転とは、磁性体の中を通過してスピン偏極した電子を、他の磁性体に注入することにより、他の磁性体において磁化反転を起こさせるものである。

#### 【0008】

例えば、巨大磁気抵抗効果素子（GMR 素子）や磁気トンネル接合素子（MTJ 素子）に対して、その膜面に垂直な方向に電流を流すことにより、これらの素子の少なくとも一部の磁性層の磁化の向きを反転させることができる。

#### 【0009】

そして、スピン注入による磁化反転は、素子が微細化されても、少ない電流で磁化反転を実現することができる利点を有している。

#### 【0010】

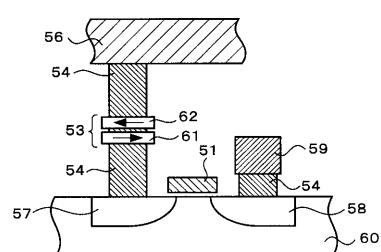

また、上述したスピン注入による磁化反転を利用する構成の磁気メモリの模式図を図 10 及び図 11 に示す。図 10 は斜視図、図 11 は断面図である。

シリコン基板等の半導体基体 60 の素子分離層 52 により分離された部分に、各メモリセルを選択するための選択用トランジスタを構成する、ドレイン領域 58、ソース領域 57、並びにゲート電極 51 が、それぞれ形成されている。このうち、ゲート電極 51 は、図 10 中前後方向に延びるワード線を兼ねている。

ドレイン領域 58 は、図 10 中左右の選択用トランジスタに共通して形成されており、このドレイン領域 58 には、配線 59 が接続されている。

そして、ソース領域 57 と、上方に配置された、図 10 中左右方向に延びるビット線 56 との間に、スピン注入により磁化の向きが反転する記憶層を有する記憶素子 53 が配置されている。

この記憶素子 53 は、例えば磁気トンネル接合素子（MTJ 素子）により構成される。図中 61 及び 62 は磁性層を示しており、2 層の磁性層 61、62 のうち、一方の磁性層を磁化の向きが固定された磁化固定層として、他方の磁性層を磁化の向きが変化する磁化自由層即ち記憶層とする。

また、記憶素子 53 は、ビット線 56 と、ソース領域 57 とに、それぞれ上下のコンタ

10

20

30

40

50

クト層 5 4 を介して接続されている。これにより、記憶素子 5 3 に電流を流して、スピニ注入により記憶層の磁化の向きを反転させることができる。

#### 【 0 0 1 1 】

このようなスピニ注入による磁化反転を利用する構成のメモリの場合、図 1 2 に示した一般的な M R A M と比較して、電流磁界発生用の配線（図 1 2 の 1 0 5 ）が不要となるため、デバイス構造を単純化することができる、という特徴も有している。

また、スピニ注入による磁化反転を利用することにより、外部磁界により磁化反転を行う一般的な M R A M と比較して、素子の微細化が進んでも、書き込みの電流が増大しないという利点がある。

#### 【 0 0 1 2 】

【非特許文献 1】日経エレクトロニクス 2 0 0 1 . 2 . 1 2 号（第 1 6 4 頁 - 1 7 1 頁）

【特許文献 1】特開 2 0 0 3 - 1 7 7 8 2 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【 0 0 1 3 】

ところで、M R A M の場合は、記憶素子とは別に書き込み配線（ワード線やビット線）を設けて、書き込み配線に電流を流して発生する電流磁界により、情報の書き込み（記録）を行っている。そのため、書き込み配線に、書き込みに必要となる電流量を充分に流すことができる。

#### 【 0 0 1 4 】

一方、スピニ注入を利用する構成のメモリにおいては、記憶素子に流す電流によりスピニ注入を行って、記憶層の磁化の向きを反転させる必要がある。

そして、このように記憶素子に直接電流を流して情報の書き込み（記録）を行うことから、書き込みを行うメモリセルを選択するために、記憶素子を選択トランジスタと接続してメモリセルを構成する。この場合、記憶素子に流れる電流は、選択トランジスタに流すことが可能な電流（選択トランジスタの飽和電流）の大きさに制限される。

このため、選択トランジスタの飽和電流以下の電流で書き込みを行う必要があり、スピニ注入の効率を改善して、記憶素子に流す電流を低減する必要がある。

#### 【 0 0 1 5 】

また、読み出し信号を大きくするためには、大きな磁気抵抗変化率を確保する必要があり、そのためには、記憶層の両側に接している中間層をトンネル絶縁層（トンネルバリア層）とした記憶素子の構成にすることが効果的である。

このように中間層としてトンネル絶縁層を用いた場合には、トンネル絶縁層が絶縁破壊することを防ぐために、記憶素子に流す電流量に制限が生じる。この観点からも、スピニ注入時の電流を抑制する必要がある。

#### 【 0 0 1 6 】

従って、スピニ注入により記憶層の磁化の向きを反転させる構成の記憶素子では、スピニ注入効率を改善して、必要とする電流を減らす必要がある。

#### 【 0 0 1 7 】

スピニ注入により記憶層の磁化の向きを反転させるために必要となる、書き込み電流閾値は、例えば、記憶層に厚さが 2 n m の C o F e B 合金を使用し、平面パターンが 1 3 0 n m × 1 0 0 n m の略楕円形の巨大磁気抵抗効果素子（G M R 素子）において、+ 側の閾値 + I c = + 0 . 6 m A であり、- 側の閾値 - I c = - 0 . 2 m A である。また、このときの電流密度は約  $6 \times 1 0 ^ 6$  A / cm<sup>2</sup> である（屋上他著、日本応用磁気学会誌、Vol. 28, No. 2, p. 149, 2004 年参照）。

また、例えば、強磁性層として一般的な C o F e を記憶層の材料に使用した場合、磁化反転を生じさせるためには、およそ  $1 \times 1 0 ^ 7$  A / cm<sup>2</sup> 程度の電流密度が必要である。

そして、電流密度が上述した値のときに、例えば記憶素子の大きさが 9 0 n m × 1 3 0

10

20

30

40

50

$n\text{m}$ であるとすると、書き込み電流閾値は、およそ  $550 \mu\text{A}$  となる。

#### 【0018】

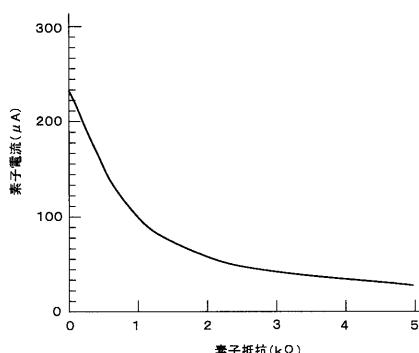

ここで、S P I C E シミュレータによる一般的な選択トランジスタと記憶素子とを接続した場合に、記憶素子の素子抵抗と記憶素子に流れる素子電流との関係を図13に示す。

読み出し信号の大きさを考えると、素子抵抗は大きいほど良いが、図13より、素子抵抗を大きくすると記憶素子に流せる電流が小さくなってしまう。

そして、読み出し特性を充分に確保する上で下限と推定される素子抵抗  $2.5\text{k}\Omega$  の場合を考えると、図13より、記憶素子に流せる電流の上限は約  $400 \mu\text{A}$  となることから、上述した値からさらに書き込み電流閾値を  $30\%$  以上低減させなくてはならないことになる。

10

このため、読み出し特性を充分に確保するためには、さらに書き込み電流閾値を低減することが求められる。

#### 【0019】

さらに、書き込み電流閾値を減少させるためには、記憶層の体積及び飽和磁化ができる限り小さくすることが望ましい。

ところが、記憶層の体積及び飽和磁化を小さくすると、記憶素子の熱安定性が減少し、動作が不安定になるという問題点があった。

#### 【0020】

上述した問題の解決のために、本発明においては、情報を安定して保持することができる記憶素子及びこの記憶素子を備えたメモリを提供するものである。

20

#### 【課題を解決するための手段】

#### 【0021】

本発明の記憶素子は、積層方向に電流を流すことにより、情報を磁性体の磁化状態により保持する記憶層の磁化の向きが変化して、この記憶層に対して情報の記録が行われる記憶素子であって、記憶層と、中間層と、記憶層に対して、中間層を介して設けられて、記憶層及び中間層とにより積層膜を形成する磁化固定層とを有し、積層膜のうち、少なくとも記憶層において、平面パターンの長軸の端部の曲率半径 R が、 $31\text{nm} \leq R \leq 90\text{nm}$  を満足するものである。

本発明のメモリは、互いに交差する 2 種類の配線を備え、この 2 種類の配線の交点付近かつ 2 種類の配線の間に配置され、積層方向に電流を流すことにより、情報を磁性体の磁化状態により保持する記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる構成であり、2 種類の配線を通じて、記憶素子に積層方向の電流が流れ、上記本発明の記憶素子の構成の記憶素子を備えたものである。

30

#### 【0022】

上述の本発明の記憶素子の構成によれば、情報を磁性体の磁化状態により保持する記憶層を有し、この記憶層に対して、中間層を介して磁化固定層が設けられて積層膜が形成され、積層方向に電流を流すことにより、記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われるので、積層方向に電流を流すことによって情報の記録を行うことができる。このとき、積層方向に電流を流すことにより、スピン偏極した電子が注入され、前述したスピン注入による情報の記録が行われる。

40

また、記憶素子を構成する積層膜のうち、少なくとも記憶層において、平面パターンの長軸の端部の曲率半径 R が、 $31\text{nm} \leq R \leq 90\text{nm}$  を満足することにより、記憶層の保磁力を大きくすることができる。これにより、記憶層の熱等に対する安定性を向上させることができるため、記憶層に記録された情報を安定して保持することができる。

#### 【0023】

上述の本発明のメモリの構成によれば、互いに交差する 2 種類の配線を備え、情報を磁性体の磁化状態により保持する記憶層を有する記憶素子を備え、記憶素子は上記本発明の記憶素子の構成であり、2 種類の配線の交点付近かつ 2 種類の配線の間に記憶素子が配置され、これら 2 種類の配線を通じて記憶素子に積層方向の電流が流れるものであることにより、2 種類の配線を通じて記憶素子の積層方向に電流を流してスピン注入による情報の

50

記録を行うことができる。

また、記憶素子の記憶層に記録された情報を安定して保持することができる。

#### 【発明の効果】

##### 【0024】

上述の本発明によれば、記憶素子の記憶層が熱等に対して充分な安定性を有するため、記憶素子が情報の保持特性に優れている。

従って、安定して動作する、信頼性の高いメモリを実現することができる。

##### 【0025】

また、記憶層が充分な安定性を有することから、記憶素子のパターンを小さくして微細化を図っても、情報を安定して保持することが可能になる。 10

記憶素子の微細化により、記憶素子を用いたメモリの集積化を進めて、メモリの小型化や記憶容量の増大を図ることが可能になる。

さらにまた、記憶素子の微細化により、前述したように、スピン注入により情報の記録を行う場合の、記憶層の磁化の向きを反転させるために必要となる書き込み電流閾値も小さくすることが可能になる。これにより、情報の記録に必要な電流量を低減することができるため、メモリ全体の消費電力を低減して、従来にない低消費電力のメモリを実現することが可能になる。

#### 【発明を実施するための最良の形態】

##### 【0026】

まず、本発明の具体的な実施の形態の説明に先立ち、本発明の概要について説明する。 20

本発明は、前述したスピン注入により、記憶素子の記憶層の磁化の向きを反転させて、情報を記録を行うものである。記憶層は、強磁性層等の磁性体により構成され、情報を磁性体の磁化状態（磁化の向き）により保持するものである。

##### 【0027】

スピン注入により磁性層の磁化の向きを反転させる基本的な動作は、巨大磁気抵抗効果素子（GMR素子）もしくはトンネル磁気抵抗効果素子（MTJ素子）から成る記憶素子に対して、その膜面に垂直な方向に、ある閾値以上の電流を流すものである。このとき、電流の極性（向き）は、反転させる磁化の向きに依存する。

この閾値よりも絶対値が小さい電流を流した場合には、磁化反転を生じない。

##### 【0028】

スピン注入によって、磁性層の磁化の向きを反転させるときに、必要となる電流の閾値（書き込み電流閾値） $I_c$ は、現象論的に、下記の式1により表される（J. Z. Sun, Phys. Rev. B, Vol. 62, p. 570, 2000年参照）。

##### 【0029】

##### 【数1】

$$I_c = \frac{1}{\eta} \left( \frac{2e}{h} \right) \frac{\alpha}{|\cos \phi|} (\alpha^2 l_m H_k M_s) \left( 1 + \frac{2\pi M_s}{H_k} + \frac{H}{H_k} \right) \quad (式1)$$

（ただし、 $\eta$ ：記憶層のダンピング定数、 $H_k$ ：記憶層の面内一軸異方性磁界、 $M_s$ ：記憶層の飽和磁化、 $\alpha$ ：スピン注入係数、 $a$ ：記憶層の半径、 $l_m$ ：記憶層の厚さ、 $H$ ：外部印加磁界） 40

##### 【0030】

書き込み閾値電流 $I_c$ を低減するためには、上記式1中の各種パラメータを調整すれば良いことになる。

一方、メモリとしての性能を維持するという観点から、上記各種パラメータが制約される。例えば、式1中の $(\alpha^2 l_m H_k M_s)$ の項は、熱ゆらぎを決定する項として知られており、書き込み閾値電流 $I_c$ のばらつきを抑えて、書き込んだデータの長期安定性を確保するためには、一定以上の値を保たなければならず、ある一定値以下に小さくすることはできない。このため、記憶素子の大きさや記憶層の厚さ $l_m$ ・飽和磁化 $M_s$ には下限が 50

存在し、これらのパラメータを減少させることにより書き込み電流を低減させる手法は、ある所で限界となる。

#### 【0031】

そこで、本発明では、記憶層の平面パターンを工夫することにより、書き込んだデータの長期安定性を確保するものである。そして、書き込み閾値電流  $I_c$  を低減することも可能にするものである。

#### 【0032】

即ち、本発明では、磁性体の磁化の向き（磁化状態）を情報として保持する記憶層を有し、記憶層に対して、中間層（絶縁層又は非磁性導電層）を介して磁化の向きが固定された磁化固定層を設けて、これら各層を含む積層膜を形成して、記憶素子を構成する。

また、積層方向に電流を流すことにより、前述したスピン注入により、記憶層を構成する磁性体の磁化の向きを反転させて、記憶層に対して情報の記録を行う。

そして、記憶素子を構成する積層膜のうち、少なくとも記憶層において、平面パターンの長軸の端部の曲率半径  $R$  が、 $31\text{ nm} \leq R \leq 90\text{ nm}$ を満足する構成とする。

これにより、記憶層の保磁力  $H_c$  が大きくなり、記憶層の熱等に対する安定性を向上させることができるために、記憶層に記録された情報を安定して保持することができる。

#### 【0033】

また、記憶層が充分な安定性を有することから、記憶素子のパターンを小さくして微細化を図っても、情報を安定して保持することが可能になる。

記憶素子の微細化により、記憶素子を用いたメモリの集積化を進めて、メモリの小型化や記憶容量の増大を図ることが可能になる。

さらにまた、記憶素子の微細化により、前述したように、スピン注入により情報の記録を行う場合の、記憶層の磁化の向きを反転させるために必要となる書き込み電流閾値も小さくすることが可能になる。

#### 【0034】

なお、曲率半径  $R$  が小さくなることにより、上述の熱ゆらぎを決定する項において、記憶層の半径  $a$  が小さくなると考えられるが、その一方で記憶層の面内一軸異方性磁界  $H_k$  が増大するため、熱ゆらぎを決定する項の大きさを保つことが可能である。そして、上述の式からわかるように、面内一軸異方性磁界  $H_k$  が増大することによっても、書き込み電流閾値を小さくすることが可能である。

#### 【0035】

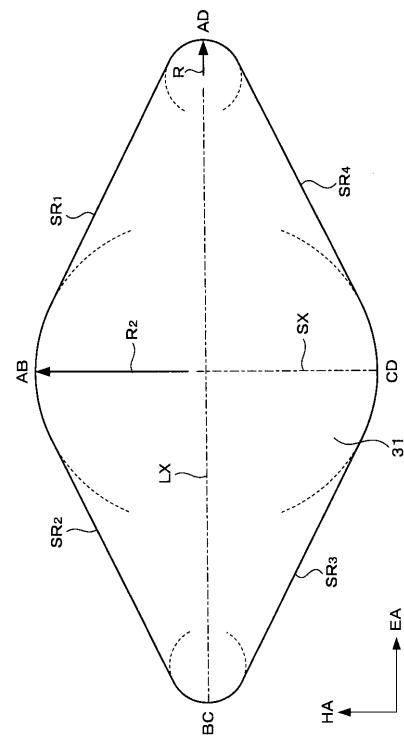

ここで、記憶素子の記憶層の平面パターンの各形態を、それぞれ図2～図4に示す。

#### 【0036】

図2に示す形態では、記憶素子の記憶層の平面パターン31が、4辺  $SR_1, SR_2, SR_3, SR_4$  を有する菱形疑似形状から成る。尚、各辺  $SR_1, SR_2, SR_3, SR_4$  は、記憶層の平面パターン31と菱形疑似形状の長軸  $LX$ （一点鎖線で表す）との交点  $BC, AD$  及び記憶層の平面パターン31と菱形疑似形状の短軸  $SX$ （一点鎖線で表す）との交点  $AB, CD$  を結んでいる。

そして、菱形疑似形状を構成する4つの辺  $SR_1, SR_2, SR_3, SR_4$  は、その中央部に直線部分を有している。

また、このような平面パターン31において、記憶層の磁化容易軸  $EA$  は、菱形疑似形状の長軸  $LX$  と略平行であり、記憶層の磁化困難軸  $HA$  は、菱形疑似形状の短軸  $SX$  と略平行である。

平面パターン31は、菱形疑似形状の長軸  $LX$  及び短軸  $SX$  に関して略線対称である。

そして、平面パターン31は、長軸  $LX$  の端部（交点  $AD$  及び  $BC$  の近傍）及び短軸  $SX$  の端部（交点  $AB$  及び  $CD$  の近傍）において外形が曲線形状となっており、4辺  $SR_1, SR_2, SR_3, SR_4$  の直線部分によって、曲線形状の部分が滑らかに結ばれている。

また、長軸  $LX$  の端部の曲率半径  $R$  は、短軸  $SX$  の端部の曲率半径  $R_2$  と比較して、充分に小さくなっている（ $R < R_2$ ）。

10

20

30

40

50

## 【0037】

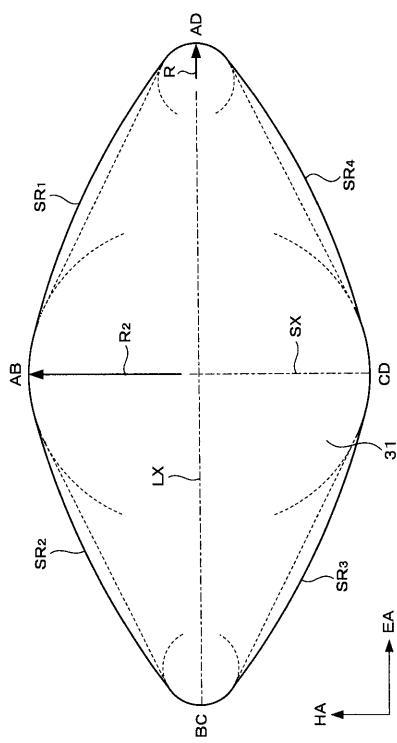

図2では、平面パターン31が菱形擬似形状となっており、その4辺SR<sub>1</sub>, SR<sub>2</sub>, SR<sub>3</sub>, SR<sub>4</sub>の中央部が直線部分となっていたが、図3に示すように、菱形疑似形状を構成する4辺SR<sub>1</sub>, SR<sub>2</sub>, SR<sub>3</sub>, SR<sub>4</sub>が、外側に向かって、中央部が湾曲した滑らかな曲線から成る構成とすることもできる。

平面パターン31を図3に示す形状とした場合には、長軸LXの端部（交点AD及びBCの近傍）及び短軸SXの端部（交点AB及びCDの近傍）では、図2に示した形状と、曲率半径R<sub>1</sub>, R<sub>2</sub>の大きさが等しくなっている。ただし、曲率半径R<sub>3</sub>, R<sub>4</sub>の曲線形状の部分が図2に示した形状よりも狭くなっている。

## 【0038】

10

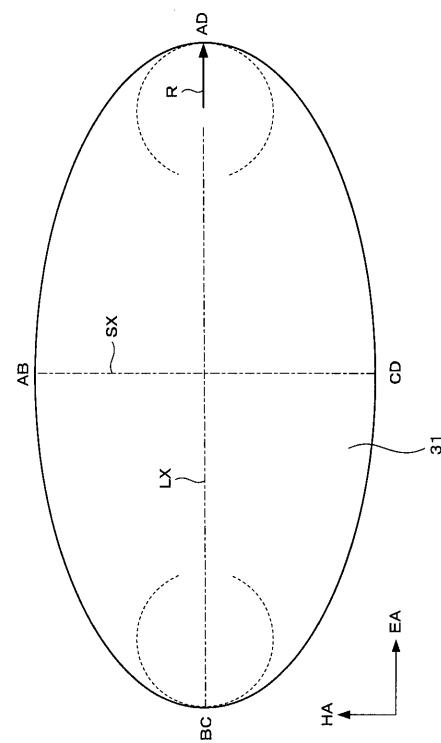

図4に示す形状は、平面パターン31をさらに膨らませて、菱形擬似形状から略橍円形状に変化させたものである。

このように平面パターン31を略橍円形状とすると、長軸LXの端部及び短軸SXの端部が緩やかな曲面形状となる。このため、長軸LX及び短軸SXが等しいもので、菱形擬似形状と比較すると、長軸LXの端部及び短軸SXの端部の曲率半径R<sub>1</sub>, R<sub>2</sub>が共に大きくなる。

## 【0039】

本発明においては、図2～図4に示したいずれの形状とする場合でも、記憶層の平面パターン31の長軸LXの端部の曲率半径Rが、31nm R 90nmを満足するよう積層膜に対してパターンニングを行って、記憶素子を形成する。

20

## 【0040】

なお、本発明では、記憶層の平面パターンの詳細な形状は特に問わない。

しかしながら、平面パターンを図4に示すような略橍円形状とすると、長軸LXの長さに対する長軸LX端部の曲率半径Rの比が大きくなる。

このため、平面パターンを略橍円形状とする場合には、曲率半径RがR 100nmを満足するように、長軸LXの長さを比較的短くする。

## 【0041】

また、長軸LX端部の曲率半径Rが、短軸SXの長さの半分よりも大きいと、平面パターンが略橍円形状よりさらに膨らんで、矩形に近い形状となり、記憶層の磁気異方性が小さくなって保磁力Hcが小さくなる。

30

そのため、好ましくは、長軸LX端部の曲率半径Rと、短軸SXの長さWとが、R W / 2の関係を満たすようにする。

## 【0042】

また、好ましくは、平面パターンの短軸の長さWと長軸の長さLの比であるアスペクト比(L/W)を、1.5以上とする。

平面パターンのアスペクト比(短軸の長さWと長軸の長さLとの比L/W)が1.5未満であると、形状磁気異方性が得られるだけの曲率半径の小さな領域を形成しにくくなるため、曲率半径Rを小さく設定する効果が小さくなる。

なお、平面パターンのアスペクト比(L/W)の上限は、磁気異方性の観点からは特に規定されない。ただし、アスペクト比(L/W)が4.0以上になると保磁力Hcが飽和するようになるため、磁気異方性による熱安定性の改善効果よりも、素子の面積の増大による電流増大の影響が大きくなってくる。そのため、より好ましくは、平面パターンのアスペクト比(L/W)を、1.5以上、4.0以下に設定する。

40

## 【0043】

平面パターンの長軸LX端部の曲率半径Rに対して、長軸の長さLが非常に大きくなると、パターン形成が難しくなると共に、平面パターンの形状が菱形や細長い形状となっていく。平面パターンの形状が菱形や細長い形状となった場合、長軸LX端部に磁区や磁化的渦(vortex)を生じやすくなることから、高抵抗状態と低抵抗状態の2値の中間抵抗値をとったり、不完全な磁化反転の原因になったりする。

このような場合、記憶層の磁化反転による情報の記録を行うための、電流等の条件が厳

50

しくなる。

従って、好ましくは、曲率半径Rと、長軸の長さLとが、 $L / 2 \leq R$  の関係を満たすようとする。

#### 【0044】

記憶層の磁化反転にはある一定の電流密度が必要であることと、前述したように記憶素子に流すことのできる電流量には上限があることから、平面パターンの面積が小さい方が望ましい。

一方で、熱安定性の確保の観点から、記憶層の体積及び磁気異方性の確保も必要である。

これらの相反する要望、即ち、平面パターンの面積を小さくすることと、磁気異方性の向上により値を確保することとを、両立させるためには、平面パターンの短軸の長さWを小さくすればよい。好ましくは、平面パターンの短軸の長さWを、175nm以下とする。

なお、平面パターンの短軸の長さWの下限については、特性上の制限よりも製造技術による制限が大きいが、特殊な条件で作製された極微細記憶素子の磁気特性と値の評価実験を行った結果、短軸の長さWを20nm程度とすると充分な磁化が得られなくなった。従って、平面パターンの短軸の長さWは、20nm以上とすることが望ましい。ただし、今後の磁性材料開発によっては、さらに小さくしても磁化が得られるようになる可能性がある。

#### 【0045】

記憶素子の他の構成は、スピノ注入により情報を記録する記憶素子の従来の構成と同様とすることができます。

#### 【0046】

記憶層は、通常、主として、Co, Fe, Ni, Gd等の強磁性材料から構成され、これら2種以上の合金を一つの層として、一層以上の積層状態で記憶層が形成される。

各強磁性層には、飽和磁化量等の磁気特性や、結晶構造（結晶質、微結晶構造、アモルファス構造）の制御のために合金元素が添加される。例えば、CoFe合金、CoFeB合金、Fe合金或いはNiFe合金を主成分として、Gd等の磁性元素や、他の元素として、B, C, N, Si, P, Al, Ta, Mo, Cr, Nb, Cu, Zr, W, V, Hf, Gd, Mn, Pdが1種或いは複数添加された材料を用いることができる。また、例えば、CoにZr, Hf, Nb, Ta, Tiから選ばれる1種類以上の元素を添加したアモルファス材料、CoMnSi, CoMnAlやCoCrFeAl等のホイスラー材料を用いることができる。

#### 【0047】

また、材料又は組成範囲の異なる複数の強磁性層を直接積層させて記憶層を構成することも可能である。また、強磁性層と軟磁性層とを積層させたり、軟磁性層を介して複数層の強磁性層を積層させたりすることも可能である。このように積層させた場合でも、本発明の効果が得られる。

#### 【0048】

また、記憶層と磁化固定層との間の非磁性の中間層として、トンネル絶縁層を用いて磁気トンネル接合（MTJ）素子を構成することにより、非磁性導電層を用いて巨大磁気抵抗効果（GMR）素子を構成した場合と比較して、磁気抵抗変化率（MR比）を大きくすることができ、読み出し信号強度を大きくすることができる。

トンネル絶縁層の材料としては、例えば、酸化アルミニウム（AlOx）や酸化マグネシウム（MgO）等の酸化物を用いることができる。

#### 【0049】

そして、トンネル絶縁層の材料として、特に、酸化マグネシウム（MgO）を用いることにより、これまで一般的に用いられてきた酸化アルミニウムを用いた場合よりも、磁気抵抗変化率（MR比）を大きくすることができる。

一般に、スピノ注入効率はMR比に依存し、MR比が大きいほど、スピノ注入効率が向

10

20

30

40

50

上し、磁化反転電流密度を低減することができる。

従って、中間層のトンネル絶縁層の材料として酸化マグネシウムを用いることにより、スピン注入による書き込み閾値電流を低減することができ、少ない電流で情報の書き込み（記録）を行うことができる。また、読み出し信号強度を大きくすることができる。

これにより、M R 比（T M R 比）を確保して、スピン注入による書き込み閾値電流を低減することができ、少ない電流で情報の書き込み（記録）を行うことができる。また、読み出し信号強度を大きくすることができる。

#### 【0050】

磁化固定層は、強磁性層のみにより、或いは反強磁性層と強磁性層の反強磁性結合を利用することにより、その磁化の向きが固定された構成とする。10

また、磁化固定層は、単層の強磁性層から成る構成、或いは複数層の強磁性層が非磁性層を介して積層した積層フェリ構造とする。磁化固定層を積層フェリ構造としたときには、磁化固定層の外部磁界に対する感度を低下させることができるために、外部磁界による磁化固定層の不要な磁化変動を抑制して、記憶素子を安定して動作させることができる。さらに、各強磁性層の膜厚を調整することができ、磁化固定層からの漏洩磁界を抑えることができる。

積層フェリ構造の磁化固定層を構成する強磁性層の材料としては、Co, CoFe, CoFeB等を用いることができる。また、非磁性層の材料としては、Ru, Re, Ir, Os等を用いることができる。

#### 【0051】

反強磁性層の材料としては、FeMn合金、PtMn合金、PtCrMn合金、NiMn合金、IrMn合金、NiO, Fe<sub>2</sub>O<sub>3</sub>等の磁性体を挙げることができる。20

また、これらの磁性体に、Ag, Cu, Au, Al, Si, Bi, Ta, B, C, O, N, Pd, Pt, Zr, Hf, Ir, W, Mo, Nb等の非磁性元素を添加して、磁気特性を調整したり、他の結晶構造や結晶性や物質の安定性等の各種物性を調整したりすることができる。

#### 【0052】

また、記憶素子の膜構成は、記憶層が磁化固定層の上側に配置される構成でも、下側に配置される構成でも全く問題はない。

#### 【0053】

なお、記憶素子の記憶層に記録された情報を読み出す方法としては、記憶素子の記憶層に薄い絶縁膜を介して、情報の基準となる磁性層を設けて、絶縁層を介して流れる強磁性トンネル電流によって読み出してもよいし、磁気抵抗効果により読み出してもよい。30

#### 【0054】

続いて、本発明の具体的な実施の形態について説明する。

#### 【0055】

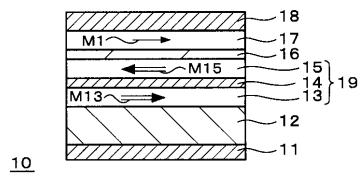

図1は、本発明の一実施の形態として、記憶素子の概略構成図（断面図）を示す。

この記憶素子10は、下層から、下地層11、反強磁性層12、強磁性層13、非磁性層14、強磁性層15、トンネル絶縁層16、記憶層17、キャップ層（保護層）18が積層されて成る。40

なお、積層された各層11～18は、図示しないが、ほぼ同じ平面パターンにパターニングされている。

記憶層17は、磁性体から成り、情報を磁化状態（記憶層17の磁化M1の向き）で保持することができるように構成される。

強磁性層13・非磁性層14・強磁性層15の3層により、積層フェリ構造の磁化固定層19が構成される。このうち、強磁性層13は反強磁性層12により磁化M13の向きが右向きに固定されている。強磁性層15の磁化M15の向きは、強磁性層13の磁化M13の向きとは反平行の左向きになっている。

また、この強磁性層15は、記憶層17に対する磁化の向きの基準となるものであるため、参照層とも称される。50

## 【0056】

磁化固定層19の強磁性層13, 15の材料としては、特に問わないが、鉄、ニッケル、コバルトの1種もしくは2種以上からなる合金材料、例えばCoFe合金を用いることができる。さらにNb、Zr等の遷移金属元素やB等の軽元素を含有させることもできる。

例えば、CoFe合金にボロンBが20~30原子%添加されたアモルファス(非晶質)のCoFeBを用いることも可能である。

## 【0057】

また、特に、磁化固定層19のトンネル絶縁層16に接する強磁性層(参照層)15に、CoFeBを用いることにより、スピン分極率を大きくして、記憶素子10のスピン注入効率を向上することができる。これにより、記憶層17の磁化M1の向きを反転させるための電流をさらに低減することができる。

10

## 【0058】

トンネル絶縁層16の材料としては、Al, Mg, Hf, Si等の酸化物や、その他の酸化物、窒化物等の絶縁材料を用いることができる。

特に、トンネル絶縁層16の材料として酸化マグネシウム(MgO)を用いると、前述したように、大きい磁気抵抗変化率(MR比)が得られる。

## 【0059】

下地層11及びキャップ層18の間に電流を流すことにより、スピン注入による記憶層17の磁化の向きの反転を行うことができる。

20

キャップ層18から下地層11に向けて、即ち記憶層17から強磁性層(参照層)15に向けて電流を流すと、強磁性層(参照層)15から記憶層17に偏極電子が注入され、記憶層17の磁化の向きが参照層15の磁化の向きと平行になる。

下地層11からキャップ層18に向けて、即ち参照層15から記憶層17に向けて電流を流すと、記憶層17から参照層15に偏極電子が注入され、記憶層17の磁化の向きが参照層15の磁化の向きと反平行になる。

このようにして、電流を流す向きによって、記録する情報を選択することができる。

## 【0060】

そして、強磁性層(参照層)15の磁化の向きと記憶層17の磁化の向きが、平行の状態ではトンネル絶縁層16を通る電流の抵抗が小さくなり、反平行の状態ではトンネル絶縁層16を通る電流の抵抗が大きくなる。このことを利用して、抵抗値から記憶層17に記録された情報の内容を読み出すことができる。

30

なお、読み出し時に流す電流は、スピン注入による記憶層17の磁化反転が生じないように、反転電流よりも小さくする。

## 【0061】

本実施の形態では、特に、記憶層17を含む記憶素子10の積層膜の平面パターンが、前述した本発明の要件、即ち、長軸LXの端部の曲率半径R(図2~図4参照)がR $\geq$ 100nmを満足する構成とする。

これにより、前述したように、記憶層17の保磁力Hcを大きくするため、記憶層の熱等に対する安定性を向上させることができる。

40

## 【0062】

本実施の形態の記憶素子10は、下地層11からキャップ層18までを真空装置内で連続的に形成して、その後エッチング等の加工により記憶素子10のパターンを形成することにより、製造することができる。

## 【0063】

また、本実施の形態の記憶素子10を用いて、図10に示したメモリと同様の構成のメモリを構成することができる。

即ち、記憶素子10を2種類のアドレス配線の交点付近に配置してメモリを構成し、2種類のアドレス配線を通じて記憶素子10に上下方向(積層方向)の電流を流して、スピン注入により記憶層17の磁化の向きを反転させて、記憶素子10に情報の記録を行うこ

50

とができる。

#### 【0064】

上述の本実施の形態の記憶素子10の構成によれば、記憶層17を含む記憶素子10の積層膜の平面パターンが、長軸LXの端部の曲率半径RがR 100 nmを満足することにより、記憶層17の保磁力Hcを大きくすることができる。

これにより、記憶層17の熱等に対する安定性を向上させることができ、記憶層17に記録された情報を安定して保持することができる。

即ち、情報の保持特性に優れた記憶素子10を構成することができる。

従って、本実施の形態の記憶素子10を備えてメモリを構成することにより、安定して動作する、信頼性の高いメモリを実現することができる。

10

#### 【0065】

また本実施の形態によれば、記憶層17が充分な安定性を有することから、記憶素子10のパターンを小さくして微細化を図っても、情報を安定して保持することができる。

#### 【0066】

そして、記憶素子10の微細化により、記憶素子10を備えたメモリの集積化を進めて、メモリの小型化や記憶容量の増大を図ることが可能になる。

さらにまた、記憶素子10の微細化により、スピノ注入により情報の記録を行う場合の、記憶層17の磁化M1の向きを反転させるために必要となる書き込み電流閾値Icも小さくすることが可能になる。

20

これにより、情報の記録に必要な電流量を低減することができるため、メモリ全体の消費電力を低減して、従来にない低消費電力のメモリを実現することができる。

#### 【0067】

なお、上述の実施の形態では、記憶素子10を構成する積層膜（記憶層17を含む）の各層11～18が同じ平面パターンに形成されている場合を説明したが、本発明では、少なくとも記憶層の平面パターンが前述した条件を満足していれば、他の層の平面パターンが前述した条件を満足していなくても構わない。

例えば、図1に示した記憶素子10に対して、下地層11や反強磁性層12を、上層の他の各層13～18よりも大きい平面パターンに形成した構成や、キャップ層18を記憶層17とは異なる平面パターンに形成した構成等が考えられる。

30

#### 【0068】

##### （実施例）

ここで、本発明の記憶素子の構成において、具体的に記憶層の寸法や組成等を設定して、特性がどのようになるか検討を行った。

なお、実際には、メモリには、図10に示したように、記憶素子以外にもスイッチング用の半導体回路等が存在するが、ここでは、記憶層の磁気抵抗特性を調べる目的で、記憶素子のみを形成したウエハにより検討を行った。

#### 【0069】

##### <実験1>

まず、厚さ0.575 mmのシリコン基板上に厚さ2 μmの熱酸化膜を形成し、図1に示した記憶素子10と同様の記憶素子を形成した。

40

具体的には、図1に示した構成の記憶素子10において、下地層11を膜厚3 nmのTa膜、反強磁性層12を膜厚20 nmのPtMn膜、磁化固定層19を構成する強磁性層13, 15を膜厚2 nmのCoFe膜、積層フェリ構造の磁化固定層19を構成する非磁性層14を膜厚0.8 nmのRu膜、トンネル絶縁層16を膜厚0.5 nmのAl膜を酸化した酸化アルミニウム膜、記憶層17を膜厚3 nmのCo<sub>72</sub>Fe<sub>8</sub>B<sub>20</sub>膜、キャップ層18を膜厚5 nmのTa膜と選定し、また下地層11と反強磁性層12との間に図示しない膜厚100 nmのCu膜（後述するワード線となるもの）を設けて、各層を形成した。

即ち、各層の材料及び膜厚を、下記の構成（膜構成1）として、記憶素子10を作製し

50

た。

**膜構成 1 :**

Ta(3nm)/Cu(100nm)/PtMn(20nm)/CoFe(2nm)/Ru(0.8nm)/CoFe(2nm)/Al(0.5nm)-O<sub>x</sub>/Co<sub>72</sub>Fe<sub>8</sub>B<sub>20</sub>(3nm)/Ta(5nm)

なお、上記膜構成で、合金組成の示されていない Pt Mn の組成は Pt 50 Mn 50 (原子%)とした。

酸化アルミニウム膜から成るトンネル絶縁層 16 以外の各層は、DC マグнетロンスパッタ法を用いて成膜した。

酸化アルミニウム (Al - O<sub>x</sub>) 膜から成るトンネル絶縁層 16 は、まず金属 Al 膜を DC スパッタ法により 0.5 nm 堆積させて、その後に酸素 / アルゴンの流量比を 1 : 1 とし、自然酸化法により金属 Al 層を酸化させた。酸化時間は 10 分とした。

さらに、記憶素子 10 の各層を成膜した後に、磁場中熱処理炉で、10 kOe · 270 · 4 時間の熱処理を行い、反強磁性層 12 の Pt Mn 膜の規則化熱処理を行った。

**【0070】**

次に、ワード線部分をフォトリソグラフィによってマスクした後に、ワード線以外の部分の積層膜に対して Ar プラズマにより選択エッチングを行うことにより、ワード線（下部電極）を形成した。この際に、ワード線部分以外は、基板の深さ 5 nm までエッチングされた。

**【0071】**

その後、電子ビーム描画装置により記憶素子 10 のパターンのマスクを形成し、積層膜に対して選択エッチングを行い、記憶素子 10 を形成した。記憶素子 10 部分以外は、ワード線の Cu 層直上までエッチングした。

**【0072】**

次に、記憶素子 10 部分以外を、厚さ 100 nm 程度の Al<sub>2</sub>O<sub>3</sub> のスパッタリングによって絶縁した。

その後、フォトリソグラフィを用いて、上部電極となるピット線及び測定用のパッドを形成して記憶素子の試料を作製して、サンプル 1 の記憶素子の試料とした。

**【0073】**

そして、上述の製造方法により、記憶素子 10 の平面パターンの長軸端の曲率半径 R を変えた、記憶素子 10 の各試料を作製した。

長軸端の曲率半径 R は、31 nm, 47 nm, 53 nm, 90 nm, 120 nm, 170 nm の 6 通りとした。

また、各試料の平面パターンにおいて、長軸長を 400 nm とし、短軸長を 150 nm とした。

**【0074】**

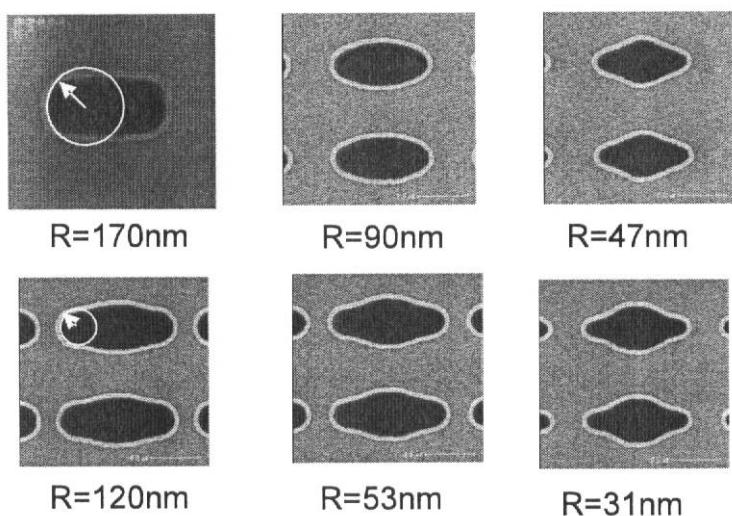

各試料の記憶素子 10 を上方から見た顕微鏡写真を、図 5 に示す。

長軸端の曲率半径 R を 170 nm とした場合には、この曲率半径 R が短軸長より大きいため、矩形（長方形）に近い平面パターンとなっている。

曲率半径 R を 90 nm とした場合には、ほぼ橍円に近い平面パターンとなっている。

そして、曲率半径 R を小さくしていくに従い、長軸端付近が絞られた形状になっていくことがわかる。

**【0075】**

**(記憶層の保磁力の測定)**

各試料の記憶素子 10 について、記憶層 17 の保磁力 H<sub>c</sub> を測定した。

図 5 に示した、記憶素子 10 を上方から見た顕微鏡写真により、記憶素子 10 の平面パターンの正確な寸法・形状を求め、この寸法・形状と、記憶層 17 の材料の磁気特性（飽和磁束密度等）とから、計算によって記憶層 17 の保磁力 H<sub>c</sub> を見積もった。

**【0076】**

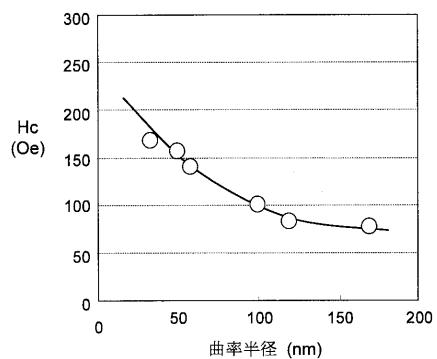

結果として、記憶素子 10 のパターンの長軸端の曲率半径 R と、記憶層 17 の保磁力 H<sub>c</sub> との関係を、図 6 に示す。

10

20

30

40

50

**【0077】**

図6から、曲率半径Rを小さくすると、保磁力Hcを大きくすることができることがわかる。また、曲率半径R = 100 nm付近から保磁力Hcの増大が大きくなることがわかる。

従って、曲率半径RをR = 100 nmを満たす範囲とすることにより、記憶層17の保磁力Hcを大きくして、記憶層17の熱等に対する安定性を向上させることができることがわかる。

**【0078】**

## &lt;実験2&gt;

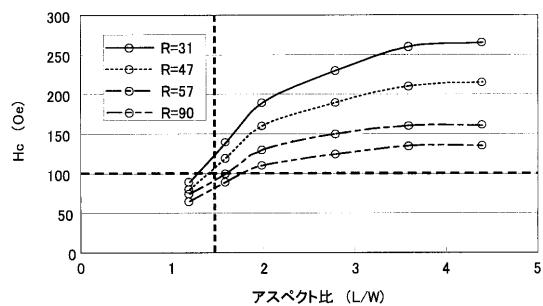

実験1と同様の製造方法により、記憶素子10の平面パターンの長軸端の曲率半径Rとアスペクト比とを変えた、記憶素子10の各試料を作製した。 10

長軸端の曲率半径Rを、31 nm, 47 nm, 53 nm, 90 nmの4通りとした。

また、各試料の平面パターンにおいて、短軸長Wを120 nmとして、長軸長Lを145 nm, 190 nm, 240 nm, 430 nm, 525 nmの6つの条件として、アスペクト比(L/W)を1.2, 1.6, 2.0, 2.8, 3.6, 4.4と変化させた。

各試料の記憶素子10について、記憶層17の保磁力Hcを測定した。

**【0079】**

測定結果として、記憶素子10のパターンのアスペクト比(長軸長L / 短軸長W)と、記憶層の保磁力Hcとの関係を、図7に示す。

**【0080】**

この実験2の各試料は、W = 120 nmであることから、曲率半径RをR = W / 2 = 60 nmを満たす範囲とすることが望ましい。 20

図7から、曲率半径Rをこの条件を満たす31 nm, 47 nm, 53 nmとした場合に、R = 90 nmとした場合よりも、保磁力Hcを大きくできることがわかる。

また、図7から、アスペクト比を1.5以上にすると、記憶層17の保磁力Hcを大きくして、記憶層17の熱等に対する安定性を向上させることができることがわかる。

なお、図7から、アスペクト比を4.0以上にすると、記憶層17の保磁力Hcが飽和して、ほとんど増大しなくなることもわかる。

**【0081】**

## &lt;実験3&gt;

実験1と同様の製造方法により、記憶素子10の平面パターンの長軸端の曲率半径Rを変えた、記憶素子10の各試料を作製した。 30

長軸端の曲率半径Rは、15 nm, 22 nm, 31 nm, 53 nmの4通りとした。

また、各試料の平面パターンにおいて、長軸長を400 nmとし、短軸長を150 nmとした。

各試料の記憶素子10について、外部磁界に対する抵抗変化の連続的な変化を求め、R - H曲線を得た。

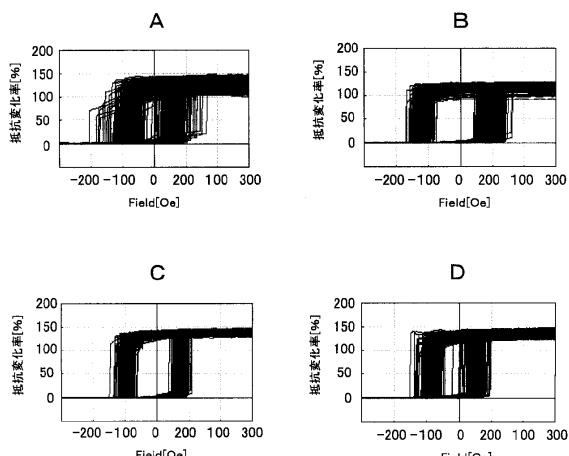

**【0082】**

各試料について、200個のメモリセルの素子を測定した結果を、図8A～図8Dに示す。図8の各図では、200個の素子のR - H曲線を重ねて表示しており、縦軸は低抵抗状態の抵抗値を基準とした抵抗変化率であり、横軸は外部磁界の大きさである。図8AはR = 15 nmの場合を示し、図8BはR = 22 nmの場合を示し、図8CはR = 31 nmの場合を示し、図8DはR = 53 nmの場合を示している。 40

**【0083】**

図8Aから、曲率半径Rが長軸長Lの1/24以下になるR = 15 nmの場合には、R - H曲線に乱れが生じ、高抵抗状態と低抵抗状態以外に中間的な抵抗値をとる場合があることがわかる。

このような場合、前述したように、記憶層17の磁化反転による情報の記録を行うための、電流等の条件が厳しくなる。

図8B～図8Dより、曲率半径Rが長軸長Lの1/24以上である、その他の場合には

50

、良好なR - H曲線が得られている。

従って、曲率半径R及び長軸長Lが、 $L / 2 \leq R$ を満たす範囲とすることにより、安定したR - H曲線が得られることがわかる。

#### 【0084】

##### <実験4>

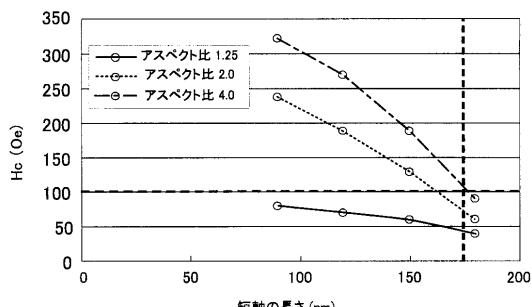

実験1と同様の製造方法により、記憶素子10の平面パターンの長軸長Lと短軸長Wとを変えた、記憶素子10の各試料を作製した。

記憶素子10の平面パターンの短軸長Wを90nm, 120nm, 150nm, 180nmの4通りとし、各々アスペクト比を1.25, 2.0, 4.0の3通りになるように長軸長Lを調整して、記憶素子10をパターニングした。即ち、合計12種類の平面パターンとした。10

なお、各試料の平面パターンにおいて、長軸端の曲率半径Rは31nmに固定した。

各試料の記憶素子10について、記憶層17の保磁力Hcを測定した。

測定結果を、図9に示す。図9の横軸は平面パターンの短軸長Wであり、縦軸は保磁力Hcであり、同じアスペクト比毎に線で結んである。15

#### 【0085】

図7に示したように、保磁力Hcの値はアスペクト比を4.0以上に大きくしても飽和してしまうため、図9より、保磁力Hcの値を100[Oe]以上確保するためには、短軸寸法が、アスペクト比4.0で保磁力Hc = 100[Oe]となる、175nm以下である必要があることがわかる。20

#### 【0086】

本発明は、上述の実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲でその他様々な構成が取り得る。

#### 【図面の簡単な説明】

#### 【0087】

【図1】本発明の一実施の形態の記憶素子の概略構成図(断面図)である。

【図2】記憶層の平面パターンの形状を示す図である。

【図3】記憶層の平面パターンの形状を示す図である。

【図4】記憶層の平面パターンの形状を示す図である。

【図5】各試料の記憶素子を上から見た状態の写真である。30

【図6】平面パターンの長軸端の曲率半径と記憶層の保磁力Hcとの関係を示す図である。

【図7】平面パターンのアスペクト比と記憶層の保磁力Hcとの関係を示す図である。

【図8】A ~ D 記憶素子のR - H曲線である。

【図9】平面パターンの短軸の長さと記憶層の保磁力Hcとの関係を示す図である。

【図10】スピノ注入による磁化反転を利用した磁気メモリの概略構成図(斜視図)である。35

【図11】図10の磁気メモリの断面図である。

【図12】従来のMRAMの構成を模式的に示した斜視図である。

【図13】SPICEシミュレータによる一般的な選択トランジスタと記憶素子とを接続した場合の、素子抵抗と素子電流の関係を示す図である。40

#### 【符号の説明】

#### 【0088】

10 記憶素子、11 下地層、12 反強磁性層、13 強磁性層、14 非磁性層

、15 強磁性層(参照層)、16 トンネル絶縁層、17 記憶層、18 キャップ層

(保護層)、19 磁化固定層、31 (記憶層の)平面パターン、L X 長軸、S X

短軸、R, R1 曲率半径

【図1】

【図2】

【図3】

【図4】

【図6】

【図8】

【図7】

【図9】

【図10】

【図12】

【図11】

【図13】

【図5】

---

フロントページの続き

(72)発明者 肥後 豊

東京都品川区北品川6丁目7番35号 ソニー株式会社内

(72)発明者 別所 和宏

東京都品川区北品川6丁目7番35号 ソニー株式会社内

(72)発明者 山元 哲也

東京都品川区北品川6丁目7番35号 ソニー株式会社内

(72)発明者 大森 広之

東京都品川区北品川6丁目7番35号 ソニー株式会社内

(72)発明者 山根 一陽

東京都品川区北品川6丁目7番35号 ソニー株式会社内

(72)発明者 大石 雄紀

東京都品川区北品川6丁目7番35号 ソニー株式会社内

(72)発明者 山岸 肇

東京都品川区北品川6丁目7番35号 ソニー株式会社内

審査官 正山 旭

(56)参考文献 特開2002-332537(JP,A)

特開2005-150482(JP,A)

特開2003-163330(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8246

H01L 27/105

H01L 29/82

H01L 43/08

H01L 43/10