(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7466643号

(P7466643)

(45)発行日 令和6年4月12日(2024.4.12)

(24)登録日 令和6年4月4日(2024.4.4)

(51)国際特許分類

|         |                  |     |         |        |

|---------|------------------|-----|---------|--------|

| G 0 6 F | 30/343 (2020.01) | F I | G 0 6 F | 30/343 |

| G 0 6 F | 30/27 (2020.01)  |     | G 0 6 F | 30/27  |

| G 0 6 F | 30/337 (2020.01) |     | G 0 6 F | 30/337 |

請求項の数 17 (全18頁)

(21)出願番号 特願2022-530483(P2022-530483)

(86)(22)出願日 令和3年6月1日(2021.6.1)

(86)国際出願番号 PCT/JP2021/020784

(87)国際公開番号 WO2021/251206

(87)国際公開日 令和3年12月16日(2021.12.16)

審査請求日 令和4年10月25日(2022.10.25)

(31)優先権主張番号 特願2020-100016(P2020-100016)

(32)優先日 令和2年6月9日(2020.6.9)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74)代理人 110001195

弁理士法人深見特許事務所

森 敦弘

東京都千代田区丸の内二丁目7番3号

(72)発明者 三菱電機株式会社内

松浦 功

審査官

最終頁に続く

(54)【発明の名称】 学習装置、推論装置、学習方法、および推論方法

## (57)【特許請求の範囲】

## 【請求項1】

プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報と、前記テクノロジ毎のリソース使用率データおよび前記テクノロジマッピング時のタイミングスラック情報における前記プログラマブルロジックデバイスの開発用ツールチェーンの目標クロック周波数および反復合成用パラメータとを含む学習用データを取得するデータ取得部と、

前記学習用データを用いて、前記プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報から配置配線を成功させるための前記プログラマブルロジックデバイスの開発用ツールチェーンに与える反復合成用パラメータを推論するための学習済モデルを生成するモデル生成部と、

を備える学習装置。

## 【請求項2】

前記テクノロジ毎のリソース使用率データは、前記プログラマブルロジックデバイス内のロジックエレメントまたはプロセッシングエレメントの算術論理演算ユニットの使用率と、マルチプレクサの使用率と、加算器の使用率と、減算器の使用率と、算術シフタの使用率とを含む、請求項1記載の学習装置。

## 【請求項3】

前記テクノロジマッピング時のタイミングスラック情報は、前記目標クロック周波数で

決まるサイクル時間に対して前記プログラマブルロジックデバイス内のフリップフロップ間の信号伝搬遅延時間のうち最も大きなものにおける前記サイクル時間に対する余裕値を含む、請求項 1 または 2 記載の学習装置。

**【請求項 4】**

前記反復合成用パラメータは、

中心となるクロック周波数と、

クロック周波数の下限値および上限値を決定するための閾値と、

前記閾値で決定される前記クロック周波数の前記下限値から前記上限値までの範囲を網羅するためのステップ値とを含む、請求項 1 ~ 3 のいずれか 1 項に記載の学習装置。

**【請求項 5】**

前記配置配線を成功させるための反復合成用パラメータは、

前記配置配線後の回路が目的とする信号処理性能を達成できるための前記中心となるクロック周波数と、

反復合成実行時における前記配置配線の結果が成功となる確率が最も高く、かつ前記配置配線の試行回数が最も少なくて済むような条件を満たす前記閾値および前記ステップ値の組み合わせを含む、請求項 4 に記載の学習装置。

**【請求項 6】**

前記モデル生成部は、報酬基準として、前記配置配線が成功した場合に、前記プログラマブルロジックデバイス内のロジックエレメントまたはプロセッシングエレメントの使用率の余裕度、または前記プログラマブルロジックデバイス内のインターフェクトリソースの使用率の余裕度、または前記プログラマブルロジックデバイス内の前記フリップフロップ間の前記信号伝搬遅延時間のうち最も大きなものにおける前記サイクル時間に対する余裕度を用いて報酬を増大させる、請求項 3 に記載の学習装置。

**【請求項 7】**

前記モデル生成部は、報酬基準として、前記配置配線が失敗した場合に、前記プログラマブルロジックデバイス内のロジックエレメントまたはプロセッシングエレメントの使用率の溢れ度合、または前記プログラマブルロジックデバイス内の前記インターフェクトリソースの溢れ度合、または前記プログラマブルロジックデバイス内の前記フリップフロップ間の前記信号伝搬遅延時間のうち最も大きなものにおける前記サイクル時間に対するタイミング違反度合を用いて報酬を低減させる、請求項 6 に記載の学習装置。

**【請求項 8】**

プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報を取得するデータ取得部と、

テクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報をから配置配線を成功させるための前記プログラマブルロジックデバイスの開発用ツールチェーンに与える反復合成用パラメータを推論するための学習済モデルを用いて、前記データ取得部で取得した前記テクノロジ毎のリソース使用率データおよび前記テクノロジマッピング時のタイミングスラック情報をから配置配線を成功させるための反復合成用パラメータを出力する推論部と、

を備える推論装置。

**【請求項 9】**

前記テクノロジ毎のリソース使用率データは、前記プログラマブルロジックデバイス内のロジックエレメントまたはプロセッシングエレメントの算術論理演算ユニットの使用率と、マルチプレクサの使用率と、加算器の使用率と、減算器の使用率と、算術シフタの使用率とを含む、請求項 8 記載の推論装置。

**【請求項 10】**

前記テクノロジマッピング時のタイミングスラック情報を、前記プログラマブルロジックデバイスの開発用ツールチェーンの目標クロック周波数で決まるサイクル時間に対して前記プログラマブルロジックデバイス内のフリップフロップ間の信号伝搬遅延時間のうち

10

20

30

40

50

最も大きなものにおける前記サイクル時間に対する余裕値を含む、請求項 8 または 9 記載の推論装置。

【請求項 1 1】

前記配置配線を成功させるための反復合成用パラメータは、

前記配置配線後の回路が目的とする信号処理性能を達成できるための中心となるクロック周波数と、

反復合成実行時における前記配置配線の結果が成功となる確率が最も高く、かつ前記配置配線の試行回数が最も少なくて済むような条件を満たすクロック周波数の下限値および上限値を決定するための閾値、および前記下限値から前記上限値までの範囲を網羅するためのステップ値の組み合わせとを含む、請求項 8 ~ 10 のいずれか 1 項に記載の推論装置。

10

【請求項 1 2】

プログラマブルロジックデバイスの開発用ツールチェーンの目標クロック周波数と、反復合成用パラメータと、前記プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データと、テクノロジマッピング時のタイミングスラック情報とを含む学習用データを取得するデータ取得部と、

前記学習用データを用いて、前記プログラマブルロジックデバイスの開発用ツールチェーンの前記目標クロック周波数と、前記反復合成用パラメータと、前記テクノロジ毎の前記リソース使用率データと、前記テクノロジマッピング時の前記タイミングスラック情報とから配置配線の成功確率を推論するための学習済モデルを生成するモデル生成部と、

を備える学習装置。

20

【請求項 1 3】

プログラマブルロジックデバイスの開発用ツールチェーンの目標クロック周波数と、反復合成用パラメータと、前記プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データと、テクノロジマッピング時のタイミングスラック情報とを取得するデータ取得部と、

前記目標クロック周波数と、前記反復合成用パラメータと、前記テクノロジ毎の前記リソース使用率データと、前記テクノロジマッピング時の前記タイミングスラック情報とから配置配線の成功確率を推論するための学習済モデルを用いて、前記データ取得部で取得した前記目標クロック周波数と、前記反復合成用パラメータと、前記テクノロジ毎の前記リソース使用率データと、前記テクノロジマッピング時の前記タイミングスラック情報とから配置配線の成功確率を出力する推論部と、

30

を備える推論装置。

【請求項 1 4】

プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報と、前記テクノロジ毎のリソース使用率データおよび前記テクノロジマッピング時のタイミングスラック情報における前記プログラマブルロジックデバイスの開発用ツールチェーンの目標クロック周波数および反復合成用パラメータとを含む学習用データを取得するステップと、

前記学習用データを用いて、前記プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報から配置配線を成功させるための前記プログラマブルロジックデバイスの開発用ツールチェーンに与える反復合成用パラメータを推論するための学習済モデルを生成するステップと、

40

を備える学習方法。

【請求項 1 5】

プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報を取得するステップと、

テクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報をから配置配線を成功させるための前記プログラマブルロジックデバイスの開発用

50

ツールチェーンに与える反復合成用パラメータを推論するための学習済モデルを用いて、前記取得した前記テクノロジ毎のリソース使用率データおよび前記テクノロジマッピング時のタイミングスラック情報から配置配線を成功させるための反復合成用パラメータを出力するステップと、

を備える推論方法。

#### 【請求項 16】

プログラマブルロジックデバイスの開発用ツールチェーンの目標クロック周波数と、反復合成用パラメータと、前記プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データと、テクノロジマッピング時のタイミングスラック情報とを含む学習用データを取得するステップと、

10

前記学習用データを用いて、前記プログラマブルロジックデバイスの開発用ツールチェーンの前記目標クロック周波数と、前記反復合成用パラメータと、前記テクノロジ毎の前記リソース使用率データと、前記テクノロジマッピング時の前記タイミングスラック情報とから配置配線の成功確率を推論するための学習済モデルを生成するステップと、

を備える学習方法。

#### 【請求項 17】

プログラマブルロジックデバイスの開発用ツールチェーンの目標クロック周波数と、反復合成用パラメータと、前記プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データと、テクノロジマッピング時のタイミングスラック情報とを取得するステップと、

20

前記目標クロック周波数と、前記反復合成用パラメータと、前記テクノロジ毎の前記リソース使用率データと、前記テクノロジマッピング時の前記タイミングスラック情報とから配置配線の成功確率を推論するための学習済モデルを用いて、前記取得した前記目標クロック周波数と、前記反復合成用パラメータと、前記テクノロジ毎の前記リソース使用率データと、前記テクノロジマッピング時の前記タイミングスラック情報とから配置配線の成功確率を出力するステップと、

を備える推論方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

30

本開示は、学習装置、推論装置、およびプログラマブルロジックデバイスの開発用ツールチェーンに関する。

##### 【背景技術】

##### 【0002】

近年、半導体プロセス世代の進化とともにカスタムASIC (Application Specific Integrated Circuit) 開発のコストが増大している。そのため、FPGA (Field Programmable Gate Array) またはDRP (Dynamic ReConfigurable Processor) などのプログラマブルロジックデバイスへのニーズが高まっている。

##### 【0003】

これらのプログラマブルデバイスを用いてユーザーアプリケーション回路を開発するツールチェーンにおいては、大別して高位合成、論理マッピング、および配置配線などの工程が存在する。この中に特に実行時間を要するのが配置配線である。配置配線を完了するためにはクロック周波数および入出力遅延設定などの制約条件、およびツールオプションなどを様々に変更した上で試行を繰り返す必要がある。特にコストを抑えたデバイスを用いて比較的規模の大きな回路を開発する場合には、試行に要する時間が開発期間に大きな影響を及ぼす。

40

##### 【0004】

たとえば、特許文献1には、半導体回路設計のEDAツールにおいて、性能向上のため、その回路の特徴ベクターを抽出し、特徴量ライブラリを参照して、ツールが推奨する第1の配置配線トポロジーを生成する。特許文献1には、第1の配置配線トポロジーを元に

50

、さらに別の推奨する配置配線トポロジーを生成するための手法が記載されている。

【先行技術文献】

【特許文献】

【0005】

【文献】米国特許 10,437,954 明細書

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献 1 においては、回路の特徴量を求めて配置配線のための適切なトポロジーを推奨する。しかしながら、特許文献 1 に記載した手法は、ASIC 回路設計に特化したものであり、プログラマブルロジックデバイスへの適用は考慮されていない。

10

【0007】

本開示の目的は、プログラマブルロジックデバイスを用いてユーザアプリケーション回路を開発する際に、配置配線の高速化を実現できる学習装置、推論装置、およびプログラマブルロジックデバイスの開発用ツールチェーンを提供することである。

【課題を解決するための手段】

【0008】

本開示の学習装置は、プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報と、テクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報におけるプログラマブルロジックデバイスの開発用ツールチェーンの目標クロック周波数および反復合成用パラメータとを含む学習用データを取得するデータ取得部と、学習用データを用いて、プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報から配置配線を成功させるためのプログラマブルロジックデバイスの開発用ツールチェーンに与える反復合成用パラメータを推論するための学習済モデルを生成するモデル生成部とを備える。

20

【0009】

本開示の推論装置は、プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報を取得するデータ取得部と、テクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報から配置配線を成功させるためのプログラマブルロジックデバイスの開発用ツールチェーンに与える反復合成用パラメータを推論するための学習済モデルを用いて、データ取得部で取得したテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報から配置配線を成功させるための反復合成用パラメータを出力する推論部とを備える。

30

【0010】

本開示の学習装置は、プログラマブルロジックデバイスの開発用ツールチェーンの目標クロック周波数と、反復合成用パラメータと、プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データと、テクノロジマッピング時のタイミングスラック情報を含む学習用データを取得するデータ取得部と、学習用データを用いて、プログラマブルロジックデバイスの開発用ツールチェーンの目標クロック周波数と、反復合成用パラメータと、テクノロジ毎のリソース使用率データと、テクノロジマッピング時のタイミングスラック情報とから配置配線の成功確率を推論するための学習済モデルを生成するモデル生成部とを備える。

40

【0011】

本開示の推論装置は、プログラマブルロジックデバイスの開発用ツールチェーンの目標クロック周波数と、反復合成用パラメータと、プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データと、テクノロジマッピング時のタイミングスラック情報を取得するデータ取得部と、目標クロック周波数と、反復合成用

50

パラメータと、テクノロジ毎のリソース使用率データと、テクノロジマッピング時のタイミングスラック情報とから配置配線の成功確率を推論するための学習済モデルを用いて、データ取得部で取得した目標クロック周波数と、反復合成用パラメータと、テクノロジ毎のリソース使用率データと、テクノロジマッピング時のタイミングスラック情報とから配置配線の成功確率を出力する推論部とを備える。

【発明の効果】

【0012】

本開示によれば、プログラマブルロジックデバイスを用いてユーザアプリケーション回路を開発する際に、配置配線の高速化を実現できる。

【図面の簡単な説明】

【0013】

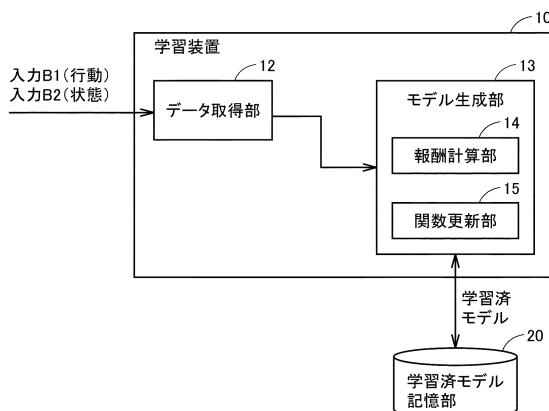

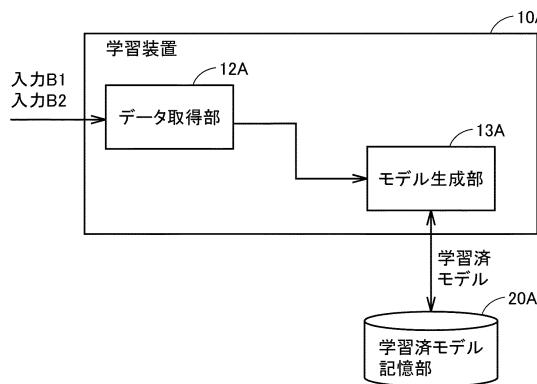

【図1】実施の形態1におけるプログラマブルロジックデバイスの開発用ツールチェーンに関する学習装置10の構成図である。

10

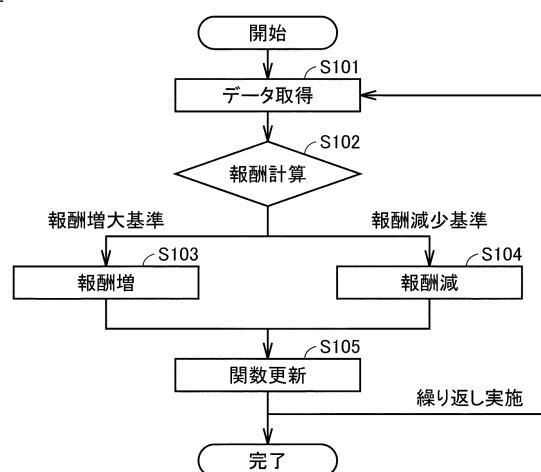

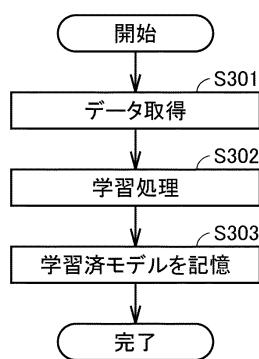

【図2】実施の形態1における学習装置10の学習処理に関するフローチャートである。

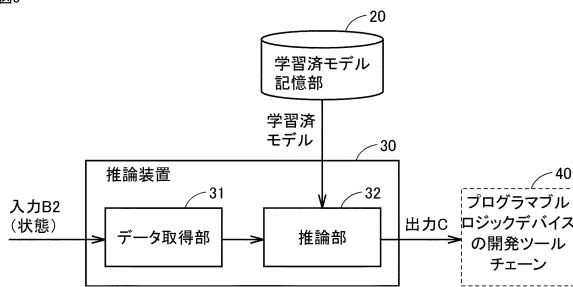

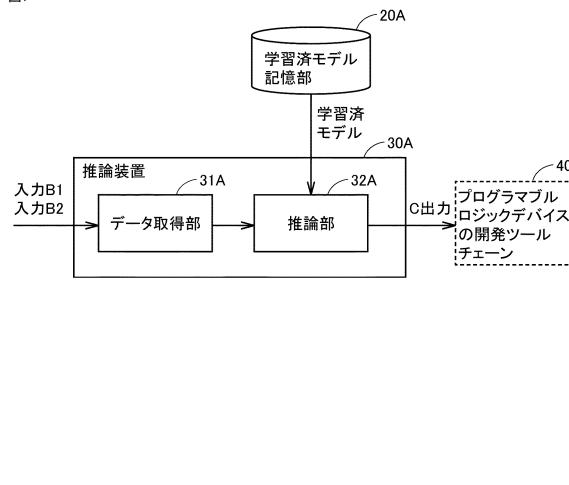

【図3】実施の形態1におけるプログラマブルロジックデバイスの開発用ツールチェーンに関する推論装置30の構成図である。

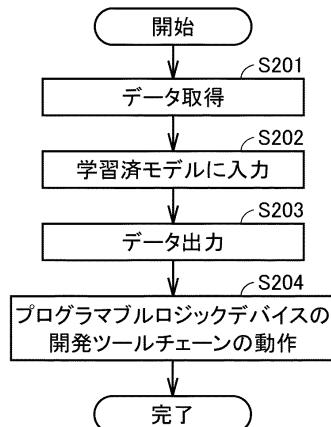

【図4】実施の形態1における推論装置30による反復合成用パラメータの推論手順を表わすフローチャートである。

【図5】実施の形態2におけるプログラマブルロジックデバイスの開発用ツールチェーンに関する学習装置10Aの構成を表わす図である。

20

【図6】実施の形態2における学習装置10Aの学習処理に関するフローチャートである。

【図7】実施の形態2におけるプログラマブルロジックデバイスの開発用ツールチェーンに関する推論装置30Aの構成を表わす図である。

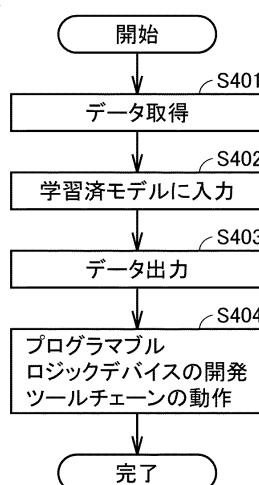

【図8】実施の形態2における推論装置30Aの配置配線の成功確率の推論手順を表わすフローチャートである。

【図9】学習装置10, 10A、推論装置30, 30A、またはプログラマブルロジックデバイスの開発用ツールチェーン40のハードウェア構成を表わす図である。

【発明を実施するための形態】

【0014】

以下、実施の形態について、図面を参照して説明する。

30

実施の形態1.

図1は、実施の形態1におけるプログラマブルロジックデバイスの開発用ツールチェーンに関する学習装置10の構成図である。学習装置10は、データ取得部12と、モデル生成部13とを備える。

【0015】

データ取得部12は、目標クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報を学習用データとして取得する。

【0016】

目標クロック周波数とは、プログラマブルロジックデバイスを実際に動作させる目標のクロック周波数のことである。

40

【0017】

反復合成とは、目標クロック周波数を配置配線後に達成するために複数回の配置配線を試行することを意味する。反復合成では、例えば、目標クロック周波数、または目標クロック周波数よりも高いクロック周波数を中心周波数X [MHz]として、周波数の低い側および高い側に閾値 [MHz]の範囲を設定し、すなわち(X - ) [MHz]から(X + ) [MHz]までの範囲を設定し、その範囲の間をステップ値 [MHz]ずつ変化させながら配置配線の試行が繰り返される。反復合成の試行回数は(2 / + 1)回となる。反復合成用パラメータとは、上記のX、-、+のことを指す。下限値(X - )は、目標クロック周波数よりも大きな値とする。

50

**【 0 0 1 8 】**

テクノロジ毎のリソース使用率データとは、プログラマブルロジックデバイス内の各種演算資源毎の使用可能な数に対する使用数の割合を示す。

**【 0 0 1 9 】**

テクノロジ毎のリソース使用率データは、たとえば、プログラマブルロジックデバイスのテクノロジマッピングの結果、L E (Logic Element) または P E (Processing Element) の A L U (算術論理演算ユニット) の使用率、マルチプレクサの使用率、加算器の使用率、減算器の使用率、および算術シフタの使用率などを含む。

**【 0 0 2 0 】**

テクノロジマッピング時のタイミングスラック情報は、テクノロジマッピング後の静的タイミング解析の結果、目標クロック周波数で決まるサイクル時間に対して、プログラマブルデバイス内の F F (Flip Flop) 間の信号伝搬遅延時間のうち最も大きなもの (クリティカルパス) における、サイクル時間に対するタイミングの余裕度を含む。たとえば、目標クロック周波数が 1 0 0 [MHz] で決まるサイクル時間が 1 0 . 0 [ns] で、クリティカルパスにおける F F (Flip Flop) 間の信号伝搬遅延時間が 7 . 0 [ns] の場合は、タイミングスラックは 1 0 . 0 [ns] - 7 . 0 [ns] = 3 . 0 [ns] となる。

10

**【 0 0 2 1 】**

モデル生成部 1 3 は、データ取得部 1 2 で取得した目標クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報を含む学習用データを用いて、プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報から配置配線を成功させるためのプログラマブルロジックデバイスの開発用ツールチェーンに与える反復合成用パラメータを推論するための学習済モデルを生成する。

20

**【 0 0 2 2 】**

反復合成用パラメータとは、前述の反復合成実施のためのクロック中心周波数 X [MHz] 、周波数の低い側および高い側の周波数範囲を決定するための閾値 [MHz] 、その周波数範囲内を変化させながら配置配線の試行を繰返すためのステップ値 [MHz] である。

**【 0 0 2 3 】**

「配置配線を成功させるための反復合成用パラメータ」とは、配置配線後の回路が目的の信号処理性能を達成できる中心クロック周波数と、反復合成実行時における各々の配置配線結果が成功となる確率が最も高く、かつ配置配線の試行回数が最も少なくて済むような条件を満たすような閾値 [MHz] およびステップ値 [MHz] の組み合わせである。

30

**【 0 0 2 4 】**

上記条件を満たすために、たとえば、小さな閾値 を選択して周波数範囲を狭める、あるいは、大きなステップ値 を選択して配置配線の試行回数を削減することによって、閾値 [MHz] およびステップ値 [MHz] の組み合わせが決定される。

**【 0 0 2 5 】**

使用可能な最大の演算リソース数を超えないこと、かつ使用するインターフェクトリソースがプログラマブルロジックデバイス上で使用可能な最大のインターフェクトリソース数を超えないこと、かつ、F F (Flip Flop) 間の信号伝搬遅延時間のうち最も大きな値が目標クロック周波数で決まるサイクル時間を超えないことを示す。

40

**【 0 0 2 6 】**

モデル生成部 1 3 が用いる学習アルゴリズムとして、教師あり学習、教師なし学習、または強化学習等の公知のアルゴリズムを用いることができる。一例として、強化学習を適用した場合について説明する。強化学習では、ある環境内におけるエージェント (行動主体) が、現在の状態 (環境のパラメータ) を観測し、取るべき行動を決定する。エージェントの行動により環境が動的に変化し、エージェントには環境の変化に応じて報酬が与えられる。エージェントはこれを繰り返し、一連の行動を通じて報酬が最も多く得られる行動方針を学習する。強化学習の代表的な手法である Q 学習、または T D 学習 (Temporal

50

Difference Learning) を用いることができる。例えば、Q学習 (Q-learning) の場合、行動価値関数  $Q(s, a)$  の一般的な更新式は、式(1)で表される。

【0027】

【数1】

$$Q(s_t, a_t) \leftarrow Q(s_t, a_t) + \alpha \left( r_{t+1} + \gamma \max_a Q(s_{t+1}, a) - Q(s_t, a_t) \right) \quad \cdots(1)$$

【0028】

式(1)において、 $s_t$  は時刻  $t$  における環境の状態を表わす。 $a_t$  は時刻  $t$  における行動を表わす。行動  $a_t$  により、状態は  $s_{t+1}$  に変わる。 $r_{t+1}$  はその状態の変化によってもらえる報酬を表わす。 $\gamma$  は割引率を表わす。 $\alpha$  は学習係数を表わす。 $0 < \alpha < 1$ 、 $0 < \gamma < 1$  の範囲とする。反復合成用パラメータが行動  $a_t$  である。テクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報が状態  $s_t$  である。Q学習では、時刻  $t$  の状態  $s_t$  における最良の行動  $a_t$  を学習する。

10

【0029】

式(1)で表される更新式は、時刻  $t+1$  における最も  $Q$  値の高い行動  $a$  の行動価値  $Q$  が、時刻  $t$  において実行された行動  $a$  の行動価値  $Q$  よりも大きければ、行動価値  $Q$  を大きくし、逆の場合は、行動価値  $Q$  を小さくする。換言すれば、時刻  $t$  における行動  $a$  の行動価値  $Q$  を、時刻  $t+1$  における最良の行動価値に近づけるように、行動価値関数  $Q(s, a)$  を更新する。それにより、或る環境における最良の行動価値が、それ以前の環境における行動価値に順次伝播していくようになる。

20

【0030】

上記のように、強化学習によって学習済モデルを生成する場合、モデル生成部13は、報酬計算部14と、関数更新部15とを備える。

【0031】

報酬計算部14は、目標クロック周波数および反復合成用パラメータ、テクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報に基づいて報酬を計算する。報酬計算部14は、配置配線の結果に基づいて、報酬  $r$  を計算する。たとえば、報酬計算部14は、配置配線が成功した場合には報酬  $r$  を増大させ(例えば「1」の報酬を与える。)、他方、配置配線が失敗した場合には報酬  $r$  を低減する(例えば「-1」の報酬を与える。)。

30

【0032】

具体的には、報酬計算部14は、配置配線が成功した場合には、プログラマブルロジックデバイス内のLEまたはPEの使用率の余裕度(%)に比例して報酬を増大させる、またはプログラマブルロジックデバイス内のインターネットリソースの余裕度(%)に比例して報酬を増大させる、またはプログラマブルロジックデバイス内のFF(Flip Flop)間の信号伝搬遅延時間のうち最も大きなもの(クリティカルパス)における、サイクル時間に対するタイミングの余裕度(Positive Slack値)に比例して報酬を増大させる。報酬計算部14は、これらの3つの報酬を増大させる要素(演算リソースの余裕度、インターネットリソースの余裕度、クリティカルパスのタイミング余裕度)のうち複数の要素を組み合わせて報酬を増大させてもよく、また必要に応じて各々の要素に重み係数を掛けて報酬を増大させてもよい。

40

【0033】

報酬計算部14は、配置配線が失敗した場合には、プログラマブルロジックデバイス内のLEまたはPEの溢れ度合に比例して報酬を低減させる、またはプログラマブルロジックデバイス内インターネットリソースの溢れ度合に比例して報酬を低減させる、またはいずれのリソースも溢れていらない場合は、プログラマブルデバイス内のFF(Flip Flop)間の信号伝搬遅延時間のうち最も大きなもの(クリティカルパス)におけるサイクル時間に対するタイミング違反度合(Negative Slack値)または全タイミング違反度(Total Negative Slack値)に比例して報酬を低減させる。報酬計算部14は、これらの3つの

50

報酬を低減させる要素（演算リソースの溢れ度合、インターフェースの溢れ度合、タイミング違反度）のうち複数の要素を組み合わせて報酬を低減させてもよく、また必要に応じて各々の要素に重み係数を掛けて報酬を低減させてよい。

【0034】

関数更新部15は、報酬計算部14によって計算される報酬に従って、配置配線を成功させるための反復合成用パラメータを決定するための関数を更新し、学習済モデル記憶部20に出力する。例えばQ学習の場合、関数更新部15は、式(1)で表される行動価値関数 $Q(s_t, a_t)$ を、配置配線を成功させるための反復合成用パラメータを算出するための関数として用いる。

【0035】

以上のような学習を繰り返し実行する。学習済モデル記憶部20は、関数更新部15によって更新された行動価値関数 $Q(s_t, a_t)$ 、すなわち、学習済モデルを記憶する。

【0036】

次に、図2を用いて、学習装置10が学習する処理について説明する。図2は、実施の形態1における学習装置10の学習処理に関するフローチャートである。

【0037】

ステップS101において、データ取得部12は、目標クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報を学習用データとして取得する。

【0038】

ステップS102において、モデル生成部13は、目標クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報に基づいて報酬を計算する。具体的には、報酬計算部14は、目標クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報を取得し、配置配線の結果に基づいて、報酬を増大させるか、減少させるかを決定する。報酬計算部14が報酬を増大させると判断した場合に、処理がステップS103に進む。報酬計算部14が報酬を減少させると判断した場合に、処理がステップS104に進む。

【0039】

ステップS103において、報酬計算部14が、報酬を増大させる。

ステップS104において、報酬計算部14は、報酬を減少させる。

【0040】

ステップS105において、関数更新部15は、報酬計算部14によって計算された報酬に基づいて、学習済モデル記憶部20が記憶する式(1)で表される行動価値関数 $Q(s_t, a_t)$ を更新する。

【0041】

学習装置10は、以上のステップS101からS105までのステップを繰り返し実行し、生成された行動価値関数 $Q(s_t, a_t)$ を学習済モデルとして記憶する。

【0042】

本実施の形態に係る学習装置10は、学習済モデルを学習装置10の外部に設けられた学習済モデル記憶部20に記憶するものとしたが、学習済モデル記憶部20を学習装置10の内部に備えていてよい。

【0043】

図3は、実施の形態1におけるプログラマブルロジックデバイスの開発用ツールチェーンに関する推論装置30の構成図である。推論装置30は、データ取得部31、および推論部32を備える。

【0044】

データ取得部31は、テクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報を取得する。

【0045】

10

20

30

40

50

推論部 3 2 は、学習済モデル記憶部 2 0 から、プログラマブルロジックデバイスの開発用ツールチェーンのテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報から配置配線を成功させるためのプログラマブルロジックデバイスの開発用ツールチェーンに与える反復合成用パラメータを推論するための学習済モデルを読み出す。

#### 【 0 0 4 6 】

推論部 3 2 は、データ取得部 3 1 で取得したデータと、学習済モデルを利用して、配置配線を成功させるための反復合成用パラメータを推論する。すなわち、推論部 3 2 は、学習済モデルにデータ取得部 3 1 が取得したテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報を入力することで、テクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報に適した配置配線を成功させるための反復合成用パラメータを推論することができる。

#### 【 0 0 4 7 】

たとえば、推論部 3 2 は、学習済モデル記憶部 2 0 から学習済みモデルとして、行動価値関数  $Q(s, a_t)$  を読み出す。推論部 3 2 は、テクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報（状態  $s$   $t$ ）に対して、行動価値関数  $Q(s, a)$  に基づいて、反復合成用パラメータ（行動  $a_t$ ）を得る。この行動  $a_t$  に含まれる反復合成用パラメータが配置配線を成功させるための反復合成用パラメータである。

#### 【 0 0 4 8 】

本実施の形態では、プログラマブルロジックデバイスの開発用ツールチェーンのモデル生成部 1 3 で学習した学習済モデルを用いて配置配線を成功させるための反復合成用パラメータを出力するものとして説明したが、他のプログラマブルロジックデバイスの開発用ツールチェーンから学習済モデルを取得し、この学習済モデルに基づいて配置配線を成功させるための反復合成用パラメータを出力するようにしてもよい。

#### 【 0 0 4 9 】

次に、図 4 を用いて、配置配線を成功させるための反復合成用パラメータを得るための処理を説明する。

#### 【 0 0 5 0 】

図 4 は、実施の形態 1 における推論装置 3 0 による反復合成用パラメータの推論手順を表わすフローチャートである。

#### 【 0 0 5 1 】

ステップ S 2 0 1 において、データ取得部 3 1 は、テクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報を取得する。

#### 【 0 0 5 2 】

ステップ S 2 0 2 において、推論部 3 2 は、学習済モデル記憶部 2 0 に記憶された学習済モデルにテクノロジ毎のリソース使用率データおよびテクノロジマッピング時のタイミングスラック情報を入力する。

#### 【 0 0 5 3 】

ステップ S 2 0 3 において、推論部 3 2 は、学習済モデルから配置配線を成功させるための反復合成用パラメータを得る。推論部 3 2 は得られた配置配線を成功させるための反復合成用パラメータをプログラマブルロジックデバイスの開発用ツールチェーンに出力する。

#### 【 0 0 5 4 】

ステップ S 2 0 4 において、プログラマブルロジックデバイスの開発用ツールチェーンは、出力された配置配線を成功させるための反復合成用パラメータと、テクノロジマッピングによる回路構成情報を用いて、プログラマブルデバイス上の実際の P E ( Processing Element ) 、 L E ( Logic Element ) 、 S R A M ( Static Random Access Memory ) およびインターフェクトリソースを用いた配置配線の試行を繰り返し、すなわち反復合成を行う。このとき、反復合成の合成制約は、ステップ S 2 0 3 によって出力された配置

10

20

30

40

50

配線を成功させるための反復合成用パラメータである。中心周波数  $X$  [MHz]、閾値 [MHz]、ステップ値 [MHz]を用いて、 $(X - )$  [MHz]から $(X + )$  [MHz]までの周波数範囲を設定し、クロック周波数をその範囲の間でステップ値 [MHz]ずつ変化させる。この場合の反復合成の試行回数は $(2 / + 1)$ 回となる。これにより、最も少ない配置配線の試行回数、すなわち短時間での配置配線の試行によって、目的の信号処理性能を達成できるクロック周波数以上での配置配線を成功させることができる。

#### 【0055】

本実施の形態では、推論部が用いる学習アルゴリズムに強化学習を適用した場合について説明したが、これに限られるものではない。学習アルゴリズムについては、強化学習以外にも、教師あり学習、教師なし学習、または半教師あり学習等を適用することも可能である。

10

#### 【0056】

モデル生成部 13 に用いられる学習アルゴリズムとしては、特徴量そのものの抽出を学習する深層学習を用いることもできる。あるいは、これに代えて他の公知の方法、例えばニューラルネットワーク、遺伝的プログラミング、機能論理プログラミング、またはサポートベクターマシンなどに従って機械学習を実行してもよい。

#### 【0057】

学習装置 10 及び推論装置 30 は、例えば、ネットワークを介してプログラマブルロジックデバイスの開発用ツールチェーンに接続され、このプログラマブルロジックデバイスの開発用ツールチェーンとは別個の装置であってもよい。また、学習装置 10 及び推論装置 30 は、プログラマブルロジックデバイスの開発用ツールチェーンに内蔵されていてもよい。さらに、学習装置 10 及び推論装置 30 は、クラウドサーバ上に存在していてもよい。

20

#### 【0058】

モデル生成部 13 は、複数のプログラマブルロジックデバイスの開発用ツールチェーンから取得される学習用データを用いて、配置配線を成功させるための反復合成用パラメータを学習するようにしてもよい。なお、モデル生成部 13 は、同一の場所で使用される複数のプログラマブルロジックデバイスの開発用ツールチェーンから学習用データを取得してもよいし、異なる場所で独立して動作する複数のプログラマブルロジックデバイスの開発用ツールチェーンから学習用データを取得してもよい。また、学習用データを収集するプログラマブルロジックデバイスの開発用ツールチェーンを途中で対象に追加したり、対象から除去することも可能である。さらに、あるプログラマブルロジックデバイスの開発用ツールチェーンに関して配置配線を成功させるための反復合成用パラメータを学習した学習装置を、これとは別のプログラマブルロジックデバイスの開発用ツールチェーンに適用し、この別のプログラマブルロジックデバイスの開発用ツールチェーンに関して配置配線を成功させるための反復合成用パラメータを再学習して更新するようにしてもよい。

30

#### 【0059】

以上のように、本実施の形態によれば、プログラマブルデバイスの開発ツールチェーンを用いて反復して配置配線を実行し、配置配線が成功するクロックおよびタイミング制約条件を見つける工程において、人工知能による推論結果によって得られたクロック中心周波数と周波数範囲とを用いる。これによって、配置配線工程の試行回数を大幅に削減することができるので、配置配線工程に要する時間の大幅な短縮を図ることができる。

40

#### 【0060】

##### 実施の形態 2 .

図 5 は、実施の形態 2 におけるプログラマブルロジックデバイスの開発用ツールチェーンに関する学習装置 10 A の構成を表わす図である。

#### 【0061】

学習装置 10 A は、データ取得部 12 A と、モデル生成部 13 A とを備える。

データ取得部 12 A は、クロック周波数と、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、テクノロジマッピング時のタイミングスラック情報を学習用データ

50

として取得する。

【0062】

モデル生成部13Aは、データ取得部12Aから出力されるクロック周波数と、反復合成用パラメータ、およびテクノロジ毎のリソース使用率データ、テクノロジマッピング時のタイミングスラック情報の組合せに基づいて作成される学習用データに基づいて、配置配線の成功確率を学習する。すなわち、プログラマブルロジックデバイスの開発用ツールチェーンのクロック周波数と、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、テクノロジマッピング時のタイミングスラック情報から配置配線の成功確率を推論する学習済モデルを生成する。ここで、学習用データは、クロック周波数と、反復合成用パラメータおよびテクノロジ毎のリソース使用率データ、テクノロジマッピング時のタイミングスラック情報を互いに関連付けたデータである。プログラマブルロジックデバイスの開発用ツールチェーンにAIを活用する場合、学習済モデルは、配置配線が成功したときのクロック周波数と、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、テクノロジマッピング時のタイミングスラック情報と、配置配線が失敗したときのクロック周波数と、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、テクノロジマッピング時のタイミングスラック情報を分類（クラスタリング）するためのモデルとして構成される。

10

【0063】

モデル生成部13Aが用いる学習アルゴリズムは、教師あり学習、教師なし学習、強化学習等の公知のアルゴリズムを用いることができる。一例として、教師なし学習であるK平均法（クラスタリング）を適用した場合について説明する。教師なし学習とは、結果（ラベル）を含まない学習用データを学習装置に与えることで、それらの学習用データにある特徴を学習する手法をいう。

20

【0064】

モデル生成部13Aは、例えば、K平均法によるグループ分け手法に従って、いわゆる教師なし学習により、配置配線の成功確率を学習する。

【0065】

K平均法とは、非階層型クラスタリングのアルゴリズムであり、クラスタの平均を用い、与えられたクラスタ数をk個に分類する手法である。

30

【0066】

具体的に、K平均法は以下のような流れで処理される。まず、各データ $\times_i$ に対してランダムにクラスタを割り振る。次いで、割り振ったデータをもとに各クラスタの中心 $V_j$ を計算する。次いで、各 $\times_i$ と各 $V_j$ との距離を求め、 $\times_i$ を最も近い中心のクラスタに割り当て直す。そして、上記の処理で全ての $\times_i$ のクラスタの割り当てが変化しなかった場合、あるいは変化量が事前に設定した一定の閾値を下回った場合に、収束したと判断して処理を終了する。

【0067】

本願においては、データ取得部12Aによって取得されるクロック周波数と、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、テクノロジマッピング時のタイミングスラック情報の組合せに基づいて作成される学習用データに従って、いわゆる教師なし学習により、配置配線の成功確率を学習する。

40

【0068】

モデル生成部13Aは、以上のような学習を実行することで学習済モデルを生成し、出力する。

【0069】

学習済モデル記憶部20Aは、モデル生成部13Aから出力された学習済モデルを記憶する。

【0070】

次に、図6を用いて、学習装置10Aが学習する処理について説明する。図6は、実施の形態2における学習装置10Aの学習処理に関するフローチャートである。

50

## 【0071】

ステップS301において、データ取得部12Aは、クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報を取得する。クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報を同時に取得するものとしたが、クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報を関連づけて入力できれば良く、クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報のデータをそれぞれ別のタイミングで取得しても良い。

10

## 【0072】

ステップS302において、モデル生成部13Aは、データ取得部12Aによって取得されるクロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報の組合せに基づいて作成される学習用データに従って、いわゆる教師なし学習により、配置配線の成功確率を学習し、学習済モデルを生成する。

## 【0073】

ステップS303において、学習済モデル記憶部20Aは、モデル生成部13Aが生成した学習済モデルを記憶する。

20

## 【0074】

図7は、実施の形態2におけるプログラマブルロジックデバイスの開発用ツールチェーンに関する推論装置30Aの構成を表わす図である。推論装置30Aは、データ取得部31Aと、推論部32Aとを備える。

## 【0075】

データ取得部31Aは、クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報を取得する。

## 【0076】

推論部32Aは、学習済モデル記憶部20Aに記憶された学習済モデルを利用して得られる配置配線の成功確率を推論する。すなわち、推論部32Aは、学習済モデルにデータ取得部31Aで取得したクロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報を入力することで、クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報がいずれのクラスタに属するかを推論し、推論結果を配置配線の成功確率として出力することができる。プログラマブルロジックデバイスの開発用ツールチェーンにAIを活用する場合、推論部32Aは、学習済モデルに入力されたクロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報が、配置配線の成功を示すクラスタに属しているか、それとも配置配線の失敗を示すクラスタに属しているかを判定する。そして、配置配線の成功を示すクラスタに属している場合、推論部32Aは、配置配線が成功すると推論する。一方、配置配線の失敗を示すクラスタに属している場合、推論部は配置配線が失敗すると推論する。

30

## 【0077】

あるいは、推論部32Aは、学習済モデルにデータ取得部31Aで取得したクロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報を入力することで、クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報が配置配線の成功を示すクラスタに属する確率を推論し、出力することとしてもよい。たとえば、学習済モデルに入力されたクロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報と、配置配線の成功を示すクラスタの重心との距離が小さいほど、

40

50

配置配線の成功を示すクラスタに属する確率が大きくなるものとしてもよい。

【0078】

あるいは、モデル生成部13Aは、K平均法の代わりに、ソフトクラスタリング手法を用いて、配置配線の成功を示すクラスタに属する確率を生成するモデルを生成し、推論部32Aは、ソフトクラスタリング手法を用いて、生成されたモデルから配置配線の成功を示すクラスタに属する確率を推論するものとしてもよい。

【0079】

本実施の形態では、プログラマブルロジックデバイスの開発用ツールチェーンのモデル生成部で学習した学習済モデルを用いて配置配線の成功確率を出力するものとして説明したが、他のプログラマブルロジックデバイスの開発用ツールチェーン等の外部から学習済モデルを取得し、この学習済モデルに基づいて配置配線の成功確率を出力するようにしてもよい。

10

【0080】

このようにして、推論部32Aは、クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報を基づいて得られた配置配線の成功確率をプログラマブルロジックデバイスの開発用ツールチェーンの入出力部に対して出力する。入出力部としては、例えばディスプレイなどの表示装置が挙げられる。

【0081】

次に、図8を用いて、推論装置30Aを使って配置配線の成功確率を得るための処理を説明する。

20

【0082】

図8は、実施の形態2における推論装置30Aの配置配線の成功確率の推論手順を表わすフローチャートである。

【0083】

ステップS401において、データ取得部31Aは、クロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報を取得する。

【0084】

ステップS402において、推論部32Aは、学習済モデル記憶部20Aに記憶された学習済モデルにクロック周波数、反復合成用パラメータ、テクノロジ毎のリソース使用率データ、およびテクノロジマッピング時のタイミングスラック情報を入力し、配置配線の成功確率を得る。

30

【0085】

ステップS403において、推論部32Aは、学習済モデルにより得られた配置配線の成功確率をプログラマブルロジックデバイスの開発用ツールチェーンに出力する。

【0086】

ステップS404において、プログラマブルロジックデバイスの開発用ツールチェーンは、出力された配置配線の成功確率を考慮して、プログラマブルデバイス上の実際のPE(Processing Element)、LE(Logic Element)、SRAM(Static Random Access Memory)およびインターフェクトリソースを用いた配置配線の試行を繰り返し、すなわち反復合成を行う。これにより、配置配線の成功確率をディスプレイなどの表示装置に表示することができる。

40

【0087】

なお、本実施の形態では、モデル生成部13Aおよび推論部32Aが用いる学習アルゴリズムに教師なし学習を適用した場合について説明したが、これに限られるものではない。学習アルゴリズムについては、教師なし学習以外にも、強化学習、教師あり学習、又は半教師あり学習等を適用することも可能である。

【0088】

また、学習に用いられる学習アルゴリズムとしては、特徴量そのものの抽出を学習する

50

、深層学習（Deep Learning）を用いることもでき、他の公知の方法でもよい。

【0089】

本実施形態における教師なし学習を実現する場合、上記のようなK平均(k-means)法による非階層型クラスタリングに限らず、クラスタリング可能な他の公知の方法であればよい。例えば、最短距離法等の階層型クラスタリングであってもよい。

【0090】

本実施の形態において、学習装置10A及び推論装置30Aは、例えば、ネットワークを介してプログラマブルロジックデバイスの開発用ツールチェーンに接続され、このプログラマブルロジックデバイスの開発用ツールチェーンとは別個の装置であってもよい。また、学習装置10A及び推論装置30Aは、プログラマブルロジックデバイスの開発用ツールチェーンに内蔵されていてもよい。さらに、学習装置10A及び推論装置30Aは、クラウドサーバ上に存在していてもよい。

10

【0091】

モデル生成部13Aは、複数のプログラマブルロジックデバイスの開発用ツールチェーンに対して作成される学習用データに従って、配置配線の成功確率を学習するようにしてもよい。なお、モデル生成部13Aは、同一のエリアで使用される複数のプログラマブルロジックデバイスの開発用ツールチェーンから学習用データを取得してもよいし、異なるエリアで独立して動作する複数のプログラマブルロジックデバイスの開発用ツールチェーンから収集される学習用データを利用して配置配線の成功確率を学習してもよい。また、学習用データを収集するプログラマブルロジックデバイスの開発用ツールチェーンを途中で対象に追加したり、対象から除去したりすることも可能である。さらに、あるプログラマブルロジックデバイスの開発用ツールチェーンに関して配置配線の成功確率を学習した学習装置を、これとは別のプログラマブルロジックデバイスの開発用ツールチェーンに適用し、当該別のプログラマブルロジックデバイスの開発用ツールチェーンに関して配置配線の成功確率を再学習して更新するようにしてもよい。

20

【0092】

図9は、学習装置10, 10A、推論装置30, 30A、またはプログラマブルロジックデバイスの開発用ツールチェーン40のハードウェア構成を表わす図である。

30

【0093】

学習装置10, 10A、推論装置30, 30A、およびプログラマブルロジックデバイスの開発用ツールチェーン40は、相当する動作をデジタル回路のハードウェアまたはソフトウェアで構成することができる。学習装置10, 10A、推論装置30, 30A、およびプログラマブルロジックデバイスの開発用ツールチェーン40の機能をソフトウェアを用いて実現する場合には、学習装置10, 10A、推論装置30, 30A、およびプログラマブルロジックデバイスの開発用ツールチェーン40は、例えば、図9に示すように、バス53によって接続されたプロセッサ51とメモリ52とを備え、メモリ52に記憶されたプログラムをプロセッサ51が実行するようにすることができる。

【0094】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本開示の範囲は上記した説明ではなくて請求の範囲によって示され、請求の範囲と均等の意味及び範囲内でのすべての変更が含まれることが意図される。

40

【符号の説明】

【0095】

10, 10A 学習装置、12, 12A データ取得部、13, 13A モデル生成部、14 報酬計算部、15 関数更新部、20, 20A 学習済みモデル記憶部、31, 31A データ取得部、32, 32A 推論部、40 プログラマブルロジックデバイスの開発用ツールチェーン、51 プロセッサ、52 メモリ、53 バス。

50

## 【図面】

## 【図1】

図1

## 【図2】

図2

## 【図3】

図3

## 【図4】

図4

10

20

30

40

50

【図 5】

図5

【図 6】

図6

10

【図 7】

図7

【図 8】

図8

20

30

【図 9】

図9

40

50

---

フロントページの続き

- (56)参考文献      特開2016-095606 (JP, A)

特表2020-506491 (JP, A)

特表2007-538474 (JP, A)

米国特許第07500216 (US, B1)

- (58)調査した分野 (Int.Cl., DB名)

G06F 30/00 - 30/398

H01L 21/82