(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-191336

(P2015-191336A)

(43) 公開日 平成27年11月2日(2015.11.2)

(51) Int.Cl.

**G06F 21/60** (2013.01)

**G06F 12/02** (2006.01)

**G06F 12/00** (2006.01)

F 1

G06F 21/24

G06F 12/02

G06F 12/02

G06F 12/00

テーマコード(参考)

5B060

160B

570A

530E

597U

審査請求 未請求 請求項の数 12 O L (全 21 頁)

(21) 出願番号

特願2014-66810(P2014-66810)

(22) 出願日

平成26年3月27日(2014.3.27)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】メモリ制御装置、情報処理装置とその制御方法、及びプログラム

## (57) 【要約】

【課題】 全てのデータを完全消去すると多くの時間を要し、パフォーマンスが低下するおそれがある。

【解決手段】 論理アドレスと不揮発性記憶装置の物理アドレスとを対応付けておき、不揮発性記憶装置のデータを完全に消去する完全消去モードが設定されている場合、不揮発性記憶装置の物理アドレスを完全消去対象とそれ以外とに分割して管理する。論理アドレスに基づいて不揮発性記憶装置に記憶されているデータの消去が指示されると、当該論理アドレスに対応付けられた物理アドレスが完全消去対象に属しているか否かを判定し、完全消去対象に属していると判定されると、その論理アドレスに対応付けられた物理アドレスのデータを完全に消去し、完全消去対象に属していないと判定されると、その論理アドレスに対応付けられた物理アドレスのデータのリンクを解除する。

【選択図】 図17

**【特許請求の範囲】****【請求項 1】**

不揮発性記憶装置へのアクセスを制御するメモリ制御装置であって、論理アドレスと前記不揮発性記憶装置の物理アドレスとを対応付けるアドレス手段と、前記不揮発性記憶装置のデータを完全に消去する完全消去モードを設定する設定手段と、

前記設定手段により前記完全消去モードが設定されている場合に、前記不揮発性記憶装置の物理アドレスを完全消去対象とそれ以外とに分割して管理する管理手段と、

前記論理アドレスに基づいて前記不揮発性記憶装置に記憶されているデータの消去が指示されると、当該論理アドレスに対応付けられた物理アドレスが前記完全消去対象に属しているか否かを判定する判定手段と、

前記判定手段により前記完全消去対象に属していると判定されると前記論理アドレスに対応付けられた物理アドレスのデータを完全に消去し、前記判定手段により前記完全消去対象に属していないと判定されると前記論理アドレスに対応付けられた物理アドレスのデータのリンクを解除するように制御する制御手段と、

を有することを特徴とするメモリ制御装置。

**【請求項 2】**

前記設定手段は、外部装置からのコマンドに従って前記完全消去モードを設定することを特徴とする請求項 1 に記載のメモリ制御装置。

**【請求項 3】**

前記コマンドは更に、前記完全消去モードの対象となる前記不揮発性記憶装置のアドレスを含むことを特徴とする請求項 2 に記載のメモリ制御装置。

**【請求項 4】**

前記不揮発性記憶装置は、NAND型フラッシュメモリであることを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載のメモリ制御装置。

**【請求項 5】**

不揮発性記憶装置にアクセスする情報処理装置であって、論理アドレスと前記不揮発性記憶装置の物理アドレスとを対応付けるアドレス手段と、前記不揮発性記憶装置のデータを完全に消去する完全消去モードを設定する設定手段と、

前記設定手段により前記完全消去モードが設定されている場合に、前記不揮発性記憶装置の物理アドレスを完全消去対象とそれ以外とに分割して管理する管理手段と、

前記不揮発性記憶装置に記憶されているデータの消去が指示されると、前記データの物理アドレスが前記完全消去対象に属しているか否かを判定する判定手段と、

前記判定手段により前記完全消去対象に属していると判定されると前記データを完全に消去し、前記判定手段により前記完全消去対象に属していないと判定されると前記データと前記論理アドレスとのリンクを解除するように制御する制御手段と、

を有することを特徴とする情報処理装置。

**【請求項 6】**

前記制御手段は、前記完全消去モードでは前記不揮発性記憶装置に記憶されているデータの消去が指示されると、前記データを全て 0 のデータに書き換えることを特徴とする請求項 5 に記載の情報処理装置。

**【請求項 7】**

前記アドレス手段は、前記論理アドレスと前記不揮発性記憶装置の物理アドレスとをブロック単位で対応付けることを特徴とする請求項 5 又は 6 に記載の情報処理装置。

**【請求項 8】**

前記完全消去対象に属している物理アドレスのブロックにデータを書き込む際は、当該ブロックに全て 1 のデータを書き込んだ後に前記データを書き込み、前記完全消去対象に属していない物理アドレスのブロックにデータを書き込む際は、当該ブロックに全て 0 のデータを書き込み、その後、全て 1 のデータを書き込んだ後に前記データを書き込む書き

10

20

30

40

50

込み手段を更に有することを特徴とする請求項 7 に記載の情報処理装置。

**【請求項 9】**

不揮発性記憶装置へのアクセスを制御するメモリ制御装置を制御する制御方法であって、

論理アドレスと前記不揮発性記憶装置の物理アドレスとを対応付けるアドレス工程と、前記不揮発性記憶装置のデータを完全に消去する完全消去モードを設定する設定工程と、

前記設定工程で前記完全消去モードが設定されている場合に、前記不揮発性記憶装置の物理アドレスを完全消去対象とそれ以外とに分割して管理する管理工程と、

前記論理アドレスに基づいて前記不揮発性記憶装置に記憶されているデータの消去が指示されると、当該論理アドレスに対応付けられた物理アドレスが前記完全消去対象に属しているか否かを判定する判定工程と、

前記判定工程で前記完全消去対象に属していると判定されると前記論理アドレスに対応付けられた物理アドレスのデータを完全に消去し、前記判定工程で前記完全消去対象に属していないと判定されると前記論理アドレスに対応付けられた物理アドレスのデータのリンクを解除するように制御する制御工程と、

を有することを特徴とするメモリ制御装置の制御方法。

**【請求項 10】**

不揮発性記憶装置にアクセスする情報処理装置を制御する制御方法であって、論理アドレスと前記不揮発性記憶装置の物理アドレスとを対応付けるアドレス工程と、前記不揮発性記憶装置のデータを完全に消去する完全消去モードを設定する設定工程と、

前記設定工程で前記完全消去モードが設定されている場合に、前記不揮発性記憶装置の物理アドレスを完全消去対象とそれ以外とに分割して管理する管理工程と、

前記不揮発性記憶装置に記憶されているデータの消去が指示されると、前記データの物理アドレスが前記完全消去対象に属しているか否かを判定する判定工程と、

前記判定工程で前記完全消去対象に属していると判定されると前記データを完全に消去し、前記判定工程で前記完全消去対象に属していないと判定されると前記データと前記論理アドレスとのリンクを解除するように制御する制御工程と、

を有することを特徴とする情報処理装置の制御方法。

**【請求項 11】**

コンピュータを、請求項 1 乃至 4 のいずれか 1 項にメモリ制御装置として機能させるためのプログラム。

**【請求項 12】**

コンピュータを、請求項 5 乃至 8 のいずれか 1 項に情報処理装置として機能させるためのプログラム。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、メモリ制御装置、情報処理装置とその制御方法、及びプログラムに関する。

**【背景技術】**

**【0002】**

NAND フラッシュメモリを制御する NAND フラッシュメモリコントローラは、NAND フラッシュメモリの寿命を延ばすために、ウェアレベリング (Wear-Leveling) を行うことが一般的に知られている。このウェアレベリングは、NAND フラッシュメモリコントローラによって様々な手法があり、そのウェアレベリングの実行タイミングも NAND フラッシュメモリコントローラにより異なる。

**【0003】**

いまシステムコントローラが NAND フラッシュメモリコントローラと接続される構成の場合、ウェアレベリングの実行後、システムコントローラが管理するテーブルのデータ

10

20

30

40

50

は、NANDフラッシュメモリの他のブロックにコピーされている可能性がある。このためシステムコントローラが、あるデータをセキュリティのために消去したとしても、そのデータが別の場所に残存している可能性がある。そこでこのような残存しているデータを完全に消去するために、NANDフラッシュメモリコントローラには、完全消去機能を有するものがある。この完全消去機能は、NANDフラッシュメモリコントローラが書き込んだデータに上書きして、そのデータを完全に消去する機能で、このデータの消去はNANDフラッシュメモリのブロック単位で実行される。このためNANDフラッシュメモリのブロックよりも小さいデータを消去する場合はパフォーマンスの低下が発生するおそれがあるため、例えば特許文献1には、これを解決する提案がなされている。

【先行技術文献】

10

【特許文献】

【0004】

【特許文献1】特開2012-191370号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記特許文献1では、完全消去モードが有効になったときに、ジョブのセキュリティレベルによって画像処理のパスを動的に切り替えることが記載されている。

【0006】

完全消去モードをオンにすると、フラッシュメモリに記憶されたデータが完全に消去されるためセキュリティレベルを維持できる。しかしながら、この場合は、ユーザ領域の全てのデータが完全消去の対象となってしまうため、完全消去をする必要がないデータに対しても完全消去を行ってしまう。このため、全てのデータを完全消去すると多くの時間を要し、パフォーマンスが低下するおそれがある。

20

【0007】

本発明の目的は、上記従来技術の問題点を解決することにある。

【0008】

本発明の特徴は、不揮発性記憶装置のメモリの全てを完全消去対象のエリアとせずに、完全消去対象のエリアとそれ以外のエリアとに分けて管理することにより、セキュリティレベルを維持しながら、パフォーマンスの低下を少なくすることにある。

30

【課題を解決するための手段】

【0009】

上記目的を達成するために本発明の一態様に係るメモリ制御装置は以下のような構成を備える。即ち、

不揮発性記憶装置へのアクセスを制御するメモリ制御装置であって、

論理アドレスと前記不揮発性記憶装置の物理アドレスとを対応付けるアドレス手段と、前記不揮発性記憶装置のデータを完全に消去する完全消去モードを設定する設定手段と、

前記設定手段により前記完全消去モードが設定されている場合に、前記不揮発性記憶装置の物理アドレスを完全消去対象とそれ以外とに分割して管理する管理手段と、

前記論理アドレスに基づいて前記不揮発性記憶装置に記憶されているデータの消去が指示されると、当該論理アドレスに対応付けられた物理アドレスが前記完全消去対象に属しているか否かを判定する判定手段と、

前記判定手段により前記完全消去対象に属していると判定されると前記論理アドレスに対応付けられた物理アドレスのデータを完全に消去し、前記判定手段により前記完全消去対象に属していないと判定されると前記論理アドレスに対応付けられた物理アドレスのデータのリンクを解除するように制御する制御手段と、を有することを特徴とする。

【発明の効果】

【0010】

本発明によれば、不揮発性記憶装置のデータのセキュリティレベルを維持しながら、不

40

50

揮発性記憶装置のデータを消去する際のパフォーマンスの低下を少なくできる効果がある。

【0011】

本発明のその他の特徴及び利点は、添付図面を参照とした以下の説明により明らかになるであろう。なお、添付図面においては、同じ若しくは同様の構成には、同じ参照番号を付す。

【図面の簡単な説明】

【0012】

添付図面は明細書に含まれ、その一部を構成し、本発明の実施の形態を示し、その記述と共に本発明の原理を説明するために用いられる。

10

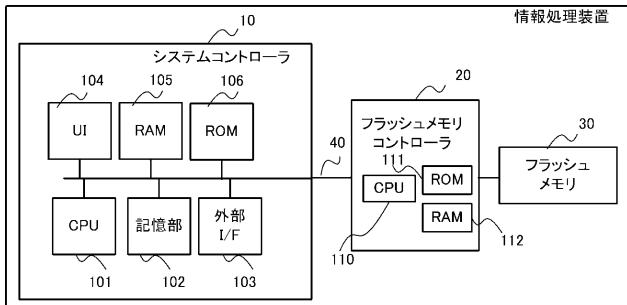

【図1】本実施形態に係る情報処理装置の構成を示すブロック図。

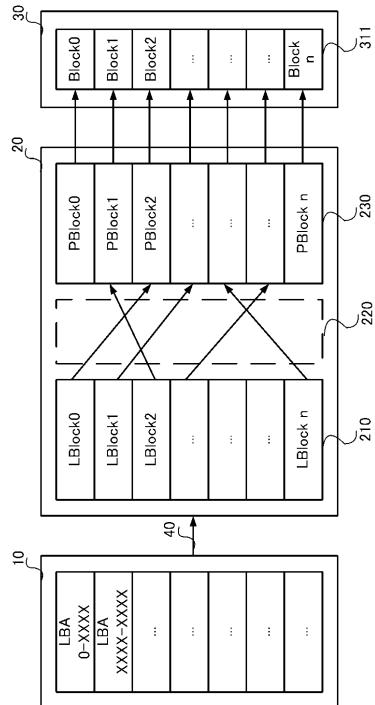

【図2】実施形態に係るフラッシュメモリのアドレス管理を説明する概念図。

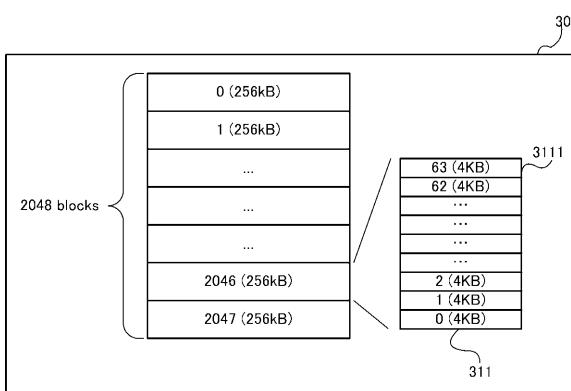

【図3】実施形態に係る4ギガビットのフラッシュメモリのブロックとページの概念を説明する図。

【図4】実施形態に係るフラッシュメモリコントローラのリンクテーブルの概念図。

【図5】実施形態に係るフラッシュメモリコントローラが書き込みコマンド（ライトコマンド）を受信した場合の処理を説明するフローチャート。

【図6】実施形態に係るフラッシュメモリコントローラがライトコマンドを受信した場合のリンクテーブルの遷移を説明する図。

【図7】実施形態に係るフラッシュメモリコントローラが消去コマンドを受信した場合の処理を説明するフローチャート。

20

【図8】実施形態に係るフラッシュメモリコントローラが消去コマンドを受信した場合のリンクテーブルの遷移を説明する図。

【図9】実施形態に係るフラッシュメモリコントローラが消去コマンドを受信した場合のリンクテーブルの接続変化を説明する図。

【図10】実施形態に係るフラッシュメモリコントローラによるフラッシュメモリのブロック初期化処理を説明するフローチャート。

【図11】実施形態に係るフラッシュメモリコントローラによるフラッシュメモリのブロック初期化処理におけるリンクテーブルの遷移を説明する図。

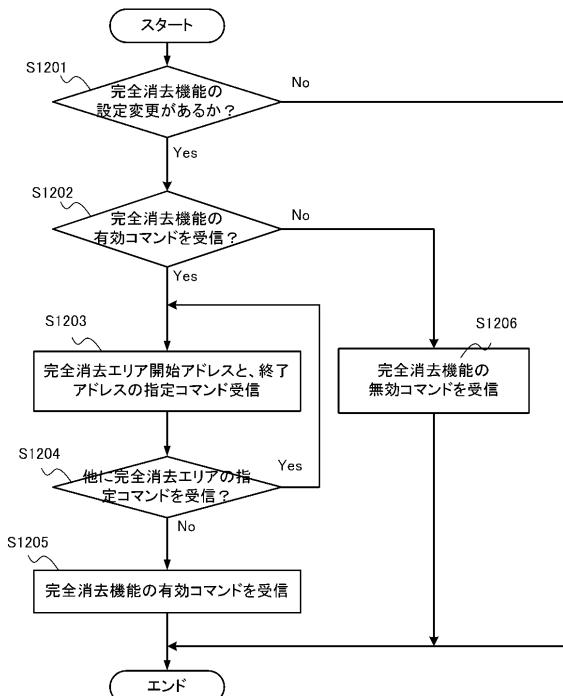

【図12】実施形態1に係るフラッシュメモリコントローラが、リンクテーブルのメインエリアに完全消去エリアを設ける処理を説明するフローチャート。

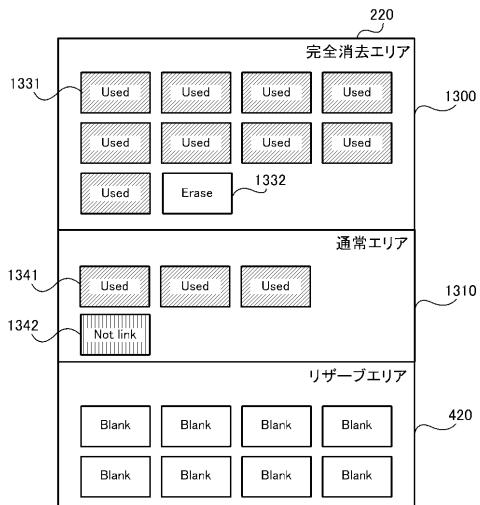

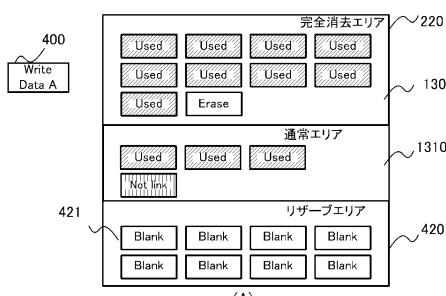

【図13】実施形態1に係るフラッシュメモリコントローラが、リンクテーブルのメインエリアを完全消去エリアと通常エリアとに分割した状態を説明する図。

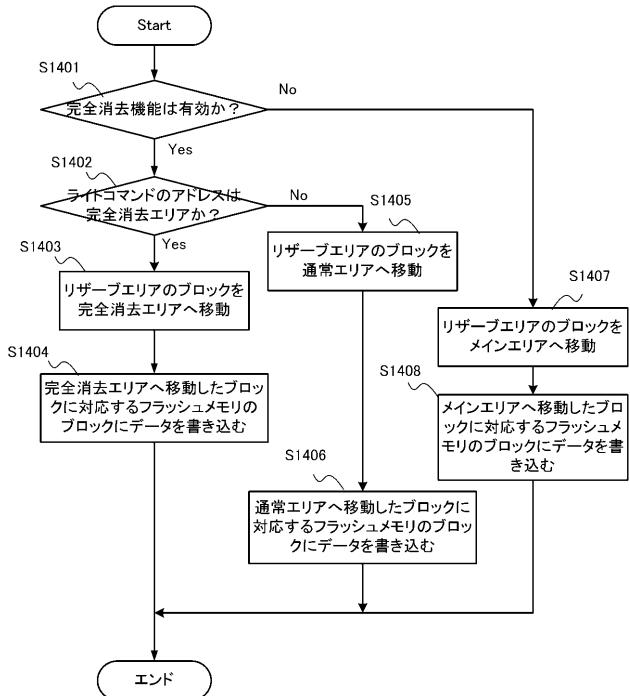

【図14】実施形態1に係るフラッシュメモリコントローラが、リンクテーブルのメインエリアを完全消去エリアと通常エリアとに分割して管理しているときにライトコマンドを受信した場合の処理を示すフローチャート。

【図15】実施形態1に係るフラッシュメモリコントローラが完全消去エリアにデータを書き込むときのリンクテーブルの遷移を説明する図。

【図16】実施形態1に係るフラッシュメモリコントローラが通常エリアにデータを書き込むときのリンクテーブルの遷移を説明する図。

40

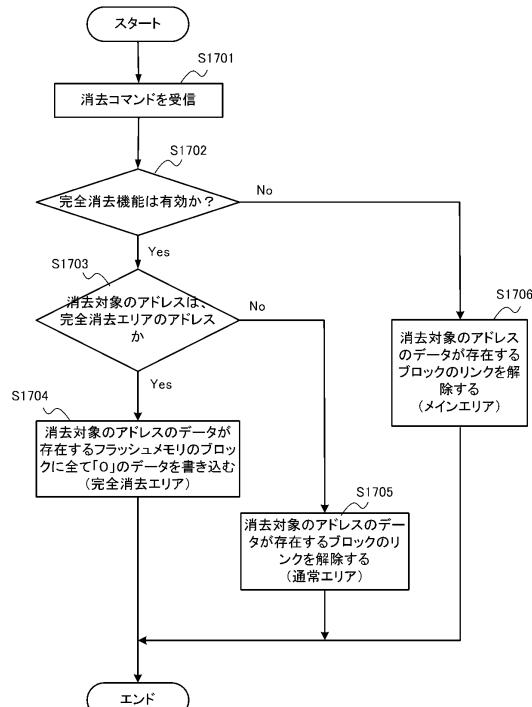

【図17】実施形態1に係るフラッシュメモリコントローラが、完全消去エリアと通常エリアとに分割して管理している場合に消去コマンドを受信したときの処理を説明するフローチャート。

【図18】実施形態1に係るフラッシュメモリコントローラが完全消去エリアのデータを消去するときのリンクテーブルの遷移を説明する図。

【図19】実施形態1に係るフラッシュメモリコントローラが通常エリアのアドレスのデータを消去するコマンドを受信した場合のブロックの変化を説明する図。

【図20】実施形態1に係るフラッシュメモリコントローラが、完全消去エリアと通常エリアとに分けて管理している場合のブロック初期化処理を説明するフローチャート。

【図21】図20のブロック初期化処理におけるリンクテーブルの遷移を説明する図。

50

**【発明を実施するための形態】**

**【0013】**

以下、添付図面を参照して本発明の実施形態を詳しく説明する。尚、以下の実施形態は特許請求の範囲に係る本発明を限定するものでなく、また本実施形態で説明されている特徴の組み合わせの全てが本発明の解決手段に必須のものとは限らない。以下の実施形態では、本発明のメモリ制御装置を、不揮発性記憶装置であるNAND型フラッシュメモリへのデータの読み書き（アクセス）を制御するフラッシュメモリコントローラを例に説明する。

**【0014】**

図1は、本実施形態に係る情報処理装置の構成を示すブロック図である。

10

**【0015】**

この情報処理装置は、装置全体の動作を制御するシステムコントローラ10と、NANDフラッシュメモリ（以下、フラッシュメモリ）30を制御するNANDフラッシュメモリコントローラ（以下、フラッシュメモリコントローラ）20とを有している。

**【0016】**

システムコントローラ10は、フラッシュメモリコントローラ20と汎用のバス40で接続される。システムコントローラ10は、CPU101、記憶部102、外部I/F103、UI（ユーザインターフェース）104、RAM105、ROM106を有し、これらはバスを介して相互に接続されている。CPU101は、装置の起動時、ROM106からブートプログラムを読み出して実行し、記憶部102に格納されているプログラムをRAM105へ展開する。そしてCPU101は、そのRAM105に展開されたプログラムを実行して、この装置の動作を制御する。またCPU101は、UI104に画像データを出力してユーザインターフェースの画面を表示する。また外部I/F103にはUSBメモリ等が接続される。

20

**【0017】**

フラッシュメモリコントローラ20は、CPU110、ROM111、RAM112を有する。フラッシュメモリコントローラ20は、システムコントローラ10のCPU101が指定した、フラッシュメモリ30のアドレスへのデータのリード／ライト／イレース等のコマンドを受信する。フラッシュメモリコントローラ20は、システムコントローラ10からコマンドを受け取ると、そのコマンドに応じた処理をフラッシュメモリ30に対して行う。

30

**【0018】**

フラッシュメモリコントローラ20のCPU110は、ROM111に格納されているプログラムに従ってフラッシュメモリコントローラ20の動作を制御する。RAM112は、CPU110による制御の際にCPU110が使用する各種データを一時的に保存するワークエリアを提供している。

**【0019】**

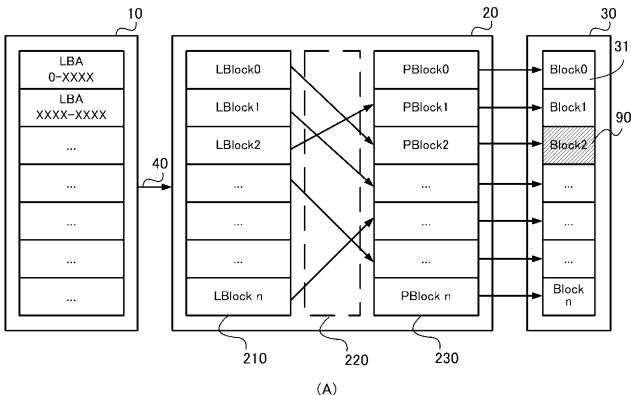

図2は、実施形態に係るフラッシュメモリのアドレス管理を説明する概念図である。ここで汎用バス40は、SATA/I/Fを例に説明する。

40

**【0020】**

システムコントローラ10のCPU101は、LBA方式で指定したアドレスに対してリード／ライト等のコマンドをフラッシュメモリコントローラ20へ発行する。フラッシュメモリコントローラ20は、CPU101から受信したライト／イレースのコマンドから論理ブロック（LBlock）210と物理ブロック230の関係を表すリンクテーブル220を作成する。リンクテーブル220を図2の例で説明すると、LBlock0はPBlock2と接続され、LBlock2はPBlock1と接続されるリンクテーブル220となっており、この関係はウェアレベリングが実行されることで更新される。フラッシュメモリコントローラ20の物理ブロック230であるPBlock0, 1, 2, ..., nは、それぞれフラッシュメモリ30のブロック311のBlock0, 1, 2..., nと1対1で接続され、この関係が崩れることはない。

50

**【0021】**

図3は、実施形態に係る4ギガビットのフラッシュメモリ30のブロックとページの概念を説明する図である。

**【0022】**

フラッシュメモリ30は、4ギガビット( $=256\text{Kビット} \times 2048$ )のサイズで、それぞれが256キロビットの2048個のブロック311で構成される。ここで各ブロック311は64個のページ3111で構成され、一つのページ3111のサイズは4Kビットである。フラッシュメモリコントローラ20は、フラッシュメモリ30へデータを書き込む場合は、ページ単位でデータを書き込む。またフラッシュメモリコントローラ20が、フラッシュメモリ30のデータを消去する場合は、ブロック単位でデータの消去を行う。

10

**【0023】**

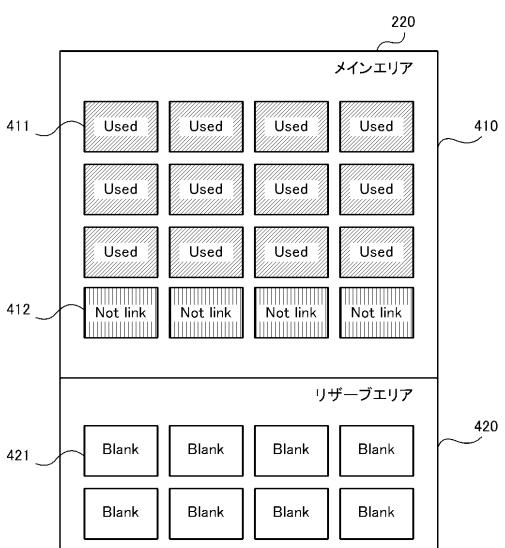

図4は、実施形態に係るフラッシュメモリコントローラ20のリンクテーブル220の概念図で、ここではフラッシュメモリ30へデータを書き込んだ後の状態を示している。

**【0024】**

リンクテーブル220は、ユーザ領域であるメインエリア410とリザーブエリア420の二つの領域を備えている。尚、このユーザ領域以外にも、フラッシュメモリコントローラ20が管理するシステム領域が存在するが、本実施形態ではそれらの領域に関する説明を割愛する。メインエリア410には、有効データが記憶されているフラッシュメモリ30のブロック311に対応する使用済ブロック411と、論理ブロック210とのリンクが解除されたフラッシュメモリ30のブロックに対応するブロック412とが存在する。この論理ブロック210とリンクが解除されたブロック412に対応するフラッシュメモリ30のブロック311のデータは、リンクが解除されているためシステムコントローラ10から読み出すことはできない。しかし、フラッシュメモリ30に対して直接リードコマンドを発行した場合は、そのデータ自体はフラッシュメモリ30に残存しているため読み出すことができる。リザーブエリア420には、複数の書き込み可能な空きブロック421を含んでいる。この書き込み可能な空きブロック421とは、フラッシュメモリ30が書き込み可能なように、全ビットが「1」に初期化されたブロックである。

20

**【0025】**

メインエリア410とリザーブエリア420のブロック数は、フラッシュメモリコントローラ20のファームウェア等で予め決まっており、フラッシュメモリ30が未使用状態では、メインエリア410のブロックは全て空きブロックである。

30

**【0026】**

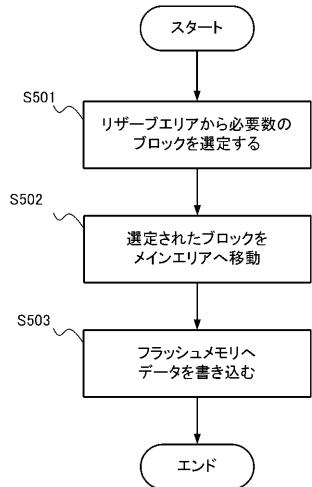

図5は、実施形態に係るフラッシュメモリコントローラ20が書き込みコマンド(ライトコマンド)を受信した場合の処理を説明するフローチャートである。この処理を実行するプログラムはROM111に記憶されており、CPU110がそのプログラムを実行することによりこの処理が達成される。

**【0027】**

図6は、実施形態に係るフラッシュメモリコントローラ20がライトコマンドを受信した場合のリンクテーブル220の遷移を説明する図である。図5のフローチャートを図6のリンクテーブルのブロック遷移を参照しながら説明する。

40

**【0028】**

図5の処理は、フラッシュメモリコントローラ20がシステムコントローラ10からライトコマンドを受信することにより開始される。このときリンクテーブル220の状態は、図6(A)に示す状態であるとし、ライトコマンドで書き込まれるデータはライトデータA400で示されている。

**【0029】**

まずS501でCPU110は、その受信したライトデータA400をフラッシュメモリ30に書き込むために、そのライトデータA400のデータサイズから、そのデータを書き込むのに必要なブロック数を求める。そして、その求めた数のブロックをリザーブエ

50

リア420から選定する。尚、図6(A)では、ライトデータA400のサイズは、1ブロック以下のサイズとする。

#### 【0030】

次にS502に進みCPU110は、S501で選定した数のブロックを、リザーブエリア420からメインエリア410に移動する。この状態を図6(B)に示す。図6(B)では、リンクテーブル220のリザーブエリア420にある一つの空きブロック421をメインエリア410へ移動している。

#### 【0031】

次にS503に進みCPU110は、メインエリア410へ移動したブロック421に対応するフラッシュメモリ30のブロックへ、そのデータA400を書き込んで、図6(C)に示すように、リンクテーブル220を更新する。10

#### 【0032】

ここでライトデータA400のサイズは、一つのブロックのサイズ以下となっているため、リザーブエリア420からメインエリア410に移動する空きブロック421の数は一つである。しかしながら、そのデータサイズが複数ブロックのサイズに相当している場合は、リザーブエリア420から複数の空きブロック421をメインエリア410へ移動する。

#### 【0033】

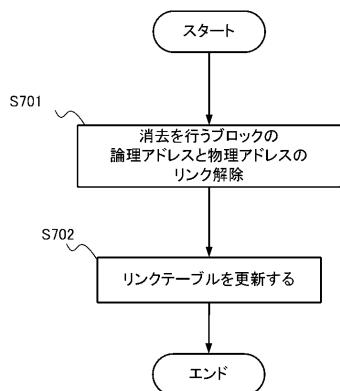

図7は、実施形態に係るフラッシュメモリコントローラ20が消去コマンドを受信した場合の処理を説明するフローチャートである。この処理を実行するプログラムはROM11に記憶されており、CPU110がそのプログラムを実行することによりこの処理が達成される。20

#### 【0034】

図8は、実施形態に係るフラッシュメモリコントローラ20が消去コマンドを受信した場合のリンクテーブル220の遷移を説明する図である。

#### 【0035】

図9は、実施形態に係るフラッシュメモリコントローラ20が消去コマンドを受信した場合のリンクテーブル220の接続変化を説明する図である。以下、図7のフローチャートを、図8、図9を参照して説明する。

#### 【0036】

図7の処理は、フラッシュメモリコントローラ20が、システムコントローラ10から、フラッシュメモリ30のB10ck2(901)のデータを消去する消去コマンドを受信することにより開始される。このときリンクテーブル220は、図8(A)に示す状態であり、リンクテーブル220の接続は図9(A)に示す状態とする。30

#### 【0037】

まずS701でCPU110は、消去対象のデータの論理アドレス(LB10ck0)と物理アドレス(PB10ck2)のリンクを解除する。図9(A)では、フラッシュメモリコントローラ20は、フラッシュメモリ30のブロック901を、論理アドレス210(LB10ck0)と物理ブロック230(PB10ck2)に対応付けて管理している。40

#### 【0038】

図9(B)では、フラッシュメモリコントローラ20が、フラッシュメモリ30のB10ck2(901)のデータの消去コマンドを受信することにより、LB10ck0とPB10ck2のリンクが解除された状態を示している。

#### 【0039】

次にS702に進みCPU110は、S701でリンクを解除したリンクテーブル220を更新する。このとき図8(B)に示すように、フラッシュメモリコントローラ20は、フラッシュメモリ30のB10ck2(901)に対応するメインエリア410のブロック801のリンクを解除する。このとき図9(B)に示すように、ブロック901とリンクテーブル220の論理アドレスとのリンクは解除されているが、フラッシュメモリ3

0 の B l o c k 2 のデータは、フラッシュメモリ 3 0 に残存している。

【 0 0 4 0 】

このようにフラッシュメモリ 3 0 のあるブロックのデータの消去コマンドを受信すると、そのブロックと論理アドレスとのリンクが解除されることにより、そのフラッシュメモリ 3 0 のブロックのデータは読み出せなくなる。しかしながら、フラッシュメモリ 3 0 のそのブロックのデータは残存したままとなる。

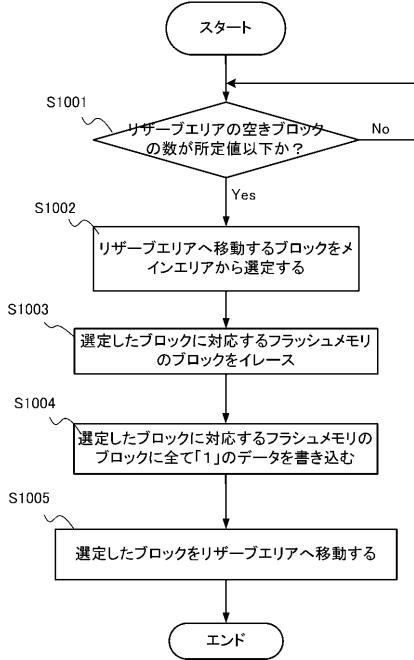

【 0 0 4 1 】

図 1 0 は、実施形態に係るフラッシュメモリコントローラ 2 0 によるフラッシュメモリ 3 0 のブロック初期化処理を説明するフローチャートである。この処理を実行するプログラムは R O M 1 1 1 に記憶されており、C P U 1 1 0 がそのプログラムを実行することによりこの処理が達成される。

10

【 0 0 4 2 】

図 1 1 は、実施形態に係るフラッシュメモリコントローラ 2 0 によるフラッシュメモリ 3 0 のブロック初期化処理によるリンクテーブル 2 2 0 の遷移を説明する図である。以下、図 1 0 のフローチャートを図 1 1 を参照しながら説明する。

【 0 0 4 3 】

まず S 1 0 0 1 で C P U 1 1 0 は、リザーブエリア 4 2 0 の空きブロックの数が所定値以下になったかどうか判定する。図 1 1 ( A ) では、リザーブエリア 4 2 0 の空きブロック 4 2 1 の数が「 5 」になっている。ここでは、所定値を「 8 」として説明する。図 1 1 ( A ) は、リザーブエリア 4 2 0 の空きブロックの数が 5 であるため、リザーブエリア 4 2 0 のブロック数が所定値以下になったと判定して S 1 0 0 2 へ進む。

20

【 0 0 4 4 】

S 1 0 0 2 で C P U 1 1 0 は、リザーブエリア 4 2 0 へ移動するブロックをメインエリア 4 1 0 の中のリンクのないブロック 4 1 2 から選定する。ここでは図 1 1 ( A ) に示すブロック 1 1 1 1 , 1 1 1 2 , 1 1 1 3 を選定する。この実施形態では、ブロックの消去回数が少ない順にブロックを選定するが、この選定手法は他の手法でも構わない。

【 0 0 4 5 】

次に S 1 0 0 3 に進み C P U 1 1 0 は、S 1 0 0 2 で選定したブロック 1 1 1 1 , 1 1 1 2 , 1 1 1 3 に対応するフラッシュメモリ 3 0 のブロックに全て「 0 」を書き込んでイレースする。このイレースは、ブロックの電荷を抜くことである(図 1 1 ( B ) )。

30

【 0 0 4 6 】

次に S 1 0 0 4 に進み C P U 1 1 0 は、S 1 0 0 2 で選定したブロック 1 1 1 1 , 1 1 1 2 , 1 1 1 3 に対応するフラッシュメモリ 3 0 のブロックに全て「 1 」を書き込んで初期化する。

【 0 0 4 7 】

次に S 1 0 0 5 に進み C P U 1 1 0 は、S 1 0 0 2 で選定したブロックを、メインエリア 4 1 0 からリザーブエリア 4 2 0 へ移動する。図 1 1 ( C ) は、このときのリンクテーブル 2 2 0 のイメージ図である。図 1 1 ( C ) では、S 1 0 0 2 で選定したメインエリア 4 1 0 のブロック 1 1 1 1 , 1 1 1 2 , 1 1 1 3 をリザーブエリア 4 2 0 へ移動している。

40

【 0 0 4 8 】

尚、リザーブエリア 4 2 0 へ移動されたブロック 1 1 1 1 ~ 1 1 1 3 に対応するフラッシュメモリ 3 0 のブロックは全て「 1 」で初期化されているため、そのブロックには直ぐにデータを書き込むことができる。

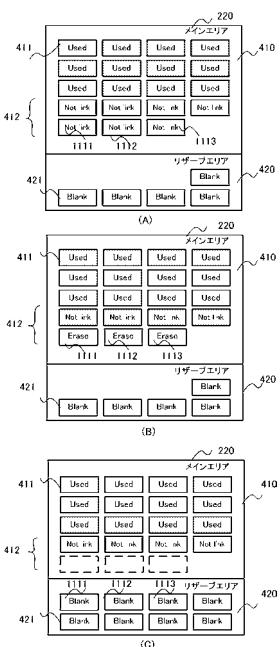

【 0 0 4 9 】

[ 実施形態 1 ]

以下、本実施形態 1 に係るリンクテーブル 2 2 0 のメインエリア 2 2 0 に、完全消去エリア 1 3 0 0 と通常エリア 1 3 1 0 を設けた例について説明する。

【 0 0 5 0 】

図 1 2 は、実施形態 1 に係るフラッシュメモリコントローラ 2 0 が、リンクテーブル 2

20のメインエリアに完全消去エリアを設ける処理を説明するフローチャートである。この処理を実行するプログラムはROM111に記憶されており、CPU110がそのプログラムを実行することによりこの処理が達成される。

#### 【0051】

この処理は、実施形態1に係る情報処理装置の電源がオンされることにより開始される。先ずS1201でCPU110は、完全消去機能の設定変更があるかどうかを判定し、設定変更がある場合はS1202に進むが、設定変更がないときは、そのまま処理を終了する。尚、この完全消去機能の設定は、フラッシュメモリ30に保持されており、情報処理装置の電源オフ時の設定が、情報処理装置の電源オン時に反映される。S1202でCPU110は、完全消去機能を有効にするか否かを判定する。ここではCPU1100は、システムコントローラ10から完全消去機能を有効にするコマンドを受信したかどうかを判定し、そのコマンドを受信した場合はS1203に進み、そのコマンドを受信しないときはS1206へ移行する。10

#### 【0052】

S1203でCPU110は、システムコントローラ10から完全消去エリア1300の開始アドレスと終了アドレスとを受信し、フラッシュメモリ30へ、その設定を格納してS1204へ進む。S1204でCPU110は、システムコントローラ10から他に完全消去エリア1300の指定のコマンドを受信したかどうかを判定し、他に完全消去エリアの指定コマンドを受信した場合はS1203に進んで前述の処理を実行する。一方、他に完全消去エリアの指定コマンドを受信していないときはS1205に進む。S1205でCPU110は、完全消去機能の有効コマンドをシステムコントローラ10から受信して、この処理を終了する。一方、S1206でCPU110は、システムコントローラ10から完全消去機能の無効コマンドを受信して、この処理を終了する。20

#### 【0053】

尚、事前に設定されている完全消去エリア1300の開始アドレスと終了アドレスは、フラッシュメモリ30で保持される。また完全消去機能が無効になったとしても、フラッシュメモリ30で保持される完全消去エリア1300の開始アドレスと終了アドレスはマスクされるだけである。また完全消去機能の設定と開始アドレス、終了アドレスの設定は、フラッシュメモリ30のシステム領域に保存される。30

#### 【0054】

このように実施形態1に係るフラッシュメモリコントローラ20は、システムコントローラ10から完全消去エリア1300の指定のコマンドを受信すると、図13に示すように、メインエリア220に完全消去エリア1300と通常エリア1310を設ける。

#### 【0055】

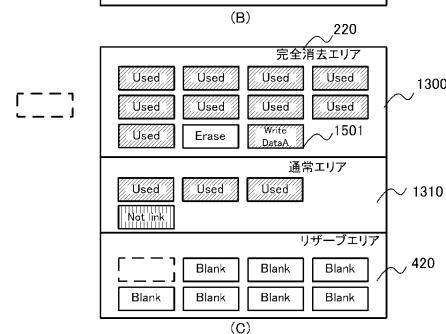

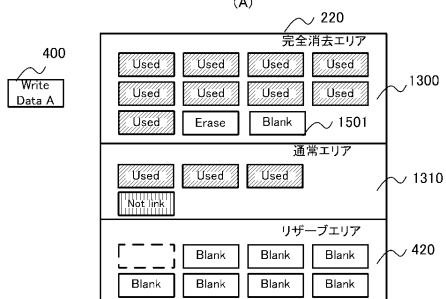

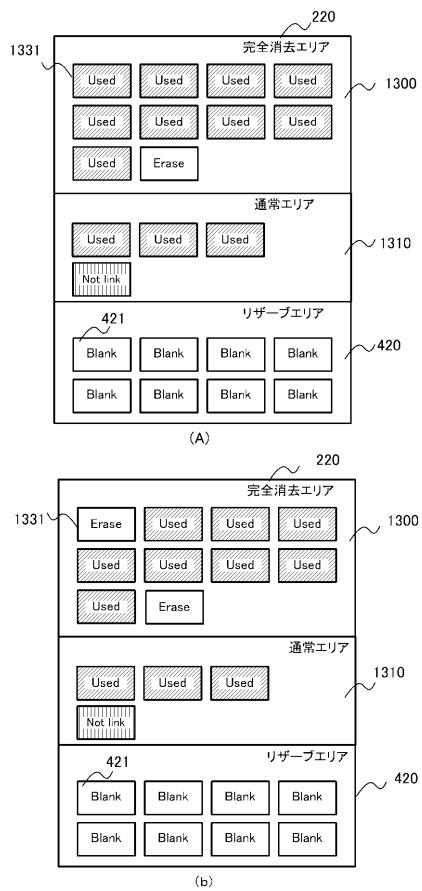

図13は、実施形態1に係るフラッシュメモリコントローラ20が、リンクテーブル220のメインエリア410を完全消去エリア1300と通常エリア1310とに分割した例を説明する図である。図13では、フラッシュメモリ30のブロックが、完全消去エリア1300と通常エリア1310、リザーブエリア420のブロックに対応している。40

#### 【0056】

完全消去エリア1300は、使用中のフラッシュメモリ30のブロックに対応するブロック1331と、イレース済みのフラッシュメモリ30のブロックに対応するブロック1332とを含む。通常エリア1310のブロックは、使用中のフラッシュメモリ30のブロックに対応するブロック1341と、システムコントローラ10の論理ブロックとのリンクが解除されたブロック1342とを含む。

#### 【0057】

ここで、イレース済みのフラッシュメモリ30のブロックには、全て「1」のデータが書き込まれて初期化されている。

#### 【0058】

図14は、実施形態に係るフラッシュメモリコントローラ20が、リンクテーブル220のメインエリア410を完全消去エリア1300と通常エリア1310とに分割して管50

理しているときにライトコマンドを受信した場合の処理を示すフローチャートである。この処理を実行するプログラムはROM111に記憶されており、CPU110がそのプログラムを実行することによりこの処理が達成される。

#### 【0059】

この処理は、フラッシュメモリコントローラ20がシステムコントローラ10からライトコマンドを受信することにより開始される。まずS1401でCPU110は、フラッシュメモリ30に格納される完全消去機能の設定を読み出し、その完全消去機能が有効かどうかを判定する。ここで完全消去機能が有効であると判定するとS1402に進み、無効であればS1407へ移行する。S1402でCPU110は、受信したライトコマンドの書き込みアドレスが示すブロックは、完全消去エリア1300のブロックに対応しているかどうかを判定する。ここで完全消去エリア1300のブロックに対応していると判定するとS1403に進みそうでないときはS1405に進む。10

#### 【0060】

S1403でCPU110は、リザーブエリア420のブロックを完全消去エリア1300へ移動する。

#### 【0061】

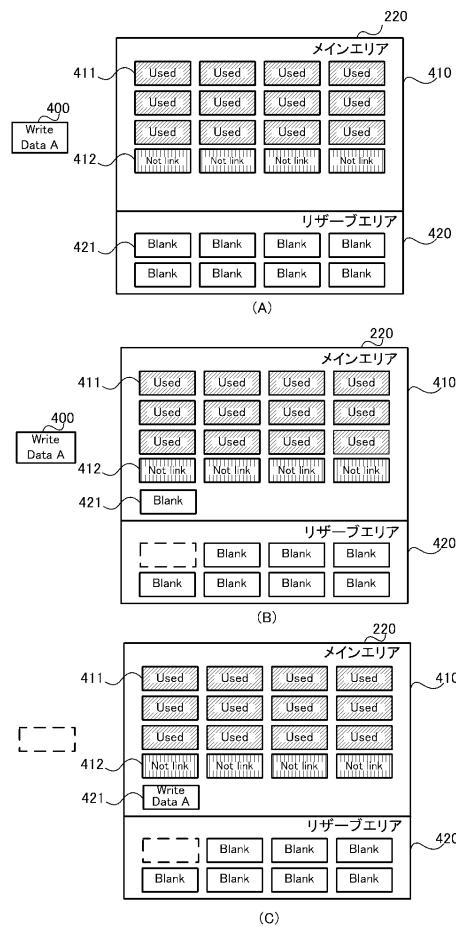

図15は、実施形態に係るフラッシュメモリコントローラ20が完全消去エリアにデータを書き込むときのリンクテーブル220の遷移を説明する図である。

#### 【0062】

図15(A)は、完全消去エリア1300、通常エリア1310、リザーブエリア420に各ブロックが配置されている状態を示す。ここで、フラッシュメモリコントローラ20がフラッシュメモリ30に書き込みたいデータはライトデータA400である。図15(B)では、完全消去エリア1300のブロックに対応するフラッシュメモリ30のブロックにデータを書き込むために、完全消去エリア1300へリザーブエリア420の空きブロック1501を移動した状態を示す図である。20

#### 【0063】

こうしてS1403の処理を実行するとS1404へ処理を進めCPU110は、S1403で完全消去エリア1300に移動した空きブロック1501に対応するフラッシュメモリ30のブロックにデータA400を書き込んで処理を終了する(図15(C))。

#### 【0064】

これにより、ライトコマンドで指定されたデータは、フラッシュメモリ30の完全消去エリアに対応するブロックに書き込まれる。従って、このブロックに書き込まれたデータが消去されるときは、完全消去モードで消去されることになる。30

#### 【0065】

一方、S1405でCPU110は、リザーブエリア420の空きブロック421を通常エリア1310へ移動する。

#### 【0066】

図16は、実施形態に係るフラッシュメモリコントローラ20が通常エリア1310にデータを書き込むときのリンクテーブル220の遷移を説明する図である。

#### 【0067】

図16(A)では、完全消去エリア1300、通常エリア1310、リザーブエリア420に各ブロックが配置されている状態を示す。ここでも、フラッシュメモリコントローラ20がフラッシュメモリ30に書き込みたいデータはライトデータA400である。図16(B)は、通常エリア1310のデータライトコマンドを受信したことにより、S1405で、リザーブエリア420の空きブロック1601を通常エリア1310へ移動した状態を示す。40

#### 【0068】

次にS1406に進みCPU110は、通常エリア1310へ移動した空きブロック1601に対応するフラッシュメモリ30のブロックにデータA400を書き込んで、この処理を終了する。この状態を図16(C)に示す。50

## 【0069】

またS1407でCPU110は、図5及び図6を参照して説明した完全消去エリア1300と通常エリア1310とに分けていない場合の通常の書き込み処理で、リザーブエリア420のブロックをメインエリア410へ移動する。そしてS1408に進みCPU110は、S1407でメインエリア410へ移動したブロックに対応するフラッシュメモリ30のブロックにデータA400を書き込んで、この処理を終了する。

## 【0070】

このようにして、ライコマンドを受信すると、完全消去機能が有効であるとき、そのデータを書き込むブロックが完全消去エリアに対応するかどうかにより、リンクテーブル220で、その書き込んだブロックを完全消去エリアに配置するかどうかを制御する。これにより、そのデータの消去コマンドを受信したときの処理が、以下に説明するように異なってくる。

10

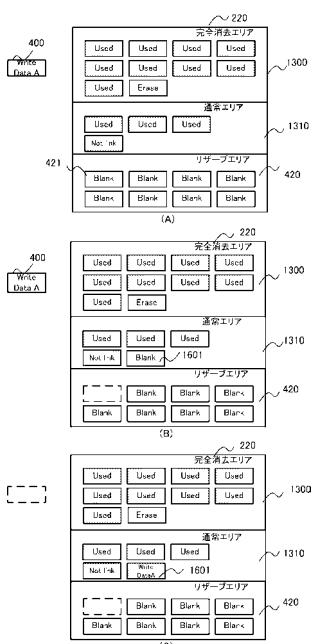

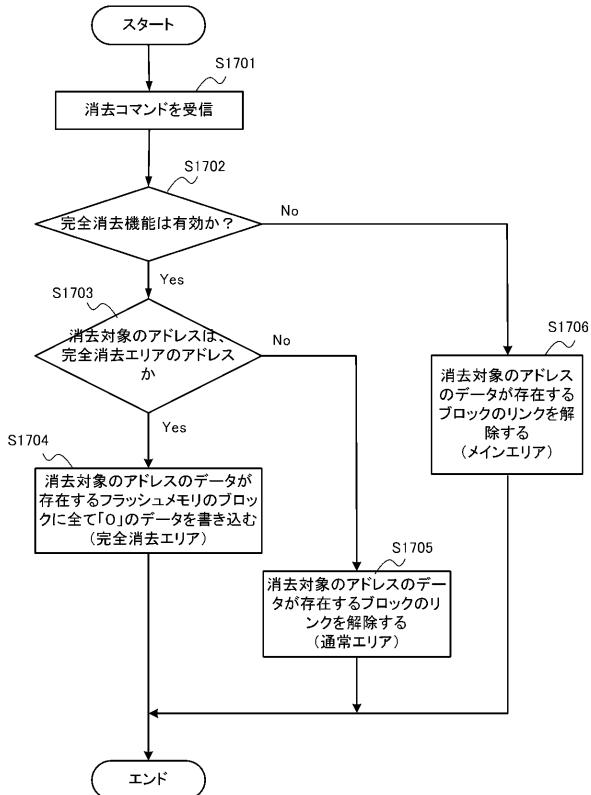

## 【0071】

図17は、実施形態1に係るフラッシュメモリコントローラ20が、リンクテーブル220のメインエリア410を完全消去エリア1300と通常エリア1310とに分割している場合に、消去コマンドを受信したときの処理を説明するフローチャートである。この処理を実行するプログラムはROM111に記憶されており、CPU110がそのプログラムを実行することによりこの処理が達成される。

## 【0072】

20

まずS1701でCPU110は、システムコントローラ10から消去コマンドを受信する。次にS1702に進みCPU110は、フラッシュメモリ30に格納された完全消去機能の設定に基づいて、完全消去機能が有効かどうかを判定する。ここで完全消去機能が有効に設定されていると判定するとS1703へ進み、無効と判定するとS1706へ進む。S1703でCPU110は、消去対象に指示されたアドレスが、完全消去エリア1300のブロックに属するアドレスかどうかを判定する。ここで消去対象のアドレスが、完全消去エリア1300のブロックに属するアドレスであると判定するとS1704に進むが、消去対象のアドレスが通常エリア1310のブロックに対応するアドレスであると判定したときはS1705へ進む。

## 【0073】

30

S1704でCPU110は、消去対象のアドレスを含むフラッシュメモリ30のブロックを全て「0」で上書きして、この処理を終了する。一方、S1705でCPU110は、通常エリア1310のブロックに対応しているため、消去対象のアドレスが存在するブロックのリンクを解除して、この処理を終了する。

## 【0074】

また完全消去機能が無効に設定されているときはS1706に進みCPU110は、完全消去機能が無効なので図7で説明した通常の動作と同様の処理を実行する。即ち、メインエリア410に存在する、指定されたアドレスを含むフラッシュメモリ30のブロックのリンクを解除して、この処理を終了する。

## 【0075】

40

図18は、実施形態1に係るフラッシュメモリコントローラ20が完全消去エリア1300のデータを消去するときのリンクテーブル220の遷移を説明する図である。

## 【0076】

図18(A)は、フラッシュメモリコントローラ20が完全消去エリア1300の対象アドレスのデータを消去するコマンドを受信する前のリンクテーブル220の状態を示す図である。

## 【0077】

フラッシュメモリコントローラ20が、完全消去エリア1300のブロック1331に対応するフラッシュメモリ30のブロックを消去する場合、完全消去が実行される。このときブロック1331に対応するフラッシュメモリ30のブロックはイレースされ、そのブロックに全て「0」のデータが書き込まれる。その状態を図18(B)に示す。

50

**【0078】**

このように実施形態1では、完全消去エリア1300のブロック1331に対応するフラッシュメモリ30のブロックのデータを消去するときは、そのブロックに全て「0」のデータが書き込まれる。

**【0079】**

図19は、実施形態1に係るフラッシュメモリコントローラ20が通常エリア1310のアドレスのデータを消去するコマンドを受信した場合のブロックの変化を説明する図である。

**【0080】**

図19(A)は、通常エリア1310のアドレスのデータを消去するコマンドを受信する前のリンクテーブル220の状態を示す。 10

**【0081】**

図19(B)は、通常エリア1310のブロック1341に対応するフラッシュメモリ30のデータを消去すると、リンクテーブル220でブロック1341のリンクが解除された状態を示している。

このように実施形態1では、完全消去エリアに該当しないブロックに対応するフラッシュメモリ30のブロックのデータを消去するときは、そのブロックのデータを残したままでデータのリンクを解除する。

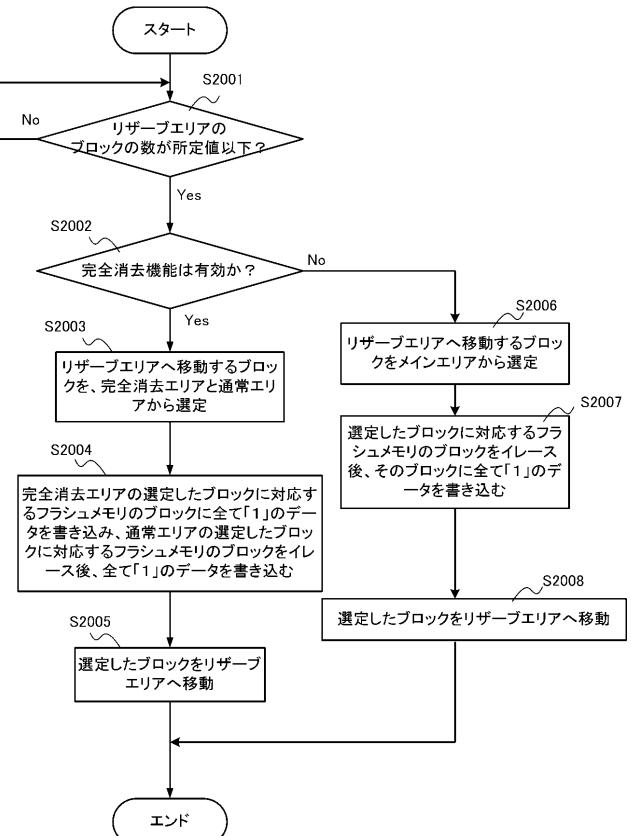

**【0082】**

図20は、実施形態1に係るフラッシュメモリコントローラ20が、リンクテーブル220のメインエリア410を完全消去エリア1300と通常エリア1310に分けて管理している場合のブロック初期化処理を説明するフローチャートである。この処理を実行するプログラムはROM111に記憶されており、CPU110がそのプログラムを実行することによりこの処理が達成される。 20

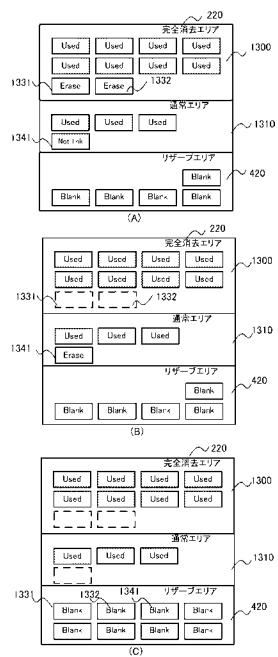

**【0083】**

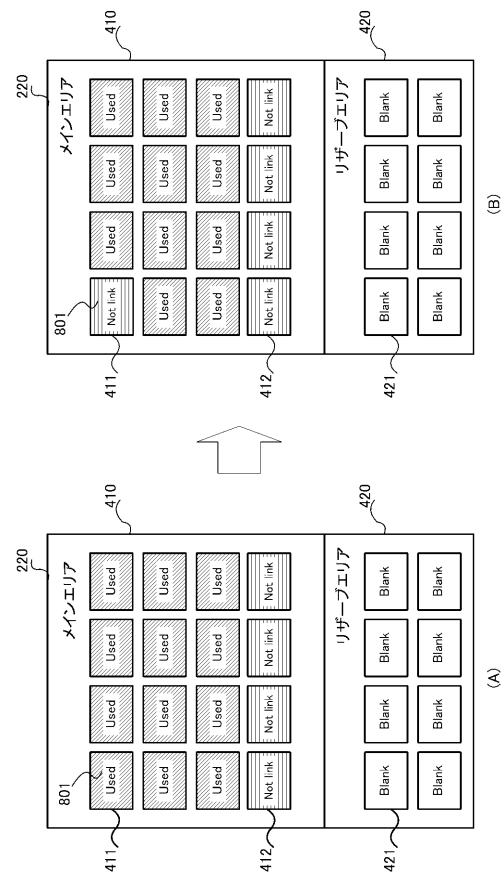

図21は、図20のブロック初期化処理におけるリンクテーブルの遷移を説明する図である。図21(A)は、ブロック初期化処理を実行する前の状態を示し、図21(B)は、ブロック初期化処理を実行している状態を示し、図21(C)は、ブロック初期化処理が完了した状態を示している。以下、図20のフローチャートを、図21を参照して説明する。 30

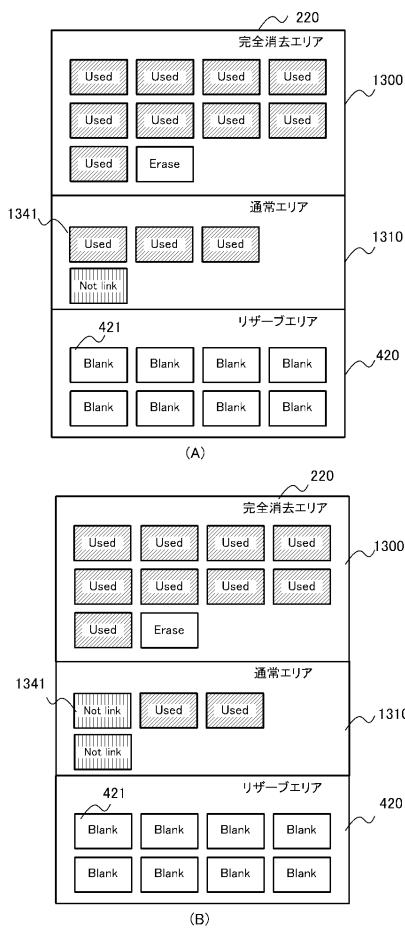

**【0084】**

まずS2001でCPU110は、リンクテーブル220のリザーブエリア420の空きブロック421の数が所定値以下になったかどうかを判定する。図21(A)では、リザーブエリア420の空きブロック421の数は5つであり、ここでは所定値を「8」とする。S2001で空きブロック421の数が所定値以下になったと判定するとS2002に進みCPU110は、フラッシュメモリ30に格納される完全消去エリアの設定情報を読み出して、完全消去機能が有効かどうかを判定する。ここでCPU110は有効であると判定するとS2003へ進み、無効と判定するとS2006へ進む。

**【0085】**

S2003でCPU110は、リザーブエリア420へ移動するブロックを完全消去エリア1300と通常エリア1310から選定する。この選定条件としては、例えばブロックの消去回数が少ないものからリザーブエリア420へ移動するように決めても良いが、他の手法でも良いものとする。図21(A)では、完全消去エリア1300のイレース済のブロック1331, 1332の数が2つ、通常エリア1310のリンク解除済みのブロック1341の数が1つであるため、これらのブロックをリザーブエリア420へ移行するように選定する。 40

**【0086】**

次にS2004に進みCPU110は、完全消去エリア1300の中の選定したブロック1331, 1332に対応するフラッシュメモリ30のブロックに全て「1」のデータを書き込む。また通常エリア1310で選定されたブロック1341に対応するフラッジ

ュメモリ30のブロックに全て「0」のデータを書き込んでイレースした後、全て「1」のデータを書き込んで初期化する。次にS2005に進みCPU110は、S2003で選定したブロックをリザーブエリア420へ移動する。

#### 【0087】

図21(B)は、S2004の処理が完了した状態を示す。また図21(C)は、初期化したブロック1331, 1332, 1341をリザーブエリア420へ移動した状態を示す。

#### 【0088】

S2006～S2008の処理は、図10のS1002～S1005の処理と同じであるため、簡単に説明する。

#### 【0089】

S2006でCPU110は、リザーブエリア420へ移動するブロックをメインエリア410から選定する。そしてS2007へ進みCPU110は、S2006で選定したブロックに全て「0」のデータを書き込んでイレースした後、そのブロックに全て「1」のデータを書き込んで初期化する。そしてS2008に進みCPU110は、S2006で選定したブロックを、メインエリア410からリザーブエリア420へ移動して、この処理を終了する。

#### 【0090】

こうして、リザーブエリア420の空きブロックの数が所定値以下になると、メインエリア、或いは完全消去機能が有効であれば、完全消去エリア或いは通常エリアのイレース済或いはリンク解除済みのブロックで補充できる。

#### 【0091】

このような本実施形態1によれば、メインエリアのブロックを完全消去対象エリアと、従来のメインエリアと同じ通常エリアとに分割し、完全消去対象エリアに対応するブロックのデータだけを完全に消去し、それ以外のブロックはリンクの解除だけを行う。これにより、メインエリアの全てのブロックに対応するブロックのデータを完全に消去する場合に比べて、データの消去に要する時間を短縮できる。

#### 【0092】

(その他の実施形態)

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(又はCPUやMPU等)がプログラムを読み出して実行する処理である。

#### 【0093】

本発明は上記実施の形態に制限されるものではなく、本発明の精神及び範囲から離脱することなく、様々な変更及び変形が可能である。従って、本発明の範囲を公にするために、以下の請求項を添付する。

#### 【符号の説明】

#### 【0094】

10…システムコントローラ、20…フラッシュメモリコントローラ、30…フラッシュメモリ

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(72)発明者 伊藤 武弘

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

Fターム(参考) 5B060 AA09 AB26