(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2018년08월24일

(11) 등록번호 10-1891829

(24) 등록일자 2018년08월20일

(51) 국제특허분류(Int. Cl.)

H01L 43/08 (2006.01) G11B 5/39 (2006.01)

G11C 11/14 (2006.01)

(21) 출원번호 10-2011-0086657

(22) 출원일자 2011년08월29일

심사청구일자 2016년08월10일

(65) 공개번호 10-2012-0024469

(43) 공개일자 2012년03월14일

(30) 우선권주장

JP-P-2010-198936 2010년09월06일 일본(JP)

JP-P-2011-007665 2011년01월18일 일본(JP)

(56) 선행기술조사문현

JP2007059879 A

(73) 특허권자

소니 주식회사

일본국 도쿄도 미나토구 코난 1-7-1

(72) 발명자

야마네 가즈파끼

일본 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

호소미 마사노리

일본 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

(뒷면에 계속)

(74) 대리인

장수길, 박충범, 이중희

전체 청구항 수 : 총 2 항

심사관 : 노영철

(54) 발명의 명칭 기억 소자 및 메모리 장치

### (57) 요 약

본 발명은 기입 전류를 증대시키지 않고, 열 안정성을 개선할 수 있는 기억 소자의 제공에 관한 것이다.

기억 소자는 막면에 수직한 자화를 갖고, 정보에 대응해서 자화의 방향이 변화되는 기억층(17)과, 기억층에 기억된 정보의 기준이 되는 막면에 수직한 자화를 갖는 자화 고정층(15)과, 기억층과 자화 고정층 사이에 설치되는 비자성체에 의한 절연층(16)을 갖는다. 그리고 적층 방향에 스픈 편극된 전자를 주입함으로써, 기억층의 자화의 방향이 변화하여 정보의 기록이 행해진다. 여기서 기억층이 받는 실효적인 반자계의 크기가 기억층의 포화 자화량보다 작은 것으로 여겨지고 있다.

**대 표 도** - 도2

(72) 발명자

**오모리 히로유끼**

일본 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

**벳쇼 가즈히로**

일본 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

**히고 유파까**

일본 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

---

**아사야마 데쓰야**

일본 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

**우찌다 히로유끼**

일본 도쿄도 미나토구 코난 1-7-1 소니 주식회사

내

## 명세서

### 청구범위

#### 청구항 1

기억 소자로서,

제면 자기 이방성 에너지를 기원으로 하는 막면에 수직한 자화를 갖고, 정보에 대응해서 자화의 방향이 변화되는 기억층과,

상기 기억층에 기억된 정보의 기준이 되는 막면에 수직한 자화를 갖는 자화 고정층과,

상기 기억층과 상기 자화 고정층 사이에 설치되는 비자성체에 의한 절연층을 갖고,

상기 기억층, 상기 절연층, 상기 자화 고정층을 갖는 층 구조의 적층 방향으로 스핀 편극된 전자를 주입함으로써, 상기 기억층의 자화 방향이 변화되어, 상기 기억층에 대하여 정보의 기록이 행해짐과 함께,

상기 기억층이 받는 실효적인 반자계의 크기가, 상기 기억층의 포화 자화량보다 작고,

상기 기억층을 구성하는 강자성 재료가  $Co-Fe-B$ 이고,

상기  $Co-Fe-B$ 의 조성은,

$0 \leq X \leq 40$ ,  $60 \leq Y \leq 100$ ,  $30 \leq Z \leq 40$ 에서,

$(Co_x-Fe_y)_{100-z}-B_z$ 인, 기억 소자.

#### 청구항 2

메모리 장치로서,

정보를 자성체의 자화 상태에 의해 유지하는 기억 소자와,

서로 교차하는 2종류의 배선을 구비하고,

상기 기억 소자는

제면 자기 이방성 에너지를 기원으로 하는 막면에 수직한 자화를 갖고, 정보에 대응해서 자화의 방향이 변화되는 기억층과, 상기 기억층에 기억된 정보의 기준이 되는 막면에 수직한 자화를 갖는 자화 고정층과, 상기 기억층과 상기 자화 고정층 사이에 설치되는 비자성체에 의한 절연층을 갖고, 상기 기억층, 상기 절연층, 상기 자화 고정층을 갖는 층 구조의 적층 방향으로 스핀 편극된 전자를 주입함으로써, 상기 기억층의 자화 방향이 변화되어, 상기 기억층에 대하여 정보의 기록이 행해짐과 함께, 상기 기억층이 받는 실효적인 반자계의 크기가, 상기 기억층의 포화 자화량보다 작은 구성이 되고,

상기 2종류의 배선 사이에 상기 기억 소자가 배치되고,

상기 2종류의 배선을 통해 상기 기억 소자에 상기 적층 방향의 전류가 흘러, 스핀 편극된 전자가 주입되고,

상기 기억층을 구성하는 강자성 재료가  $Co-Fe-B$ 이고,

상기  $Co-Fe-B$ 의 조성은,

$0 \leq X \leq 40$ ,  $60 \leq Y \leq 100$ ,  $30 \leq Z \leq 40$ 에서,

$(Co_x-Fe_y)_{100-z}-B_z$ 인, 메모리 장치.

#### 청구항 3

삭제

#### 청구항 4

삭제

청구항 5

삭제

### 발명의 설명

#### 기술 분야

[0001]

본 발명은 강자성층의 자화 상태를 정보로서 기억하는 기억층과, 자화의 방향이 고정된 자화 고정층을 갖고, 전류를 흘림으로써 기억층의 자화의 방향을 변화시키는 기억 소자 및 이 기억 소자를 구비한 메모리 장치에 관한 것이다.

#### 배경 기술

[0002]

컴퓨터 등의 정보 기기에서는 랜덤·액세스·메모리로서, 동작이 고속으로 고밀도인 DRAM이 널리 사용되고 있다.

[0003]

그러나, DRAM은 전원을 끄면 정보가 사라져버리는 휘발성 메모리이기 때문에, 정보가 지워지지 않는 불휘발성의 메모리가 요망되고 있다.

[0004]

그리고, 불휘발성 메모리의 후보로서, 자성체의 자화에서 정보를 기록하는 자기 랜덤·액세스·메모리(MRAM)가 주목받아, 개발이 진행되고 있다.

[0005]

MRAM은 거의 직교하는 2종의 어드레스 배선(워드선, 비트선)에 각각 전류를 흘려, 각 어드레스 배선으로부터 발생하는 전류 차장에 의해, 어드레스 배선의 교점에 있는 자기 기억 소자의 자성층의 자화를 반전해서 정보의 기록을 행하는 것이다.

[0006]

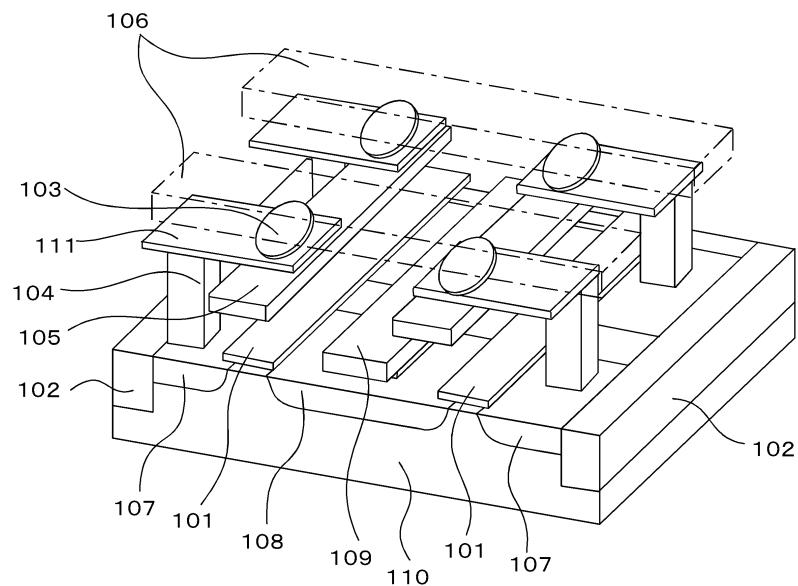

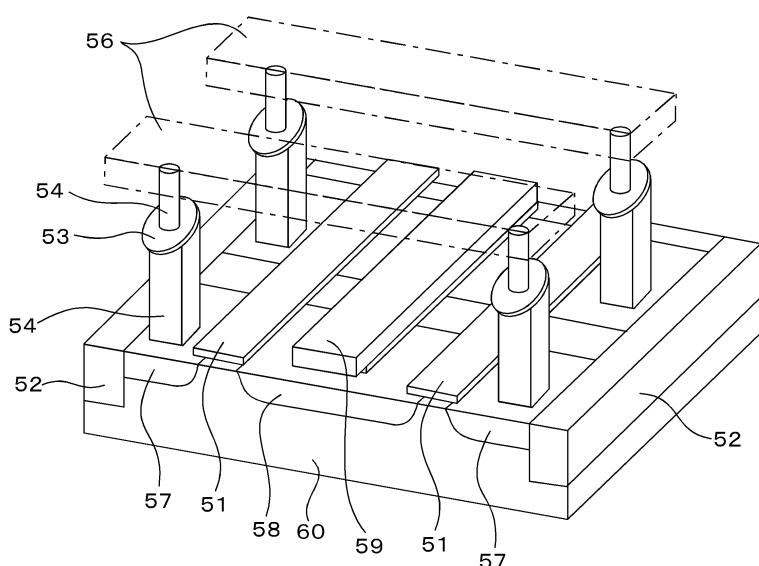

일반적인 MRAM의 모식도(사시도)를 도 10에 도시한다.

[0007]

실리콘 기판 등의 반도체 기체(110)의 소자 분리층(102)에 의해 분리된 부분에, 각 메모리 셀을 선택하기 위한 선택용 트랜지스터를 구성하는 드레인 영역(108), 소스 영역(107), 및 게이트 전극(101)이 각각 형성되어 있다.

[0008]

또한, 게이트 전극(101)의 상방에는 도중 전후 방향으로 연장되는 워드선(105)이 설치되어 있다.

[0009]

드레인 영역(108)은 도면 중 좌우의 선택용 트랜지스터에 공통되게 형성되어 있고, 이 드레인 영역(108)에는 배선(109)이 접속되어 있다.

[0010]

그리고, 워드선(105)과, 상방에 배치된 도면 중 좌우 방향으로 연장되는 비트선(106) 사이에, 자화의 방향이 반전하는 기억층을 갖는 자기 기억 소자(103)가 배치되어 있다. 이 자기 기억 소자(103)는, 예를 들면 자기 터널 접합 소자(MTJ 소자)에 의해 구성된다.

[0011]

또한, 자기 기억 소자(103)는 수평 방향의 바이 패스선(111) 및 상하 방향의 컨택트층(104)을 통하여, 소스 영역(107)에 전기적으로 접속되어 있다.

[0012]

워드선(105) 및 비트선(106)에 각각 전류를 흘림으로써, 전류 차계를 자기 기억 소자(103)에 인가하고, 이에 의해 자기 기억 소자(103)의 기억층의 자화의 방향을 반전시켜서, 정보의 기록을 행할 수 있다.

[0013]

그리고, MRAM 등의 자기 메모리에 있어서, 기록한 정보를 안정적으로 유지하기 위해서는 정보를 기록하는 자성층(기억층)이, 일정한 보자력을 갖고 있는 것이 필요하다.

[0014]

한편, 기록된 정보를 재기입하기 위해서는 어드레스 배선에 어느 정도의 전류를 흘리지 않으면 안된다.

[0015]

그런데, MRAM을 구성하는 소자의 미세화에 따라, 어드레스 배선도 가늘어지기 때문에, 충분한 전류를 흘릴 수 없게 된다.

[0016]

따라서, 보다 적은 전류에서 자화 반전이 가능한 구성으로서, 스핀 주입에 의한 자화 반전을 이용하는 구성의 메모리가 주목받고 있다(예를 들면, 특허문헌 1, 2, 4, 비특허문헌 1, 2 참조).

[0017]

스핀 주입에 의한 자화 반전이란, 자성체 안을 통과해서 스핀 편극된 전자를 다른 자성체에 주입함으로써, 다른 자성체에 있어서 자화 반전을 일으키게 하는 것이다.

- [0018] 예를 들면, 거대 자기 저항 효과 소자(GMR 소자)나 자기 터널 접합 소자(MTJ 소자)에 대하여, 그의 막면에 수직인 방향으로 전류를 흘림으로써, 이들 소자 중 적어도 1부의 자성층의 자화의 방향을 반전시킬 수 있다.

- [0019] 그리고, 스핀 주입에 의한 자화 반전은 소자가 미세화되어도, 전류를 증가시키지 않고 자화 반전을 실현할 수 있는 이점을 갖고 있다.

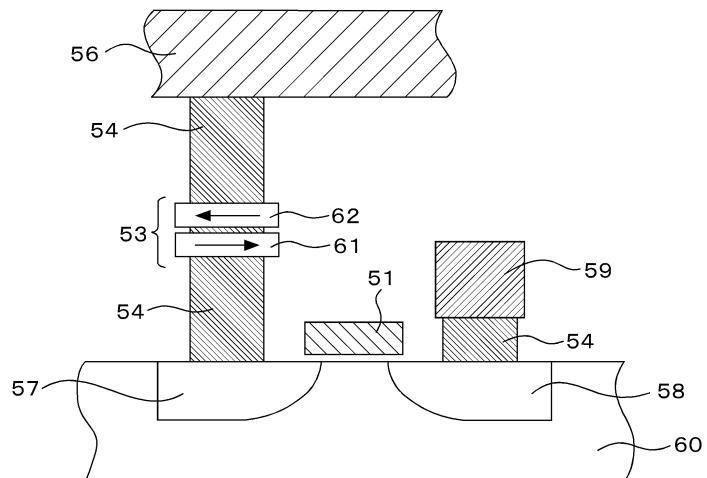

- [0020] 상술한 스핀 주입에 의한 자화 반전을 이용하는 구성의 메모리 장치의 모식도를 도 11 및 도 12에 나타내었다. 도 11은 사시도, 도 12는 단면도이다.

- [0021] 실리콘 기판 등의 반도체 기체(60)의 소자 분리층(52)에 의해 분리된 부분에, 각 메모리 셀을 선택하기 위한 선택용 트랜지스터를 구성하는 드레인 영역(58), 소스 영역(57), 및 게이트 전극(51)이 각각 형성되어 있다. 이 중, 게이트 전극(51)은 도 7 중 전후 방향으로 연장되는 워드선을 겹하고 있다.

- [0022] 드레인 영역(58)은 도 11 중 좌우 선택용 트랜지스터에 공통되게 형성되어 있고, 이 드레인 영역(58)에는 배선(59)이 접속되어 있다.

- [0023] 그리고, 소스 영역(57)과, 상방에 배치된 도 11 중 좌우 방향으로 연장되는 비트선(56) 사이에, 스핀 주입에 의해 자화의 방향이 반전하는 기억층을 갖는 기억 소자(53)가 배치되어 있다.

- [0024] 이 기억 소자(53)는, 예를 들면 자기 터널 접합 소자(MTJ 소자)에 의해 구성된다. 기억 소자(53)는 2개의 자성층(61,62)을 갖는다. 이 2층의 자성층(61,62) 중, 한쪽의 자성층을 자화의 방향이 고정된 자화 고정층으로서, 다른쪽의 자성층을 자화의 방향이 변화되는 자화 자유층 즉 기억층으로 한다.

- [0025] 또한, 기억 소자(53)는 비트선(56)과, 소스 영역(57)에, 각각 상하의 컨택트층(54)를 통해서 접속되어 있다. 이에 의해, 기억 소자(53)에 전류를 흘려, 스핀 주입에 의해 기억층의 자화의 방향을 반전시킬 수 있다.

- [0026] 이러한 스핀 주입에 의한 자화 반전을 이용하는 구성의 메모리 장치의 경우, 도 10에 나타낸 일반적인 MRAM과 비교하여, 디바이스 구조를 단순화할 수 있고, 그 때문에 고밀도화가 가능해진다는 특징도 갖고 있다.

- [0027] 또한, 스핀 주입에 의한 자화 반전을 이용함으로써, 외부 자계에 의해 자화 반전을 행하는 일반적인 MRAM과 비교하여, 소자의 미세화가 진행되어도, 기입의 전류가 증대하지 않는다는 이점이 있다.

## 선행기술문헌

### 특허문헌

- [0028] (특허문헌 0001) 일본 특허 공개 제2003-17782호 공보

(특허문헌 0002) 미국 특허 제6256223호 명세서

(특허문헌 0003) 미국 특허 공개 2005-0184839 A1

(특허문헌 0004) 일본 특허 공개 제2008-227388호 공보

### 비특허문헌

- [0029] (비)특허문헌 0001) PHYS. Rev. B, 54.9353(1996)

(비)특허문헌 0002) J. Magn. Mat., 159, L1(1996)

(비)특허문헌 0003) F. J. Albert et al., Appl. Phy. Lett., 77, 3809(2000)

(비)특허문헌 0004) Nature Materials., 5, 210(2006)

## 발명의 내용

### 해결하려는 과제

- [0030] 그런데, MRAM의 경우에는, 기억 소자와는 별도로 기입 배선(워드선이나 비트선)을 설치하여, 기입 배선에 전류

를 흘려서 발생하는 전류 자체에 의해, 정보의 기입(기록)을 행하고 있다. 그로 인해, 기입 배선에, 기입에 필요로 되는 전류량을 충분히 흘릴 수 있다.

[0031] 한편, 스픈 주입에 의한 자화 반전을 이용하는 구성의 메모리 장치에 있어서는 기억 소자에 흘리는 전류에 의해 스픈 주입을 행하면, 기억층의 자화의 방향을 반전시킬 필요가 있다.

[0032] 그리고, 이렇게 기억 소자에 직접 전류를 흘려서 정보의 기입(기록)을 행하는 점에서, 기입을 행하는 메모리 셀을 선택하기 위해서, 기억 소자를 선택 트랜지스터와 접속해서 메모리 셀을 구성한다. 이 경우, 기억 소자에 흐르는 전류는 선택 트랜지스터에 흘리는 것이 가능한 전류(선택 트랜지스터의 포화 전류)의 크기로 제한된다.

[0033] 이로 인해, 선택 트랜지스터의 포화 전류 이하의 전류에서 기입을 행할 필요가 있고, 스픈 주입의 효율을 개선하여, 기억 소자에 흘리는 전류를 저감할 필요가 있다.

[0034] 또한, 판독 신호를 크게 하기 위해서는 큰 자기 저항 변화율을 확보할 필요가 있고, 그것을 위해서는 기억층의 양측에 접하고 있는 중간층을 터널 절연층(터널 배리어층)으로 한 기억 소자의 구성으로 하는 것이 효과적이다.

[0035] 이렇게 중간층으로서 터널 절연층을 사용한 경우에는, 터널 절연층이 절연 과정되는 것을 방지하기 위해서, 기억 소자에 흘리는 전류량에 제한이 발생한다. 이 관점에서도, 스픈 주입시의 전류를 억제할 필요가 있다.

[0036] 이 전류값을 내리기 위해서는, 이 전류값이 기억층의 막 두께에 비례하여, 기억층의 포화 자화의 2승에 비례하므로, 이들(막 두께나 포화 자화)을 조절하면 되는 것을 알 수 있다(예를 들면, 비특허문헌 3 참조).

[0037] 그리고, 예를 들면 특허문헌 3에는 기록 재료의 자화량( $M_s$ )을 저감하면, 전류값을 저감할 수 있는 것이 나타나 있다.

[0038] 그러나, 한편으로, 전류에 의해 기입된 정보를 기억하지 않으면 불휘발성 메모는 될 수 없다. 즉, 기억층의 열 요동에 대한 안정성(열 안정성)의 확보가 필요하다.

[0039] 스픈 주입에 의한 자화 반전을 이용하는 기억 소자의 경우, 종래의 MRAM과 비교하여, 기억층의 체적이 작아지므로, 단순하게 생각하면 열 안정성은 저하되는 방향에 있다.

[0040] 기억층의 열 안정성이 확보되어 있지 않으면, 반전한 자화의 방향이 열에 의해 재반전해버려, 기입 에러가 되어 버린다.

[0041] 그리고, 스픈 주입에 의한 자화 반전을 이용하는 기억 소자의 대용량화를 진척시켰을 경우, 기록 소자의 체적은 한층 작아지므로, 열 안정성의 확보는 중요한 과제가 된다.

[0042] 그로 인해, 스픈 주입에 의한 자화 반전을 이용하는 기억 소자에 있어서, 열 안정성은 매우 중요한 특성이다.

[0043] 따라서, 스픈 주입에 의해 기억층의 자화의 방향을 반전시키는 구성의 기억 소자가 메모리로서 존재할 수 있기 위해서는, 스픈 주입에 의한 자화 반전에 필요한 전류를 트랜지스터의 포화 전류 이하로 저감시키고, 또한, 기입된 정보를 확실하게 유지하는 열 안정성을 확보할 필요가 있다.

[0044] 이상과 같이, 스픈 주입에 의한 자화 반전에 필요한 전류를 저감하기 위해서는 기억층의 포화 자화량  $M_s$ 를 저감하는 것이나, 기억층을 얇게 하는 것이 생각된다. 예를 들면, 상술한 특허문헌 3과 같이, 기억층의 재료에 포화 자화량  $M_s$ 가 낮은 재료를 사용하는 것이 유효하다. 그러나, 이와 같이, 단순히 포화 자화량  $M_s$ 가 낮은 재료를 사용한 경우, 정보를 확실하게 유지하는 열 안정성을 확보할 수 없다.

[0045] 따라서 본 발명에 있어서는 기입 전류를 증대시키지 않고, 열 안정성을 개선할 수 있는 기억 소자, 및 이 기억 소자를 갖는 메모리 장치를 제공하는 것을 목적으로 한다. 또한 본 발명에서는, 기억층을 구성하는 자성 재료가 350 이상의 열 처리된 경우라도 우수한 특성이 되는 기억 소자를 제공하는 것도 목적으로 한다.

### 과제의 해결 수단

[0046] 본 발명의 기억 소자는 막면에 수직한 자화를 갖고, 정보에 대응해서 자화의 방향이 변화되는 기억층과, 상기 기억층에 기억된 정보의 기준이 되는 막면에 수직한 자화를 갖는 자화 고정층과, 상기 기억층과 상기 자화 고정층 사이에 설치되는 비자성체에 의한 절연층을 갖는다. 그리고 상기 기억층, 상기 절연층, 상기 자화 고정층을 갖는 층 구조의 적층 방향에 스픈 편극된 전자를 주입함으로써, 상기 기억층의 자화의 방향이 변화되고, 상기 기억층에 대하여 정보의 기록이 행해짐과 동시에, 상기 기억층이 받는 실효적인 반자계의 크기가, 상기 기억층의 포화 자화량보다 작은 기억 소자이다.

- [0047] 또한 상기 기억층을 구성하는 강자성층 재료가 Co-Fe-B이다.

- [0048] 그 경우, 상기 Co-Fe-B의 조성이  $0 \leq Co_x \leq 40$ ,  $60 \leq Fe_y \leq 100$ ,  $0 < B_z \leq 30$ 에 있어서,  $(Co_x-Fe_y)_{100-z}-B_z$ 이다.

- [0049] 또는, 상기 Co-Fe-B의 조성이  $0 \leq Co_x \leq 40$ ,  $60 \leq Fe_y \leq 100$ ,  $20 < B_z \leq 40$ 에 있어서,  $(Co_x-Fe_y)_{100-z}-B_z$ 이도록 한다.

- [0050] 본 발명의 메모리 장치는 정보를 자성체의 자화 상태에 의해 유지하는 기억 소자와, 서로 교차 하는 2종의 배선을 구비하고, 기억 소자는 상기 본 발명의 기억 소자의 구성이며, 2종의 배선 사이에 기억 소자가 배치되고, 이들 2종의 배선을 통해 기억 소자에 적층 방향의 전류가 흘러, 스핀 편극된 전자가 주입되는 것이다.

- [0051] 상술한 본 발명의 기억 소자의 구성에 의하면, 정보를 자성체의 자화 상태에 의해 유지하는 기억층을 갖고, 이 기억층에 대하여 중간층을 개재하여 자화 고정층이 설치되고, 중간층이 절연체로 이루어지고, 적층 방향에 스핀 편극된 전자를 주입함으로써, 기억층의 자화의 방향이 변화되어, 기억층에 대하여 정보의 기록이 행해지므로, 적층 방향에 전류를 흘려서 스핀 편극된 전자를 주입함으로써 정보의 기록을 행할 수 있다.

- [0052] 그리고, 기억층이 받는 실효적인 반자계의 크기가 기억층의 포화 자화량보다도 작음으로써, 기억층이 받는 반자계가 낮아져 있고, 기억층의 자화의 방향을 반전시키기 위해 필요해지는 기입 전류량을 저감할 수 있다.

- [0053] 한편, 기억층의 포화 자화량을 저감하지 않아도 기입 전류량을 저감할 수 있기 때문에, 기억층의 포화 자화량을 충분한 양으로 하여, 기억층의 열 안정성을 충분히 확보하는 것이 가능하게 된다.

- [0054] 특히 본 발명의 기억 소자는, 기억층 및 자화 고정층은 막면에 수직한 자화를 갖는다. 면내 자기 이방성을 갖는 것보다도 수직 자기 이방성을 갖는 것쪽이 저전력화, 대용량화에 바람직하다. 이유는 수직 자화쪽이 스핀 토크 자화 반전시에 초과해야 할 에너지 배리어가 낮고, 또한 수직 자화막이 갖는 높은 자기 이방성에 의해 기억층의 정보 유지의 열 안정성이 유리해지기 때문이다.

- [0055] 또한 상술한 본 발명의 메모리 장치의 구성에 의하면, 2종의 배선 사이에 기억 소자가 배치되어, 이들 2종의 배선을 통해서 기억 소자에 적층 방향의 전류가 흘러, 스핀 편극된 전자가 주입되는 것임으로써, 2종의 배선을 통해서 기억 소자의 적층 방향에 전류를 흘려서 스핀 주입에 의한 정보의 기록을 행할 수 있다.

- [0056] 또한, 기억층의 포화 자화량을 저감하지 않아도, 기억 소자의 기입 전류량을 저감하는 것이 가능하게 되기 때문에, 기억 소자에 기록된 정보를 안정되게 유지함과 동시에, 메모리 장치의 소비 전력을 저감하는 것이 가능하게 된다.

### 발명의 효과

- [0057] 본 발명에 따르면, 기억층의 포화 자화량을 저감하지 않아도, 기억 소자의 기입 전류량을 저감하는 것이 가능하게 되기 때문에, 정보 유지 능력인 열 안정성을 충분히 확보하고, 특성 균형이 우수한 기억 소자를 구성할 수 있다. 이에 의해, 동작 에러를 없애고, 기억 소자의 동작 마진을 충분히 얻을 수 있다.

- [0058] 또한 특히, 기억층을 구성하는 강자성층 재료를 Co-Fe-B로 하고, Co-Fe-B의 조성이  $0 \leq Co_x \leq 40$ ,  $60 \leq Fe_y \leq 100$ ,  $0 < B_z \leq 30$ 에 있어서,  $(Co_x-Fe_y)_{100-z}-B_z$ 이면 수직 자화의 기억층의 형성에 적합하다.

- [0059] 또한, 열 처리 온도가  $350^{\circ}\text{C}$  내지  $450^{\circ}\text{C}$  정도의 비교적 고온이 되는 경우를 생각하면, Co-Fe-B의 조성이  $0 \leq Co_x \leq 40$ ,  $60 \leq Fe_y \leq 100$ ,  $20 < B_z \leq 40$ 에 있어서,  $(Co_x-Fe_y)_{100-z}-B_z$ 이도록 하면, 기억층을 구성하는 강자성층 재료가 고온 열 처리에서도 높은 터널 자기 저항 효과를 나타내게 되어, 적합하다.

- [0060] 이들에 의해, 안정되게 동작하는 신뢰성이 높은 메모리 장치를 실현할 수 있다.

- [0061] 또한, 기입 전류를 저감하고, 기억 소자에 기입을 행할 때의 소비 전력을 저감하는 것이 가능하게 된다.

- [0062] 따라서, 메모리 장치 전체의 소비 전력을 저감하는 것이 가능하게 된다.

### 도면의 간단한 설명

- [0063] 도 1은 본 발명의 실시 형태의 메모리 장치의 개략 구성의 설명도이다.

- 도 2는 실시 형태의 기억 소자의 단면도이다.

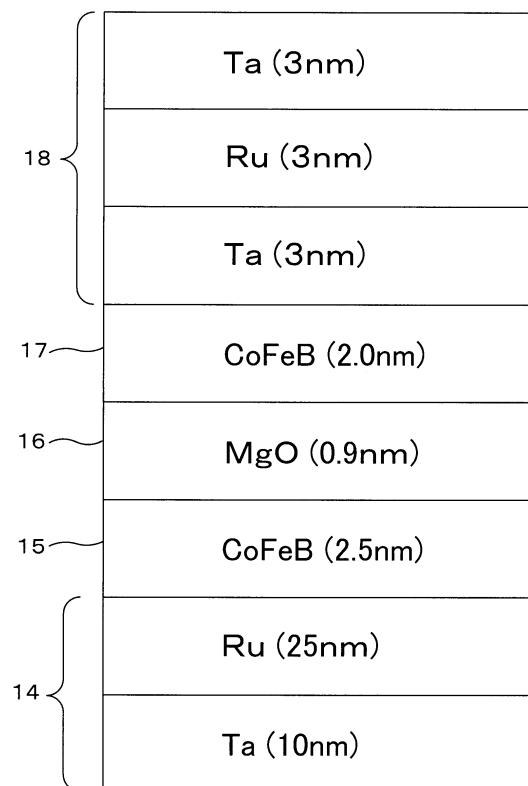

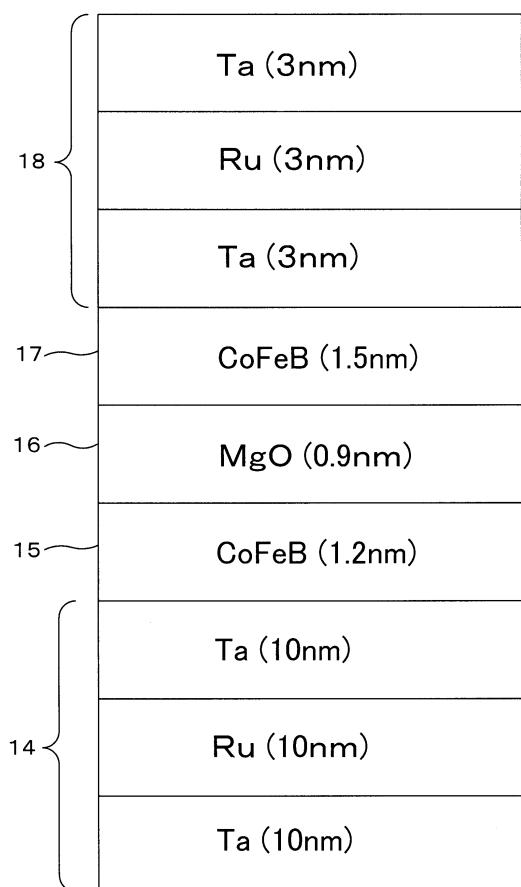

- 도 3은 실험에서 사용한 기억 소자의 시료의 층 구조의 설명도이다.

도 4는  $0.09 \times 0.18 \mu\text{m}$  크기의 기억층의 Co의 양과, 반전 전류 밀도와의 관계를 도시한 도면이다.

도 5는  $0.09 \times 0.18 \mu\text{m}$  크기의 기억층의 Co의 양과, 열 안정성의 지표와의 관계를 도시한 도면이다.

도 6은  $50\text{nm}\phi$  크기의 기억층의 Co의 양과, 열 안정성의 지표와의 관계를 도시한 도면이다.

도 7은 실험에서 사용한 기억 소자의 시료의 층 구조의 설명도이다.

도 8은 실시 형태의 기억층의 Co-Fe-B의 조성마다의 TMR의 열 처리 온도 의존성을 도시한 도면이다.

도 9는 실시 형태의 기억층의 Co-Fe-B에 대해서, Co/Fe비에서 B 농도 및 열 처리 온도를 바꾸었을 경우의 TMR 특성의 측정 결과를 도시한 도면이다.

도 10은 종래의 MRAM의 구성을 모식적으로 도시한 사시도이다.

도 11은 스핀 주입에 의한 자화 반전을 이용한 메모리 장치의 개략 구성의 설명도이다.

도 12는 도 11의 메모리 장치의 단면도이다.

### 발명을 실시하기 위한 구체적인 내용

[0064]

이하, 본 발명의 실시 형태를 다음의 순서로 설명한다.

[0065]

<1. 실시 형태의 기억 소자의 개요>

[0066]

<2. 제1 실시 형태의 구성>

[0067]

<3. 제1 실시 형태에 관한 실험>

[0068]

<4. 제2 실시 형태의 구성>

[0069]

<5. 제2 실시 형태에 관한 실험>

[0070]

<6. 변형 예>

[0071]

<1. 실시 형태의 기억 소자의 개요>

[0072]

우선, 발명의 실시 형태가 되는 기억 소자의 개요에 대해서 설명한다.

[0073]

본 발명의 실시 형태는 전술한 스핀 주입에 의해, 기억 소자의 기억층의 자화의 방향을 반전시켜서, 정보의 기록을 행하는 것이다.

[0074]

기억층은 강자성층 등의 자성체에 의해 구성되어, 정보를 자성체의 자화 상태(자화의 방향)에 의해 유지하는 것이다.

[0075]

상세하게는 후술하지만, 기억 소자는, 예를 들면 도 2에 일례를 나타내는 층 구조로 되어, 적어도 2개의 자성층으로서의 기억층(17), 자화 고정층(15)을 구비하고, 또한 그의 2개의 자성층 사이의 중간층으로서의 절연층(16)(터널 절연층)을 구비한다.

[0076]

기억층(17)은 막면에 수직한 자화를 갖고, 정보에 대응해서 자화의 방향이 변화된다.

[0077]

자화 고정층(15)은 기억층(17)에 기억된 정보의 기준이 되는 막면에 수직한 자화를 갖는다.

[0078]

절연층(16)은 비자성체이며, 기억층(17)과 자화 고정층(15) 사이에 설치된다.

[0079]

그리고 기억층(17), 절연층(16), 자화 고정층(15)을 갖는 층 구조의 적층 방향으로 스핀 편극된 전자를 주입함으로써, 기억층(17)의 자화의 방향이 변화되어, 기억층(17)에 대하여 정보의 기록이 행해진다.

[0080]

스핀 주입에 의해 자성층(기억층(17))의 자화의 방향을 반전시키는 기본적인 동작은 거대 자기 저항 효과 소자(GMR 소자) 또는 터널 자기 저항 효과 소자(MTJ 소자)로 이루어지는 기억 소자에 대하여, 그의 막면에 수직한 방향으로, 어느 임계값 이상의 전류를 흘리는 것이다. 이 때, 전류의 극성(방향)은 반전시키는 자화의 방향에 의존한다.

[0081]

이 임계값보다도 절대값이 작은 전류를 흘렸을 경우에는, 자화 반전을 발생하지 않는다.

[0082]

스핀 주입에 의해, 자성층의 자화의 방향을 반전시킬 때에, 필요로 되는 전류의 임계값  $I_c$ 는 일반적으로는,

- [0083]  $I_c = A \cdot \alpha \cdot M_s \cdot V \cdot H_d / 2 \eta$

- [0084] 예 의해 나타난다.

- [0085] 여기서, A: 상수,  $\alpha$ : 스픈 제동 상수,  $\eta$ : 스픈 주입 효율,  $M_s$ : 포화 자화량, V: 기억층의 체적,  $H_d$ : 실효적인 반자계이다.

- [0086] 이 식에서 나타나는 바와 같이, 전류의 임계값은 자성층의 체적 V, 자성층의 포화 자화  $M_s$ , 스픈 주입 효율  $\eta$ , 스픈 제동 상수  $\alpha$ 를 제어함으로써, 임의로 설정하는 것이 가능하다.

- [0087] 또한 염밀하게는 스픈 토크 자화 반전에 의해, 자성층의 자화의 방향을 반전시킬 때에, 필요해지는 전류의 임계값  $I_c$ 는 자성층의 자화 용이축이 면내 방향인지, 수직 방향인지에 따라 상이하다.

- [0088] 본 실시 형태의 기억 소자는 수직 자화형이지만, 종전의 면내 자화형의 기억 소자의 경우에 있어서의 자성층의 자화의 방향을 반전시키는 반전 전류를  $I_c_{para}$ 로 하면,

- [0089] 동일 방향으로부터 역방향(또한, 동일 방향, 역방향이란, 자화 고정층의 자화의 방향을 기준으로서 본 기억층의 자화의 방향)으로 반전시키는 경우,

- [0090]  $I_c_{para} = (A \cdot \alpha \cdot M_s \cdot V / g(0) / P) (H_k + 2\pi M_s)$

- [0091] 가 되고, 역방향으로부터 동일 방향으로 반전시키는 경우,

- [0092]  $I_c_{para} = -(A \cdot \alpha \cdot M_s \cdot V / g(\pi) / P) (H_k + 2\pi M_s)$

- [0093] 가 된다.

- [0094] 한편, 본 예와 같은 수직 자화형의 기억 소자의 반전 전류를  $I_c_{perp}$ 로 하면, 동일 방향으로부터 역방향으로 반전시키는 경우,

- [0095]  $I_c_{perp} = (A \cdot \alpha \cdot M_s \cdot V / g(0) / P) (H_k - 4\pi M_s)$

- [0096] 가 되고, 역방향으로부터 동일 방향으로 반전시키는 경우,

- [0097]  $I_c_{perp} = -(A \cdot \alpha \cdot M_s \cdot V / g(\pi) / P) (H_k - 4\pi M_s)$

- [0098] 가 된다.

- [0099] 단, A는 상수,  $\alpha$ 는 덤핑 상수,  $M_s$ 는 포화 자화, V는 소자 체적, P는 스픈 분극률,  $g(0)$ ,  $g(\pi)$ 는 각각 동일 방향시, 역방향시에 스픈 토크가 상대의 자성층에 전달되는 효율에 대응하는 계수,  $H_k$ 는 자기 이방성이다(비특허 문헌 4 참조).

- [0100] 상기 각 식에 있어서, 수직 자화형의 경우의  $(H_k - 4\pi M_s)$ 와 면내 자화형의 경우의  $(H_k + 2\pi M_s)$ 를 비교하면, 수직 자화형이 저기록 전류화에 보다 적합한 것을 이해할 수 있다.

- [0101] 본 예의 기억 소자는 터널 자기 저항 효과에 의한 저항의 차에서 정보의 판독을 행한다. 즉, 터널 자기 저항 효과가 큰 경우에 출력도 커진다. 터널 자기 저항 효과 TMR은 스픈 분극률: P를 사용해서 수학식 1에 의해 표현된다.

## 수학식 1

$$TMR(\%) = \frac{P_1 P_2}{1 - P_1 P_2} \times 100$$

- [0102] 여기서,  $P_1$ 은 고정층의 스픈 분극률,  $P_2$ 는 기록층의 스픈 분극률이다. 수학식 1에 있어서, 스픈 분극률이 클 때에, TMR이 커지는 것을 이해할 수 있다.

- [0104] 그리고, 반전 전류의 식과의 비교에 의해, 저전류화와 고출력화(=고TMR화)가 양립하는 관계인 것도 알 수 있다.

- [0105] 본 실시 형태에서는, 자화 상태에 의해 정보를 유지할 수 있는 자성층(기억층(17))과, 자화의 방향이 고정된 자화 고정층(15)을 갖는 기억 소자를 구성한다.

[0106] 메모리로서 존재할 수 있기 위해서는 기입된 정보를 유지할 수 없으면 안된다. 정보를 유지하는 능력의 지표로서, 열 안정성의 지표  $\Delta$  ( $=KV/k_B T$ )의 값으로 판단된다. 이  $\Delta$ 는 하기 수학식 2에 의해 표현된다.

## 수학식 2

$$\Delta = KV/k_B T = M_s \cdot V \cdot H_k \cdot (1/2k_B T)$$

[0108] 여기서,  $H_k$ : 실효적인 이방성 자계,  $k_B$ : 볼트먼 상수,  $T$ : 온도,  $M_s$ : 포화 자화량,  $V$ : 기억층의 체적이다.

[0109] 실효적인 이방성 자계  $H_k$ 에는 형상 자기 이방성, 유도 자기 이방성, 결정 자기 이방성 등의 영향이 도입되어 있어, 단자구의 코히어런트 로테이션 모델(coherent rotation model)을 가정했을 경우, 보자력과 동등하다.

[0110] 열 안정성의 지표  $\Delta$ 와 전류의 임계값  $I_c$ 와는 상반된 관계가 되는 경우가 많다. 그 때문에, 메모리 특성을 유지하기 위해서는 이들의 양립이 과제가 되는 경우가 많다.

[0111] 기억층(17)의 자화 상태를 변화시키는 전류의 임계값은 실제로는, 예를 들면 기억층(17)의 두께가 2nm이며, 평면 패턴이 100nm  $\times$  150nm의 생략 타원형의 TMR 소자에 있어서, +측의 임계값  $+I_c=+0.5mA$ 이며, -측의 임계값  $-I_c=-0.3mA$ 이며, 그 때의 전류 밀도는 약  $3.5 \times 10^6 A/cm^2$ 이다. 이들은 상기의  $I_c$ 의 식( $I_c_{para}$ 의 식)과 거의 일치한다.

[0112] 이에 대해, 전류 자장에 의해 자화 반전을 행하는 통상의 MRAM에서는 기입 전류가 수 mA 이상 필요하게 된다.

[0113] 따라서, 스핀 주입에 의해 자화 반전을 행하는 경우에는, 상술한 바와 같이 기입 전류의 임계값이 충분히 작아지기 때문에, 짐작 회로의 소비 전력을 저감시키기 위해서 유효한 것을 알 수 있다.

[0114] 또한, 통상의 MRAM에서 필요하게 되는 전류 자계 발생용의 배선(도 10의 배선(105))이 불필요하게 되기 때문에, 짐작도에 있어서도 통상의 MRAM에 비교해서 유리하다.

[0115] 그리고, 스핀 주입에 의해 자화 반전을 행하는 경우에는, 기억 소자에 직접 전류를 흘려서 정보의 기입(기록)을 행하는 점에서, 기입을 행하는 메모리 셀을 선택하기 위해서, 기억 소자를 선택 트랜지스터와 접속해서 메모리 셀을 구성한다.

[0116] 이 경우, 기억 소자에 흐르는 전류는 선택 트랜지스터에서 흘리는 것이 가능한 전류(선택 트랜지스터의 포화 전류)의 크기에 의해 제한된다.

[0117] 선택 트랜지스터의 포화 전류보다도, 스핀 주입에 의한 자화 반전의 전류의 임계값  $I_c$ 를 작게하기 위해서는 상기  $I_c$ 의 식에 의해, 기억층(17)의 포화 자화량  $M_s$ 를 저감시키면 되는 것을 알 수 있다.

[0118] 그러나, 단순하게 포화 자화량  $M_s$ 를 저감시켰을 경우(예를 들면, 특허문헌3)에는 기억층(17)의 열 안정성이 현저하게 손상되어, 메모리로서의 기능을 달성할 수 없게 된다.

[0119] 메모리를 구성하기 위해서는, 열 안정성의 지표  $\Delta$ 가 어느 정도 이상의 크기일 필요가 있다.

[0120] 따라서, 본원의 발명자들이 다양하게 검토를 행한 결과, 기억층(17)을 구성하는 강자성층으로서, 예를 들면 Co-Fe-B의 조성을 선정함으로써, 기억층(17)이 받는 실효적인 반자계(Meffective)의 크기가, 기억층(17)의 포화 자화량  $M_s$ 보다도 작아지는 것을 발견하였다.

[0121] 상술한 강자성 재료를 사용함으로써, 기억층(17)이 받는 실효적인 반자계의 크기가, 기억층(17)의 포화 자화량  $M_s$ 보다 작은 구성이 된다.

[0122] 이에 의해, 기억층(17)이 받는 반자계를 작게할 수 있으므로, 수학식 2에 의해 표현되는 열 안정성  $\Delta$ 를 손상시킬 일 없이, 상기  $I_c$ 의 식에 의해 표현되는 전류의 임계값  $I_c$ 를 저감하는 효과가 얻어진다.

[0123] 또한, 발명자들은 상기의 선정된 Co-Fe-B 조성 내, 한정된 조성 범위에 있어서, Co-Fe-B가 막면 수직 방향으로 자화하여, 그것에 의해, Gbit급의 용량을 실현 가능한 극미소 기록 소자에 있어서도 충분한 열 안정성이 확보 가능한 것을 발견하였다.

[0124] 따라서, Gbit급의 스핀 주입형 자화 반전 메모리에 있어서 열 안정성을 유지한 상태에서, 저전류에서 정보의 기

입을 할 수 있다고 하는 안정된 메모리의 형성을 가능하게 한다.

[0125] 본 실시 형태에서는 기억층(17)이 받는 실효적인 반자계의 크기가, 기억층(17)의 포화 자화량 Ms보다 작은 구성, 즉 기억층(17)의 포화 자화량 Ms에 대한 실효적인 반자계의 크기의 비의 값을 1보다 작게 한다.

[0126] 또한, 선택 트랜지스터의 포화 전류값을 고려하여, 기억층(17)과 자화 고정층(15) 사이의 비자성의 중간층으로서, 절연체로 이루어지는 터널 절연층(절연층(16))을 사용해서 자기 터널 접합(MTJ) 소자를 구성한다.

[0127] 터널 절연층을 사용해서 자기 터널 접합(MTJ) 소자를 구성함으로써, 비자석성 도전층을 사용해서 거대 자기 저항 효과(GMR) 소자를 구성한 경우와 비교하여, 자기 저항 변화율(MR비)을 크게 할 수 있고, 판독 신호 강도를 크게 할 수 있기 때문이다.

[0128] 그리고, 특히 이 터널 절연층(16)의 재료로서, 산화마그네슘(MgO)을 사용함으로써, 지금까지 일반적으로 사용되어 온 산화 알루미늄을 사용한 경우보다도, 자기 저항 변화율(MR비)을 크게 할 수 있다.

[0129] 또한, 일반적으로, 스핀 주입 효율은 MR비에 의존하고, MR비가 클수록, 스핀 주입 효율이 향상되고, 자화 반전 전류 밀도를 저감할 수 있다.

[0130] 따라서, 중간층인 터널 절연층(16)의 재료로서 산화마그네슘을 사용하고, 동시에 상기의 기억층(17)을 사용함으로써, 스핀 주입에 의한 기입 임계값 전류를 저감할 수 있고, 적은 전류에서 정보의 기입(기록)을 행할 수 있다. 또한, 판독 신호 강도를 크게 할 수 있다.

[0131] 이에 의해, MR비(TMR비)를 확보하여, 스핀 주입에 의한 기입 임계값 전류를 저감할 수 있고, 적은 전류에서 정보의 기입(기록)을 행할 수 있다. 또한, 판독 신호 강도를 크게 할 수 있다.

[0132] 이렇게 터널 절연층(16)을 산화마그네슘(MgO)막에 의해 형성하는 경우에는 MgO막이 결정화되어 있어서, 001 방향으로 결정 배향성을 유지하고 있는 것이 보다 바람직하다.

[0133] 또한, 본 실시 형태에 있어서, 기억층(17)과 자화 고정층(15) 사이의 중간층(터널 절연층(16))은 산화마그네슘으로 이루어지는 구성으로 하는 것 이외에도, 예를 들면 산화알루미늄, 질화알루미늄,  $\text{SiO}_2$ ,  $\text{Bi}_2\text{O}_3$ ,  $\text{MgF}_2$ ,  $\text{CaF}$ ,  $\text{SrTiO}_2$ ,  $\text{AlLaO}_3$ ,  $\text{Al-N-O}$  등의 각종 절연체, 유전체, 반도체를 사용해서 구성할 수도 있다.

[0134] 터널 절연층(16)의 면적 저항값은 스핀 주입에 의해 기억층(17)의 자화의 방향을 반전시키기 위해서 필요한 전류 밀도를 얻는 관점에서, 몇십  $\Omega \mu\text{m}^2$  정도 이하로 제어할 필요가 있다.

[0135] 그리고, MgO막으로 이루어지는 터널 절연층(16)에서는 면적 저항값을 상술한 범위로 하기 위해서, MgO막의 막 두께를 1.5nm 이하로 설정할 필요가 있다.

[0136] 또한, 기억층(17)의 자화의 방향을 작은 전류에서 용이하게 반전할 수 있도록, 기억 소자를 작게 하는 것이 바람직하다.

[0137] 따라서, 바람직하게는 기억 소자의 면적을  $0.01 \mu\text{m}^2$  이하로 한다.

[0138] 또한, 본 실시 형태에 있어서의 기억층(17)은 조성이 상이한 다른 강자성층을 직접 적층시키는 것도 가능하다. 또한, 강자성층과 연자성층을 적층시키거나, 복수층의 강자성층을 연자성층이나 비자성층을 개재하여 적층시키거나 하는 것도 가능하다. 이렇게 적층시킨 경우에도, 본 발명에서 말하는 효과가 얻어진다.

[0139] 특히 복수층의 강자성층을 비자성층에 개재하여 적층시킨 구성으로 했을 때에는 강자성층의 층간 상호 작용의 강도를 조정하는 것이 가능하게 되기 때문에, 기억 소자의 치수가 서브 마이크로 미터 이하가 되어도, 자화 반전 전류가 커지지 않도록 억제하는 것이 가능해진다는 효과가 얻어진다. 이 경우의 비자성층의 재료로서는 Ru, Os, Re, Ir, Au, Ag, Cu, Al, Bi, Si, B, C, Cr, Ta, Pd, Pt, Zr, Hf, W, Mo, Nb 또는 그들의 합금을 사용할 수 있다.

[0140] 자화 고정층(15) 및 기억층(17)은 일방향의 이방성을 갖고 있는 것이 바람직하다.

[0141] 또한, 자화 고정층(15) 및 기억층(17) 각각의 막 두께는 0.5nm 내지 30nm인 것이 바람직하다.

[0142] 기억 소자의 그 밖의 구성은 스핀 주입에 의해 정보를 기록하는 기억 소자의 종래 공지의 구성과 동일하게 할 수 있다.

[0143] 자화 고정층(15)은 강자성층만에 의해, 또는 반강자성층과 강자성층의 결합을 이용함으로써, 그의 자

화의 방향이 고정된 구성으로 할 수 있다.

[0144] 또한, 자화 고정층(15)은 단층의 강자성층으로 이루어지는 구성, 또는 복수층의 강자성층을 비자성층을 개재하여 적층한 적층 폐리핀(ferri-pin) 구조로 할 수 있다.

[0145] 적층 폐리핀 구조의 자화 고정층(15)을 구성하는 강자성층이 재료로서는 Co, CoFe, CoFeB 등을 사용할 수 있다. 또한, 비자성층의 재료로는 Ru, Re, Ir, Os 등을 사용할 수 있다.

[0146] 반강자성층의 재료로서는 FeMn 합금, PtMn 합금, PtCrMn 합금, NiMn 합금, IrMn 합금, NiO, Fe<sub>2</sub>O<sub>3</sub> 등의 자성체를 들 수 있다.

[0147] 또한, 이들의 자성체에 Ag, Cu, Au, Al, Si, Bi, Ta, B, C, O, N, Pd, Pt, Zr, Hf, Ir, W, Mo, Nb 등의 비자성 원소를 첨가하여, 자기 특성을 조정하거나, 그 밖의 결정 구조나 결정성이거나 물질의 안정성 등의 각종 물성을 조정하거나 할 수 있다.

[0148] 또한, 기억 소자의 막 구성은 기억층(17)이 자화 고정층(15)의 하측에 배치되는 구성에서도, 하측에 배치되는 구성에서도 전혀 문제는 없다. 나아가, 자화 고정층(15)이 기억층(17)의 상하에 존재하는, 소위 듀얼 구조에서도 전혀 문제없다.

[0149] 또한, 기억 소자의 기억층(17)에 기록된 정보를 판독하는 방법으로서는 기억 소자의 기억층(17)에 얇은 절연막을 통하여, 정보의 기준이 되는 자성층을 설치하여, 절연층(16)을 통해 흐르는 강자성 터널 전류에 의해 판독해도 되고, 자기 저항 효과에 의해 판독해도 된다.

## <2. 제1 실시 형태의 구성>

[0151] 계속해서, 본 발명의 제1 실시 형태의 구체적 구성에 대해서 설명한다.

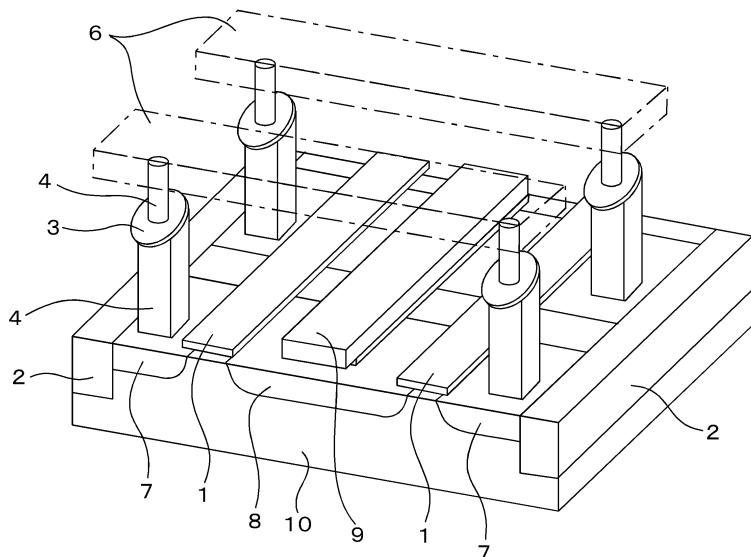

[0152] 본 발명의 일 실시 형태로서의 메모리 장치의 개략 구성도 사시도를 도 1에 도시한다.

[0153] 이 메모리 장치는 서로 직교하는 2종의 어드레스 배선(예를 들면 워드선과 비트선)의 교점 부근에, 자화 상태에서 정보를 유지할 수 있는 기억 소자(3)가 배치되어 이루어진다.

[0154] 즉, 실리콘 기판 등의 반도체 기체(10)의 소자 분리층(2)에 의해 분리된 부분에, 각 메모리 셀을 선택하기 위한 선택용 트랜지스터를 구성하는 드레인 영역(8), 소스 영역(7), 및 게이트 전극(1)이 각각 형성되어 있다. 이 중, 게이트 전극(1)은 도면 중 전후 방향으로 연장되는 한쪽의 어드레스 배선(예를 들면 워드선)을 겹하고 있다.

[0155] 드레인 영역(8)은 도면 중 좌우의 선택용 트랜지스터에 공통되어서 형성되어 있고, 이 도레인 영역(8)에는 배선(9)이 접속되어 있다.

[0156] 그리고, 소스 영역(7)과, 상방에 배치된 도면 중 좌우 방향으로 연장되는 다른 쪽의 어드레스 배선(예를 들면 비트선)(6) 사이에, 기억 소자(3)가 배치되어 있다. 이 기억 소자(3)는 스픬 주입에 의해 자화의 방향이 반전하는 강자성층으로 이루어지는 기억층을 갖는다.

[0157] 또한, 이 기억 소자(3)는 2종의 어드레스 배선(1,6)의 교점 부근에 배치되어 있다.

[0158] 이 기억 소자(3)는 비트선(6)과, 소스 영역(7)에, 각각 상하의 콘택트층(4)을 통해서 접속되어 있다.

[0159] 이에 의해, 2종의 어드레스 배선(1,6)을 통해서, 기억 소자(3)에 상하 방향의 전류를 흘려, 스픬 주입에 의해 기억층의 자화의 방향을 반전시킬 수 있다.

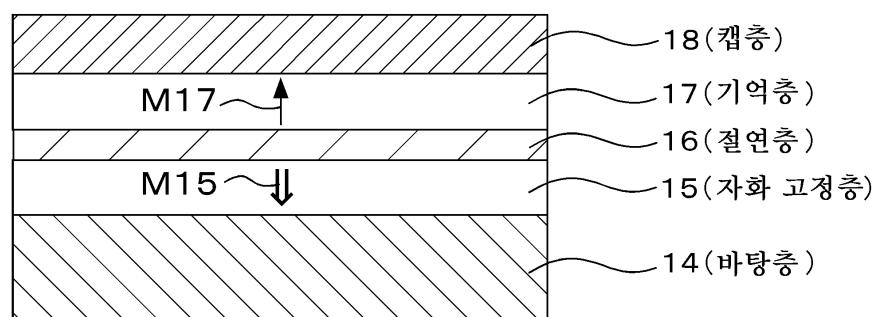

[0160] 또한, 본 실시 형태의 메모리 장치의 기억 소자(3)의 단면도를 도 2에 도시한다.

[0161] 도 2에 도시한 바와 같이, 이 기억 소자(3)는 하층부터 순서대로 바탕층(14), 자화 고정층(15), 절연층(16), 기억층(17), 캡층(18)이 적층되어 있다.

[0162] 이 경우, 스픬 주입에 의해 자화(M17)의 방향이 반전하는 기억층(17)에 대하여, 하층에 자화 고정층(15)을 설치하고 있다.

[0163] 스픬 주입형 자화 반전 메모리에 있어서는 기억층(17)의 자화(M17)와 자화 고정층(15)의 자화(M15)가 상대적인 각도에 의해 정보의 「0」 「1」을 규정하고 있다.

[0164] 기억층(17)과 자화 고정층(15) 사이에는 터널 베리어층(터널 절연층)이 되는 절연층(16)이 설치되어, 기억층

(17)과 자화 고정층(15)에 의해, MTJ 소자가 구성되어 있다.

[0165] 또한, 자화 고정층(15) 아래에는 바탕층(14)이 형성되고, 기억층(17) 위에는 캡층(18)이 형성되어 있다.

[0166] 기억층(17)은 자화(M17)의 방향이 층면 수직 방향으로 자유롭게 변화하는 자기 모멘트를 갖는 강자성체로 구성되어 있다. 자화 고정층(15)은 자화(M15)가 막면 수직 방향으로 고정된 자기 모멘트를 갖는 강자성체로 구성되어 있다.

[0167] 정보의 기억은 일축 이방성을 갖는 기억층(17)의 자화의 방향에 의해 행한다. 기입은 막면 수직 방향에 전류를 인가하고, 스펀 토크 자화 반전을 일으킴으로써 행한다. 이와 같이, 스펀 주입에 의해 자화의 방향이 반전하는 기억층(17)에 대하여, 하층에 자화 고정층(15)이 설치되어, 기억층(14)의 기억 정보(자화의 방향)의 기준이 된다.

[0168] 본 실시 형태에서는 기억층(17), 자화 고정층(15)로서는 Co-Fe-B를 사용한다.

[0169] 특히, 그의 Co-Fe-B의 조성이  $0 \leq Co_x \leq 40$ ,  $60 \leq Fe_y \leq 100$ ,  $0 < B_z \leq 30$ 에 있어서,  $(Co_x-Fe_y)_{100-z}-B_z$ 로 한다.

[0170] 자화 고정층(15)은 정보의 기준이므로, 기록이나 판독에 의해 자화의 방향이 변화해서는 안되지만, 반드시 특정한 방향으로 고정되어 있을 필요는 없고, 기억층(17)보다도 보자력을 크게 하거나, 막 두께를 두껍게 하거나, 또는 자기 덤핑 상수를 크게 해서 기억층(17)보다도 움직이기 어렵게 하면 된다.

[0171] 자화를 고정할 경우에는 PtMn, IrMn 등의 반강 자성체를 자화 고정층(15)에 접촉시키거나, 또는 그것들의 반강 자성체에 접촉한 자성체를 Ru 등의 비자성체를 통해서 자기적으로 결합시켜, 자화 고정층(15)을 간접적으로 고정할 수도 있다.

[0172] 본 실시 형태에 있어서는 특히, 기억층(17)이 받는 실효적인 반자계의 크기가 기억층(17)의 포화 자화량(Ms)보다도 작아지도록, 기억 소자(3)의 기억층(17)의 조성이 조정되어 있는 것을 특징으로 한다.

[0173] 즉, 상술한 바와 같이, 기억층(17)의 강자성 재료 Co-Fe-B 조성을 선정하고, 기억층(17)이 받는 실효적인 반자계의 크기를 낮게 하여, 기억층(17)의 포화 자화량(Ms)보다도 작아지도록 한다.

[0174] 또한, 본 실시 형태에 있어서, 중간층인 절연층(16)을 산화마그네슘층으로 한 경우에는, 자기 저항 변화율(MR비)을 높게 할 수 있다.

[0175] 이렇게 MR비를 높게 함으로써, 스펀 주입의 효율을 향상하고, 기억층(17)의 자화(M1)의 방향을 반전시키기 위해서 필요한 전류 밀도를 저감할 수 있다.

[0176] 본 실시 형태의 기억 소자(3)는 바탕층(14)으로부터 캡층(18)까지를 전공 장치 내에서 연속적으로 형성하고, 그 후 에칭 등의 가공에 의해 기억 소자(3)의 패턴을 형성함으로써, 제조할 수 있다.

[0177] 상술한 본 실시 형태에 의하면, 기억 소자(3)의 기억층(17)이 기억층(17)이 받는 실효적인 반자계의 크기가 기억층(17)의 포화 자화량(Ms)보다도 작아지도록 구성되어 있기 때문에, 기억층(17)이 받는 반자계가 낮아져 있고, 기억층(17)의 자화(M17)의 방향을 반전시키기 위해서 필요로 되는 기입 전류량을 저감할 수 있다.

[0178] 한편, 기억층(17)의 포화 자화량(Ms)을 저감하지 않아도 기입 전류량을 저감할 수 있기 때문에, 기억층(17)의 포화 자화량(Ms)을 충분한 양으로서, 기억층(17)의 열 안정성을 충분히 확보하는 것이 가능하게 된다.

[0179] 이와 같이, 정보 유지 능력인 열 안정성을 충분히 확보할 수 있기 때문에, 특성 균형이 우수한 기억 소자(3)를 구성할 수 있다.

[0180] 이에 의해, 동작 에러를 없애고, 기억 소자(3)의 동작 마진을 충분히 얻을 수 있고, 기억 소자(3)를 안정적으로 동작시킬 수 있다.

[0181] 따라서, 안정적으로 동작하는, 신뢰성이 높은 메모리 장치를 실현할 수 있다.

[0182] 또한, 기입 전류를 저감하여, 기억 소자(3)에 기입을 행할 때의 소비 전력을 저감하는 것이 가능하게 된다.

[0183] 따라서, 본 실시 형태의 기억 소자(3)에 의해 메모리 셀을 구성한 메모리 장치 전체의 소비 전력을 저감하는 것이 가능하게 된다.

[0184] 따라서, 정보 유지 특성이 우수한, 안정적으로 동작하는 신뢰성이 높은 메모리 장치를 실현할 수 있고, 기억 소자(3)를 구비한 메모리 장치에 있어서, 소비 전력을 저감할 수 있다.

- [0185] 또한, 도 2에 도시한 기억 소자(3)를 구비하는, 도 1에 나타낸 구성의 메모리 장치는 메모리 장치를 제조할 때에, 일반적인 반도체 MOS 형성 프로세스를 적용할 수 있다고 하는 이점을 갖고 있다.

- [0186] 따라서, 본 실시 형태의 메모리 장치를 범용 메모리로서 적용하는 것이 가능하게 된다.

- [0187] <3. 제1 실시 형태에 관한 실험>

- [0188] 여기서, 본 실시 형태의 기억 소자의 구성에 있어서, 구체적으로 기억층(17)을 구성하는 강자성층의 재료를 선정함으로써, 기억층이 받는 실효적인 반자계의 크기를 조정하고, 기억 소자의 시료를 제작하여, 그의 특성을 조사하였다.

- [0189] 실제의 메모리 장치에는 도 1에 도시한 바와 같이, 기억 소자(3) 이외에도 스위칭용의 반도체 회로 등이 존재하지만, 여기에서는 기억층(17)의 자화 반전 특성을 조사하는 목적에서, 기억 소자만을 형성한 웨이퍼에 의해 검토를 행하였다.

- [0190] [실험 1]

- [0191] 두께 0.725mm의 실리콘 기판 상에, 두께 300nm의 열 산화막을 형성하고, 그 위에 도 2에 도시한 구성의 기억 소자(3)를 형성하였다.

- [0192] 구체적으로는, 도 2에 도시한 구성의 기억 소자(3)에 있어서, 각 층의 재료 및 막 두께를 도 3에 나타내도록 선정하였다.

- [0193] · 바탕층(14): 막 두께 10nm의 Ta막과 막 두께 25nm의 Ru막의 적층막

- [0194] · 자화 고정층(15): 막 두께 2.5nm의 CoFeB막

- [0195] · 터널 절연층(16): 막 두께 0.9nm의 산화마그네슘막

- [0196] · 기억층(17): 자화 고정층과 동일한 조성의 CoFeB막

- [0197] · 캡층(18): 막 두께 3nm의 Ta막, 막 두께 3nm의 Ru막, 막 두께 3nm의 Ta막의 적층막

- [0198] 이렇게 각 층을 선정하고, 또한 바탕층(14)과 실리콘 기판 사이에 도시하지 않은 막 두께 100nm의 Cu막(후술하는 워드선이 되는 것)을 설치하였다.

- [0199] 상기 막 구성에서, 기억층(17)의 강자성층은 재질을 Co-Fe-B의 3원계 합금이라고 하고, 강자성층의 막 두께를 2.0nm로 고정하였다.

- [0200] 산화마그네슘막으로 이루어지는 절연층(16) 이외의 각 층은 DC 마그네트론 스퍼터법을 사용해서 성막하였다.

- [0201] 산화마그네슘(MgO)막으로 이루어지는 절연층(16)은 RF 마그네트론 스퍼터법을 사용해서 성막하였다.

- [0202] 또한, 기억 소자(3)의 각 층을 성막한 후에, 자장 중 열 처리로에서 가열 처리를 행하였다.

- [0203] 이어서, 워드선 부분을 포토리소그래피에 의해 마스크한 후에, 워드선 이외의 부분의 적층막에 대하여 Ar 플라즈마에 의해 선택 에칭을 행함으로써, 워드선(하부 전극)을 형성하였다.

- [0204] 이 때에, 워드선 부분 이외는 기판의 깊이 5mm까지 에칭되었다.

- [0205] 그 후, 전자 빔 묘화 장치에 의해 기억 소자(3)의 패턴의 마스크를 형성하고, 적층막에 대하여 선택 에칭을 행하여, 기억 소자(3)를 형성하였다. 기억 소자(3) 부분 이외는 워드선의 Cu층 바로 위까지 에칭하였다.

- [0206] 또한, 특성 평가용의 기억 소자에는 자화 반전에 필요한 스핀 토크를 발생시키기 위해서, 기억 소자에 충분한 전류를 흘릴 필요가 있기 때문에, 터널 절연층의 저항값을 억제할 필요가 있다. 따라서, 기억 소자(3)의 패턴을 단축  $0.09 \mu\text{m} \times \text{장축 } 0.18 \mu\text{m}$ 의 타원 형상으로 하여, 기억 소자(3)의 면적 저항값( $\Omega \mu\text{m}^2$ )이  $20 \Omega \mu\text{m}^2$ 가 되도록 하였다.

- [0207] 이어서, 기억 소자(3) 부분 이외를, 두께 100nm 정도의  $\text{Al}_2\text{O}_3$ 의 스퍼터링에 의해서 절연하였다.

- [0208] 그 후, 포토리소그래피를 사용하여, 상부 전극이 되는 비트선 및 측정용의 패드를 형성하였다.

- [0209] 이와 같이 하여, 기억 소자(3)의 시료를 제작하였다.

- [0210] 그리고, 상술한 제조 방법에 의해, 각각 기억층(17)의 강자성층의 Co-Fe-B 합금의 조성을 변경한 기억 소자(3)의 각 시료를 제작하였다.

- [0211] Co-Fe-B 합금의 조성은 CoFe와 B와의 조성비(원자%)를 80:20으로 고정하여, CoFe 중의 Co의 조성비 x(원자%)를 90%, 80%, 70%, 60%, 50%, 40%, 30%, 20%, 10%, 0%로 변화시켰다.

- [0212] 이상, 제작한 기억 소자(3)의 각 시료에 대하여, 각각 이하와 같이 하여, 특성의 평가를 행하였다.

- [0213] 측정에 앞서, 반전 전류의 플러스 방향과 마이너스 방향의 값을 대칭이 되도록 제어하는 것을 가능하게 하기 위해서, 기억 소자(3)에 대하여, 외부로부터 자계를 부여할 수 있도록 구성하였다.

- [0214] 또한, 기억 소자(3)에 인가되는 전압이, 절연층(16)을 파괴하지 않는 범위 내의 1V까지 되도록 설정하였다.

- [0215] (포화 자화량의 측정)

- [0216] 포화 자화량(Ms)을 시료 진동형 자력계(Vibrating Sample Magnetometer)를 사용한 VSM 측정에 의해, 측정하였다.

- [0217] (실효적인 반자계의 측정)

- [0218] 실효적인 반자계의 측정용의 시료로서, 상술한 기억 소자(3)의 시료와는 별도로, 기억 소자(3)를 구성하는 각 층을 형성하고, 이것을 20mm×20mm 각의 평면 패턴으로 형성한 시료를 제작하였다.

- [0219] 그리고, FMR(Ferromagnetic Resonance) 측정에 의해, 실효적인 반자계의 크기  $M_{\text{effective}}$ 를 구하였다.

- [0220] 이 FMR 측정에 의해 구해지는 임의의 외부 자장  $H_{\text{ex}}$ 에 대한 공명 주파수  $f_{\text{FMR}}$ 은 하기의 수학식 3으로 부여된다.

### 수학식 3

$$f_{\text{FMR}} = \gamma' \sqrt{4\pi M_{\text{effective}} (H_k + H_{\text{ex}})}$$

- [0221] 여기서, 수학식 3 중의  $M_{\text{effective}}$ 는  $4\pi M_{\text{effective}} = 4\pi M_{\text{s}} - H_{\perp}$  ( $H_{\perp}$ : 막면에 수직인 방향의 이방성 자계)로 나타낼 수 있다.

- [0222] (반전 전류값 및 열 안정성의 측정)

- [0223] 본 실시 형태에 의한 기억 소자(3)의 기입 특성을 평가하는 목적에서, 반전 전류값의 측정을 행하였다.

- [0224] 기억 소자(3)에 10  $\mu\text{s}$  내지 100ms의 펄스폭의 전류를 흘리고, 그 후의 기억 소자(3)의 저항값을 측정하였다.

- [0225] 또한, 기억 소자(3)에 흘리는 전류량을 변화시켜, 이 기억 소자(3)의 기억층(17)의 자화(M17)의 방향이 반전하는 전류값을 구하였다. 이 전류값의 펄스폭 의존성을 펄스폭 1ns에 외부 삽입한 값을 반전 전류값으로 하였다.

- [0226] 또한, 반전 전류값의 펄스폭 의존성의 기울기는 기억 소자(3)의 상술한 열 안정성의 지표( $\Delta$ )에 대응한다. 반전 전류값이 펄스폭에 의해 변화되지 않을(기울기가 작을)수록, 열의 요란에 강한 것을 의미한다.

- [0227] 그리고, 기억 소자(3) 사이의 편차를 고려하기 위해서, 동일 구성의 기억 소자(3)를 20개 정도 제작하여, 상술한 측정을 행하고, 반전 전류값 및 열 안정성의 지표  $\Delta$ 의 평균값을 구하였다.

- [0228] 또한, 측정에 의해 얻어진 반전 전류값의 평균값과, 기억 소자(3)의 평면 패턴의 면적으로부터, 반전 전류 밀도  $J_{\text{c}0}$ 를 산출하였다.

- [0229] 기억 소자(3)의 각 시료에 대해서, 기억층(17)의 Co-Fe-B 합금의 조성과, 포화 자화량 Ms 및 실효적인 반자계의 크기  $M_{\text{effective}}$ 의 측정 결과, 또한 포화 자화량과 실효적인 반자계의 크기와의 비  $M_{\text{effective}}/Ms$ 를 표 1에 나타내었다. 여기서, 표 1에 기재된 기억층(17)의 Co-Fe-B 합금의 Co량은 원자%로 나타내고 있다.

## 표 1

|                               | Ms(emu/cc) | Meffective(emu/cc) | Meffective/Ms |

|-------------------------------|------------|--------------------|---------------|

| $(Co_{90}Fe_{10})_{80}B_{20}$ | 960        | 1210               | 1.26          |

| $(Co_{80}Fe_{20})_{80}B_{20}$ | 960        | 1010               | 1.05          |

| $(Co_{70}Fe_{30})_{80}B_{20}$ | 1040       | 900                | 0.87          |

| $(Co_{60}Fe_{40})_{80}B_{20}$ | 1200       | 830                | 0.69          |

| $(Co_{50}Fe_{50})_{80}B_{20}$ | 1300       | 690                | 0.53          |

| $(Co_{40}Fe_{60})_{80}B_{20}$ | 1300       | 500                | 0.38          |

| $(Co_{30}Fe_{70})_{80}B_{20}$ | 1260       | 390                | 0.31          |

| $(Co_{20}Fe_{80})_{80}B_{20}$ | 1230       | 360                | 0.29          |

| $(Co_{10}Fe_{90})_{80}B_{20}$ | 1200       | 345                | 0.29          |

| $Fe_{80}B_{20}$               | 1160       | 325                | 0.28          |

[0231]

[0232] 표 1로부터,  $(Co_xFe_{100-x})_{80}B_{20}$ 의 Co량 x가 70% 이하인 경우에 있어서는, 실효적인 반자계의 크기(Meffective)는 포화 자화량 Ms보다도 작고, 즉 Co량 x가 70% 이하일 때의 비 Meffective/는 Ms, 1.0보다 작은 값으로 되어 있다.

[0233] 또한, Co량 x가 작아질수록, Meffective와 Ms의 차가 커지고 있는 것을 확인할 수 있다.

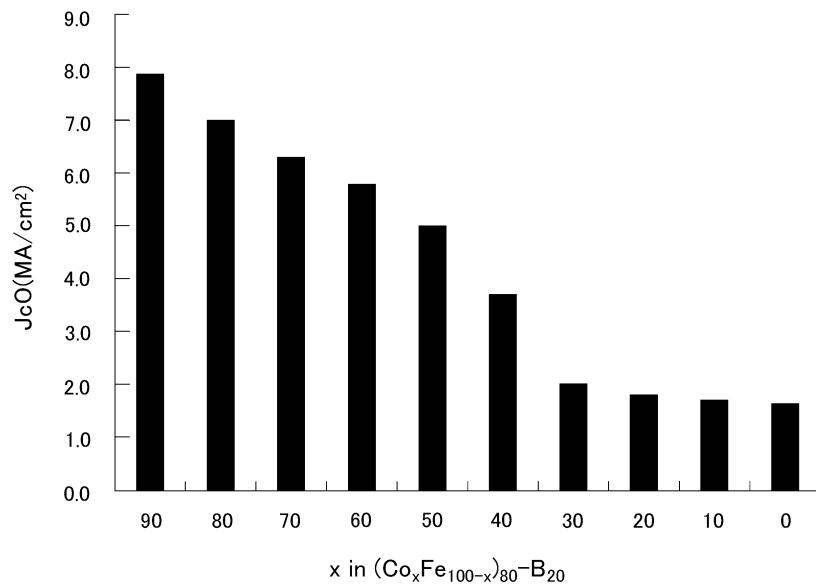

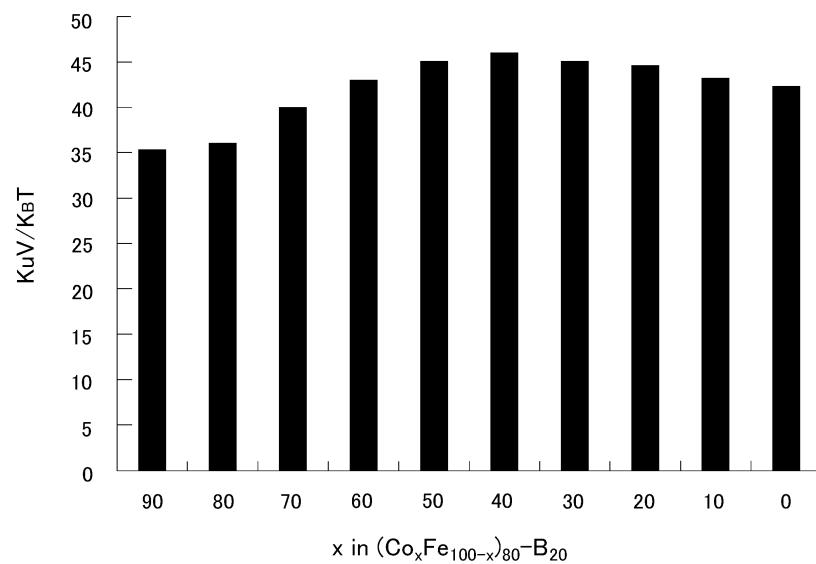

[0234] 반전 전류값의 측정 결과를 도 4에 도시하고, 열 안정성의 지표의 측정 결과를 도 5에 도시한다.

[0235] 도 4는 기억총(17)의 Co-Fe-B 합금의 Co량 x(CoFe 중의 함유량; 원자%)와, 반전 전류값으로부터 구한 반전 전류 밀도  $J_{c0}$ 와의 관계를 나타내고 있다.

[0236] 도 5는 기억총(17)의 Co-Fe-B 합금의 Co량(CoFe 중의 함유량; 원자%)과, 열 안정성의 지표  $\Delta$  ( $KV/k_B T$ )와의 관계를 나타내고 있다.

[0237] 도 4로부터, Co량 x가 작아짐에 따라서, 반전 전류 밀도  $J_{c0}$ 가 작아져 가는 것을 알 수 있었다.

[0238] 이것은 Co량 x가 작아졌을 경우, 포화 자화량 Ms는 증가하지만 실효적인 반자계 Meffective가 작아지기 때문에, 양자의 곱( $Ms \times Meffective$ )으로서는 작아지는 것에 기인한다.

[0239] 도 5로부터, Co량 x가 작아짐에 따라서, 열 안정성의 지표  $\Delta$  ( $=KV/k_B T$ )가 커져가고, Co량 x가 어느 정도 이상 작아지면 열 안정성의 지표  $\Delta$ 가 큰 값에서 안정되는 것을 알 수 있었다.

[0240] 이것은 도 5에 도시한 포화 자화량 Ms의 측정 결과와, 수학식 2로부터 열 안정성의 지표  $\Delta$ 가 포화 자화량 Ms에 비례하는 점에서 예상되는 변화와 잘 일치하고 있다.

[0241] 표 1, 도 4, 도 5의 결과로부터, 실효적인 반자계 Meffective가 포화 자화량 Ms보다도 적어지는, Co량 x가 70% 이하의 조성에 있어서, Ms를 내린다고 하는 열 안정성을 회생으로 하는 방법을 사용하지 않고, 높은 열 안정성을 가진 채, 반전 전류값  $J_{c0}$ 를 저감할 수 있는 것이 밝혀졌다.

[0242] [실험 2]

[0243] 상기의 [실험 1]에 의해,  $(Co_xFe_{100-x})_{80}B_{20}$ 의 경우, Co량 x가 70% 이하의 조성에서 높은 열 안정성을 가진 채, 반전 전류값  $J_{c0}$ 를 저감할 수 있는 것을 알 수 있었다.

[0244] 따라서, [실험 2]에 있어서  $(Co_{70}Fe_{30})_{80}B_z$ , 및  $(Co_{80}Fe_{20})_{80}B_z$  조성의 기억총(17)을 사용하여, B량 z가 Co와 Fe의

비와  $M_{\text{effective}}/Ms$ 에 어떤 영향을 부여하는지를 조사하였다. 시료의 상세는 [실험 1]과 동일하다.

[0245] 표 2에  $(\text{Co}_{70}\text{Fe}_{30})_{100-z}\text{B}_z$ 에서, B량  $z$ (원자%)를 5 내지 40%로 한 CoFeB 합금의 조성과, 포화 자화량  $Ms$  및 실효적인 반자계의 크기  $M_{\text{effective}}$ 의 측정 결과, 또한 포화 자화량과 실효적인 반자계의 크기와의 비  $M_{\text{effective}}/Ms$ 를 나타낸다.

[0246] 또한 표 3에는  $(\text{Co}_{80}\text{Fe}_{20})_{100-z}\text{B}_z$ 의 경우에서, 동일하게 B량  $z$ (원자%)를 5 내지 40%로 한 CoFeB 합금의 조성과, 포화 자화량  $Ms$ , 실효적인 반자계의 크기  $M_{\text{effective}}$ , 비  $M_{\text{effective}}/Ms$ 를 나타내고 있다.

## 표 2

|                                                     | $Ms(\text{emu/cc})$ | $M_{\text{effective}}(\text{emu/cc})$ | $M_{\text{effective}}/Ms$ |

|-----------------------------------------------------|---------------------|---------------------------------------|---------------------------|

| $(\text{Co}_{70}\text{Fe}_{30})_{95}\text{-B}_5$    | 1310                | 1090                                  | 0.83                      |

| $(\text{Co}_{70}\text{Fe}_{30})_{90}\text{-B}_{10}$ | 1250                | 1080                                  | 0.89                      |

| $(\text{Co}_{70}\text{Fe}_{30})_{80}\text{-B}_{20}$ | 1040                | 900                                   | 0.87                      |

| $(\text{Co}_{70}\text{Fe}_{30})_{70}\text{-B}_{30}$ | 820                 | 730                                   | 0.89                      |

| $(\text{Co}_{70}\text{Fe}_{30})_{60}\text{-B}_{40}$ | 450                 | 690                                   | 1.53                      |

[0247]

## 표 3

|                                                     | $Ms(\text{emu/cc})$ | $M_{\text{effective}}(\text{emu/cc})$ | $M_{\text{effective}}/Ms$ |

|-----------------------------------------------------|---------------------|---------------------------------------|---------------------------|

| $(\text{Co}_{80}\text{Fe}_{20})_{95}\text{-B}_5$    | 1250                | 1280                                  | 1.02                      |

| $(\text{Co}_{80}\text{Fe}_{20})_{90}\text{-B}_{10}$ | 1100                | 1140                                  | 1.04                      |

| $(\text{Co}_{80}\text{Fe}_{20})_{80}\text{-B}_{20}$ | 960                 | 1010                                  | 1.05                      |

| $(\text{Co}_{80}\text{Fe}_{20})_{70}\text{-B}_{30}$ | 750                 | 890                                   | 1.19                      |

| $(\text{Co}_{80}\text{Fe}_{20})_{60}\text{-B}_{40}$ | 430                 | 690                                   | 1.60                      |

[0248]

표 2의 결과로부터,  $(\text{Co}_{70}\text{Fe}_{30})_{100-z}\text{B}_z$ 와 같이 Co와 Fe의 비를 70/30으로 고정한 경우, B량  $z=40$ 원자% 이외의 조성에서는 실효적인 반자계  $M_{\text{effective}}$ 가 포화 자화량  $Ms$ 보다 작아져 있는 것을 확인할 수 있다.

[0250]

표 3의 결과로부터,  $(\text{Co}_{80}\text{Fe}_{20})_{100-z}\text{B}_z$ 와 같이 Co와 Fe의 비를 80/20으로 고정한 경우, 어느 쪽의 조성에 있어서도 실효적인 반자계  $M_{\text{effective}}$ 가 포화 자화량  $Ms$ 보다 커져 있는 것을 확인할 수 있다.

[0251]

상술한 표 1 내지 3의 결과로부터, B량  $z$ 가 30 원자% 이하의 범위이면, 포화 자화량  $Ms$ 과 실효적인 반자계  $M_{\text{effective}}$ 의 대소 관계는 Co와 Fe의 비로 결정되는 것이 명백하게 되었다.

[0252]

따라서, 기억총(17)의 실효적인 반자계  $M_{\text{effective}}$ 가 포화 자화량  $Ms$ 보다 작아지는 Co-Fe-B 합금의 조성은

[0253]

$0 \leq \text{Co}_x \leq 70$ ,

[0254]

$30 \leq \text{Fe}_y \leq 100$ ,

[0255]

$0 < B_z \leq 30$ 에 있어서,

[0256]

$(\text{Co}_x\text{-Fe}_y)_{100-z}\text{-B}_z$ 이다.

## [0257] [실험 3]

[0258] Gbit급의 스핀 주입형 자화 반전 메모리에서는 기록 소자의 크기가  $100\text{nm}\phi$  이하로 되는 것이 상정된다. 따라서, [실험 3]에 있어서,  $50\text{nm}\phi$ 의 크기의 기록 소자를 사용하여, 열 안정성을 평가하였다.

[0259] Co-Fe-B 합금의 조성은 CoFe와 B와의 조성비(원자%)를 80:20으로 고정하여, CoFe 중의 Co의 조성비  $x$ (원자%)를 90%, 80%, 70%, 60%, 50%, 40%, 30%, 20%, 10%, 0%로 변화시켰다.

[0260] 소자 크기 이외의 시료의 상세한 것은 [실험 1]과 동일하다.

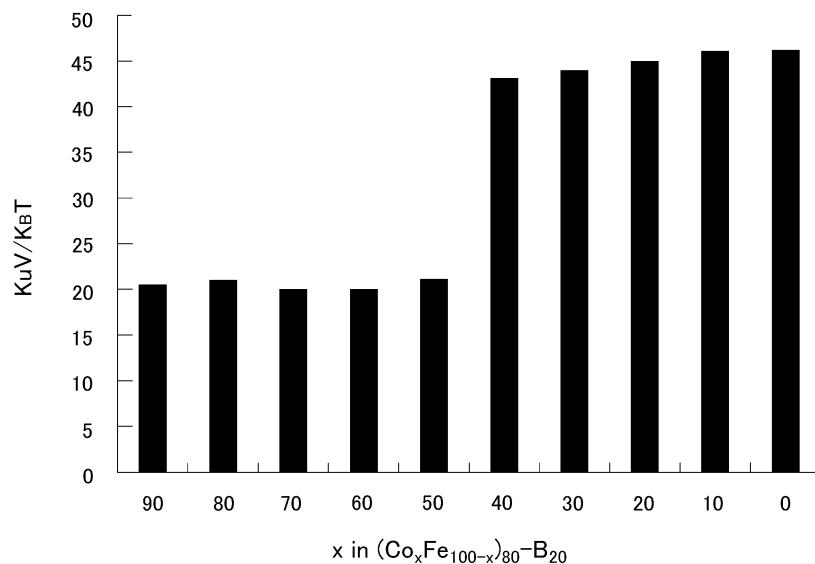

[0261] 기록 소자(3)의 크기가  $50\text{nm}\phi$ 의 경우의 Co-Fe-B 합금의 Co량(CoFe 중의 함유량; 원자%)과 열 안정성의 지표  $\Delta$ ( $\text{KV}/k_B T$ )의 관계를 도 6에 나타내었다.

[0262] 도 6으로부터, 소자 크기가  $50\text{nm}\phi$ 가 됨으로써, 열 안정성 지수  $\Delta$ 의 Co-Fe-B 합금 조성 의존성이 도 4에 도시한 단축  $0.09 \mu\text{m} \times$  단축  $0.18 \mu\text{m}$ 의 타원 형상 기록 소자에서 얻어진  $\Delta$ 의 Co-Fe-B 합금 조성 의존성으로부터 크게 변화된 것을 알 수 있었다.

[0263] 도 6에 의하면, Fe가 60 원자% 이상 존재하는 Co-Fe-B 합금 조성의 경우에만, 높은 열 안정성이 유지되고 있다.

[0264] 다양한 검토를 행한 결과, Fe가 60원자% 이상 존재하는 Co-Fe-B 합금이 지극히 미소한 기록 소자에 있어서 높은 열 안정성  $\Delta$ 를 나타내는 이유는, Co-Fe-B 합금의 자화가 막면 면직 방향(a direction perpendicular to a film face)을 향하고 있는 것에 기인하고 있는 것이 밝혀졌다.

[0265] Co-Fe-B 합금의 자화가 막면 면직 방향이 되어 있는 이유는, 실효적인 반자계  $M_{\text{effective}}$ 가 포화 자화량  $M_s$ 보다 현저하게 작은 조성인 것에 기인하고 있다고 생각된다.

[0266] 또한, 수직 자화막이 되면 극미소 소자에 있어서도 열 안정성이 유지되는 이유는, 수학식 2 종의  $H_k$ [실효적인 이방성 자계]에 관계하고 있고, 수직 자화막의  $H_k$ 는 일반적으로 면내 자화막보다도 훨씬 큰 값이 된다. 즉, 수직 자화막에서는 큰  $H_k$ 의 효과에 의해, 면내 자화막에서는 충분한 열 안정성  $\Delta$ 를 확보할 수 없는 지극히 미소한 소자에 있어서도 높은 열 안정성  $\Delta$ 를 유지할 수 있다.

[0267] 상기의 실험 결과로부터,  $(\text{Co}_x\text{Fe}_{100-x})_{80}\text{B}_{20}$ 이라고 하는 조성의 Co-Fe-B 합금에서는  $\text{Fe}_{100-x}$ 가 60 이상이 될 경우, Gbit급의 스핀 주입을 이용한 메모리 장치에 적합해진다고 할 수 있다.

## [0268] [실험 4]

[0269] 상기 [실험 3]에 있어서,  $(\text{Co}_x\text{Fe}_{100-x})_{80}\text{B}_{20}$ 이라고 하는 조성의 Co-Fe-B 합금에서는 Fe량이 60 이상이 될 경우, Gbit급의 스핀 주입을 이용한 메모리 장치에 적합해지는 것을 나타내었다. [실험 4]에서는 또한, B량을 5 내지 30원자% 범위의 Co-Fe-B 합금에서  $50\text{nm}\phi$ 의 크기의 기록 소자를 제작하여, 열 안정성을 평가하였다.

[0270] 소자 크기 이외의 시료의 상세한 것은 [실험 1]과 동일하다.

[0271] Co량  $x=50, 40, 30, 20, 10, 0$  및 B량  $z=5, 10, 20, 30$ 이라고 하는 범위에 있어서의  $(\text{Co}_x\text{Fe}_{100-x})_{100-z}\text{B}_z$ 라고 하는 조성의 Co-Fe-B 합금과 열 안정성의 지표  $\Delta$ ( $\text{KV}/k_B T$ )의 관계를 표 4에 나타내었다.

표 4

|                     | $(\text{Co}_{50}\text{Fe}_{50})_{100-z}\text{B}_z$ | $(\text{Co}_{40}\text{Fe}_{60})_{100-z}\text{B}_z$ | $(\text{Co}_{30}\text{Fe}_{70})_{100-z}\text{B}_z$ | $(\text{Co}_{20}\text{Fe}_{80})_{100-z}\text{B}_z$ | $(\text{Co}_{10}\text{Fe}_{90})_{100-z}\text{B}_z$ | $\text{Fe}_{100-z}\text{B}_z$ |

|---------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|-------------------------------|

| $B_z=5\text{원자\%}$  | 19                                                 | 40                                                 | 42                                                 | 42                                                 | 43                                                 | 44                            |

| $B_z=10\text{원자\%}$ | 20                                                 | 41.5                                               | 43                                                 | 44                                                 | 44                                                 | 45                            |

| $B_z=20\text{원자\%}$ | 20                                                 | 43                                                 | 44                                                 | 45                                                 | 46                                                 | 46                            |

| $B_z=30\text{원자\%}$ | 21                                                 | 45                                                 | 47                                                 | 48                                                 | 48                                                 | 48                            |

[0272] 표 4로부터, Co량  $x=50$  및 B량  $z=5$  내지 30의 경우를 제외한 모든 조성에 있어서 열 안정성  $\Delta$ 가 크게 유지되어

있는 것을 알 수 있었다.

[0274] 즉, [실험 4]의 결과와 마찬가지로, Co량  $x=50$ 과  $60$ 이 Gbit급의 스핀 주입형 자화 반전 메모리에 대응한 극미소 소자에서 높은 열 안정성을 확보할 때의 경계선이 되는 것이 밝혀졌다.

[0275] 따라서, 상기의 결과로부터, 기억층(17)의 Co-Fe-B 합금의 조성이

[0276]  $0 \leq Co_x \leq 40$ ,

[0277]  $60 \leq Fe_y \leq 100$ ,

[0278]  $0 < B_z \leq 30$ 에 있어서,

[0279]  $(Co_x-Fe_y)_{100-z}-B_z$ 일 경우, Gbit급의 스핀 주입형 자화 반전 메모리를 제작하기에 적합한 것이 판명되었다.

[0280] 또한 Co-Fe-B 합금은 Co와 Fe비의 Fe가 큰 조성에 있어서, 실효적인 반자계  $M_{\text{effective}}$ 와 포화 자화량  $M_s$ 의 차리가 커지고, 수직 자화하기 쉬워지기 때문에, 열 안정성을 확보하기 쉬워진다.

[0281] 그로 인해, 자기 메모리의 용량이 증가되고, 기억 소자(3)의 크기가 작아졌을 때는 Fe를 많이 포함하는 Co-Fe-B 합금쪽이 열 안정성을 확보하기 쉬워진다.

[0282] 거기에서, 예를 들면  $Fe_y$ 가  $60$ ,  $70\text{nm}\phi$ 의 기억층(17)에서 Gbit급의 스핀 주입형 자기 메모리를 실현할 수 있는 상황을 생각하면, 기억 소자(3)의 직경이  $5\text{nm}\phi$  작아질 때마다 Co-Fe-B 합금의 Fe량  $y$ 는 5씩 증가한 상태가 되어 있는 것이 바람직하다.

[0283] 예를 들면 Fe량  $y$ 는 상기의  $(Co_x-Fe_y)_{100-z}-B_z$ 의 경우에 있어서, CoFe 중의 함유량으로서의 원자%가  $65\%$ ,  $70\%$ ,  $75\%$ ,  $80\%$ …라고 하는 조성으로 하는(Co량  $x$ 에서 말하면,  $35\%$ ,  $30\%$ ,  $25\%$ ,  $20\%$ …로 하는) 것이, 기억 소자 크기의 축소에 따라 보다 적합한 예가 된다.

[0284] <4. 제2 실시 형태의 구성>

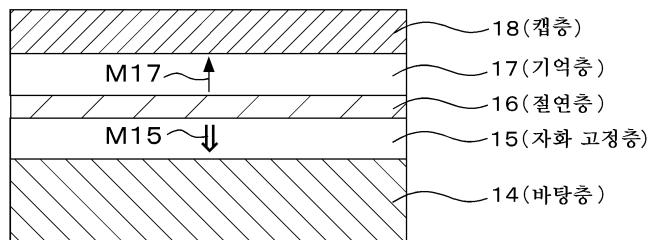

[0285] 제2 실시 형태에 대해서 설명한다. 또한 제2 실시 형태의 메모리 장치 및 기억 소자(3)의 구성에는 도 1, 도 2 와 동일하기 때문에, 그의 중복 설명은 피한다.

[0286] 이 제2 실시 형태는 제1 실시 형태와 동일하게, 기억층(17), 자화 고정층(15)으로서 Co-Fe-B를 사용하지만, 그의 Co-Fe-B의 조성이  $0 \leq Co_x \leq 40$ ,  $60 \leq Fe_y \leq 100$ ,  $20 < B_z \leq 40$ 에 있어서,  $(Co_x-Fe_y)_{100-z}-B_z$ 로 하는 것이다.

[0287] 반도체 디바이스인 스핀 주입형 자화 반전 메모리의 제조를 생각한 경우, 기억 소자(3)를 구성하는 자성 재료는 반도체 프로세스가 허용하는 온도 범위에서 우수한 특성을 발휘하는 것이 요망된다.

[0288] 예를 들면, Si 기판으로부터 모든 공정을 거쳐, 칩이 될 때까지 사이에 행해지는 반도체 프로세스에서 가해지는 열 부하는 350도 이상이 되는 경우가 있기 때문에, 그것을 고려하면, 기억 소자(3)를 구성하는 자성 재료는 350도 이상의 열 처리를 했을 때라도 우수한 특성이 될 필요가 있다.

[0289] 또한, 한편, 메모리 장치의 동작에 필요한 트랜지스터는 통상, 예를 들면 450도 이상의 고온에 노출되면 특성이 열화되어 버린다. 이 때문에 450도, 500도 등의 고온에서 가열한 상태에서 우수한 특성을 나타내는 자성 재료도 적합하지 않다.

[0290] 따라서, 스핀 주입형 자화 반전 메모리의 제조를 생각했을 경우, 기억 소자(3)를 구성하는 자성 재료는 대강 350도 이상 내지 450도 미만 정도의 온도 범위에서 양호한 특성을 나타내는 것이 필요하다.

[0291] 반도체 프로세스와의 열적인 친화성의 관점에서 생각하면, 일반적인 수직 자화 재료는 250도 이상의 고온에서 자기 및 TMR 특성을 열화시키는, 또는 500도 이상의 고온에 있어서 자기 특성이 출현되는 경우가 많기 때문에, 수직 자화막은 취급이 어렵다.

[0292] 그러나, 상술한 바와 같이 수직 자화막은 대용량, 저소비 전력화에 적합하다. 따라서, 반도체 프로세스와 친화성이 높은 열 처리 조건에서 저반전 전류이면서 고출력의 특성을 나타내는 스핀 주입형 자화 반전 메모리용의 수직 자화막을 개발하는 것은 중요하다.

[0293] 거기에서 제2 실시 형태는 상술한 바와 같이 대용량, 저소비 전력화에 적합한 수직 자기 이방성을 갖는 기록 소

자(3)를 사용한 메모리 장치에 있어서, 열 처리 온도가 350도 이상, 450도 미만의 범위에서 큰 자기 저항 변화율을 확보할 필요가 있다고 하는 인식에 기초하는 것이다.

[0294] 상술한 바와 같이 기록 전류를 저감시키기 위해서는, 수직 자화형을 채용하는 것이 바람직하다. 또한 수직 자화막은 일반적으로 면내 자화막보다도 높은 자기 이방성을 갖게 하는 것이 가능하기 때문에, 상술한 열 안정성  $\Delta$ 를 크게 유지하는 점에서도 바람직하다.

[0295] 수직 이방성을 갖는 자성 재료로는 희토류-전이 금속 합금(TbCoFe 등), 금속 다층막(Co/Pd 다층막 등), 규칙 합금(FePt 등), 산화물과 자성 금속 사이의 계면 이방성의 이용(Co/MgO 등) 등 몇가지 종류가 있다. 그러나, 희토류-전이 금속 합금은 가열에 의해 확산, 결정화되면 수직 자기 이방성을 상실하기 때문에, 스핀 주입형 자화 반전 메모리용 재료로서는 바람직하지 않다. 또한 금속 다층막도 가열에 의해 확산되어, 수직 자기 이방성이 열화되는 것이 알려져 있고, 또한 수직 자기 이방성이 발현하는 것은 면심 입방의 (111) 배향이 되어 있는 경우 이기 때문에, MgO나 그것에 인접해서 배치되는 Fe, CoFe, CoFeB 등의 고분극률층에 요구되는 (001) 배향을 실현시키는 것이 곤란해진다.

[0296] L10 규칙 합금은 고온에서도 안정되고, (001) 배향시에 수직 자기 이방성을 나타내는 점에서, 상술한 바와 같은 문제는 일어나지 않지만, 제조시에 500°C 이상의 충분히 높은 온도에서 가열하거나, 또는 제조 후에 500°C 이상의 고온에서 열 처리를 행함으로써 원자를 규칙 배열시킬 필요가 있고, 반도체 프로세스와의 친화성이 낮다. 또한, 터널 배리어 등 적층막의 다른 부분에 있어서의 바람직하지 않은 확산이나 계면 거칠기의 증대를 일으킬 가능성이 있다.

[0297] 이에 대해, 계면 자기 이방성을 이용한 재료, 즉 터널 배리어인 MgO 상에 Co계 또는 Fe계 재료를 적층시킨 것은 상기 어느 문제도 일어나기 어렵고, 이 때문에 스핀 주입형 자화 반전 메모리의 기억층 재료로서 유망시되어 있다.

[0298] 따라서, 본원의 발명자들이 다양하게 검토를 행한 결과, Co-Fe-B에서 구성되는 자성 재료이며, 조성이  $0 \leq Co_x \leq 40$ ,  $60 \leq Fe_y \leq 100$ ,  $20 \leq B_z \leq 40$ ,  $[(Co_x-Fe_y)_{100-z}-B_z]$ 의 범위에 있을 경우, 열 처리 온도를 350도 이상으로 한 상태에서도, 상기한 반전 전류를 나타내는 식 중의 스핀 분극률 P를 높게 유지할 수 있는 것을 발견하였다.

[0299] 고출력 소자는 스핀 분극률 P가 높은 점에서, 본 실시 형태에 의하면 저반전 전류화도 가능하다.

[0300] 또한, 높은 자기 이방성을 갖는 수직 자화 재료를 사용함으로써, 열 안정성을 희생으로 하는 일없이, 고출력이고 저소비 전력인 스핀 주입형의 자화 반전 소자(기억 소자 3)가 제공 가능하게 된다.

[0301] 제2 실시 형태의 메모리 장치 및 기억 소자(3)의 구성은 상기 도 1, 도 2와 동일하지만, 기억 소자(3)의 기억층 (17)이 상기 조성의 것이 된다.

[0302] 즉 제2 실시 형태의 기록 소자에 의하면, 정보를 자성체의 자화 상태에 의해 유지하는 기억층(17)을 갖고, 기억 층(17)에 대하여, 중간층인 절연층(16)을 통해서 자화 고정층(15)이 설치된다. 그리고 적층 방향에 스핀 편극 된 전자를 주입함으로써, 막면 수직 방향에 자기를 띠게 한 기억층(17)의 자화의 방향이 변화되어, 기억층(17)에 대하여 정보의 기록이 행해진다. 여기서 기억층(17)을 구성하는 강자성층 재료로서 예를 들면 상기 조성의 Co-Fe-B를 사용함으로써, 고온 열 처리에서도 높은 터널 자기 저항 효과 및 저반전 전류의 특성을 얻을 수 있다.

[0303] 이에 의해 고온 열 처리에서도 고출력, 저전류에서의 자화 반전을 가능하게 한다.

[0304] 또한 이 기억 소자(3)를 사용한 메모리 장치는 2종의 배선(도 1의 배선(1,6))을 통해, 기억 소자(3)에 적층 방향의 전류가 흘러, 스핀 트랜스퍼가 일어남으로써, 2종의 배선을 통해서 기억 소자(3)의 적층 방향에 전류를 흘려서 스핀 토크 자화 반전에 의한 정보의 기록을 행할 수 있다.

[0305] 이러한 제2 실시 형태에서는 고온 열 처리에서도 고출력이면서 저전류 동작과 같은 특성이 얻어지기 때문에, 특성 균형이 우수한 기억 소자(3)를 구성할 수 있다.

[0306] 또한, 높은 자기 이방성을 갖는 수직 자화막을 사용하고 있기 때문에, 정보의 열 안정성이 저하되는 경우도 없다.

[0307] 이에 의해, 동작 에러를 없애고, 기억 소자(3)의 동작 마진을 충분히 얻을 수 있고, 기억 소자(3)를 안정적으로 동작시킬 수 있다.

- [0308] 또한, 350도 이상 450도 미만의 고온 열 처리에서 뛰어난 특성을 나타내는 재료이기 때문에, 반도체 프로세스와의 친화성이 높다.

- [0309] 또한, 기록 소자(3)에 대한 기입 전류가 저감됨으로써, 기록 소자의 소비 전력을 저감하는 것이 가능하게 된다.

- [0310] 따라서, 본 실시 형태의 기억 소자(3)에 의해 메모리 셀을 구성한, 메모리 전체의 소비 전력을 저감하는 것이 가능하게 된다.

- [0311] 따라서, 안정적으로 동작하는 신뢰성이 높은 메모리를 실현할 수 있다.

- [0312] 또한, 도 2에 도시한 기억 소자(3)를 구비하는, 도 1에 도시한 구성의 메모리는 메모리를 제조할 때에 일반의 반도체 MOS 형성 프로세스를 적용할 수 있다고 하는 이점을 갖고 있다.

- [0313] 따라서, 본 실시 형태의 메모리를, 범용 메모리로서 적용하는 것이 가능하게 된다.

- [0314] 또한 자화 고정층(15)에 대해서도, 상기 조성의 Co-Fe-B로 해도 좋다.

- [0315] 또한 제2 실시 형태에 있어서도, 중간층인 절연층(16)을 산화마그네슘층으로 한 경우에는, 자기 저항 변화율(MR비)을 높게 할 수 있다.

- [0316] MR비를 높게 함으로써, 스팬 주입의 효율을 향상하고, 기억층(17)의 자화(M17)의 방향을 반전시키기 위해서 필요한 전류 밀도를 더 저감할 수 있다.

- [0317] 또한 기억 소자(3)는 바탕층(14)으로부터 캡층(18)까지를 진공 장치 내에서 연속적으로 형성하고, 그 후 에칭 등의 가공에 의해 기억 소자(3)의 패턴을 형성함으로써, 제조할 수 있다.

- [0318] <5. 제2 실시 형태에 관한 실험>

- [0319] 여기서, 실시 형태의 기억 소자(3)의 구성에 있어서, 구체적으로 기억층(17)을 구성하는 강자성층의 재료를 선정하여, 기억 소자(3)의 특성을 조사하였다.

- [0320] 상술한 [실험 1] 내지 [실험 4]와 동일하게, 기억층(17)의 자화 반전 특성을 조사하는 목적에서, 기억 소자(3)만을 형성한 웨이퍼에 의해 검토를 행하였다.

- [0321] [실험 5]

- [0322] 두께 0.725mm의 실리콘 기판 상에, 두께 300nm의 열 산화막을 형성하고, 그 위에 도 2에 도시한 구성의 기억 소자(3)를 도 7에 도시한 바와 같이 형성하였다.

- [0323] · 바탕층(14): 막 두께 10nm의 Ta막과 막 두께 10nm의 Ru막과 막 두께 10nm의 Ta막의 적층막

- [0324] · 자화 고정층(15): 막 두께 1.2nm의 CoFeB막

- [0325] · 터널 절연층(16): 막 두께 0.9nm의 산화마그네슘막

- [0326] · 기억층(17): 자화 고정층과 동일한 조성의 CoFeB막

- [0327] · 캡층(18): 막 두께 3nm의 Ta막, 막 두께 3nm의 Ru막, 막 두께 3nm의 Ta막의 적층막

- [0328] 이렇게 각 층을 선정하고, 또한 바탕막(14)과 실리콘 기판 사이에 도시하지 않은 막 두께 100nm의 Cu막(후술하는 워드선이 되는 것)을 설치하여, 각 층을 형성하였다.

- [0329] 상기 막 구성에서, 기억층(17)의 강자성층은 재질을 Co-Fe-B의 3원계 합금으로 하고, 강자성층의 막 두께를 1.5nm로 고정하였다.

- [0330] 산화마그네슘막으로 이루어지는 절연층(16) 이외의 각 층은 DC 마그네트론 스퍼터법을 사용해서 성막하였다.

- [0331] 산화마그네슘(MgO)막으로 이루어지는 절연층(16)은 RF 마그네트론 스퍼터법을 사용해서 성막하였다.

- [0332] 또한, 기억 소자(3)의 각 층을 성막한 후에, 자장 중 열 처리로에서, 각종 온도 · 1시간의 열 처리를 행하였다.

- [0333] 이어서, 워드선 부분을 포토리소그래피에 의해 마스크한 후에, 워드선 이외의 부분의 적층막에 대하여 Ar 플라즈마에 의해 선택 에칭을 행함으로써, 워드선(하부 전극)을 형성하였다. 이 때에, 워드선 부분 이외는 기판의 깊이 5nm까지 에칭되었다.

- [0334] 그 후, 전자 빔 묘화 장치에 의해 기억 소자(3)의 패턴의 마스크를 형성하고, 적층막에 대하여 선택 에칭을 행

하여, 기억 소자(3)를 형성하였다. 기억 소자(3) 부분 이외는 워드선의 Cu층 바로 위까지 예칭하였다.

[0335] 또한, 특성 평가용의 기억 소자에는 자화 반전에 필요한 스핀 토크를 발생시키기 위해서, 기억 소자에 충분한 전류를 흘릴 필요가 있기 때문에, 터널 절연층의 저항값을 억제할 필요가 있다. 따라서, 기억 소자(3)의 패턴을 단축  $0.09 \mu\text{m} \times$  장축  $0.09 \mu\text{m}$ 의 타원형 형상으로 하고, 기억 소자(3)의 면적 저항값( $\Omega \mu\text{m}^2$ )이  $20 \Omega \mu\text{m}^2$ 가 되도록 하였다.

[0336] 이어서, 기억 소자(3) 부분 이외를, 두께 100nm 정도의  $\text{Al}_2\text{O}_3$ 의 스퍼터링에 의해서 절연하였다.

[0337] 그 후, 포토리소그래피를 사용하여, 상부 전극이 되는 비트선 및 측정용의 패드를 형성하였다.

[0338] 이와 같이 하여, 기억 소자(3)의 시료를 제작하였다.

[0339] 그리고, 상술한 제조 방법에 의해, 각각 기억층(17)의 강자성층의 Co-Fe-B 합금의 조성을 변경한 기억 소자(3)의 각 시료를 제작하였다.

[0340] Co-Fe-B 합금의 조성은 Co와 Fe의 조성비(원자%)를 20:80으로 고정하여, B의 조성비 z(원자%)를 10%, 20%, 30%, 35%, 40%, 50%로 변화시켰다.

[0341] 이상, 제작한 기억 소자(3)의 각 시료에 대하여, 각각 이하와 같이 하여, 특성의 평가를 행하였다.

[0342] (TMR의 측정)

[0343] 본 발명에 의한 기억 소자의 출력 특성을 평가하는 목적에서, TMR의 측정을 행하였다.

[0344] 기억 소자(3)에 자장을 3kOe의 범위에서 소인하면서 100mV의 전압을 인가하여, 기억 소자(3)의 저항값을 측정하였다.

[0345] 그리고, 기억 소자(3) 사이의 편차를 고려하기 위해서, 동일 구성의 기억 소자(3)를 20개 정도 제작하고, 상술한 측정을 행하여, 특성의 평균값을 구하였다.

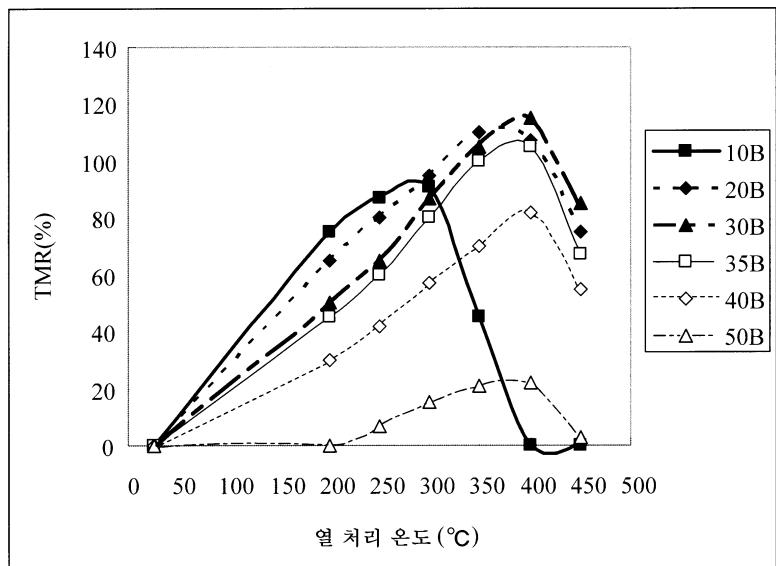

[0346] 기억 소자(3)의 각 시료에 대해서, 도 8에 기억층(17)의 Co-Fe-B 합금의 조성마다 TMR의 열 처리 온도 의존성을 나타내었다.

[0347] 도 8로부터, B 농도가 10%인 경우[도면 중의 10B], TMR은 열 처리 온도: 300도 부근에서 피크를 취하고 있는 것을 알 수 있었다.

[0348] 이에 대해, B 농도가 20 내지 40%의 조성 범위인 경우[도면 중의 20B 내지 40B], TMR의 피크가 열 처리 온도 350 내지 400도 부근으로 시프트하고 있다.

[0349] 또한, B 농도가 50%인 경우[도면 중의 50B], 200도 이상의 열 처리가 되면, TMR이 관측되게 되지만, TMR의 절대값이 다른 조성의 Co-Fe-B 합금과 비교해서 극단적으로 작아져 있는 것을 알 수 있었다.

[0350] B 농도가 40%인 경우, B 농도가 10 내지 35%의 시료의 최대 TMR[110% 정도]과 비교하여, 약간 작은 TMR에 머물고 있지만, 열 처리 온도 350 내지 400도 부근에서 약 80% 정도의 TMR은 확보되어 있고, 스핀 주입형 자화 반전 메모리에 적응 가능한 출력에 달하고 있다.

[0351] 또한 B 농도가 20 내지 30%의 시료에서는 450도 부근에서도 충분한 TMR이 확보되어 있다.

[0352] 결론으로서, B 농도가 20 내지 40%의 조성 범위인 경우, 반도체 프로세스로 가장 적합한 열 처리 범위에서, 가장 양호한 TMR 특성이 얻어지는 것을 확인할 수 있다.

[0353] 일반적으로, Co-Fe-B 합금을 사용해서 터널 자기 접합을 만들 경우, 열 처리에 의해 B가 MgO 배리어(절연층(16)) 또는 캡층(18)으로 확산되는 것이 알려져 있다. 열 처리 온도 350도 내지 400도의 범위에서 B 농도가 20 내지 40%가 적합해지는 이유는 이 B의 확산과 관계하고 있고, 초기의 Co-Fe-B 합금 조성으로서 어느 일정량의 B를 합금막 중에 존재시킴으로써, 원하는 열 처리 온도 범위에서 우수한 수직 자기 특성 및 TMR 특성이 얻어지는 B의 분포가 실현되고, 거기에 따른 MgO 배리어와 Co-Fe-B 합금의 계면 자기 이방성을 강화했기 때문이라고 예상된다.

[0354] 이 예상에 의하면, 450도 이상의 고온 열 처리에서도 우수한 TMR 특성이 얻어지는 B 농도가 존재하게 되지만, 본 실험에서 사용한 시료의 경우, 450도를 초과하는 열 처리에서는 바탕층(14)의 조도가 증대하고, 또한 과도한

바탕층(14), 캡층(18)의 확산이 발생하기 때문에, 모든 B 농도의 Co-Fe-B에서 TMR 특성이 열화된다고 생각된다.

[0355] B 농도가 10%인 경우, 350도 이상의 고온에서 TMR 특성이 열화된 원인은, 고온에서 열 처리한 경우에는 B 농도가 지나치게 적기 때문에, MgO 배리어와 Co-Fe-B 합금의 계면 자기 이방성을 강화할 수 없는 것에 기인한다고 생각된다.

[0356] 또한, B 농도가 50%인 경우에 양호한 TMR 특성이 얻어지지 않는 원인은, B 농도가 지나치게 높아 포화 자화가 극단적으로 저하되었기 때문이라고 추정된다.

[0357] 이상의 결과로부터, Co와 Fe의 조성비(원자%)를 20:80으로 고정한 Co-Fe-B 합금의 경우, B 농도가 20 내지 40 %로 열 처리 온도 350 내지 450의 범위에서 고출력의 기록 소자(3)를 작성할 수 있는 것이 실증되었다.

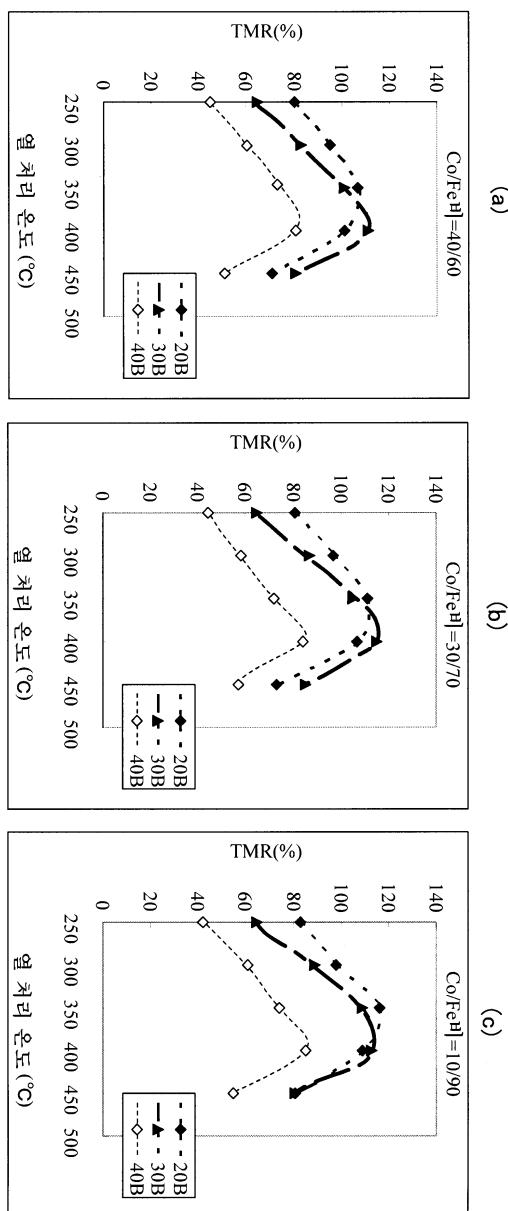

#### [실험 6]

[0359] 상기한 [실험 5]에서는 특정한 Co/Fe비로 B 농도를 바꾸었을 경우의 상세한 실험 결과를 나타내었다. 이어서, [실험 6]에서는 Co/Fe비를 40/60, 30/70, 10/90으로 하여, B 농도를 각각 20%, 30%, 40%로 변화시킨 기록 소자(17)를 작성하고, TMR 특성의 평가를 행하였다.

[0360] 도 9 (a) (b) (c)에, 각 Co/Fe비로 B 농도 및 열 처리 온도를 바꾸었을 경우의 TMR 특성을 나타내었다.

[0361] 이 결과로부터 알 수 있는 바와 같이, 어느 쪽의 조성에 있어서도 [실험 5]에서 나타낸 B 농도 [20 내지 40%], 열 처리 범위 [350도 내지 400도]에 있어서, 고출력[=고TMR]이 되는 특성이 얻어지고 있다.

[0362] 또한 450도 부근에서도 고출력[=고TMR]이 되는 조성도 보인다. 예를 들면 B 농도가 20 내지 30%의 조성이다.

[0363] 또한, TMR의 값에, Co/Fe비에 대한 큰 의존성은 관측되지 않는다.

[0364] 이상의 [실험 5] 및 [실험 6]의 결과에 의해, 조성이  $0 \leq Co_x \leq 40$ ,  $60 \leq Fe_y \leq 100$ ,  $20 < B_z \leq 40$ 에 있어서,  $(Co_x - Fe_y)_{100-z} - B_z$ 가 되는 수직 자화 강자성 재료 Co-Fe-B를 사용함으로써, 반도체 프로세스와 친화성이 높은 열 처리 온도 범위: 350도 내지 400도에서 고출력의 기록 소자가 제공 가능한 것이 나타난다.

[0365] 또한, 고출력을 실현함으로써, 높은 스픬 분극률 P도 동시에 실현함으로써, 저소비 전력화도 가능하게 된다.

[0366] 이렇게 수직 자화가 높은 자기 이방성을 활용함으로써 열 안정성을 희생으로 하는 수법을 이용하는 일없이, 고출력이면서 저반전 전류의 스픬 주입 자화 반전 소자가 제공 가능하게 된다.

[0367] 또한, 상기 제1 실시 형태에서는, B 농도에 대해서는  $0 < B_z \leq 30$ 의 범위에서 실효적인 반자계 M<sub>effective</sub>가 포화 자화량 M<sub>s</sub>보다 작아져, 수직 자화에 적합하다고 설명하였다.(예를 들면 상기 표 2 참조). 이에 대해, 제2 실시 형태에서는 B 농도에 대해서  $20 < B_z \leq 40$ 로 하는 것이지만, 그러면 30 내지 40%의 범위는 적절하지 않은 것처럼 보인다.

[0368] 그러나, 비교적 고온의 열 처리를 행하는 경우, B 농도가 30 내지 40%의 범위도, 실효적인 반자계 M<sub>effective</sub>가 포화 자화량 M<sub>s</sub>보다 작아져, 수직 자화에 적합한 것을 알 수 있었다.

[0369] 이하의 [표 5]는 기억층(17)의 Co-Fe-B 조성이  $(Co_{70}Fe_{30})_{65} - B_{35}$ 와,  $(Co_{70}Fe_{30})_{60} - B_{40}$ 의 경우에 대해서, 열 처리 온도를 400도로 했을 경우의 포화 자화량 M<sub>s</sub>와 실효적인 반자계 M<sub>effective</sub>에 대해서 조사한 것이다.

#### 표 5

|                                  | Ms(emu/cc) | M <sub>effective</sub> (emu/cc) | M <sub>effective</sub> /Ms |

|----------------------------------|------------|---------------------------------|----------------------------|

| $(Co_{70}Fe_{30})_{65} - B_{35}$ | 740        | 650                             | 0.88                       |

| $(Co_{70}Fe_{30})_{60} - B_{40}$ | 720        | 550                             | 0.89                       |

[0371] B 농도가 35%, 40%의 어느 경우에도, 실효적인 반자계 M<sub>effective</sub>가 포화 자화량 M<sub>s</sub>보다 작아져 (M<sub>effective</sub>/Ms<1) 있다.

[0372] 즉, 열 처리 온도가 높은 경우, B 농도가 30 내지 40%의 범위에서도, 기억층(17)이 받는 실효적인 반자계의 크

기가, 기억층(17)의 포화 자화량보다도 작다는 것을 만족하고 있는 것이 된다.

[0373] <6. 변형예>

[0374] 이상 실시 형태에 대해서 설명해 왔지만, 본 발명에서는 상술한 실시 형태에서 나타낸 기억 소자(3)의 막 구성으로 한정되지 않고, 여러가지 층 구성을 채용하는 것이 가능하다.

[0375] 예를 들면 실시 형태에서는 기억층(17)과 자화 고정층(15)의 Co-Fe-B의 조성을 동일한 것으로 하였지만, 상술한 실시 형태로 한정되는 것은 아니고, 본 발명의 요지를 일탈하지 않는 범위에서 기타 여러가지 구성을 취할 수 있다.

[0376] 또한, 실시 형태에서는 단일한 바탕층(14)이나, 캡 재료, 기억 소자 형상밖에 나타내고 있지 않지만, 그것들로 한정되는 것은 아니고, 본 발명의 요지를 일탈하지 않는 범위에서 그 밖의 다양한 구성을 취할 수 있다.

[0377] 또한 실시 형태에서는 자화 고정층(15)은 단층이었지만, 2층의 강자성층과 비자성층으로 이루어지는 적층 페리핀 구조를 사용해도 된다. 또한, 추가로 적층 페리핀 구조막에 반강자성막을 부여한 구조라도 좋다.

[0378] 또한, 기억 소자의 막 구성을 기억층(17)이 자화 고정층(15)의 상측에 배치되는 구성에서도, 하측에 배치되는 구성에서도 전혀 문제는 없다. 나아가, 자화 고정층(15)이 기억층(17)의 상하에 존재하는, 소위 듀얼 구조에서도 전혀 문제 없다.

### 부호의 설명

[0379] 3 기억 소자, 14 바탕층, 15 자화 고정층, 16 절연층, 17 기억층, 18 캡층

### 도면

#### 도면1

## 도면2

3

## 도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12