(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

H01L 21/28 (2006.01)

(45) 공고일자

2007년08월06일

(11) 등록번호

10-0746543

(24) 등록일자

2007년07월31일

(21) 출원번호 10-2000-0046084

(22) 출원일자 2000년08월09일

심사청구일자 2005년08월08일

(65) 공개번호

10-2001-0030070

(43) 공개일자

2001년04월16일

(30) 우선권주장 1999-226876 1999년08월10일 일본(JP)

(73) 특허권자 가부시키가이샤 히타치세이사쿠쇼

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 6고(72) 발명자 노구찌 준지

일본 도쿄도 지요다꾸 마루노우찌 1초메 5-1 신마루 빌딩가부시키가이

샤 히타치세이사쿠쇼 지적 소유권 본부 내

오하시 나오후미

일본 도쿄도 지요다꾸 마루노우찌 1초메 5-1 신마루 빌딩가부시키가이

샤 히타치세이사쿠쇼 지적 소유권 본부 내

다께다 겐이찌

일본 도쿄도 지요다꾸 마루노우찌 1초메 5-1 신마루 빌딩가부시키가이

샤 히타치세이사쿠쇼 지적 소유권 본부 내

사이또 다쓰유끼

일본 도쿄도 지요다꾸 마루노우찌 1초메 5-1 신마루 빌딩가부시키가이

샤 히타치세이사쿠쇼 지적 소유권 본부 내

야마구찌 히즈루

일본 도쿄도 지요다꾸 마루노우찌 1초메 5-1 신마루 빌딩가부시키가이

샤 히타치세이사쿠쇼 지적 소유권 본부 내

오와다 노부오

일본 도쿄도 지요다꾸 마루노우찌 1초메 5-1 신마루 빌딩가부시키가이

샤 히타치세이사쿠쇼 지적 소유권 본부 내

(74) 대리인

구영창

장수길

(56) 선행기술조사문현

JP11087353

JP11016912

심사관 : 이우식

전체 청구항 수 : 총 24 항

## (54) 반도체 집적 회로 장치의 제조 방법

---

### (57) 요약

다마신법을 이용하여 형성된 구리 배선의 절연 파괴 내성(신뢰성)을 향상하기 위해서, 실리콘 산화막(39)의 배선홈(40)에 매립하는 Cu 배선(46a ~ 46e)을 CMP를 이용한 연마로 형성하고, CMP 후의 세정 공정을 거친 후에 실리콘 산화막(39) 및 Cu 배선(46a ~ 46e)의 표면을 환원성 플라즈마(암모니아 플라즈마)로 처리한다. 그 후, 진공 파괴하지 않고 연속적으로 캡막(실리콘 질화막)을 형성한다.

### 대표도

도 16

### 특허청구의 범위

#### 청구항 1.

삭제

#### 청구항 2.

삭제

#### 청구항 3.

삭제

#### 청구항 4.

삭제

#### 청구항 5.

삭제

#### 청구항 6.

(a) 반도체 기판의 상층에 제1 절연막을 형성하고, 상기 제1 절연막에 홈을 형성하는 공정,

(b) 상기 홈 내 및 상기 홈 밖의 제1 절연막 상에 배리어 도전막을 퇴적하고, 상기 배리어 도전막 상에 구리를 주성분으로 하는 도전막을 퇴적하고, 상기 도전막으로 상기 홈 내를 매립하고 상기 제1 절연막 상에도 상기 도전막을 형성하는 공정,

(c) 상기 홈 이외의 상기 제1 절연막 상의 상기 도전막을 제1 연마 패드 및 제1 연마액에 의해 연마하여 제거한 후, 상기 제1 절연막 상의 상기 배리어 도전막을 제2 연마 패드 및 제2 연마액에 의해 연마하여 제거하여, 상기 홈 내에 상기 배리어 도전막 및 상기 도전막으로 이루어지는 배선을 형성하는 공정,

(d) 상기 제1 절연막 상 및 배선의 표면을 환원성 분위기의 플라즈마에 의해 처리하는 공정, 및

(e) 상기 플라즈마 처리 공정의 종료 후, 상기 제1 절연막 및 배선 상에 배리어 절연막을 퇴적하는 공정

을 포함하고,

상기 환원성 분위기의 플라즈마는, 수소(H<sub>2</sub>)와 희석 가스와의 혼합 가스 플라즈마이고,

상기 희석 가스는, 암모니아( $\text{NH}_3$ ), 질소( $\text{N}_2$ ), 아르곤(Ar), 헬륨(He)으로부터 선택된 단일 또는 복수의 가스이고, 상기 혼합 가스에 대한 수소( $\text{H}_2$ )의 농도는 5% 이상인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

### 청구항 7.

- (a) 반도체 기판의 상층에 제1 절연막을 형성하고, 상기 제1 절연막에 홈을 형성하는 공정,

- (b) 상기 홈 내 및 상기 홈 밖의 제1 절연막 상에 배리어 도전막을 퇴적하고, 상기 배리어 도전막 상에 구리를 주성분으로 하는 도전막을 퇴적하고, 상기 도전막으로 상기 홈 내를 매립하고 상기 제1 절연막 상에도 상기 도전막을 형성하는 공정,

- (c) 상기 홈 이외의 상기 제1 절연막 상의 상기 도전막을 제1 연마 패드 및 제1 연마액에 의해 연마하여 제거한 후, 상기 제1 절연막 상의 상기 배리어 도전막을 제2 연마 패드 및 제2 연마액에 의해 연마하여 제거하여, 상기 홈 내에 상기 배리어 도전막 및 상기 도전막으로 이루어지는 배선을 형성하는 공정,

- (d) 상기 제1 절연막 상 및 배선의 표면을 환원성 분위기의 플라즈마에 의해 처리하는 공정, 및

- (e) 상기 플라즈마 처리 공정의 종료 후, 상기 제1 절연막 및 배선 상에 배리어 절연막을 퇴적하는 공정

을 포함하고,

상기 제1 연마액의 지립(砥粒) 농도는 상기 제2 연마액의 지립 농도보다 낮은 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

### 청구항 8.

- (a) 반도체 기판의 상층에 제1 절연막을 형성하고, 상기 제1 절연막에 홈을 형성하는 공정,

- (b) 상기 홈 내 및 상기 홈 밖의 제1 절연막 상에 배리어 도전막을 퇴적하고, 상기 배리어 도전막 상에 구리를 주성분으로 하는 도전막을 퇴적하고, 상기 도전막으로 상기 홈 내를 매립하고 상기 제1 절연막 상에도 상기 도전막을 형성하는 공정,

- (c) 상기 홈 이외의 상기 제1 절연막 상의 상기 도전막을 제1 연마 패드 및 제1 연마액에 의해 연마하여 제거한 후, 상기 제1 절연막 상의 상기 배리어 도전막을 제2 연마 패드 및 제2 연마액에 의해 연마하여 제거하여, 상기 홈 내에 상기 배리어 도전막 및 상기 도전막으로 이루어지는 배선을 형성하는 공정,

- (d) 상기 제1 절연막 상 및 배선의 표면을 환원성 분위기의 플라즈마에 의해 처리하는 공정, 및

- (e) 상기 플라즈마 처리 공정의 종료 후, 상기 제1 절연막 및 배선 상에 배리어 절연막을 퇴적하는 공정

을 포함하고,

상기 환원성 분위기의 플라즈마는, 암모니아( $\text{NH}_3$ ), 수소( $\text{H}_2$ ), 또는, 이들의 가스와 질소( $\text{N}_2$ ), 아르곤(Ar), 헬륨(He)으로부터 선택된 단일 또는 복수의 가스와의 혼합 가스의 플라즈마인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

### 청구항 9.

- (a) 기판 주면 상에 실리콘 산화막보다 유전율이 낮은 유기 실록산계의 실리콘 산화막과 실리콘 산화막을 적층한 층간 절연막을 형성하는 공정,

- (b) 상기 실리콘 산화막을 관통하여 상기 유기 실록산계의 실리콘 산화막에 달하는 배선홈을 형성하고 상기 배선홈 내에 비어를 형성하는 공정,

- (c) 상기 배선홈 및 비어 내에 구리 또는 구리 합금을 매립하는 공정,

- (d) 상기 구리 또는 구리 합금의 표면 및 상기 실리콘 산화막의 표면을 암모니아 플라즈마로 처리하는 공정, 및

- (e) 상기 암모니아 플라즈마 처리된 표면에 구리 확산 배리어 절연막을 형성하는 공정

을 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

### 청구항 10.

- (a) 기판 주면 상에 층간 접속용 홈이 형성된 실리콘 산화막을 형성하는 공정,

- (b) 상기 홈 내 및 상기 실리콘 산화막 상에 배리어 금속막을 형성하는 공정,

- (c) 상기 배리어 금속막 상에 구리를 주성분으로 하는 도체막을 매립하고, 상기 홈 내 및 상기 실리콘 산화막 상에 상기 도체막을 퇴적하는 공정,

- (d) 상기 실리콘 산화막 상의 상기 도체막을 연마 지립 농도가 연마액의 0.5wt% 이하인 제1 연마액을 이용하여 연마하여 상기 실리콘 산화막 상의 상기 도체막을 제거하고, 또한 상기 실리콘 산화막 상의 상기 배리어 금속막을 제2 연마액을 이용하여 연마하여 제거하여, 상기 홈 내에 배리어 금속과 도체막을 형성하는 공정,

- (e) 상기 홈 내의 도체막 표면 및 상기 실리콘 산화막의 표면을 암모니아 플라즈마로 처리하여 표면을 환원함과 함께 질화하는 공정, 및

- (f) 상기 암모니아 플라즈마 처리된 표면에 구리 확산 배리어 절연막을 형성하는 공정

- 을 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

### 청구항 11.

- (a) 기판 주면 상에 층간 접속용 홈이 형성된 실리콘 산화막을 형성하는 공정,

- (b) 상기 홈 내 및 상기 실리콘 산화막 상에 배리어 금속막을 형성하는 공정,

- (c) 상기 배리어 금속막 상에 구리를 주성분으로 하는 도체막을 매립하고, 상기 홈 내 및 상기 실리콘 산화막 상에 상기 도체막을 퇴적하는 공정,

(d) 상기 실리콘 산화막 상의 상기 도체막을 산화제와 유기산을 포함하고 상기 도체막에 대한 pH 및 산화 환원 전위가 부식 영역에 있는 연마액을 이용하여 연마하여 상기 실리콘 산화막 상의 상기 도체막을 제거하고, 또한 상기 실리콘 산화막 상의 상기 배리어 금속막을 다른 연마액을 이용하여 연마하여 제거하여, 상기 홈 내에 배리어 금속과 도체막을 형성하는 공정,

(e) 상기 홈 내의 도체막 표면 및 상기 실리콘 산화막의 표면을 암모니아

플라즈마로 처리하는 공정, 및

(f) 상기 암모니아 플라즈마 처리된 표면에 구리 확산 배리어 절연막을

형성하는 공정

을 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

## 청구항 12.

(a) 기판 주면 상에 층간 접속용 홈이 형성된 실리콘 산화막을 형성하는 공정,

(b) 상기 홈 내 및 상기 실리콘 산화막 상에 배리어 금속막을 형성하는 공정,

(c) 상기 배리어 금속막 상에 구리를 주성분으로 하는 도체막을 매립하고, 상기 홈 내 및 상기 실리콘 산화막 상에 상기 도체막을 퇴적하는 공정,

(d) 상기 실리콘 산화막 상의 상기 도체막을 상기 배리어 금속막을 스토퍼층으로 하여 제1 연마액을 이용하여 연마하여 상기 실리콘 산화막 상의 상기 도체막을 제거하고, 또한 상기 실리콘 산화막 상의 상기 배리어 금속막을 제2 연마액을 이용하여 연마하여 제거하여, 상기 홈 내에 배리어 금속과 도체막을 형성하는 공정,

(e) 상기 홈 내의 도체막 표면 및 상기 실리콘 산화막의 표면을 암모니아

플라즈마로 처리하여 표면을 환원함과 함께 질화하는 공정, 및

(f) 상기 암모니아 플라즈마 처리된 표면에 구리 확산 배리어 절연막을

형성하는 공정

을 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

## 청구항 13.

(a) 기판 주면 상에 층간 접속용 홈이 형성된 실리콘 산화막을 주체로 하는

층간 절연막을 형성하는 공정,

(b) 상기 홈 내 및 상기 층간 절연막 상에 배리어 금속막을 형성하는 공정,

(c) 상기 배리어 금속막 상에 구리를 주성분으로 하는 도체막을 매립하고, 상기 홈 내 및 상기 층간 절연막 상에 상기 도체막을 퇴적하는 공정,

- (d) 상기 충간 절연막 상의 상기 도체막과 상기 배리어 금속막을 화학 기계 연마법으로 연마하여 제거하여, 상기 홈 내에 배리어 금속과 도체막을 형성하는 공정,

- (e) 상기 배리어 금속과 도체막을 매립한 표면 상을 유기산을 포함하는 세정액으로 클리닝하는 공정,

- (f) 상기 홈 내의 도체막 표면 및 상기 실리콘 산화막의 표면을 암모니아 플라즈마로 처리하여 표면을 환원함과 함께 질화하는 공정, 및

- (g) 상기 암모니아 플라즈마 처리된 표면에 실란을 주체로 하는 플라즈마 CVD법에 의해 실리콘을 포함하는 구리 확산 배리어 절연막을 형성하는 공정

- 을 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

#### 청구항 14.

제13항에 있어서,

상기 유기산은 구연산인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

#### 청구항 15.

- (a) 기판 주면 상에 충간 접속용 홈이 형성된 실리콘 산화막을 주체로 하는 충간 절연막을 형성하는 공정,

- (b) 상기 홈 내 및 상기 충간 절연막 상에 배리어 금속막을 형성하는 공정,

- (c) 상기 배리어 금속막 상에 구리를 주성분으로 하는 도체막을 매립하고 상기 홈 내 및 상기 충간 절연막 상에 상기 도체막을 퇴적하는 공정,

- (d) 상기 충간 절연막 상의 상기 도체막과 상기 배리어 금속막을 화학 기계 연마법으로 연마하여 제거하여 상기 홈 내에 배리어 금속과 도체막을 형성하는 공정,

- (e) 상기 배리어 금속과 도체막을 매립한 표면 상을 유기산을 포함하는 세정액으로 PVA 브러시를 사용하여 클리닝하는 공정,

- (f) 상기 클리닝한 기판을 건조하는 공정,

- (g) 상기 홈 내의 도체막 표면 및 상기 실리콘 산화막의 표면을 암모니아 플라즈마로 처리하여 표면을 환원함과 함께 질화하는 공정, 및

- (h) 상기 암모니아 플라즈마 처리된 표면에 플라즈마 CVD법에 의해 실리콘을 포함하는 구리 확산 배리어 절연막을 형성하는 공정

- 을 포함하고, 상기 (g), (h) 공정은 기판을 대기중에 노출시키지 않고 처리하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

#### 청구항 16.

- (a) 기판 주면 상에 충간 접속용 홈이 형성된 실리콘 산화막을 주체로 하는 충간 절연막을 형성하는 공정,

- (b) 상기 홈 내 및 상기 층간 절연막 상에 배리어 금속막을 형성하는 공정,

- (c) 상기 배리어 금속막 상에 구리를 주성분으로 하는 도체막을 매립하고 상기 홈 내 및 상기 층간 절연막 상에 상기 도체막을 퇴적하는 공정,

- (d) 상기 층간 절연막 상의 상기 도체막과 상기 배리어 금속막을 화학 기계 연마법으로 연마하여 제거하여 상기 홈 내에 배리어 금속과 도체막을 형성하는 공정,

- (e) 상기 배리어 금속과 도체막을 매립한 표면 상을 브러시를 사용하여 유기산을 포함하는 세정액으로 클리닝하는 공정,

- (f) 상기 홈 내의 도체막 표면 및 상기 실리콘 산화막의 표면을 암모니아 플라즈마로 처리하여 표면을 환원함과 함께 질화하는 공정, 및

- (g) 상기 암모니아 플라즈마 처리된 표면에 실란을 주체로 하는 플라즈마 CVD법에 의해 실리콘을 포함하는 구리 확산 배리어 절연막을 형성하는 공정

- 을 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

#### 청구항 17.

- (a) 기판 주면 상에 층간 접속용 홈이 형성된 실리콘 산화막을 주체로 하는 층간 절연막을 형성하는 공정,

- (b) 상기 홈 내 및 상기 층간 절연막 상에 배리어 금속막을 형성하는 공정,

- (c) 상기 배리어 금속막 상에 구리를 주성분으로 하는 도체막을 매립하고 상기 홈 내 및 상기 층간 절연막 상에 상기 도체막을 퇴적하는 공정,

- (d) 상기 층간 절연막 상의 상기 도체막과 상기 배리어 금속막을 화학 기계 연마법으로 연마하여 제거하여 상기 홈 내에 배리어 금속과 도체막을 형성하는 공정,

- (e) 상기 (d) 공정 후 다음의 (f) 공정까지의 사이에서 상기 기판의 표면을 100 Lux 이하로 차광된 상태에서 유수(流水)로 습윤 상태로 보관하는 공정,

- (f) 상기 홈 내의 도체막 표면 및 상기 실리콘 산화막의 표면을 암모니아 플라즈마로 처리하여 표면을 환원함과 함께 질화하는 공정, 및

- (g) 상기 암모니아 플라즈마 처리된 표면에 플라즈마 CVD법에 의해 구리 확산 배리어 절연막을 형성하는 공정

- 을 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

#### 청구항 18.

삭제

#### 청구항 19.

삭제

#### 청구항 20.

삭제

### 청구항 21.

제17항에 있어서,

상기 (d) 공정과 (e) 공정 사이에서 상기 기판 표면에 방식(防食) 처리를 행하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

### 청구항 22.

- (a) 기판 주변 상에 층간 접속용 흄이 형성된 실리콘 산화막을 주체로 하는 층간 절연막을 형성하는 공정,

- (b) 상기 흄 내 및 상기 층간 절연막 상에 배리어 금속막을 형성하는 공정,

- (c) 상기 배리어 금속막 상에 구리를 주성분으로 하는 도체막을 매립하고 상기 흄 내 및 상기 층간 절연막 상에 상기 도체막을 퇴적하는 공정,

- (d) 상기 층간 절연막 상의 상기 도체막과 상기 배리어 금속막을 화학 기계 연마법으로 연마하여 제거하여 상기 흄 내에 배리어 금속과 도체막을 형성하는 공정,

- (e) 상기 기판의 표면을 100Lux 이하로 차광된 상태에서 상기 배리어 금속과 도체막을 매립한 표면 상을 브러시를 사용하여 세정액으로 클리닝하는 공정,

- (f) 상기 흄 내의 도체막 표면 및 상기 실리콘 산화막의 표면을 암모니아 플라즈마로 처리하여 표면을 환원함과 함께 질화하는 공정, 및

- (g) 상기 암모니아 플라즈마 처리된 표면에 플라즈마 CVD법에 의해 구리 확산 배리어 절연막을 형성하는 공정

을 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

### 청구항 23.

제22항에 있어서,

상기 (d) 공정과 (e) 공정 사이에서 상기 기판 표면에 방식 처리를 행하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

### 청구항 24.

- (a) 기판 주변 상에 층간 접속용 흄이 형성된 실리콘 산화막을 주체로 하는 층간 절연막을 형성하는 공정,

- (b) 상기 흄 내 및 상기 층간 절연막 상에 배리어 금속막을 형성하는 공정,

- (c) 상기 배리어 금속막 상에 구리를 주성분으로 하는 도체막을 매립하고 상기 흄 내 및 상기 층간 절연막 상에 상기 도체막을 퇴적하는 공정,

- (d) 상기 층간 절연막 상의 상기 도체막과 상기 배리어 금속막을 화학 기계 연마법으로 연마하여 제거하여 상기 흄 내에 배리어 금속과 도체막을 형성하는 공정,

- (e) 상기 (d) 공정 후 다음의 (f) 공정의 개시까지의 사이에서 상기 기판의 표면을 100Lux 이하로 차광된 상태에서 유수로 습윤 상태로 보관하는 공정,

- (f) 상기 배리어 금속과 도체막을 매립한 표면 상을 브러시를 사용하여 세정액으로 클리닝하는 공정,

- (g) 상기 홈 내의 도체막 표면 및 상기 실리콘 산화막의 표면을 암모니아 플라즈마로 처리하여 표면을 환원함과 함께 질화하는 공정, 및

- (h) 상기 암모니아 플라즈마 처리된 표면에 플라즈마 CVD법에 의해 구리 확산 배리어 절연막을 형성하는 공정을 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

## 청구항 25.

- (a) 기판 주면 상에 저유전율 충간 절연막을 형성하는 공정,

- (b) 상기 저유전율 충간 절연막보다 유전율이 큰 실리콘 산화막을 상기 저유전율 충간 절연막 상에 형성하여 상기 실리콘 산화막과 상기 저유전율 충간 절연막으로 이루어지는 제1 충간 절연막을 형성하는 공정,

- (c) 상기 제1 충간 절연막에 홈을 형성하는 공정,

- (d) 상기 홈 내 및 상기 제1 충간 절연막 상에 배리어 금속막을 형성하는 공정,

- (e) 상기 배리어 금속막 상에 구리를 주성분으로 하는 도체막을 매립하고 상기 홈 내 및 상기 제1 충간 절연막 상에 상기 도체막을 퇴적하는 공정,

- (f) 상기 제1 충간 절연막 상의 상기 도체막과 상기 배리어 금속막을 화학 기계 연마법으로 연마하여 상기 홈 내에 배리어 금속과 도체막을 형성하는 공정,

- (g) 상기 홈 내의 도체막 표면 및 상기 실리콘 산화막의 표면을 암모니아 플라즈마로 처리하여 표면을 환원함과 함께 질화하는 공정, 및

- (h) 상기 암모니아 플라즈마 처리된 표면에 플라즈마 CVD법에 의해 구리 확산 배리어 절연막을 형성하는 공정을 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

## 청구항 26.

제25항에 있어서,

상기 저유전율 충간 절연막은 유기 폴리머막인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

## 청구항 27.

제25항에 있어서,

상기 저유전율 충간 절연막은 비유전율이 3.0 이하의 실리콘 산화막인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

## 청구항 28.

제27항에 있어서,

상기 저유전율 층간 절연막은 유기 SOG 또는 무기 SOG인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

## 청구항 29.

(a) 기판 주면 상에 저유전율 층간 절연막을 형성하는 공정,

(b) 상기 저유전율 층간 절연막보다 유전율이 큰 실리콘 산화막을 상기 저유전율 층간 절연막 상에 형성하여 상기 실리콘 산화막과 상기 저유전율 층간 절연막으로 이루어지는 제1 층간 절연막을 형성하는 공정,

(c) 상기 제1 층간 절연막에 층간 접속영역을 형성하는 공정,

(d) 상기 홈 내 및 상기 제1 층간 절연막 상에 배리어 금속막을 형성하는 공정,

(e) 상기 배리어 금속막 상에 구리를 주성분으로 하는 도체막을 매립하고 상기 홈 내 및 상기 제1 층간 절연막 상에 상기 도체막을 퇴적하는 공정,

(f) 상기 제1 층간 절연막 상의 상기 도체막과 상기 배리어 금속막을 화학 기계 연마법으로 연마하여 제거하여 상기 홈 내에 배리어 금속과 도체막을 형성하는 공정,

(g) 상기 홈 내의 도체막 표면 및 상기 실리콘 산화막의 표면을 암모니아 플라즈마로 처리하여 표면을 활원함과 함께 질화하는 공정, 및

(h) 상기 암모니아 플라즈마 처리된 표면에 플라즈마 CVD법에 의해 구리 확산 배리어 절연막을 형성하는 공정

을 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

## 청구항 30.

제29항에 있어서,

상기 저유전율 층간 절연막은 유기 폴리머막인 것을 특징으로 하는 반도체

집적 회로 장치의 제조 방법.

## 청구항 31.

제29항에 있어서,

상기 저유전율 층간 절연막은 비유전율이 3.0 이하의 실리콘 산화막인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

## 청구항 32.

제31항에 있어서,

상기 저유전율 층간 절연막은 유기 SOG 또는 무기 SOG인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 반도체 집적 회로 장치 및 반도체 집적 회로 장치의 제조 방법에 관한 것으로, 특히 구리를 주도전층으로 하는 배선을 절연막으로의 홈 형성, 홈을 매립하는 구리막의 형성, 및 CMP(Chemical Mechanical Polishing)법을 이용한 연마에 의해 형성되는 소위 다마신법(damascene method)에 적용하여 유효한 기술에 관한 것이다.

최근 반도체 집적 회로 장치에서의 배선의 미세화에 따른 배선 저항의 증대, 배선 지연의 증가, 및 이들에 기인하는 반도체 집적 회로 장치 성능의 저하가 문제가 되고 있다. 특히, 고성능인 논리 LSI에서는 그 성능 저해 요인으로서 큰 문제를 야기하고 있다. 이 때문에, 예를 들면 1993 VMIC(VLSI Multilevel Interconnection Conference) 예비 요약 원고집, p15 ~ p21에 기재되어 있듯이 절연막에 형성한 배선홈에 구리 (Cu)를 주도체층으로 하는 배선용 금속을 매립한 후, 배선홈 외부의 여분의 금속을 화학 기계 연마법(CMP법)을 이용하여 제거함으로써 배선홈 내에 배선 패턴을 형성하는 방법이 검토되고 있다.

또, 특개평 9-306915호 공보에는 반도체 기판 상의 실리콘 산화막에 배선홈을 형성한 후, 스퍼터링법(sputtering method)을 이용하여 질화 티탄막 및 구리막을 퇴적하고, 리플로우(reflow)에 의해 홈 내에 구리를 충전하고, 그 후 CMP 법에 의해 홈 이외의 구리막을 제거하여 또한 수소 분위기 중에서 열처리를 실시하는 기술이 기재되어 있다. 이에 따라 구리 배선 중의 결함을 저감할 수 있다.

또한, 특개평 10-56014호 공보에는 반도체 기판 상에 형성된 질화 티탄막 및 텅스텐막을 갖는 피연마 재료를 CMP법에 의해 연마한 후, 그 연마된 표면에 할로겐계 혼합 가스를 이용한 플라즈마 처리를 실시하는 기술이 기재되어 있다. 이에 따라, CMP법에 의해 형성되는 마이크로 스크래치(micro scratch)가 형성되어도 배선 쇼트(short)가 생기지 않는다.

또한, 특개평 10-56014호 공보에는 배선을 형성하고자 하는 하지측(base) 상에 감광성 SOG막을 형성하고, 이 SOG막에 배선홈을 형성하고, 질화 티탄막, 구리막, 및 구리 티탄 합금막을 형성하고, CMP법에 의한 연마에 의해 배선홈 내에만 상기 피막을 남기며 또한 암모니아 분위기에서 가열 처리하여 구리 티탄 합금막의 표층부에 질화 티탄막을 형성하는 기술이 기재되어 있다.

또한, 특개평 11-16912호 공보에는 다마신법에 의한 구리 배선 등에서의 관통 구멍 등의 표면을 암모니아 등의 분위기 중에서 플라즈마 처리 등을 실시하는 기술이 기재되고 있다.

#### 발명이 이루고자 하는 기술적 과제

상기 배선홈을 형성한 후에 이것을 매립하는 금속막(예를 들면 구리막)을 형성하고, 배선홈 이외의 구리막을 CMP법에 의해 제거하는 배선 형성법 소위 다마신법에 의한 배선 형성 기술에 있어서 본 발명자 등은 이하에 설명하는 것과 같은 문제를 인식하였다.

즉, 고성능의 논리 LSI로의 적용을 고려한 경우, 배선 저항의 저감은 중요한 기술 검토 과제 중 하나이다. 그래서, 발명자 등은 배선을 구성하는 금속으로서 구리를 검토하고 있다. 구리는 그 물성으로서 다른 금속(예를 들면 알루미늄, 텅스텐)과 비교하여 절연막인 실리콘 산화막 내에 확산하기 쉬운 성질을 포함한다. 따라서, 배선을 덮는 배리어막의 검토가 중요하다. 배선홈 내의 배리어막으로서는 질화 티탄막이 검토되고 있다. 한편, 배선 상층부를 덮는 피막(캡막)으로서 실리콘 질화막이 검토되고 있다. 이들 배선홈에 따른 질화 티탄막과 배선의 상부를 덮는 실리콘 질화막으로 구리를 덮어, 층간 절연막(실리콘 산화막)으로의 구리의 확산을 차단하여 배선의 신뢰성을 높이는 것이 검토되고 있다.

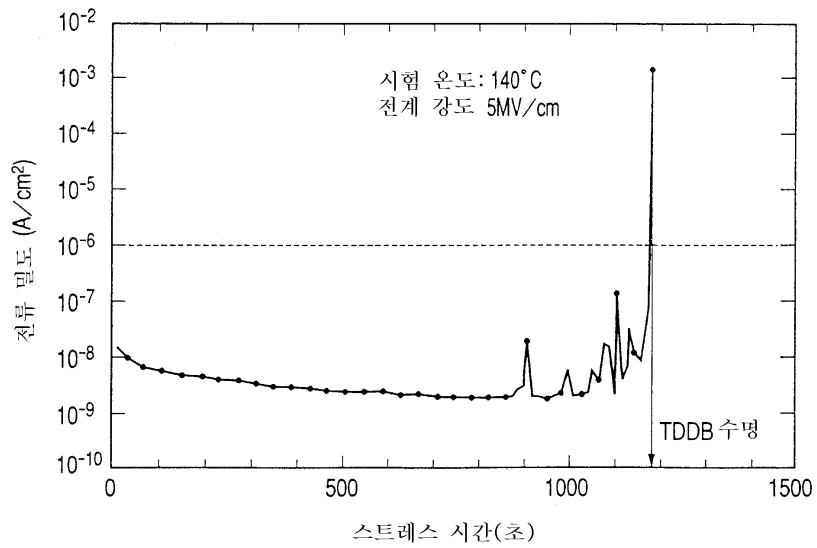

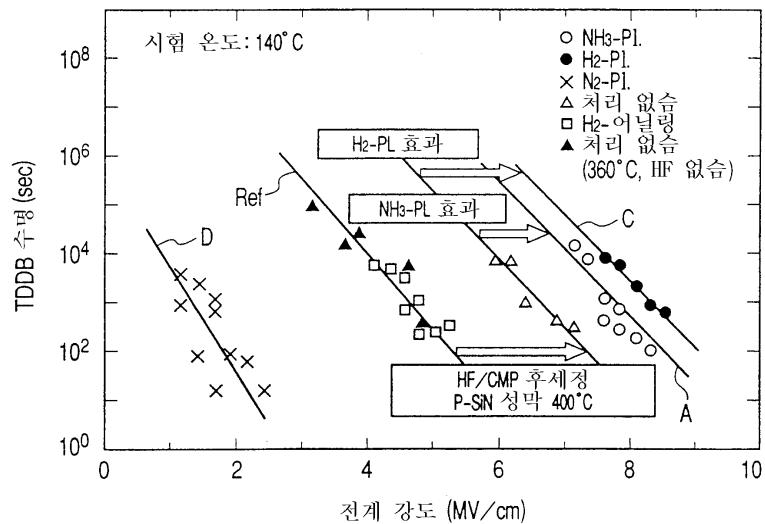

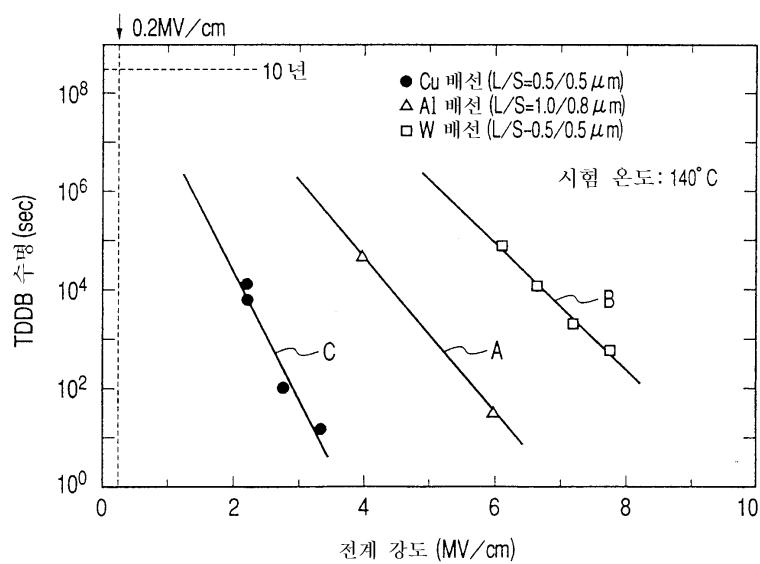

그런데, 구리를 배선 재료에 이용한 경우, TDDB(Time Dependence on Dielectric Breakdown) 수명이 다른 금속 재료(예를 들면 알루미늄, 텡스텐)에 비해 현저하게 짧다는 문제가 존재한다. 또, TDDB 시험이란 배선간의 절연 파괴 강도를 평가하는 가속 시험 방법의 일종으로, 통상 사용 환경보다 높은 소정의 온도로 고전계 하에서의 절연 파괴 시간으로부터 통상 사용 상태에서의 절연 파괴 시간(수명)을 추정하는 시험 방법이다. TDDB 수명은 이 TDDB 시험으로부터 추정되는 수명이다. TDDB 수명에 대해서는 후에 상술한다.

도 55는 구리 배선, 알루미늄 배선, 텡스텐 배선의 TDDB 특성을 측정한 데이터를 나타내는 그래프이다. 종축에 TDDB 수명을, 횡축에는 전계 강도를 할당하고 있다. 알루미늄 배선의 특성(데이터 A) 및 텡스텐 배선의 특성(데이터 B)을 외삽하면, 전계 강도가  $0.2\text{MV}/\text{cm}$ (통상 사용 상태)에서의 TDDB 수명은 본 발명자 등의 개발 목표인  $3 \times 10^8\text{sec}$ (10년)을 거뜬히 넘는다. 한편, 구리 배선의 특성(데이터 C)을 외삽하면, 10년의 개발 목표에 대하여 거의 마진이 없는 상태인 것을 알 수 있다. 알루미늄 배선은 피막의 퇴적과 포토리소 그래프를 이용한 패터닝에 의해 형성하고 있지만, 텡스텐 배선은 구리 배선과 마찬가지로 다마신법을 이용하여 형성하고 있다. 즉, 구리 배선과 텡스텐 배선의 차이는 재료에만 있으며 구조 상의 차이는 없다. 그럼에도 불구하고 TDDB 특성이 현저한 차이가 있는 것은 배선 재료의 차이에 기인함이 시사된다. 또한, 여기서의 TDDB 특성은  $140^\circ\text{C}$ 의 온도하에서 행한 데이터를 나타내고 있다.

이러한 TDDB 수명의 열화 원인은 배선 재료에 적용된 구리가 주변으로 확산하여, 이것이 배선 간의 절연 내압을 저하시키는 것으로 일반적으로는 생각되지만, 본 발명자 등의 검토에 따르면 그 구리는 원자형의 구리보다는 산화 구리 혹은 구리 실리사이드로부터 공급되는 이온화 구리가 배선간의 전위로 드리프트(drift)하여 확산하는 요인이 지배적이라 생각된다. 또한, 구리의 확산 경로는 구리 배선이 형성된 절연막과 캡막과의 계면(interface)이 지배적이라고 생각된다. 즉, 구리 배선의 표면에 산화 구리 혹은 구리 실리사이드가 형성되며, 이들 구리의 화합물로부터 구리 이온이 형성되고, 이온화된 구리가 배선 형성용 절연막과 캡막과의 계면에 따라서 배선간 전계에 의해 드리프트하여 확산하고, 이 확산한 구리 원자가 누설 전류를 증가시키는 원인이 된다고 생각된다. 그리고 누설 전류의 증가는 열 스트레스를 증가시키고, 최종적으로 누설 패스로 절연 파괴가 생기고 TDDB 수명에 이른다고 생각된다. 또, 이 점의 메카니즘은 뒤에 상술한다.

또한, 본 발명자 등의 검토에서는 배선층을 다층으로 형성한 경우, 상층 배선의 형성 공정인 CMP 공정에 있어서, 하층 배선과 그 상층에 형성된 절연막(캡막) 간에 박리(peeling)가 생기는 문제도 있다.

또한, 구리 배선 상의 캡막으로서 실리콘 질화막을 이용하면, 구리와 실리콘 질화막과의 계면에 실리사이드물이 형성되고 구리 배선의 저항이 증가한다고 하는 문제도 있다.

본 발명의 목적은 다마신법을 이용하여 형성된 구리 배선의 절연 파괴 내성(신뢰성)을 향상하는데 있다.

또한, 본 발명의 목적은 배선층과 캡막과의 박리의 발생을 억제하는데 있다.

또한, 본 발명의 목적은 캡막에 실리콘 질화막을 이용한 경우의 구리 배선의 저항치의 증가를 방지하는데 있다.

본 발명의 상기 및 그 외의 목적과 신규인 특징은 본 명세서의 기술 및 첨부도면에서 밝혀질 것이다.

본원에 있어서 개시되는 발명 중, 대표적인 개요를 간단하게 설명하면 다음과 같다.

즉, 본 발명은 CMP 공정 후, 배선 상에 캡막(예를 들면, 실리콘 질화막)을 형성하기 전에 배선 및 그것이 매립된 층간 절연막(예를 들면, 실리콘 산화막)의 표면을 환원성 플라즈마로 처리하는 것이다.

이에 따라, 배선 및 층간 절연막과 캡 절연막 간의 계면을 연속적으로 형성할 수 있어 계면에서의 밀착성을 개선하여 TDDB 수명을 현저하게 향상할 수 있다.

이하, 본 발명의 개요를 열거하여 설명한다.

본 발명의 제조 방법은 반도체 기판의 상층에 제1 절연막(예를 들면, 실리콘 산화막)을 형성하고, 제1 절연막에 홈(배선홈)을 형성한다. 그 후 제1 도전막(구리의 확산을 방지하는 블로킹막 예를 들면 질화 티탄막), 홈을 매립하는 제2 도전막(구리

막)을 순차 형성하고, 제2 도전막 및 제1 도전막을 연마하여 홈 내에 배선을 형성한다. 그 후, 제1 절연막 및 배선의 표면을 환원성 분위기의 플라즈마에 의해 처리한다. 또한, 제1 절연막 및 배선 상에 제2 절연막(캡 절연막, 예를 들면 실리콘 질화막)을 퇴적한다.

여기서, 환원성 분위기의 플라즈마는 암모니아( $\text{NH}_3$ ) 플라즈마 혹은 수소( $\text{H}_2$ ) 플라즈마로 할 수 있다. 또한, 암모니아( $\text{NH}_3$ )와 희석 가스[수소( $\text{H}_2$ ), 질소( $\text{N}_2$ ), 아르곤(Ar), 헬륨(He)으로부터 선택된 단일 또는 복수의 가스]와의 혼합 가스 플라즈마 혹은 수소( $\text{H}_2$ )와 희석 가스[암모니아( $\text{NH}_3$ ), 질소( $\text{N}_2$ ), 아르곤(Ar), 헬륨(He)으로부터 선택된 단일 또는 복수의 가스]와의 혼합 가스 플라즈마로 할 수 있다. 또, 혼합 가스에 대한 암모니아 혹은 수소의 농도는 5% 이상이다.

또한, 제1 절연막은 실리콘 산화막으로 하고, 제2 도전막은 구리, 제2 절연막은 실리콘 질화막으로 할 수 있다. 또, 말할 필요도 없는 것이지만, 구리는 배선으로서의 특성을 손상시키지 않는 범위에서 합금 요소나 첨가물, 불순물을 포함하는 것을 허용한다. 실시 형태에서 이용하는 고순도의 구리는 일반적으로 4N 즉 99.99% 이상이 이용된다.

또한, 연마 공정 후 플라즈마 처리 전에 제1 절연막 및 배선의 표면을 산 세정(acid washing)할 수 있다. 산 세정에는 불화수소(HF) 또는 구연산[ $\text{C}(\text{CH}_2\text{COOH})_2(\text{OH})(\text{COOH})$ ]의 수용액을 이용할 수 있다.

또한, 연마 공정에는 지립 프리(abrasive-grain-free)의 화학 기계 연마법을 이용할 수 있다. 연마는 지립 프리 화학 기계 연마를 행하는 제1 연마, 유지립(abrasive-grain) 화학 기계 연마를 행하는 제2 연마 및 제2 도전막에 대하여 제1 도전막의 선택비가 5 이상인 화학 기계 연마를 행하는 제3 연마의 3 단계의 화학 기계 연마로 행할 수 있다.

본 발명의 제조 방법은 반도체 기판의 상층에 제1 절연막을 형성하고, 제1 절연막에 홈을 형성하고, 제1 도전막, 홈을 매립하는 제2 도전막을 형성하고, 제2 도전막 및 제1 도전막을 연마하여 홈 내에 배선을 형성하고, 제1 절연막 및 배선의 표면에 플라즈마를 이용하여 환원 처리 및 질화 처리를 하고, 제1 절연막 및 배선 상에 제2 절연막을 퇴적하는 것이다.

이 경우의 플라즈마는 암모니아( $\text{NH}_3$ ) 또는 암모니아 및 수소( $\text{H}_2$ )와, 질소( $\text{N}_2$ ), 아르곤(Ar), 헬륨(He)으로부터 선택된 단일 또는 복수의 가스와의 혼합 가스의 플라즈마이다.

또한, 본 발명의 제조 방법은 보호막(패시베이션막)에 포함되는 실리콘 산화막보다도 유전률이 낮은 제1 절연막을 형성하고, 제1 절연막에 홈 또는 구멍을 형성하고, 제1 절연막의 노출면을 환원성 분위기의 플라즈마에 의해 처리하고, 홈 또는 구멍의 내벽을 포함하는 표면을 덮는 제1 도전막을 퇴적하고, 홈 또는 구멍을 매립하는 제2 도전막을 형성하고, 홈 또는 구멍 이외의 제2 도전막 및 제1 도전막을 연마에 의해 제거하여, 홈 또는 구멍 내에 도전 부재를 형성하는 것이다. 이 경우의 환원성 분위기의 플라즈마도 상기와 마찬가지이다. 또, 제1 절연막 상에 제2 절연막을 형성해도 된다.

본 발명의 반도체 집적 회로 장치는 제1 절연막과, 제1 절연막의 홈 내에 매립하여 형성된 배선과, 제1 절연막 및 배선 상에 형성된 제2 절연막을 포함하고, 제1 절연막 및 배선과 제2 절연막과의 계면에는 질화막이 형성되어 있다. 이 경우, 제1 절연막은 실리콘 산화막으로써, 배선은 구리이고, 제2 절연막은 실리콘 질화막이다. 또한, 질화막은 그 막속의 질소 농도가 제1 절연막 및 배선층에서부터 제2 절연막층으로 진행함에 따라서 높아지는 것이다.

또한, 본 발명의 제조 방법은 반도체 기판의 상층에 제1 절연막을 형성하고, 제1 절연막에 홈을 형성하고, 제1 절연막 상에 제1 도전막을 퇴적하는 단계와, 홈을 매립하는 제2 도전막을 형성하고, 제2 도전막 및 제1 도전막을 연마하여 홈 내에 배선을 형성하고, 제1 절연막 및 배선의 표면을 환원성 분위기의 플라즈마에 의해 처리하고, 또한 반도체 기판을 대기 분위기에 노출하지 않고 감압 또는 불활성 상태를 유지하고 연속적으로 제1 절연막 및 배선 상에 제2 절연막을 퇴적하는 것이다.

또한, 본원의 그 외의 발명의 개요를 번호로 나누어서 간단하게 설명한다. 즉,

1. 반도체 집적 회로의 제조 방법에 있어서,

(a) 반도체 기판의 상층에 제1 절연막을 형성하고, 상기 제1 절연막에 홈을 형성하는 단계와,

(b) 상기 제1 절연막 상에 제1 도전막을 퇴적하고, 상기 홈을 매립하는 제2 도전막을 형성하는 단계와,

- (c) 상기 홈 이외의 상기 제1 절연막 상의 상기 제2 도전막 및 제1 도전막을 연마에 의해 제거하여, 상기 홈 내에 배선을 형성하는 단계와,

- (d) 상기 제1 절연막 및 배선의 표면을 환원성 분위기의 플라즈마에 의해 처리하는 단계와,

- (e) 상기 플라즈마 처리 단계의 종료 후, 상기 제1 절연막 및 배선 상에 제2 절연막을 퇴적하는 단계를 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

2. 제1에 있어서, 상기 환원성 분위기의 플라즈마는 암모니아( $\text{NH}_3$ ) 플라즈마 또는 수소( $\text{H}_2$ ) 플라즈마인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

3. 제1에 있어서, 상기 환원성 분위기의 플라즈마는 암모니아( $\text{NH}_3$ )와 희석 가스와의 혼합 가스 플라즈마이고,

상기 희석 가스는 수소( $\text{H}_2$ ), 질소( $\text{N}_2$ ), 아르곤(Ar), 헬륨(He)으로부터 선택된 단일 또는 복수의 가스인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

4. 제3에 있어서, 상기 혼합 가스에 대한 암모니아( $\text{NH}_3$ )의 농도는 5% 이상인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

5. 제1에 있어서, 상기 환원성 분위기의 플라즈마는 수소( $\text{H}_2$ )와 희석 가스와의 혼합 가스 플라즈마이고,

상기 희석 가스는 암모니아( $\text{NH}_3$ ), 질소( $\text{N}_2$ ), 아르곤(Ar), 헬륨(He)으로부터 선택된 단일 또는 복수의 가스인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

6. 제5에 있어서, 상기 혼합 가스에 대한 수소( $\text{H}_2$ )의 농도는 5% 이상인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

7. 제1에 있어서, 상기 제1 절연막은 실리콘 산화막이고,

상기 제2 도전막은 구리로 이루어지는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

8. 제7에 있어서, 상기 제2 절연막은 실리콘 질화막인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

9. 제8에 있어서, 상기 환원성 분위기의 플라즈마는 암모니아( $\text{NH}_3$ ), 수소( $\text{H}_2$ ) 또는 이들의 가스와 질소( $\text{N}_2$ ), 아르곤(Ar), 헬륨(He)으로부터 선택된 단일 또는 복수의 가스와의 혼합 가스의 플라즈마인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

10. 제9에 있어서, 상기 구리는 99.99% 이상의 고순도인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

11. 제1에 있어서, 상기 (c) 단계와 (d) 단계 사이에 상기 제1 절연막 및 배선의 표면을 산 세정하는 단계를 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

12. 제11에 있어서 상기 산 세정에는 불화 수소(HF) 또는 구연산[ $\text{C}(\text{CH}_2\text{COOH})_2(\text{OH})(\text{COOH})$ ]의 수용액을 이용하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

13. 제12에 있어서, 상기 제1 절연막은 실리콘 산화막이며, 상기 제2 도전막은 구리로 이루어지고, 상기 제2 절연막은 실리콘 질화막인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

14. 제13에 있어서, 상기 환원성 분위기의 플라즈마는 암모니아( $\text{NH}_3$ ), 수소( $\text{H}_2$ ) 또는 이들의 가스와 질소( $\text{N}_2$ ), 아르곤(Ar), 헬륨(He)으로부터 선택된 단일 또는 복수의 가스와의 혼합 가스의 플라즈마인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

15. 제14에 있어서, 상기 구리는 99.99% 이상의 고순도인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

16. 제1에 있어서, 상기 (c) 단계에서의 연마에는 지립 프리의 화학 기계 연마법을 이용하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

17. 제16에 있어서, 상기 (c) 단계에서의 연마는 지립 프리 화학 기계 연마를 행하는 제1 연마, 유지립 화학 기계 연마를 행하는 제2 연마, 및 상기 제2 도전막에 대하여 상기 제1 도전막의 선택비가 5 이상인 화학 기계 연마를 행하는 제3 연마의 3 단계의 화학 기계 연마로 행해지는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

18. 제17에 있어서, 상기 제1 절연막은 실리콘 산화막이며, 상기 제2 도전막은 구리로 이루어지고, 상기 제2 절연막은 실리콘 질화마인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

19. 제18에 있어서, 상기 환원성 분위기의 플라즈마는 암모니아( $\text{NH}_3$ ), 수소( $\text{H}_2$ ) 또는 이들의 가스와 질소 ( $\text{N}_2$ ), 아르곤(Ar), 헬륨(He)으로부터 선택된 단일 또는 복수의 가스와의 혼합 가스의 플라즈마인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

20. 제19에 있어서, 상기 (c) 단계와 (d) 단계 사이에 상기 제1 절연막 및 배선의 표면을 불화 수소(HF) 또는 구연산[ $\text{C}(\text{CH}_2\text{COOH})_2(\text{OH})(\text{COOH})$ ]의 수용액을 이용하여 산 세정하는 단계를 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

21. 제20에 있어서, 상기 구리는 99.99% 이상의 고순도인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

22. 반도체 집적 회로 장치의 제조 방법에 있어서,

(a) 반도체 기판의 상층에 제1 절연막을 형성하고, 상기 제1 절연막에 홈을 형성하는 단계와,

(b) 상기 제1 절연막 상에 제1 도전막을 퇴적하고, 상기 홈을 매립하는 제2 도전막을 형성하는 단계와,

(c) 상기 홈 이외의 상기 제1 절연막 상의 상기 제2 도전막 및 제1 도전막을 연마에 의해 제거하여 상기 홈 내에 배선을 형성하는 단계와,

(d) 상기 제1 절연막 및 배선의 표면에 플라즈마를 이용하여 환원 처리 및 질화 처리를 실시하는 단계와,

(e) 상기 제1 절연막 및 배선 상에 제2 절연막을 퇴적하는 단계

를 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

23. 제22에 있어서, 상기 플라즈마는 암모니아( $\text{NH}_3$ ) 또는 암모니아와 희석 가스와의 혼합 가스의 플라즈마이고, 상기 희석 가스는 수소( $\text{H}_2$ ), 질소( $\text{N}_2$ ), 아르곤(Ar), 헬륨(He)으로부터 선택된 단일 또는 복수의 가스인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

24. 반도체 기판의 상층에 형성된 제1 절연막과, 상기 제1 절연막보다 더 상층에 형성된 불순물의 침입을 방지하는 보호막을 포함하는 반도체 집적 회로 장치의 제조 방법으로서,

(a) 상기 보호막에 포함되는 실리콘 산화막의 유전률보다 낮은 유전률을 포함하는 제1 절연막을 형성하는 단계와,

(b) 상기 제1 절연막에 홈 또는 구멍을 형성하는 단계와,

- (c) 상기 제1 절연막의 노출면을 환원성 분위기의 플라즈마에 의해 처리하는 단계와,

- (d) 상기 홈 또는 구멍의 내벽을 포함하는 표면을 덮는 제1 도전막을 퇴적하고 상기 홈 또는 구멍을 매립하는 제2 도전막을 형성하는 단계와,

- (e) 상기 홈 또는 구멍 이외의 상기 제2 도전막 및 제1 도전막을 연마에 의해 제거하여 상기 홈 또는 구멍 내에 도전 부재를 형성하는 단계

를 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

25. 제24에 있어서, 상기 환원성 분위기의 플라즈마는 암모니아( $\text{NH}_3$ ), 수소( $\text{H}_2$ ) 또는 이들의 가스와 질소( $\text{N}_2$ ), 아르곤(Ar), 헬륨(He)으로부터 선택된 단일 또는 복수의 가스와의 혼합 가스의 플라즈마인 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

26. 제25에 있어서, 상기 제1 절연막의 상면에 제2 절연막을 형성하는 단계와, 상기 (b) 단계에서 상기 제1 및 제2 절연막에 홈 또는 구멍을 형성하는 단계와, 상기 (c) 단계에서 상기 홈 또는 구멍의 내벽에 노출한 상기 제1 절연막의 노출면을 환원성 분위기의 플라즈마에 의해 처리하는 단계를 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

27. 반도체 기판의 상층에 형성된 제1 절연막과, 상기 제1 절연막의 홈 내에 매립하여 형성된 배선과, 상기 제1 절연막 및 배선 상에 형성된 제2 절연막을 포함하는 반도체 집적 회로 장치로서,

상기 제1 절연막 및 배선과 상기 제2 절연막과의 계면에는 질화막이 형성되어 있는 것을 특징으로 하는 반도체 집적 회로 장치.

28. 제27에 있어서, 상기 제1 절연막은 실리콘 산화막이고, 상기 배선은 구리이고 상기 제2 절연막은 실리콘 질화막인 것을 특징으로 하는 반도체 집적 회로 장치.

29. 제28에 있어서, 상기 질화막은 그 막 내의 질소 농도가 상기 제1 절연막 및 배선측에서부터 상기 제2 절연막측으로 진행함에 따라서 높아지는 것을 특징으로 하는 반도체 집적 회로 장치.

30. 제1에 있어서, 상기 (d) 단계의 종료 후, 상기 반도체 기판을 대기 분위기에 노출하지 않고 감압 또는 불활성 상태를 유지하는 단계와, 상기 제1 절연막 및 배선 상에 상기 (e) 단계의 상기 제2 절연막을 연속적으로 퇴적하는 단계를 포함하는 것을 특징으로 하는 반도체 집적 회로 장치의 제조 방법.

이하, 본원에 있어서, 사용하는 용어의 일반적 의미에 대하여 설명한다.

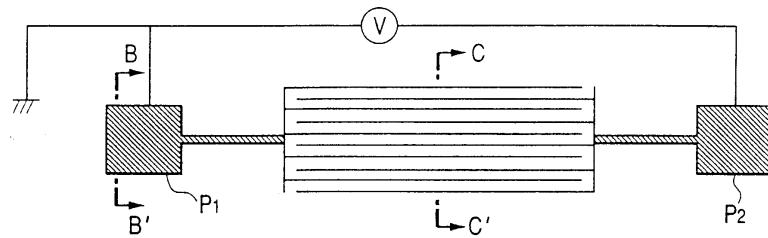

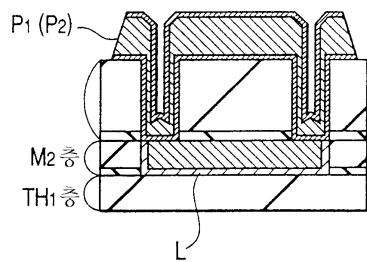

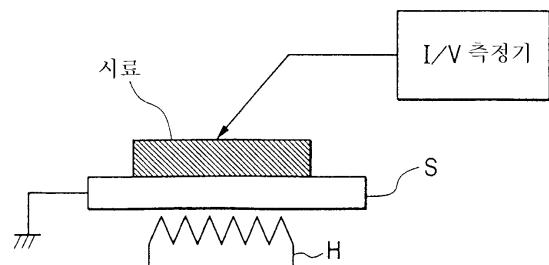

TDDB 수명이란, 소정의 온도(예를 들면  $140^{\circ}\text{C}$ )의 측정 조건 하에서 전극 간에 비교적 높은 전압을 가하고, 전압 인가로부터 절연 파괴까지의 시간을 인가 전계에 대하여 플롯(plot)한 그래프를 작성하고, 이 그래프로부터 실제의 사용 전계 강도(예를 들면  $0.2\text{MV}/\text{cm}$ )로 외삽하여 구한 시간(수명)을 말한다. 도 56a는 본원의 TDDB 수명 측정에 사용한 시료를 나타내는 평면도를, 도 56b 및 도 56c는 도 56a에서의 B-B'선 단면 및 C-C'선 단면을 각각 나타낸다. 이 시료는 실제로는 웨이퍼의 TEG(Test Equipment Group) 영역으로 형성할 수 있다. 도시한 바와 같이 한쌍의 빗형 배선 L을 제2 배선층 M2에 형성하고, 최상층의 패드 P1, P2에 각각 접속한다. 이 빗형 배선 L 간에 전계가 인가되어 전류가 측정된다. 패드 P1, P2는 측정 단자이다. 빗형 배선 L의 배선 폭, 배선 간격, 배선 두께는 모두  $0.5\mu\text{m}$ 이다. 또한 배선 대향 길이는  $1.58 \times 10^5\mu\text{m}$ 로 하였다. 도 57은 측정의 개요를 나타낸 개념도이다. 시료는 측정 스테이지 S로 유지되고, 패드 P1과 P2 간에 전류 전압 측정기(I/V 측정기)를 접속한다. 시료 스테이지 S는 히터 H로 가열되어 시료 온도가  $140^{\circ}\text{C}$ 로 조정된다. 도 58은 전류 전압 측정 결과의 일례이다. 시료 온도  $140^{\circ}\text{C}$ , 전계 강도  $5\text{MV}/\text{cm}$ 의 경우를 예시하였다. TDDB 수명 측정에는 정전압 스트레스법과 저전류 스트레스법이 있지만, 본 원에서는 절연막에 인가되는 평균 전계가 일정해지는 정전압 스트레스법을 이용하고 있다. 전압 인가 후, 시간의 경과와 함께 전류 밀도는 감소하고, 그 후 급격한 전류 증가(절연 파괴)가 관측된다. 여기서는 누설 전류 밀도가  $1\mu\text{A}/\text{cm}^2$ 에 달한 시간을 TDDB 수명( $5\text{MV}/\text{cm}$ 에서의 TDDB 수명)으로 하였다. 또, 본 원에서 TDDB 수명이란, 특히 언급하지 않는 한  $0.2\text{MV}/\text{cm}$ 에서의 파괴 시간(수명)을 말하지만, 광의로는 소정의 전계 강도로 언급한 후에 파괴

까지의 시간으로서 TDDB 수명이라는 단어를 이용하는 경우도 있다. 또한, 특히 언급하지 않는 한 TDDB 수명은 시료 온도 140°C의 경우를 말한다. 또, TDDB 수명은 상기한 빗형 배선(comb-like interconnection) L로 측정한 경우를 말하지만 실제 배선간의 파괴 수명을 반영하는 것은 물론이다.

플라즈마 처리란, 플라즈마 상태에 있는 환경에 기판 표면 혹은 기판 상에 절연막, 금속막 등의 부재가 형성되어 있을 때는 그 부재 표면을 노출하고, 플라즈마의 화학적, 기계적(충격) 작용을 표면에 제공하여 처리하는 것을 말한다. 일반적으로 플라즈마는 특정한 가스(처리 가스)로 치환한 반응실 내에 필요에 따라서 처리 가스를 보충하면서 고주파 전계 등의 작용에 의해 가스를 전리시켜서 생성하지만, 현실적으로는 완전히 처리 가스로 치환할 수 없다. 따라서, 본원에서는 예를 들면 암모니아 플라즈마라고 칭해도 완전한 암모니아 플라즈마를 의도하는 것은 아니고, 그 플라즈마 내에 포함되는 불순물 가스(질소, 산소, 이산화탄소, 수증기 등)의 존재를 배제하는 것은 아니다. 마찬가지로, 말할 필요도 없지만 플라즈마 중에 다른 희석 가스나 첨가 가스를 포함하는 것을 배제하는 것은 아니다.

환원성(reducing) 분위기의 플라즈마란, 환원 작용 즉 산소를 인출하는 작용을 갖는 래디컬(radical), 이온, 원자, 분자 등의 반응종이 지배적으로 존재하는 플라즈마 환경을 말하며, 래디컬 및 이온에는 원자 또는 분자형의 래디컬 또는 이온이 포함된다. 또한, 환경 내에는 단일의 반응종뿐만 아니라, 복수종의 반응종이 포함되어 있어도 된다. 예를 들면, 수소 래디컬과 NH<sub>2</sub> 래디컬이 동시에 존재하는 환경이라도 좋다.

본원에서 예를 들면, 구리로 이루어진다고 표현된 경우, 주성분으로서 구리가 이용되어 있는 것이 의도된다. 즉, 일반적으로 고순도인 구리라고 해도 불순물이 포함되는 것은 당연하며, 첨가물이나 불순물도 구리로 이루어지는 부재에 포함되는 것을 배제하지는 않는다. 본원에 있어서 고순도의 구리로 이루어진다고 표현한 경우에는, 일반적인 고순도 재료[예를 들면 4N(99.99%)] 정도의 구리로 구성되는 것을 의도하고 0.01% 정도의 임의의 불순물이 포함되는 것을 전제로 한다. 이것은 구리에 한하지 않고 그 외의 금속(질화 티탄 등)이라도 마찬가지이다.

본 원에서 가스의 농도와 같은 경우에는 질량 유량에 있어서의 유량비를 말하는 것으로 한다. 즉, 가스 A와 가스 B와의 혼합 가스에 있어서, 가스 A의 농도가 5%일 때는 가스 A의 질량 유량을 Fa로, 가스 B의 질량 유량을 Fb로 해서, Fa/(Fa+Fb)=0.05인 것을 말한다.

연마액(슬러리(slurry))이란, 일반적으로 화학 에칭약제에 연마 지립을 혼합한 혼탁액을 말하고, 본 원에서는 발명의 성질상, 연마 지립이 혼합되어 있지 않은 것을 포함하는 것으로 한다.

지립(슬러리 입자)이란, 일반적으로 슬러리에 포함되는 알루미나, 실리카 등의 분말을 말한다.

화학 기계 연마(CMP)란, 일반적으로 피연마면을 상대적으로 부드러운 천모양의 시트 재료 등으로 이루어지는 연마 패드에 접촉시킨 상태에서 슬러리를 공급하면서 면방향으로 상대 이동시켜서 연마를 행하는 것을 말하고, 본원에서는 기타, 피연마면을 경질의 지석면에 대하여 상대 이동시킴으로써 연마를 행하는 CML(Chemical Mechanical Lapping) 등도 포함하는 것으로 한다.

지립 프리(abrasive-grain-free) 화학 기계 연마란, 일반적으로 지립의 중량 농도가 0.5% 미만인 슬러리를 이용한 화학 기계 연마를 말하고, 유지립(abrasive-grain) 화학 기계 연마란 지립의 중량 농도가 0.5% 이상의 슬러리를 이용한 화학 기계 연마를 말한다. 그러나, 이들은 상대적인 것으로, 제1 단계의 연마가 지립 프리 화학 기계 연마로, 그에 계속되는 제2 단계의 연마가 유지립 화학 기계 연마인 경우, 제1 단계의 연마 농도가 제2 단계의 연마 농도보다도 1자리수 이상, 바람직하게는 2자리수 이상 작은 경우 등에는, 이 제1 단계의 연마를 지립 프리 화학 기계 연마라는 경우도 있다.

방식제(anticorrosive)란, 금속의 표면에 내식성 및/또는 소수성(hydrophobic)의 보호막을 형성함으로써, CMP에 의한 연마의 진행을 저지 또는 억제하는 약제를 말하고, 일반적으로 벤조트리아졸(BTA) 등이 사용된다(자세하게는 특개평8-64594호 공보 참조).

도전성 배리어층이란, 일반적으로 매립 배선 재료를 구성하는 원자나 이온이 수송(확산 등을 포함한다)되어 하층의 소자 등에 악영향을 미치게 하는 것을 막기 위한 것으로, 전기 전도성이 절연막에 비해 비교적 높은 Ti 등의 금속, TiN 등의 금속 질화물, 도전성 산화물, 도전성 질화물 그 외의 확산 저지성을 갖는 도전 재료로 이루어지는 층을 말한다.

선택적 제거, 선택적 연마, 선택적 에칭, 선택적 화학 기계 연마일 때는 모두 선택비가 5 이상인 것을 말한다.

매립 배선이란 일반적으로 성글 다마신(single damascene)이나 듀얼 다마신(dual damascene) 등과 같이, 절연막에 형성된 홈 등의 내부에 도전막을 매립한 후, 절연막 상 불필요한 도전막을 제거하는 배선 형성 기술에 의해서 형성된 배선을 말한다.

선택비에 대하여, 「A의 B에 대한」(또는 「B에 대한 A의」) 선택비가 X라고 할 때, 연마율을 예로 든 경우 B에 대한 연마율을 기준으로 하여 A에 대한 연마율을 계산했을 때 X가 되는 것을 말한다.

이하의 실시 형태에서는 특히 필요할 때 이외에는 동일하거나 또는 유사한 부분의 설명은 원칙적으로 반복하지 않는다.

또한, 이하의 실시 형태에서는 편의상 그 필요가 있을 때는 복수의 섹션 또는 실시 형태로 분할하여 설명하지만, 특히 명시한 경우를 제외하고, 그들은 서로 관계없는 것은 아니고, 한쪽은 다른쪽의 일부 또는 전부의 변형예, 상세, 보충 설명 등의 관계에 있다.

또한, 이하의 실시 형태에서 요소의 수 등(갯수, 수치, 양, 범위 등을 포함함)을 언급하는 경우, 특히 명시했을 때와 원리적으로 분명하게 특정한 수에 한정될 때를 제외하고는 그 특정한 수에 한정되지는 않으며, 특정한 수 이상이나 이하도 좋다. 또한, 이하의 실시 형태에서, 그 구성 요소(요소 단계 등을 포함한다)는 특히 명시한 경우와 원리적으로 분명히 필수적이라 생각되는 경우를 제외하고는 반드시 필수적인 것이 아닌 것은 물론이다.

마찬가지로, 이하의 실시 형태에서 구성 요소 등의 형상, 위치 관계 등에 언급할 때는 특히 명시한 경우와 원리적으로 분명히 그렇지 않다고 생각되는 경우를 제외하고, 실질적으로 그 형상 등에 근사 또는 유사한 것 등을 포함하는 것으로 한다. 이것은 상기 수치 및 범위에 대해서도 마찬가지이다.

또한, 본원에서 반도체 집적 회로 장치라고 할 때는 특히 단결정 실리콘 기판 상에 만들어지는 것뿐만 아니라, 특히 그렇지 않은 취지가 명시된 경우를 제외하고, SOI(Silicon On Insulator) 기판이나 TFT(Thin Film Transistor) 액정 제조용 기판 등과 같은 다른 기판 상에 만들어지는 것을 포함하는 것으로 한다. 또한, 웨이퍼란 반도체 집적 회로 장치의 제조에 이용하는 단결정 실리콘 기판(일반적으로 거의 원반형), SOS 기판, 유리 기판, 그 외의 절연, 반절연 또는 반도체 기판 등이나 이를 복합한 기판을 말한다.

## 발명의 구성

이하, 본 발명의 실시 형태를 도면에 기초하여 상세하게 설명한다. 또, 실시 형태를 설명하기 위한 전 도면에서 동일한 부재에는 동일한 부호를 붙여서, 그 반복된 설명은 생략한다.

### <실시 형태 1>

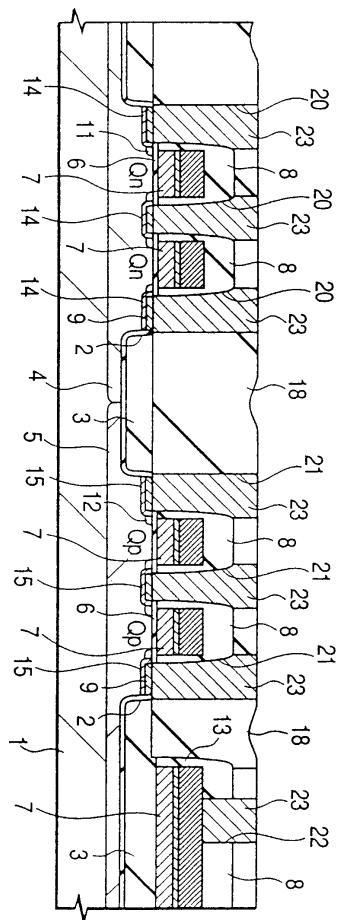

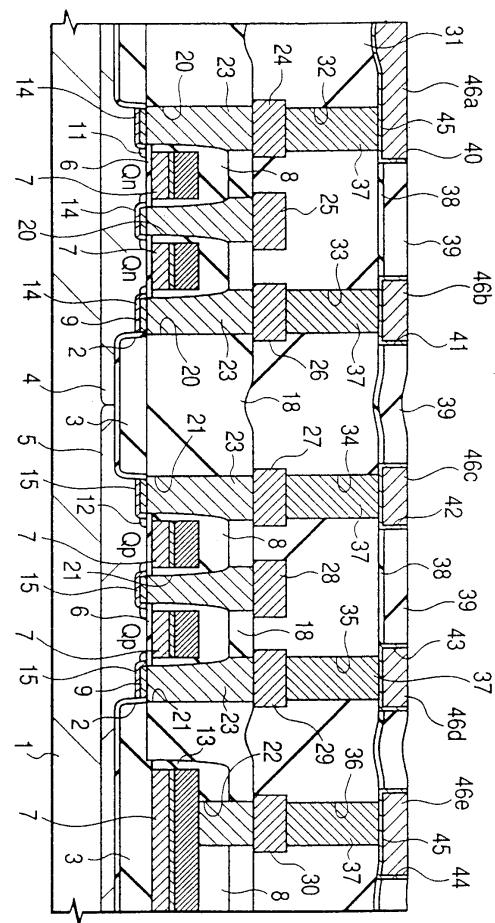

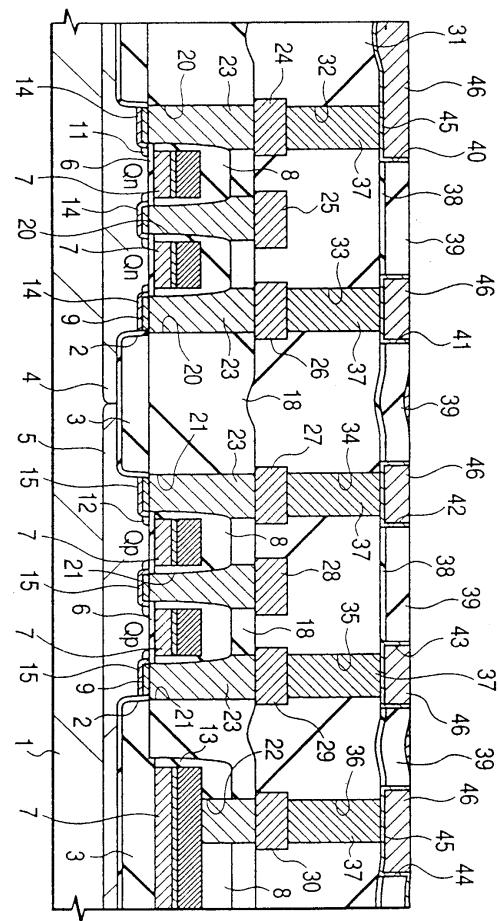

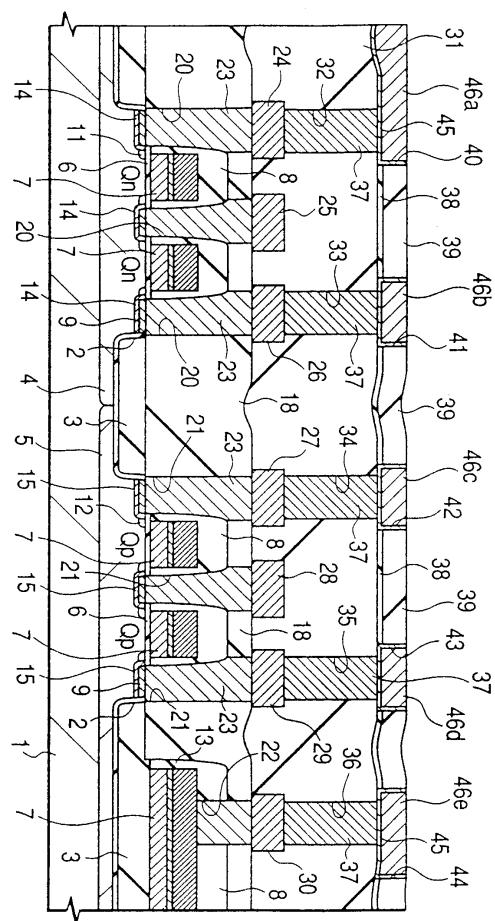

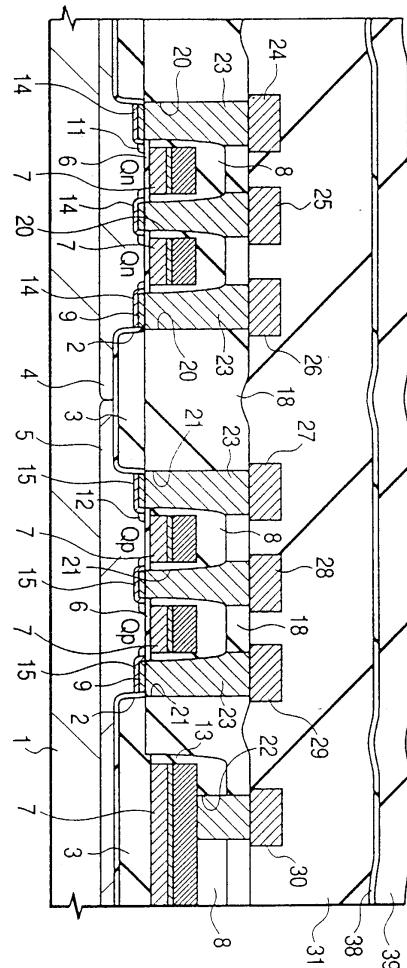

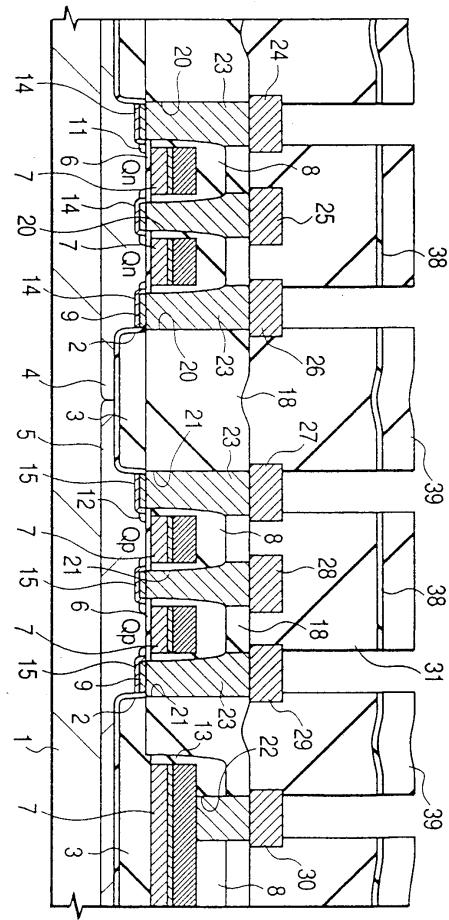

본 발명의 실시 형태 1인 CMOS-LSI의 제조 방법을 도 1 ~ 도 19를 이용하여 공정 순으로 설명한다.

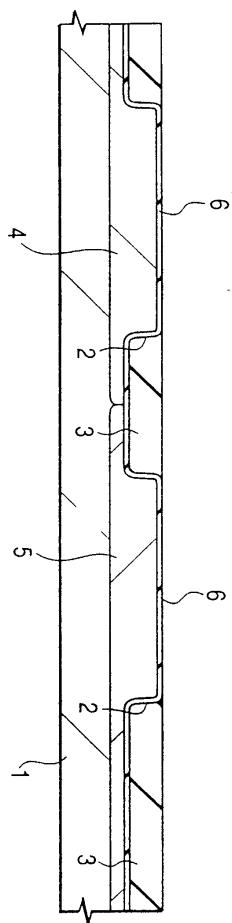

우선, 도 1에 도시한 바와 같이, 예를 들면  $1 \sim 10\Omega\text{cm}$  정도의 비저항을 갖는 p형의 단결정 실리콘으로 이루어지는 반도체 기판(이하, 기판이라 함; 1)에 깊이 350nm 정도의 소자 분리홈(2)을 포토리소그래피와 드라이 에칭을 이용하여 형성한 후, 홈의 내부를 포함하는 기판(1) 상에 CVD법으로 실리콘 산화막(3)을 퇴적한다. 계속해서 홈의 상부의 실리콘 산화막(3)을 화학 기계 연마(CMP)에 의해서 그 표면을 평탄화한다. 그 후, 기판(1)에 p형 불순물(붕소) 및 n형 불순물(예를 들면 인)을 이온 주입함으로써, p형 웨(4) 및 n형 웨(5)를 형성한 후, 기판(1)을 스텁 산화함으로써 p형 웨(4) 및 n형 웨(5)의 표면에 막두께 6nm 정도의 게이트 산화막(6)을 형성한다.

다음에, 도 2에 도시한 바와 같이, 게이트 산화막(6)의 상부에, 저저항 다결정 실리콘막, WN(질화 텅스텐)막 및 W(텅스텐)막으로 이루어지는 게이트 전극(7)을 형성한다. 다결정 실리콘막은 CVD법에 의해, WN막 및 W막은 스팍터법에 의해 형성할 수 있다. 게이트 전극(7)은 이들 퇴적막의 패터닝에 의해 형성한다. 게이트 전극(7)은 저저항 다결정 실리콘막과 W 실리사이드막과의 적층막 등을 사용하여 형성해도 된다. 그 후, 이온 주입함으로써, p형 웨(4)에 저불순물 농도의 n<sup>-</sup>형 반도체 영역(11)을, n형 웨(5)에 저불순물 농도의 p<sup>-</sup>형 반도체 영역(12)을 형성한다.

다음에, 도 3에 도시한 바와 같이, 예를 들면 실리콘 질화막을 CVD법으로 퇴적하고, 이것을 이방적으로 에칭함으로써 게이트 전극(7)의 측벽에 측벽 스페이서(13)를 형성한다. 이 후, 이온 주입함으로써, p형 웨(4)에 고불순물 농도의 n<sup>+</sup>형 반도

체 영역(14 ; 소스, 드레인)을 형성하고, n형 웨(5)에 고불순물 농도의 p<sup>+</sup>형 반도체 영역(15 ; 소스, 드레인)을 형성한다. 또, n형 불순물로는 인 또는 비소를, p형 불순물로는 봉소를 예시할 수 있다. 그 후, 티탄, 코발트 등의 금속막을 퇴적하고, 열처리 후에 미반응의 금속막을 제거하는 소위 실리사이드법을 이용하여, n<sup>+</sup>형 반도체 영역(14 ; 소스, 드레인)의 표면 및 p<sup>+</sup>형 반도체 영역(15 ; 소스, 드레인)의 표면에 실리사이드층(9)을 형성한다. 여기까지의 공정에서 n 채널형 MISFETQn 및 p 채널형 MISFETQp가 완성된다.

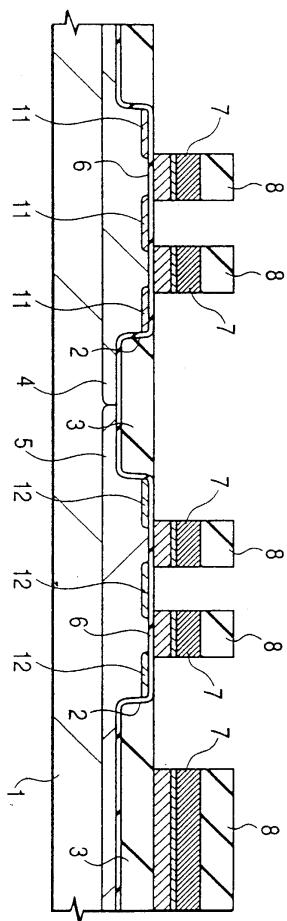

다음에, 도 4에 도시한 바와 같이, 기판(1) 상에 CVD법으로 실리콘 산화막(18)을 퇴적하고, 계속해서 포토레지스트막을 마스크로 하여 실리콘 산화막(18)을 드라이 에칭함으로써, n<sup>+</sup>형 반도체 영역(14 ; 소스, 드레인)의 상부에 컨택트 홀(20)을 형성하고, p<sup>+</sup>형 반도체 영역(15 ; 소스, 드레인)의 상부에 컨택트홀(21)을 형성한다. 또한 이 때, 게이트 전극(7)의 상부에도 컨택트홀(22)을 형성한다.

실리콘 산화막(18)은 게이트 전극(7, 7)이 좁은 스페이스를 매립할 수 있는 리플로우성이 높은 막, 예를 들면 BPSG (Boron-doped Phospho Silicate Glass)막으로 구성한다. 또한, 스픬 도포법에 의해서 형성되는 SOG(Spin On Glass)막으로 구성해도 된다.

다음에, 컨택트홀(20, 21, 22) 내부에 플러그(23)를 형성한다. 플러그(23)를 형성하기 위해서는, 예를 들면 컨택트홀(20, 21, 22)의 내부를 포함하는 실리콘 산화막(18)의 상부에 CVD법으로 TiN막 및 W막을 퇴적한 후, 실리콘 산화막(18)의 상부의 불필요한 TiN막 및 W막을 화학 기계 연마(CMP)법 또는 에치백법에 의해서 제거하고, 컨택트홀(20, 21, 22)의 내부에만 이들의 막을 남긴다.

다음에, 도 5에 도시한 바와 같이, 실리콘 산화막(18)의 상부에 제1층째의 배선이 되는 W 배선(24 ~ 30)을 형성한다. W 배선(24 ~ 30)을 형성하기 위해서는 예를 들면 실리콘 산화막(18)의 상부에 스퍼터링법으로 W막을 퇴적한 후, 포토레지스트막을 마스크로 하여 이 W막을 드라이 에칭한다. 제1층째의 W 배선(24 ~ 30)은, 컨택트 홀(20, 21, 22)을 통하여 n 채널형 MISFETQn의 소스, 드레인(n<sup>+</sup>형 반도체 영역), p 채널형 MISFETQp의 소스, 드레인(p<sup>+</sup>형 반도체 영역) 혹은 게이트 전극(7)과 전기적으로 접속된다.

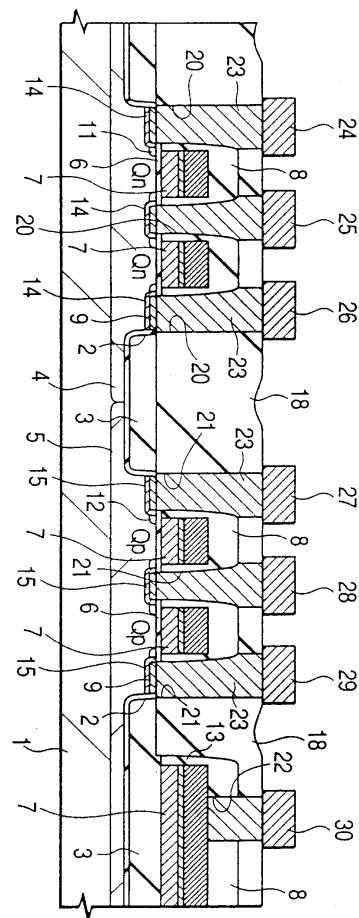

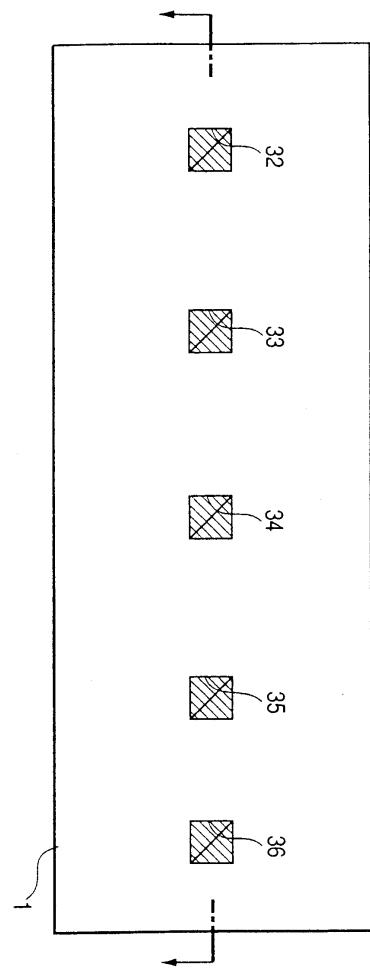

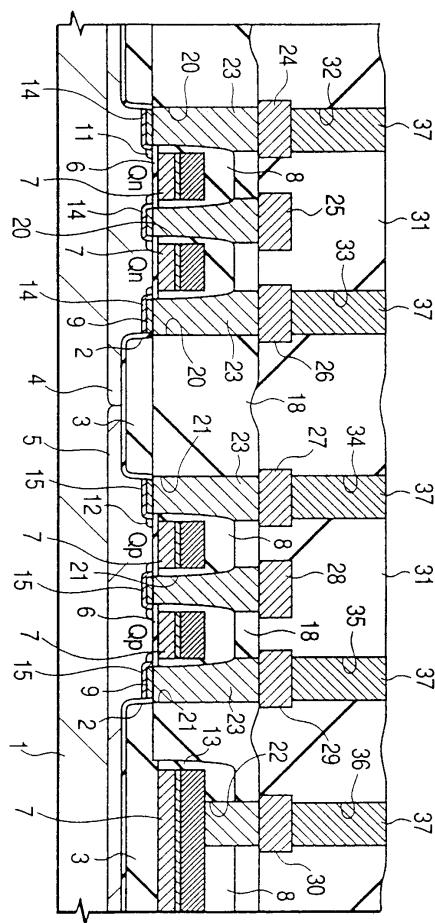

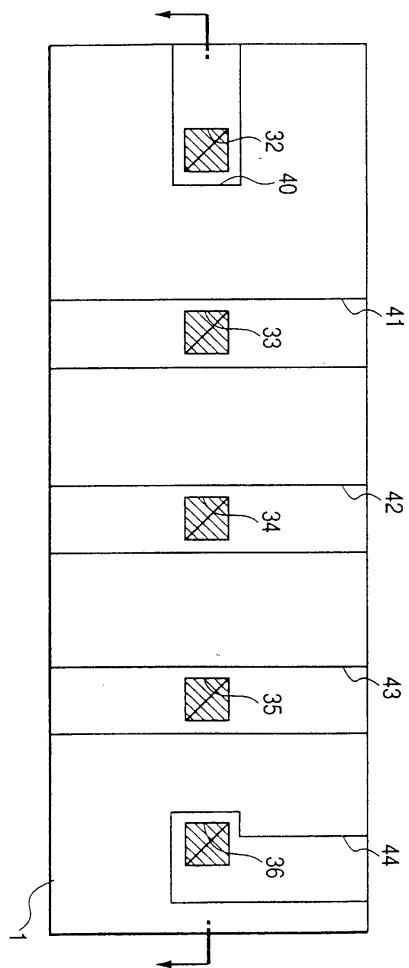

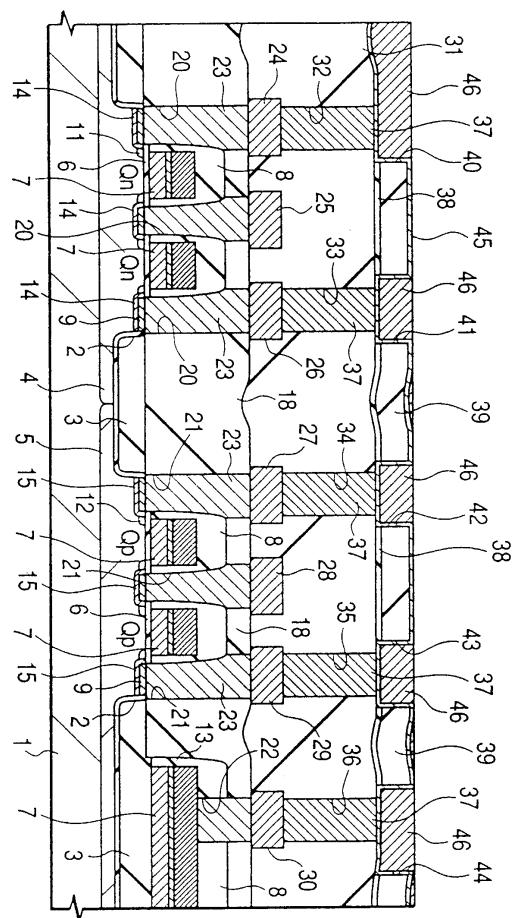

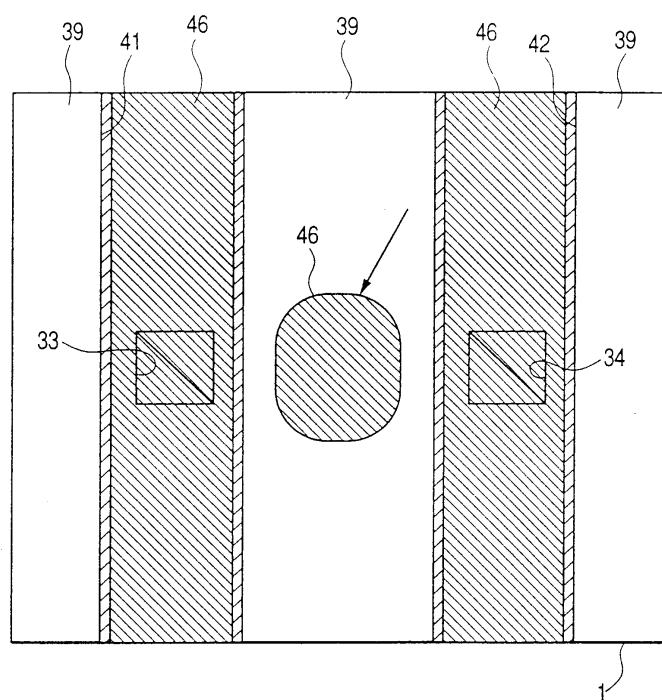

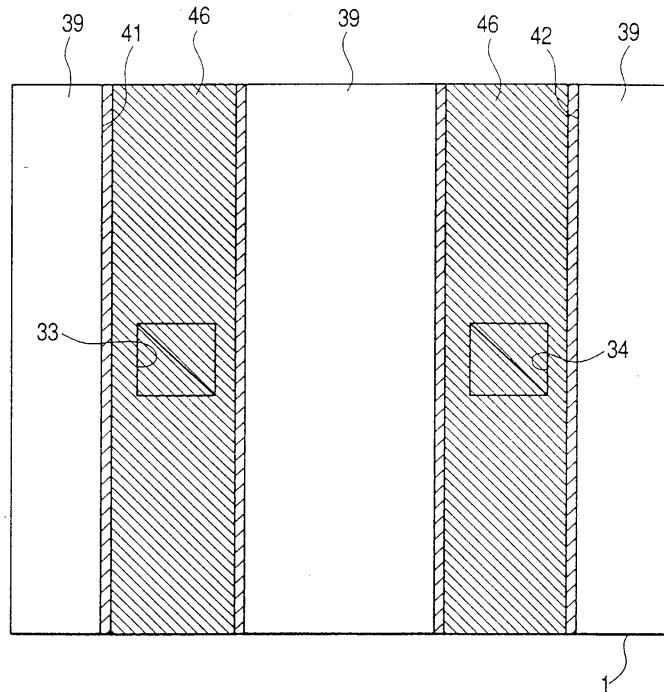

다음에, 도 6a, 도 6b에 도시한 바와 같이, 제1층째의 W 배선(24 ~ 30)의 상부에 실리콘 산화막(31)을 퇴적하고, 계속해서 포토 레지스트막을 마스크로 한 드라이 에칭으로 실리콘 산화막(31)에 관통 구멍(32 ~ 36)을 형성한 후, 관통 구멍(32 ~ 36)의 내부에 플러그(37)를 형성한다.

실리콘 산화막(31)은 예를 들면 오존(또는 산소)과 테트라 에톡시 실란(TEOS)을 소스 가스에 이용한 플라즈마 CVD법으로 퇴적한다. 또한, 플러그(37)는 예를 들면 W막으로 구성하고, 상기 컨택트홀(20, 21, 22)의 내부에 플러그(23)를 형성한 방법과 동일 방법으로 형성한다.

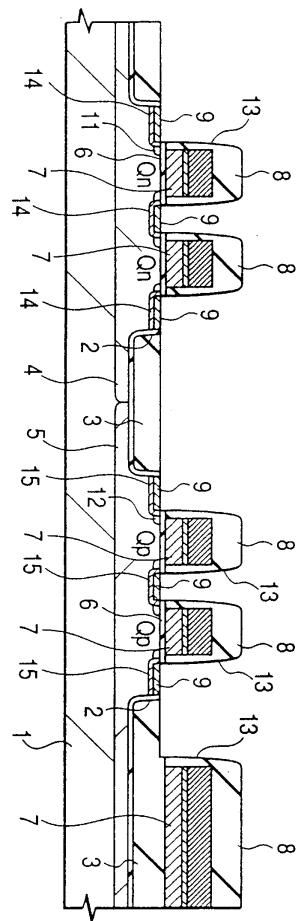

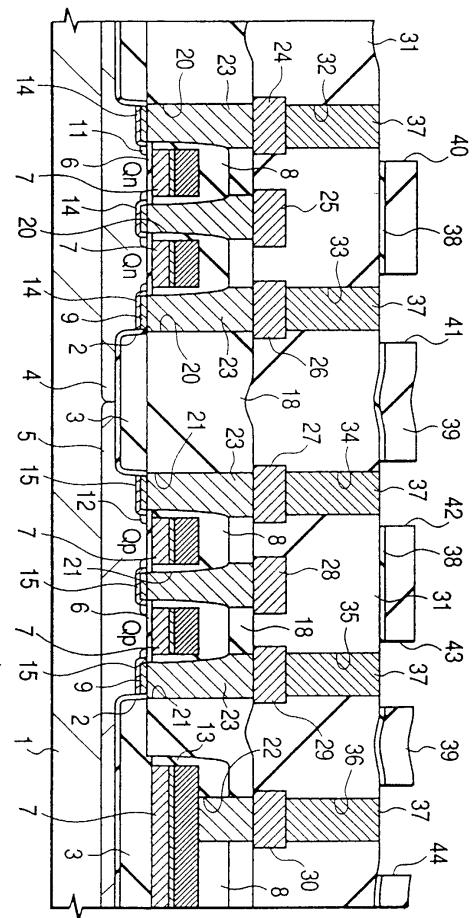

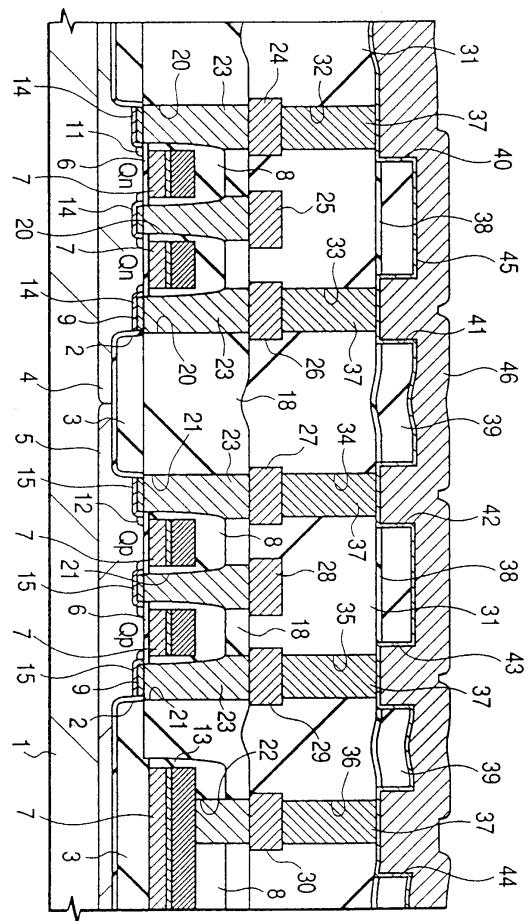

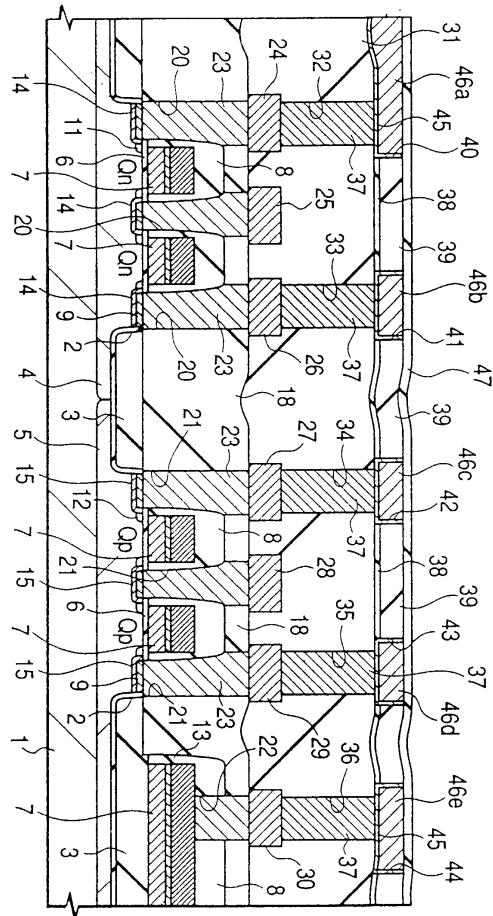

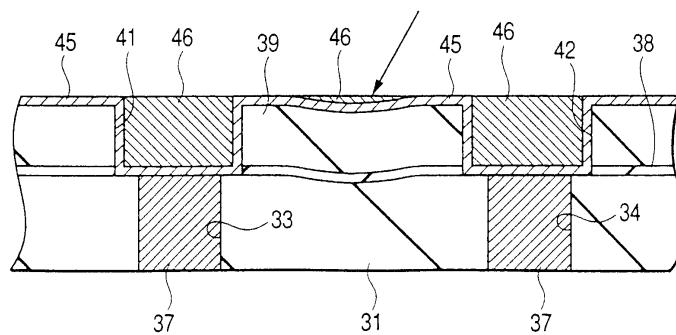

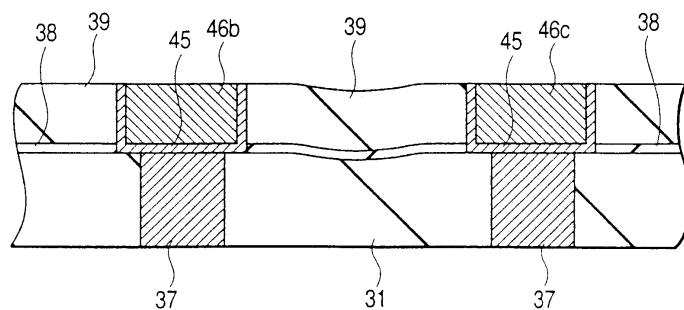

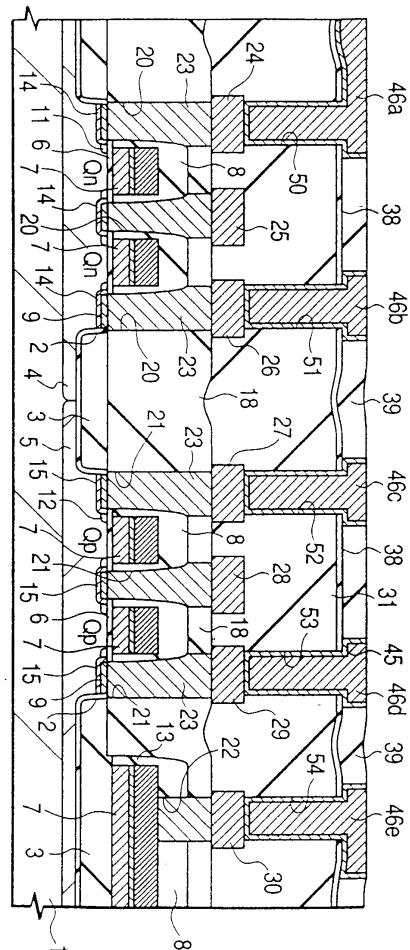

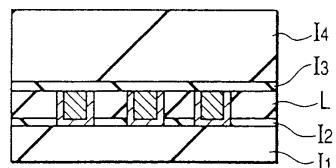

다음에, 도 7a, 도 7b에 도시한 바와 같이, 실리콘 산화막(31)의 상부에 플라즈마 CVD법으로 막 두께 50nm 정도의 얇은 실리콘 질화막(38)을 퇴적하고, 계속해서 실리콘 질화막(38)의 상부에 플라즈마 CVD법으로 막 두께 450nm 정도의 실리콘 산화막(39)을 퇴적한다. 그 후, 포토 레지스트막을 마스크로 한 드라이 에칭으로 관통 구멍(32 ~ 36)의 상부의 실리콘 산화막(39) 및 실리콘 질화막(38)을 제거하여, 배선홈(40 ~ 44)을 형성한다.

배선홈(40 ~ 44)을 형성하기 위해서는 우선 실리콘 질화막(38)을 에칭 스토퍼로 하여 실리콘 산화막(39)을 선택적으로 에칭하고, 그 후, 실리콘 질화막(38)을 에칭한다. 이와 같이, 배선홈(40 ~ 44)이 형성되는 실리콘 산화막(39)의 하층에 얇은 실리콘 질화막(38)을 형성해두고 이 실리콘 질화막(38)의 표면에서 에칭을 일단 정지한 후, 실리콘 질화막(38)을 에칭 함으로써, 배선홈(40 ~ 44)의 깊이를 정밀도 좋게 제어 할 수 있다.

다음에, 상기 배선홈(40 ~ 44)의 내부에 이하와 같은 방법으로 제2층째의 배선이 되는 매립 Cu 배선을 형성한다.

우선, 도 8에 도시한 바와 같이, 배선홈(40 ~ 44)의 내부를 포함하는 실리콘 산화막(39)의 상부에 스퍼터링법으로 막 두께 50nm 정도의 얇은 TiN(질화 티탄)막(45)을 퇴적한 후, TiN막(45)의 상부에 배선홈(40 ~ 44)의 깊이보다도 충분히 두꺼운 막 두께(예를 들면 800nm 정도)의 Cu막(46)을 스퍼터링법으로 퇴적한다. 계속해서, 475°C 정도의 비산화성 분위기 (예를 들면 수소 분위기) 중에서 기판(1)을 열처리함으로써 Cu막(46)을 리플로우시키고, 배선홈(40 ~ 44)의 내부에 간극 없이 Cu막(46)을 매립한다.

또, 여기서는 스퍼터법에 의한 Cu막(46)과 그 후의 리플로우에 의한 매립을 설명하였지만, 얇은 Cu막을 스퍼터법에 의해 형성하고, 그 후 도금법으로 Cu막(46)에 상당하는 Cu막을 형성해도 된다.

Cu는 실리콘 산화막 중에 확산하기 쉽다고 하는 성질이 있기 때문에, 배선홈(40 ~ 44)의 내부에 Cu 배선을 형성한 경우, 실리콘 산화막(39) 중에 Cu가 확산하고, 배선간의 단락이나 실리콘 산화막(39)의 유전률 상승에 의한 배선간 기생 용량의 증가를 야기한다. 또한, Cu는 산화 실리콘 등의 절연 재료에 대한 밀착성이 부족하다고 하는 성질이 있기 때문에, 실리콘 산화막(39)과의 계면에서 박리를 야기하기 쉽다.

따라서, 배선홈(40 ~ 44)의 내부에 Cu 배선을 형성하는 경우에는 실리콘 산화막(39)과 Cu막(46) 간에 Cu의 확산을 억제하고 또한 절연 재료에 대한 밀착성이 높은 배리어층을 설치할 필요가 있다. 또한, 상기한 바와 같은 리플로우·스퍼터링법으로 배선홈(40 ~ 44)의 내부에 Cu막(46)을 매립하는 경우에는 리플로우 시에 Cu막(46)의 습윤성을 향상시키는 성질도 배리어층에 요구된다.

Cu와 거의 반응하지 않는 상기 TiN이나 WN, TaN(질화 탄탈) 등의 고융점 금속 질화물은 이러한 배리어층으로서 적합한 재료이다. 또한, 고융점 금속 질화물에 Si(실리콘)을 첨가한 재료나 Cu와 반응하기 어려운 Ta, Ti, W, TiW 합금 등의 고융점 금속도 배리어층으로서 이용할 수 있다.

또한, 이하에서 설명하는 Cu 배선의 형성 방법은 고순도의 Cu막을 사용하여 Cu 배선을 형성하는 경우뿐만 아니라 Cu를 주성분으로 하는 합금막을 사용하여 Cu 배선을 형성하는 경우에도 적용할 수 있다.

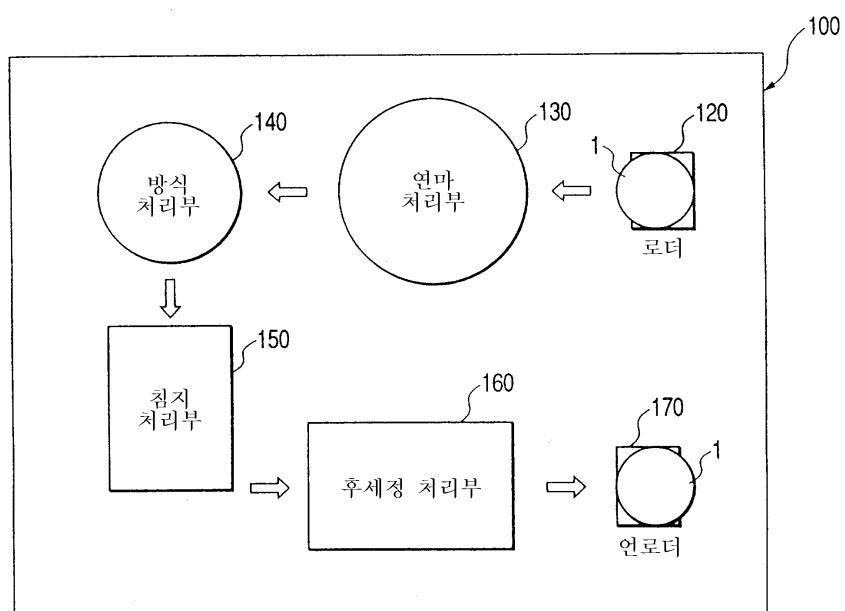

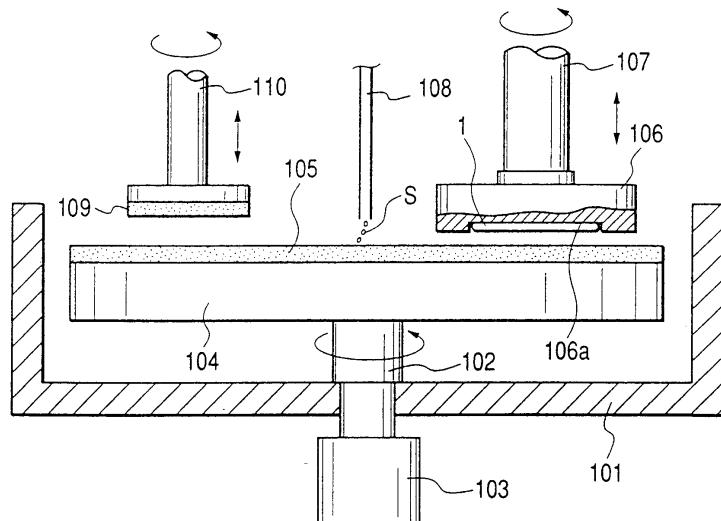

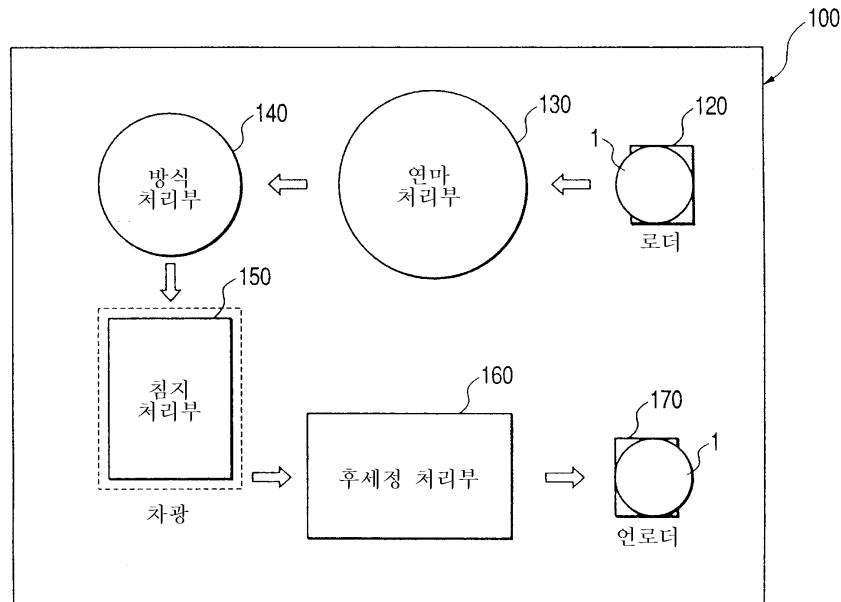

도 9는 상기 Cu막(46)의 연마에 이용하는 웨이퍼형의 CMP 장치(100)를 나타낸 개략도이다. 이 CMP 장치(100)는 표면에 Cu막(46)이 형성된 기판(1)을 복수매 수용하는 로더(loader)(120), Cu막(46)을 연마, 평탄화하는 연마 처리부(130), 연마가 종료한 기판(1)의 표면에 방식 처리를 실시하는 방식 처리부(140), 방식 처리가 종료한 기판(1)을 후세정하기까지의 동안, 그 표면이 건조하지 않도록 유지해두는 침지 처리부(150), 방식 처리가 종료한 기판(1)을 후세정하는 후세정 처리부(160), 및 후세정이 종료한 기판(1)을 복수매 수용하는 언로더(unloader)(170)를 포함한다.

도 10에 도시한 바와 같이, CMP 장치(100)의 연마 처리부(130)는 상부가 개구된 케이싱(box-like body)(101)을 가지고 있고, 이 케이싱(101)에 부착된 회전축(102)의 상단부에는 모터(103)에 의해서 회전 구동되는 연마반(polishing disc)(플래튼(platen) ; 104)이 부착되어 있다. 이 연마반(104)의 표면에는 다수의 기공을 갖는 합성 수지를 균일하게 접착하여 형성한 연마 패드(105)가 부착되어 있다.

또한, 이 연마 처리부(130)는 기판(1)을 유지하기 위한 웨이퍼 캐리어(106)를 구비하고 있다. 웨이퍼 캐리어(106)를 부착한 구동축(107)은 웨이퍼 캐리어(106)와 일체가 되어 모터(도시하지 않음)에 의해 회전 구동되며 또한 연마반(104)의 상측에서 상하 이동되도록 되어 있다.

기판(1)은 웨이퍼 캐리어(106)에 설치된 진공 흡착 기구(도시하지 않음)에 의해 그 주요면 즉 피연마면을 하향으로 하여 웨이퍼 캐리어(106)에 유지된다. 웨이퍼 캐리어(106)의 하단부에는 기판(1)이 수용되는 오목부(106a)가 형성되어 있고, 이 오목부(106a) 내에 기판(1)을 수용하면, 그 피연마면이 웨이퍼 캐리어(106)의 하단면과 거의 동일하거나 약간 돌출한 상태가 된다.

연마반(104)의 상측에는 연마 패드(105)의 표면과 기판(1)의 피연마면 간에 연마 슬러리(S)를 공급하기 위한 슬러리 공급관(108)이 설치되어 있으며, 그 하단으로부터 공급되는 연마 슬러리(S)에 의해서 기판(1)의 피연마면이 화학적 및 기계적으로 연마된다. 연마 슬러리(S)로서는 예를 들면 알루미나 등의 지립과 과산화 수소수 또는 질산 제2 철수용액 등의 산화제를 주성분으로 하고, 이들을 물에 분산 또는 용해시킨 것이 사용된다.

또한, 이 연마 처리부(130)는 연마 패드(105)의 표면을 정형(드레싱)하기 위한 공구인 드레서(109)를 구비하고 있다. 이 드레서(109)는 연마반(104)의 상측에서 상하 이동하는 구동축(110)의 하단부에 부착되며, 모터(도시하지 않음)에 의해 회전 구동되도록 되어 있다.

연마가 종료한 기판(1)은 방식 처리부(140)에 있어서, 그 표면에 방식 처리가 실시된다. 방식 처리부(140)는 상기한 연마 처리부(130)의 구성과 유사한 구성으로 되어 있고, 여기서는 우선 연마반(플래튼)의 표면에 부착한 연마 패드에 기판(1)의 주요면이 압박되어 연마 슬러리가 기계적으로 제거된 후, 예를 들면 벤조트리아졸(BTA) 등의 방식제를 포함한 약액이 기판(1)의 주요면에 공급됨으로써, 기판(1)의 주요면에 형성된 Cu 배선의 표면 부분에 소수성 보호막이 형성된다.

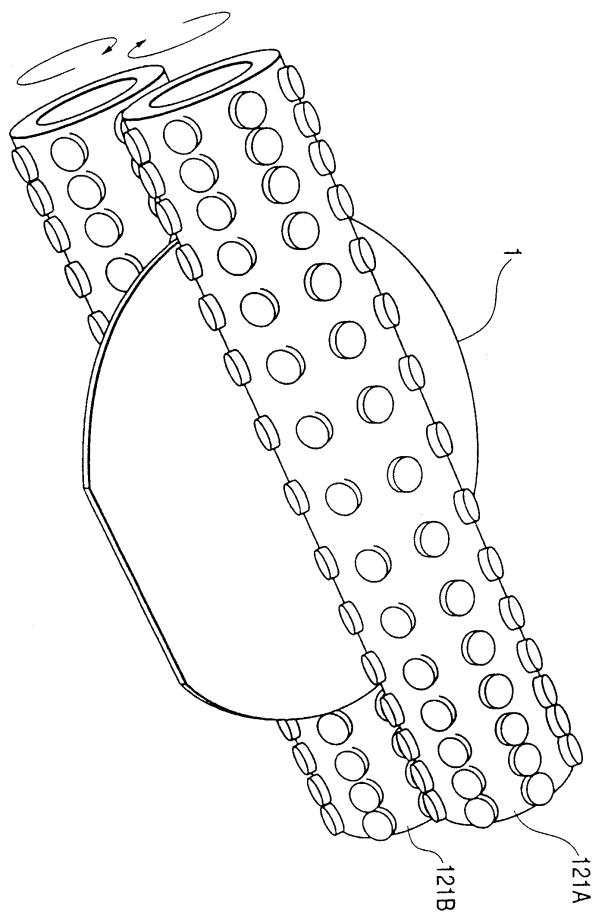

연마 슬러리의 기계적 세정(전 세정)은 예를 들면, 도 11에 도시한 바와 같이, 수평면 내에서 회전시킨 기판(1)의 양면을 PVA(폴리비닐 알콜)와 같은 합성 수지의 다공질체로 이루어지는 원통형의 브러시(121A, 121B)에 끼워서, 브러시(121A, 121B)를 기판(1) 면에 대하여 수직인 면 내에서 회전하면서 기판(1)의 양면을 동시에 세정한다. 또한, 전 세정 후의 방식 처리에 있어서는 필요에 따라 순수 스크럽 세정, 순수 초음파 세정, 순수 유수 세정 또는 순수 스펀 세정 등을 방식 처리에 선행 또는 병행하여 행함으로써, 연마 처리부(130)에서 기판(1)의 주요면에 부착한 연마 슬러리 중의 산화제를 충분히 제거하고, 산화제가 실질적으로 작용하지 않은 조건 하에서 소수성의 보호막을 형성하도록 한다.

방식 처리가 종료한 기판(1)은 그 표면의 건조를 막기 위하여, 침지 처리부(150)에 일시적으로 보관된다. 침지 처리부(150)는 방식 처리가 종료한 기판(1)을 후세정하기까지의 동안, 그 표면이 건조하지 않도록 유지하기 위한 것으로, 예를 들면 순수(pure water)를 오버플로우시킨 침지조(저장 컨테이너(storage container)) 중에 소정 매수의 기판(1)을 침지시켜서 보관하는 구조로 되어 있다. 이 때, Cu 배선(28 ~ 30)의 전기 화학적 부식 반응이 실질적으로 진행하지 않을 정도의 저온으로 냉각한 순수를 침지조에 공급함으로써 Cu 배선(28 ~ 30)의 부식을 한층 더 확실하게 방지할 수 있다.

기판(1)의 건조 방지는 예를 들면, 순수 샤워(pure shower)의 공급 등, 적어도 기판(1)의 표면을 습윤 상태로 유지할 수 있는 방법이면, 상기한 침지조 중에서의 보관 이외 방법으로 행해도 된다.

후세정 처리부(160)로 반송된 기판(1)은 그 표면의 습윤 상태가 유지된 상태에서 즉시 후세정 된다. 여기서는, 산화제를 중화하기 위해서 NH<sub>4</sub>OH를 포함하는 세정액 등의 약 알칼리 약액을 공급하면서, 기판(1)의 표면을 스크럽 세정(또는 브러쉬 세정(brush washing))한 후, 불산 수용액을 기판(1)의 표면에 공급하여 에칭에 의한 이물 입자(particle)의 제거를 행한다. 또한, 상기한 스크럽 세정에 선행 또는 병행하여, 기판(1)의 표면을 순수 스크럽 세정, 순수 초음파 세정, 순수 유수(running pure water) 세정 또는 순수 스펀 세정하거나 기판(1)의 이면을 순수 스크립 세정하거나 해도 된다.

상기 후세정 처리가 종료한 기판(1)은 순수 린스 및 스펀 드라이 후, 건조한 상태에서 언로더(170)에 수용되며 복수매 단위로 일괄하여 다음 공정으로 반송된다.

또, 도 12에 나타낸 바와 같이, 방식 처리가 종료한 기판(1)의 표면 건조를 막기 위한 침지 처리부(웨이퍼 보관부 ; 150)를 차광 구조로 하고, 보관 중인 기판(1)의 표면에 조명광 등이 조사되지 않도록 할 수 있다. 이에 따라, 광기전력 효과에 의한 단락 전류의 발생을 막도록 할 수 있다. 침지 처리부(150)를 차광 구조로 하기 위해서는, 구체적으로는 침치조(저장 컨테이너)의 주위를 차광 시트 등으로 피복함으로써, 침치조(저장 컨테이너)의 내부의 조도를 적어도 500룩스(lux) 이하, 바람직하게는 300룩스 이하, 더 바람직하게는 100룩스 이하로 한다.

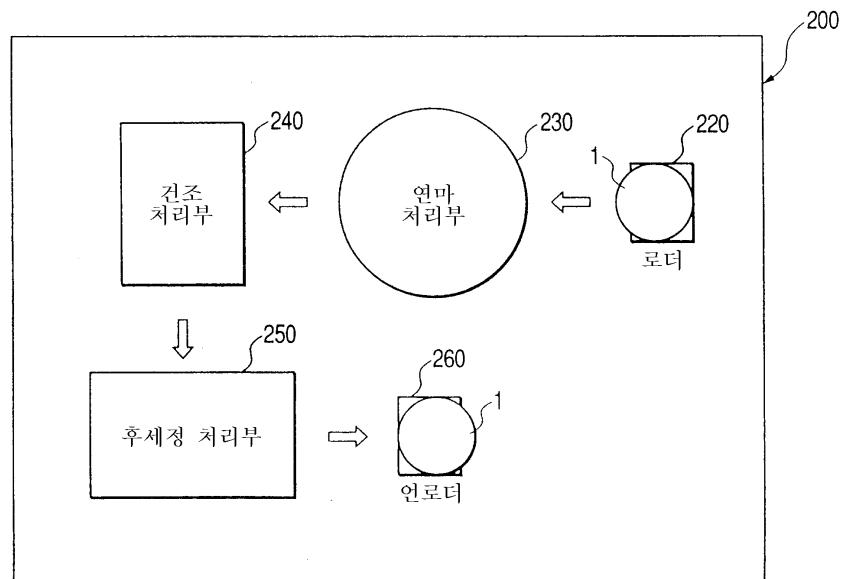

또한, 도 13에 도시한 바와 같이, 연마 처리의 직후, 즉 그 표면에 남은 연마 슬러리 중의 산화제에 의한 전기 화학적 부식 반응이 개시되기 전에 즉시 건조 처리부로 반송되며, 연마 슬러리 중의 수분이 강제 건조에 의해서 제거되어도 된다. 도 13에 도시하는 CMP 장치(200)는 표면에 Cu막이 형성된 기판(1)을 복수매 수용하는 로더(220), Cu막을 연마, 평탄화하여 배선을 형성하는 연마 처리부(230), 연마가 종료한 기판(1)의 표면을 건조시키는 건조 처리부(240), 기판(1)을 후세정하는 후세정 처리부(250) 및 후세정이 종료한 기판(1)을 복수매 수용하는 언로더(260)를 포함한다. 이 CMP 장치(200)를 사용한 Cu 배선 형성 프로세스에서는 연마 처리부(230)에 있어서, 연마 처리된 기판(1)은 연마 처리의 직후 즉 그 표면에 남은 연마 슬러리 중의 산화제에 의한 전기 화학적 부식 반응이 개시되기 전에 즉시 건조 처리부(240)에 반송되며, 연마 슬러리 중의 수분이 강제 건조에 의해서 제거된다. 그 후, 기판(1)은 건조 상태가 유지된 채로 후세정 처리부(250)에 반송되며 후세정 처리에 첨부된 후, 순수 린스 및 스펀 드라이를 거쳐서 언로더(260)에 수용된다. 이 경우, 연마 처리의 직후부터 후세정이 개시되기까지의 동안, 기판(1)의 표면이 건조 상태로 유지되기 때문에, 전기 화학적 부식 반응의 개시가 억제되며, 이에 따라, Cu 배선의 부식을 유효하게 방지하는 것이 가능해진다.

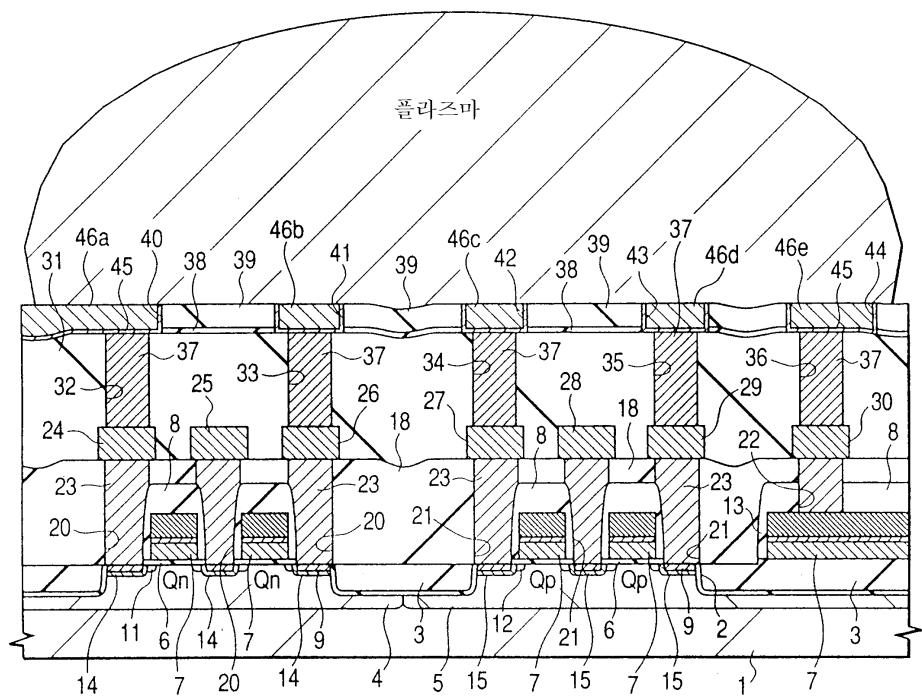

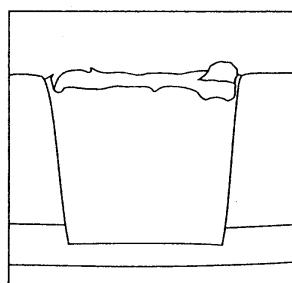

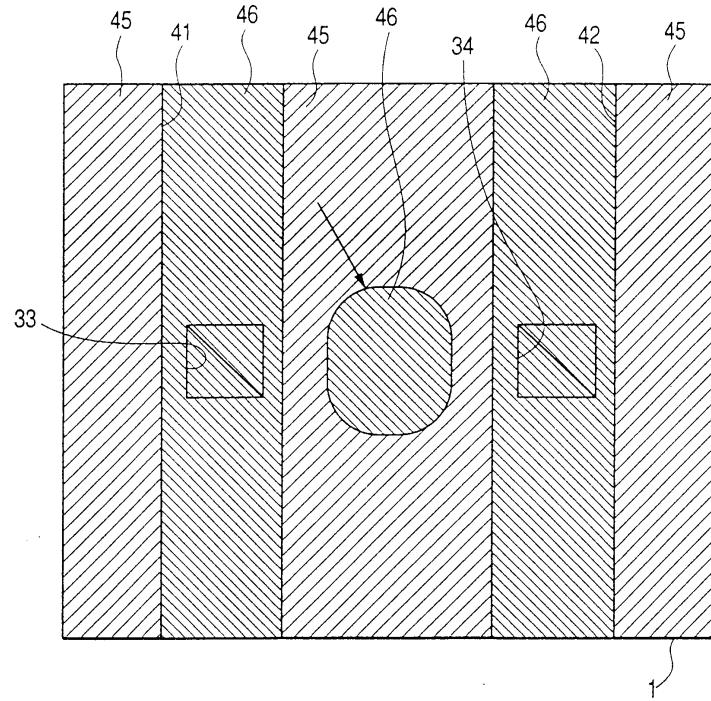

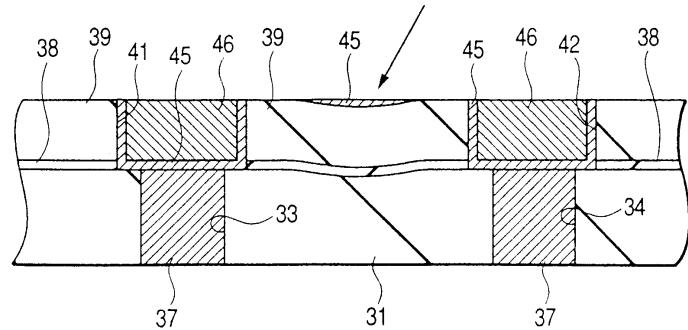

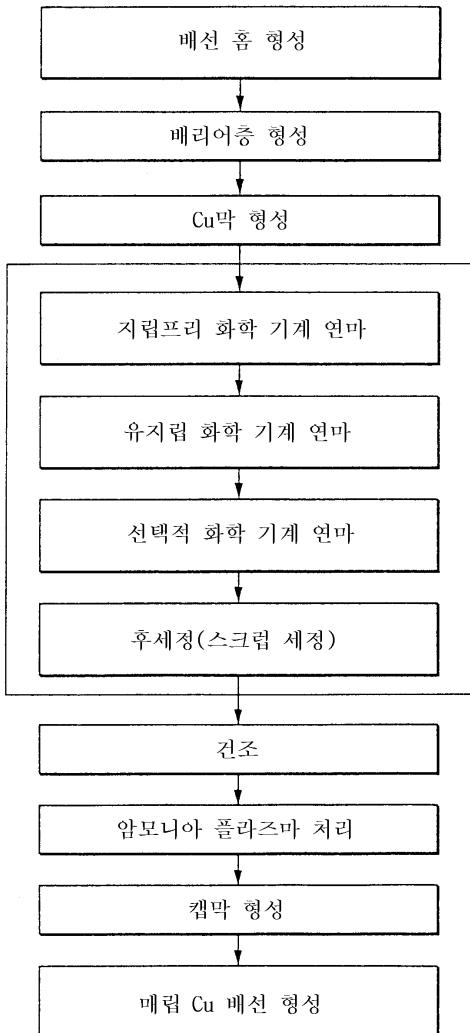

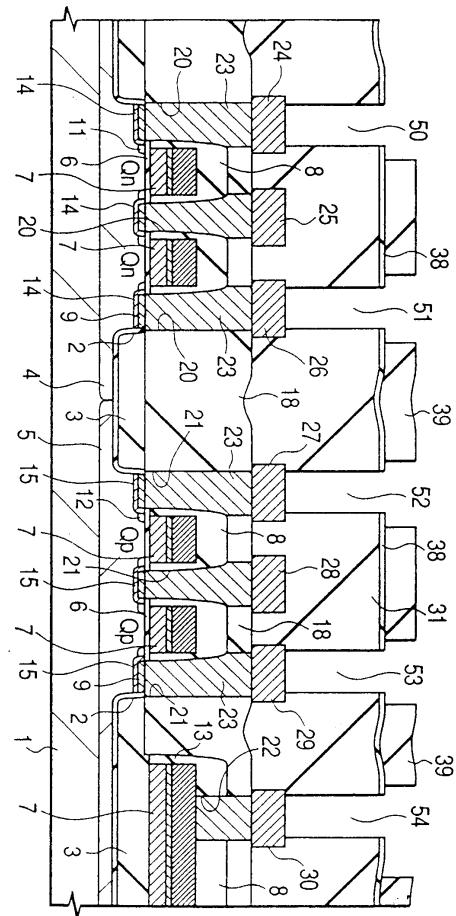

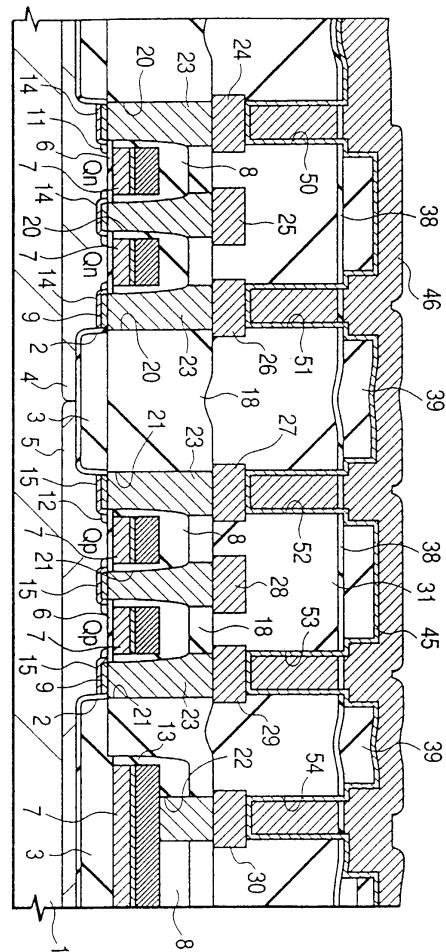

이러한 CMP법에 의해, 실리콘 산화막(39) 상의 Cu막(46) 및 TiN막(45)을 제거하고 도 14에 도시한 바와 같이, 배선홈(40 ~ 44) 내에 Cu 배선(46a ~ 46e)을 형성한다.

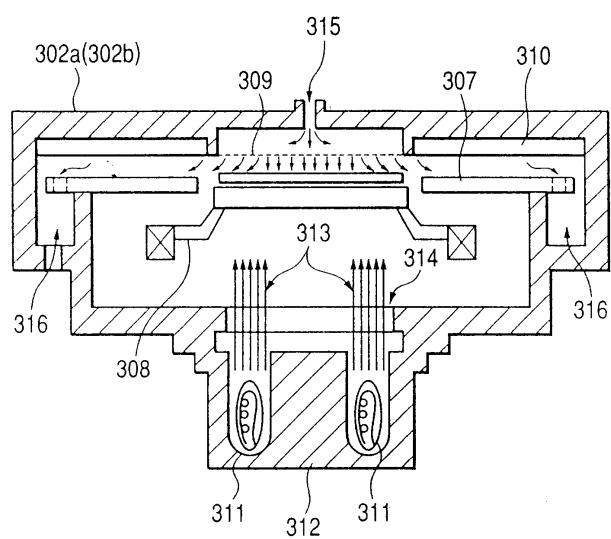

다음에, Cu 배선(46a ~ 46e)과 실리콘 산화막(39)의 표면에 플라즈마 처리를 실시한다. 도 15a는 플라즈마 처리에 이용하는 처리 장치의 개요를 나타낸 단면도이며, 도 15b는 플라즈마 처리에 이용하는 처리 장치의 개요를 나타낸 평면도이다.

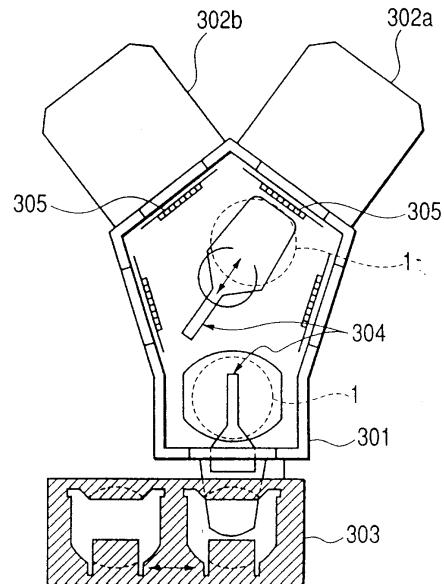

이 처리 장치에는 로드 로크실(load lock chamber)(301)에 2개의 처리실(treatment chamber)(302a, 302b)과 카세트 인터페이스(303)가 부착되어 있다. 로드 로크실(301) 내에는 기판(1)을 반송하는 로봇(304)을 갖는다. 로드 로크실(301)과 처리실(302a, 302b) 간에는 처리 중에도 로드 로크실(301)내의 고진공 상태가 이어질 수 있도록 게이트 밸브(305)를 갖는다.

처리실(302a, 302b) 내에는 기판(1)을 유지하는 서셉터(susceptor)(306), 가스류(gas flow)를 조정하는 배플판(baffle plate)(307), 서셉터(306)를 지지하는 지지 부재(308), 서셉터(306)에 대향하여 배치되는 매쉬 형상의 전극(309), 배플판(307)에 거의 대향하여 배치된 절연판(310)을 갖는다. 절연판(310)은 서셉터(306)와 전극(309) 간 이외의 불필요한 영역에서의 기생 방전을 억제하는 작용이 있다. 서셉터(306)의 이면측에는 반사 유닛(311) 내에 설치된 램프(312)가 배치되며, 램프(312)를 발한 적외선(313)이 석영창(314)을 통과하여 서셉터(306) 및 기판(1)에 조사된다. 이에 따라 기판(1)이 가열된다. 또, 기판(1)은 서셉터(306) 상에 페이스 업으로 설치된다.

처리실(302a, 302b)은 그 내부를 고진공으로 배기하는 것이 가능하고, 처리 가스 및 고주파 전력이 가스 포트(315)로부터 공급된다. 처리 가스는 매쉬 형상의 전극(309)을 통과하여 기판(1)의 근방에 공급된다. 처리 가스는 진공 매니폴드(316)로부터 배출되며, 처리 가스의 공급 유량 및 배기 속도를 제어함으로써 압력이 제어된다. 고주파 전력은 전극(309)에 인가되며, 서셉터(306)와 전극(309) 간에서 플라즈마를 생성한다. 고주파 전력은 예를 들면 13.56MHz의 주파수를 이용한다.

처리실(302a)에서는 예를 들면 다음에 설명하는 암모니아 플라즈마 처리가 행해진다. 또한, 처리실(302b)에서는 후에 설명하는 캡막(실리콘 질화막)의 퇴적이 행해진다. 처리실(302a)과 처리실(302b)과는 로드 로크실(301)을 통하여 접속되어 있기 때문에, 암모니아 플라즈마 처리 후에 진공 파괴하지 않고 기판(1)을 처리실(302b)에 반송할 수 있어 암모니아 플라즈마 처리와 캡막의 형성을 연속적으로 행할 수 있다.

다음에, 상기한 플라즈마 처리 장치를 이용하여 기판(1)에 암모니아 플라즈마 처리를 실시한다. 카세트 인터페이스(303)로부터 기판(1)이 로봇(304)에 의해 로드 로크실(301)에 반입된다. 로드 로크실(301)을 충분한 감압 상태가 되기까지 진공 배기하고, 로봇(304)을 이용하여 처리실(302a)에 기판(1)을 반송한다. 처리실(302a)의 게이트 밸브(305)를 폐쇄하고, 처리실(302a) 내가 충분한 진공도가 되기까지 배기한 후, 처리실(302a)에 암모니아 가스를 도입하고, 압력 조정을 행하여 소정의 압력으로 유지한다. 그 후, 고주파 전원으로부터 전극(309)에 전계를 인가하고, 도 16에 나타낸 바와 같이, 기판(1)의 표면을 플라즈마 처리한다. 소정 시간의 경과 후 고주파 전계를 정지하고, 플라즈마를 정지한다. 그 후, 처리실(302a) 내를 진공 배기하고, 게이트 밸브(305)를 개방하여 로봇(304)에 의해 기판(1)을 로드 로크실(301)에 반출한다. 또, 로드 로크실(301)은 고진공 상태로 유지되어 있기 때문에, 기판(1)의 표면이 대기 분위기에 노출되지는 않는다.

플라즈마 처리 조건은 예를 들면, 기판(1)의 사이즈를 8인치로 한 경우, 처리 압력을 5.0Torr, RF 전력을 600W, 기판 온도를 400°C, 암모니아 유량을 200sccm, 처리 시간을 10초로 할 수 있다. 전극 간 거리는 600mils로 하였다. 또, 플라즈마 처리 조건은 이들 예시한 조건에 한정되지 않지 않은 것은 물론이다. 본 발명자 등의 검토에서는 압력이 높을수록 플라즈마 손상을 저감할 수 있고, 기판 온도가 높을수록 TDDB 수명의 기판 내 변동의 저감과 장기 수명화가 시도된다. 또한, 기판 온도가 높고 RF 전력이 크며, 처리 시간이 길수록 Cu의 표면에 힐록이 발생하기 쉽다는 지견을 얻을 수 있다. 이들 지견과 장치 구성에 의한 조건의 변동을 고려하면, 처리 압력은 0.5 ~ 6Torr, RF 전력은 300 ~ 600W, 기판 온도는 350 ~ 450°C, 암모니아 유량은 20 ~ 500sccm, 처리 시간은 5 ~ 180초, 전극 간 거리는 300 ~ 600mils의 범위로 설정할 수 있다.

이와 같이, Cu 배선(46a ~ 46e)과 실리콘 산화막(39)의 표면에 플라즈마 처리를 실시함으로써, Cu 배선(46a ~ 46e) 및 실리콘 산화막(39)의 표면의 극히 얇은 영역에 각각의 하지 재료의 질화막을 형성할 수 있다. 이에 따라, 다음에 설명하는 캡막(실리콘 질화막)과 Cu 배선(46a ~ 46e) 및 실리콘 산화막(39)과의 밀착성이 향상하고, TDDB 수명을 현저하게 향상할 수 있다.

이 점은 본 발명자 등의 실험 결과와 함께 뒤에 자세히 설명한다.

다음에, 로봇(304)을 이용하여 기판(1)을 처리실(302b)에 반송한다. 처리실(302b)의 게이트 밸브(305)를 폐쇄하고, 처리실(302b) 내가 충분한 진공도가 되기까지 배기한 후, 처리실(302b)에 실란(SiH<sub>4</sub>), 암모니아, 질소의 혼합 가스를 도입하고, 압력 조정을 행하여 소정의 압력으로 유지한다. 그 후, 고주파 전원으로부터 전극(309)에 전계를 인가하여 플라즈마를 발생하고, 도 17에 도시한 바와 같이, Cu 배선(46a ~ 46e) 및 실리콘 산화막(39) 표면에 실리콘 질화막(47 ; 캡막)을 퇴적

한다. 소정 시간의 경과 후 고주파 전계를 정지하여 플라즈마를 정지한다. 그 후, 처리실(302b) 내를 진공 배기하고, 게이트 밸브(305)를 개방하여 로봇(304)에 의해 기판(1)을 로드 로크실(301)에 반출한다. 또한, 로봇(304)을 이용하여 카세트 인터페이스(303)에 기판(1)을 배출한다.

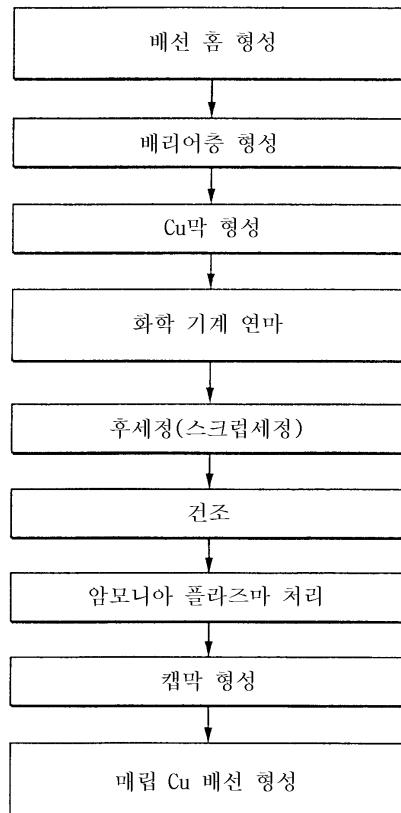

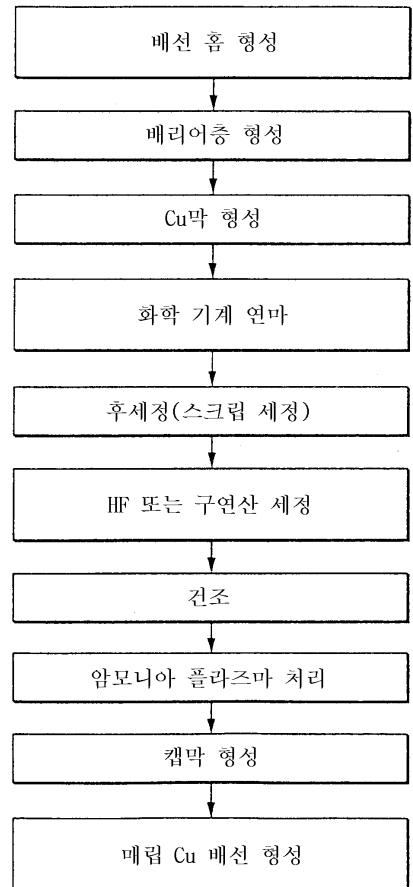

실리콘 질화막(47)의 막 두께는 예를 들면, 50nm으로 한다. 그 후, 제3층째의 배선과 제2층째의 배선[Cu 배선(46a ~ 46e)]을 접속하는 플러그를 형성하기 위한 실리콘 산화막을 형성하고, 상기한 바와 마찬가지 방법으로, 제3층째 이후의 매텁 Cu 배선이 형성된다. 도 18은 상술한 Cu 배선(46a ~ 46e)의 형성 프로세스의 전체 흐름도이다.

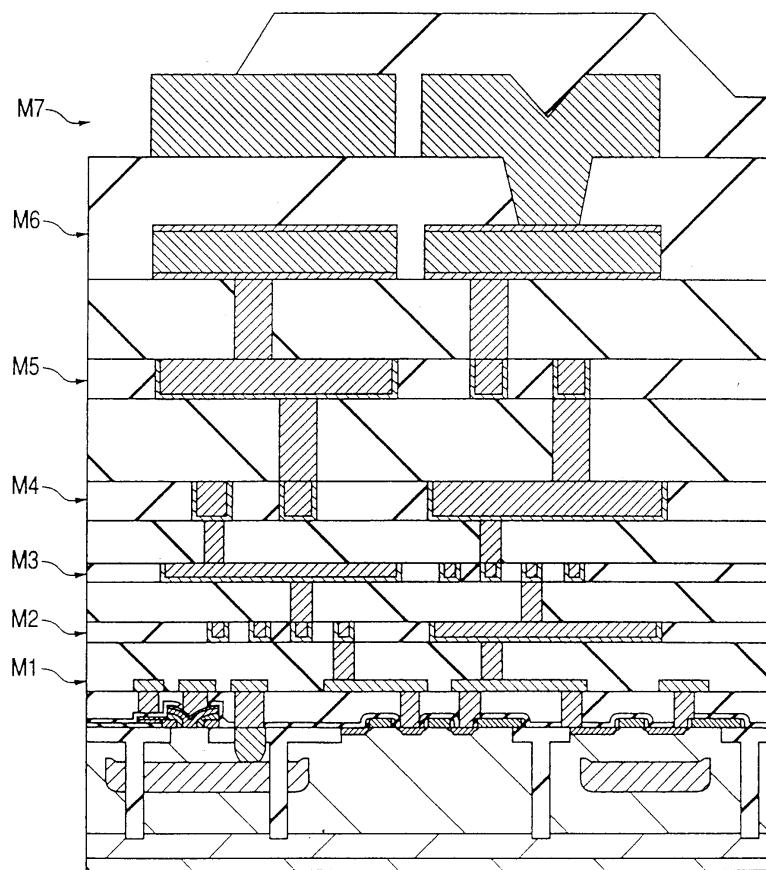

또, 도 19에 제7층째의 배선까지를 형성한 CMOS-LSI의 일례를 나타낸다. 제1층째의 배선(M1)은 상기한 바와 같이 텅스텐막으로 이루어진다. 제2층 배선(M2)으로부터 제5층 배선(M5)까지는 상기한 Cu 배선의 형성 방법으로 제조한다. 또, 제2층 배선(M2) 및 제3층 배선(M3)은 배선폭, 배선간 거리 및 배선 높이(두께)는 모두 0.5μm로 형성한다. 제4층 배선(M4) 및 제5층 배선(M5)은 배선 폭, 배선 간 거리 및 배선 높이(두께)는 모두 1μm로 형성한다. 제6층 배선(M6)은 텅스텐막, 알루미늄막 및 텅스텐막의 3층 구성으로 하고, 제7 층배선(M7)은 알루미늄막으로 구성한다. 제7 층배선(M7)에는 범프 등이 형성되지만 도시를 생략하고 있다.

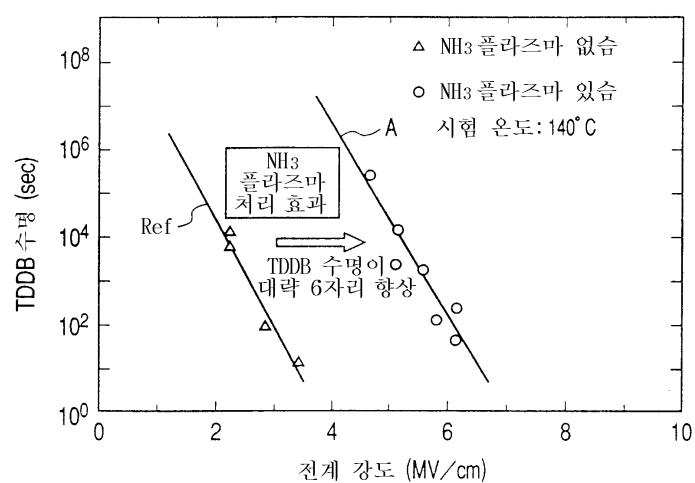

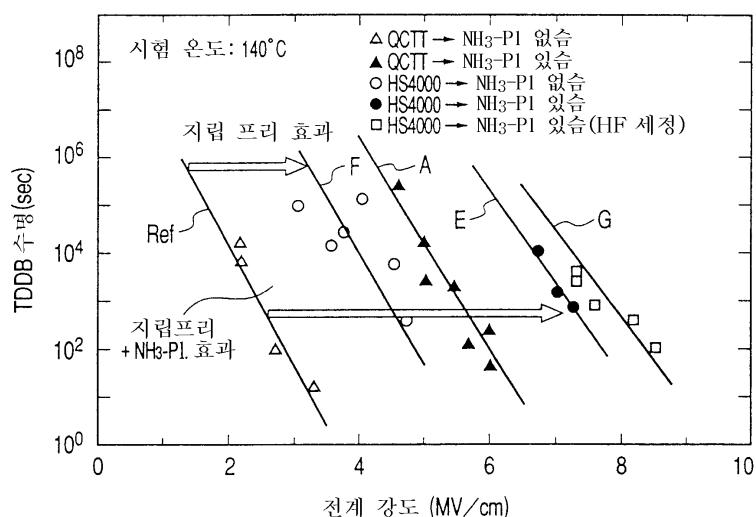

본 실시 형태에 따르면, TDDB 수명이 대폭 개선된다. 도 20은 본 실시 형태의 제2층 배선 M2[Cu 배선(46a ~ 46e)]와 동층으로 형성된 TEG 샘플의 TDDB 수명을 나타내는 그래프로, 본 실시 형태의 경우의 데이터를 라인 A로 나타낸다. 비교를 위해 암모니아 플라즈마 처리를 하지 않은 경우의 TDDB 수명 데이터(라인 Ref)도 동시에 나타낸다. 도면에서부터 분명한 바와 같이, 본 실시 형태에서는 비교 데이터와 비교하여 약 6자릿수의 수명 향상을 알 수 있다.

도 21은 본 실시 형태에서 적용한 실리콘 산화막(39)을 그보다도 치밀하게 강고한 실리콘 질화막으로 치환한 경우의 데이터(라인 B)를 나타낸다. 절연막을 질화 실리콘으로 치환한 경우라도 암모니아 플라즈마 처리를 실시하지 않으면 절연막을 실리콘 산화막으로 한 경우와 아무런 차이는 없다(라인 Ref). 한편, 실리콘 질화막을 절연막에 적용하고, 암모니아 플라즈마 처리를 실시하면, 본 실시 형태 이상으로 TDDB 수명이 향상된다. 그러나 그 향상의 비율은 크지 않고 암모니아 플라즈마 처리를 행함에 의한 요인쪽이 지배적인 것을 알 수 있다. 이것은 TDDB 수명을 지배하는 요인은 절연막의 별크보다는 그 계면이 지배적인 것을 나타내고 있다.

그래서, 본 발명자 등은 암모니아 플라즈마 처리에 의해 TDDB 수명이 향상하는 기구를 해석하기 위해서 구리와 실리콘 산화막의 표면 분석을 행하였다. 이하에 해석의 결과를 설명한다.

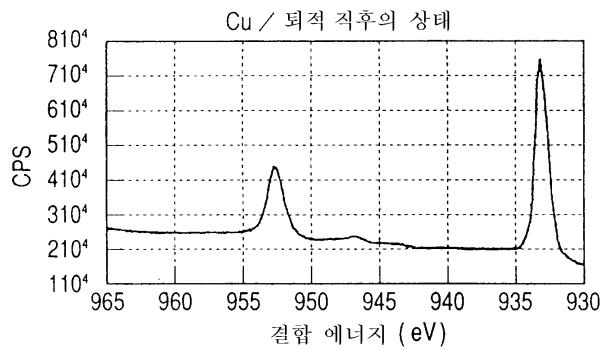

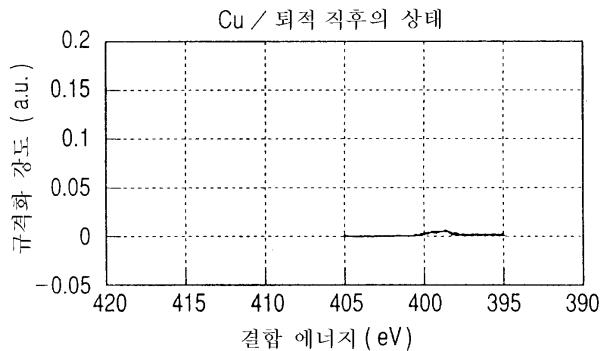

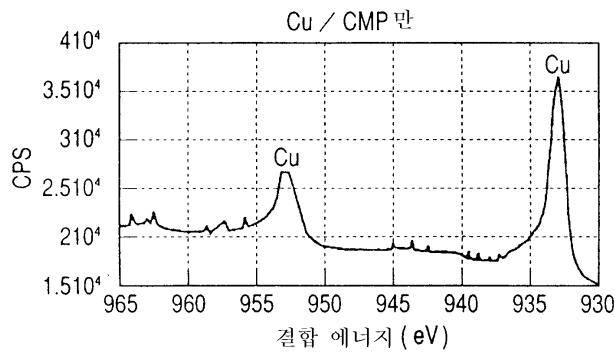

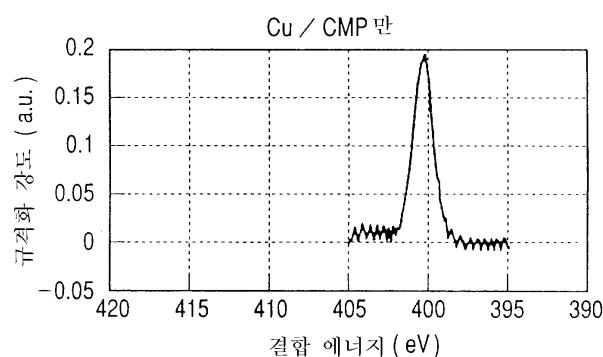

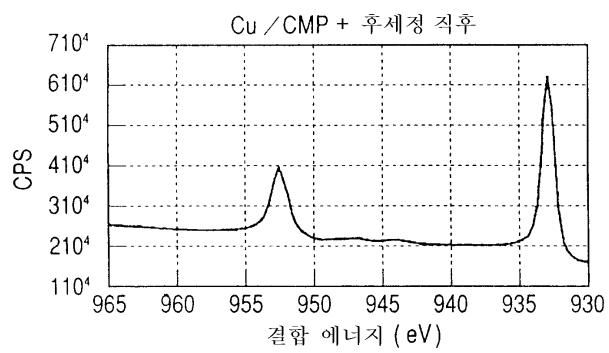

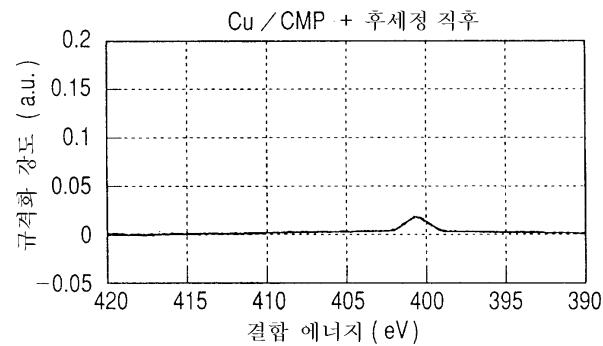

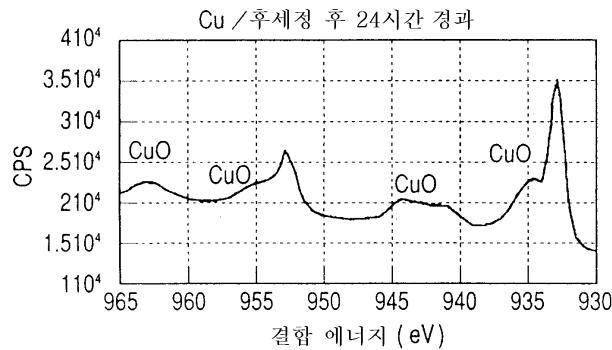

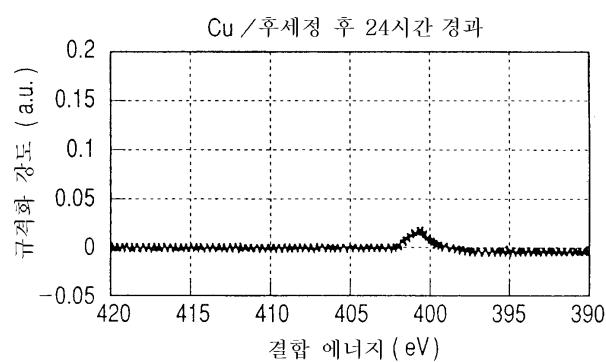

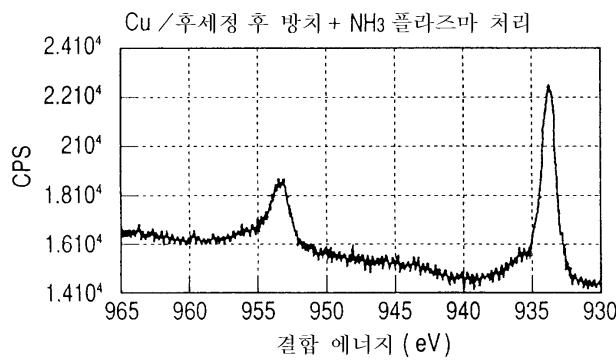

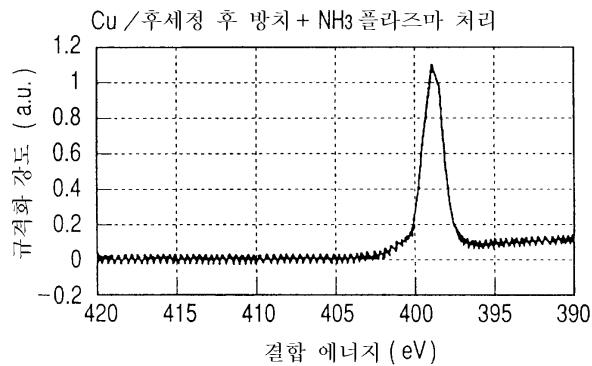

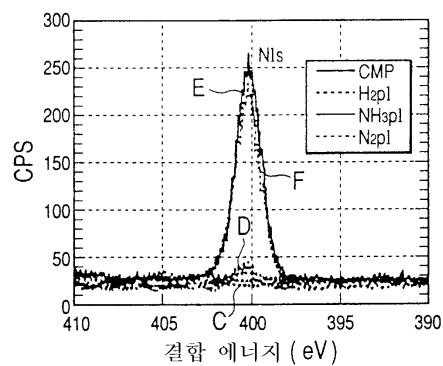

도 22 ~ 도 24는 Cu 배선 표면의 XPS(X-ray Photo-electron Spectroscopy) 분석의 결과를 나타낸 그래프이다. 각 도면의 (a), (c)는 Cu2p의 분광 결과를 나타내고, (b), (d)는 N1s의 분광 결과를 나타낸다.

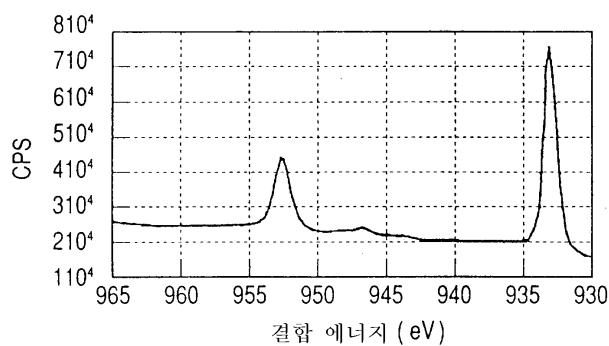

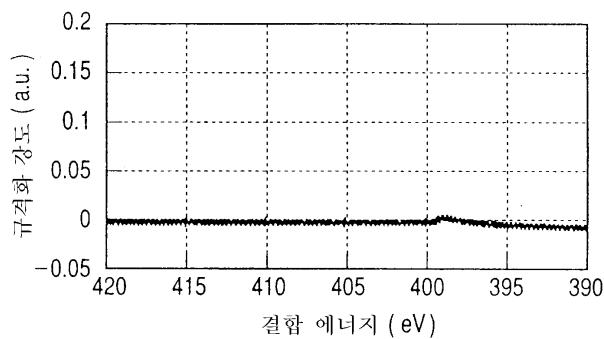

도 22a, 도 22b는 퇴적 직후의 상태의 Cu막 표면을 분석한 결과이다. Cu2p의 피크가 관찰되며, N1s의 피크는 노이즈 레벨이기 때문에, 퇴적 직후의 상태의 Cu막에는 질소는 존재하지 않은 것을 알 수 있다. 도 22c, 도 22d는 Cu막에 CMP만을 실시한 직후의 Cu 배선 표면을 분석한 결과이다. Cu2p의 피크와 함께 N1s의 피크가 관찰된다. 상기한 바와 같이 슬러리에는 BTA가 포함되기 때문에, Cu 표면에 잔류한 BTA 내의 질소가 관찰되고 있는 것으로 추찰할 수 있다. 도 23a, 도 23b는 CMP 후에 후세정까지 행한 상태의 Cu 배선 표면을 분석한 결과이다. Cu2p 피크에 변화는 보이지 않았지만, N1s 피크가 저하하고 있다. 세정에 의해 BTA가 제거되었다고 생각된다. 도 23c, 도 23d는 후세정 후 대기 분위기로 24시간 방치한 상태의 Cu 배선 표면을 분석한 결과이다. Cu2p의 피크와 함께 CuO의 피크가 관찰된다. N1s 피크에는 방치에 의한 변화는 보이지 않는다. 방치에 의해 Cu 표면이 산화되며 CuO가 생성되고 있는 것을 알 수 있다.

이와 같이 산화된 Cu 배선에 암모니아 플라즈마 처리를 실시한 상태의 Cu 배선 표면을 분석한 결과가 도 24a, 도 24b이다. CuO의 피크는 거의 소실하고 있다. 한편, N1s 피크는 강하게 생기고 있다. Cu 표면이 환원되어 산소가 방출되고 있음과 함께 표면이 질화되고 있다고 생각된다. 비교를 위해, 산화된 Cu 배선에 350°C의 수소 열처리를 실시한 상태의 Cu 배선 표면을 분석하였다. 결과는 도 24c, 도 24d이다. Cu2p 피크에 대하여 도 24c와 도 24a를 비교하면 보다 퇴적 직후 상태(도 22a)에 가깝기 때문에, 수소 열 처리쪽이 환원성은 강하다고 생각된다. 한편, N1s 피크는 거의 관찰되지 않기 때문에 수소 열 처리에서는 Cu 표면이 환원될 뿐이다.

이상의 결과로부터, 암모니아 플라즈마 처리에 의해 Cu 배선(46a ~ 46e)의 표면이 환원됨과 함께 질화층이 형성된 것을 알 수 있다. 이 질화층은 암모니아 플라즈마 처리 후에 실리콘 질화막을 퇴적할 때의 원료 가스에 포함되는 실란과 구리와의 반응을 방지하고, 구리의 실리사이드의 형성을 억제하는 기능을 갖는다고 생각된다. 실리사이드 형성의 방지는 배선 저항의 증가를 억제하는 역할이 있다고 생각한다.

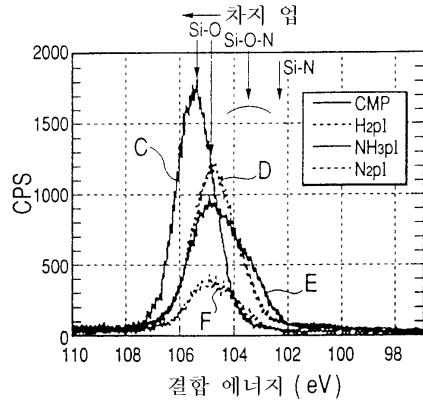

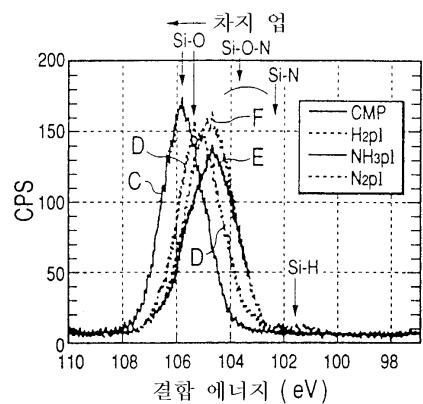

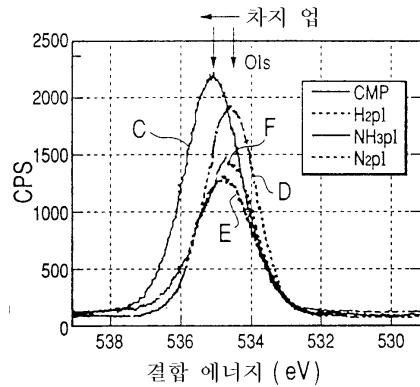

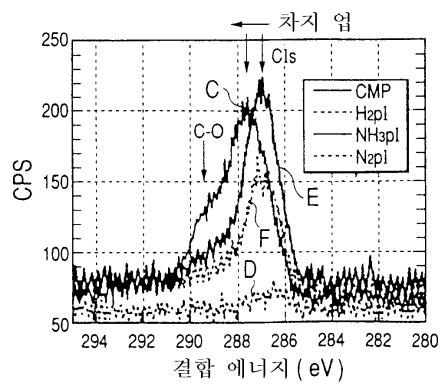

도 25는 실리콘 산화막 표면의 XPS 분석을 행한 결과를 나타내는 그래프이고, 도 26 및 도 27은 실리콘 산화막의 질량 분석(TDS-APIMS)을 행한 결과를 나타내는 그래프이다. 실리콘 산화막의 분석에서는 CMP 후세정까지 행한 상태(프로파일 C), CMP 후세정 후 수소 플라즈마 처리를 행한 상태(프로파일 D), CMP 후세정 후 암모니아 플라즈마 처리를 행한 상태(프로파일 E), CMP 후세정 후 질소 플라즈마 처리를 행한 상태(프로파일 F)에 대하여 분석하였다. 또, 프로파일 C의 1eV 정도의 고에너지 방향으로의 어긋남은 차지 업의 영향에 따른 것이다.

도 25a, 도 25b는 모두 Si2p 스펙트럼을 관찰한 데이터로, 도 25a는 10nm 정도의 깊이를 도 25b는 2nm 정도의 깊이를 분석한 것이다. 도 25c, 도 25d, 도 25e는 각각 N1s, O1s, C1s 스펙트럼을 관찰한 데이터이다.

도 25b로부터, 수소 플라즈마 처리(프로파일 D)의 저에너지측(102eV 부근)에 넓은 피크가 나타난다. 이것은 Si-H 결합이 존재한다고 생각되며 수소 플라즈마 처리에 의해 실리콘 산화막 표면에 Si-H가 형성된다고 추찰된다.

도 25a로부터, 암모니아 플라즈마 처리(프로파일 E)와 질소 플라즈마 처리(프로파일 F)의 105eV의 피크가 저에너지측으로 넓어진 비대칭인 피크로 되어 있다. 비대칭 부분의 피크(103.5eV)는 Si-O-N 결합이라고 생각된다. 암모니아 플라즈마 처리 및 질소 플라즈마 처리에 의해 실리콘 산화막의 표면이 질화되고 있다고 추찰된다. 또한, 도 25a와 도 25b와의 비교로부터, 질화는 표면에서 보다 강하다고 생각된다. 암모니아 플라즈마 처리 및 질소 플라즈마 처리에 의한 질화는 도 25c에서도 확인할 수 있다.

도 25e로부터, 수소 플라즈마 처리(프로파일 D)에서는 탄소는 거의 검출되지 않는다. 수소 플라즈마 처리에 의해 표면의 유기물이 제거되고 있는 것을 알 수 있다. 또한, CMP 후(프로파일 C)의 289eV의 피크는 C-O 결합이라고 생각된다. CMP 후에서는 슬러리가 잔류하고 있다고 생각한다.

도 25f는 Si 피크와 N 피크로부터 그들의 존재비를 구하고, N량을 추정한 값을 나타낸다. 암모니아 플라즈마 처리와 질소 플라즈마 처리에서는 거의 동등한 질화가 이루어지고 있다고 생각한다.

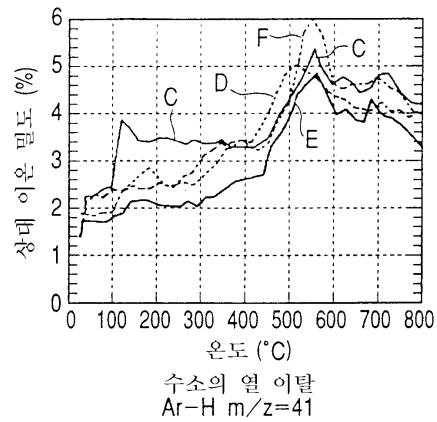

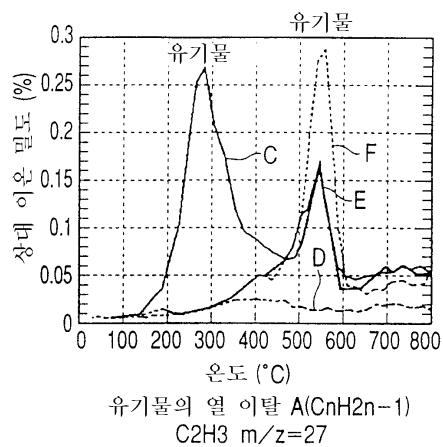

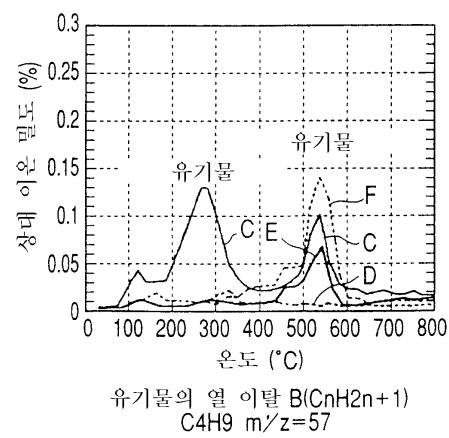

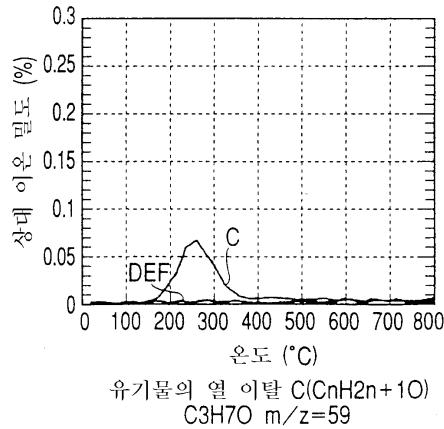

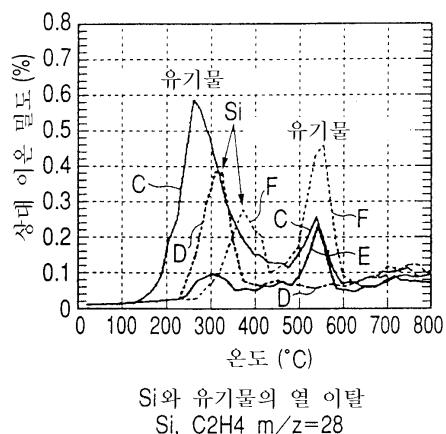

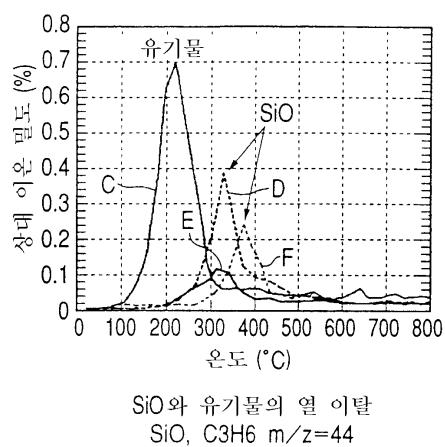

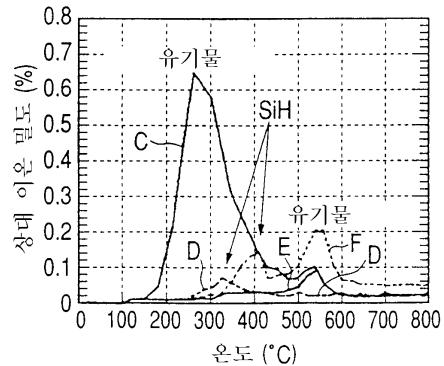

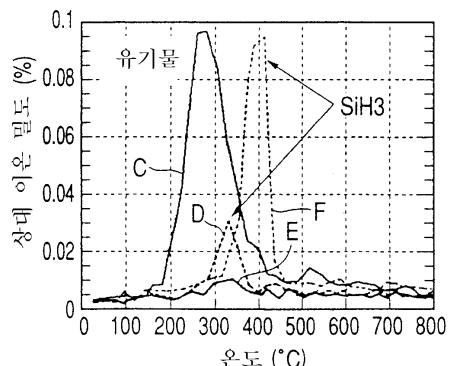

도 26a, 도 26b, 도 26c, 도 26d는 각각 질량수 41(Ar-H), 질량수 27(C<sub>2</sub>H<sub>3</sub>), 질량수 57(C<sub>4</sub>H<sub>9</sub>), 질량수 59(C<sub>3</sub>H<sub>7</sub>O)를 측정한 그래프이다. 또한, 도 27a, 도 27b, 도 27c, 도 27d는 각각 질량수 28(Si, C<sub>2</sub>H<sub>4</sub>), 질량수 44(SiO, C<sub>3</sub>H<sub>6</sub>), 질량수 29(SiH, C<sub>2</sub>H<sub>5</sub>), 질량수 31(SiH<sub>3</sub>)을 측정한 그래프이다.

도 26a로부터, 플라즈마 처리에 의한 수소의 이탈량의 차이는 거의 없지만, 수소 플라즈마 처리(프로파일 D)의 이탈 온도가 다른 경우(560°C)와 비교하여 520°C로 낮은 것을 알 수 있다.

도 26a, 도 26b, 도 26c에서부터 각 프로세스와 유기물의 이탈이 나타난다. 한편, 도 27a ~ 도 27d에서부터, 유기물의 이탈 이외의 피크의 존재가 나타난다. 즉, 300 ~ 400°C에서의 피크는 각각, Si, SiO, SiH, SiH<sub>3</sub>이라고 생각된다. 각 도면을 비교하면, 수소, 암모니아, 질소의 각 플라즈마 처리(3)에서 SiO의 이탈은 나타나지만, 암모니아 플라즈마 처리에서는 SiH, SiH<sub>3</sub>의 이탈은 거의 관찰되지 않는다. 즉, 암모니아 플라즈마 처리에서는 Si-O-N이 형성되며, 비교적 낮은 에너지로 용이하게 이탈한다. 또한, 이탈 분리에 필요한 에너지는 질소 플라즈마 처리의 경우가 가장 높고, 수소 플라즈마 처리와 암모니아 플라즈마 처리에서는 거의 동일하다고 할 수 있다.

이들의 결과로부터, 실리콘 산화막 표면의 댕글링 결합(dangling bond)의 원인이 되는 Si-OH나 Si-O-는 암모니아 플라즈마 처리에 의해, 약한 결합인 Si-O-N로 종단된다고 생각된다. 암모니아 플라즈마 처리 후의 실리콘 질화막의 성막에서 극히 표면의 Si-O-N이 이탈하여, 벌크의 Si-O 결합과 실리콘 질화막의 Si-N이 강고하게 결합하고 연속적인 계면을 형성한다. 이것이 계면의 밀착성을 향상하는 기구라고 생각된다. 한편, 암모니아 플라즈마 처리를 행하지 않은 경우에는 해당 초 Si-OH 결합이 많은 실리콘 산화막의 표면과 실리콘 질화막의 원료 가스인 암모니아가 축합 반응하고, 댕글링 결합의 원인인 Si-O- 결합이 다수 발생하고 있다고 생각된다. 실리콘 산화막과 실리콘 질화막과의 계면에 다수의 댕글링 결합이 존재하면, 그곳에는 누설 패스가 형성되어 배선간의 누설 전류, 나아가서는 절연 파괴의 원인이 된다고 생각된다.

이상의 분석 결과로부터, 암모니아 플라즈마 처리에 의해 산화된 Cu 배선의 표면은 환원되어 Cu 단원소로 변환되고, 이온화된 Cu보다도 전기적으로 안정된 상태가 되며 또한 실리콘 산화막/ 실리콘 질화막 계면은 연속적인 강고한 막이 되기 때문에 누설 전류가 감소하고 TDDB 수명도 대폭 향상한다고 생각된다.

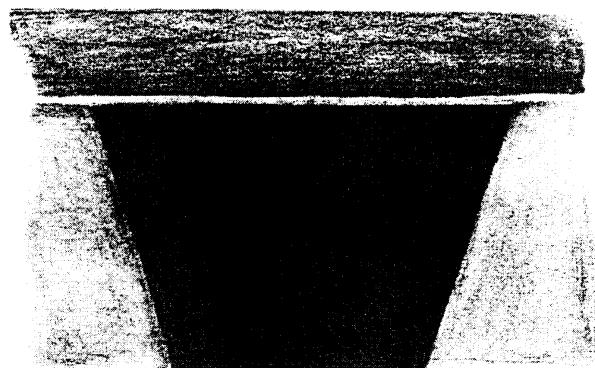

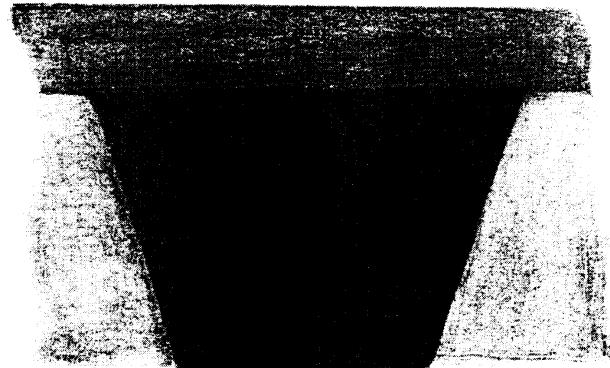

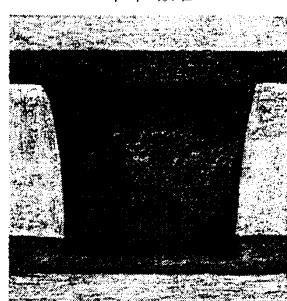

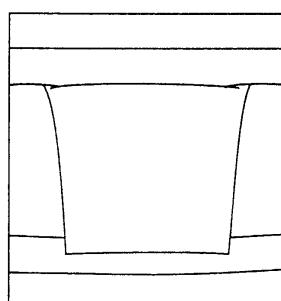

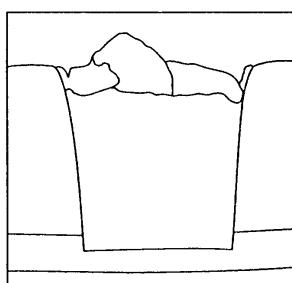

도 28은 암모니아 플라즈마 처리를 행한 본 실시 형태의 경우의 배선층과 실리콘 질화막(캡막)과의 계면을 관찰한 TEM 사진이다. 한편 도 29는 암모니아 플라즈마 처리를 행하지 않은 경우의 계면의 TEM 사진이다. 도 28에서는 계면에 얇은 피막의 존재를 확인할 수 있다(화살표로 나타내었음). 이 얇은 피막이 상기한 질화층이라고 생각된다. 한편으로 도 29에서는 그와 같은 피막은 확인할 수 없었다.

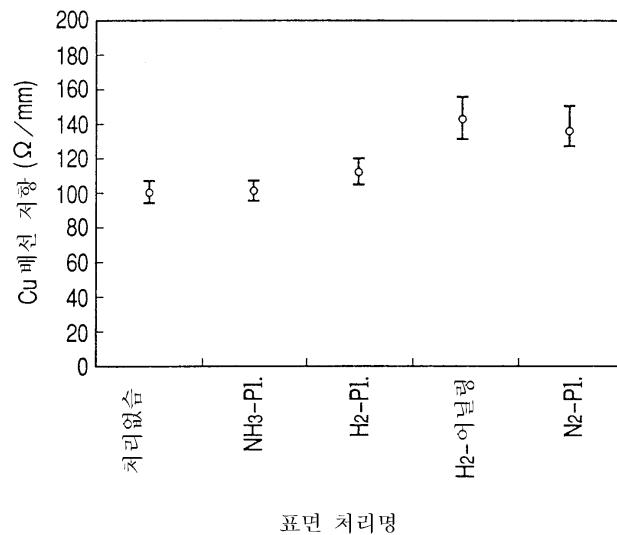

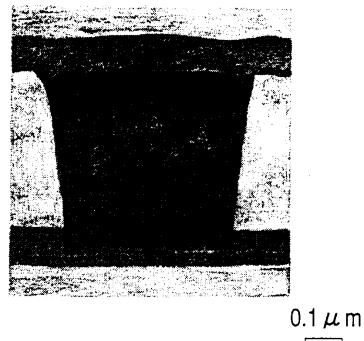

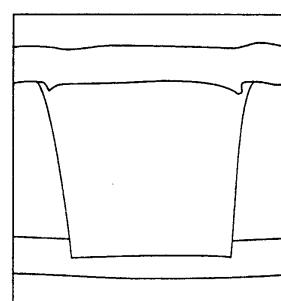

또한, 본 실시 형태에서는 Cu 배선의 저항을 저감할 수 있다. 도 30은 각 종 처리를 행한 경우의 배선 저항의 측정 결과이다. 처리를 하지 않은 것(플라즈마 처리없음)과 암모니아 플라즈마 처리를 한 경우에 있어서는 다른 경우(수소 플라즈마 처리, 수소 어닐링, 질소 플라즈마 처리)와 비교하여 상당히 낮은 값으로 되어 있다. 도 31 및 도 32는 이들 각 처리를 실시한 경우의 Cu 배선과 캡막(실리콘 질화막)과의 계면을 관찰한 TEM 사진이다. 처리를 하지 않은 것과 암모니아 플라즈마 처리를 한 경우(도 31)에는 계면에 특이한 것은 나타나지 않았지만, 수소 어닐링, 질소 플라즈마 처리의 경우(도 32)에서는 계면에 구리의 실리사이드(CuSi)층이 형성되고 있다. 이 실리사이드층이 저항 증가의 원인이라고 생각된다. 이러한 실리사이드층은 실리콘 질화막의 형성 시의 실란 가스와의 반응으로 형성되지만, 암모니아 처리를 행하고 있는 경우에는 Cu 표면에 극히 얇은 질화막이 형성되어 있고, 이 질화막이 실리사이드화의 블로킹층(blocking layer)으로서 기능하고 있다고 생각된다. 한편, 수소 어닐링 등 단순히 구리 표면을 환원하는 것만으로는 활성인 Cu 표면이 노출하여 실리콘과의 반응이 촉진되기 때문에, 실리사이드층이 생성되기 쉽다고 생각된다. 또, 수소 플라즈마 처리(도 32c, 도 32f)인 경우에는 계면에 어떠한 생성물이 보인다. 다만, 대부분의 경우에는 그와 같은 생성물이 형성되지 않은 경우도 있고 수소 플라즈마 처리의 경우에는 실리사이드화의 정도는 작다고 생각된다. 또, 도 31 및 도 32에서 TEM 사진(도 31a 및 도 31b, 도 32a ~ 도 32c) 외에 각각 대응하는 트레이스 도면(도 31c 및 도 31d, 도 32d ~ 도 32f)을 참고하기 위해서 각 TEM 사진 순서대로 나타내었다.

상기한 분석 결과로부터, TDDB 수명의 열화 기구로서 이하와 같은 모델이 생각된다. 즉, 본 실시 형태의 암모니아 처리를 실시하지 않은 경우에는 Cu 배선의 표면 부분에 산화 구리(CuO)가 형성되고 또한 캡막[실리콘 질화막(47)]이 형성될 때 구리 실리사이드가 형성된다. 이러한 산화 구리 혹은 구리 실리사이드는 순수한 구리와 비교하여 이온화되기 쉽고, 이러한 이온화된 구리는 배선간의 전계에 의해 드리프트되어 배선간의 절연막에 확산된다. 또한, 구리 배선을 매립하여 형성하는 절연막[실리콘 산화막(39)]과 캡막[실리콘 질화막(47)]과의 계면은 본 실시 형태의 암모니아 처리를 실시하지 않은 경우에는 댕글링 결합이 많이 형성되고, 불연속이며, 밀착성도 부족하다. 이러한 댕글링 결합의 존재는 구리 이온의 확산을 조장하는 작용을 가지며, 구리 이온은 계면에 따라서 드리프트되어 확산한다. 즉, 배선 간의 상기 계면에 누설 패스가 형성된다. 누설 패스를 흐르는 누설 전류는 장시간의 누설 작용과 전류에 의한 열 스트레스도 더해져서 그 후 가속도적으로 전류 치가 증가하여 파괴에 이른다(TDDB 수명).

이것에 대하여, 본 실시 형태에서는 Cu 배선(46a ~ 46e)의 표면에 암모니아 처리를 실시하기 때문에, Cu 배선(46a ~ 46e) 표면의 산화층은 환원되어 소실하고 Cu 배선(46a ~ 46e)의 표면에 얇은 질화층이 형성되기 때문에 실리콘 질화막(47)의 형성 시에 구리 실리사이드가 형성되지 않는다. 이 때문에, 누설 및 절연 파괴의 원인이 되는 구리 이온을 지배적으로 공급하는 원인 물질이 생기지 않게 할 수도 있다.

또한, 본 실시 형태에서는 실리콘 산화막(39)의 표면에 암모니아 처리를 실시하기 때문에, 실리콘 질화막(47)과의 접속을 연속적으로 하여 댕글링 결합의 밀도를 저감하고 누설 패스의 형성을 억제할 수 있다. 즉, TDDB 수명 저하의 원인이 되는 구리 이온의 발생을 억제하고 또한 구리의 확산을 억제할 수 있도록 실리콘 산화막(39)과 실리콘 질화막(47)과의 접합 계면을 형성할 수 있다. 이에 따라 TDDB 수명을 향상할 수 있는 것이다.

또, 상기한 해석으로부터 수소 플라즈마 처리에서도 TDDB 수명이 향상될 수 있다고 생각된다. 즉, 수소 플라즈마 처리에 의해 Cu 표면은 환원되며, Si-O 등의 댕글링 결합이나 그 원인이 되는 Si-OH가 Si-H로 종단된다. 그리고, 실리콘 질화막의 형성 시에 결합이 약한 표면의 Si-H가 이탈하여 Si-N으로 치환된다. 이에 따라, 연속적인 실리콘 산화막과 실리콘 질화막의 계면이 형성된다. 다만 배선 저항은 상기한 바와 같이 증가한다. 도 33은 수소 플라즈마 처리를 행한 경우의 TDDB 수명의 데이터를 나타낸 그래프이다. 참고로 라인 Ref(처리 없음)과 라인 A(암모니아 플라즈마 처리)를 나타내었다. 수소 플라즈마 처리(라인 C)에서는 특히, TDDB 수명이 눈에 띄게 향상하는 것을 알 수 있다. 수소 플라즈마 처리의 경우에는 플라즈마 손상이 경감되는 것이 기대되므로, 캡막으로서 실리콘 질화막 대신에 다른 재료로써 Cu와의 반응 생성물을 만들지 않는 것과 같은 재료를 적용할 수 있을 때는 매우 유효하다. 또, 질소 플라즈마 처리(라인 D)에서는 TDDB 수명이 오히려 저하한다. 도 26, 도 27로부터도 알 수 있듯이, 질소 플라즈마 처리에 의해서 오히려 유기물의 부착이 증가하고 있는 것에 기인한다고 생각된다.

본 실시 형태에서는 또한 Cu 배선(46a ~ 46e) 및 실리콘 산화막(39)과 캡막(47)과의 접착성이 향상되고 있기 때문에, 계면의 박리 강도가 증가하고, 마진이 커지는 효과도 있다.

또, 암모니아, 수소의 단일 가스에 한정되지 않고, 질소, 아르곤, 헬륨 등의 불활성 가스와의 혼합 가스 플라즈마로 처리해도 된다. 즉, 암모니아와 수소, 질소, 아르곤 또는 헬륨과의 혼합 가스 혹은 수소와 암모니아, 질소, 아르곤 또는 헬륨과의 혼합 가스라도 좋다. 또한, 이들 가스로부터 선택된 3원계, 4원계 등 다원계의 혼합 가스라도 좋다. 이 때, 수소, 암모니아 혹은 수소와 암모니아의 합은 총 유량(질량 유량)에 대하여 5% 이상 혼합되어 있는 것이 필요하다.

### <실시 형태 2>

본 발명의 실시 형태 2인 CMOS-LSI의 제조 방법을 도 34 ~ 도 43을 이용하여 공정 순으로 설명한다.

본 실시 형태의 제조 방법은 실시 형태 1에서의 도 1 ~ 도 8까지의 공정에 대해서는 마찬가지이다. 이하 CMP 공정 이후의 공정을 설명한다.

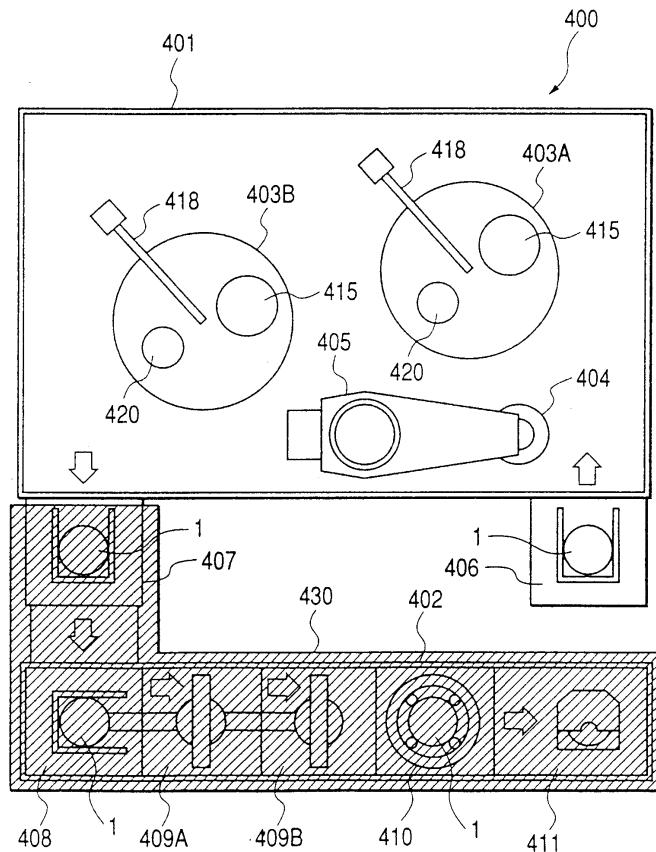

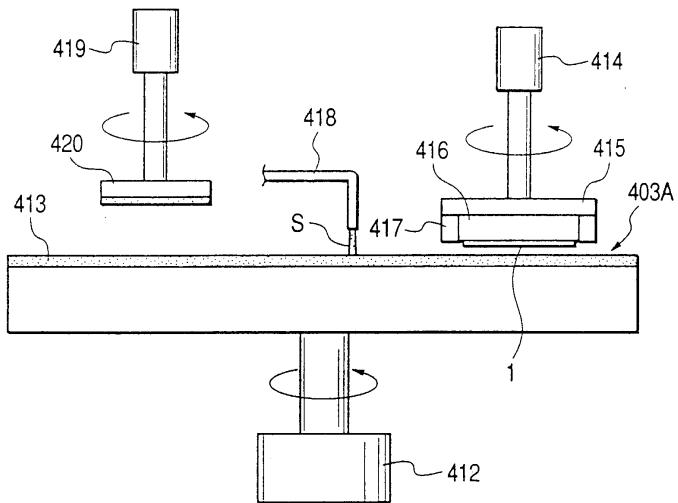

도 34는 매립 Cu 배선의 형성에 이용하는 CMP 장치의 전체 구성의 일례를 나타낸 개략도이다.

도시한 바와 같이, CMP 장치(400)는 연마 처리부(401)와 그 후단에 설치된 후세정부(402)에 따라서 구성되어 있다. 연마 처리부(401)에는 웨이퍼(기판 ; 1)의 연마 처리를 행하는 2대의 정반(fixed disk)[제1 정반(403A), 제2 정반(403B)], 연마 처리가 끝난 기판(1)을 예비 세정하고 그 표면에 방식 처리(corrosion treatment)를 실시하는 크린·스테이션(clean station)(404), 기판(1)을 로더(406)와 제1 정반(403A)과 제2 정반(403B)과 크린·스테이션(404)과 언로더(407) 간에 이동시키는 회전 아암(rotary arm)(405) 등이 설치되어 있다.

연마 처리부(401)의 후단에는 예비 세정이 끝난 기판(1)의 표면을 스크럽 세정하는 후세정부(402)가 설치되어 있다. 후세정부(402)에는 로더(408), 제1 세정부(409A), 제2 세정부(409B), 스픈 드라이어(410), 언로더(411) 등이 설치되어 있다. 또한, 후세정부(402)는 세정 중의 기판(1)의 표면에 광이 조사하는 것을 막기 위해서 전체가 차광벽(430)으로 둘러싸이고 내부가 180룩스, 바람직하게는 100룩스 이하의 암실 상태로 되어 있다. 이것은 표면에 연마액이 부착한 기판(1)에 습윤 상태에서 광이 조사되면, 실리콘의 광기전력에 의해서 pn 접합에 단락 전류가 흐르고, pn 접합의 p측(+측)에 접속된 Cu 배선의 표면으로부터 Cu 이온이 해리하여 배선 부식을 야기하기 때문이다.

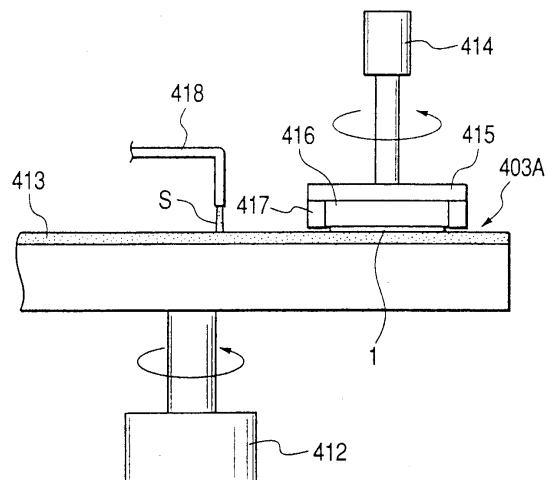

도 35에 도시한 바와 같이, 제1 정반(403A)은 그 하부에 설치된 구동 기구(412)에 의해서 수평면 내에서 회전 구동한다. 또한, 제1 정반(403A)의 상면에는 다수의 기공을 가지는 폴리우레탄 등의 합성 수지를 균일하게 접착하여 형성한 연마 패드(413)가 부착되어 있다. 제1 정반(403A)의 상측에는 구동 기구(414)에 의해서 상하 이동 및 수평면 내에서 회전 구동하는 웨이퍼 캐리어(wafer carrier)(415)가 설치되어 있다. 기판(1)은 이 웨이퍼 캐리어(415)의 하단부에 설치된 웨이퍼 척(chuck)(416) 및 리테이너링(retainer ring)(417)에 의해서, 그 주요면(피연마면)을 하향으로 하여 유지되고, 소정의 하중으로 연마 패드(413)에 압박된다. 연마 패드(413)의 표면과 기판(1)의 피연마면 간에는 슬러리 공급관(418)을 통하여 슬러리(연마액) S가 공급되며, 기판(1)의 피연마면이 화학적, 기계적으로 연마된다. 또한, 제1 정반(403A)의 상측에는 구동 기구(419)에 의해서 상하 이동 및 수평면 내에서 회전 구동하는 드레서(dresser)(420)가 설치되어 있다. 드레서(420)의 하단부에는 다이아몬드 입자를 전착(electrodeposited)한 기재가 부착되어 있고, 연마 패드(413)의 표면은 연마 지립에 의한 눈메움(clogging)을 막기 위해서, 이 기재에 의해서 정기적으로 절삭된다. 또, 제2 정반(403B)은 2개의 슬러리 공급관(418a, 418b)이 설치되어 있는 점을 제외하고, 제1 정반(403A)와 거의 마찬가지의 구성으로 되어 있다.

상기 CMP 장치(400)를 사용하여 Cu 배선을 형성하기 위해서는 로더(406)에 수용된 기판(1)을 회전 아암(405)을 사용하여 연마 처리부(401)에 반입하고, 우선 도 36에 도시한 바와 같이, 제1 정반(403A) 상에서 지립을 포함하지 않은 슬러리를 사용한 화학 기계 연마(지립 프리 화학 기계 연마 ; 제1 단계의 CMP)를 행하여 상기 배선홈(40 ~ 44)의 외부의 Cu막(46)을 제거한다(도 37).

여기서 지립 프리 화학 기계 연마란 알루미나, 실리카 등의 분말로 이루어지는 지립의 함유량이 0.5% 중량 미만의 연마액(슬러리)을 사용한 화학 기계 연마를 의미하고, 연마액으로서는 특히 지립의 함유량이 0.1 중량% 미만인 것이 바람직하고, 0.01 중량% 미만인 것은 보다 바람직하다.

또한, 연마액으로서는 Cu의 부식 영역에 속하도록 그 pH가 조정된 것이 사용되고 또한 TiN막(45 ; 배리어층)에 대한 Cu막(46)의 연마 선택비가 적어도 5이상이 되도록 그 조성이 조정된 것이 사용된다. 이러한 연마액으로서, 산화제와 유기산을 포함한 슬러리를 예시할 수 있다. 산화제로서는 과산화수소, 수산화 암모늄, 질산 암모늄, 염화 암모늄 등을 예시할 수 있고, 유기산으로서는 구연산, 말론산, 푸마르산, 말산(malic acid), 아디핀산, 안식향산, 프탈산, 타르타르산, 쟁산, 호박산(succinuc acid) 등을 예시할 수 있다. 이들 중에서, 과산화수소는 금속 성분을 포함하지 않고 또한 강산이 아니기 때문에,

연마액에 이용하여 적합한 산화제이다. 또한, 구연산은 식품 첨가물로서도 일반적으로 사용되고 있고, 독성이 낮으며 폐액(waste liquid)으로서의 해도 낮고, 냄새도 없으며 물에서의 용해도도 높기 때문에, 연마액에 이용하기 적합한 유기산이다. 본 실시 형태에서는 예를 들면, 순수(pure water)에 5체적%의 과산화 수소와 0.03 중량%의 구연산을 더하여, 지립의 함유량을 0.01 중량% 미만으로 한 연마액을 사용한다.

상기 연마액으로 화학 기계 연마를 행하면, 우선 Cu 표면이 산화제에 의해서 산화되며, 표면에 얇은 산화층이 형성된다. 다음에 산화물을 수용성화하는 물질이 공급되면 상기 산화층이 수용액이 되어 용출되고, 상기 산화층의 두께가 감소한다. 산화층이 얇아진 부분은 재차 산화성 물질에 노출되며 산화층의 두께가 증가하여, 이 반응을 반복하여 화학 기계 연마가 진행된다. 또, 이러한 지립 프리의 연마액을 사용한 화학 기계 연마에 대해서는 본원 발명자 등에 의한 일본 특원평 9-299937호 및 특원평 10-317233호에 자세하게 기재되어 있다.

연마의 조건은 일례로서 하중(load)=250g/cm<sup>2</sup>, 웨이퍼 캐리어 회전수=30rpm, 정반 회전수=25rpm, 슬러리 유량=150cc/min으로 하고, 연마 패드는 미국 로델(Rodel)사의 경질 패드(IC1400)를 사용한다. 연마의 종점은 Cu막(46)이 제거되어 하지의 TiN막(45)이 노출한 시점으로 하고, 종점의 검출은 연마 대상이 Cu막(46)으로부터 TiN막(45)이 되었을 때로 변화하는 정반 또는 웨이퍼 캐리어의 회전 토크 신호 강도를 검출함으로써 행한다. 또한, 연마 패드의 일부에 구멍을 뚫어서, 웨이퍼 표면으로부터의 광 반사 스펙트럼 변화에 기초하여 종점을 검출하거나 슬러리의 광학적 스펙트럼 변화에 기초하여 종점을 검출하여도 된다.

도 37에 도시한 바와 같이, 상기한 지립 프리 화학 기계 연마를 행함으로써 배선홈(40 ~ 44)의 외부의 Cu막(46)은 거의 제거되어 하층의 TiN막(45)이 노출하지만, 도 38a, 도 38b에 확대하여 나타낸 바와 같이, 하지 단차에 기인하여 생긴 TiN막(45)의 오목부(화살표로 나타낸다) 등에는 이 연마에서는 제거할 수 없던 Cu막(46)이 잔존한다.

다음에, 배선홈(40 ~ 44)의 외부의 TiN막(45)과 그 상측면에 국소적으로 남은 Cu막(46)을 제거하기 위해서, 기판(1)을 제1 정반(403A)에서부터 제2 정반(403B)으로 옮겨, 지립을 포함하는 연마액(슬러리)을 사용한 화학 기계 연마(유지립 화학 기계 연마; 제2 단계의 CMP)를 행한다. 여기에서 유지립 화학 기계 연마란 알루미나, 실리카 등의 분말로 이루어지는 지립의 함유량이 0.5 중량% 이상의 연마액을 사용한 화학 기계 연마를 의미한다. 본 실시 형태에서는 연마액으로서 순수에 5체적%의 과산화 수소, 0.03 중량%의 구연산 및 0.5 중량%의 지립을 혼합한 것을 사용하지만, 이에 한정되는 것은 아니다. 이 연마액은 상기한 슬러리 공급관(418a)을 통하여 제2 정반(403B)의 연마 패드(413)에 공급된다.

또한, 이 유지립 화학 기계 연마에서는 TiN막(45)의 상면에 국소적으로 남은 Cu막(46)을 제거한 후, 배선홈(40 ~ 44)의 외부의 TiN막(45)을 제거한다. 그래서, TiN막(45; 배리어층)에 대한 Cu막(46)의 연마 선택비가 상기 지립 프리 화학 기계 연마보다도 낮은 조건, 예를 들면 선택비 3 이하의 조건으로 연마를 행하여 배선홈(40 ~ 44)의 내부의 Cu막(46)의 표면이 연마되는 것을 억제한다.

연마의 조건은, 일례로서 하중=120g/cm<sup>2</sup>, 웨이퍼 캐리어 회전수=30rpm, 정반 회전수=25rpm, 슬러리 유량=150cc/min으로 하고, 연마 패드는 로델사의 IC1400을 사용한다. 연마량은 TiN막(45)의 막 두께 상당분으로 해서, 연마의 종점은 TiN막(45)의 막 두께 및 연마 속도로부터 산출한 시간에 의해서 제어된다.

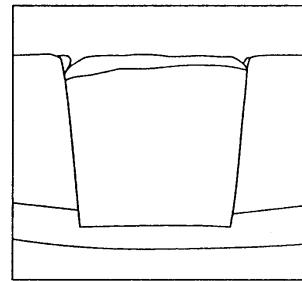

도 39에 도시한 바와 같이, 상기한 유지립 화학 기계 연마를 행함으로써, 배선홈(40 ~ 44)의 외부의 TiN막(45)은 거의 제거되어 하층의 실리콘 산화막(39)이 노출되지만, 도 40a, 도 40b로 확대하여 도시한 바와 같이, 하지 단차에 기인하여 생긴 실리콘 산화막(39)의 오목부(화살표로 나타낸다) 등에는 상기한 연마로 제거할 수 없었던 TiN막(45)이 잔존한다.

다음에, 배선홈(40 ~ 44)의 내부의 Cu막(46)의 연마를 가능한 한 억제하면서 배선홈(40 ~ 44)의 외부 실리콘 산화막(39) 상에 국소적으로 남은 TiN막(45; 배리어층)을 제거하기 위한 선택적 화학 기계 연마(제3 단계의 CMP)를 행한다. 이 선택적 화학 기계 연마는 Cu막(46)에 대한 TiN막(45)의 연마 선택비가 적어도 5 이상이 되는 조건으로 행한다. 또한, 이 화학 기계 연마는 Cu막(46)의 연마 속도에 대한 실리콘 산화막(39)의 연마 속도의 비가 1보다도 커지는 조건으로 행한다.

상기 선택적 화학 기계 연마를 행하기 위해서는 일반적으로 상기 유지립 화학 기계 연마로 사용한 것과 같은 0.5% 중량 이상의 지립을 함유하는 연마액에 방식제를 첨가한 것을 사용한다. 방식제란, Cu막(46)의 표면에 내식성의 보호막을 형성함으로써 연마의 진행을 저지 또는 억제하는 약제를 말하며, 벤조트리아졸(BTA), BTA 카르본산 등의 BTA 유도체, 도데실 메르캅탄(dodecyl mercaptan), 트리아졸(triazole), 톨릴트리아졸(tolyltriazole) 등이 사용되지만, 특히 BTA를 사용한 경우에 안정된 보호막을 형성할 수 있다.

방식제로서 BTA를 사용하는 경우, 그 농도는 슬러리의 종류에도 따르지만, 통상은 0.001 ~ 1중량%, 보다 바람직하게는 0.01 ~ 1중량%, 더 바람직하게는 0.1 ~ 1 중량%(3 단계)의 첨가로 충분한 효과가 얻어진다. 본 실시 형태에서는 연마액으로서 상기 제2 단계의 유지립 화학 기계 연마로 사용한 연마액에 방식제로서 0.1 중량%의 BTA를 혼합한 것을 사용하지만, 이에 한정되지는 않는다. 또한, 방식제의 첨가에 의한 연마 속도의 저하를 피하기 위해서, 폴리아크릴산(polyacrylic acid), 폴리메타크릴산(polymethacrylic acid), 이들의 암모늄염 또는 에틸렌디아민사초산(EDTA) 등을 필요에 따라서 첨가해도 된다. 또, 이러한 방식제를 포함하는 슬러리를 사용한 화학 기계 연마에 대해서는 본원 발명자 등에 따른 특원평 10-209857호, 특원평 9-299937호 및 특원평 10-317233호에 자세하게 기재되어 있다.

이 선택적 화학 기계 연마(제3 단계의 CMP)는 상기한 유지립 화학 기계 연마(제2 단계의 CMP)가 종료한 후, 이어서 제2 정반(403B) 상에서 행해진다. 방식제를 첨가한 연마액은 상기한 슬러리 공급관(418b)을 통하여 연마 패드(413)의 표면에 공급된다. 연마의 조건은 일례로서 하중=120g/cm<sup>2</sup>, 웨이퍼 캐리어 회전수=30rpm, 정반 회전수=25rpm, 슬러리 유량=190cc/min으로 한다.

도 41 및 도 42a, 도 42b에 도시한 바와 같이, 상기한 선택적 화학 기계 연마를 행함으로써, 배선홈(40 ~ 44)의 외부의 TiN막(45)이 전부 제거되며 배선홈(40 ~ 44)의 내부에 매립 Cu 배선(46a ~ 46e)가 형성된다.

매립 Cu 배선(46a ~ 46e)의 형성이 완료한 상기 기판(1)의 표면에는 지립 등의 입자나 Cu 산화물 등의 금속 입자를 포함한 슬러리 잔사가 부착되어 있다. 그래서 이 슬러리 잔사를 제거하기 위해서, 우선 상기 도 34에 도시하는 크린·스테이션(404)에서 BTA를 포함하는 순수로 기판(1)을 세정한다. 이 때, 세정액에 800kHz 이상의 고주파 진동을 가하여 기판(1)의 표면에서부터 슬러리 잔사를 유리시키는 메가소닉 세정을 병용해도 된다. 다음에, 표면의 건조를 막기 위해서 기판(1)을 습윤 상태로 유지한 상태에서 연마 처리부(401)로부터 후세정부(402)에 반송하고, 제1 세정부(409A)에서 0.1 중량%의 NH<sub>4</sub>OH를 포함하는 세정액을 이용한 스크립 세정을 행하고, 계속해서 제2 세정부(409B)에서 순수를 이용한 스크립 세정을 행한다. 상기한 바와 같이, 후세정부(402)는 세정 중의 기판(1)의 표면에 광이 조사하는 것에 기인하여 Cu 배선(46a ~ 46e)에 부식이 발생하는 것을 막기 위해서 전체가 차광벽(430)으로 덮어지고 있다.

상기 스크립 세정(후세정)이 완료된 기판(1)은 스펀 드라이어(410)로 건조된 후, 다음 공정으로 반송된다.

그 후의 공정은 실시 형태 1과 마찬가지이다. 도 43은 상술한 Cu 배선(46a ~ 46e)의 형성 프로세스의 전체 플로우도이다.

본 실시 형태에 따르면, 실시 형태 1의 경우로부터 또한 TDDB 수명을 향상할 수 있다. 도 44는 본 실시 형태의 경우의 TDDB 수명을 나타낸 그래프이다. 본 실시 형태의 경우의 데이터는 라인 E에서 나타내고 있다. 참고하기 위해서, 처리없음(라인 Ref)과 유지립의 화학 기계 연마의 경우(실시 형태 1)의 데이터(라인 A)를 동시에 나타내고 있다. 또, 암모니아 플라즈마 처리를 행하지 않고, 지립 프리의 화학 기계 연마만을 행한 것뿐이라도 라인 F로 나타낸 바와 같이 TDDB 특성이 개선된다. 이와 같이 지립 프리의 경우에 TDDB 수명이 향상하는 것은 실리콘 산화막에 주어지는 손상을 저감할 수 있기 때문이라고 생각된다. 유지립인 경우, 슬러리에는 2 ~ 3μm의 입자 지름(2차 입자 지름)의 지립(알루미나 등)이 포함된다. 이 지립에 의해 마이크로 스크래치가 생기고, 실리콘 산화막(39)의 표면에 손상을 끼친다. 그러나, 지립 프리인 경우에는 슬러리에 지립이 포함되지 않거나 혹은 포함되어 있어도 극히 소수이기 때문에 손상을 대폭 경감할 수 있다. 이 때문에, TDDB 특성이 개선된 것이라고 생각된다.

또, 다음의 실시 형태에서 설명하는 산 처리(HF 처리)를 조합하면, 또한 TDDB 특성이 개선한다(라인 G). 산 처리는 CMP 후세정 후, 또한 산성 수용액(예를 들면 HF 수용액)으로 기판(1)을 처리하고, 그 후 암모니아 플라즈마 처리를 행하는 것이다. 산 처리에 의해 표면의 손상층이 제거되어 계면의 밀착성이 향상하고 TDDB 수명이 개선된 것이라고 생각된다.

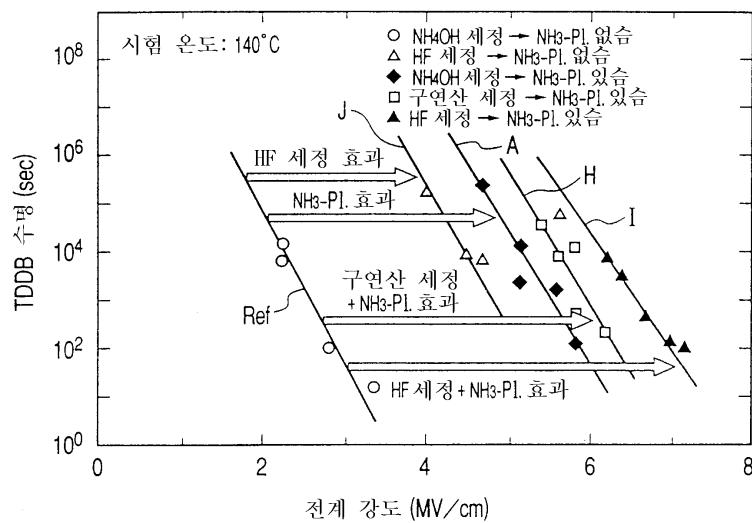

### <실시 형태 3>

도 45는 Cu 배선(46a ~ 46e)의 형성 프로세스의 전체 플로우도이다. 도 45에 도시한 바와 같이, HF 또는 구연산에 의한 세정 공정을 삽입한 것 이외는 실시 형태 1과 마찬가지이다.

HF 세정은 예를 들면, 브러시 스크립 세정을 이용하여 HF 농도를 0.5%, 세정 시간을 20초의 조건을 선택할 수 있다.

혹은 HF 세정을 대신하여 구연산 세정을 이용해도 된다. 구연산 세정은 예를 들면 브러시 스크립 세정을 이용하여 구연산 농도를 5%, 세정 시간을 45초의 조건으로 선택할 수 있다.

이와 같이 HF 또는 구연산 세정을 이용함으로써, CMP 등으로 생긴 표면의 손상층을 제거할 수 있다. 이에 따라 TDDB 수명을 향상할 수 있다. 도 46은 본 실시 형태의 경우 TDDB 수명을 나타낸 그래프이다. 본 실시 형태의 경우의 구연산을 적용한 데이터는 라인 H, HF 세정을 적용한 데이터는 라인 I로 나타내고 있다. 참고하기 위해서 처리를 하지 않은 것(라인 Ref)과 실시 형태 1의 데이터(라인 A)를 동시에 나타내고 있다. 또, 암모니아 플라즈마 처리를 행하지 않고, HF 세정만을 행한 것뿐이라도 라인 J로 나타낸 바와 같이 TDDB 특성이 개선된다. 이것은 손상층의 제거에 의해 계면의 특성을 향상할 수 있기 때문이라고 생각된다.

#### <실시 형태 4>

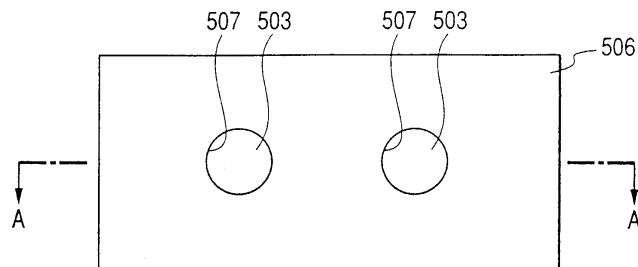

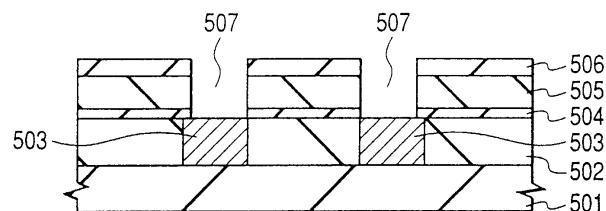

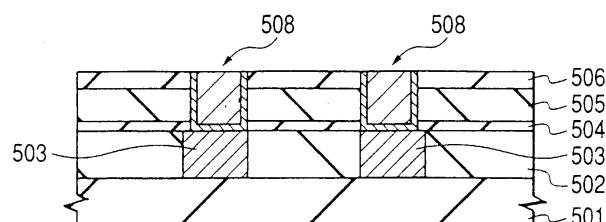

도 47 ~ 도 49는 본 발명의 실시 형태 4인 반도체 집적 회로 장치의 제조 방법을 나타낸 평면도 및 단면도이다. 도 47 ~ 도 49에서는 배선부만 나타내고 있다.

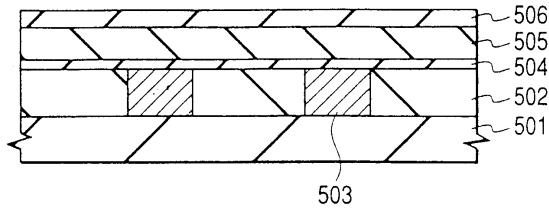

도 47에 도시한 바와 같이, 절연막(501) 상에 배선 형성용 절연막(502)을 형성하고, 이 절연막(502)에 매립하여 구리 배선(503)을 형성한다. 층배선(503)의 형성 방법은 실시 형태 1 ~ 3과 마찬가지이다.

또한, 실리콘 질화막(504), 저유전률의 실리콘 산화막(505) 및 TEOS를 원료 가스에 이용하여 플라즈마 CVD법에 의해 형성한 실리콘 산화막(TEOS 산화막 ; 506)을 형성한다.

저유전률의 실리콘 산화막(505)은 예를 들면, 수소 실세스퀴옥산(Hydrogen Silsesqui oxane)을 원료로 하는 무기계 SOG막, 테트라 알콕시 실란(tetra alkoxy silane)과 알킬 알콕시 실란(alkyl alkoxy silane)을 원료로 하는 유기계 SOG막과 같은 도포형 절연막이나 플라즈마 CVD법으로 성막하는 플루오로카본(fluorocarbon) 폴리머막 등, 비유전률( $\epsilon$ )이 3.0 이하의 산화 실리콘계 절연막에 의해서 구성한다. 이러한 저유전률의 실리콘 산화막을 이용함으로써 배선간 기생 용량을 저감하고, 배선 지연의 문제를 회피할 수 있다.

다음에, 도 48a에 도시한 바와 같은 패턴으로, 도 48b에 도시한 바와 같이, 접속 구멍(connecting hole)(507)을 개구한다. 접속 구멍(507)의 개구에는 포토리소그래피와 에칭을 이용한다. 그런데, 저유전률의 실리콘 산화막(505)은 표면이 거친 막 구조를 가지며, Si-OH 결합을 많이 갖는다. 이 때문에 그 상층에 형성하는 막의 막질이나 계면 상태가 좋지 않다는 것이 경험적으로 판명되어 있다. 또한, 다음 공정에서 설명하는 배리어막(질화 티탄)을 그대로 미처리로 성막하면 TDDB 특성이 좋지 않은 것도 경험적으로 판명되고 있다. 그래서, 다음에 실시 형태 1에서 설명한 암모니아 플라즈마 처리를 접속 구멍(507) 내부의 실리콘 산화막(505) 노출부에 실시한다. 이에 따라, 표면의 Si-OH 결합이 개질되어 실시 형태 1에서 설명한 바와 같이 Si-O-N 결합으로 전환된다.

다음에, 도 49에 도시한 바와 같이, 접속 구멍(507) 내에 질화 티탄 및 텅스텐으로 이루어지는 플러그(508)를 형성한다. 이 질화 티탄의 퇴적 시에, 실시 형태 1과 마찬가지로 Si-O-N 결합이 이탈하여 질화 티탄과 저유전률의 실리콘 산화막(505)과의 계면이 개선되어 접착성이 향상된다.

또, 이러한 접속 구멍 내의 플라즈마 처리는 배선홈에도 적용할 수 있는 것은 물론이다.

또한, 암모니아 플라즈마 처리 대신에 수소 플라즈마 처리, 질소, 아르곤, 헬륨 등이 혼합된 플라즈마 처리도 된다.

또, 접속 구멍(507)의 개구 후에 포토레지스트막을 제거하기 위한 애싱 공정에 있어서, 접속 구멍(507) 바닥부의 배선(503)의 표면이 산화되는 경우가 있다. 이러한 산화층을 제거하는 기술로서 특개평 11-16912호 공보에 기재된 기술이 있다.

또한, 저유전률의 실리콘 산화막(505)은 패시베이션막으로서 형성되는 보호막에 포함되는 실리콘 산화막(예를 들면 TEOS 산화막)의 유전률보다도 낮은 유전률을 갖는 실리콘 산화막이라고 정의할 수 있다.

이상, 본 발명자에 의해서 이루어진 발명을 발명의 실시 형태에 기초하여 구체적으로 설명하였지만, 본 발명은 상기 실시 형태에 한정되는 것이 아니고, 그 요지를 일탈하지 않는 범위에서 여러가지 변경 가능한 것은 물론이다.

즉, 상기한 매립 Cu 배선(46a ~ 46e)의 형성 방법은 이중 다마신법을 이용한 매립 Cu 배선의 형성에 적용할 수 있게 된다. 이 경우에는 제1층째의 W 배선(24 ~ 30)을 형성한 후, 우선 도 50에 도시한 바와 같이, 제1층째의 W 배선(24 ~ 30)의 상부에 플라즈마 CVD법으로 막 두께 1200nm 정도의 실리콘 산화막(31), 막 두께 50nm 정도의 얇은 실리콘 질화막(38) 및 막 두께 350nm 정도의 실리콘 산화막(39)을 순차 퇴적한다.

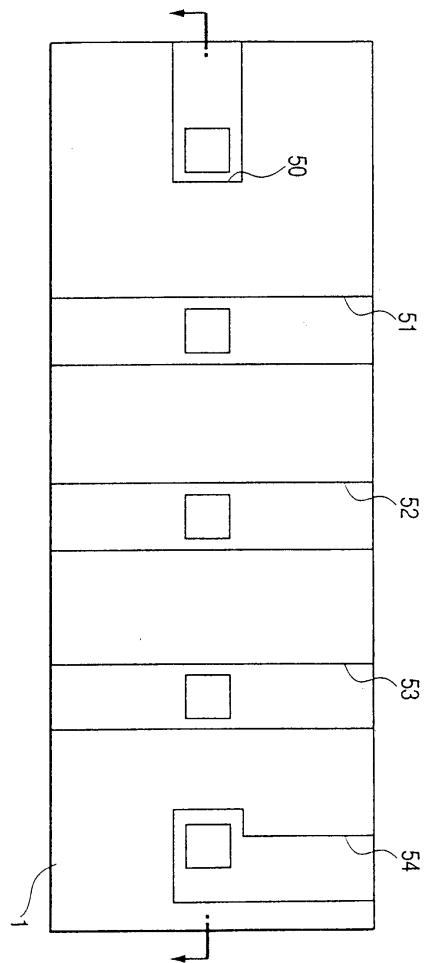

다음에, 도 51에 도시한 바와 같이, 포토레지스트막을 마스크로 한 드라이 에칭으로 제1 층의 W 배선(24, 26, 27, 29, 30) 상부의 실리콘 산화막(39), 실리콘 질화막(38) 및 실리콘 산화막(31)을 순차 제거한 후, 도 52a, 도 52b에 도시한 바와 같이, 다른 포토레지스트막을 마스크에 이용하여 실리콘 질화막(38)을 에칭의 스토펑 드라이 에칭으로 실리콘 산화막(39)을 제거함으로써 관통 구멍을 겹한 배선홈(50 ~ 54)을 형성한다.

다음에, 도 53에 도시한 바와 같이, 배선홈(50 ~ 54)의 내부를 포함하는 실리콘 산화막(39)의 상부에 막 두께 50nm 정도의 얇은 TiN막(45)을 퇴적한 후, TiN막(45)의 상부에 배선홈(50 ~ 54)의 깊이보다 충분히 두꺼운 막 두께의 Cu막(46)을 퇴적한다. 관통 구멍을 겹한 배선홈(50 ~ 54)은 상기 배선홈(40 ~ 44)에 비교하여 어스펙트비가 크기 때문에, TiN막(45)은 CVD법으로 퇴적한다. 또한, Cu막(46)은 스퍼터링을 2회 이상 반복함으로써 퇴적한다. 또한, CVD법, 전해 도금법 혹은 무전해 도금법으로 형성해도 된다. 도금법으로 Cu막(46)을 형성하는 경우에는 배선홈(50 ~ 54)의 하층에 Cu의 시드층을 스퍼터링 법 등으로 형성하는 공정이 필요해진다.

다음에, 도 54에 도시한 바와 같이, 전술한 지립 프리 화학 기계 연마, 유지립 화학 기계 연마 및 선택적 화학 기계 연마에 의해서 배선홈(50 ~ 54)의 외부의 Cu막(46)과 TiN막(45)을 제거하고, 배선홈(50 ~ 54)의 내부에 매립 Cu 배선(46a ~ 46e)을 형성한다. 그 후의 공정은 상기 싱글 다마신법을 이용한 매립 Cu 배선(46a ~ 46e)의 형성 방법과 동일하다.

또한, 상기 실시 형태 1 ~ 4는 각각 독립적으로 적용할 수 있는 것은 물론이며 서로 조합하여 적용할 수 있는 것도 물론이다. 예를 들면, 실시 형태 2의 기술을 적용하여 지립 프리 화학 기계 연마를 실시하고, 그 후 실시 형태 3을 적용하여 산처리를 실시하고 또한 실시 형태 1을 적용하여 암모니아 혹은 수소, 그 외의 플라즈마 처리를 실시해도 된다.

또한, 상기 실시 형태에서는 암모니아 플라즈마 처리 후의 실리콘 질화막(47)의 형성을 진공 파괴(vacuum break)하지 않고 연속적으로 행하였지만, 암모니아 플라즈마 처리 후, 일단 진공 파괴를 하고 그 후 실리콘 질화막(47)을 형성해도 된다. 진공 파괴하지 않은 쪽이 본 발명의 효과를 보다 효과적으로 발휘할 수 있지만, 암모니아 플라즈마 처리에 의해 얇은 질화층이 형성되기 때문에, 진공 파괴를 행하여 대기 분위기에 노출해도 산화층의 형성을 억제할 수 있다. 따라서, 진공 파괴한 경우라도 본 실시 형태의 효과를 어느 정도 발휘하는 것은 가능하다.

### 발명의 효과

본 원에 있어서 개시되는 발명 중, 대표적인 것에 의해서 얻어지는 효과를 간단하게 설명하면 이하와 같다.

다마신법을 이용하여 형성된 구리 배선의 절연 파괴 내성(신뢰성)을 향상할 수 있다.

배선층과 캡막과의 박리의 발생을 억제할 수 있다.

캡막에 실리콘 질화막을 이용한 경우의 구리 배선의 저항치의 증가를 방지할 수 있다.

### 도면의 간단한 설명

도 1은 본 발명의 일 실시 형태(실시 형태 1)인 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 2는 실시 형태 1의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 3은 실시 형태 1의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 4는 실시 형태 1의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 5는 실시 형태 1의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 6a는 실시 형태 1의 제조 방법을 나타내는 평면도.

도 6b는 실시 형태 1의 제조 방법을 나타내는 주요부 단면도.

도 7a는 실시 형태 1의 제조 방법을 나타내는 평면도.

도 7b는 실시 형태 1의 제조 방법을 나타내는 주요부 단면도.

도 8은 실시 형태 1의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 9는 매립 Cu 배선의 형성에 이용하는 CMP 장치의 전체 구성의 일례를 나타낸 개략도.

도 10은 매립 Cu 배선의 형성에 이용하는 CMP 장치의 일부를 나타낸 개략도.

도 11은 웨이퍼의 스크럽 세정 방법을 나타내는 사시도.

도 12는 매립 Cu 배선의 형성에 이용하는 CMP 장치의 전체 구성의 다른 예를 나타내는 개략도.

도 13은 매립 Cu 배선의 형성에 이용하는 CMP 장치의 전체 구성의 또 다른 예를 나타내는 개략도.

도 14는 실시 형태 1의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 15a는 암모니아 플라즈마 처리 및 실리콘 질화막의 퇴적에 이용하는 플라즈마 처리 장치의 개요를 나타낸 단면도.

도 15b는 도 15a와 동일한 평면도.

도 16은 실시 형태 1의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 17은 실시 형태 1의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 18은 실시 형태 1의 반도체 집적 회로 장치의 제조 방법을 나타내는 플로우도.

도 19는 실시 형태 1의 반도체 집적 회로 장치의 개요를 나타내는 단면도.

도 20은 TDDB 수명을 나타내는 그래프.

도 21은 TDDB 수명을 나타내는 그래프.

도 22a는 XPS 데이터를 나타내는 그래프.

도 22b는 XPS 데이터를 나타내는 그래프.

도 22c는 XPS 데이터를 나타내는 그래프.

도 22d는 XPS 데이터를 나타내는 그래프.

도 23a는 XPS 데이터를 나타내는 그래프.

도 23b는 XPS 데이터를 나타내는 그래프.

도 23c는 XPS 데이터를 나타내는 그래프.

도 23d는 XPS 데이터를 나타내는 그래프.

도 24a는 XPS 데이터를 나타내는 그래프.

도 24b는 XPS 데이터를 나타내는 그래프.

도 24c는 XPS 데이터를 나타내는 그래프.

도 24d는 XPS 데이터를 나타내는 그래프.

도 25a는 XPS 데이터를 나타내는 그래프.

도 25b는 XPS 데이터를 나타내는 그래프.

도 25c는 XPS 데이터를 나타내는 그래프.

도 25d는 XPS 데이터를 나타내는 그래프.

도 25e는 XPS 데이터를 나타내는 그래프.

도 25f는 조성비를 나타내는 도표.

도 26a는 질량 분석 결과를 나타내는 그래프.

도 26b는 질량 분석 결과를 나타내는 그래프.

도 26c는 질량 분석 결과를 나타내는 그래프.

도 26d는 질량 분석 결과를 나타내는 그래프.

도 27a는 질량 분석 결과를 나타내는 그래프.

도 27b는 질량 분석 결과를 나타내는 그래프.

도 27c는 질량 분석 결과를 나타내는 그래프.

도 27d는 질량 분석 결과를 나타내는 그래프.

도 28은 실시 형태 1의 배선 부분을 나타내는 TEM 사진.

도 29는 비교로서 나타내는 TEM 사진.

도 30은 배선 저항을 나타내는 그래프.

도 31a는 처리를 하지 않은 경우의 배선 부분을 나타내는 TEM 사진.

도 31b는 실시 형태 1의 배선 부분을 나타내는 TEM 사진.

도 31c는 도 31a를 트레이스(trace)한 도면.

도 31d는 도 31b를 트레이스한 도면.

도 32a는 비교로서 나타내는 TEM 사진.

도 32b는 비교로서 나타내는 TEM 사진.

도 32c는 비교로서 나타내는 TEM 사진.

도 32d는 각각 도 32a를 트레이스한 도면.

도 32e는 각각 도 32b를 트레이스한 도면.

도 32f는 각각 도 32c를 트레이스한 도면.

도 33은 TDDB 수명을 나타내는 그래프.

도 34는 본 발명의 실시 형태 2인 반도체 집적 회로 장치의 제조 방법에 이용하는 CMP 장치의 전체 구성의 일례를 나타낸 개략도.

도 35는 매립 Cu 배선의 형성에 이용하는 CMP 장치의 일부를 나타낸 개략도.

도 36은 Cu막의 연마 상태를 나타내는 CMP 장치의 개략도.

도 37은 실시 형태 2의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 38a는 실시 형태 2의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 평면도.

도 38b는 도 38a와 동일한 주요부 단면도.

도 39는 실시 형태 2의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 40a는 실시 형태 2의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 평면도.

도 40b는 도 40a와 동일한 주요부 단면도.

도 41은 실시 형태 2의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 42a는 실시 형태 2의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 평면도.

도 42b는 도 42a와 동일한 주요부 단면도.

도 43은 실시 형태 2의 반도체 집적 회로 장치의 제조 방법을 나타내는 플로우도.

도 44는 TDDB 수명을 나타내는 그래프.

도 45는 실시 형태 3의 반도체 집적 회로 장치의 제조 방법을 나타내는 플로우도.

도 46은 TDDB 수명을 나타내는 그래프.

도 47은 실시 형태 4의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 48a는 실시 형태 4의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 평면도.

도 48b는 도 48a와 동일한 주요부 단면도.

도 49는 실시 형태 4의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 50은 본 발명의 다른 실시 형태의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 51은 본 발명의 다른 실시 형태의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 52a는 다른 실시 형태의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 평면도.

도 52b는 도 52a와 동일한 주요부 단면도.

도 53은 본 발명의 다른 실시 형태의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 54는 본 발명의 다른 실시 형태의 반도체 집적 회로 장치의 제조 방법을 나타내는 반도체 기판의 주요부 단면도.

도 55는 구리 배선, 알루미늄 배선, 및 텅스텐 배선의 TDDB 특성을 측정한 데이터를 나타내는 그래프.

도 56a는 본원의 TDDB 수명 측정에 사용한 시료를 나타내는 평면도.

도 56b는 도 56a에서의 B-B'선 단면을 나타내는 도면.

도 56c는 도 56a에서의 C-C'선 단면을 나타내는 도면.

도 57은 측정의 개요를 나타낸 개념도.

도 58은 전류 전압 측정 결과의 일례.

<도면의 주요 부분에 대한 부호의 설명>

1 : 기판

2: 소자 분리홈

3 : 실리콘 산화막

20 ~ 22: 컨택트홀

40 ~ 44 : 배선홈

107 : 구동축

108 : 슬러리 공급관

109 : 드레서

110 : 구동축

120 : 로더

121A : 브러시

130 : 연마 처리부

140 : 방식 처리부

150 : 침지 처리부

160 : 후세정 처리부

170 : 언로더

306 : 서셉터

307 : 배플판

308 : 지지 부재

309 : 전극

310 : 절연판

311 : 반사 유닛

도면

도면1

도면2

도면3

도면4

도면5

도면6a

도면6b

도면7a

### 도면7b

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15a

도면15b

도면16

도면17

## 도면18

도면19

도면20

도면21

도면22a

도면22b

도면22c

도면22d

도면23a

도면23b

도면23c

도면23d

도면24a

도면24b

도면24c

도면24d

도면25a

도면25b

도면25c

도면25d

도면25e

도면25f

| 조건                 | Si <sub>3</sub> N <sub>x</sub>    |

|--------------------|-----------------------------------|

| CMP                | —                                 |

| H <sub>2</sub> pI  | Si <sub>3</sub> N <sub>1.08</sub> |

| NH <sub>3</sub> pI | Si <sub>3</sub> N <sub>4.22</sub> |

| N <sub>2</sub> pI  | Si <sub>3</sub> N <sub>3.81</sub> |

도면26a

도면26b

도면26c

도면26d

도면27a

도면27b

도면27c

SiH와 유기물의 열 이탈

SiH, C<sub>2</sub>H<sub>5</sub> m/z=29

도면27d

SiH<sub>3</sub>와 유기물의 열 이탈

SiH<sub>3</sub> m/z=31

도면28

도면29

도면30

표면 처리방법

도면31a

처리 없음

도면31b

NH<sub>3</sub> 플라즈마

도면31c

도면31d

도면32a

H<sub>2</sub> 아닐링

도면32b

N<sub>2</sub> 플라즈마

도면32c

H<sub>2</sub> 플라즈마

0.1 μm

도면32d

도면32e

도면32f

도면33

도면34

도면35

도면36

도면37

도면38a

도면38b

도면39

도면40a

## 도면40b

도면41

도면42a

도면42b

도면43

도면44

도면45

도면46

도면47

도면48a

도면48b

도면49

도면50

도면51

도면52a

도면52b

도면53

도면54

도면55

도면56a

도면56b

도면56c

도면57

## 도면58