(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6165008号

(P6165008)

(45) 発行日 平成29年7月19日(2017.7.19)

(24) 登録日 平成29年6月30日(2017.6.30)

(51) Int.Cl.

F 1

G06F 12/06 (2006.01)

G06F 12/00 (2006.01)G06F 12/06 510A

G06F 12/06 515H

G06F 12/06 520A

G06F 12/00 550E

G06F 12/00 597U

請求項の数 8 (全 22 頁)

(21) 出願番号

特願2013-198330 (P2013-198330)

(22) 出願日

平成25年9月25日(2013.9.25)

(65) 公開番号

特開2015-64758 (P2015-64758A)

(43) 公開日

平成27年4月9日(2015.4.9)

審査請求日

平成28年9月23日(2016.9.23)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100125254

弁理士 別役 重尚

(72) 発明者 野村賀久

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

審査官 後藤 彰

最終頁に続く

(54) 【発明の名称】メモリ制御装置、メモリ制御方法、情報機器及びプログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

データの書き込みと読み出しが可能な半導体メモリが不揮発性メモリであるか揮発性メモリであるかを検出する検出手段と、

所定のデータが、前記検出手段が不揮発性メモリと検出した半導体メモリの中へ格納されるよう前記半導体メモリの設定を行う設定手段とを備えることを特徴とするメモリ制御装置。

## 【請求項 2】

前記設定手段は、前記検出手段が検出した不揮発性メモリに対して、所定のデータを格納するアドレスをマッピングするマッピング手段を有することを特徴とする請求項1記載のメモリ制御装置。 10

## 【請求項 3】

前記設定手段は、前記不揮発性メモリを通常の動作モードから省電力モードに移行する際に前記不揮発性メモリの電源をOFFとし、前記省電力モードから前記通常の動作モードへ復帰させる際に前記不揮発性メモリの電源をONとする電源制御手段を有することを特徴とする請求項1又は2に記載のメモリ制御装置。

## 【請求項 4】

前記検出手段は、前記半導体メモリの所定のアドレスに対して所定のデータの書き込みを行った後、前記アドレスに対して、一定時間以上、リフレッシュコマンドを発行しなかったときに、前記アドレスのデータが変化していない場合に前記半導体メモリは不揮発性

メモリであると判断することを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載のメモリ制御装置。

**【請求項 5】**

前記検出手段は、前記半導体メモリの所定のアドレスに対して所定のデータの書き込みを行った後、前記半導体メモリの電源を遮断し、再度、前記半導体メモリに通電を行ったときに前記アドレスのデータが変化していない場合に前記半導体メモリは不揮発性メモリであると判断することを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載のメモリ制御装置。

**【請求項 6】**

前記設定手段は、ファームウェア、ファクシミリ画像データ、ページカウントデータ、トナー残量等のデータの中の少なくとも一つのデータについては、前記検出手段が不揮発性メモリと検出した半導体メモリに記憶させるよう設定を行うことを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載のメモリ制御装置。 10

**【請求項 7】**

コンピュータによって実行されるメモリ制御方法であって、

データの書き込みと読み出しが可能な半導体メモリが不揮発性メモリであるか揮発性メモリであるかを検出する検出ステップと、

所定のデータが、前記検出ステップで不揮発性メモリと検出された半導体メモリの中へ格納されるよう前記半導体メモリの設定を行う設定ステップとを有することを特徴とするメモリ制御方法。 20

**【請求項 8】**

コンピュータを、

データの書き込みと読み出しが可能な半導体メモリが不揮発性メモリであるか揮発性メモリであるかを検出する検出手段と、

所定のデータが、前記検出手段が不揮発性メモリと検出した半導体メモリの中へ格納されるよう前記半導体メモリの設定を行う設定手段と、して機能させることを特徴とするプログラム。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体メモリに対して種々の制御を行うメモリ制御装置及びメモリ制御方法、このメモリ制御装置を備える情報機器、このメモリ制御方法をコンピュータに実行させるためのプログラムに関する。

**【背景技術】**

**【0002】**

近年、CPUや周辺回路用LSIの処理速度の高速化に伴い、半導体メモリのデータ転送速度にも高速化が要求されている。種々の半導体メモリのうちの1つに同期型半導体メモリであるSDRAMがある。SDRAMは、LSIのシステムクロックに同期した制御とデータの入出力を行う。SDRAMでは、RASやCAS、WE等の制御信号がシステムクロックであるCLKの立ち上りエッジに同期して入力され、これらの入力信号のHighレベルとLowレベルの組み合わせによって制御命令(コマンド)が決まる。また、SDRAMでは、アドレスとデータもCLKの立ち上りエッジに同期して入力される。このような同期型半導体メモリを実現することにより、メモリに対するデータの入出力転送速度を大幅に向上させることができる。 40

**【0003】**

しかしながら、半導体メモリのデータ転送速度の高速化に伴い、CLKとの同期化に対して、各種の入力信号のセットアップタイム及びホールドタイムが短くなるという問題が生じる。同期型半導体メモリにおいて必要なセットアップタイム及びホールドタイムを実現するためには、制御命令にかかるらず、常にアドレスやデータ入力の初段回路を活性化状態にしておく必要がある。そこで、高速データ通信を実現するために、データストロー

10

20

30

40

50

ブ信号（DQS）を採用した半導体メモリに関する技術が知られている。データストローブ信号を採用した半導体メモリとして、例えば、DDR2 SDRAMやDDR3 SDRAM等がある。

#### 【0004】

ところで、複合機（MFP）をはじめとした各種の情報機器では、内部のLSIや半導体メモリの消費電力の増大が深刻化しており、低電力化が求められている。低電力化の方法としては、LSI等を局所的に省電力モード（スリープモード）へ移行させる方法や供給する電源を遮断する方法等がある。しかし、揮発性メモリに記憶されたデータは電源遮断により消失するため、電源遮断前に揮発性メモリに記憶されたデータを不揮発性メモリへ退避させる必要が生じる。また、次に電源を投入したときには、退避したデータの移行を行う必要が生じるため、データ移行に時間を要してしまうことで起動時間が長くなってしまうという新たな問題が生じる。10

#### 【0005】

この問題に対して、DDR3 SDRAM等の揮発性メモリの代替として、磁気抵抗メモリ（以下「MRAM」と記す）等の不揮発性メモリを用いる技術が提案されている（例えば、特許文献1参照）。MRAMは、装置電源を遮断しても磁気によってデータを保持することができ、高速アクセスも可能であるため、装置電源を遮断するに際して、前述のデータを退避する必要が無くなる。また、MRAMを用いた情報機器では、最初の電源投入時に起動プログラムをMRAMに格納し、その後に電源が遮断され、再度電源が投入されたときには、MRAMから起動プログラムを実行することができ、これにより高速起動20が可能になる。

#### 【先行技術文献】

##### 【特許文献】

##### 【0006】

##### 【特許文献1】特開2013-4043号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0007】

しかしながら、MRAMは、揮発性メモリであるDDR3 SDRAMと互換性を持つ構成となっている。そのため、複数のメモリデバイスを搭載することができるよう複数のメモリスロットを備える情報機器では、ユーザがメモリデバイスを追加、交換することができるため、1台の情報機器内にDDR3 SDRAMとMRAMとが混在する可能性がある。この場合、起動プログラムをMRAMに格納すべきところをDDR3 SDRAMに格納してしまう可能性があり、MRAMの特性を有効に活用することができない。30

##### 【0008】

本発明は、情報機器が備える不揮発性メモリの特性を確実に発揮させることができるメモリ制御装置を提供することを目的とする。

##### 【課題を解決するための手段】

##### 【0009】

本発明に係るメモリ制御装置は、データの書き込みと読み出しが可能な半導体メモリが不揮発性メモリであるか揮発性メモリであるかを検出する検出手段と、所定のデータが、前記検出手段が不揮発性メモリと検出した半導体メモリの中へ格納されるよう前記半導体メモリの設定を行う設定手段とを備えることを特徴とする。40

##### 【発明の効果】

##### 【0010】

本発明では、情報機器の起動時にメモリ情報を検出し、不揮発性メモリを特定する。これにより、検出結果に応じてメモリマッピングや電源制御を設定、変更することができるため、不揮発性メモリの特性を確実に発揮させることができる。

##### 【図面の簡単な説明】

##### 【0011】

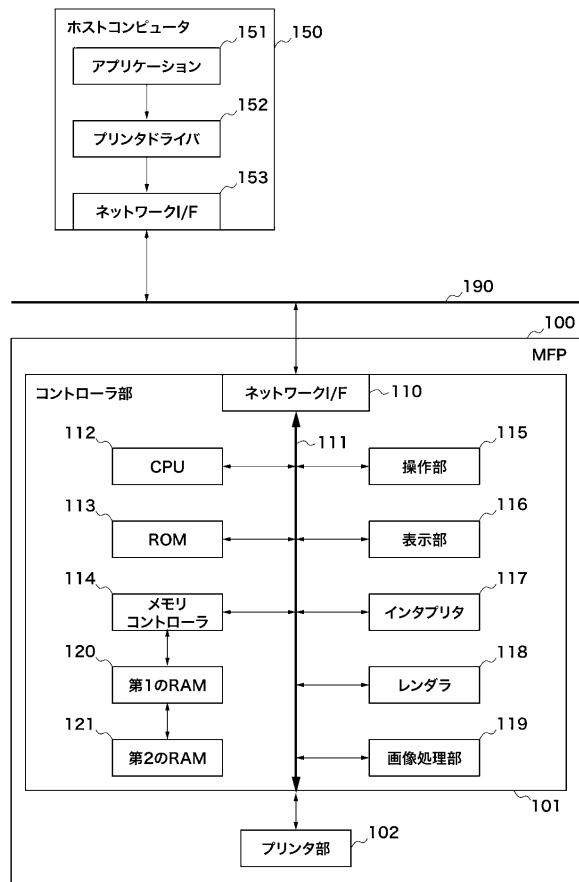

【図1】本発明の実施形態に係るMFPを含むネットワークシステムの概略構成と、MFPのハードウェアの概略構成とを示す図である。

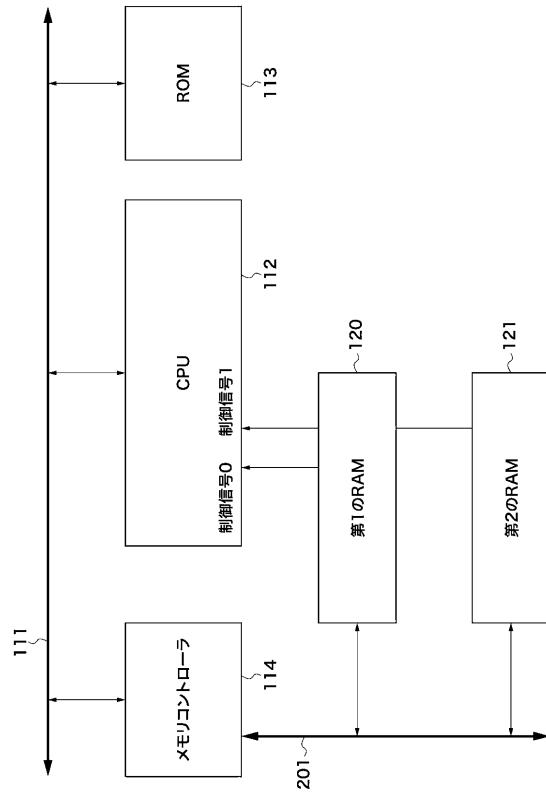

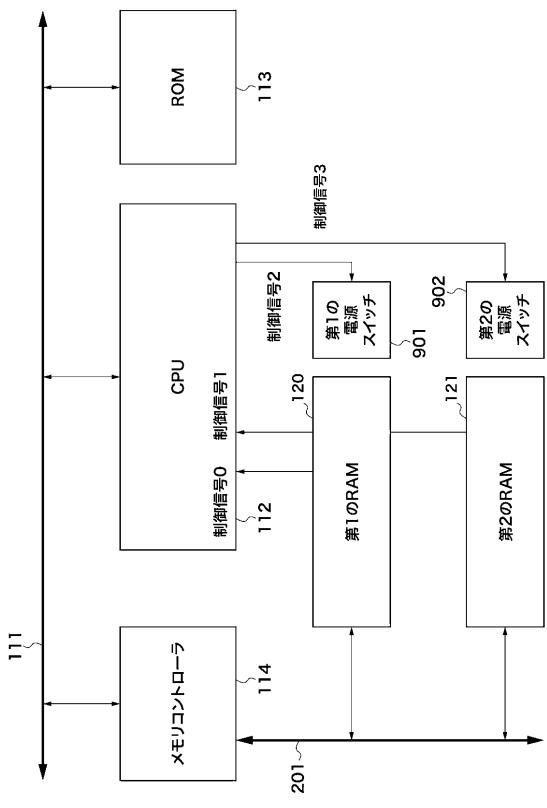

【図2】図1のMFPが備えるコントローラ部におけるCPUとメモリコントローラとの関係を示すブロック図である。

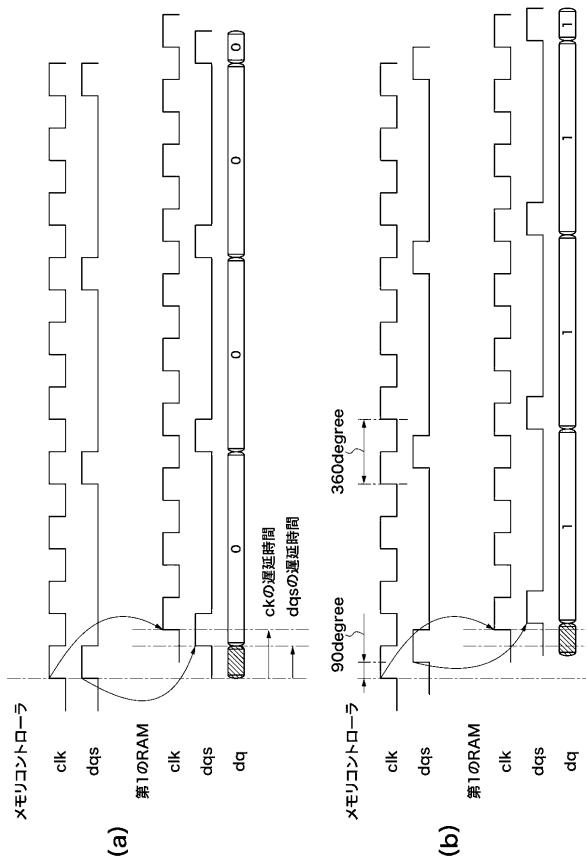

【図3】図1のMFPにおけるライトレベリング中のメモリバス上のメモリコントローラと第1のRAMのc1k, dq5のタイミングチャートである。

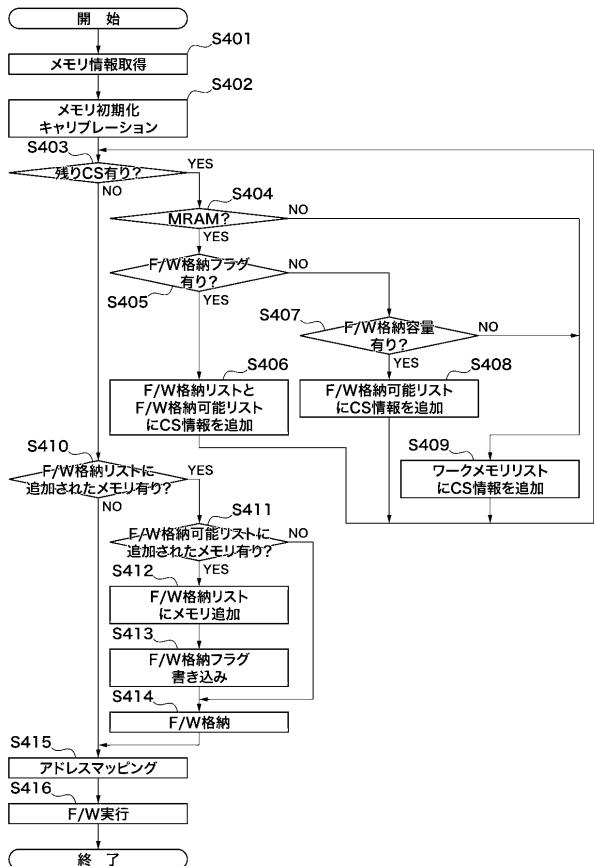

【図4】図1のMFPにおけるメモリデバイス（第1のRAM及び第2のRAM）の初期化シーケンスのフローチャートである。

【図5】図1のMFPが備える第1のRAM及び第2のRAM（メモリモジュール）のSPDから読み取ることができるメモリ情報の一例を示す図である。 10

【図6】図1のMFPが備える第1のRAM及び第2のRAMの初期化キャリブレーションの結果の一例を示す図である。

【図7】図1のMFPのワークメモリリストの一例を示す図である。

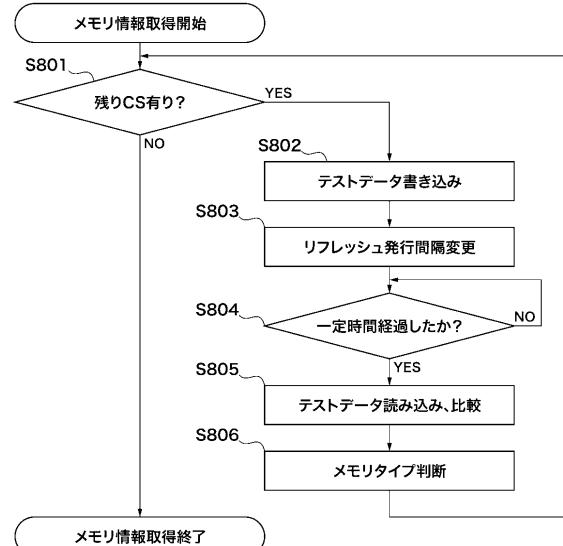

【図8】図1のMFPが備えるメモリデバイス（第1のRAM及び第2のRAM）が揮発性メモリであるか不揮発性メモリであるかをリフレッシュコマンド間隔の変更を利用して検出する方法のフローチャートである。

【図9】図1のMFPのコントローラ部において第1のRAM及び第2のRAMの電源制御を行う構成を示すブロック図である

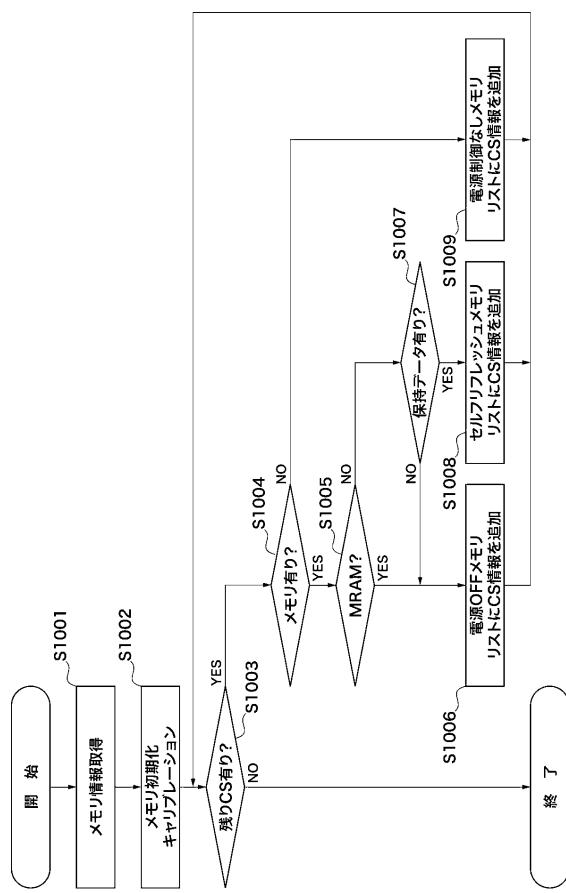

【図10】図9の構成において、不揮発性メモリを検出して電源制御を行うための電源制御メモリリストの初期化シーケンスのフローチャートである。 20

【図11】図10のフローチャートの処理により作成される電源制御メモリリストの一例を示す図である。

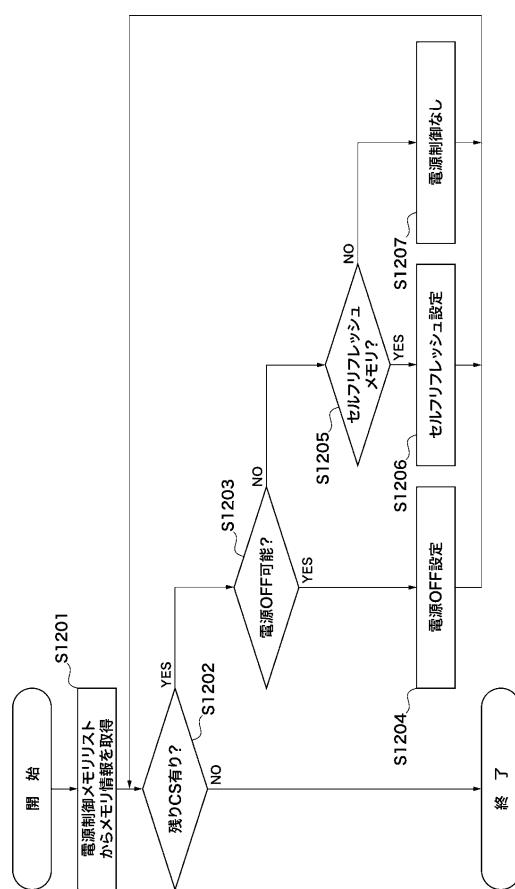

【図12】図9の構成において、MFPが省電力モードに入るときの電源制御シーケンスのフローチャートである。

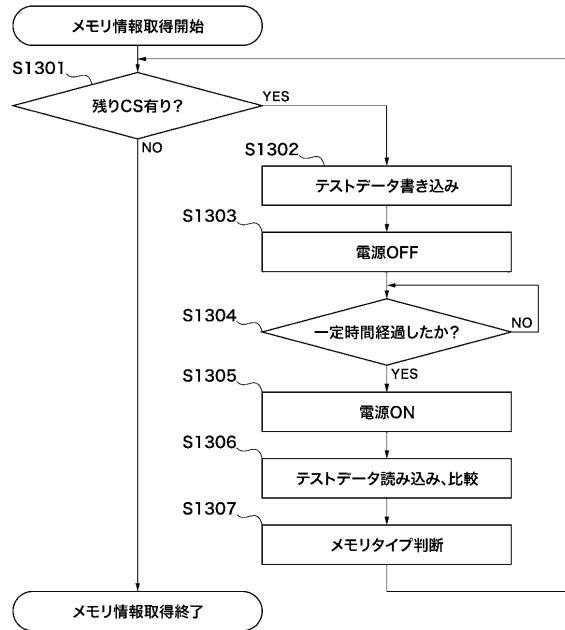

【図13】図9の構成において、MFPが備えるメモリデバイス（第1のRAM及び第2のRAM）が揮発性メモリであるか不揮発性メモリであるかを電源の遮断を利用して検出する方法のフローチャートである。

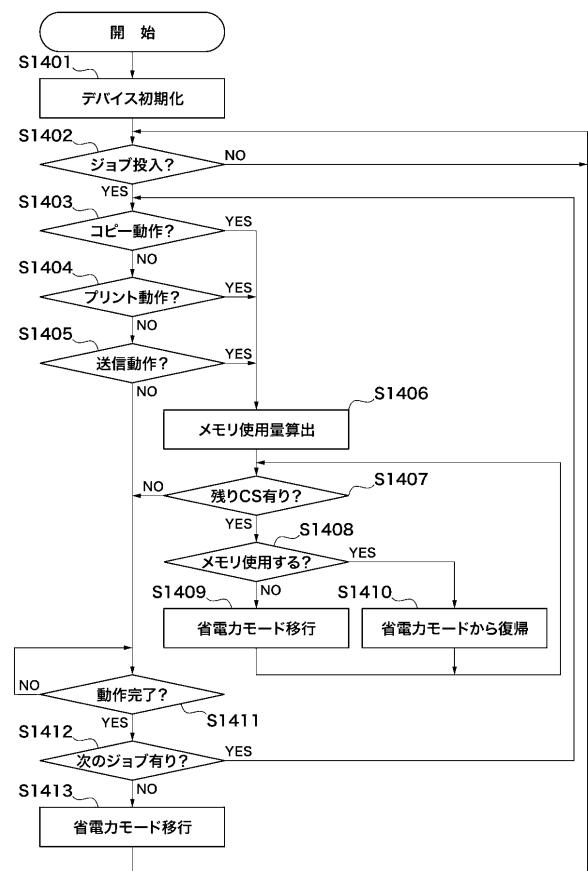

【図14】図1及び図9の構成を備えるMFPの動作時における電源制御シーケンスのフローチャートである。

#### 【発明を実施するための形態】

##### 【0012】

以下、本発明の実施形態について、添付図面を参照して詳細に説明する。ここでは、メモリ制御装置を備える情報機器としてMFP（Multifunction Peripheral）を取り上げることとするが、本発明はこれに限定されるものではない。

##### 【0013】

###### <第1実施形態>

図1は、本発明の実施形態に係るMFPを含むネットワークシステムの概略構成と、MFPのハードウェアの概略構成とを示す図である。このネットワークシステムは、ホストコンピュータ150とMFP100とが外部ネットワーク190を介して接続されることによって構成されている。例えば、ホストコンピュータ150は描画コマンド（印刷データ）をMFP100へ送り、描画コマンドを受け取ったMFP100は出力（印刷）可能な画像データに変換して紙面に印刷する処理を行う。 40

##### 【0014】

ホストコンピュータ150は、アプリケーション151、プリンタドライバ152及びネットワークI/F153を備える。アプリケーション151は、ホストコンピュータ150上で動作するアプリケーション（ソフトウェア）であり、所定のアプリケーションを実行することで、ページレイアウト文書やワードプロセッサ文書、グラフィック文書等の作成が可能となる。アプリケーション151で作成されたデジタル文書データは、プリンタドライバ152に送信され、デジタル文書に基づいた描画コマンドが生成される。プリンタドライバ152で生成される描画コマンドには、例えば、PDL（Page Description 50

Language) と呼ばれるページ画像データを作成するためのプリンタ記述言語が用いられる。描画コマンドには、通常、文字やグラフィックス、イメージ等のデータの描画命令が含まれており、プリンタドライバ 152 で生成された描画コマンドは、ネットワーク I/F 153 と外部ネットワーク 190 とを介して MFP 100 に送信される。

#### 【0015】

MFP 100 は、コントローラ部 101、プリンタ部 102、不図示のスキャナ部及びモデムを備える。コントローラ部 101 は、ネットワーク I/F 110、CPU 112、ROM 113、メモリコントローラ 114、操作部 115、表示部 116、インタプリタ 117、レンダラ 118、画像処理部 119、第 1 の RAM 120 及び第 2 の RAM 121 を含む。コントローラ部 101 に含まれるこれらのモジュールは、システムバス 111 を介して接続されている。

10

#### 【0016】

ネットワーク I/F 110 は、MFP 100 を外部ネットワーク 190 に接続するためのインターフェースである。ネットワーク I/F 110 は、イーサネット(登録商標)等の通信プロトコルに基づき、外部ネットワーク 190 を介してホストコンピュータ 150 をはじめとして外部ネットワーク 190 に接続された不図示の外部機器から描画コマンドを受信する。また、ネットワーク I/F 110 を介して、MFP 100 のデバイス情報(例えば、ジャム情報や紙サイズ情報等)や画像データが、外部ネットワーク 190 に接続されたホストコンピュータ 150 や不図示の外部機器へ送信される。

#### 【0017】

ROM 113 には、MFP 100 の動作を制御するための、後述する初期化シーケンスや電源制御シーケンス等を含む各種のプログラムが格納されている。CPU 112 は、ROM 113 に格納されている各種のプログラムやデータを第 1 の RAM 120 又は第 2 の RAM 121 のワークエリアに展開、実行して、MFP 100 を構成する各種モジュールの動作を制御する。これにより、MFP 100 の全体的な動作が制御される。

20

#### 【0018】

半導体メモリである第 1 の RAM 120 及び第 2 の RAM 121 について、ここでは一般的な使用方法について説明することとし、本実施形態における具体的な使用方法については後述する。第 1 の RAM 120 及び第 2 の RAM 121 は、前述の通り、一時的な記憶デバイスとして CPU 112 のワークエリアとして用いられる他、CPU 112 が各種プログラムを実行する際に生成する各種のデータを一時的に記憶する。また、第 1 の RAM 120 及び第 2 の RAM 121 は、プリンタ部 102 での処理時には、後述する中間言語データやラスター画像データ等のデータを一時的に記憶する。なお、MFP 100 が備える RAM は、第 1 の RAM 120 及び第 2 の RAM 121 に制限されるものではなく、より多くのメモリデバイス(RAM に限る)を備えていてもよい。

30

#### 【0019】

メモリコントローラ 114 は、第 1 の RAM 120 及び第 2 の RAM 121 と、コントローラ部 101 に含まれる他のモジュールとの間のデータ送受信制御を行う。操作部 115 は、ユーザからの入力を受け付けるためのインターフェースであり、各種のハードボタンやタッチパネルからなる。表示部 116 は、ユーザへの指示や MFP 100 の状態を表示する UI (User Interface) 画面を表示するものであり、具体的には、液晶ディスプレイ等であり、液晶ディスプレイは操作部 115 のタッチパネルであってもよい。

40

#### 【0020】

インタプリタ 117 は、ネットワーク I/F 110 を介して受信した描画コマンドを解釈して、中間言語データを生成する。レンダラ 118 は、インタプリタ 117 で生成された中間言語データからラスター画像を生成する。画像処理部 119 は、レンダラ 118 で生成されたラスター画像に対して、色変換処理やルックアップテーブルによる補正処理、擬似中間調処理等の画像処理を行い、プリンタ部 102 に供給する画像データを生成する。プリンタ部 102 は、画像処理部 119 で生成された画像データに基づき、トナー等を用いて紙面上への画像形成を行う。

50

**【0021】**

MFP100において、第1のRAM120及び第2のRAM121に不揮発性メモリであるMRAMと揮発性メモリであるDRAM又はSDRAMとが混在する場合がある。本実施形態では、CPU112は、不揮発性メモリを検出し、検出した不揮発性メモリにファームウェア（以下「F/W」と記す）を格納するメモリマッピングを行う。以下、その詳細について説明する。

**【0022】**

図2は、MFP100のコントローラ部101におけるCPU112とメモリコントローラ114との関係を示すブロック図である。CPU112は、ROM113に格納された起動プログラムを実行することにより、第1のRAM120及び第2のRAM121を始めとして、システムバス111に接続される各モジュールの初期化シーケンスを実行する。また、CPU112は、ROM113又は不図示のハードディスク（HDD）からF/Wを第1のRAM120及び第2のRAM121に展開したプログラムによって様々な数値計算（情報処理）を行い、MFP100の動作を制御する。CPU112は更に、コントローラ部101を構成する各種モジュールの情報を第1のRAM120若しくは第2のRAM121又は不図示のHDDに格納して保持する。

10

**【0023】**

第1のRAM120及び第2のRAM121の制御を行うメモリコントローラ114は、メモリバス201を介して、第1のRAM120及び第2のRAM121に対してコマンドを発行し、メモリアクセスを行う。また、メモリコントローラ114は、第1のRAM120及び第2のRAM121と高速通信を行うためのライトアクセスやリードアクセスのタイミングを調整するキャリブレーションを実行する。このキャリブレーションには、周知の技術を用いることができ、以下に簡単に説明する。

20

**【0024】**

RAMに対して高速でデータの読み書きを行うためには、一般的に、遅延調整の設計を適切に行なうことが求められる。例えば、RAMから出力されたリードデータを内部のフリップフロップによりキャプチャーする部分や、そのフリップフロップからシステムクロックに同期化させる部分の設計を行う必要がある。

**【0025】**

同期化したデータの有効範囲を決定するために、メモリコントローラから出力したクロックがRAMを経由してデータストローブ信号DQSとしてメモリコントローラに戻ってくるまでの遅延量を算出する技術が知られている。遅延値は、ラウンドトリップディレイ（Round Trip Delay）と呼ばれている。例えば、DDR3 SDRAMには、半導体技術協会（JEDEC）の仕様において、リード/ライト（read/write）のアクセスタイミングを調整するためのライトレベリング（Write Leveling）やリードレベリング（Read Leveling）の機能が盛り込まれている。ライトレベリングは、RAMのMR1レジスタのライトレベリングエナブル（Write Leveling Enable）に「1」を設定すると、clk-dqs間のSlew情報を出力する。具体的には、メモリコントローラが発行するdqsの立ち上がりエッジに対してclkをサンプリングし、dqs信号にHighレベルを返す。メモリコントローラは、clkとdqsを少しずつ位相をずらして、dqsの結果から最もタイミングに余裕が生じるようにタイミング調整を行う。

30

**【0026】**

図3は、ライトレベリング中のメモリバス201上でのメモリコントローラ114と第1のRAM120のclk, dqsのタイミングチャートである。なお、図3の説明では、第1のRAM120は、DDR3 SDRAMであるとする。

40

**【0027】**

メモリコントローラ114からclk信号とdqs信号が同時に出力されても、第1のRAM120では、配線長、配線負荷等の影響によりclkとdqsの立ち上がりタイミングが異なる。図3(a)では、clk, dqsが同時に到達していないため、第1のRAM120はdqsに「0」を返す。メモリコントローラ114は、clk, dqsの出力

50

タイミングをずらしていき、 $d q$  の変化ポイントを探す。これに対して、図 3 ( b ) では、 $d q = 1$  となっているため、 $d q s$  の立ち上がりエッジで  $c l k$  サンプリングが行われている。

#### 【 0 0 2 8 】

一方、リードレベリングにおいて M P R ( Multi Purpose Register ) を有効にすると、第 1 の RAM 1 2 0 から予め決められたデータパターンが output される。メモリコントローラ 1 1 4 は、このデータパターンを受信可能なタイミングを知ることができ、リードコマンドを発行してからの、リードデータを受信するレイテンシ ( Latency ) を調整する。リードアクセス時には、第 1 の RAM 1 2 0 が  $d q s$  を output する。

#### 【 0 0 2 9 】

先ず、メモリコントローラ 1 1 4 は、リードコマンドを発行してからデータを受信するまでのサイクル数を検出する。メモリコントローラ 1 1 4 は、リードコマンドを発行してからの第 1 の RAM 1 2 0 のリードレイテンシ ( Read Latency ) 時間に、コマンド及びデータ転送遅延時間を加味したサイクル数を 1 サイクルずつ加算し、M P R の値を読むことができるタイミングを検出する。メモリコントローラ 1 1 4 は、サイクル数を検出すると、 $c l k$  と  $d q s$  スキューを調整するために、内部の  $d q s$  を検出してからリードデータを読み込むタイミングを少しずつずらして、最も良い変化ポイントを検出する。

#### 【 0 0 3 0 】

第 1 の RAM 1 2 0 及び第 2 の RAM 1 2 1 に対しては、所定のプロトコルに則ってデータの書き込みと読み出しを行うことができる。本実施形態では、第 1 の RAM 1 2 0 及び第 2 の RAM 1 2 1 はそれぞれ、複数のメモリデバイスと S P D ( Serial Presence Detect ) から成るメモリモジュールであるものとする。また、本実施形態では、第 1 の RAM 1 2 0 は揮発性メモリであり、揮発性メモリは DDR 3 SDRAM であるとする。但し、揮発性メモリは、これに限定されず、SDRAM、DDR SDRAM、DDR2 SDRAM、DDR4 SDRAM、SRAM 等であってもよい。また、本実施形態では、第 2 の RAM 1 2 1 は不揮発性メモリであり、不揮発性メモリは DDR3 MRAM であるとするが、これに限定されず、その他の不揮発性メモリであってもよい。

#### 【 0 0 3 1 】

図 2 の説明に戻る。メモリバス 2 0 1 は、メモリコントローラ 1 1 4 と第 1 の RAM 1 2 0 及び第 2 の RAM 1 2 1 とを接続するための高速通信バスである。C P U 1 1 2 は、M F P 1 0 0 に電源が投入されると、システムバス 1 1 1 を介して R O M 1 1 3 に格納されている起動プログラムを読み出し、M F P 1 0 0 を初期化するための初期化シーケンスを実行する。以下、起動プログラムによる第 1 の RAM 1 2 0 及び第 2 の RAM 1 2 1 の初期化シーケンスについて、図 4 のフローチャートを参照して説明する。

#### 【 0 0 3 2 】

図 4 は、M F P 1 0 0 に実装された第 1 の RAM 1 2 0 及び第 2 の RAM 1 2 1 の初期化シーケンスのフローチャートである。図 4 のフローチャートの各処理は、C P U 1 1 2 が R O M 1 1 3 に格納されている起動プログラムを読み出し、第 1 の RAM 1 2 0 又は第 2 の RAM 1 2 1 に展開し、実行することによって実現される。なお、本実施形態では、第 1 の RAM 1 2 0 及び第 2 の RAM 1 2 1 以外のモジュールの初期化シーケンス及び制御シーケンスについての説明は省略する。また、ここでは、第 1 の RAM 1 2 0 及び第 2 の RAM 1 2 1 に限定されず、メモリデバイス ( RAM に限る ) としての説明を行い、適宜、第 1 の RAM 1 2 0 及び第 2 の RAM 1 2 1 に対する処理結果について説明することとする。

#### 【 0 0 3 3 】

先ず、ステップ S 4 0 1 において、C P U 1 1 2 は、シリアルバスを介して制御信号 0 , 1 ( 図 2 参照 ) により、メモリデバイスのメモリ情報を取得する。例えば、メモリモジュールに実装されている S P D からスペック情報を取得し、これにより、各メモリデバイスの電源制御が可能になる。なお、スペック情報とは、例えば、揮発性メモリか又は不揮発性メモリかに関する情報、最大クロック周波数、容量、信号タイミング等である。

10

20

30

40

50

**【0034】**

図5は、メモリモジュールのSPDから読み取ることができるメモリ情報の一例を示す図である。なお、図5に示したアドレスや値は一例であり、タイミングパラメータについても全ては記載されていない。CPU112は、SPDから読みとったメモリ情報の中から必要な情報を、例えば、不図示のHDDに記憶する。

**【0035】**

図5(a)は、第1のRAM120について取得したメモリ情報を示しており、読み取ったアドレスと値から、第1のRAM120は、DDR3 SDRAM、1066MHz、1Gbit、8bank、揮発性であることがわかる。図5(b)は、第2のRAM121について取得したメモリ情報を示しており、第2のRAM121は、DDR3 MRAM、1066MHz、1Gbit、8bank、不揮発性であることがわかる。

10

**【0036】**

次に、CPU112は、メモリコントローラ114に対してメモリ初期化のキャリブレーションの実行命令を発行する。これにより、ステップS402において、メモリコントローラ114は、メモリデバイスを初期化するキャリブレーションを実行する。具体的には、CPU112は、ステップS401での取得情報に基づき、メモリコントローラ114により、メモリ初期化時に実装されているメモリデバイスに対して、順次、アドレスをマッピングする。そして、CPU112は、メモリコントローラ114により、各メモリデバイスに対して、ライトレベリングとリードレベリングの両方のタイミング調整を行う。CPU112は、各メモリデバイスの各バンクのライトアクセス及びリードアクセス時のclk-dqs間のSkew情報をリードレイテンシを記憶する。

20

**【0037】**

図6は、第1のRAM120及び第2のRAM121の初期化キャリブレーションの結果の一例を示す図である。メモリコントローラ114による第1のRAM120及び第2のRAM121の初期化キャリブレーションが完了すると、CPU112は第1のRAM120及び第2のRAM121へアクセス可能となる。

**【0038】**

ステップS402の終了後、CPU112は、チップセレクト(以下「CS」と記す)毎にメモリマッピング処理を開始し、ステップS403において、メモリマッピング処理がなされていない残りのCSが有るか否かを判断する。CPU112は、残りCSが有る場合(S403でYES)、処理をステップS404へ進め、残りCSが無い場合(S403でNO)、処理をステップS410へ進める。

30

**【0039】**

ステップS404において、CPU112は、ステップS403において選択したCSのメモリデバイスがDDR3 MRAM(不揮発性メモリ)であるか否かを、ステップS401で取得したメモリ情報に基づいて判断する。CPU112は、DDR3 MRAMである(不揮発性メモリである(S404でYES))場合、処理をステップS405へ進め、DDR3 MRAMではない(揮発性メモリである(S404でNO))場合、処理をステップS409へ進める。

40

**【0040】**

ステップS405において、CPU112は、選択したCSにF/W格納フラグが有るか否かを判断する。例えば、この判断は、メモリデバイスの先頭番地0x0に予め定めたフラグ値が格納されているか否かにより行われる。CPU112は、F/W格納フラグが有る場合(S405でYES)、処理をステップS406へ進め、F/W格納フラグが無い場合(S405でNO)、処理をステップS407へ進める。

**【0041】**

ステップS406において、CPU112は、F/W格納リスト及びF/W格納可能リストにCS情報を追加、格納する。その後、処理はステップS403へ戻される。

**【0042】**

ステップS407において、CPU112は、F/W格納容量が有るか否かを判断する

50

。具体的には、CPU112は、ステップS401で取得したメモリ容量情報とROM113に予め格納されているF/W容量情報を比較する。CPU112は、F/W格納容量が有る場合(S407でYES)、処理をステップS408へ進め、F/W格納容量が無い場合(S407でNO)、処理をステップS409へ進める。

#### 【0043】

ステップS408において、CPU112は、F/W格納可能リストにCS情報を追加、格納する。ステップS409において、CPU112は、ワークメモリリストにCS情報を追加、格納する。ステップS408、S409の終了後、処理はステップS403へ戻される。

#### 【0044】

図7は、MFP100のワークメモリリストの一例を示す図である。ステップS403～S409の処理が全てのCSに対して終了すると、図7に示すワークメモリリストが得られる。本実施形態では、CS0及びCS1はそれぞれ、第1のRAM120及び第2のRAM121に該当するものとし、第2のRAM121にF/W格納フラグが書き込まれているものとする。第1のRAM120は揮発性メモリであるため、F/W格納リスト及びF/W格納可能リストのCS0に「No」が、ワークメモリリストのCS0に「Yes」がそれぞれ書き込まれる。一方、第2のRAM121は不揮発性メモリであり、F/W格納フラグが有るため、F/W格納リスト及びF/W格納可能リストのCS1に「Yes」が、ワークメモリリストのCS1に「No」がそれぞれ書き込まれる。

#### 【0045】

ステップS403の判断がNoとなった後のステップS410において、CPU112は、図7のワークメモリリストからF/W格納リストに追加されたメモリが有る否かを判断する。CPU112は、追加されたメモリが有る場合(S410でYES)、処理をステップS411へ進め、追加されたメモリが無い場合(S410でNO)、処理をステップS415へ進める。

#### 【0046】

ステップS411において、CPU112は、図7のワークメモリリストからF/W格納可能リストに追加されたメモリが有る否かを判断する。CPU112は、追加されたメモリが有る場合(S411でYES)、処理をステップS412へ進め、追加されたメモリが無い場合(S411でNO)、処理をステップS414へ進める。

#### 【0047】

ステップS412において、CPU112は、F/W格納可能リストで「Yes」になっているCSを1つ選択し、F/W格納リストにそのCSのメモリデバイスを追加する。続くステップS413において、CPU112は、ステップS412で選択したCSのメモリデバイスの先頭番地0×0に予め定めたフラグ値を格納する。これにより、ステップS412においてF/W格納リストに追加されたメモリデバイスは、MFP100の次の起動時には、ステップS405においてF/W格納フラグ有りとして検出されることとなる。

#### 【0048】

ステップS414において、CPU112は、F/W格納フラグの有るメモリデバイスにF/Wを格納する。なお、F/Wは、ROM113又は不図示のHDD等の記憶媒体や、外部ネットワーク190のストレージに外部ネットワーク190経由で格納してもよい。ステップS414の後、処理はステップS415へ進められる。

#### 【0049】

ステップS415において、CPU112は、図7のワークメモリリストにあるように、アドレスマッピングを実施する。具体的には、ステップS415では、F/Wが格納されているメモリデバイス(CS)に対して、起動プログラムがF/Wを実行する際に指定されているアドレス領域を割り当てる。本実施形態では、F/W実行アドレスが0×0000\_0000であるとし、図7に示すように、CS1のDDR3 MRAM(第2のRAM121)に0×0000\_0000が割り当てられる。F/W実行アドレスが割り当

10

20

30

40

50

てられたメモリデバイス以外のメモリデバイスに対しては、ワークメモリとして使用されるアドレス領域が割り当てられる。本実施形態では、図7に示すように、C S 0 の D D R 3 S D R A M ( 第1の R A M 1 2 0 ) に  $0 \times 8 0 0 0\_0 0 0 0$  が割り当てられる。

#### 【 0 0 5 0 】

続くステップ S 4 1 6 において、C P U 1 1 2 は、ステップ S 4 1 5 で指定したアドレスから F / W を実行し、その後、本処理は終了となる。

#### 【 0 0 5 1 】

なお、本実施形態では、F / W を不揮発性メモリ ( D D R 3 M R A M ( 第2の R A M 1 2 1 ) ) に格納されるようにメモリマッピングを実施した。これに対して、例えば、M F P 1 0 0 において保持していかなければならないファクシミリ画像データやページカウントデータ、トナー残量等のデータについても、同様の手法により不揮発性メモリに格納するよりもよい。また、揮発性メモリ ( D D R 3 S D R A M ( 第1の R A M 1 2 0 ) ) には、一時的に使用される中間画像データ ( 例えば、M F P 1 0 0 が備える不図示のスキヤナ部により読み取られたスキャンデータ ) が格納されるようにしてもよい。

10

#### 【 0 0 5 2 】

ところで、不揮発性メモリである第2の R A M 1 2 1 の容量が F / W を格納するのに十分でない場合が想定される。この場合、F / W やその他の保持しておかなければならぬプログラムやデータは、その他の不揮発性メモリ ( 例えば、フラッシュメモリ ) や H D D がある場合には、これらにマッピングするようにする。また、第1の R A M 1 2 0 及び第2の R A M 1 2 1 の双方が揮発性メモリである場合、つまり、不揮発性メモリを備えない場合も想定される。この場合も、前述の不揮発性メモリの容量が足りない場合と同様の対処法が採られる。

20

#### 【 0 0 5 3 】

以上の説明の通り、本実施形態によれば、M F P 1 0 0 に不揮発性メモリと揮発性メモリとが混在して実装されている場合、どのメモリデバイスが不揮発性メモリであるかを知ることができる。これにより、F / W を不揮発性メモリにマッピングすることができるため、例えば、M F P 1 0 0 の省電力モード ( スリープモード ) への移行と省電力モードからの復帰に要する時間を短縮することができる。

#### 【 0 0 5 4 】

##### < 第2実施形態 >

30

上記第1実施形態では、初期化シーケンスのステップ S 4 0 1 において、C P U 1 1 2 は、メモリモジュールに実装されている S P D からメモリデバイスのメモリ情報を入手し、そのメモリデバイスが不揮発性メモリであるか揮発性メモリであるかを判断している。これに対して、本実施形態では、S P D からのメモリ情報が無い場合に、リフレッシュコマンド間隔を変更することによりメモリデバイスが不揮発性メモリであるか揮発性メモリであるかを判断する。より具体的には、C P U 1 1 2 は、メモリデバイスに対して、一定時間以上、リフレッシュコマンドを発行しないことで、メモリデバイスが揮発性メモリであるか不揮発性メモリであるかを検出する。

#### 【 0 0 5 5 】

図8は、リフレッシュコマンド間隔の変更を利用した不揮発性 / 挥発性メモリ検出シーケンスのフローチャートである。ここでも、第1の R A M 1 2 0 及び第2の R A M 1 2 1 に限定されず、メモリデバイス ( R A M に限る ) としての説明を行い、適宜、第1の R A M 1 2 0 及び第2の R A M 1 2 1 についての処理結果について説明することとする。

40

#### 【 0 0 5 6 】

ステップ S 8 0 1 に先立って、図4のステップ S 4 0 2 の処理が実行されるが、ステップ S 4 0 2 の処理内容についてのここでの説明は省略する。ステップ S 4 0 2 の後のステップ S 8 0 1 において、C P U 1 1 2 は、C S 毎にメモリタイプの判断 ( ステップ S 8 0 6 ) を実施していない残りの C S が有るか否かを判断する。C P U 1 1 2 は、残り C S が有る場合 ( S 8 0 1 で Y E S ) 、処理をステップ S 8 0 2 へ進め、残り C S がない場合 ( S 8 0 1 で N O ) 、処理を終了させる。

50

**【 0 0 5 7 】**

ステップ S 8 0 2において、CPU112は、ステップ S 8 0 1で残り CSとして選択した CSのメモリデバイスに対してテストデータを書き込む。例えば、複数のアドレスに特定パターンを書き込む。続くステップ S 8 0 3において、CPU112は、メモリコントローラ114に対してリフレッシュコマンドの発行間隔を変更する処理を実行する。例えば、揮発性メモリである DDR3 SDRAMにおいては、放電で失った電荷を定期的に再充電する必要がある。そのために、JEDDECのAverage Periodic Refresh Interval tREFI(0 T case 85)によれば、平均 7.8 μs 以内にリフレッシュコマンドを発行しなければならない。この規定外ではデータを保持することは保証されないため、メモリコントローラ114は、平均で 7.8 μs に1度、リフレッシュコマンドを発行する。しかしながら、不揮発性メモリでは、リフレッシュコマンドを発行しなくてもデータを保持することができる。したがって、CPU112は、リフレッシュコマンドの発行を停止し又は発行間隔を 10 ms のように十分大きい値に設定する。

**【 0 0 5 8 】**

次に、ステップ S 8 0 4において、CPU112は、ステップ S 8 0 3で設定した時間以上の一定時間経過したか否かを判断する。CPU112は、一定時間が経過するまで待機し(S 8 0 4で NO)、一定時間が経過すると(S 8 0 4で YES)、処理をステップ S 8 0 5へ進める。ステップ S 8 0 5において、CPU112は、選択した CSのメモリデバイスから、ステップ S 8 0 2で書き込みを行ったアドレスの値を読み出して、書き込みデータと比較する。

**【 0 0 5 9 】**

次いで、ステップ S 8 0 6において、CPU112は、選択した CSのメモリタイプ判断、つまり、メモリデバイスが不揮発性メモリであるか否かの判断を行う。CPU112は、ステップ S 8 0 5での比較の結果、選択した CSのメモリデバイスは、全ての書き込みデータと読み出しデータとが一致している場合には不揮発性メモリであると判断し、一致しない場合は揮発性メモリであると判断する。その後、処理はステップ S 8 0 1へ戻される。

**【 0 0 6 0 】**

このような処理により、DDR3 SDRAMである第1の RAM120については、揮発性メモリであるとの判断がなされ、DDR3 MRAMである第2の RAM121については、不揮発性メモリであるとの判断がなされる。

**【 0 0 6 1 】**

以上のリフレッシュコマンド間隔の変更を利用した不揮発性 / 挥発性メモリ検出シーケンスによれば、メモリデバイスが不揮発性か否かを判断することが可能となる。よって、MFP100に実装されたメモリデバイスに不揮発性メモリと揮発性メモリとが混在して実装されていても、F / Wを不揮発性メモリに確実にマッピングすることができる。これにより、第1実施形態と同じ効果が得られる。

**【 0 0 6 2 】**

## &lt; 第3実施形態 &gt;

本実施形態では、CPU112が、MFP100に実装されたメモリデバイス(第1の RAM120及び第2の RAM121)を検出した後に、省電力モード(スリープモード)に移行する際に、各メモリデバイスに対して行う電源制御処理について説明する。

**【 0 0 6 3 】**

図9は、MFP100のコントローラ部101において第1の RAM120及び第2の RAM121の電源制御を行う構成を示すブロック図である。図9に示す構成は、図2に示した構成に対して第1の電源スイッチ901及び第2の電源スイッチ902を付加した構成となっており、よって、図2と重複する部分の説明は省略する。

**【 0 0 6 4 】**

第1の電源スイッチ901及び第2の電源スイッチ902はそれぞれ、設定によって第1の RAM120及び第2の RAM121に対する電源のON/OFFを切り替えること

ができる。CPU112は、第1実施形態での処理に加えて、制御信号2及び制御信号3により第1の電源スイッチ901及び第2の電源スイッチ902の設定を行うことで、第1のRAM120及び第2のRAM121の電源制御を行う。

#### 【0065】

図9に示した構成において、CPU112が、不揮発性メモリを検出して電源制御を行う方法について、図10及び図11を参照して説明する。図10は、電源制御メモリリストの初期化シーケンスのフローチャートである。また、図11は、図10のフローチャートの処理により作成される電源制御メモリリストの一例を示す図である。図10のフローチャートの各処理は、CPU112がROM113に格納されている起動プログラムを読み出し、第1のRAM120又は第2のRAM121に展開し、実行することによって実現される。10

#### 【0066】

なお、ここでも、第1のRAM120及び第2のRAM121に限定されず、メモリデバイス(RAMに限る)としての説明を行い、適宜、第1のRAM120及び第2のRAM121についての処理結果について説明することとする。また、ここでは、メモリデバイス以外の制御シーケンスについての説明は省略する。

#### 【0067】

ステップS1001, S1002の処理は、先に図4を参照して説明したステップS401, 402の処理と同じである。即ち、CPU112は、MFP100に電源が投入されると、第1実施形態で説明したように、システムバス111を介してROM113にある起動プログラムを実行する。これにより、CPU112は、メモリ情報を取得し、初期化シーケンスを実行する。このとき、第1の電源スイッチ901及び第2の電源スイッチ902は、常に電源ONの状態になっているものとする。20

#### 【0068】

ステップS1003において、CPU112は、電源制御設定が行われていない残りのCSがあるか否かを判断する。CPU112は、残りCSが有る場合(S1003でYES)、処理をステップS1004へ進め、残りCSがない場合(S1003でNO)、処理を終了させる。ステップS1004において、CPU112は、ステップS1003において選択したCSにメモリモジュールが実装されているか否かを判断する。CPU112は、メモリモジュールが実装されている場合(S1004でYES)、処理をステップS1005へ進め、メモリモジュールが実装されていない場合(S1004でNO)、処理をステップS1009へ進める。30

#### 【0069】

ステップS1005において、CPU112は、選択したCSのメモリデバイスがDDR3 MRAM(不揮発性メモリ)であるか否かを、ステップS1001で取得したメモリ情報に基づいて判断する。CPU112は、DDR3 MRAMである(不揮発性メモリである(S1005でYES))場合、処理をステップS1006へ進め、DDR3 MRAMではない(揮発性メモリである(S1005でNO))場合、処理をステップS1007へ進める。ステップS1007において、CPU112は、選択したCSのメモリデバイスにデータを格納するか否か(保持させるデータが有るか否か)を判断する。CPU112は、保持させるデータが有る場合(S1007でYES)、処理をステップS1008へ処理を進め、保持させるデータが無い場合(S1007でNO)、処理をステップS1006へ進める。40

#### 【0070】

ステップS1006において、CPU112は、電源制御メモリリストの電源OFFメモリリスト欄に選択したCSのCS情報を追加(格納)する。ステップS1008において、CPU112は、電源制御メモリリストのセルフリフレッシュメモリリストに選択したCSのCS情報を追加する。ステップS1009において、CPU112は、選択したCSにメモリデバイスは実装されていないため、電源制御メモリリストの電源制御なしメモリリストにCS情報を追加する。CPU112は、ステップS1006, S1008, 50

S 1 0 0 9 の後、処理をステップ S 1 0 0 3 へ戻す。

**【 0 0 7 1 】**

本実施形態では、CS0 及びCS1 はそれぞれ第1のRAM120 及び第2のRAM121に該当し、それ以外のCSにはメモリデバイスはなく、第1のRAM120がDDR3 SDRAMであって、第2のRAM121はDDR3 MRAMである。よって、図10の電源制御メモリリストの作成シーケンスによれば、図11に示す電源制御メモリリストが得られる。なお、電源制御メモリリストは、例えば、不図示のHDDに格納される。ここでは、ステップS1007の保持させるデータが有るか否かを起動時に判断したが、F/W起動後に同判断を行って、電源制御メモリリストを変更するようにしてもよい。

**【 0 0 7 2 】**

上述の電源制御シーケンスは、MFP100 に電源が投入されたときに、CPU112 がメモリデバイスに対して実行するものであり、MFP100 が省電力モードに入るときの電源制御シーケンスについて図12を参照して説明する。図12は、MFP100 が省電力モードに入るときの電源制御シーケンスのフローチャートである。

**【 0 0 7 3 】**

先ず、ステップS1201において、CPU112 は、図10のフローチャートに従う初期化シーケンスで作成した電源制御メモリリストを参照して、メモリ情報を取得する。続くステップS1202において、CPU112 は、CS毎に電源制御設定（ステップS1204, S1206, S1207のいずれか）が行われていない残りのCSが有るか否かを判断する。CPU112 は、残りCSが有る場合（S1202でYES）、処理をステップS1203へ進め、残りCSが無い場合（S1202でNO）、本処理を終了させる。

**【 0 0 7 4 】**

ステップS1203において、CPU112 は、選択したCSのメモリデバイスに対する電源OFFが可能か否かを、ステップS1201で取得したメモリ情報に基づき判断する。CPU112 は、不揮発性メモリであるために電源OFFが可能な場合（S1203でYES）、処理をステップS1204へ進め、揮発性メモリであるために電源OFFが不可能な場合（S1203でNO）、処理をステップS1205へ進める。

**【 0 0 7 5 】**

ステップS1205において、CPU112 は、選択したCSのメモリデバイスにセルフリフレッシュ設定が必要か否かを判断する。CPU112 は、セルフリフレッシュ設定が必要な場合（S1205でYES）、処理をステップS1206へ進め、セルフリフレッシュ設定が必要な場合（S1205でNO）、処理をステップS1207へ進める。

**【 0 0 7 6 】**

ステップS1204において、CPU112 は、選択したCSのメモリデバイスの電源をOFFにするために、電源スイッチ（第1の電源スイッチ901又は第2の電源スイッチ902）の設定を行う。これにより、MFP100 が省電力モードに入るときには、選択したCSのメモリデバイスの電源はOFFにされる。

**【 0 0 7 7 】**

ステップS1206において、CPU112 は、選択したCSのメモリデバイスをセルフリフレッシュモードに移行させるための設定をメモリコントローラ114に対して行う。これによりMFP100 が省電力モードに入るときには、選択したCSのメモリデバイスは、セルフリフレッシュモードに移行される。なお、セルフリフレッシュを行わずに、メモリデバイスに保持されていたデータを不図示のHDD等に退避させて、電源をOFFにしてもよい。

**【 0 0 7 8 】**

ステップS1207において、CPU112 は、選択したCSにはメモリデバイスが実装されておらず、電力消費が無いため、電源制御は行わない。ステップS1204, S1206, S1207の後、CPU112 は、処理をステップS1202に戻す。

**【 0 0 7 9 】**

10

20

30

40

50

なお、MFP100が省電力モードから通常の動作モードに復帰するときには、CPU112は、電源OFFのメモリデバイスの電源スイッチに対して、電源をONにする設定を行う。よって、図11の電源制御メモリリストの場合、不揮発性メモリ(DDR3RAM)である第2のRAM121の第2の電源スイッチ902の電源がONされる。また、MFP100が省電力モードから通常の動作モードに復帰するときには、CPU112は、メモリコントローラ114を介して、セルフリフレッシュのメモリデバイス(図11の電源制御メモリリストではなし)を通常動作に復帰させる。

#### 【0080】

本実施形態では、上述の通りに電源制御を行うことにより、MFP100が省電力モードにあるときの消費電力を小さく抑えることができる。

10

#### 【0081】

##### <第4実施形態>

第3実施形態では、第1実施形態と同様に、初期化シーケンスのステップS1001において、CPU112は、メモリモジュールに実装されているSPDからメモリ情報を入手し、メモリモジュールが不揮発性メモリであるか揮発性メモリであるかを判断している。これに対して、本実施形態では、実装されているメモリデバイスに対して電源を遮断し、一定時間経過後に再度、電源を通電したときにデータが保持されているかを確認することで、メモリデバイスが不揮発性メモリであるか揮発性メモリであるかを判断する。

#### 【0082】

図13は、電源の遮断を利用した不揮発性／揮発性メモリ検出シーケンスのフローチャートである。図13の不揮発性／揮発性メモリ検出シーケンスは、初期化シーケンスのステップS1002(図10参照)の実行後に、起動プログラムによって実行される。なお、ここでも、第1のRAM120及び第2のRAM121に限定されず、メモリデバイス(但し、RAMに限る)としての説明を行い、適宜、第1のRAM120及び第2のRAM121についての処理結果について説明することとする。

20

#### 【0083】

先ず、ステップS1301において、CPU112は、メモリタイプの判断(ステップS1307)を行っていない残りのCSが有るか否かを判断する。CPU112は、残りCSが有る場合(S1301でYES)、処理をステップS1302へ進め、残りCSが無い場合(S1301でNO)、本処理を終了させる。ステップS1302において、CPU112は、ステップS1301で選択した残りCSのメモリデバイスに対してテストデータを書き込む。例えば、残りCSのメモリデバイスの複数のアドレスに特定パターンを書き込む。

30

#### 【0084】

続くステップS1303において、CPU112は、選択したCSのメモリデバイスの電源スイッチに電源OFFの設定を実行し、その結果、選択したCSのメモリデバイスに対する通電は停止される。その後、ステップS1304において、CPU112は、ステップS1303で設定した時間以上の一定時間が経過したかを判断し、一定時間が経過するまで待機する(S1304でNO)。CPU112は、一定時間が経過すると(S1304でYES)、処理をステップS1305へ進める。ステップS1305において、CPU112は、選択したCSのメモリデバイスの電源スイッチに電源ONの設定を実行し、これにより、選択したCSのメモリデバイスに対する通電が再開される。

40

#### 【0085】

次に、ステップS1306において、CPU112は、選択したCSのメモリデバイスからステップS1302で書き込みを行ったアドレスの値を読み出し、書き込みデータと比較する。そして、ステップS1307において、CPU112は、選択したCSのメモリデバイスのメモリタイプを判断する。具体的には、CPU112は、ステップS1306での比較の結果に基づき、全ての書き込みデータと読み込みデータとが一致している場合には、選択したCSのメモリデバイスは不揮発性メモリであると判断する。一方、CPU112は、全ての書き込みデータと読み込みデータとが一致しない場合には、選択した

50

C S のメモリデバイスは揮発性メモリデバイスであると判断する。ステップS 1 3 0 7の後、処理はステップS 1 3 0 1へ戻される。

#### 【0086】

このような処理により、DDR3 SDRAMである第1のRAM120については、揮発性メモリであるとの判断がなされ、DDR3 MRAMである第2のRAM121については、不揮発性メモリであるとの判断がなされる。

#### 【0087】

以上の電源の遮断を利用した不揮発性 / 挥発性メモリ検出シーケンスによれば、メモリデバイスが不揮発性か否かを判断することが可能となる。よって、MFP100に実装されたメモリデバイスに不揮発性メモリと揮発性メモリとが混在して実装されていても、省電力モードにあるときの消費電力を小さく抑えることができる。10

#### 【0088】

##### <第5実施形態>

上記第1及び第2実施形態では、MFP100の起動時におけるメモリデバイスに対するマッピングについて、また、上記第3及び第4実施形態では、MFP100の起動時及び省電力モードへの移行時の電源制御処理について説明した。これに対して、本実施形態では、MFP100が備える各種機能（コピー機能、プリント機能、送信機能）の実行時における電源制御について、図14を参照して説明する。

#### 【0089】

図14は、MFP100の動作時における電源制御シーケンスのフローチャートである。20 図14のフローチャートの各処理は、CPU112がROM113に格納されている起動プログラムを読み出し、第1のRAM120又は第2のRAM121に展開し、実行することによって実現される。

#### 【0090】

MFP100が実行可能なコピー動作やプリント動作、送信動作等の各動作では、中間画像データ等を格納するためのワークメモリとして必要なメモリ容量が異なる。したがって、本実施形態では、各動作に必要なメモリ容量に応じて、メモリデバイスに対する電源の切り替え動作を実施することとし、図14のフローチャートは、そのキャリブレーション方法を示している。

#### 【0091】

MFP100に電源が投入されると、先ず、ステップS 1 4 0 1において、CPU112は、第1実施形態及び第3実施形態で説明した初期化シーケンスを実施する。これにより、F/Wが所定のメモリデバイスに格納され、また、電源制御メモリリストが作成（更新）されて、MFP100はスタンバイ状態となる。本実施形態では、第1のRAM120が揮発性メモリであるため、第1のRAM120に一時的に使用される中間画像データ等が保持されるものとする。また、第2のRAM121は不揮発性メモリであるため、第2のRAM121にF/Wが格納されるものとする。30

#### 【0092】

続くステップS 1 4 0 2において、CPU112は、ジョブが投入されたか否かを判定し、ジョブが投入されるまで待機し（S 1 4 0 2でNO）、ジョブが投入されると（S 1 4 0 2でYES）、処理をステップS 1 4 0 3へ進める。ステップS 1 4 0 3において、CPU112は、ジョブがコピー動作か否かを判断する。CPU112は、コピー動作である場合（S 1 4 0 3でYES）、処理をステップS 1 4 0 6へ進め、コピー動作ではない場合（S 1 4 0 3でNO）、処理をステップS 1 4 0 4へ進める。なお、コピー動作とは、MFP100のフィーダにセットされた原稿の画像をスキャナ部で取り込み、色変換や濃度変換、エッジ強調処理、スクリーン処理等の画像処理を施して、プリンタ部102で紙（シート）面上に画像形成し、出力する動作である。40

#### 【0093】

ステップS 1 4 0 4において、CPU112は、ジョブがプリント動作か否かを判断する。CPU112は、プリント動作である場合（S 1 4 0 4でYES）、処理をステップ50

S 1 4 0 6 へ進め、プリント動作ではない場合（S 1 4 0 4 でNO）、処理をステップS 1 4 0 5 へ進める。なお、プリント動作とは、ホストコンピュータ150や不図示のUSB等の外部装置から受信したPDLやJPEG等の画像データに対して、レンダリング処理や色変換、濃度変換、エッジ強調処理、スクリーン処理等の画像処理を実行し、プリンタ部102で紙（シート）面上に画像形成し、出力する動作である。

#### 【0094】

ステップS 1 4 0 5において、CPU112は、ジョブが送信動作か否かを判断する。CPU112は、送信動作である場合（S 1 4 0 5 でYES）、処理をステップS 1 4 0 6 へ進め、送信動作ではない場合（S 1 4 0 5 でNO）、処理をステップS 1 4 1 1 へ進める。なお、送信動作では、先ず、MFP100のフィーダにセットされた原稿の画像がスキヤナ部で読み取られ、色変換や濃度変換、エッジ強調処理、圧縮処理等の画像処理が施されて、JPEG形式等のファイルが作成される。その後、作成されたファイルは、指定された電子メールアドレスにネットワークを介して送信され、或いは、モデムに接続された電話回線を通じて外部のファクシミリ装置へ送信される。なお、ステップS 1 4 0 3 ~ 1 4 0 5 の各処理（判断）は、順序を問わず、どの判断が先に行われてもよい。

10

#### 【0095】

ステップS 1 4 0 6において、CPU112は、ステップS 1 4 0 3 ~ S 1 4 0 5 のいずれかの処理に対して必要なワークメモリ領域（メモリ使用量）を計算する。CPU112は、コピー動作及び送信動作の場合には、中間画像データであるスキャンデータを一時保持するために、用紙サイズ等に基づきワークメモリ領域を計算する。プリント動作の場合、CPU112は、中間言語データやラスター画像データ等を一時保持するためのワークメモリ領域とプリント時に必要なワークメモリ領域とを、用紙サイズ等に基づいて計算する。その結果として、CPU112は、ステップS 1 4 0 1 の初期化シーケンスで実行したメモリマッピングの結果に従って使用すべきメモリデバイスを選択する。

20

#### 【0096】

続くステップS 1 4 0 7において、CPU112は、第3実施形態に従って全てのCSのメモリデバイスに対して電源制御の設定を更新する処理を行い、処理が行われていない残りのCSが有るか否かを判断する。CPU112は、残りCSが有る場合（S 1 4 0 7 でYES）、処理をステップS 1 4 0 8 へ進め、残りCSが無い場合（S 1 4 0 7 でNO）、処理をステップS 1 4 1 1 へ進める。

30

#### 【0097】

ステップS 1 4 0 8において、CPU112は、ステップS 1 4 0 7 で選択したCSのメモリデバイスが、ステップS 1 4 0 6 において使用するメモリデバイスとして選択されているか否かを判断する。CPU112は、使用するメモリデバイスとして選択されていない場合（S 1 4 0 8 でNO）、処理をステップS 1 4 0 9 へ進め、使用するメモリデバイスとして選択されている場合（S 1 4 0 8 でYES）、処理をステップS 1 4 1 0 へ進める。

#### 【0098】

ステップS 1 4 0 9において、CPU112は、選択したCSのメモリデバイスは使用されないと判断し、第3実施形態のステップS 1 2 0 3 ~ S 1 2 0 7 で実行した省電力モードへの移行処理を実施する。なお、このとき、各CSのメモリデバイスに対して電源がOFFされたとしても、他のメモリデバイスが動作することができるよう、例えば、信号タイミングの調整等が行われる。ステップS 1 4 1 0 において、CPU112は、選択したCSのメモリデバイスが省電力モードに入っていて電源がOFFとなっている場合には、省電力モードから通常の動作モードへ復帰させる。なお、ステップS 1 4 1 0 では、選択したCSのメモリデバイスが通常の動作モードにあるときには、特に処理がおこなわれることはない。ステップS 1 4 0 9, S 1 4 1 0 の後、CPU112は、処理をステップS 1 4 0 7 へ戻す。

40

#### 【0099】

ステップS 1 4 1 1 において、CPU112は、実行したジョブが終了したか否かを判

50

断する。CPU112は、ジョブが終了するまで待機し(S1411でNO)、ジョブが終了すると(S1411でYES)、処理をステップS1412へ進める。ステップS1412において、CPU112は、次のジョブが有るか否かを判断する。CPU112は、次のジョブが有る場合(S1412でYES)、処理をステップS1403へ戻し、次のジョブが無い場合(S1412でNO)、処理をステップS1413へ進める。

#### 【0100】

ステップS1413において、CPU112は、全てのメモリデバイスに対して第3実施形態のステップS1203～S1207で実行した省電力モードへの移行処理を実施する。その後、処理はステップS1402へ戻される。

#### 【0101】

以上の電源制御方法を用いて、ジョブが投入されたときでも不要なメモリデバイスを省電力モードに移行するようにすることで、MFP100の消費電力を低く抑えることができる。

#### 【0102】

##### <その他の実施形態>

以上、本発明をその好適な実施形態に基づいて詳述してきたが、本発明はこれら特定の実施形態に限られるものではなく、この発明の要旨を逸脱しない範囲の様々な形態も本発明に含まれる。更に、上述した各実施形態は本発明の一実施形態を示すものにすぎず、各実施形態を適宜組み合わせることも可能である。

#### 【0103】

なお、第1実施形態では、MFP100を構成するモジュールをハードウェアとしてサポートした(図1参照)。これに対して、画像処理部119等の所定のモジュールについては、ROM113に格納されたプログラムをCPU112が実行することで、その機能が実現されるようにしてもよい。その場合、例えば、インタプリタ117、レンダラ118及び画像処理部119の機能を実現する各プログラムは、揮発性メモリへの各種データの読み込み/書き込み機能をサポートするものとする。

#### 【0104】

本発明は以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)をネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(又はCPUやMPU等)がプログラムコードを読み出して実行する処理である。この場合、そのプログラム、及び該プログラムを記憶した記憶媒体は本発明を構成することになる。

#### 【符号の説明】

#### 【0105】

|     |           |

|-----|-----------|

| 100 | MFP       |

| 112 | CPU       |

| 113 | ROM       |

| 114 | メモリコントローラ |

| 120 | 第1のRAM    |

| 121 | 第2のRAM    |

| 901 | 第1の電源スイッチ |

| 902 | 第2の電源スイッチ |

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

| address | value | contents                                    |

|---------|-------|---------------------------------------------|

| 02h     | 0x0B  | Memory Type (General)                       |

| 04h     | 0x02  | SDRAM device density and banks              |

| 12h     | 0x0F  | Minimum SDRAM cycle time(tCK_MIN) 1.875ns   |

| 14h     | 0x1C  | CAS latencies supported CA58.7.6            |

| 16h     | 0x69  | Minimum CAS latency time(tAA_MIN) 13.125ns  |

| 17h     | 0x78  | Minimum write recovery time(tWR_MIN) 15ns   |

| 18h     | 0x69  | Minimum RAS to CAS delay(tRCD_MIN) 13.125ns |

| 100h    | 0x0   | Volatile                                    |

(a)

| address | value | contents                                    |

|---------|-------|---------------------------------------------|

| 02h     | 0x0B  | Memory Type (General)                       |

| 04h     | 0x02  | SDRAM device density and banks              |

| 12h     | 0x0F  | Minimum SDRAM cycle time(tCK_MIN) 1.875ns   |

| 14h     | 0x1C  | CAS latencies supported CA58.7.6            |

| 16h     | 0x69  | Minimum CAS latency time(tAA_MIN) 13.125ns  |

| 17h     | 0x78  | Minimum write recovery time(tWR_MIN) 15ns   |

| 18h     | 0x69  | Minimum RAS to CAS delay(tRCD_MIN) 13.125ns |

| 100h    | 0x1   | Volatile                                    |

(b)

【図6】

| パラメータ                | degree | 第1のRAM | 第2のRAM |

|----------------------|--------|--------|--------|

| write clk 対 dqs スキュー | bank0  | 90     | 98     |

|                      | bank1  | 92     | 99     |

|                      | bank2  | 93     | 100    |

|                      | bank3  | 95     | 101    |

|                      | bank4  | 96     | 102    |

|                      | bank5  | 98     | 104    |

|                      | bank6  | 100    | 106    |

|                      | bank7  | 101    | 107    |

| リードレイテンシ             | bank0  | 270    | 252    |

|                      | bank1  | 271    | 254    |

|                      | bank2  | 273    | 255    |

|                      | bank3  | 275    | 257    |

|                      | bank4  | 277    | 258    |

|                      | bank5  | 279    | 260    |

|                      | bank6  | 281    | 261    |

|                      | bank7  | 283    | 263    |

| リードレイテンシ             | cycle  | 7      | 8      |

【図7】

| リスト         |              | 値   | アドレス        |

|-------------|--------------|-----|-------------|

| F/W 格納リスト   | chip select0 | No  | 0x8000_0000 |

|             | chip select1 | Yes | 0x0000_0000 |

|             | chip select2 | 未実装 | -           |

|             | chip select3 | 未実装 | -           |

|             | chip select4 | 未実装 | -           |

|             | chip select5 | 未実装 | -           |

|             | chip select6 | 未実装 | -           |

|             | chip select7 | 未実装 | -           |

| F/W 格納可能リスト | chip select0 | No  | -           |

|             | chip select1 | Yes | -           |

|             | chip select2 | 未実装 | -           |

|             | chip select3 | 未実装 | -           |

|             | chip select4 | 未実装 | -           |

|             | chip select5 | 未実装 | -           |

|             | chip select6 | 未実装 | -           |

|             | chip select7 | 未実装 | -           |

| ワークメモリリスト   | chip select0 | Yes | -           |

|             | chip select1 | No  | -           |

|             | chip select2 | 未実装 | -           |

|             | chip select3 | 未実装 | -           |

|             | chip select4 | 未実装 | -           |

|             | chip select5 | 未実装 | -           |

|             | chip select6 | 未実装 | -           |

|             | chip select7 | 未実装 | -           |

【図8】

【 四 9 】

【図10】

【図 1 1】

| リスト             |              | 値   |

|-----------------|--------------|-----|

| 電源OFFメモリリスト     | chip select0 | No  |

|                 | chip select1 | Yes |

|                 | chip select2 | 未実装 |

|                 | chip select3 | 未実装 |

|                 | chip select4 | 未実装 |

|                 | chip select5 | 未実装 |

|                 | chip select6 | 未実装 |

|                 | chip select7 | 未実装 |

| セルフリフレッシュメモリリスト | chip select0 | No  |

|                 | chip select1 | No  |

|                 | chip select2 | 未実装 |

|                 | chip select3 | 未実装 |

|                 | chip select4 | 未実装 |

|                 | chip select5 | 未実装 |

|                 | chip select6 | 未実装 |

|                 | chip select7 | 未実装 |

| 電源制御なしメモリリスト    | chip select0 | No  |

|                 | chip select1 | No  |

|                 | chip select2 | Yes |

|                 | chip select3 | Yes |

|                 | chip select4 | Yes |

|                 | chip select5 | Yes |

|                 | chip select6 | Yes |

|                 | chip select7 | Yes |

【図 1-2】

【図13】

【図14】

---

フロントページの続き

(56)参考文献 特開昭58-125125(JP,A)

特開平4-248641(JP,A)

特開2012-33002(JP,A)

米国特許出願公開第2009/0144577(US,A1)

米国特許出願公開第2012/0324251(US,A1)

米国特許第8051253(US,B2)

米国特許第5918242(US,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 00

G 06 F 12 / 06