**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>5</sup>

G11B 27/02

(45) 공고일자 1992년08월10일

(11) 공고번호 특 1992-0006646

---

|           |                |           |                |

|-----------|----------------|-----------|----------------|

| (21) 출원번호 | 특 1984-0005355 | (65) 공개번호 | 특 1985-0002137 |

| (22) 출원일자 | 1984년08월31일    | (43) 공개일자 | 1985년05월06일    |

---

|            |                                                             |

|------------|-------------------------------------------------------------|

| (30) 우선권주장 | 528229 1983년08월31일 미국(US)                                   |

| (71) 출원인   | 알 씨 에이 코포레이션 글렌 에이춰. 브루스 헬<br>미합중국, 뉴욕 10020, 뉴욕, 록펠러프라자 30 |

|          |                                     |

|----------|-------------------------------------|

| (72) 발명자 | 찰스 마틴 와인                            |

| (74) 대리인 | 미합중국, 뉴저지, 프린스턴, 해밀턴 애비뉴 144<br>이병호 |

**심사관 : 강응선 (책자공보 제2893호)**

---

**(54) 비데오 동기장치**

---

**요약**

내용 없음.

**대표도**

**도1**

**형세서**

[발명의 명칭]

비데오 동기장치

[도면의 간단한 설명]

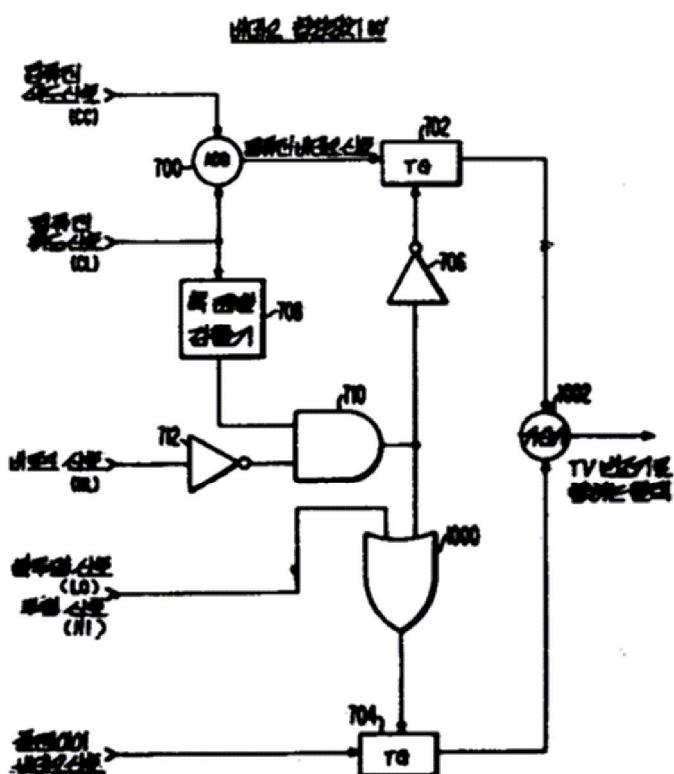

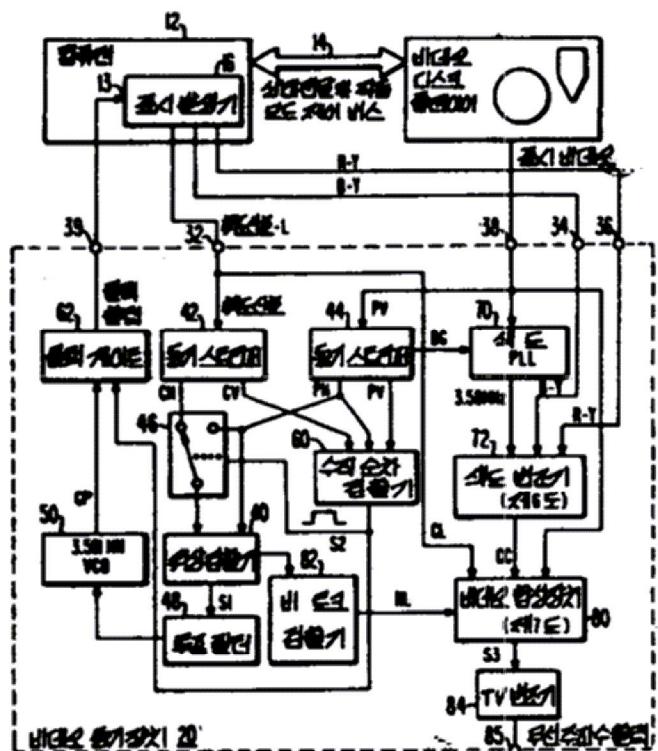

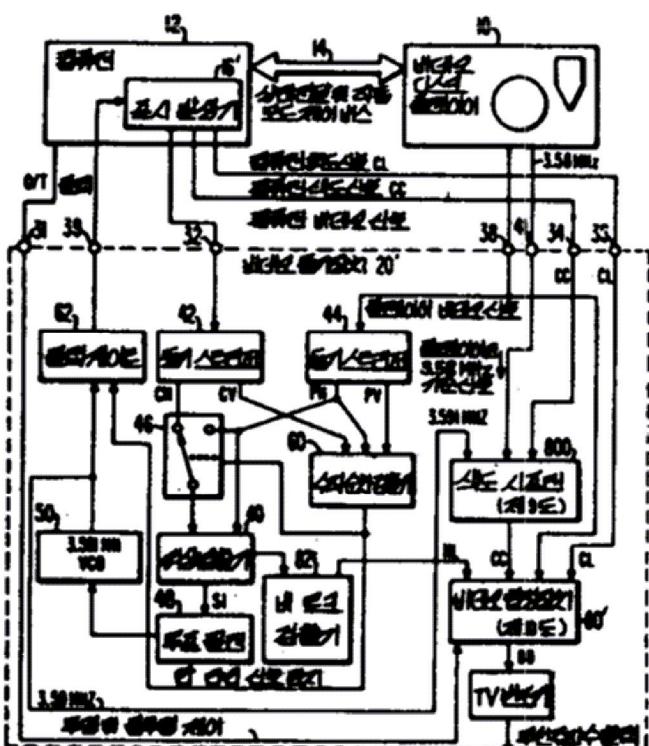

제1도는 본 발명을 구체화한 비데오 동기장치를 구비한 컴퓨터 제어 비데오 디스크 플레이어 시스템에 대한 블럭선도.

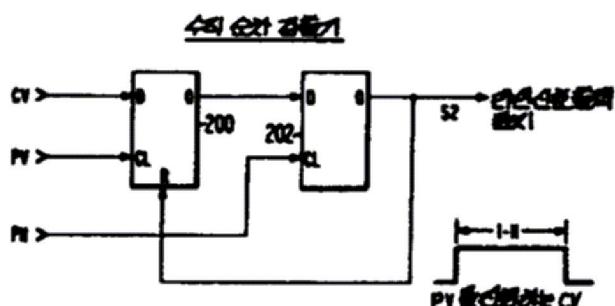

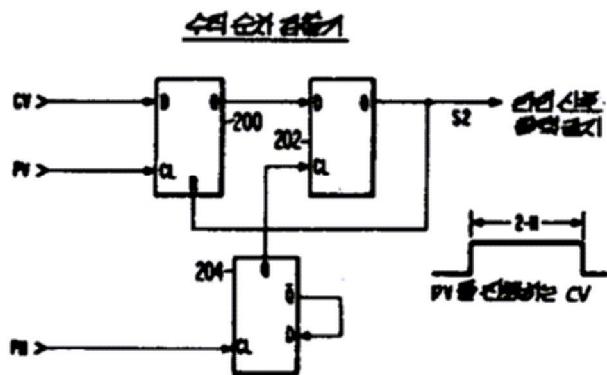

제2도 및 제3도는 본 발명을 구체화한 1비데오 동기장치에 이용하기 적합한 수직 순차 검출기에 대한 논리선도.

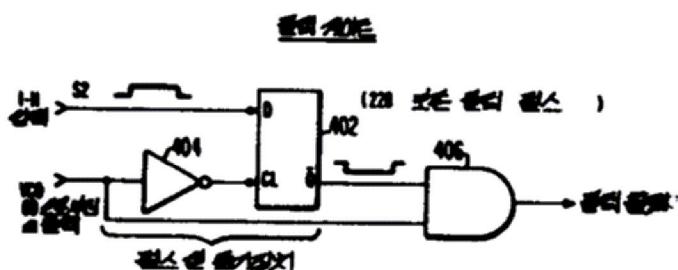

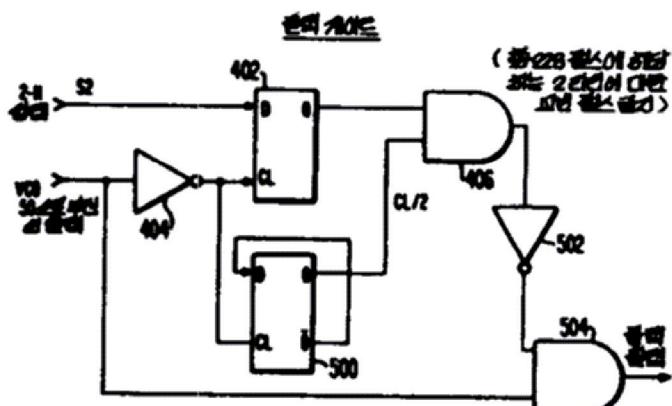

제4도 및 제5도는 본 발명을 구체화한 비데오 동기장치에 이용하기 적합한 펄스 강하 회로.

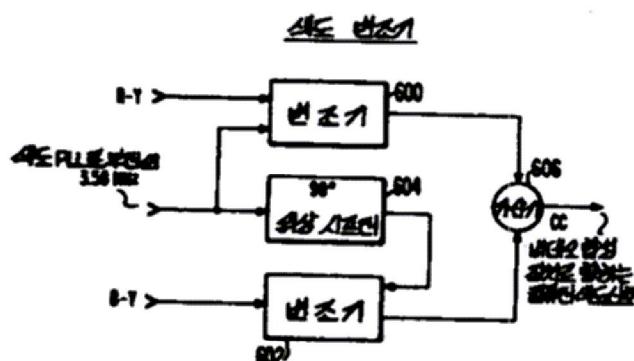

제6도는 제1도의 비데오 동기장치에 이용하기 적합한 색도 변조기에 대한 블럭선도.

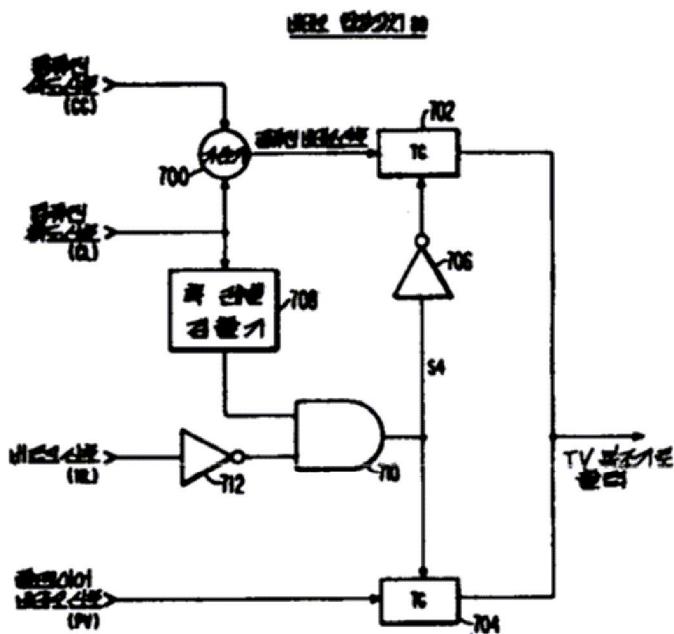

제7도는 제1도의 동기장치에 이용하기 적합한 비데오 합성장치에 대한 블럭선도.

제8도는 제1도의 컴퓨터 제어식 비데오 디스크 플레이어 시스템을 변형한 시스템에 변형한 시스템에 대한 블럭선도.

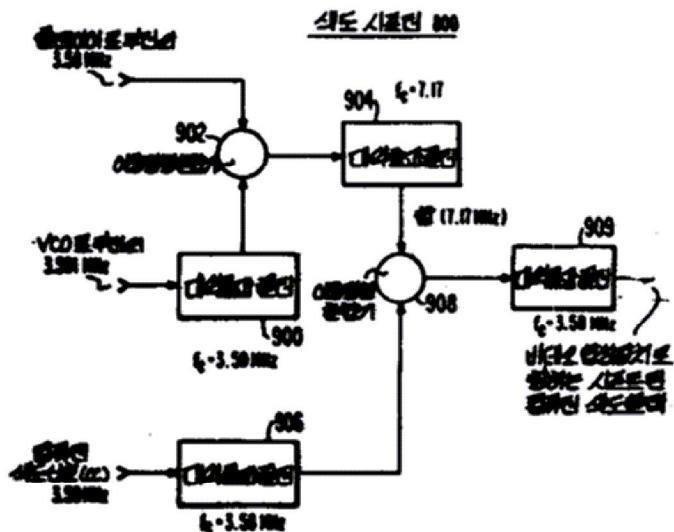

제9도는 제8도의 시스템에 이용하기 적합한 색도 신호 시프터에 대한 블럭선도.

제10도는 제8도의 비데오 동기장치에 이용하기 적합한 비데오 합성 장치에 대한 블럭선도.

\* 도면의 주요부분에 대한 부호의 설명

20 : 비데오 동기장치 40 : 위상 검출기

42,44 : 동기 스트리퍼(stripper) 50 : 전압 제어형 발진기

60 : 수직 순차검출기 62 : 클럭 게이트

[발명의 상세한 설명]

본 발명은 비데오 시스템에 관한 것이며 특히, 비데오 동기장치에 관한 것이다. 비데오 동기장치는 예를 들면, 여러가지 비데오원(예를들면, 카메라, VTR 등)을 공동 표준 오디오 타이밍 신호원에 동기시키기 위하여 텔레비전 수신기에 이용된다. 상업적인(방송질) 동기장치(예를들면, 프레임 보존장치)는 가정용 컴퓨터 제어식 비데오 게임과 같은 다른 신호원을 구비한 디스크나 테이프 플레이어와 같은 소비자 비데오 제품을 동기시킬 경우에는 너무 비싸다. 공지된 바와같이, 이러한 비데오 시스템은 라인 비율과 칼라 부반송파 주파수 허용 오차에 대해 NTSC표준과 부응하는 비데오 출력신호를 일반적으로 제공하는것 않는

다.

소비자 비데오 제품에 대한 비데오 동기화의 문제점에 관한 해결 방법은 1982년 8월 24일 베어등에게 허여된 "컴퓨터 제어식 비데오를 다른 비데오원에 동기 시키기 위한 장치"라는 명칭의 미합중국 특허원 제4,346,407호에 공개된다. 베어등의 시스템은 비교적 값비싼 프레임이나 라인 보존장치를 이용하는 것을 피하는 것이 바람직하다. 베어등의 시스템에서 주파수 간섭성을 얻기 위해 다른 비데오원의 수평 동기 주파수의 몇 배의 주파수에서 컴퓨터 제어식 비데오원에 클럭 필스를 제공하고, 두 비데오원으로부터의 신호 사이의 위상 비간섭성을 검출하여 여기에 응답하여 예정된 주기동안 클럭필스는 컴퓨터 제어식 비데오원이 동기에서 벗어나 위상 간섭성을 얻게 되는 것을 허용하지 않게 컴퓨터 제어식 비데오원(예를들면, 가정용 컴퓨터나 비데오 게임)을 다른 비데오원(예를들면, 디스크나 테이프 플레이어)에 동기 시키게 된다.

베어등의 시스템은 종래의 프레임이나 라인 보존장치를 이용하지 않고서 외부에 발생된 비데오의 비데오 원에 컴퓨터에서 발생된 비데오 신호를 로크(lock)하는 목적을 이룬다. 그러나, 이러한 장점은 어떤 회생없이 얻어지지는 않는다. 특히 베어등에 따르면, 실례로든 시스템의 위상 로크 루프 성분중 하나는 위상 로크를 이루는데 최고 910필드를 필요로 한다. 이는 약 15초의 로크업(lock-up)시간과 대응한다. 본 발명은 910필드(15초)이하의 로크업 시간을 갖는 동기장치를 제공하기 위한 것이다. 본 발명은 또한, 가격 개선을 위해 단순화된 설계 즉, 개선된 신뢰도를 갖는 동기장치를 제공하기 위한 것이다.

컴퓨터 제어식 비데오 신호의 제1신호원을 제2비데오 신호원에 동기시키기 위한, 본 발명을 구체화한 비데오 동기장치를 비데오 신호를 수신하기 위해 비데오원에 연결하기 위한 입력수단과, 클럭 필스를 공급하기 위해 제1비데오 신호원에 연결하기 위한 출력을 포함한다. 위상 검출수단은 비데오 신호의 수평 성분을 수신하고 에러신호를 발생하기 위하여 입력수단에 결합된다. 제어된 발진기는 이 발진기에 클럭필스를 공급하고, 비데오 신호의 수평 성분을 동기 시키기 위해 클럭필스율을 변경시키기 위하여 에러신호에 응답하는 출력수단에 결합한다. 순차 검출수단을 제1비데오 신호원의 수직 성분이 제2비데오 신호원의 수직성분을 앞설때 한 수평라인의 지속기간의 정수배와 실제로 동일한 지속기간을 갖는 제어신호를 발생하기 위해 입력수단에 결합된다. 클럭 게이팅(gating)수단은 제어신호가 나타날때 예정된 수의 클럭 필스 사이클을 단속하기 위하여 제어신호에 응답하는데, 단속된 클럭 필스의 수는 정부배와 실제로 무관하고, 단속된 클럭사이클의 지속시간의 합은 제1비데오 신호원의 수직 성분을 제2비데오 신호원의 수직 성분에 동기시키기 위해 1수평 라인과 실제로 동일하다.

본 발명의 한 실시예에 따르면, 정수 배수는 N이고, 단속된 클럭필스는 제어신호가 나타날때 제어할수 있는 발진기에 의해 발생된 각각의 N클럭 필스중 하나와 대응한다. 제1도의 시스템은 버스(14)를 통해 비데오 디스크 플레이어(10)에 결합된 컴퓨터(12)를 이용하여 비데오 디스크 플레이어(10)를 제어한다. 버스(14)는 컴퓨터 상태 및 프로그램 데이터 정보를 컴퓨터(12)에 전달하고, 여러가지 플레이어 작동 모드(예를들면, 탐색, 주사, 플레이, 중지등)를 제어하기 위해 제어 데이터를 플레이어(10)에 전달한다. 컴퓨터(12)는 가정용이나 개인용 컴퓨터거나 컴퓨터 제어식 게임이며, 영문자나 그래픽 도안을 제공하기 위하여 클럭된 표시발생기(16)를 포함한다.

이러한 본 발명의 실시예에서, 컴퓨터(12)에서 표시 발생기(16)에 의해 발생된 비데오 신호는 휴드출력 신호 L 및 두 색차신호 R-Y 및 B-Y를 포함하는 성분이다. 비데오 디스크 플레이어(10)는 광학형 혹은, 커패시턴스형으로 구성되며, 플레이어 비데오 출력신호를 합성형태로 제공하는데, 여기서 칼라성분은 NTSC 표준 주파수(약 3.58MHz)의 칼라 부반송파 신호상에서 각각 진폭 변조되어 휴드신호 성분에 부가되어 화성 플레이어 비데오신호를 형성한다.

이러한 목적은 종래의 텔레비전 수상기에 표시하기 위해 단일 비데오 신호를 형성하도록 컴퓨터 및 플레이어 비데오 신호를 합성하기 위한 것이다. 플레이어는 자체 자율시간을 가지며 전 프레임 보존장치와 같은 방법을 사용하지 않고서는 외부신호와 동기될 수 없는 문제점이 있다. 비데오 발생 컴퓨터나 컴퓨터 게임은 표준 텔레비전 신호조차 발생하지 않는다. 전형적으로, 한 라인에서 3.58MHz사이클의 수는 수

**455**

평 라인 주파수의  $\frac{1}{2}$  배에 해당하는 NTSC값이 아니며, 주사라인의 수는 525가 아니다.

제1도의 시스템에 대한 실시예에서, 비데오 동기 장치(20)(점선으로 윤곽이 그려짐)는 컴퓨터에 의해 발생된 비데오 신호(Y,R-Y,B-Y)를 플레이어 비데오 신호 PV에 동기시킨다. 동기장치(20)는 각각 L,B-Y,R-Y 및 PV신호를 수신하기 위한 단자(32),(34),(36),(38)를 포함하는 입력수단과, 컴퓨터(12)내의 표시발생기의 클럭 입력단자CL에 클럭필스를 공급하기 위한 단자(39)를 포함하는 출력수단을 포함한다.

뉴저지, 서머빌 소재의 알 씨 에이의 고체상태 분야에서 유용한 CD 4046집적회로와 같은 위상 검출기(40)는 컴퓨터(12) 및 플레이어(10)의 비데오 신호의 수평성분을 수신하여 수평 위상 에러를 나타내는 에러신호 S1을 발생하기 위한 입력수단의 단자(32),(38)에 결합된다. 이러한 위상 검출기는 위상 로크의 유무를 나타내는 신호를 제공하는 로크 검출기를 포함한다. 단자(32),(38)에 연결된 입력을 구비한 두 동기 스트리퍼(42),(44)를 이용하여 결합이 이루어진다. 스트리퍼(42)는 표시 발생기(16)로부터 휴드신호 L를 수신하며, 컴퓨터 수평 동기 신호(CH) 및 수직 동기신호(CV)를 제공한다. 동기 스트리퍼(44)는 플레이어비데오 신호(PV)를 수신하고 플레이어 수평 동기신호(PH) 및 플레이어 수직 동기신호(PV)를 제공한다. 신호 PH는 위상검출기(40)의 한 입력에 직접 인가되고, 신호 CH는 스위치(40)를 통하여 검출기(40)의 다른 입력에 인가된다. 스위치(46)는 수직 동기가 이루어질때 도시된 위치에 있지만, 설명된 바와 같이 에러신호 S1의 일시적인 혼신을 방지하도록 수직 동기를 필요로 하는 동안 검출기(40)의 입력을 단락상태로 되도록 변경된다. 에러신호 S1은 루프가 편심률과 같은 디스크 결점에 의해 생길 수 있는 트랙의 변화를 허용할 수 있을 정도로 충분히 넓은 대역(예를들면, 200 내지 300 Hz)을 갖는 루프 필터(48)에서 평활화된다. 평활화 된 후, 에러신호 S1은 표시 발생기(16)의 수평 라인비율(CH)을 플레이어(10)의 수평 라인 비율(PH)에 로크하기 위하여 클럭필스 CP를 출력수단(단자(39))에 공급하는 전압 제어형 발진기(50)에 인가된다.

동기 스트리퍼(42), (44)를 통하여 입력수단에 결합된 수직 순차 검출기(60)를 이용하여 수직 동기가 이루어진다. 특히, 수직 순차 검출기(60)는 컴퓨터 수직 동기신호(CV), 플레이어 수직 동기 신호(PV) 및 플레이어 수평 동기 신호(PH)를 수신하며, 컴퓨터의 수직 성분 CV이 플레이어의 수직 성분 CP를 진행할 때 수평 라인의 정수배와 실제로 동일한 지속기간을 갖는 제어신호 S2를 발생한다.

클럭게이트(62)는 신호S2가 나타날 때 CV를 PV에 로크하기 위하여 예정된 수의 클럭펄스 사이클을 효과적으로 인터럽트하기 위해 전압 제어형 발진기(50)의 출력회로에 삽입하고, 신호 S2에 응답한다. 신호 S2는 또한 스위치(46)를 이용하여 위상 검출기(40)의 입력을 단락시킨다.

매우 급히(예를들면, 상기 시스템에서의 15조 로크와 비교해 볼 때 약 2초 이내) 일어나는 본 발명의 수직동기 로크 특징을 설명하기 위하여 두 실시예가 설명된다. 제1실시예에서와 같이 신호 S2는 1-H의 지속시간을 갖는 것으로 추정하자. 스위치 S2가 활성화되어 위상 검출기(40)의 입력을 단락시킬 때 전압 제어형루프(50)의 중앙 주파수가 3.591MHz로 설정된다. 이 주파수는 3.58MHz인 NTSC 표준보다 약간 높다. 그 결과로, 컴퓨터 표시 발생기(16)는 정상의 수직 및 수평 비율보다 약간 높은 비율을 갖는다. 3.591MHz의 특정 클럭 주파수는 플레이어(10)에 대해 추정된 60Hz의 필드비율과, 수평 라인당 228클럭 사이클과, 매초당 15750라인을 기준으로 한다.

이 실시예에서, 컴퓨터 수직동기가 플레이어 수직 동기 이전에 발생하는 모든 필드에서 228 클럭사이클(1라인에 해당)을 생략함으로써 수직 동기가 이루어진다. 신호 S2가 1-H의 지속시간을 갖는다고 추정된 상태에서, 생략된 클럭 사이클은 228개의 보존 사이클이다. 제2실시예에서, 신호 S2의 지속시간을 2-H와 동일하게 함으로써 상기와 동일한 전체 효과를 얻을 수 있다. 이 경우에, 두 라인에 대해 교번 클럭 펄스가 검출되지만 검출된 펄스의 총수는 동일한 수(228)로 남는다. 고속의 수직 로크를 제공하는 본 발명의 클럭라인 금지 양상에 대한 종합적인 관계에 있어서, 인터럽트된 클럭펄스의 수는 신호 S2가 나타날 때 라인의 수(정수)와 실제로 무관하고, 인터럽트된 클럭 사이클의 지속기간의 합은 실제로 한 수평 라인과 동일하다.

실시예로서, S2가 N라인과 동일할 때 금지된 클럭 펄스의 수는 신호 S2가 나타날 때 각각의 N클럭펄스 중 하나와 대응한다. N=1일 때 228보존펄스가 한라인에서 금지된다. N=2일 때 하나 건너 하나씩의 펄스가 총 228펄스에 해당하는 2라인에서 금지된다. N에 대한 양호한 값은 2나 그 이상이다. N=2이거나 그 이상인

것이 좋은 이유는 N=2일 경우 실효 클럭 주파수가 정상 주파수의  $\frac{1}{2}$  감소되기 때문이다. 이러한 것은 표시발생기(16)가 특정 최소 클럭비율을 구비하고, 1-H의 클럭 갭이 생기도록 허용될 경우 데이터를 내보내는 다이나믹 저항을 포함하는 경우에 좋다. 물론, 이러한 문제점은 표시 발생기(16)가 완전히 정적 상태일 경우 실재하지 않는다.

수직 로크가 구해지는 속도는 아래와 같은 요소에 의해 결정된다. 한 필드에는 약 262 라인이 있다. 표시발생기는 플레이어의 수직 위상과의 일치점에서 최대  $\frac{1}{2}$  필드나 131라인에 있다. 매 필드당 한 주사 라인이나 매초당 60주사 라인의 비율로 정정된다. 따라서, 최고  $\frac{131}{60}$  초나 2.18초 후에 로크된다.

제2도 및 제3도는 비데오 동기장치(20)에서 검출기(60)로 이용되는 1H 및 2H 수직 순차검출기에 대한 실시예이다. 제2도에서, 플립플롭(200)은 데이터 입력에서 CV를 수신하고 클럭 입력에서 PV를 수신하며 따라서, CV가 PV를 진행할 때마다 세트된다. 플립플롭(202)은 세트될 때 플립플롭(202)의 데이터(D) 입력을 장전하여 라인 비율 신호 PH가 발생하자마자 세트된다. 이 플립플롭(202)은 신호 S2의 시작부분을 발생하는데 이 신호는 플립플롭(200)을 리세트시킨다.

다음 라인을 시작하자 마자 플립플롭(202)의 D는 논리 0상태에서 플립플롭(202)이 정확히 1H 늦게 리세트된다. 모든 D 입력이 논리 0상태에 있으므로 PV가 CV를 진행할 경우 플립플롭의 상태는 변하지 않는다. 제3도는 제2도와 유사하지만 CV가 PV를 진행할 때 S2에 대해 2H의 지속기간을 제공한다. 이러한 것은 라인 비율신호 PH를 플립플롭(202)의 클럭입력에 인가하기 전에 2로 나누도록 연결된 플립플롭(204)에 의해 이루어진다.

제4도 및 제5도는 제1도의 동기 장치에서 제2도 및 제3도의 수직 순차 검출기와 함께 이용하기에 적합한 클럭 게이트에 대한 실시예를 나타낸 것이다. 제4도의 게이트는 한 라인(1H)동안 228 보존펄스를 누락한다. 반전기(404)는 클럭펄스의 하강에지에서 플립플롭(402)을 클럭하여 S1 신호를 각각의 클럭펄스의 단부와 동기시킨다. 반전된 Q 출력과 클럭신호는 AND게이트(406)에 인가된다. 따라서, 게이트(406)로부터의 모든 클럭펄스가 동기화되는데 즉, 게이팅된 펄스는 신호 S1에 의해 절단되지 않아서 표시발생기(16)에 스파이크나 특정펄스가 전달되지 않고 이에 의해 작동을 신뢰할 수 있게 되고 잡음 스파이크 현상에서 벗어나게 된다.

제5도의 클럭 게이트는 제4도의 클럭 게이트와 유사하지만 신호 S2에 대해 2H의 값으로 이용하도록 지정된다. 소자(402), (404), (406)는 2분할 플립플롭(500)이 계수 2로 게이트(406)의 클럭입력을 나누는 점을 제외하면 상기된 바와같이 작동한다. 게이트(406)의 출력은 반전기(502)에 의해 반전되고 전압 제어형발진기(50)로부터의 클럭신호와 함께 AND게이트(504)에 인가되어, 신호 S2가 나타날 때 하나 건너 하나씩의 클럭펄스가 검출된다.

제1도의 동기장치에서, 동기 스트리퍼(44)로부터의 칼라 버스트 게이트(BG)신호와 단자(38)로 부터의 플레이어 비데오 PV신호를 수신하는 색도 위상 로크 루프에 의해 색도가 처리된다. 신호 BG가 나타날 때 PLL에서의 전압 제어형 발진기는 플레이어의 칼라 부반송파 기준신호에 로크되어 색도변조기(72)는 3.58MHz의 기준 신호를 제공하는데, 여기서 색도 변조기(72)는 기본대역 색차 신호 R-Y 및 B-Y를 수신하여 플레이어 합성 비데오 신호의 색도 성분에 로크된 색도 출력신호 CC를 제공한다.

제6도는 컴퓨터 색도를 플레이어 색도 기준 주파수에 로크하기 위한 회로에 대한 실시예이다. R-Y 및 B-

Y 신호는 각각 변조기(600), (602)에 인가된다. 변조기(600)는 90° 위상 시프트 회로를 통해 변조기(602)에 인가되는 3.58MHz 색도 기준신호를 수신한다. 변조기 출력은 가산기(606)에서 합산되어, 플레이어 칼라 부반송파 주파수 및 위상에서 각각 진폭 변조된 컴퓨터 색도 신호를 CC를 제공한다.

컴퓨터 및 디스크 플레이어의 최종적으로 완전히 동기화된 비데오 출력신호는 위상 검출기(40)에 결합된 비로크 검출기(82)로부터의 비로크신호(NL)를 수신하고 컴퓨터 회도신호 CL, 컴퓨터 색도 신호 CC 및 합성 플레이어 비데오 신호 PV도 수신하는 비데오 합성 장치(80)에 의해 형성된다. 이러한 신호는 기본 대역신호를 발생하도록 비데오 합성장치(80)에 의해 처리되고, 이 기본 대역신호는 종래의 텔레비전 체널상에 무선주파수 출력신호를 제공하는 TV변조기(48)에 인가된다.

비데오 합성장치(80)는 여러가지 기능을 제공하고, 동기신호 왜곡을 피하도록(특히, 플레쉬 톤 왜곡을 피하도록) 특수하게 설계되어 칼라 충실도를 보존하게 된다. 플레이어가 고속 탐색모드에 있을 때 비데오 합성장치의 출력만을 자동적으로 표시하고 플레이어의 비데오가 유용할 때 정지 모드에 있도록 하기 위하여 비로크 신호를 이용한다. 비데오 합성장치는 플레이어 비데오에 대해 완전히 불투명한 컴퓨터 비데오 신호를 제공할 수도 있다.

비데오 합성장치(80)에서, 컴퓨터의 색도 신호 CC 및 회도신호 CL는 가산기(700)에서 합산되어, 게이트(702)가 인에이블될 때 전송 게이트(702)를 통해 TV변조기에 결합되는 합성 컴퓨터 비데오 신호를 발생한다. 플레이어 합성 비데오 신호 PV는 또 다른 전송 게이트(702) 및 게이트(704)는 이들 게이트의 출력이 서로 직접 연결되도록 하기 위해 결코 동시에 전도상태로 될 수 없다. 이와 같이 하면 합산회로에서 출력신호를 가산할 필요가 없으며, TV변조기에 인가된 비데오 신호가 서로에 대해 불투명하게 되는데 즉, 컴퓨터 비데오가 플레이어 비데오 등을 완전히 통과되지 않게 된다.

컴퓨터나 플레이어 비데오는 컴퓨터 휘도신호가 흑레벨이고 컴퓨터 비데오가 플레이어 비데오에 로크될 때 AND 게이트(710)를 인에이블시키는 흑레벨 검출기(708)에 의해 제공된다. 후자의 특징을 클럭 검출기가 컴퓨터 비데오가 로크상태(NL, 논리 1 상태)이라는 것을 나타낼 때 게이트(710)를 장전하고 로크순설이 있을 때 마다(NL, 논리 0 상태) 게이트(710)를 디스에이블 시키는 반전기(712)에 의해 제공된다. 플레이어만이 이러한 합성장치에 출력되므로 칼라나 동기신호 사이의 부가나 상층이 없으며 따라서, 칼라 시프트나 비정상적으로 높은 동기 레벨이 생기는 것을 방지하게 된다. 다시 말하면, 비데오는 -40IRE 내지 +100IRE 단위의 정상 범위내에 있다.

제8도에 도해된 시스템에서의 한가지 변화로는 3.5MHz의 플레이어 칼라 기준 주파수 신호가 비데오디스크 플레이어 칼라 처리회로에서 직접 구해지고 비데오 동기장치(20')의 부가된 입력단자(41)에 인가된다는 점이다. 이와 같이 되면 누락된 색도 PLL(70)의 필요성이 없어진다. 단자(41)는 색도 시프터(800)의 입력에 결합되는데, 색도 시프터(800)는 3.59MHz의 전압 제어형 발진기의 출력신호와 단자(34)로부터의 컴퓨터 색도신호 CC를 수신한다.

제9도에는 색도 시프터에 대해 상세히 도시된다. 시프터의 목적은 컴퓨터 색도(본 실시예에서 3.59MHz)를 플레이어 색도 주파수 및 위상으로 주파수 변환하는 것이다. 대역 통과 필터(900)는 컴퓨터 색도에 나타나는 전압제어형 발진기의 출력(3.59MHz)로부터의 고조파를 제거한다. 이중 평형 혼합기(902)는 플레이어 반송파(3.58MHz)를 여과된 컴퓨터 반송파(3.5gMHz)와 혼합한다. 최종의 합신호는 3.58MHz+3.59MHz +△로 생각될 수 있는데, 여기서 △는 컴퓨터 출력색도가 예상 상태이어서 시프트 되어야 하는 크기이다.

합 주파수(7.17MHz)에 동조된 또 다른 대역 통과 필터(904)는 차 주파수와 제1혼합기(102)로 부터의 불평형 출력을 제거한다. 시프트 될 컴퓨터 색도 신호(CC) 디지탈식으로 발생된 신호에 있는 고조파를 제거하는 3.58MHz의 대역 통과 필터에 인가된다. 이 신호는 반송파와 반송차 주변의 측피대로 생각될 수 있는데 여기서 반송파는 3.58MHz +△이다.

제2의 이중 평형 혼합기(908)는 필터(906)로 부터의 대역 제한된 색도를 필터(904)로 부터의 합 주파수와 결합된다. 또다시, 합신호 및 차 신호가 발생된다. 차는 3.58MHz +3.58MHz +△ -3.58MHz -△인데 이 차는 소망의 NTSC 표준인 3.58MHz와 동일하다.

제8도의 시스템은 제1도의 시스템과 유사하지만, 휘도, 색도 및 합성 비데오 출력신호를 발생하는 표시 발생기(16')를 구비하는 형태의 컴퓨터(12)와 함께 이용하기 위한 것이다. 또 다른 특성도 또한 비데오 합성장치에 부가되었고 색도 처리가 변경되었다. 상세히 설명하면, 컴퓨터 합성 비데오 신호 CV는 단자(32)에 인가되며, 단자(39)에서의 클럭신호는 표시 발생기에 인가된다. 제1도의 소자와 동일한 소자(42) 내지(60)에 의해 수직 및 수평 동기가 제공되고 따라서, 이러한 소자의 작동은 여기서 반복하지 않는다.

제8도의 실시예는 컴퓨터(12)에 의해(혹은 적절한 스위치에 의해) 제어된 불투명 및 투명 선택을 부가한 것이다. 이러한 선택으로 플레이어 및 컴퓨터 비데오 신호가 불투명하거나 텔레비전 수상기상에 동시에 표시되는 새로운 모드가 요구될 경우 비데오 합성장치(80')가 비데오 합성장치(80)의 불투명 모드로 작동하도록 허용한다. 그 결과는 부가처리에 의해 새로운 칼라가 생기므로 칼라가 수반되는 곳에서 특히 흥미롭다. 이러한 결과를 구하는데 있어서, 동기신호가 표준 동기레벨을 연기 위해 부가되지 않는 것이 중요하다.

상세히 설명해보면, 제10도의 비데오 합성장치는 OR 게이트(1000) 및 가산기(1002)와 같은 두개의 부가 소자를 포함하는 점을 제외하면 제7도의 비데오 합성장치와 동일하다. 불투명 및 투명신호(제8도의 단자(31))가 논리 1 상태일 때 게이트(100)는 무시되고 작동은 제7도에 설명된 것과 동일하다. 불투명 및 투명신호가 동일할 때 게이트(100)는 전송 게이트(704)를 계속 전도 상태로 유지시킨다. 이러한 경우 두 전송 게이트는 동시간에 전도상태로 될 수 있으므로 가산기(1002)는 단락 회로를 방지하도록 나타나고 TV변조기에 혼합된 활성 비데오를 제공한다. 활성 비데오가 혼합된다 할지라도 흑 레벨 검출기(708)는 컴퓨터 비데오 신호의 동기 간격동안 게이트(710)를 디스에이블시킨다. 마찬가지로, 이러한 모드에서 동기신호는 플레이어 비데오 신호에 의해서만 제공되지만 활성 비데오 신호는 두 비데오 원으로부터 합산

된다.

### (57) 청구의 범위

#### 청구항 1

제1컴퓨터 제어형 비데오 신호원을 제2비데오 신호원에 동기시키고, 상기 비데오 신호를 수신하기 위하여 상기 신호원에 연결된 입력수단과 클럭펄스를 공급하기 위하여 상기 제1비데오 신호원에 연결된 출력수단을 구비하는 비데오 동기장치로서, 상기 비데오 신호의 수평 성분을 수신하고 에러신호를 발생하기 위하여 상기 입력수단에 결합된 위상 검출수단(40)과 상기 클럭펄스를 공급하기 위해 상기 출력수단(62)에 연결되고, 상기 비데오 신호의 수평 성분에 동기 시키도록 클럭신호 비율을 변경시키기 위해 상기 에러신호에 응답하는 제어형 발진기 수단(50)과, 상기 제1비데오 신호원의 수직 성분이 상기 제2비데오 신호의 수직 성분을 앞설때 한 수평라인의 정수배와 동일한 지속기간을 갖는 제어신호(S2)를 발생하기 위하여 상기입력수단(42), (44)에 결합된 순차 검출기 수단(60)과, 인터럽트된 클럭펄스의 수가 실제로 상기 정부배와는 무관하고 인터럽트된 클럭 사이클의 시간 지속기간의 합이 상기 제1비데오 신호원의 수직 성분을 상기 제2비데오 신호원의 수직성분에 동기시키기 위해 한 수평 라인의 지속시간과 실제로 동일한 상태에서, 상기 제어신호가 나타날때 예정된 수효의 상기클럭 펄스의 사이클을 효과적으로 인터럽트 하기 위해 상기 제어신호에 응답하는 클럭 게이팅 수단(46)을 포함하는 것을 특징으로 하는 비데오 동기장치.

#### 청구항 2

제1항에 있어서, 상기 정수배수는 N이고, 인터럽트된 클럭펄스는 상기 제어신호가 나타날때 상기 제어할 수 있는 발진기 수단에 의해 발생된 각각의 N클럭 펄스중 하나와 대응하는 것을 특징으로 하는 비데오 동기장치.

#### 청구항 3

제3항에 있어서, N은 2과 동일하며, 이에 의해 전도성 클럭펄스는 1라인 동안 인터럽트 되는 것을 특징으로 하는 비데오 동기장치.

#### 청구항 4

제2항에 있어서, N은 2와 동일하며, 이에 의해 교번 클럭펄스는 2라인 동안 인터럽트 되는 것을 특징으로 하는 비데오 동기장치.

#### 청구항 5

제 2 항에 있어서, 상기 한 수평 라인의 상기 정수 배수는 상기 제 2 비데오 신호의 한 수평 라인의 정수배수인 것을 특징으로 하는 비데오 동기장치.

#### 청구항 6

제1항에 있어서, 상기제어신호가 나타날때 상기 위상 검출기를 효과적으로 디스에이블시키기 위해 상기 제어신호에 응답하는 수단을 구비하는 것을 특징으로 하는 비데오 동기장치.

#### 청구항 7

제1항에 있어서, 상기 클럭 게이팅 수단은 분수펄스가 상기 클럭 게이팅 수단을 통과하지 않도록 상기 펄스의 절단을 막기 위하여 펄스 동기 수단을 포함하는 것을 특징으로 하는 비데오 동기장치.

#### 청구항 8

제1항에 있어서, 상기 제 1비데오 신호원의 색도 성분을 상기 제 2 비데오 신호원의 색도 성분과 동기시키기 위하여 상기 입력수단에 결합된 색도 동기수단을 구비하는 것을 특징으로 하는 비데오 동기장치.

#### 청구항 9

제8항에 있어서, 상기 색도 동기 수단을 상기 제1비데오 신호원의 상기 색도 성분의 주파수 및 위상 전달에 영향을 미치기 위해 다수의 혼합기를 포함하는 것을 특징으로 하는 비데오 동기장치.

#### 청구항 10

제 8 항에 있어서, 상기 제1비데오 신호원의 색도 성분은 둘이상의 기본 대역 성분을 포함하고, 상기색도 동기 수단을 상기 기본 대역 성분을 상기 제 2 비데오 신호원의 색도 성분의 부반송파 주파수와 동일한 부반송파 주파수를 갖는 직각 진폭 변조된 색도 성분으로 변환하기 위해 다수의 변조기를 포함하는 것을 특징으로 하는 비데오 동기장치.

#### 청구항 11

제1항에 있어서, 상기 제1비데오 신호원의 휴도 레벨이 흘레벨에 있을때 상기 제2비데오 신호원의 비데오 신호를 나타내는 출력신호를 형성하고 상기 출력 비데오 신호를 출력단자에 결합하기 위한 출력수단을 구비하는 것을 특징으로 하는 비데오 동기장치.

#### 청구항 12

제11항에 있어서, 상기 제1비데오 신호원의 비데오 신호를 나타내는 출력 비데오 신호를 상기 출력단자

에 자동적으로 결합하기 위하여 상기 위상 검출기 수단에 결합되고 상기 출력 수단에도 결합된 비로크검출기 수단을 포함하는 것을 특징으로 하는 비데오 동기장치.

### 청구항 13

제12항에 있어서, 상기 출력 비데오 신호중 선택된 한 신호의 동기 부분이 상기 출력단자에 결합된 상태에서 비데오 라인의 활성 주기동안 상기 출력 비데오 신호를 상기 출력단자에 동시 결합시키기 위하여 활성화될때 응답하는 회로수단을 포함하는 것을 특징으로 하는 비데오 동기장치.

### 청구항 14

제1항에 있어서, 상기 제 1비데오 신호원의 비데오 신호의 휘도 레밸이 흑배밸에 있을 때 제 2 비데오신호원의 비데오 신호와 제1비데오 신호원의 비데오 신호를 나타내는 비데오 신호를 출력단자에 동시에 결합하기 위해 활성화 될 때 응답하는 회로 수단을 구비하는 것을 특징으로 하는 비데오 동기장치.

## 도면

## 도면1

## 도면2

도면3

도면4

도면5

도면6

도면7

도면8

## 도면9

### 도면 10