(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3553988号

(P3553988)

(45) 発行日 平成16年8月11日(2004.8.11)

(24) 登録日 平成16年5月14日(2004.5.14)

(51) Int.C1.<sup>7</sup>

F 1

H03K 3/037

H03K 3/037

H03K 19/01

H03K 19/01

H03K 19/20

H03K 19/20

Z

請求項の数 9 (全 9 頁)

(21) 出願番号

特願平5-54620

(22) 出願日

平成5年2月22日(1993.2.22)

(65) 公開番号

特開平6-29793

(43) 公開日

平成6年2月4日(1994.2.4)

審査請求日

平成12年2月2日(2000.2.2)

(31) 優先権主張番号

P4206082.6

(32) 優先日

平成4年2月27日(1992.2.27)

(33) 優先権主張国

ドイツ(DE)

(73) 特許権者 390039413

シーメンス アクチエンゲゼルシャフト

Siemens Aktiengesellschaft

ドイツ連邦共和国 D-80333 ミュンヘン

ヴィッテルスバッハーブラツツ

2

100075166

弁理士 山口巖

(72) 発明者 ヨーゼフ ヘルツレ

ドイツ連邦共和国 8939 パート ウエリスホーフエン ジュートヴェーク 8

審査官 石井研一

最終頁に続く

(54) 【発明の名称】同期ディジタル論理回路

## (57) 【特許請求の範囲】

## 【請求項 1】

同期ディジタル論理回路であって、

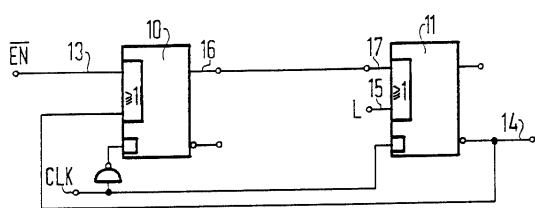

a ) 各 1 つのクロック入力端、少なくとも 2 つの互いに相補性の出力端および少なくとも 2 つの入力端を有する少なくとも第 1 および第 2 のクロック状態制御されるメモリ要素(10、11)が、第 1 のメモリ要素(10)の出力端の 1 つが第 2 のメモリ要素(11)の入力端の 1 つと接続されていることによって、縦続接続されており、

b ) 第 2 のメモリ要素(11)の一方の出力端が第 1 のメモリ要素(10)の第 1 の入力端に帰還結合されており、

c ) 第 1 のメモリ要素(10)の第 2 の入力端が同期ディジタル論理回路の入力端(13)と接続されており、第 2 のメモリ要素(11)の前記一方の出力端が同期ディジタル論理回路の出力端(14)としての役割をしており、

d ) メモリ要素のクロック入力端が互いに位相シフトされたクロック信号(CLK)により制御される

同期ディジタル論理回路において、

e ) メモリ要素(10、11)の各々がクロック状態制御される D フリップフロップおよびオア論理回路を含んでおり、

f ) オア論理回路の出力端が D フリップフロップの入力端と接続されており、メモリ要素の入力端がオア論理回路の入力端であり、メモリ要素の相補性出力端が D フリップフロップの相補性出力端であり、

10

g ) 各 2 つの縦続接続されているメモリ要素 ( 10 、 11 ) のクロック信号 ( C L K ) がメモリ要素の数により分周されたクロック周期の位相だけ互いに位相シフトされていることを特徴とする同期ディジタル論理回路。

【請求項 2】

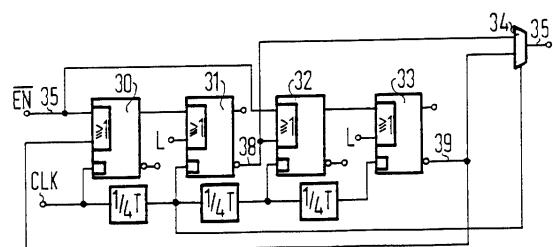

- a ) 第 3 および第 4 のメモリ要素 ( 32 、 33 ) が存在しており、

- b ) 第 2 のメモリ要素 ( 31 ) の出力端の 1 つが第 3 のメモリ要素 ( 32 ) の第 1 の入力端と接続され、第 3 のメモリ要素 ( 32 ) の出力端の 1 つが第 4 のメモリ要素 ( 33 ) の入力端の 1 つと接続されており、

- c ) 第 3 のメモリ要素 ( 32 ) の第 2 の入力端が論理回路の入力端 ( 35 ) と接続されており、第 4 のメモリ要素 ( 33 ) の出力端の 1 つが論理回路の別の出力端 ( 39 ) としての役割をしている

ことを特徴とする請求項 1 記載の同期ディジタル論理回路。

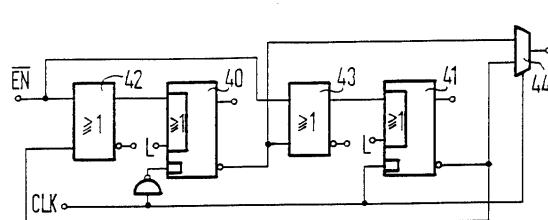

【請求項 3】

第 1 および第 2 のメモリ要素 ( 40 、 41 ) の前に、それぞれ少なくとも 2 つの入力端および少なくとも 2 つの互いに相補性の出力端を有するそれぞれ 1 つのオア論理回路 ( 42 、 43 ) が接続されており、その際

- a ) オア論理回路 ( 42 、 43 ) のそれぞれ第 1 の入力端が論理回路の入力端と接続されており、

- b ) 第 1 のメモリ要素の前に接続されているオア論理回路 ( 42 ) の第 2 の入力端が第 2 のメモリ要素 ( 41 ) の一方の出力端と接続されており、第 2 のメモリ要素の前に接続されているオア論理回路 ( 43 ) の第 2 の入力端が第 1 のメモリ要素 ( 40 ) の一方の出力端と接続されており、

- c ) 第 1 のメモリ要素の前に接続されているオア論理回路 ( 42 ) の出力端の 1 つが第 1 のメモリ要素 ( 40 ) の入力端の 1 つと接続されており、第 2 のメモリ要素の前に接続されているオア論理回路 ( 43 ) の出力端の 1 つが第 2 のメモリ要素 ( 41 ) の入力端の 1 つと接続されており、

- d ) 第 2 のメモリ要素 ( 41 ) の前記一方の出力端が論理回路の別の出力端としての役割をしている

ことを特徴とする請求項 1 記載の同期ディジタル論理回路。

【請求項 4】

論理回路の出力端および別の出力端が、メモリ要素のクロック入力端に与えられているクロック信号の 1 つにより制御されるマルチプレクサ ( 33 、 34 ) の入力端と接続されていることを特徴とする請求項 2 または 3 記載の同期ディジタル論理回路。

【請求項 5】

同期ディジタル論理回路であって、

- a ) クロック入力端、少なくとも 2 つの互いに相補性の出力端および少なくとも 2 つの入力端を有する少なくともそれぞれ 1 つのクロック状態制御されるメモリ要素 ( 10 、 11 ) を有する少なくとも第 1 および第 2 の群が、第 1 の群のメモリ要素 ( 10 ) の出力端の 1 つ ( 16 ) が第 2 の群のメモリ要素 ( 11 ) の入力端の 1 つ ( 17 ) と接続されていることによって、縦続接続されており、

- b ) 第 2 のメモリ要素 ( 11 ) の一方の出力端が第 1 の群のメモリ要素 ( 10 ) の第 1 の入力端に帰還結合されており、

- c ) 第 1 の群のメモリ要素 ( 10 ) の第 2 の入力端が論理回路の入力端 ( 13 ) と接続されており、第 2 の群のメモリ要素 ( 11 ) の前記一方の出力端が論理回路の出力端 ( 14 ) としての役割をしており、

- d ) 各群のメモリ要素のクロック入力端が互いに位相シフトされたクロック信号 ( C L K ) により制御される

同期ディジタル論理回路において、

- e ) メモリ要素 ( 10 、 11 ) の各々がクロック状態制御される D フリップフロップおよびオア論理回路を含んでおり、

10

20

30

40

50

f ) オア論理回路の出力端がDフリップフロップの入力端と接続されており、メモリ要素の入力端がオア論理回路の入力端であり、メモリ要素の相補性出力端がDフリップフロップの相補性出力端であり、

g ) 各2つの縦続接続されているメモリ要素(10、11)の群のクロック信号(CLK)が群の数により分割されたクロック周期の位相だけ互いに位相シフトされていることを特徴とする同期ディジタル論理回路。

#### 【請求項6】

a ) メモリ要素(32、33)の第3および第4の群が存在しており、

b ) 第2の群のメモリ要素(31)の出力端の1つが第3の群のメモリ要素(32)の第1の入力端と接続され、第3の群のメモリ要素(32)の出力端の1つが第4の群のメモリ要素(33)の入力端の1つと接続されており、10

c ) 第3の群のメモリ要素(32)の第2の入力端が論理回路の入力端(35)と接続されており、第4の群のメモリ要素(33)の出力端の1つが論理回路の別の入力端(39)としての役割をしている

ことを特徴とする請求項5記載の同期ディジタル論理回路。

#### 【請求項7】

第1および第2の群のメモリ要素(40、41)の前に、それぞれ少なくとも2つの入力端および少なくとも2つの互いに相補性の出力端を有するそれぞれ1つのオア論理回路(42、43)が接続されており、その際

a ) オア論理回路(42、43)の第1の入力端が論理回路の入力端と接続されており、20

b ) 第1の群のメモリ要素の前に接続されているオア論理回路(42)の第2の入力端が第2の群のメモリ要素(41)の一方の出力端と接続されており、第2の群のメモリ要素の前に接続されているオア論理回路(43)の第2の入力端が第1の群のメモリ要素(40)の出力端の1つと接続されており、

c ) 第1の群のメモリ要素の前に接続されているオア論理回路(42)の出力端の1つが第1の群のメモリ要素(40)の入力端の1つと接続されており、第2の群のメモリ要素(41)の前に接続されているオア論理回路(43)の出力端の1つが第2の群のメモリ要素(41)の入力端の1つと接続されており、

d ) 第2の群のメモリ要素(41)の前記一方の出力端が論理回路の別の出力端としての役割をしている30

ことを特徴とする請求項5記載の同期ディジタル論理回路。

#### 【請求項8】

論理回路の出力端および別の出力端が対として、マルチプレクサ(33、34)の入力端と接続され、該マルチプレクサはメモリ要素のクロック入力端に与えられているクロック信号の1つにより制御していることを特徴とする請求項6または7記載の同期ディジタル論理回路。

#### 【請求項9】

メモリ要素がバイポーラ電流スイッチ技術で実現されており、入力トランジスタ(56、57)のコレクタエミッタ間バスが並列に接続されていることを特徴とする請求項1ないし3または5ないし7の1つに記載の同期ディジタル論理回路。40

#### 【発明の詳細な説明】

##### 【0001】

##### 【産業上の利用分野】

本発明は、メモリ要素およびオア演算を行う回路手段を有する論理機能の実現のための同期ディジタル論理回路に関する。以下において、論理要素という表現は、一般的に論理ゲートまたは単に論理回路と呼ばれるような、論理演算を行う回路手段を意味する。

##### 【0002】

##### 【従来の技術】

論理回路は、システム状態がメモリ要素のなかに記憶されるディジタルの同期クロックされるシステムである。入力信号および記憶された信号から組み合わせ論理により出力信号50

が計算される。このような論理回路はたとえば図書“半導体回路技術”、ウー・ティーツエ(U.Tietze)およびツェーハー・シェンク(Ch.Schenk)著、第7版、第259~261頁から公知である。メモリ要素としてそこではエッジ制御されるメモリ要素が使用される。エッジ制御されるメモリ要素では通常、データは少なくとも特定の時間間隔だけクロックエッジの前にメモリ要素の入力端に与えられていなければならない。この時間間隔はセット時間と呼ばれる。データはクロックパルスによりメモリ要素に記憶される。その後に、データが出力端に現れるまで、ある時間間隔だけかかる。この時間はメモリ要素の遅延時間と呼ばれる。従って、2つの相い続くクロックエッジの間の組み合わせ論理の計算のために、メモリ要素のセット時間および遅延時間を差し引いたクロック周期が利用される。論理回路の最大処理速度はその場合に、メモリ要素のセット時間および遅延時間および組み合わせ論理の遅延時間から成る和がクロック周期の長さに等しいときに達成される。

#### 【0003】

##### 【発明が解決しようとする課題】

本発明の課題は、一層高い処理速度が可能である論理回路を実現することである。

#### 【0004】

##### 【課題を解決するための手段】

この課題は、この発明によれば、特許請求の範囲に記載された構成により解決される。

#### 【0005】

##### 【実施例】

以下、図面に示されている実施例により本発明を一層詳細に説明する。

#### 【0006】

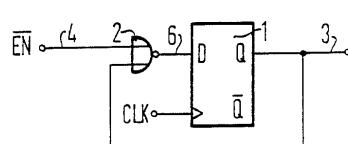

図6には従来の技術による論理回路が示されている。ここに示されているのは、クロックエッジ制御されるメモリ要素を含んでおりレリーズ入力端を設けられている分周比2の分周器である。クロックエッジ制御されるメモリ要素はDフリップフロップである。Dフリップフロップ1の出力端3はその入力端に帰還接続されている。Lアクティブレリーズ信号バーENはノット オア論理要素2を介して帰還接続と接続されている。レリーズ入力端がL電位にあるならば、ノット オア論理要素2の出力端にDフリップフロップ2の出力信号の否定された値が生ずる。それに続く負のクロックエッジによりこの論理値がDフリップフロップ1のなかに記憶される。従って、出力端3にはクロック信号CLKの周波数に対して半減された周波数を有するLおよびHの交互の列が現れる。レリーズ信号バーENがHであれば、ノット オア論理要素2の出力端は常にLであり、従って出力端3はLにとどまる。

#### 【0007】

たとえばDフリップフロップ1のようなクロックエッジ制御されるメモリ要素では一般に有効なデータ信号はその入力端6にある時間間隔、いわゆるセット時間だけクロックエッジの前に与えられていなければならない。データ信号はセット時間の間はもはや変化してはならない。クロックエッジの後に、メモリ要素のいわゆる遅延時間が、データ入力端に与えられている信号が出力端3に有効に現れるまで続く。2つの相い続くクロックエッジの時間間隔、すなわちクロック周期、からセット時間および遅延時間を差し引いた時間間隔がノット オア論理要素2の遅延時間に最大利用される。従って、図6の論理回路の最高処理速度はDフリップフロップ1のセット時間および遅延時間および論理要素2の遅延時間の和により制限されている。

#### 【0008】

図1には、図6に示されている論理回路と等しい機能を行う論理回路の本発明による実現が示されている。2つの状態制御されるメモリ要素10、11が、メモリ要素10の出力端16がメモリ要素11の入力端17の1つと接続されることによって、縦続接続されている。メモリ要素11の他方の入力端15はL電位と接続されている。メモリ要素11の否定出力端14は論理回路の出力端としての役割をし、またメモリ要素10の入力端の1つに帰還結合されている。メモリ要素10の他方の入力端13はレリーズ信号バーE

10

20

30

40

50

Nにより制御される。メモリ要素11のクロック入力端にはクロック信号CLKが与えられており、他方においてメモリ要素10は否定された、すなわち半周期だけシフトされたクロック信号により制御される。

#### 【0009】

クロック状態制御されるメモリ要素10、11としては、出力端およびそれに対して相補性の出力端を有するそれぞれ1つのメモリ要素が設けられている。それはさらに、オア演算要素に接続されている2つの入力端を有する。このオア演算の結果はメモリ要素のなかに記憶される。クロック信号のH相の間はメモリ要素は透過性であり、すなわちオア演算の結果はメモリ要素の出力端に存在し、また結果の変化は直接に出力端においても有効になる。クロック信号のL相の間は、クロックエッジの直前に記憶された結果が記憶されている。オア演算の計算は特定の時間間隔だけ継続する。もしメモリ要素の入力端におけるデータがこの時間間隔の間に変化しないならば、クロックエッジの直後にメモリ要素の出力端に有効な結果が存在する。従って、このようなクロック状態制御される透過性のメモリ要素ではメモリ過程の後に遅延時間は存在しない。10

#### 【0010】

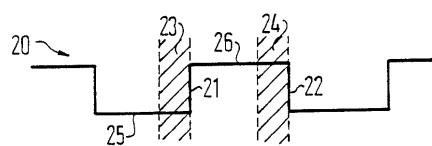

図1の論理回路の機能の仕方を説明するため図2にクロック信号ダイアグラムが示されている。クロック信号20のL相25の間はメモリ要素10が透過性である。クロックエッジ21の時点で信号バーENおよび出力端14の帰還結合される信号から成るオア演算の結果が記憶される。時間間隔23はメモリ要素10のセット時間である。クロック信号20のH相26の間はメモリ要素11が透過性であり、またクロックエッジ22においてその入力端17および15における信号のオア演算の結果を記憶する。従って、各負のクロックエッジの時点で有効な信号が出力端14に与えられている。クロック周期の長さはクロック状態制御されるメモリ要素の少なくとも2つのセット時間でなければならない。図6の論理回路を顧慮して論理要素2に対する遅延時間およびクロックエッジ制御されるDフリップフロップ1の遅延時間はなくなる。従って、クロック状態制御およびクロックエッジ制御されるメモリ要素に対する近似的に等大のセット時間から出発すると、本発明により実現される論理回路における速度は従来の技術による実現の場合よりもはるかに高い。20

#### 【0011】

実現すべき論理機能の際にデータ記憶の課題は縦続接続されているクロック状態制御される両メモリ要素10、11により行われる。クロック信号のL相25の間に実現すべき組み合わせ論理のすべてのオア演算が、またH相26の間にすべてのアンド演算が計算される。いまの組み合わせ論理はノット オア演算を含んでいる。その結果に影響することなしに、組み合わせ論理は論理Hレベルを有する後に接続されているアンド演算により拡張される。ノット オア演算はメモリ要素10のなかで計算され、論理Hレベルを有するアンド演算はメモリ要素11のなかで計算される。アンド演算はオア論理要素によりメモリ要素11のなかで行われるので、入力信号および出力信号は否定される。その結果、メモリ要素11の入力端17はメモリ要素10の正の出力端と、メモリ要素11の他方の入力端15はLレベルと、また論理回路の出力端はメモリ要素11の負の出力端と接続されている。30

#### 【0012】

いまの論理回路の別の実現可能性が図3に示されている。そこでは4つの状態制御されるメモリ要素30、...、33が縦続接続されている。メモリ要素30、31の配置は図1に示されている回路に一致している。その後にメモリ要素32、33を有する相応の装置が接続されている。メモリ要素32の入力信号は入力信号バーENおよびメモリ要素31の出力信号である。論理回路の出力信号はメモリ要素31または33の出力端38、39に与えられている。縦続接続されているメモリ要素のクロック信号はクロック周期の1/4だけシフトされている。40

#### 【0013】

クロック信号CLKが第1のクロックエッジにおいてHレベルからLレベルへ移行すると50

、メモリ要素 3 0においてオア演算の結果が入力信号バー E N の第 1 の値および継続接続されているメモリ要素の最後のものの出力端 3 9における信号から計算される。メモリ要素 3 1 の出力端 3 8 におけるアンド演算の結果は 1 / 4 クロック周期遅れて現われる。従って、入力信号バー E N の第 1 の値に対する論理機能の計算に対して半クロック周期が必要とされる。入力信号バー E N の第 1 の値に時間的に続く第 2 の値はメモリ要素 3 2 のなかで出力端 3 8 における第 1 の計算の結果と論理演算される。半クロック周期の後に第 2 の値に対する論理機能の結果がメモリ要素 3 3 の出力端 3 9 に存在する。従って、入力信号バー E N の 2 つの時間的に相い続く値の計算に対してクロック信号の 1 つの周期が必要である。図 2 の論理回路は、クロック信号 C L K の周波数が入力信号バー E N の周波数に等しいという利点を有する。メモリ要素 3 1 または 3 3 の出力端 3 8 、 3 9 における出力信号はマルチプレクサ 3 4 を介して論理回路の別の出力端 3 5 に導かれる。マルチプレクサ 3 4 は、メモリ要素 3 1 のクロック信号により、出力端 3 8 、 3 9 における出力信号のそれぞれ 1 つが、付属の入力信号バー E N の第 1 または第 2 の値に続くクロック周期の半分の間に出力端 3 5 に現れるように制御される。

#### 【 0 0 1 4 】

図 4 には、2 つの状態制御されるメモリ要素およびメモリ要素の前に接続されているオア論理要素を有する図 6 から公知の論理回路の本発明による実現が示されている。メモリ要素 4 0 、 4 1 の前にそれぞれオア論理要素 4 2 または 4 3 が、オア論理要素の正の出力端がメモリ要素の入力端の 1 つと接続されていることによって、接続されている。オア論理要素は少なくとも 2 つの入力端および正出力端に対して相補性の出力端を有する。オア論理要素 4 2 、 4 3 の入力端の 1 つはレリーズ信号バー E N により制御され、他方の入力端はメモリ要素 4 1 または 4 0 の否定された出力端と接続されている。メモリ要素 4 0 、 4 1 はクロック周期の半分だけ位相シフトされたクロック信号により制御される。論理要素 4 0 、 4 1 の否定出力端の後に、クロック信号 C L K により制御されるマルチプレクサが接続されている。図 4 の回路は、図 3 中に存在するメモリ要素 3 0 、 3 2 の代わりにオア論理要素 4 2 、 4 3 が存在することを例外として、図 3 の回路に一致している。このことは、メモリ要素 3 0 、 3 2 の記憶機能が省略され、また論理要素 3 0 、 3 2 のオア演算機能がオア論理要素 4 2 、 4 3 により行われることを意味する。図 4 による回路は図 3 の回路にくらべて、構成要素が節減されるという利点を有する。それに対して、後者は、常に同種の構成要素が使用され、従ってまた規則的な構造が可能であるという利点を有する。

#### 【 0 0 1 5 】

これまでに説明した図 1 、図 3 、図 4 の実施例は同一の論理回路の種々の実現可能性である。1 つよりも多い論理値が記憶される他の論理機能が実現されるならば、本発明による実現ではメモリ要素 1 0 、 1 1 または 3 0 、 ... 、 3 3 または 4 0 、 4 1 のただ 1 つの代わりに 1 つよりも多いメモリ要素を有するそれぞれ 1 つの群が設けられる。群のすべてのメモリ要素は等しいクロック信号により制御される。図 4 による実現の場合には、オア論理要素 4 2 、 4 3 に相応するオア論理要素の群も設けられている。これらの群の各々は実施例に示されている個々のメモリ要素およびオア論理要素の接続の仕方に相応する仕方で接続される。メモリ要素およびオア論理要素の各々のすべての入力端および出力端の具体的な接続はそれぞれ実現すべき論理機能に関係する。

#### 【 0 0 1 6 】

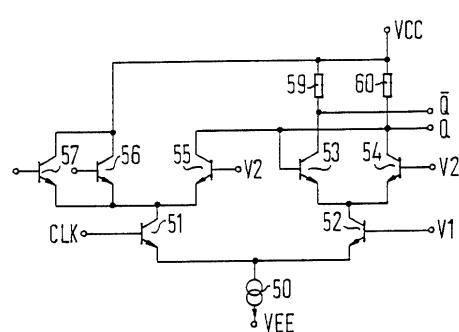

透過性のクロック状態制御されるメモリ要素の実施例が図 5 に示されている。この回路はバイポーラ電流スイッチ技術で実現されている。電流スイッチは 2 つのエミッタ結合されたバイポーラトランジスタ 5 1 、 5 2 を含んでおり、それらのエミッタは電流源 5 0 を介して供給電位 V E E と接続されている。これらのトランジスタのコレクタはそれぞれ別のトランジスタ対 5 6 、 5 5 または 5 3 、 5 4 のエミッタと接続されている。トランジスタ 5 3 、 5 4 のコレクタはそれぞれ抵抗 5 9 または 6 0 を介して別の供給電位 V C C と接続されている。トランジスタ 5 5 、 5 4 のコレクタは結合されており、出力端 Q を形成している。トランジスタ 5 3 のコレクタはそれに対して相補性の出力端バー Q としての役割を

10

20

30

40

50

する。トランジスタ 5 2 のベースは第 1 の参照電位 V 1 と接続されており、トランジスタ 5 5、5 4 のベース端子は別の参照電位 V 2 と接続されている。トランジスタ 5 1 のベースにクロック信号 C L K が与えられている。ベースで入力信号により制御されるトランジスタ 5 6 のコレクタ エミッタ間バスに対して並列に、ベース端子で別の入力信号により制御される別のバイポーラトランジスタ 5 7、5 8 のコレクタ エミッタ間バスが接続されている。出力信号 Q はトランジスタ 5 3 のベースに帰還結合されている。トランジスタ 5 6、5 7 の入力端はオア演算のために結合されている。オア演算はこれらのトランジスタの並列に接続されているコレクタ エミッタ間バスに基づいて、追加的な信号伝播時間を生じさせずに得られる。原理的に、2つよりも多い入力信号を有するメモリ要素を形成するためトランジスタ 5 6、5 7 を別の入力トランジスタに並列に接続することが可能である。10

#### 【0017】

回路は下記のように動作する。クロック信号 C L K は H であるとする。従って、電流源 5 0 の電流はトランジスタ 5 1 を通って流れ、他方においてトランジスタ 5 2 は遮断されている。トランジスタ 5 6、5 7 の少なくとも 1 つが H レベルにより制御されるならば、電流がこのトランジスタを通って流れ、またトランジスタ 5 5 は遮断される。その場合、抵抗 6 0 を通って電流が流れないので、出力端 Q は H 電位にある。出力端 Q にこうして入力信号のオア演算の結果が生ずる。たとえばすべての入力トランジスタが遮断されることによってオア演算の結果が変化すると、電流がトランジスタ 5 5 を通って流れ、出力端 Q に L レベルを生じさせる。これは入力信号の変化に応じて直接に行われる。すなわちフリップフロップは透過性である。クロック信号が L レベルに切換わると、電流がトランジスタ 5 2 を通って流れれる。トランジスタ 5 3 のベースへの出力端 Q の帰還結合により、出力端におけるいままで存在するレベルが記憶される。出力端バー Q は出力端 Q と逆に挙動する。いまトランジスタ 5 6、5 7 における入力信号が変化すると、これは出力 Q、バー Q に作用しない。なぜならば、トランジスタ 5 1 が無電流であるからである。20

#### 【0018】

クロック信号 C L K が H であれば、電流がトランジスタ 5 1 を通って流れ、トランジスタ 5 6、5 7 の入力端におけるレベル変化と寄生的なコレクタ 基板間キャパシタンスに基づく出力端 Q、バー Q におけるそれへの反応との間の第 1 の遅延時間が生ずる。同じく、負のクロックエッジの際のトランジスタ 5 1 からトランジスタ 5 2 への電流の切換に対する第 2 の遅延時間が存在している。出力端 Q、バー Q における記憶されたレベルが負のクロックエッジの時点で有効であるべきであれば、入力信号は第 1 および第 2 の遅延時間のなかでクロックエッジの開始前に変更されてはならない。従って、メモリ要素のセット時間、すなわちデータがもはや変更されてはならないクロックエッジ前の継続時間はこれらの両遅延時間の長いほうの遅延時間により決定される。メモリ要素は、組み合わせ論理の計算のための遅延時間およびメモリ要素のセット時間が一致するという利点を有する。30

#### 【図面の簡単な説明】

【図 1】本発明による論理回路の実施例。

【図 2】図 1 の回路のクロック信号ダイアグラム。

【図 3】4 つのメモリ要素を有する論理回路の実施例。

【図 4】2 つのメモリ要素およびそれらの前に接続されているオア論理要素を有する論理回路の実施例。40

【図 5】電流スイッチ技術での状態制御されるメモリ要素の実施例。

【図 6】従来の技術による論理回路。

#### 【符号の説明】

1 0、1 1 メモリ要素

1 3 入力端

1 4 出力端

3 1 ~ 3 3 メモリ要素

3 4 マルチプレクサ

40

50

3 5 入力端

3 9 出力端

4 0、4 1 メモリ要素

4 2、4 3 オア論理要素

4 4 マルチプレクサ

5 6、5 7 入力トランジスタ

C L K クロック信号

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

---

フロントページの続き

(56)参考文献 特開平02-170713(JP,A)

特開昭64-057816(JP,A)

特開昭64-053620(JP,A)

特開昭62-295508(JP,A)

特開昭62-154810(JP,A)

特開昭61-087426(JP,A)

特開昭56-138324(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H03K 3/037

H03K 19/01

H03K 19/20