| [72]  | Inve  | ntor     | Philip N. Armstrong<br>17331 Keegan Way, Santa At<br>92705 | na, Calif. |

|-------|-------|----------|------------------------------------------------------------|------------|

| [21]  | App   | l. No.   | 830,225                                                    |            |

| [22]  | File  | d        | June 4, 1969                                               |            |

| [45]  | Pate  | nted     | June 22, 1971                                              |            |

| [54]  |       |          | TING SYSTEM<br>10 Drawing Figs.                            |            |

| [52]  | U.S.  | CI       | *******************************                            | 340/172.5  |

| [51]  | Int.  | CI       |                                                            | G06f 7/22  |

| [50]  | Field | i of Sea | reh                                                        | 340/172.5  |

| [56]  |       | U        | References Cited                                           |            |

| 3,015 | .089  | 12/196   | il Armstrong                                               | 340/172.5  |

| 3,029 |       | 4/196    |                                                            | 340/172.5  |

|       |       |          |                                                            |            |

ABSTRACT: A data sorting system for multibit binary records is provided which is capable of responding to a control field in each of the records in order to sort the records into an ascending or descending progression. The sorting system to be described has the feature that it is capable of sorting a file of the aforesaid records which contains more records than the capacity of the sorting system itself. The system is controlled so that the file is repeatedly circulated therethrough until a complete sort is achieved, with the capacity of the system being reduced for each successive pass so that optimum efficiency is maintained at all times.

### SHEET 01 OF 20

SHEET 02 OF 20

#### SHEET 03 OF 20

Memory

Accord Time 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22

Input (I<sub>2</sub>)

Input (I<sub>2</sub>)

Input (I<sub>2</sub>)

Input (I<sub>2</sub>)

Input (I<sub>2</sub>)

Input (O<sub>1</sub>)

Input (O<sub>2</sub>)

Fig.5

### SHEET 04 OF 20

$F_{1} = \frac{1}{2} \frac{1}$

| Fig.7                  | •  |    |       | Memory      |                         |

|------------------------|----|----|-------|-------------|-------------------------|

|                        | A  | 8  | C     | D           | ε                       |

| * STEP<br>23           | 7  | Z  | 16    | 9 8 7 10    | 16 13 12 11 50 25 30 20 |

| 24                     | ¥  | 2  | 61    | 10 9 8 7    | 24 16 13 12 11 5 4 3    |

| 25                     | 1  | 2  | 36    | 7 10 9 8    | 25 24 16 13 12 11 5 4   |

| Sorter<br>Output Begin | v  |    |       |             |                         |

| 26                     | 2  | 4  | 63    | 8 9 10 9    | 15 25 24 16 13 12 11 5  |

| 27                     | 2  | 3  | 46    | 5 8 7 10    | 9 15 25 24 16 13 12 11  |

| 28                     | 3  | 6  | 10 4  | 11 5 8 7    | 19 9 15 25 24 16 13 12  |

| 29                     | 4  | 6  | 7 10  | 12 11 5 8   | 17 19 9 15 25 24 16 13  |

| <i>30</i>              | 6  | 8  | 10 7  | 13 12 11 5  | 14 17 19 15 25 24 16 13 |

| 31                     | 5  | 6  | 7 10  | 8 13 12 11  | 16 14 17 19 9 15 25 24  |

| 32                     | 6  | 10 | 117   | 18 8 13 12  | 24 16 14 17 19 9 15 25  |

| <i>33</i>              | 2  | 10 | 12 11 | 20 18 5 13  | 25 24 16 14 17 19 9 15  |

| 34                     | 10 | // | 13 12 | 15 20 18 8  | 21 25 28 16 14 17 19 9  |

| <i>35</i>              | 9  | Ø  | 11 13 | 12 15 20 18 | 22 21 25 24 16 14 17 19 |

| 36                     | 10 | 13 | 18 11 | 11 12 15 20 | 23 22 21 25 24 16 14 17 |

Philip N. Armstrong Surray and Breaker By Keith D. Breaker ATTORNEYS

#### SHEET 05 OF 20

Fig.8

Output (Q) 10 11 12 13 I 14 15 16 I 17 18 I I 19 20 21 22 23 24 25

Fig.9

> Philip N. Armstrong Yeroup and Busha By Kith D. Beecher ATTORNEYS

## SHEET OF OF 20

# SHEET 07 OF 20

INVENTOR.

Philip N. Armstrong

Normy and Busher

By Kirl D. Duecker

ATTORNEYS

SHEET 08 OF 20

SHEET 09 OF 20

## SHEET 10 OF 20

INVENTOR:

Philip N. Armstrong

Sumpand Buchen

By Keith D. Beechen

ATTORNEYS

#### SHEET 11 OF 20

# SHEET 12 OF 20

Fig.21

Memory

| Step | A   | 8  | _     |            | E                                                                                                                                                 | Input |

|------|-----|----|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1    | /3  | X  | XX    | XXXX       | XXXXXXXX                                                                                                                                          | (13)  |

| 2    | 13" | X  | XX    | XXXX       | XXXXXXXXX                                                                                                                                         | (8**) |

| 3    | 16  | 13 | XX    | XXXX       | XXXXXXXX                                                                                                                                          | (16)  |

| 4    | 13  | 16 | 0/    | XXXX       | XXXXXXXX                                                                                                                                          | (10)  |

| 5    | 7   | 13 | 16 16 | XXXX       | XXXXXXXXX                                                                                                                                         | (Z)   |

| 6    | Z   | 10 | 13 16 | XXXX       | XXXXXXXX                                                                                                                                          | (B**) |

| 2    | 4   | 10 | 16 13 | XXXX       | XXXXXXXX                                                                                                                                          | (4)   |

| 8    | 4   | 10 | 13 16 | fXXX       | XXXXXXXX                                                                                                                                          | (3)   |

| 9    | 2   | 10 | 16 13 | J J XX     | XXXXXXXX                                                                                                                                          | (7)   |

| 10   | 3   | 7  | 10 16 | 13 d" X X  | XXXXXXXX                                                                                                                                          | (B**) |

| 11   | 3   | 4  | 16 10 | 7 /3 XX    | XXXXXXXX                                                                                                                                          | (8**) |

| 12   | 3   | 4  | 10 16 | 13 7 X X   | X X X X X X X                                                                                                                                     | (B**) |

| 13   | 3   | 4  | 7 10  | 16 13 X X  |                                                                                                                                                   | (1)   |

| 14   | 3   | 4  | 107   | 13 16 XX   | $2^{*}/^{*}\times \times $ | (2)   |

| 15   | 3   | 4  | 5 10  | 16 X 7 13  | /*                                                                                                                                                | (5)   |

| 16   | 3   | 4  | 65    | 13 16 10 7 | $z^{\prime\prime}$ , $^{\prime\prime}$ $\times$ $\times$ $\times$ $\times$ $\times$                                                               | (6)   |

| 17   | 4   | 5  | 126   | 16 10 7 13 | 3" 2" /" X X X X X                                                                                                                                | (12)  |

| 18   | 5   | 6  | 11 12 | 13 16 10 7 |                                                                                                                                                   | (11)  |

| 19   | 5   | 6  | 12 11 | 7 13 16 10 |                                                                                                                                                   | (Z)   |

| 20   | 5   | 6  | 11 12 | 10 7 13 16 |                                                                                                                                                   | (₹)   |

| 21   | 5   | 6  | 12 11 | 7 10 16 13 |                                                                                                                                                   | (₹)   |

| 22   | 6   | 8  | 11 12 | 10 2 13 16 | 5" /" d" 5" 2" XXX                                                                                                                                | (8)   |

|      |     |    |       |            |                                                                                                                                                   |       |

Philip N. Armstrong Serry and Beach By Keith D. Beecher 1770RNEYS

SHEET 13 OF 20

## SHEET 14 OF 20

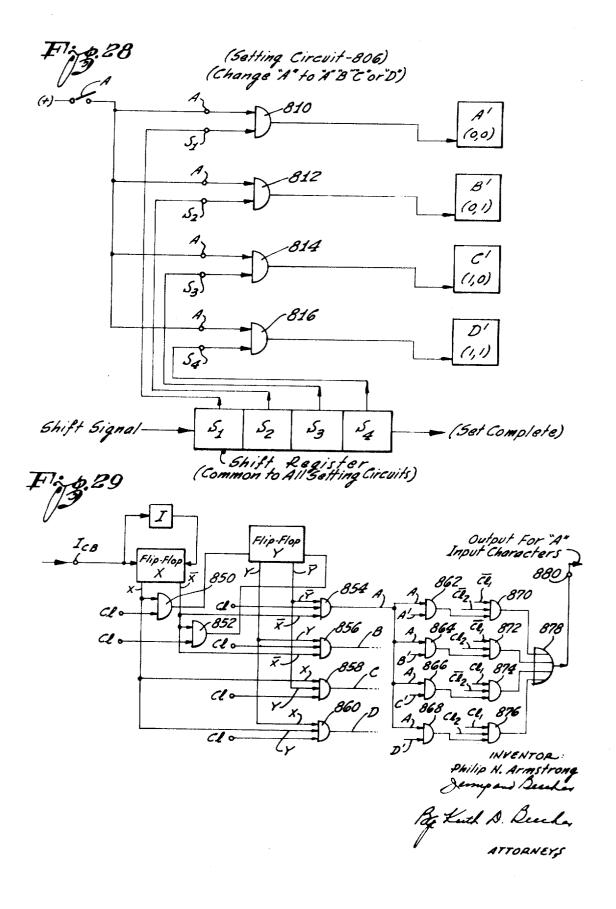

Fig26

Philip N. Armstrong & Long and Buches By Kesth B. Beeches ATTORNEYS

### SHEET 15 OF 20

SHEET 16 OF 20

SHEET 17 OF 20

# SHEET 18 OF 20

Philip N. Armstrong Story and Beecher By Lith D. Beecher ATTORNEYS

SHEET 19 OF 20

Philip N. Armstrong Jamp and Deecher By Kith D. Beecher ATTORNEYS

SHEET 20 OF 20

#### **DATA SORTING SYSTEM**

#### BACKGROUND OF THE INVENTION

The sorting system of the present invention is of the same general type as the sorting system described in U.S. Pat. No. 3,399,383, which issued Aug. 27, 1968, to Philip N. Armstrong. As is the case with the system described in the patent, the improved sorting system of the present invention is capable of rearranging binary records into a desired sequence, and it is intended to be used as an adjunct to a general purpose computer. The primary objective of the invention is to provide a system which is capable of rearranging records in a file, in which the number of records exceeds the normal capacity of 15 the system, and of achieving this sort in a rapid manner and on an efficient basis

A feature of the improved sorting system of the present invention, as was the case with the sorting system described in the aforesaid patent, is that it can be coupled to a wide variety 20 of present day digital computers, including those using magnetic tape buffering equipment. For example, the uses to which the system of the invention may be applied include magnetic tape sorting; large volume inventory control; billing; mailing list preparation; library retrieval, and so on. In 25 general, the sorting system of the invention is useful in all numerical computations in which placing data in a particular order is an essential part; and it also finds utility in the general storage of data.

The records which are to be sorted in the system of the in- 30 vention are represented by equal length multibit binary numbers. Each record includes a control field bearing an identifying number which, in turn, is represented in usual manner in multiple bit binary digital form. In the embodiment to be of the records is an integer. The sort is accomplished when the identifying numbers in the control fields of a series of records represent a monotonic sequence of numbers which, in the embodiment to be described, will be considered as increasing, although the system can just as easily be constructed to provide a decreasing series. For example, the sequence may be changed from increasing to decreasing, or vice versa, by the provision of complementing inverters at the input and output of the system. Such a complementing system will be shown and described subsequently herein.

The sorting system of the invention, as mentioned above, is intended to be used in conjunction with a file of records greater than the internal capacity of the system. The system is controlled to undergo an input operation, during which the records of the file are fed in an unsorted sequence into the sorting system until the system is full. The unsorted sequence of input records are then continued to be fed into the sorter, and together with the records already in the sorting system appear at its output in a generally sorted condition. The opera- 55 tion is continued until all the records of the file fed into the sorter have been produced at its output. If the indication is that the file of records is not completely sorted at the end of the first pass, the records are again passed through the sorting system. This is continued until a complete sort has been 60 achieved. However, during each successive pass through the sorting system, its capacity is either unchanged or reduced to that required to achieve the limited sorting function needed for each successive pass, so that the time of each successive operate at optimum efficiency at all times.

The aforesaid decrease of the capacity of the sorting system for each successive pass may continue, for example, until only two records are contained in the sorter at any particular time. The sort will be completed at the end of the pass in which no 70 than absolutely necessary. record exchanges have been made by the sorting system.

It will become evident as the description proceeds that the particular sorting system of the invention may incorporate the logic circuitry of the system described in the aforesaid patent, so that it may additionally operate in the same manner as the 75 and they may be combined in a single unit with other logic cir-

previous system to sort files of records which are fewer in number than the capacity of the sorter.

The operation of the sorting system of the invention, as will be described, and as described in the aforesaid patent, depends in part on the facility of the system for separating the records to be sorted into delay line, or other type memories of lengths corresponding to 1, 1, 2, 4, 8...2" records respectively. The number of delay line memories chosen in any particular system depends upon the desired capacity of the system. As pointed out in the patent, extreme flexibility can be achieved in the type of sorting system under consideration, since any commercial embodiment of the sorting system can in general be tailored to fit the number of records to be processed.

For purposes of simplifying the description of the invention as much as possible, the embodiment to be described is assumed to include five of the aforesaid delay line type memories, and these memories have respective lengths corresponding to 1, 1, 2, 4 and 8 records. The selection is such that two of the memories each holds one record, one of the memories holds two records, one of the memories holds four records, and one of the memories holds eight records. Whenever a record is placed in any one of the memories, it may be removed from that memory a number of record times later, as determined by the capacity of the particular memory.

In the embodiment to be described, for example, any record placed in either of the two least memories can be recovered during the next record time, any record placed in the third memory can be recovered after a delay of one record time, any record placed in the fourth memory can be recovered after a delay of three record times, and any record placed in the fifth memory can be recovered after a delay of seven record times.

The aforesaid delay line type memories are synchronous, described, it is assumed that the identifying number for each 35 and in the embodiment to be described, the memories are provided by writing the records on different tracks of a magnetic tape, and by subsequently reading the information from each track on the tape at the required different record time delays. This permits the various records to be placed simultaneously in all the memories, and it also allows the records to be recovered simultaneously from the memories. It should be evident, however, that many types of delay line and other memories are suitable for the purpose of the system of the invention.

> During the operation of the system, the received records are placed in the different memories during successive record times in a serial manner, so that the first record is compared with the contents of the empty system, and each successive record is compared with the previously inputted records. The contents of the empty system are represented by "blanks" which bear control numbers larger than the identifying number of any record to be sorted. The first record received is placed in the first least memory. Then, when the second and successive records are serially received, they are compared with the preceding records, and the records are placed in a sorted condition in the different memories.

As mentioned above, the sorting system of the present invention is one capable of handling a file of records in which the number of records is greater than the internal capacity of the system, and it serves to recirculate the records through the system for a succession of passes, until a complete sort has been achieved. For each successive pass, the number of delay line memories either remains the same or is reduced acpass may be reduced, and so that the sorting system may 65 cordingly, and the length of the remaining delay line memories may also be reduced, so that the capacity of the system is never any larger than that required to perform the sort operation for the successive pass, and so that the time required for each successive pass is reduced accordingly and is no longer

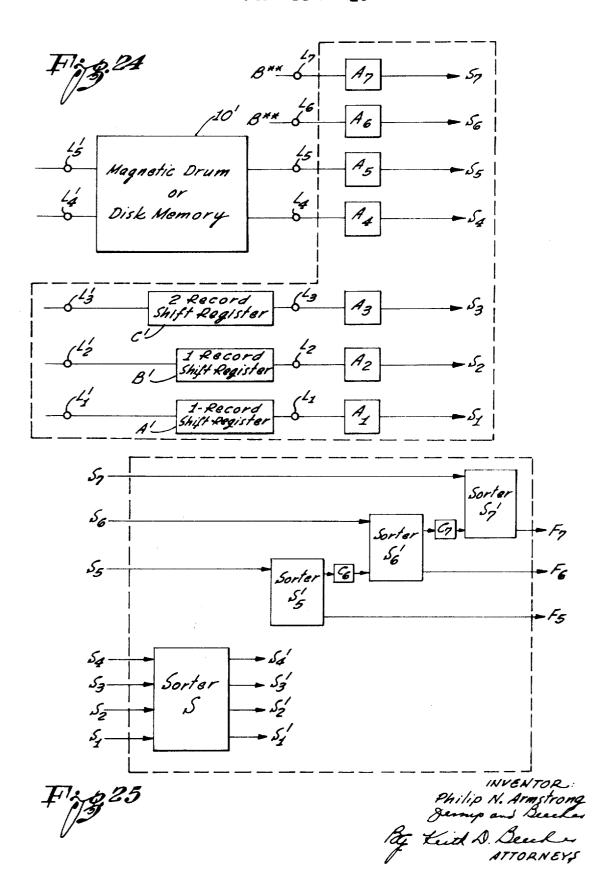

For practical purposes, and in order to adapt the system for use in conjunction with a variety of sizes and types of memories, the shorter delay line memories may be replaced by shift registers. These shift registers may be integrated circuit types, cuits in the system. The result is a standard sorter network with a predetermined number of inputs. The sorter network may then be used in conjunction with standard magnetic drum or disc memories, with tracks thereon serving as the longer delay line memories. If the shorter memory line lengths, as 5 represented by the shift registers, are so selected that the longer memory line lengths consist of integral numbers of disc drum tracks, standard magnetic memory drum or disc equipment may be used.

If the particular drum or disc magnetic memory which is 10 used in conjunction with the standard sorter network described in the preceding paragraph has fewer memory lines than inputs to the network, then appropriate circuitry is used to assure that only a corresponding part of the memory network will be used.

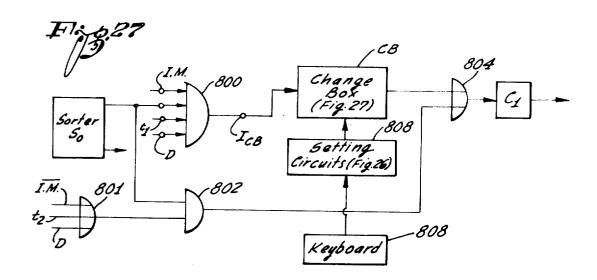

The apparatus to be described also incorporates a logic control unit, designated a "change box," through which the records to be sorted are passed, and which is capable of changing the identification field of selected records in a 20 predetermined way. This permits any desired group of records in the file to be shifted to the front of the file, for example, for the retrieval of data in that group.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

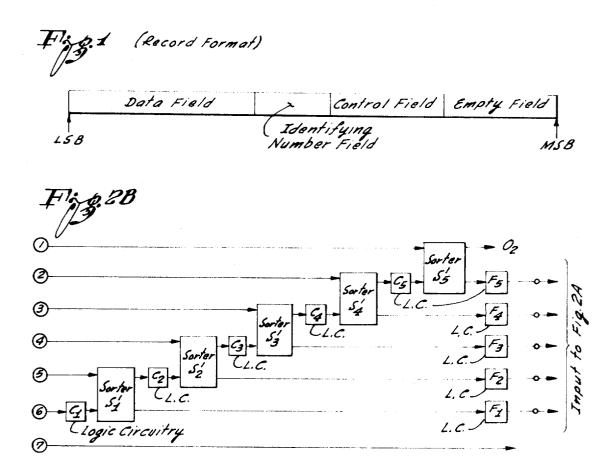

FIG. 1 is a schematic representation of the format of a typical record as processed by the sorting system of the invention;

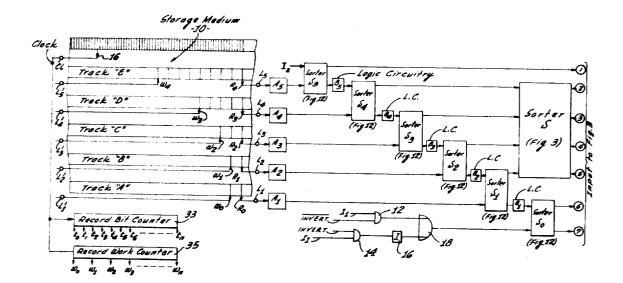

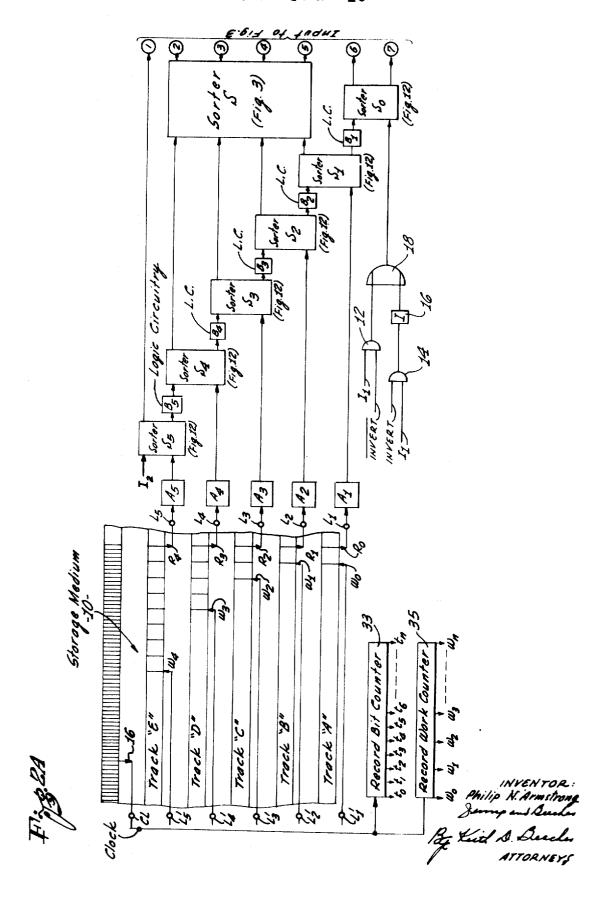

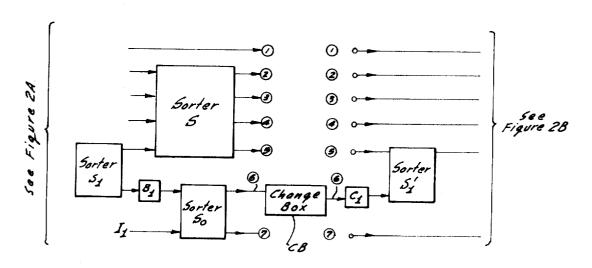

FIGS. 2A and 2B are schematic block representations of the sorter system described in the aforesaid patent, and which may be modified to perform the sort function of the present 30 invention:

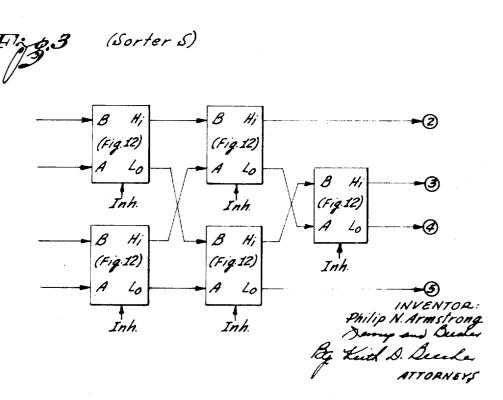

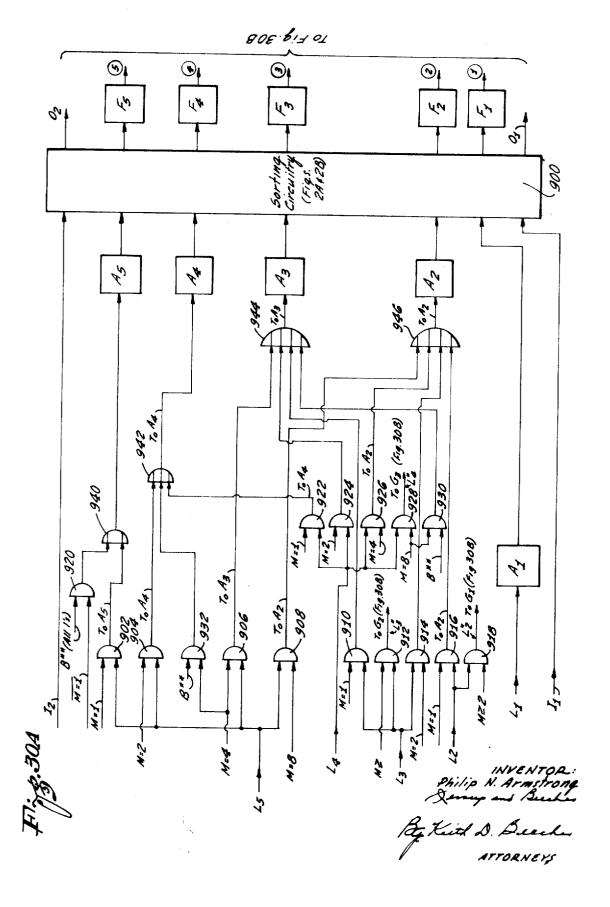

FIG. 3 is a representation of the interconnections of a plurality of sorting blocks, which are included in one of the components of the overall system of FIGS. 2A and 2B;

FIGS. 4, 6 and 8 are representations of a file of records <sup>3</sup> which are successively fed into the system on an interrupted basis:

FIGS. 5, 7 and 9 are tables showing how the aforesaid file is processed in the sorting system;

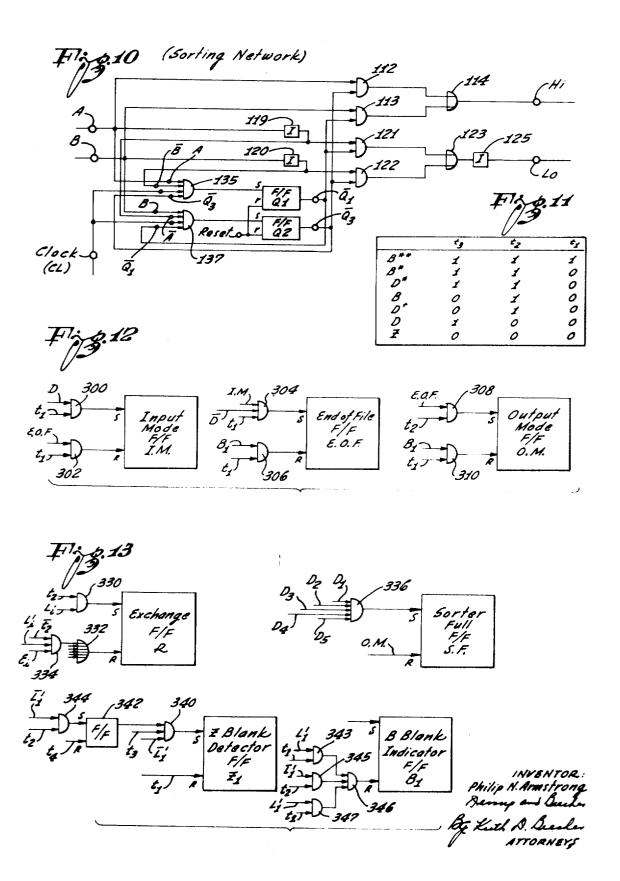

FIG. 10 is a logic diagram of a sorting network which may be used in the system;

FIG. 11 is a table showing the control bits for different records and blanks used in the system;

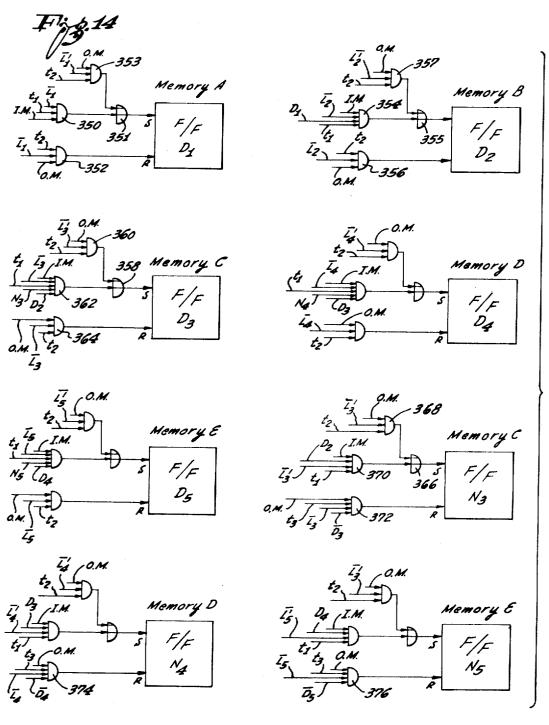

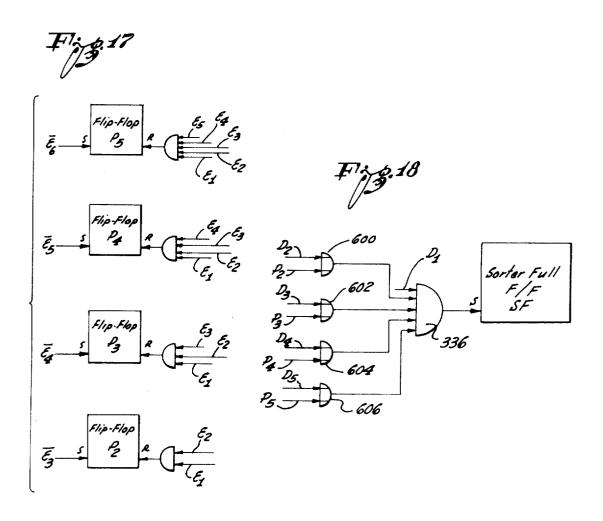

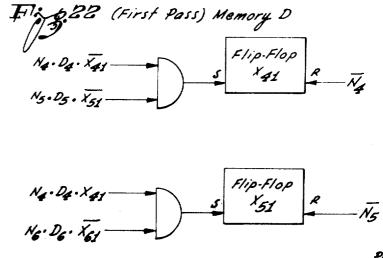

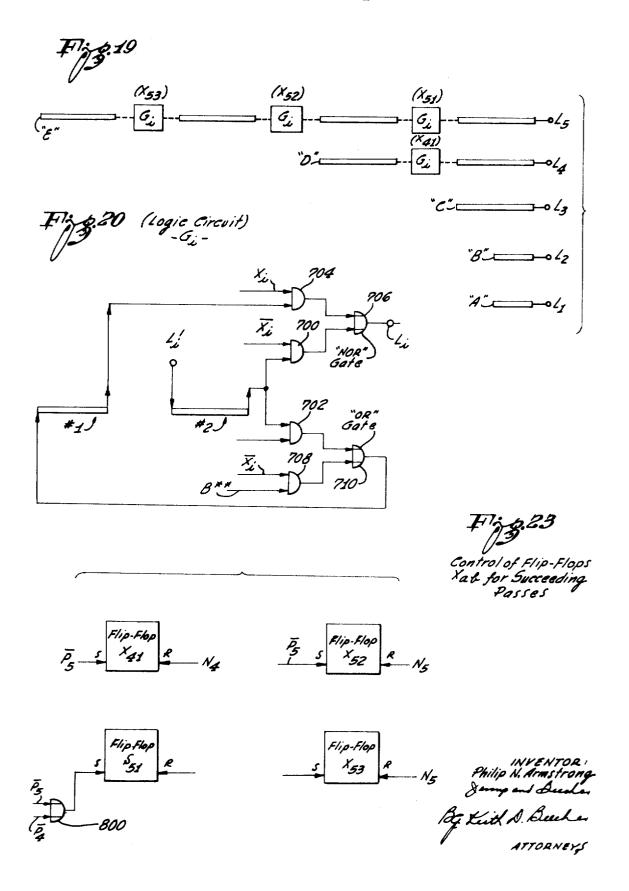

FIGS. 12, 13 and 14, 17, 18, 22 and 23 show the logic as- 45 sociated with flip-flops used in the various embodiments of the system;

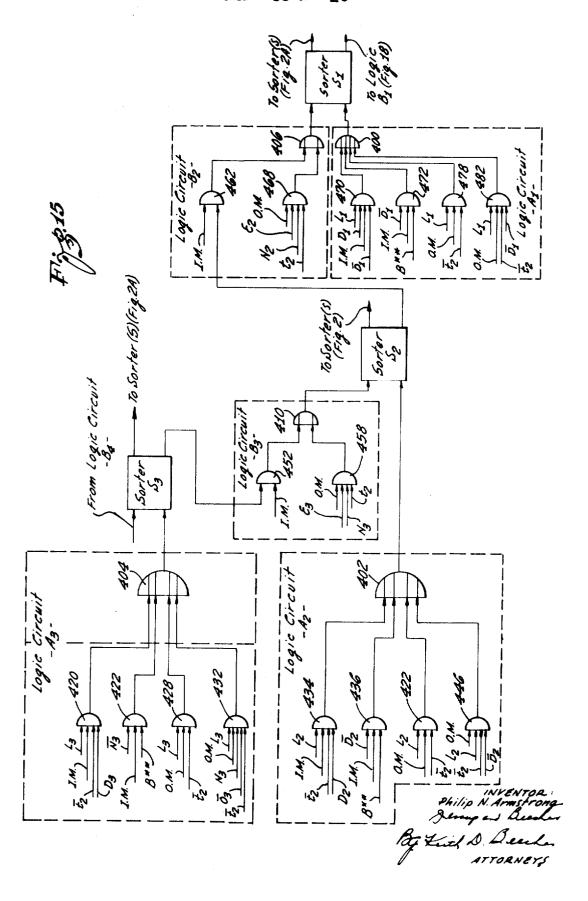

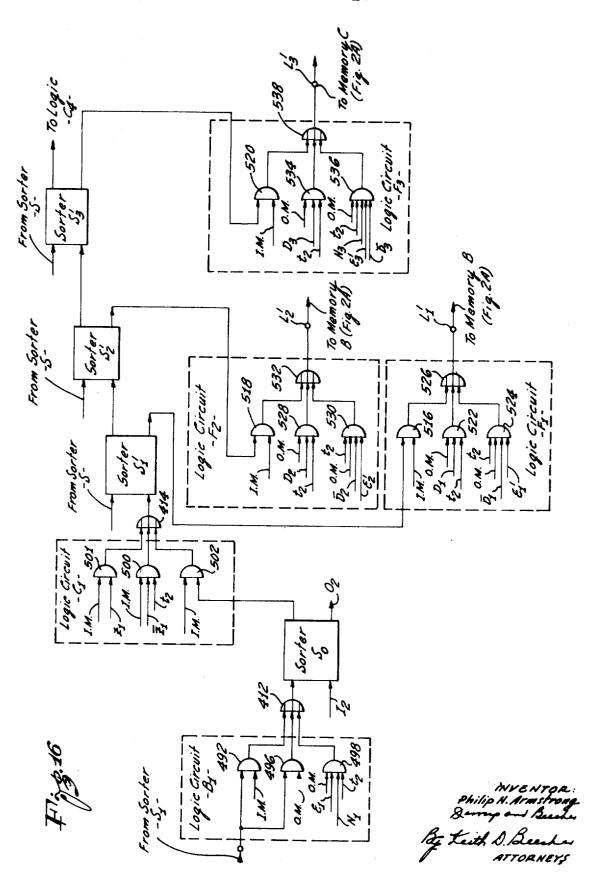

FIGS. 15 and 16 are logic diagrams of sorter networks included in the system;

FIG. 19 is a second embodiment in which the individual 50 memory lines have controllable lengths;

FIG. 20 is a logic diagram of circuitry associated with the embodiment of FIG. 19;

FIG. 21 is a table showing how the aforesaid file of records is handled by the embodiment of FIG. 19;

FIGS. 24 and 25 are block diagrams showing how the sorter may be adapted for use with standard memory equipment;

FIGS. 26, 27, 28 and 29 are block diagrams showing the inclusion of the aforesaid "change box" in the sorter system;

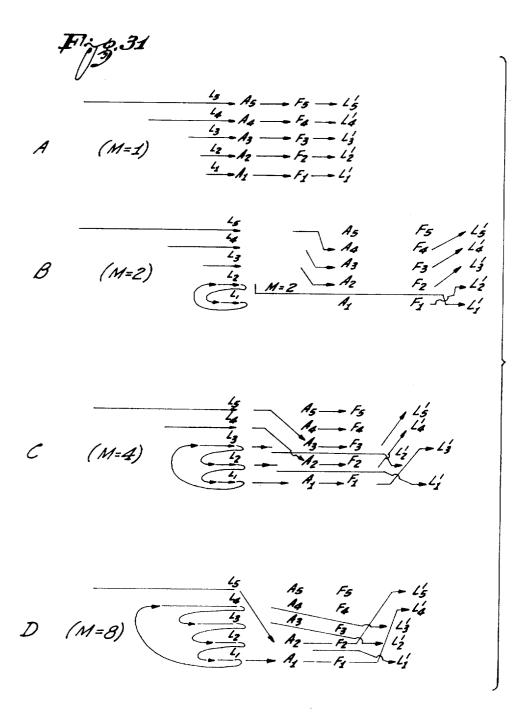

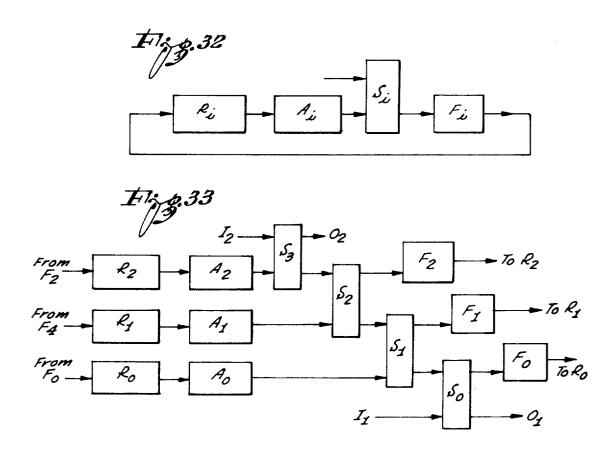

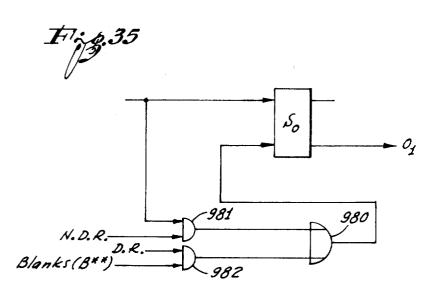

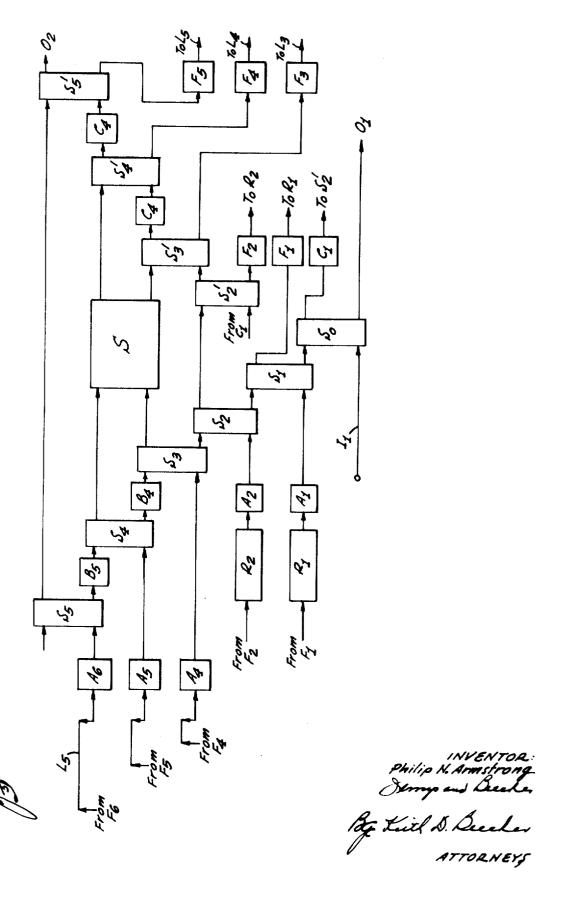

FIGS. 30A, 30B and 31a-31d are diagrams showing how 60 the system may be modified to handle records of multiple lengths; and

FIGS. 32-35 are block diagrams of a portion of the system further modified to incorporate one-record register and sorter 65 modules.

#### DETAILED DESCRIPTION OF THE ILLUSTRATED **EMBODIMENT**

The format of the records processed by the sorting system 70 of the invention is shown as FIG. 1, and as shown, each of the records includes a data field in which the data pertaining to the particular record is contained in binary coded form. Adjacent the data field is an identifying number field which conform of a multibit binary number representing a particular integer. A control field is placed adjacent the identifying number field, and this control field may be treated during the processing by the system so as to alter the identification of the record. An empty field is provided at the end of the record, and which is utilized to permit time for switching the control operations in the system.

The most significant bit of the record is to the right in FIG. 1, and the record is sensed from the right to the left, that is from the most significant bit to the least significant bit. Therefore, each record is sensed by the system first through the interval of the empty field, then the control field is sensed from the most significant to the least significant bit, and the identifying field is next sensed from the most significant to the least significant bit. This permits the identifying number of the identifying number field to be increased to any desired extent depending upon the more significant bits which may be inserted into the control field.

As will be described, multibit binary blanks are also passed through the system from time to time, these being designated as "blanks" (B) in which the data field and identifying field are all 1's; or "blanks" (Z) in which the data field and identifying number field are all 0's. In addition, further "blanks" (B\* and B\*\*) are used in the system, and which are distinguished by the binary coded numbers in their control fields. Also, there are several types of records, which likewise are distinguished from one another by the binary coded numbers in their respective control fields.

The different records and blanks handled by the sorting system to be described may be represented by the following

| Data and identifying fields                            | Control<br>field                                                                                                                      |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| All I's.                                               | 111                                                                                                                                   |

| 00                                                     | 110                                                                                                                                   |

| . Record data and identifying number                   | 110                                                                                                                                   |

| All 1's                                                | 010                                                                                                                                   |

| <ul> <li>Record data and identifying number</li> </ul> | 010                                                                                                                                   |

| do                                                     | 100                                                                                                                                   |

| All 0's                                                | 000                                                                                                                                   |

|                                                        | Data and identifying fields  All Ps. do. Record data and identifying number. All Ps. Record data and identifying number. do. All 0's. |

The identifying field of each of the record words labeled D, D+ or D\* includes a binary representation of an integer identifying the particular record. The most significant bit of the number in the identifying field is adjacent to the control field of the particular record. Therefore, as mentioned above, the identifying number which identifies and controls the sort of the particular record appears adjacent the control field, as shown in FIG. 1. Then, the bits in the control field serve to increase the significance of the identifying number in the identifving field.

At least one bit position in the data field of the D, D+ or D\* records must be a 0. It follows that if the contents of the combined data identifying and control fields are considered as binary integers, they are naturally ordered if a count is taken of the restriction of the data field to control at least one zero. Then, at all times:

#### $Z < D < D + < B < D^* < B^* < B^*$

In the operation of the system, and as mentioned above, a succession of records are caused to flow into the system until it is filled, at which time the records appear at the output of the system while the input operation is continued.

The system may have the general form shown in FIGS. 2A and 2B. The system shown in FIG. 2A, for example, includes a storage medium 10 which may be in the form of a magnetic tape, on which different tracks are provided to form different delay-line type memories for the records of FIG. 1 which are to be processed by the system. As mentioned above, these memories have different lengths in a predetermined progression corresponding to the different numbers of records to be respectively stored therein. In the illustrated embodiment, and as also noted above, the memories represent a progression 1, 1, 2, 4, 8 insofar as the individual record storage capabilities are concerned. However, the system is not limited to powers tains the identifying number for the record, this being in the 75 of two progressions, and other progressions may be used.

The magnetic tape, which constitutes the storage medium 10 in the system of FIG. 2A, is shown in fragmentary form and is assumed to be moving from the left to the right in FIG. 2A. The tape includes a series of different tracks which extend along its length. Corresponding read and write electromagnetic transducer heads are provided for writing the records and blanks in the different tracks, and for subsequently reading the records and blanks from the tracks. The read and write heads are designated by the arrows in FIG. 1.

The magnetic tape of the storage medium 10 also includes a 10 timing track which has regularly spaced magnetic recordings, these being used for bit timing clocking purposes. A transducer read head 16 is magnetically coupled to the timing track, and it responds to the recording on the track to provide clock pulses CL at its output. These clock pulses represent the 15 bit timing in each of the records processed in the system.

The clock pulses are also used to synchronize the operation of a record bit counter 33 and of a record word counter 35. The bit counter 33 produces timing pulses  $t_0$ ,  $t_1$ ,  $t_2$ ...representing the different bit times in each word time in the system; 20 and the word counter produces timing pulses  $w_0$ ,  $w_1$ ,  $w_2$ ...designating successive word or record times in the system.

The magnetic tape of FIG. 2A includes a track designated A, and this track serves as one of the least memories for the system. A write head  $w_0$  is magnetically coupled to the track A, and this head responds to binary signals applied to the input terminal L', to write the signals in that track. A read head  $R_0$  is also magnetically coupled to the track A, and the read head is displaced from the write head along the track a distance corresponding to one record time. Therefor, any record or blank stored in the least memory of the track A is read from the memory during the following record time.

A second least memory is provided by a track B on the magnetic tape, and an appropriate write head  $w_1$  and read head  $R_1$  are magnetically coupled to the track B. The write head  $w_1$  responds to binary signals applied to the input terminal  $L'_2$  to write the corresponding binary signals on the track B. The read head  $R_1$  is displaced along the track B a distance corresponding to one record from the write head  $w_1$ . Therefore, 40 in the second least memory, any record entered therein during a particular recorded time is recovered during the following record time.

The magnetic tape also includes a track designated C. A write head  $w_2$  and a read head  $R_2$  are magnetically coupled to the track C. The read head  $R_2$  is displaced along the track C from the write head  $w_2$  a distance corresponding to two records. This latter track forms the third memory, and the write head  $w_2$  responds to input terminals introduced to the input terminal  $L'_3$  to produce corresponding recordings in the track C. In this third memory, a record introduced during any record time may be recovered two record times later. In addition, the third memory is capable of storing two records, rather than one, as was the case with the two least memories.

A fourth memory is also provided on the tape by a track D, 55 and a write head  $w_3$  and a read head  $R_3$  are magnetically coupled to that track. The write head  $w_3$  responds to binary signals applied to the input terminal  $L'_4$  to produce corresponding recordings in the track D. The read head  $R_3$  is displaced from the write head  $w_3$  along the track D a distance corresponding, for example, to four records. Therefore, the fourth memory is capable of holding four separate records, and any record introduced to that memory during any particular record time can be recovered after an elapse of three record times.

A fifth memory, capable of storing eight records, is also provided on the tape in a track E. The write head  $w_4$  and a read head  $R_4$  are magnetically coupled to the track E. The write head responds to signals received from an input terminal  $L_3$  to record corresponding signals in the track E on the tape. The read head  $R_4$  is displaced from the write head  $w_4$  along the track E a distance corresponding to eight records. Any record introduced to the fifth memory may be recovered after an elapse of seven record times, and the fifth memory is capable of storing eight records at any time.

As mentioned above, the number of individual memories illustrated in FIG. 2A is for purposes of illustration only. More or less tracks on the magnetic track may be used, depending upon the required capabilities of the system. As mentioned, the number of memories follows the progression 1, 1, 2, 4, 8,...2<sup>n</sup> insofar as records stored and record times required to pass therethrough are concerned.

The read heads  $R_0 - R_4$  are connected to corresponding output terminals  $L_1 - L_5$  which, in turn, are respectively connected to logic circuits represented in FIG. 2A by the blocks  $A_1$ ,  $A_2$ ,  $A_3$ ,  $A_4$  and  $A_5$ . These logic circuits will be described in detail subsequently herein. The blocks  $A_1 - A_5$  are respectively connected to the lower input terminals of a series of sorters designated by the blocks  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ ,  $S_5$ , which also will be described.

As shown, each of the sorters  $S_1 - S_3$  includes two input terminals and two output terminals. The individual sorters respond to records serially applied to their two input terminals to process such records in a manner such that the record with the higher identifying number appears at one of the output terminals and the record with the lower identifying numbers appears at the other output terminal.

An input terminal  $I_1$  for the system is connected through the illustrated logic circuitry to the lower input terminal of a sorter  $S_0$ , which is similar to the sorters  $S_1 - S_5$ . A further input terminal  $I_2$  of the system is connected to the upper input terminal of the sorter  $S_5$ . The logic circuitry includes a pair of "AND" gates  $I_2$  and  $I_4$ , an inverter  $I_6$ , and an "OR" gate  $I_8$ , connected as shown.

The lower output terminals of the sorters  $S_1 - S_5$  are respectively connected to logic circuits represented in FIG. 2A by the blocks  $B_1 - B_5$  which also will be described in detail subsequently. These logic circuits are respectively connected to the upper input terminals of the sorters  $S_0 - S_5$ , and the upper output terminals of the sorters  $S_1 - S_4$  are connected to the input terminals of a sorter represented by the block S in FIG. 2A. The sorter S is made up of a plurality of individual blocks, such as shown in FIG. 3. Each of the individual blocks making up the sorter S may be similar to the individual sorters  $S_0 - S_5$ , and each functions in the same manner.

The blocks of the sorter S, as shown in FIG. 3, are connected so that the records applied to the input terminals are rearranged by the blocks, and appear in ascending order, insofar as their identifying numbers are concerned, at the four output terminals designated 2, 3, 4 and 5 when the INVERT term enables the "AND" gate 12 in FIG. 2A, and in descending order when the INVERT term enables the "AND" gate 14. The blocks in the sorter S may be inhibited, so that the records applied to the input terminals are passed through the sorter S in their original order.

The upper output terminal of the sorter S<sub>5</sub> is connected to the output terminal 1 of FIG. 2A, and the output terminals of the sorter S<sub>0</sub> are connected to the output terminals 6 and 7. The output terminals of the sorter S are connected to the remaining output terminals 2, 3, 4 and 5, of FIG. 2A, as indicated above. The output terminals 1—7 of FIG. 2A are connected to correspondingly numbered input numbered 1—7 of FIG. 2B.

The input terminals 1-5 of FIG. 2B are connected to the upper input terminals of respective sorters represented by the block S'<sub>5</sub>, S'<sub>4</sub>, S'<sub>3</sub>, S'<sub>2</sub> and S'<sub>1</sub>. The input terminal 6 of FIG. 2B is connected to a logic circuit represented by the block D, which, in turn, is connected to the lower input terminal of the sorter S'1. The upper output terminals of the sorters S'1, S'2, S'3 and S'4 are connected to logic circuits represented by the blocks C2, C3, C4 and C5 respectively, which in turn are connected to the lower input terminals of the sorters S'2, S'3, S'4 and S's. The lower output terminals of the sorters S's, S'4, S'3, S'2 and S'1 are connected to respective logic circuits represented by the blocks F<sub>5</sub>, F<sub>4</sub>, F<sub>3</sub>, F<sub>2</sub> and F<sub>1</sub>. These latter logic circuits are connected to respective output terminals L's, L'4, L'3, L'2 and L'1, which are connected back to the correspondingly numbered input terminals of FIG. 2A. The upper 75 output terminal of the sorter S's is connected to an output terminal of the system designated 0, and the input terminal 7 of FIG. 2B is connected to a second output terminal of the system designated 02.

Before any records are fed into the system, the memories A-E of FIG. 2A are filled with blanks of any type. The logic circuits A1-A3 respond to these blanks, representing the absence of records, to apply the maximum blanks B\*\* to the sorters S<sub>1</sub>-S<sub>5</sub>. This expedient, as described in the aforesaid patent, whereby the logic circuits A1-A5 generate the maximum blanks B\*\* in the absence of records, obviates the necessity of filling the system with the maximum blanks B\*\* before each input operation.

To carry out the sorting operation, and as shown schematically in FIG. 4, the records having the format shown in FIG. 1 are introduced serially to the input terminal I1, and the minimum blanks Z (all 0's) are introduced to the input terminal I2. In the tables of FIGS. 5 and 9, the B\*\* blanks have been designated by X's to simplify the drawing.

The action of the sorting system during the operation is such that the maximum blanks B\*\* (all 1's) appear at the output terminal 0<sub>1</sub> of FIG. 2B, and the minimum blanks Z (all 0's) appear at the output terminal 02. During this operation, as each record is fed into the sorting system, it is compared with the outputs of the different memories A-E. As explained, until 25 any one of the individual memories is filled with records, its outputs are automatically transformed to maximum blanks B\*\* by the respective logic circuits A<sub>1</sub>-A<sub>5</sub>.

When records appear at the outputs of the individual memories, they are compared with the successive input 30 records during the successive word times, and the least of these records at each word time is altered by the logic  $C_1$ , so that it becomes a maximum record D\*. This causes the altered lowest record to be placed in the longest memory exhibiting a record output. The A<sub>1</sub>-A<sub>5</sub> logic circuits remove the asterisk (\*) from each record as it leaves the corresponding individual memories A-E of FIG. 2B.

In the system of the present invention, and as will be described in detail herein, the records continue to be fed into the system after the system has reached its capacity, with the 40 overflow records being fed out of the system in a generally sorted condition for subsequent recirculation, unless a complete sort is achieved by the first pass.

Should the introduction of the records into the sorting system be interrupted, as shown in the example of FIGS. 4 and 45 5, the maximum blanks B\*\* normally applied to the input terminal I<sub>1</sub>, and the minimum blanks Z are normally applied to the input terminal I2. This causes the records previously fed into the system to be retained therein, and it prevents such records from being displaced out the output terminals 0, and 02 before the system has reached its maximum capacity

During the interruption of the records being fed into the system during the input operation, it is important to assure that as the succession of records shifts into any of the individual memories, there are no interposed B blanks in the series. For that reason, during the interrupted phase of the input operation, the inputs and outputs of each of the individual memories are examined. Whenever a memory is found with a troduced to the system by way of both the input terminals I, and I2, and this results in the introduction of Z blanks into the different memories. The aforesaid introduction of Z blanks into the system at both the input terminals I1 and I2 is continued from one word time to the next during the interruption 65 until none of the memories exhibits a record input and a B\* blank output, which is indicative of a partially filled condition. Then, the system reverts to the introduction of B\*\* blanks to the input terminal  $I_1$ , and of Z blanks to the input terminal  $I_2$ . During the interruption, the Z blanks from the least memory A 70 are not altered by the C1 logic circuit, as is normally the case with the least record in the system, as described above.

After an interruption in the input operation, the inputting of the records can be resumed at any word time. If the Z blanks were placed in the system during the interruption of the input 75 tinued to the sixth record time. However, during the fifth

mode, they will be displaced out of the system by the records subsequently fed into the system, after the longest recordbearing memory has been filled with records. Therefore, when the input mode is resumed, records are again fed to the sorting system by way of the input terminal I1, and Z blanks are again introduced into the system by way of the input terminal I2, this being continued until the longest data-bearing memory is filled with records, at which time records D or D\* or Z blanks, will appear at the output of each memory containing records. When this condition is reached, B\*\* BLANKS ARE introduced to the system by way of the input terminal l2 as long as Z blanks are detected in the memory L<sub>1</sub> or until the inputting of records is again interrupted. Should a subsequent interruption occur, then B\*\* blanks are applied to the input terminal I, and Z blanks are applied to the input terminal I2.

When the absence of Z blanks in the memory A is detected, the system resumes its normal input operation. That is, records continue to be fed into the sorting system by way of the input terminal I, and Z blanks continue to be fed into the sorting system by way of the input terminal I2. As shown in the example of FIGS. 4 and 5, records are fed into the system at successive word times during the input operation, with interruptions occurring during the operation, and with the operation again being resumed at subsequent selected record times. It will be remembered that during each word time during the operation, a B\*\* blank is displaced out from the output terminal 0, and a Z blank is displaced out from the output ter-

During the first record time of the input operation in the example of FIG. 4, a record identified by the integer "13" is fed into the sorting system by way of the input terminal I, and a Z blank is simultaneously applied to the system by way of the input terminal I2. The record "13" is distinguished to "13\*" by the logic circuit C<sub>1</sub> of FIG. 2B. However, since the distinguished record "13\*" is still less than the B\*\* blanks generated by the logic circuits  $A_1 - A_5$ , due to the unfilled condition of all the memories A-E, the record "13\*" is placed in the least memory A (Step 1 of FIG. 5). During the second record time, an interruption occurs, as designated I in FIG. 4. Since under the conditions existing at that record time, there are no memories partially filled with records, a B\*\* blank is applied to the input terminal I1 and a Z blank is applied to the input terminal I2. The record 13\* remains in the least memory during this record time as shown in the Step 2 of FIG. 5.

The input operation in the example of FIG. 4 is resumed at the third record time, and a record identified by the integer "16" is fed into the system by way of the input terminal I<sub>1</sub>, and at the same time a Z blank is fed into the system by way of the input terminal 12. Since the record "16" is less than the record 13\*, the former is placed in the memory A and the latter is placed in the memory B as shown in Step 3 of FIG. 5. During the fourth word time, a record identified by the integer "10" is introduced into the system by way of the input terminal I, and a Z blank is introduced into the system by way of the input terminal I2. The record 10 being the least record in the system is altered by the logic circuit C<sub>1</sub> of FIG. 2B, and the resulting record 10\* is placed in the memory C, the records 13 and 16 record input and a B\* blank output, Z blanks are then in- 60 being placed in the memories A and B respectively, as shown in Step 4 of FIG. 4.

> Another interruption I occurs at the fifth record time, as shown in FIG. 4. However, a condition existed during the previous word time in which the memory C was only partially filled with records (Step 4 of FIG. 5). Therefore, in order to prevent a B\*\* blank from being shifted into the memory C behind the 10\* record, with a resulting deleterious effect on the sorting process, the condition is detected, and for the particular interrupt phase of the fifth word time, Z blanks are applied to both the input terminals I, and I2. This causes the record 16 to shift into the memory C adjacent the record 10\*, the record 13 to shift into the memory B, and a Z blank to shift into the least memory A (Step 5 of FIG. 5).

The aforesaid interruption of the fifth record time is con-

record time there were no partially filled memories, so that a normal interruption control is provided for the sixth record time, whereby a B\*\* blank is applied to the input terminal I, and a Z blank is applied to the input terminal l2. This control produces a rearrangement of records, as shown in Step 6 of FIG. 5, but the Z blank remains in the least memory A. It will be remembered that the C1 logic circuit is ineffective to alter the Z blanks coming out of the least memory A.

During the seventh record time, a record 4 is fed into the system by way of the input terminal I<sub>1</sub>. This resumption of the inputting of records occurs at a record time (Step 6 of FIG. 5) when there are no memories partially filled with records. Then, since there is a Z blank in the least memory A, a B\*\* blank is now applied to the input terminal I2. The record "4" now displaced the Z blank in the least memory A, and the Z blank is forced out of the system by way of the output terminal O2, since it is less than the record "4."

During the eighth record time, a record "3" is applied to the system by way of the input terminal I<sub>1</sub>(FIG. 4). Now, since there are no Z records in the least memory, a Z blank is applied to the input terminal I2. The record "3" is altered to 3\* by the logic circuit C<sub>1</sub>, and it is placed in the memory D. The other records are distributed in the memories A, B and C, as shown by the eighth step in FIG. 5.

During the ninth record time, a record "7" is placed in the system by way of the input terminal I1. The conditions are the same as in the previous word time. That is, there is no Z blank in the least memory (Step 8 of FIG. 5). Therefore a Z blank is applied to the input terminal I2. The record "4" is now altered 30 to 4\*, since the 3\* record remains in the D memory. The resulting 4\* record is placed in the D memory adjacent the 3\* record

During the tenth record time another interruption occurs, as shown by the designation I in FIG. 4. Again, the condition 35 of a partially filled memory exists, in this case in the D memory (Step 9 in FIG. 5), so that again Z blanks are applied to both the input terminals I1 and I2. This again causes a Z blank to appear in the least memory A, and the record "13" is shifted into the D memory.

The aforesaid interruption continues during the 11th record time, as shown in FIG. 4. During this latter record time, the condition of the partially filled D memory persists (Step 10 in the record "16" is shifted into that memory, and Z blanks now appear in both the A and B memories.

The aforesaid interruption (1) continues during the 12th record time. However, there are now no partially filled memories (Step 11 of FIG. 5), so that there is no need to feed another Z blank into the system. Instead, a normal control is exerted, whereby a B\*\* blank is applied to the input terminal I<sub>1</sub> and a Z blank is applied to the input terminal I<sub>2</sub>. The records blanks remain in the A and B memories.

During the ninth record time, a record "7" is placed in the system by way of the input terminal It. The conditions are the same as in the previous word time. That is, there is no Z blank in the least memory (Step 8 of FIG. 5). Therefore, a Z blank is 60 applied to the input terminal l2. The record "4" is now altered to 4\*, since the 3\* record remains in the D memory. The resulting 4\* record is placed in the D memory adjacent the 3\* record.

During the 10th record time another interruption occurs, as 65 shown by the designation f in FIG. 4. Again, the condition of a partially filled memory exists, in this case in the D memory (Step 9 of FIG. 5), so that again Z blanks are applied to both the input terminals I1 and I2. This again causes a Z blank to apthe D memory.

The aforesaid interruption continues during the 11th record time, as shown in FIG. 4. During this latter record time, the condition of the partially filled D memory persists (Step 10 in FIG. 5), so that again Z blanks are applied to both the input 75 following 37-56 word times.

terminals I1 and I2. The D memory is now filled (Step 11) as the record "16" is shifted into that memory, and Z blanks now appear in both the A and B memories.

The aforesaid interruption (1) continues during the 12th record time. However, there are now no partially filled memories (Step 11 of FIG. 5), so that there is no need to feed another Z blank into the system. Instead, a normal control is exerted, whereby a B\*\* blank is applied to the input terminal I<sub>1</sub> and a Z blank is applied to the input terminal I<sub>2</sub>. The records become rearranged, as shown in Step 12 of FIG. 5, but the Z blanks remain in the A and B memories.

During the 13th record time, the inputting of records is resumed and a record "I" is applied to the input terminal I. The condition now exists of a Z blank being contained in the least memory A (FIG. 5, Step 12), but there is no partially filled memory. Therefore, a B\*\* blank is applied to the input terminal  $I_2$ . The remaining Z blank is now placed in the least memory A, the record "1" is placed in the memory B, and the other records are rearranged in the manner shown in Step 13 of FIG. 5. It will be observed that as the altered records 4\* and 3\* leave the D memory they are returned to their unaltered 4 and 3 form, this being achieved by the logic circuit A<sub>1</sub>—A<sub>5</sub>, as will be described. It will also be observed that the Z blanks are not altered as they leave the Z memory.

During the 14th record time the inputting of records is continued, and a record "2" is fed to the input terminal 1. We now have the same condition as in the previous word time in that there are no unfilled memories, and a Z blank exists in the least memory A (Step 13 of FIG. 5). Therefore, again a B\*\* blank is applied to the input terminal I2. This displaced the last Z blank out of the least memory A, and the records are now arranged in the memories in the manner shown in Step 14 of FIG. 5.

For the 15th record time, a record "5" is input to the system by way of the input terminal I<sub>1</sub> (FIG. 4). There is now no Z blank in the least memory A, and there is no unfilled memory. Therefore, normal input phase conditions are restored, and a Z blank is fed to the input terminal I2. The record "1" is al-40 tered by the logic circuit C<sub>1</sub>, and it becomes 1\*, the greatest record. The record 1\* is placed in the E memory, as shown in Step 15 of FIG. 5. The other records are distributed in the manner also known in Step 15 of FIG. 5.

The normal input operation continues during the record terminals I<sub>1</sub> and I<sub>2</sub>. The D memory is now filled (Step 11) as times 16-18, with the records "1," "12" and "11" being suctions of the record "15" and "15" cessively placed in the system by way of the input terminal I1, and with Z blanks being successively applied to the input terminal l2. Another interruption occurs at word time 19. During the latter word time the memory E is unfilled, and in order to prevent a B\*\* blank from being fed into that memory, Z blanks are applied to both the input terminals I, and I2. This creates the condition shown in Step 19 of FIG. 5.

The latter interruption phase continues through the record times 20 and 21, and since the same conditions prevail as durbecome rearranged, as shown in Step 12 of FIG. 5, but the Z 55 ing the word time 19, the Z blanks are still applied to both the input terminals I1 and I2 during each of these word times. Therefore, at the 21st record time, there are Z blanks in both the A and B memories, and there is a Z blank in the C memory adjacent the record 6.

Now, when the input operation is resumed at the record time 22, a record "8" is applied to the input terminal  $l_1$  (FIG. 4). Since there is no Z blank in the least memory A, and since there is an unfilled memory E, a Z blank is applied to the input terminal l2. This causes the records and the Z blanks to assume the positions shown in Step 22 of FIG. 7.

In accordance with the present invention, the inputting operation is continued until the sorter system reaches capacity, and overflows, as described above. The subsequent steps for achieving this are shown, for example, in the examples of pear in the least memory A, and the record "13" is shifted into 70 FIGS. 6 and 7, and in FIGS. 8 and 9. In the example of FIGS. 6 and 7, for example, data continues to be introduced for the following 23-26 record times, whereas in the example of FIGS. 8 and 9, no further data is introduced, but the data already in the machine is outputted from the system during the

During the 23, 24 and 25th record times in the example of FIG. 6, records identified by the integers 9, 24 and 25 respectively are introduced to the sorter by way of the input terminal  $l_1$ , and the  $B^{**}$  blanks are introduced to the sorter by way of the input terminal  $l_2$ . The sorter is filled during these three steps, and no information appears at its output terminals. Instead, the Z blanks appear at the output terminal  $0_1$  and the  $B^{**}$  blanks appear at the output terminal  $0_2$ .

In accordance with the invention, information continues to be fed into the sorting system despite the fact that it is already 10 filled. Therefore, during the 26th record time, a record identified by the integer 15 is applied to the input terminal  $l_1$ and the B\*\* blank is applied to the input terminal I2. As the record 15 enters the sorter, the lowest record 1 is displaced and appears at the output terminal 01, whereas the B\*\* blank 15 appears at the output terminal 02, and the information in the sorter assumes the positions shown, for example, in FIG. 7. During the 27th record time in the example under consideration, an interrupt occurs and a Z blank is applied to the input terminal I1, with a B\*\* blank applied to the input terminal I2. This causes the Z blank to appear at the output terminal 0, and the B\*\* blank to appear at the output terminal 02. Again, the information in the sorting system assumes the configuration shown in FIG. 8.

During the 28th record 2a record identified by the integer 19 is fed into the system by way of the input terminal  $I_1$ , and the  $B^{**}$  blank is fed into the system way way of the input terminal  $I_2$ . This causes the information in the system to assume the positions shown in FIG. 7, with the record 2 being displaced out from the output terminal  $0_1$  and the  $B^{**}$  blank appearing at the output terminal  $0_2$ . The process continues in the manner shown in FIG. 6, with  $B^{**}$  blanks being applied to the input terminal  $I_1$ , and with a Z blank being applied to the input terminal  $I_1$  during an interrupt interval, with a corresponding  $B^{**}$  blank being applied to the input terminal  $I_2$ .

As shown in FIG. 6, whenever a record is introduced into the sorting system, another record is displaced from the output terminal  $0_1$ . Also, the records displaced from the output terminal  $0_1$  are in a generally sorted condition. In fact, in the example of FIGS. 6 and 7, and FIGS. 8, 9, the records appearing at the output terminal  $0_1$  appear in a fully sorted condition. However, for many files, the records, although generally sorted at the end of the first pass, are in a condition such that some of the records may be displaced, and this requires subsequent passes through the system, as will be described.

In the steps of FIGS. 8 and 9, and as mentioned above, although the input operation is terminated, the system continues to displace records through the output terminal  $\mathbf{0}_1$ , until 50 all the records in the sorter have been displaced in a generally sorted condition out of the system. In order to achieve this, and as shown in FIG. 8, a B\*\* blank is applied to the input terminal  $l_1$  and a B\*\* blank is applied to the input terminal  $l_2$ whenever it is desired to displace a record out of the system, 55 from the output terminal 01. The outputting of the records may be interrupted at any time, such as shown during the record times 41, 45, 48 and 49, by introducing a Z blank to the input terminal I2, instead of a B\*\* blank. The Z blank, being smaller than the lowermost record, is then displaced from the 60 output terminal 0, instead of a record, as shown. During this latter operation, the records in the sorting system assume the positions shown in FIG. 9 for each successive step, until all the records have been displaced, and until only B\*\* blanks

Therefore, the basic steps involved by the sorting operation of the present invention includes the first step of filling the sorter with records. This is achieved, as described above, by feeding the unsorted records of the file successively to the system at the input terminal I<sub>1</sub>, and by feeding Z blanks to the 70 system concurrently at the input terminal I<sub>2</sub>. In the interruption intervals during this initial filling operation, and as described above, B\*\* or Z blanks are fed to the input terminal I and Z blanks or B\*\* blanks are fed to the input terminal I<sub>2</sub>, in accordance with the previously described formula.

After the sorting system has been filled, the remaining records of the file to be sorted are fed successively into the sorting system by way of the input terminal I<sub>1</sub>, and as explained in conjunction with FIGS. 6 and 7. During this operation, the records are fed into the sorting system by way of the input terminal I<sub>1</sub>, and the B\*\* blanks are fed into the system by way of the input terminal I<sub>2</sub>. This operation continues until the end of the file, with each record inputted into the system displacing generally the lowest record out from the system, as explained. During any interruption in the file during this latter operation, Z blanks are fed to the system by way of the input terminal I<sub>1</sub>, and B\*\* blanks continue to be fed to the input terminal I<sub>2</sub>. During these interruptions, the Z blanks, rather than the records in the system appear at the output terminal 0<sub>1</sub>, as previously explained.

When the end of the file is reached, and as shown in the example of FIGS. 8 and 9, for example, the system continues to displace the records at the output terminal 0<sub>1</sub>. For this latter operation, the B\*\* blanks are applied to both the input terminal 1<sub>10</sub>and 1<sub>2</sub>. Whenever these blanks are applied to both the input terminals, the generally lowermost record is displaced from the output terminal 0<sub>1</sub>. An interruption may be achieved during this output operation by introducing a Z blank, rather than a B blank for each interruption record time to the input terminal I.

When the end of the file has been reached at the output terminal  $\mathbf{0}_1$ , some means must be provided to indicate whether or not the file has been completely sorted, so that a second pass may be carried out in the event the file is not sorted. This may be achieved in a manner to be described.

Returning now to FIGS. 2A and 2B, it will be appreciated that during the input filling operation, each of the logic circuits A1-A3 serves to supply B\*\* blanks to the input of the sorter S so long as the corresponding memory A-E is not filled with records. This, as mentioned, saves the time which would otherwise be required to prepare the system to receive new data. Each of the logic circuits F1-F5 detects the first output record fed into the corresponding memory A-E and sets a flip-flip N<sub>1</sub> which indicates when the corresponding memory contains at least one record. Each of the logic circuits A<sub>1</sub>—A<sub>5</sub> then responds to the first record outputted by a corresponding memory A-E to set a flip-flop D, to indicate that the particular memory is full of records. The circuits A1-A5 each also serves to remove the distinction appended to the record output of the corresponding memory during the input filling operation, if a distinction has been affixed to a particular record.

During the aforesaid input operation, the logic circuits  $B_1 - B_5$  of FIG. 2A and  $C_2 - C_5$  of FIG. 2B are inactive. The logic circuit  $C_1$  is active during the input operation, in that it appends a distinction to records fed into the memory A, as explained. As also mentioned, distinctions are not applied to the Z blanks when they are fed into the memory A during the input operation.

The logic circuits  $B_1 - B_5$  serve during the output operation to restore the distinction to a corresponding record under certain conditions. If an undistinguished record enters any of the logic circuits  $B_1 - B_5$  and the memory whose output is to be compared with that record contains a record in addition to that output, the record as it appears at the output of the corresponding one of the logic circuits  $B_1 - B_5$  is distinguished.

The sorting units of the sorter S are disabled at the end of the input operation. Then, due to the connections of the sorting units in the sorter S, as shown in FIG. 3, the records which enter the sorter when it is inhibited are not rearranged, and appear in the same order at its output terminals. The logic circuits  $C_1-C_5$  serve to detect a distinguished data output from any of the memories. If such a distinguished data output enters one of the logic circuits  $C_1-C_5$ , the corresponding sorter  $S'_1$  and  $S'_5$  is inhibited from exchanging its outputs.

The logic circuits  $F_1 - F_5$  serve to detect an undistinguished record output. If an undistinguished record output enters any of the logic circuits  $F_1 - F_5$ , and a record is in the memory  $A - F_5$

E whose record is to be compared therewith, the corresponding logic circuit F<sub>1</sub>-F<sub>5</sub> appends a distinction to its output.

A typical sorter circuit is shown in FIG. 10. This sorter circuit is appropriate, for example, for the sorters So-S3, for the sorters S'1-S'5, and for the individual units of the sorter S in FIGS. 2 and 4. The particular sorting circuit shown in FIG. 11 is similar to that described in the aforesaid U.S. Pat. No. 3,399,383. However, as explained in the patent, other types of sorting circuits, including one using a three-state memory, as also described in the patent, may be used.

The sorting circuit of FIG. 10 includes a first input terminal A which receives, for example, a first record A; and it includes a second input terminal B which receives, for example, a second record B. The input terminal A is connected to an "AND" gate 112 and to an inverter network 119. The input terminal B is connected to an "AND" gate 113, and to an inverter network 120. The inverter network 119 responds in known manner to the input record A to produce its complement A on a bit-by-bit basis; and the inverter network 120 20 responds to the record B to produce its complement B on a bit-by-bit basis.

The inverter network 119 is connected to an "AND" gate 121, and the inverter network 120 is connected to an "AND" gate 122. The "AND" gates 112 and 113 are connected to an 25 "OR" gate 114. The "OR" gate 114 is connected to the output terminal designated "Hi." The "AND" gates 121 and 122 are connected to an "OR" gate 123. The "OR" gate 123 is connected to an inverter network 125 which, in turn, is connected to the "Lo" output terminal.

The input terminal A and the output terminal of the inverter 120 are connected to an "AND" gate 135. This means that the binary coded records A and B are introduced to the "AND" gate 135. The input terminal B and the output of the inverter 119 are connected to an "AND" gate 137. Therefore, the bi- 35 the particular records under consideration. nary coded records B and A are applied to the "AND" gate 137. Appropriate bit timing clock pulses derived from the storage medium 12, in the manner described above, are also applied to the "AND" gates 135 and 137 for bit timing pur-

The "AND" gate 135 is connected to the set input terminal of an inhibit flip-flop Q1. The "AND" gate 137 is connected to the set input terminal of an exchange flip-flop Q3. Prior to each input operation, reset pulses are applied to the input terminals of the flip-flops  $Q_1-Q_3$  to reset the flip-flops. The reset 45 output terminal Q<sub>1</sub> of the inhibit flip-flop Q<sub>1</sub> is connected to the "AND" gates 113 and 121, and also to the "AND" gate 137. This output terminal  $\overline{Q}_1$  of the flip-flop applies the term  $\overline{Q_i}$  to the "AND" gates 113, 121 and 137. The reset output terminal  $\overline{Q_3}$  of the exchange flip-flop  $Q_3$  is connected to the "AND" gates 112 and 122, and to the "AND" gate 125. This output terminal of the exchange flip-flop applies the term  $\overline{\mathbb{Q}}_{a}$ to the "AND" gates 112, 122 and 135.

As noted above, in order for the system of FIG. 3 to perform 55 its sorting function, it is necessary for the records A and B to be applied to the sorting system in a bit-by-bit serial manner, with the most significant bit of the identification field of each in the lead. At the commencement of the sorting operation, both the inhibit flip-flop Q1 and the exchange flip-flop Q3 are 60 reset, so that both the terms Q, and Q, are false. Therefore, at the beginning of the operation, the "AND" gates 112, 113, 121 and 122 are all enabled. The records A and B pass through the "AND" gates on a serial bit-by-bit basis, so long as the corresponding bits of the two records are both either 1 65 of records, so that the output operation may begin; or 0. These bits then appear unchanged, at the output terminals "Hi" and "Lo."

Assume that a bit in the identifying field of the record A is 0 at the time when the corresponding bit in the identifying field of the record B is a 1, and that this is the first instance that a 70 condition of one record having a bit different than the corresponding bit of the other record has occurred, this means that the identifying signal of the record B represents a higher integer than the identifying signal of the record A. Under this condition, the term A.B is true, so that the "AND" gate 137 is 75 troduced to the corresponding memory;

enabled. The next clock pulse CL sets the exchange flip-flop Q3, so that the "AND" gates 112 and 122 are disabled. Also, the "AND" gate 135 is disabled, so that no further triggering of either of the flip-flops Q1 or Q3 is possible during the particular comparison operation.

Following the detection of a 0 bit in the identifying field of the A record, and the simultaneous detection of a 1 bit in the identifying field of the B record, indicating that the B record is greater than the A record, the remaining bits of the control and data fields of the data record pass through the enabled "AND" gate 122 in complemented (A) form, and through the "OR" gate 123 and the inverter 125 to the output terminal "Lo."

The corresponding bits of the remaining portions of the identifying signals and the bits in the data field of the B record pass through the enabled "AND" gates 112 and 114 to the output terminal "Hi." Therefore, the detection of inequality between the identifying signals in the identifying fields of the A records causes the lower A record to appear at the output terminal "Lo" and the higher B record to appear at the output terminal "Hi."

Conversely, should the comparison described above reach a point at which the identifying signal of the Z record has a 1 bit at the time when the identifying signal of the B record has a 0 bit indicating that the A record is greater than the B record, the term A.B is applied to the "AND" gate 135 to enable the "AND" gate, so that the next clock pulse sets the inhibit flipflop Q<sub>i</sub>.

This setting of the inhibit flip-flop Q<sub>1</sub> causes the "AND" gates 113 and 121 to become disabled, and also causes the "AND" gate to become disabled. The disabling of the "AND" gate 137 prevents any setting of the exchange flip-flop 123 during the remaining portion of the comparison process for

Under the latter set of conditions, the greater record A is passed through the "AND" gate 112 and through the "OR" gate 114 to the "Hi" output terminal; whereas, the lower record B is passed through the inverter 120, through the 40 "AND" gate 122, and through the "OR" gate 123 to the inverter 125. This latter record B is reinverted to the inverter 125, and it appears at the "Lo" output terminal in its original form.

As noted above, the sorting network of FIG. 10 can be used for the sort units S<sub>0</sub>—S<sub>5</sub> and S<sub>1</sub>'—S<sub>5</sub>' and for the units making

For convenience, the bit timing of the control field bits of the different records and blanks used in the system are shown in FIG. 11.

The flip-flops involved in the system are as follows:

Input Mode (I.M.) (FIG. 12)-Indicates the input operation:

Data Input (D) (not illustrated—Controlled by the system introducing records to the sorter;

Part Full (P.F.) (FIG. 13)-Indicates when any of the memories A-E in the system has a data input with a B\*\* out-

End of File (E.O.F.) (FIG. 12)—Indicates that the last record in the file has been fed into the system;

Exchange Indicator (R) (FIG. 13)—Detects exchanges in sorters during each pass of the information through the

Sorter Full (S.F.) (FIG. 13)—Indicates that the sorter is full

Z Blank Detector (Z1) (FIG. 13)—Detects the presence of Z blanks in the memory A;

B Blank Detector (B1) (FIG. 13)—Detects B blanks in the memory A to indicate the completion of a pass through the

Output Mode (O.M.) (FIG. 12)—Indicates that an output operation is taking place;

Data Indicator (N<sub>1</sub>) (N<sub>2</sub>-N<sub>5</sub>) (one of each memory except A and B) (FIG. 14)—Indicates that a record has been in3,387,03

Memory Full Indicator  $(D_4)$   $(D_4-D_5)$  (one for each memory) (FIG. 13)—Indicates that the corresponding memory is full of records by detecting a record at the output of the memory and, during the output operation the flip-flop indicates the presence of an undistinguished record in the corresponding memory.

15

As shown in FIG. 12, the input mode flip-flop I.M. has an "AND" gate 300 connected to its set input terminal, and an "AND" gate 302 connected to its reset input terminal. The terms D and  $t_1$  are introduced to the "AND" gate 300, and the terms E.O.F. and  $t_1$  are introduced to the "AND" gate 302. This means that the input operation of the sorter is commenced, by the setting of the input mode flip-flop, under an appropriate command from the system applying the records to the sorter, which sets the aforementioned flip-flop D (not shown). The input operation is terminated, and the flip-flop I.M. is thereby reset, when the end of file indication  $(\overline{D})$  from the system applying the records causes the end of file flip-flop E.O.F. to be set.

The end of file flip-flop E.O.F. has an "AND" gate 403 connected to its set input terminal, and an "AND" gate 306 connected to its reset input terminal. The terms 1.M.,  $\overline{D}$  and  $t_1$  are introduced to the "AND" gate 304; and the terms  $B_1$  and  $t_1$  are end of file flip-flop E.O.F. is set, so as to terminate the input operation, upon the receipt of the end of file  $(\overline{D})$  command from the system feeding the records to the sorter, and assuming that the sorter is in its input operation (1.M.). The end of file flip-flop E.O.F. remains set until the B blank indicator flip-flop E.O.F. remains set until the B blank indicator flip-flop E.O.F. is the memory  $B_1$  detects blanks in the memory  $B_2$  to the set input terminal tioned above, the flip-flops in the memory  $B_2$  and the flip-flop  $B_3$  shown in FIG. 14, the memory  $B_4$  and the flip-flop  $B_4$ . Since the memories  $A_4$  and the flip-flop  $B_4$  so in need for the part junction therewith. The flip with the memory  $D_4$  and so cated with the memory  $D_4$  and so c

The output mode flip-flop (O.M.) includes an "AND" gate 308 connected to its set input terminal, and an "AND" gate 310 connected to its reset input terminal. The terms E.O.F. and  $t_2$  are applied to the "AND" gate 308, and the terms  $B_1$  and  $t_1$  are applied to the "AND" gate 310. The output mode is initiated when the output mode flip-flop O.M. is set, this occurring when the sorter becomes full of records, as indicated by the sorter full flip-flop S.F. being set. The output mode then continues until a blank is detected in the least memory  $A_1$  as indicated by the setting of the blank indicator flip-flop  $B_1$ .

The exchange flip-flop R in FIG. 13 includes an "AND" gate 330 connected to its set input terminal, and an "OR" gate 45 332 connected to its reset input terminal. The exchange flip-flop is set by any blank or distinguished record out of any of the memories A-E, due to the terms  $L_t$  and  $t_2$  applied to the "AND" gate 330. Then, the terms  $L_t$ ,  $\overline{t_2}$  and  $E_t$  applied to an "AND" gate 334, one of which is provided for each sorter, and which are connected to the "OR" gate 332, cause the exchange flip-flop R to be reset should a record exchange take place in any one of the sorters. Should no exchange take place, the exchange flip-flop R remains set during the particular pass.

The sorter full flip-flop S.F. responds to the terms  $D_1 - D_5$  applied to an "AND" gate 336 to be set and indicate that all the memories in the sorter contain records, and this flip-flop serves to set the output mode flip-flop O.M. to put the system in its output operation after it is filled with records. The setting of the output mode flip-flop serves to reset the sorter full flip-flop S.F. The S.F. flip-flop indicates that the system cannot accept any more records, although under some circumstances there still may be Z blanks in the system.

The  $Z_1$  flip-flop is used to detect Z blanks in the memory A, so that these blanks will not be distinguished during the input operation. The  $Z_1$  flip-flop includes an "AND" gate 340 connected to its set input terminal. The set output terminal of a flip-flop 342 is connected to the "AND" gate 340; and the term  $t_3$  and  $\overline{L_1}$  are applied to the "AND" gate. An "AND" gate 344 is connected to the set input terminal of the flip-flop 342, and the terms  $\overline{L_1}$  and  $t_2$  are applied to the "AND" gate 344. The term  $t_4$  resets the flip-flop 342, and the term  $t_1$  resets the term  $Z_1$ .

The presence of a Z blank in the A memory sets the flip-flop 342 to enable the "AND" gate 340, and thereby permit the  $Z_1$  flip-flop to be set.

16

The flip-flop  $B_1$  detects B blanks in the least memory A. This flip-flop is set each  $t_1$  time by the term  $t_1$  applied to its set input terminal. An "OR" gate 346 is connected to its reset input terminal, and "AND" gates 343, 345 and 347 are connected to its reset input terminal. The terms  $L'_1$  and  $t_1$  are applied to the "AND" gate 343; the terms  $L'_1$  and  $t_2$  are applied to the "AND" gate 345; and the terms  $L'_1$  and  $t_1$  are applied to the "AND" gate 347. The flip-flop  $B_1$  remains set only if a B blank is fed into the memory A.

As mentioned above, each of the memories A-E includes a  $D_i$  flip-flop, and the memories C-E each include a  $N_i$  flip-flop. When both the  $N_i$  and  $D_i$  flip-flops are reset, the corresponding memory is empty. When the flip-flop  $N_i$  is set, it means that the corresponding memory is partially full of records. When both the flip-flops  $N_i$  and  $D_i$  are set, it means that the corresponding memory is full of records. As also mentioned above, the flip-flops  $N_i$  and  $D_i$  are used to indicate the presence of undistinguished records in the output mode.

As shown in FIG. 14, the flip-flop  $B_1$  is associated with the memory A, and the flip-flop  $B_2$  is associated with the memory B. Since the memories A and B are "one word" memories, there is no need for the part full flip-flop  $N_1$  to be used in conjunction therewith. The flip-flops  $D_3$  and  $N_3$  are associated with the memory C; the flip-flops  $D_4$  and  $N_4$  are associated with the memory  $D_4$ ; and the flip-flops  $D_5$  and  $N_5$  are associated with the memory  $P_5$ .

An "AND" gate 350 is connected through an "OR" gate 351 to the set input terminal of the flip-flop  $D_1$ ; and an "AND" gate 352 is connected to the reset input terminal of that flip-flop. An "AND" gate 353 is connected to the "OR" gate 351. The terms O.M.,  $\overline{L}_1$  and  $t_2$  2 applied to the "AND" gate 353. The terms O.M.,  $\overline{L}_1$  and  $t_1$  are applied to the "AND" gate 350; and the terms O.M.,  $\overline{L}_1$  and  $t_2$  are applied to the "AND" gate 352. This means that whenever a record is outputted from the memory A during the input operation, the terms  $\overline{L}_1$ ,  $t_1$  set the flip-flop  $D_1$ . Conversely, whenever an undistinguished record is outputted from the memory A during the output mode, the terms  $\overline{L}_1$ ,  $t_2$  reset the flip-flop  $D_1$ .