(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-166350

(P2007-166350A)

(43) 公開日 平成19年6月28日(2007.6.28)

| (51) Int.CI.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>HO4B</b> 1/707 (2006.01) | HO4J 13/00 | D 5KO22     |

| <b>HO4L</b> 7/00 (2006.01)  | HO4L 7/00  | C 5KO47     |

| <b>HO4B</b> 7/26 (2006.01)  | HO4B 7/26  | N 5KO67     |

|                             | HO4B 7/26  | K           |

審査請求 未請求 請求項の数 18 O L (全 25 頁)

|                       |                                                          |                                                                                                                                                                                                                                                       |

|-----------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号<br>(22) 出願日 | 特願2005-361205 (P2005-361205)<br>平成17年12月15日 (2005.12.15) | (71) 出願人 399117121<br>アジレント・テクノロジーズ・インク<br>A G I L E N T T E C H N O L O G I E<br>S, I N C.<br>アメリカ合衆国カリフォルニア州サンタクララ スティーブンス・クリーク・ブルバード 5301<br>5301 Stevens Creek<br>Boulevard Santa Clara California U. S. A<br><br>(74) 代理人 100105913<br>弁理士 加藤 公久 |

|-----------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

最終頁に続く

(54) 【発明の名称】ゲートアレイプログラム装置、測定装置、プログラム

## (57) 【要約】

【課題】設計自由度が高い同期捕捉装置の提供

【解決手段】同期捕捉装置において、それぞれ位相が異なる複数の疑似雑音符号を発生し、複数の疑似雑音符号をN個にグループ化し、グループ毎に、被測定信号に含まれる疑似雑音符号と各疑似雑音符号との各相關処理を時分割多重する。各グループにおいて、疑似雑音符号は、固定された順序およびタイミングで周期的に繰り返し選択される。

【選択図】図2

## 【特許請求の範囲】

## 【請求項 1】

測定装置に具備される再構成可能なゲートアレイをプログラムする装置であって、前記ゲートアレイを、

被測定信号に含まれる第一の疑似雑音符号と同じ符号系列であって、それぞれ位相が異なるK個の第二の疑似雑音符号を発生する疑似雑音符号発生器と、

前記K個のうち2以上のM個の前記第二の疑似雑音符号を選択対象とし、選択対象の前記第二の疑似雑音符号から1つを選択して出力する2以上のN個のセレクタであって、あるセレクタが選択対象とする前記第二の疑似雑音符号がその他のセレクタの選択対象外であるセレクタと、

各前記セレクタに個々に接続されるN個の乗算器であって、対応する前記セレクタが出力する前記第二の疑似雑音符号と前記第一の疑似雑音符号とを乗ずる乗算器と、

各前記乗算器に個々に接続されるN個の加算器であって、対応する前記乗算器が出力する乗算結果を前記乗算結果に対応する前記第二の疑似雑音符号の位相ごとに累積加算する加算器と、

前記加算器の加算結果のうち絶対値が最大である加算結果または所定閾値を超える加算結果に対応する前記第二の疑似雑音符号の位相を、前記第一の疑似雑音符号の位相として検出する検出器、

として機能するようにプログラムし、

各前記セレクタが、対応する前記乗算器に前記第一の疑似雑音符号の同一チップデータが供給されている間に、選択対象の前記第二の疑似雑音符号の全てが前記対応する乗算器に供給されるように、前記第二の疑似雑音符号を選択し、

前記測定装置が前記第一の疑似雑音符号に同期できるようにすることを特徴とするゲートアレイプログラム装置。

## 【請求項 2】

被測定信号を格納する記憶装置を備える測定装置に具備され、前記被測定信号のチップレートよりも速いクロックで動作する再構成可能なゲートアレイをプログラムする装置であって、

前記ゲートアレイを、

前記被測定信号に含まれる第一の疑似雑音符号と同じ符号系列であって、それぞれ位相が異なるK個の第二の疑似雑音符号を発生する疑似雑音符号発生器と、

前記K個のうち2以上のM個の前記第二の疑似雑音符号を選択対象とし、選択対象の前記第二の疑似雑音符号から1つを選択して出力する2以上のN個のセレクタであって、あるセレクタが選択対象とする前記第二の疑似雑音符号がその他のセレクタの選択対象外であるセレクタと、

各前記セレクタに個々に接続されるN個の乗算器であって、対応する前記セレクタが出力する前記第二の疑似雑音符号と前記記憶装置から読み出される前記被測定信号に含まれる前記第一の疑似雑音符号とを乗ずる乗算器と、

各前記乗算器に個々に接続されるN個の加算器であって、対応する前記乗算器が出力する乗算結果を前記乗算結果に対応する前記第二の疑似雑音符号の位相ごとに累積加算する加算器と、

前記加算器の加算結果のうち絶対値が最大である加算結果または所定閾値を超える加算結果に対応する前記第二の疑似雑音符号の位相を、前記第一の疑似雑音符号の位相として検出する検出器、

として機能するようにプログラムし、

各前記セレクタが、対応する前記乗算器に前記第一の疑似雑音符号の同一チップデータが供給されている間に、選択対象の前記第二の疑似雑音符号の全てが前記対応する乗算器に供給されるように、前記第二の疑似雑音符号を選択し、

前記測定装置が前記第一の疑似雑音符号に同期できるようにすることを特徴とするゲートアレイプログラム装置。

10

20

30

40

50

**【請求項3】**

各前記セレクタが、固定された順序およびタイミングで周期的に繰り返し前記第二の疑似雑音符号を選択し、

各前記加算器が、対応する前記セレクタにおける前記第二の疑似雑音符号の選択周期と等しい時間遅延を有する第一の遅延器を用いて累積加算を行う、

ことを特徴とする請求項1または請求項2に記載のゲートアレイプログラム装置。

**【請求項4】**

前記疑似雑音符号発生器が、前記第一の疑似雑音符号と同じ符号系列を有する单一の第三の疑似雑音符号を基に、複数の第二の遅延器を介して、前記第二の疑似雑音符号の全てを並列的に発生することを特徴とする請求項1乃至請求項3のいずれかに記載のゲートアレイプログラム装置。10

**【請求項5】**

前記第三の疑似雑音符号が、前記ゲートアレイ内の記憶領域に予め格納された疑似雑音符号であることを特徴とする請求項4に記載のゲートアレイプログラム装置。

**【請求項6】**

前記Mおよび前記Nのそれぞれが、前記ゲートアレイのプログラム毎に異なる値を有することを特徴とする請求項1乃至請求項5のいずれかに記載のゲートアレイプログラム装置。20

**【請求項7】**

再構成可能なゲートアレイを具備する測定装置であって、

前記ゲートアレイが、

被測定信号に含まれる第一の疑似雑音符号と同じ符号系列であって、それぞれ位相が異なるK個の第二の疑似雑音符号を発生する疑似雑音符号発生器と、

前記K個のうち2以上のM個の前記第二の疑似雑音符号を選択対象とし、選択対象の前記第二の疑似雑音符号から1つを選択して出力する2以上のN個のセレクタであって、あるセレクタが選択対象とする前記第二の疑似雑音符号がその他のセレクタの選択対象外であるセレクタと、

各前記セレクタに個々に接続されるN個の乗算器であって、対応する前記セレクタが出力する前記第二の疑似雑音符号と前記第一の疑似雑音符号とを乗ずる乗算器と、30

各前記乗算器に個々に接続されるN個の加算器であって、対応する前記乗算器が出力する乗算結果を前記乗算結果に対応する前記第二の疑似雑音符号の位相ごとに累積加算する加算器と、

前記加算器の加算結果のうち絶対値が最大である加算結果または所定閾値を超える加算結果に対応する前記第二の疑似雑音符号の位相を、前記第一の疑似雑音符号の位相として検出する検出器、

として機能するようにプログラムされ、

各前記セレクタが、対応する前記乗算器に前記第一の疑似雑音符号の同一チップデータが供給されている間に、選択対象の前記第二の疑似雑音符号の全てが前記対応する乗算器に供給されるように、前記第二の疑似雑音符号を選択し、40

前記測定装置が前記第一の疑似雑音符号に同期できるようにしたことを特徴とする測定装置。

**【請求項8】**

被測定信号を格納する記憶装置と、前記被測定信号のチップレートよりも速いクロックで動作する再構成可能なゲートアレイとを備える測定装置であって、

前記ゲートアレイが、

前記被測定信号に含まれる第一の疑似雑音符号と同じ符号系列であって、それぞれ位相が異なるK個の第二の疑似雑音符号を発生する疑似雑音符号発生器と、

前記K個のうち2以上のM個の前記第二の疑似雑音符号を選択対象とし、選択対象の前記第二の疑似雑音符号から1つを選択して出力する2以上のN個のセレクタであって、あるセレクタが選択対象とする前記第二の疑似雑音符号がその他のセレクタの選択対象外で50

あるセレクタと、

各前記セレクタに個々に接続されるN個の乗算器であって、対応する前記セレクタが出力する前記第二の疑似雑音符号と前記記憶装置から読み出される前記被測定信号に含まれる前記第一の疑似雑音符号とを乗ずる乗算器と、

各前記乗算器に個々に接続されるN個の加算器であって、対応する前記乗算器が出力する乗算結果を前記乗算結果に対応する前記第二の疑似雑音符号の位相ごとに累積加算する加算器と、

前記加算器の加算結果のうち絶対値が最大である加算結果または所定閾値を超える加算結果に対応する前記第二の疑似雑音符号の位相を、前記第一の疑似雑音符号の位相として検出する検出器、

として機能するようにプログラムされ、

各前記セレクタが、対応する前記乗算器に前記第一の疑似雑音符号の同一チップデータが供給されている間に、選択対象の前記第二の疑似雑音符号の全てが前記対応する乗算器に供給されるように、前記第二の疑似雑音符号を選択し、

前記測定装置が前記第一の疑似雑音符号に同期できるようにしたことを特徴とする測定装置。

#### 【請求項9】

各前記セレクタが、固定された順序およびタイミングで周期的に繰り返し前記第二の疑似雑音符号を選択し、

各前記加算器が、対応する前記セレクタにおける前記第二の疑似雑音符号の選択周期と等しい時間遅延を有する第一の遅延器を用いて累積加算を行う、

ことを特徴とする請求項7または請求項8に記載の測定装置。

#### 【請求項10】

前記疑似雑音符号発生器が、前記第一の疑似雑音符号と同じ符号系列を有する单一の第三の疑似雑音符号を基に、複数の第二の遅延器を介して、前記第二の疑似雑音符号の全てを並列的に発生することを特徴とする請求項7乃至請求項9のいずれかに記載の測定装置。

#### 【請求項11】

前記第三の疑似雑音符号が、前記ゲートアレイ内の記憶領域に予め格納された疑似雑音符号であることを特徴とする請求項10に記載の測定装置。

#### 【請求項12】

前記Mおよび前記Nのそれぞれが、前記ゲートアレイのプログラム毎に異なる値を有することを特徴とする請求項1乃至請求項5のいずれかに記載の測定装置。

#### 【請求項13】

再構成可能なゲートアレイを備える測定装置に具備されるか接続されるコンピュータに、被測定信号に含まれる第一の疑似雑音符号に前記測定装置が同期するように前記ゲートアレイをプログラムさせるプログラムであって、

前記プログラムされたゲートアレイが、

前記第一の疑似雑音符号と同じ符号系列であって、それぞれ位相が異なるK個の第二の疑似雑音符号を発生する疑似雑音符号発生器と、

前記K個のうち2以上のM個の前記第二の疑似雑音符号を選択対象とし、選択対象の前記第二の疑似雑音符号から1つを選択して出力する2以上のN個のセレクタであって、あるセレクタが選択対象とする前記第二の疑似雑音符号がその他のセレクタの選択対象外であるセレクタと、

各前記セレクタに個々に接続されるN個の乗算器であって、対応する前記セレクタが出力する前記第二の疑似雑音符号と前記第一の疑似雑音符号とを乗ずる乗算器と、

各前記乗算器に個々に接続されるN個の加算器であって、対応する前記乗算器が出力する乗算結果を前記乗算結果に対応する前記第二の疑似雑音符号の位相ごとに累積加算する加算器と、

前記加算器の加算結果のうち絶対値が最大である加算結果または所定閾値を超える加算

10

20

30

40

50

結果に対応する前記第二の疑似雑音符号の位相を、前記第一の疑似雑音符号の位相として検出する検出器、

として機能し、

各前記セレクタが、対応する前記乗算器に前記第一の疑似雑音符号の同一チップデータが供給されている間に、選択対象の前記第二の疑似雑音符号の全てが前記対応する乗算器に供給されるように、前記第二の疑似雑音符号を選択する、

ことを特徴とするプログラム。

#### 【請求項 14】

被測定信号を格納する記憶装置と、前記被測定信号のチップレートよりも速いクロックで動作する再構成可能なゲートアレイとを備える測定装置に具備されるか接続されるコンピュータに、前記被測定信号に含まれる第一の疑似雑音符号に前記測定装置が同期するように前記ゲートアレイをプログラムさせるプログラムであって、

前記プログラムされたゲートアレイが、

前記第一の疑似雑音符号と同じ符号系列であって、それぞれ位相が異なる K 個の第二の疑似雑音符号を発生する疑似雑音符号発生器と、

前記 K 個のうち 2 以上の M 個の前記第二の疑似雑音符号を選択対象とし、選択対象の前記第二の疑似雑音符号から 1 つを選択して出力する 2 以上の N 個のセレクタであって、あるセレクタが選択対象とする前記第二の疑似雑音符号がその他のセレクタの選択対象外であるセレクタと、

各前記セレクタに個々に接続される N 個の乗算器であって、対応する前記セレクタが出力する前記第二の疑似雑音符号と前記記憶装置から読み出される前記被測定信号に含まれる前記第一の疑似雑音符号とを乗ずる乗算器と、

各前記乗算器に個々に接続される N 個の加算器であって、対応する前記乗算器が出力する乗算結果を前記乗算結果に対応する前記第二の疑似雑音符号の位相ごとに累積加算する加算器と、

前記加算器の加算結果のうち絶対値が最大である加算結果または所定閾値を超える加算結果に対応する前記第二の疑似雑音符号の位相を、前記第一の疑似雑音符号の位相として検出する検出器、

として機能し、

各前記セレクタが、対応する前記乗算器に前記第一の疑似雑音符号の同一チップデータが供給されている間に、選択対象の前記第二の疑似雑音符号の全てが前記対応する乗算器に供給されるように、前記第二の疑似雑音符号を選択する、

ことを特徴とするプログラム。

#### 【請求項 15】

各前記セレクタが、固定された順序およびタイミングで周期的に繰り返し前記第二の疑似雑音符号を選択し、

各前記加算器が、対応する前記セレクタにおける前記第二の疑似雑音符号の選択周期と等しい時間遅延を有する第一の遅延器を用いて累積加算を行う、

ことを特徴とする請求項 13 または請求項 14 に記載のプログラム。

#### 【請求項 16】

前記疑似雑音符号発生器が、前記第一の疑似雑音符号と同じ符号系列を有する单一の第三の疑似雑音符号を基に、複数の第二の遅延器を介して、前記第二の疑似雑音符号の全てを並列的に発生することを特徴とする請求項 13 乃至請求項 15 のいずれかに記載のプログラム。

#### 【請求項 17】

前記第三の疑似雑音符号が、前記ゲートアレイ内の記憶領域に予め格納された疑似雑音符号であることを特徴とする請求項 16 に記載のプログラム。

#### 【請求項 18】

前記 M および前記 N のそれぞれが、前記ゲートアレイのプログラム毎に異なる値を有しうることを特徴とする請求項 13 乃至請求項 17 のいずれかに記載のプログラム。

10

20

30

40

50

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、CDMA装置に係り、特に同期捕捉機能を有するCDMA装置に関する。

## 【背景技術】

## 【0002】

W-CDMA方式の携帯電話機や基地局など、直接拡散方式のCDMA受信機は、受信信号を復調するために、受信信号の拡散符号と同期する必要がある。同期方法の代表的なものとしては、直列的に演算処理するスライディング相関器（Sliding Correlator）を用いる方法や並列的に演算処理するマッチトフィルタ（Matched Filter）を用いる方法がある（例えば、特許文献1～5および非特許文献1～5を参照。）。これらの方法による同期は、受信ベースバンド信号の拡散符号の位相（タイミング）と受信機内で生成された拡散符号の位相とが一致する時に、受信機内で生成した拡散符号と受信ベースバンド信号との相関値が最大になることを利用している。

## 【0003】

【特許文献1】特開2000-36775（第3頁、図21、図22）

【特許文献2】特開2001-7734号公報（第3頁、第5頁、図1）

【特許文献3】特開平11-112384号公報（第4～8頁、図2、図6）

【特許文献4】特開平10-98412号公報（図1）

【特許文献5】特開平8-111653号公報（第4～5頁、図1～4）

【非特許文献1】菅原崇行、宮永喜一、「演算量を低減したDS-CDMA用並列ディジタル・マッチトフィルタの構成」、平成15年11月5～7日、第18回ディジタル信号処理シンポジウム

【非特許文献2】エッサム・サウラウアー（Essam Sourour）、ガプタ・サムシュワー・シー・（Someshwar C.gupta），「非選択的および周波数選択ライシアン・フェージング・チャンネルにおける直接拡散方式スペクトラム拡散並列捕捉（Direct-Sequence Spread-Spectrum Parallel Acquisition in Nonselective and Frequency-Selective Rician Fading Channels）」、米国、アイ・イー・イー・ジャーナル（Selected Areas in Communications, IEEE Journal），10巻3号（Volume 10, Issue 3），1992年4月，p 535 - 544

【非特許文献3】山田真（Makoto Yamada）、神尾享秀（Yukiyoshi Kamio）、和田善生（Yoshio Wada），「直接拡散方式スペクトラム拡散信号の並列マッチトフィルタを用いた捕捉（Acquisition of Direct-Sequence Spread-Spectrum Signal with Parallel Matched Filters）」、2000年9月18～21日、第11回アイ・イー・イー・国際シンポジウム（Personal, Indoor and Mobile Radio Communications, 2000. PIMRC 2000. The 11th IEEE International Symposium）

【非特許文献4】タン・シャオ・ヘン（TAN Xiao-heng）、ヤン・シ・チオン（YANG Shizhong），「ディジタル・マッチトフィルタに基づくロングPNコード捕捉回路の設計とFPGAでの実現（The Design and FPGA Realization of the Long PN Code Acquisition Circuit Based on Digital matched-filter）」、2003年10月、第5回国際大会（ASIC, 2003. Proceedings. 5th International Conference）

【非特許文献5】ジュン・ムーン（June Moon）、ヤン・ホワン・リー（YANG Hwan Lee），「レイリー・フェージング・チャンネルにおけるPNシーケンスの並列捕捉およびマルチ・キャリアCDMAシステムへの適用（Parallel Acquisition of PN Sequences in Rayleigh Fading Channel And the Application to the Multi-Carrier CDMA Systems）」、2001年9月30日～10月3日、第12回アイ・イー・イー・国際シンポジウム（Personal, Indoor and Mobile Radio Communications, 2001 12th IEEE International Symposium）

## 【発明の開示】

## 【発明が解決しようとする課題】

10

20

30

40

50

## 【0004】

C D M A 方式の信号を測定するディジタル受信機や測定装置は、A S I C やF P G Aなどのゲートアレイで同期捕捉装置や復調装置を構成して、当該ゲートアレイに被測定信号を処理させる。特に、測定装置は、基地局や携帯電話機に比べて市場に出回る数が少なく、また、基地局や携帯電話機と異なり汎用性が求められるので、F P G Aで構成されることが多い。ところで、ゲートアレイの設計の途中段階において、同期捕捉に許される処理時間や同期捕捉における相関長に変更が生じる場合がある。あるいは、既存の製品またはプラットフォームを流用して、新しいC D M A 方式に対応した装置を開発する場合がある。これらの場合、ゲートアレイは、使用できるリソース数や動作クロック周波数が概ねあるいは完全に決まっている。一般に、スライディング相関器は、相関処理に必要な乗算器および加算器がそれぞれ1つずつあれば足りる一方、同期捕捉に要する時間が長い。また、マッチトフィルタは、高速に同期捕捉を行える一方、膨大な数の乗算器および加算器を必要とする。従って、上記のような変更に対応しようとすると、所望の仕様の同期捕捉装置が使用予定のゲートアレイにうまく適合せず、ゲートアレイそのものの変更やゲートアレイの動作クロック周波数の変更を余儀なくされる場合があって、設計効率が悪い。そこで、所望の仕様の同期捕捉装置をゲートアレイ内に実現するにあたり、ゲートアレイ・リソースの所要数やゲートアレイの動作クロック周波数を従来に比べて柔軟に選択できる同期捕捉装置の提供が望まれている。また、測定装置は、同期捕捉装置や復調装置だけでなく、測定に必要な装置も同一ゲートアレイで構成される場合が多い。近年、測定装置において、同時にできるだけ多くの項目の測定を実施することが期待されており、ゲートアレイ内に実現される各装置のリソース消費の低減が望まれている。10 20

## 【課題を解決するための手段】

## 【0005】

本発明は、上記の課題を解決するために為されたものである。すなわち、本第一の発明は、測定装置に具備される再構成可能なゲートアレイをプログラムする装置であって、前記ゲートアレイを、被測定信号に含まれる第一の疑似雑音符号と同じ符号系列であって、それぞれ位相が異なるK個の第二の疑似雑音符号を発生する疑似雑音符号発生器と、前記K個のうち2以上のM個の前記第二の疑似雑音符号を選択対象とし、選択対象の前記第二の疑似雑音符号から1つを選択して出力する2以上のN個のセレクタであって、あるセレクタが選択対象とする前記第二の疑似雑音符号がその他のセレクタの選択対象外であるセレクタと、各前記セレクタに個々に接続されるN個の乗算器であって、対応する前記セレクタが出力する前記第二の疑似雑音符号と前記第一の疑似雑音符号とを乗ずる乗算器と、各前記乗算器に個々に接続されるN個の加算器であって、対応する前記乗算器が出力する乗算結果を前記乗算結果に対応する前記第二の疑似雑音符号の位相ごとに累積加算する加算器と、前記加算器の加算結果のうち絶対値が最大である加算結果または所定閾値を超える加算結果に対応する前記第二の疑似雑音符号の位相を、前記第一の疑似雑音符号の位相として検出する検出器、として機能するようにプログラムし、各前記セレクタが、対応する前記乗算器に前記第一の疑似雑音符号の同一チップデータが供給されている間に、選択対象の前記第二の疑似雑音符号の全てが前記対応する乗算器に供給されるように、前記第二の疑似雑音符号を選択し、前記測定装置が前記第一の疑似雑音符号に同期できるようにすることを特徴とするものである。30 40

## 【0006】

また、本第二の発明は、被測定信号を格納する記憶装置を備える測定装置に具備され、前記被測定信号のチップレートよりも速いクロックで動作する再構成可能なゲートアレイをプログラムする装置であって、前記ゲートアレイを、前記被測定信号に含まれる第一の疑似雑音符号と同じ符号系列であって、それぞれ位相が異なるK個の第二の疑似雑音符号を発生する疑似雑音符号発生器と、前記K個のうち2以上のM個の前記第二の疑似雑音符号を選択対象とし、選択対象の前記第二の疑似雑音符号から1つを選択して出力する2以上のN個のセレクタであって、あるセレクタが選択対象とする前記第二の疑似雑音符号がその他のセレクタの選択対象外であるセレクタと、各前記セレクタに個々に接続されるN個の乗算器であって、50

個の乗算器であって、対応する前記セレクタが出力する前記第二の疑似雑音符号と前記記憶装置から読み出される前記被測定信号に含まれる前記第一の疑似雑音符号とを乗ずる乗算器と、各前記乗算器に個々に接続されるN個の加算器であって、対応する前記乗算器が出力する乗算結果を前記乗算結果に対応する前記第二の疑似雑音符号の位相ごとに累積加算する加算器と、前記加算器の加算結果のうち絶対値が最大である加算結果または所定閾値を超える加算結果に対応する前記第二の疑似雑音符号の位相を、前記第一の疑似雑音符号の位相として検出する検出器、として機能するようにプログラムし、各前記セレクタが、対応する前記乗算器に前記第一の疑似雑音符号の同一チップデータが供給されている間に、選択対象の前記第二の疑似雑音符号の全てが前記対応する乗算器に供給されるように、前記第二の疑似雑音符号を選択し、前記測定装置が前記第一の疑似雑音符号に同期できるようにすることを特徴とするものである。

10

#### 【0007】

さらに、本第三の発明は、本第一の発明または本第二の発明の装置において、各前記セレクタが、固定された順序およびタイミングで周期的に繰り返し前記第二の疑似雑音符号を選択し、各前記加算器が、対応する前記セレクタにおける前記第二の疑似雑音符号の選択周期と等しい時間遅延を有する第一の遅延器を用いて累積加算を行うことを特徴とするものである。

20

#### 【0008】

またさらに、本第四の発明は、本第一の発明乃至本第三の発明のいずれかの装置において、前記疑似雑音符号発生器が、前記第一の疑似雑音符号と同じ符号系列を有する単一の第三の疑似雑音符号を基に、複数の第二の遅延器を介して、前記第二の疑似雑音符号の全てを並列的に発生することを特徴とするものである。

30

#### 【0009】

また、本第五の発明は、本第四の発明の装置において、前記第三の疑似雑音符号が、前記ゲートアレイ内の記憶領域に予め格納された疑似雑音符号であることを特徴とするものである。

#### 【0010】

さらに、本第六の発明は、本第一の発明乃至本第五の発明のいずれかの装置において、前記Mおよび前記Nのそれぞれが、前記ゲートアレイのプログラム毎に異なる値を有することを特徴とするものである。

40

#### 【0011】

またさらに、本第七の発明は、再構成可能なゲートアレイを具備する測定装置であって、前記ゲートアレイが、被測定信号に含まれる第一の疑似雑音符号と同じ符号系列であって、それぞれ位相が異なるK個の第二の疑似雑音符号を発生する疑似雑音符号発生器と、前記K個のうち2以上のM個の前記第二の疑似雑音符号を選択対象とし、選択対象の前記第二の疑似雑音符号から1つを選択して出力する2以上のN個のセレクタであって、あるセレクタが選択対象とする前記第二の疑似雑音符号がその他のセレクタの選択対象外であるセレクタと、各前記セレクタに個々に接続されるN個の乗算器であって、対応する前記セレクタが出力する前記第二の疑似雑音符号と前記第一の疑似雑音符号とを乗ずる乗算器と、各前記乗算器に個々に接続されるN個の加算器であって、対応する前記乗算器が出力する乗算結果を前記乗算結果に対応する前記第二の疑似雑音符号の位相ごとに累積加算する加算器と、前記加算器の加算結果のうち絶対値が最大である加算結果または所定閾値を超える加算結果に対応する前記第二の疑似雑音符号の位相を、前記第一の疑似雑音符号の位相として検出する検出器、として機能するようにプログラムされ、各前記セレクタが、対応する前記乗算器に前記第一の疑似雑音符号の同一チップデータが供給されている間に、選択対象の前記第二の疑似雑音符号の全てが前記対応する乗算器に供給されるように、前記第二の疑似雑音符号を選択し、前記測定装置が前記第一の疑似雑音符号に同期できるようにしたことを特徴とするものである。

#### 【0012】

また、本第八の発明は、被測定信号を格納する記憶装置と、前記被測定信号のチップレ

50

ートよりも速いクロックで動作する再構成可能なゲートアレイとを備える測定装置であって、前記ゲートアレイが、前記被測定信号に含まれる第一の疑似雑音符号と同じ符号系列であって、それぞれ位相が異なるK個の第二の疑似雑音符号を発生する疑似雑音符号発生器と、前記K個のうち2以上のM個の前記第二の疑似雑音符号を選択対象とし、選択対象の前記第二の疑似雑音符号から1つを選択して出力する2以上のN個のセレクタであって、あるセレクタが選択対象とする前記第二の疑似雑音符号がその他のセレクタの選択対象外であるセレクタと、各前記セレクタに個々に接続されるN個の乗算器であって、対応する前記セレクタが出力する前記第二の疑似雑音符号と前記記憶装置から読み出される前記被測定信号に含まれる前記第一の疑似雑音符号とを乗ずる乗算器と、各前記乗算器に個々に接続されるN個の加算器であって、対応する前記乗算器が出力する乗算結果を前記乗算結果に対応する前記第二の疑似雑音符号の位相ごとに累積加算する加算器と、前記加算器の加算結果のうち絶対値が最大である加算結果または所定閾値を超える加算結果に対応する前記第二の疑似雑音符号の位相を、前記第一の疑似雑音符号の位相として検出する検出器、として機能するようにプログラムされ、各前記セレクタが、対応する前記乗算器に前記第一の疑似雑音符号の同一チップデータが供給されている間に、選択対象の前記第二の疑似雑音符号の全てが前記対応する乗算器に供給されるように、前記第二の疑似雑音符号を選択し、前記測定装置が前記第一の疑似雑音符号に同期できるようにしたことを特徴とするものである。

【0013】

さらに、本第九の発明は、本第七の発明または本第八の発明の装置において、各前記セレクタが、固定された順序およびタイミングで周期的に繰り返し前記第二の疑似雑音符号を選択し、各前記加算器が、対応する前記セレクタにおける前記第二の疑似雑音符号の選択周期と等しい時間遅延を有する第一の遅延器を用いて累積加算を行うことを特徴とするものである。

【0014】

またさらに、本第十の発明は、本第七の発明乃至本第九の発明のいずれかの装置において、前記疑似雑音符号発生器が、前記第一の疑似雑音符号と同じ符号系列を有する単一の第三の疑似雑音符号を基に、複数の第二の遅延器を介して、前記第二の疑似雑音符号の全てを並列的に発生することを特徴とするものである。

【0015】

また、本第十一の発明は、本第十の発明の装置において、前記第三の疑似雑音符号が、前記ゲートアレイ内の記憶領域に予め格納された疑似雑音符号であることを特徴とするものである。

【0016】

さらに、本第十二の発明は、本第七の発明乃至本第十一の発明のいずれかの装置において、前記Mおよび前記Nのそれぞれが、前記ゲートアレイのプログラム毎に異なる値を有しうることを特徴とするものである。

【0017】

またさらに、本第十三の発明は、再構成可能なゲートアレイを備える測定装置に具備されるか接続されるコンピュータに、被測定信号に含まれる第一の疑似雑音符号に前記測定装置が同期するように前記ゲートアレイをプログラムさせるプログラムであって、前記プログラムされたゲートアレイが、前記第一の疑似雑音符号と同じ符号系列であって、それぞれ位相が異なるK個の第二の疑似雑音符号を発生する疑似雑音符号発生器と、前記K個のうち2以上のM個の前記第二の疑似雑音符号を選択対象とし、選択対象の前記第二の疑似雑音符号から1つを選択して出力する2以上のN個のセレクタであって、あるセレクタが選択対象とする前記第二の疑似雑音符号がその他のセレクタの選択対象外であるセレクタと、各前記セレクタに個々に接続されるN個の乗算器であって、対応する前記セレクタが出力する前記第二の疑似雑音符号と前記第一の疑似雑音符号とを乗ずる乗算器と、各前記乗算器に個々に接続されるN個の加算器であって、対応する前記乗算器が出力する乗算結果を前記乗算結果に対応する前記第二の疑似雑音符号の位相ごとに累積加算する加算器

と、前記加算器の加算結果のうち絶対値が最大である加算結果または所定閾値を超える加算結果に対応する前記第二の疑似雑音符号の位相を、前記第一の疑似雑音符号の位相として検出する検出器、として機能し、各前記セレクタが、対応する前記乗算器に前記第一の疑似雑音符号の同一チップデータが供給されている間に、選択対象の前記第二の疑似雑音符号の全てが前記対応する乗算器に供給されるように、前記第二の疑似雑音符号を選択することを特徴とするものである。

#### 【0018】

また、本第十四の発明は、被測定信号を格納する記憶装置と、前記被測定信号のチップレートよりも速いクロックで動作する再構成可能なゲートアレイとを備える測定装置に具備されるか接続されるコンピュータに、前記被測定信号に含まれる第一の疑似雑音符号に前記測定装置が同期するように前記ゲートアレイをプログラムさせるプログラムであって、前記プログラムされたゲートアレイが、前記第一の疑似雑音符号と同じ符号系列であって、それぞれ位相が異なるK個の第二の疑似雑音符号を発生する疑似雑音符号発生器と、前記K個のうち2以上のM個の前記第二の疑似雑音符号を選択対象とし、選択対象の前記第二の疑似雑音符号から1つを選択して出力する2以上のN個のセレクタであって、あるセレクタが選択対象とする前記第二の疑似雑音符号がその他のセレクタの選択対象外であるセレクタと、各前記セレクタに個々に接続されるN個の乗算器であって、対応する前記セレクタが出力する前記第二の疑似雑音符号と前記記憶装置から読み出される前記被測定信号に含まれる前記第一の疑似雑音符号とを乗ずる乗算器と、各前記乗算器に個々に接続されるN個の加算器であって、対応する前記乗算器が出力する乗算結果を前記乗算結果に対応する前記第二の疑似雑音符号の位相ごとに累積加算する加算器と、前記加算器の加算結果のうち絶対値が最大である加算結果または所定閾値を超える加算結果に対応する前記第二の疑似雑音符号の位相を、前記第一の疑似雑音符号の位相として検出する検出器、として機能し、各前記セレクタが、対応する前記乗算器に前記第一の疑似雑音符号の同一チップデータが供給されている間に、選択対象の前記第二の疑似雑音符号の全てが前記対応する乗算器に供給されるように、前記第二の疑似雑音符号を選択することを特徴とするものである。

#### 【0019】

さらに、本第十五の発明は、本第十三の発明または本第十四の発明のプログラムにおいて、各前記セレクタが、固定された順序およびタイミングで周期的に繰り返し前記第二の疑似雑音符号を選択し、各前記加算器が、対応する前記セレクタにおける前記第二の疑似雑音符号の選択周期と等しい時間遅延を有する第一の遅延器を用いて累積加算を行うことを特徴とするものである。

#### 【0020】

またさらに、本第十六の発明は、本第十三の発明乃至本第十五の発明のいずれかのプログラムにおいて、前記疑似雑音符号発生器が、前記第一の疑似雑音符号と同じ符号系列を有する単一の第三の疑似雑音符号を基に、複数の第二の遅延器を介して、前記第二の疑似雑音符号の全てを並列的に発生することを特徴とするものである。

#### 【0021】

また、本第十七の発明は、本第十六の発明のプログラムにおいて、前記第三の疑似雑音符号が、前記ゲートアレイ内の記憶領域に予め格納された疑似雑音符号であることを特徴とするものである。

#### 【0022】

さらに、本第十八の発明は、本第十三の発明乃至本第十七の発明のいずれかのプログラムにおいて、前記Mおよび前記Nのそれぞれが、前記ゲートアレイのプログラム毎に異なる値を有しうることを特徴とするものである。

#### 【発明の効果】

#### 【0023】

本発明によれば、同期捕捉に必要な相関処理を時分割多重化し並列化するので、所望の仕様の同期捕捉装置をゲートアレイ内に実現するにあたり、ゲートアレイ・リソースの所

10

20

30

40

50

要数やゲートアレイの動作クロック周波数を従来に比べて柔軟に選択できる。例えば、使用予定のゲートアレイにおいてリソース消費を抑えるために、多重度を大きくし並列度を小さくすることができる。または、使用予定のゲートアレイにおいて、相関処理の高速化を図るために、並列度を大きくし多重度を小さくすることができる。あるいは、あらかじめ決められているゲートアレイの動作クロック周波数で最も効率的な速度で相関処理を行うように調整することができる。このような選択の柔軟性は、使用予定のゲートアレイを従来に比べて有効に利用することを可能にする。

#### 【0024】

また、本発明によれば、固定された順序およびタイミングでの疑似雑音符号の周期的切換と遅延器を用いた累積加算との組み合わせを採用しているので、時分割多重された相関処理において、各相関結果を得るために累積加算処理を簡易な回路構成で実施することができる。

#### 【0025】

さらに、本発明によれば、基礎となる疑似雑音符号を記憶手段に格納し、その疑似雑音符号と複数の遅延器のみとにより様々な位相の疑似雑音符号を生成するようしているので、それぞれ位相が異なる複数の疑似雑音符号を簡易な構成で生成することができる。また、ゲートアレイのロジック・リソースの消費を抑えることにも効果を奏する。ロジック・リソースとは、例えば、FPGAのロジックセルなどである。

#### 【発明を実施するための最良の形態】

#### 【0026】

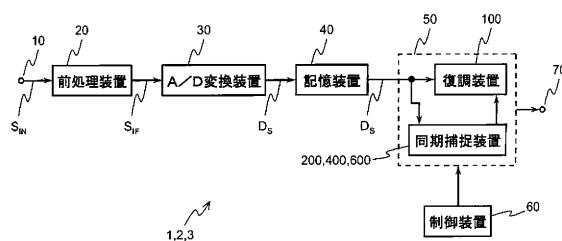

本発明の実施形態を添付の図面を参照しながら説明する。本発明の第一の実施形態は、被測定信号であるCDMA方式の信号を測定する測定装置1である。以下、図1を参照する。図1は、測定装置1の内部構成を示すブロック図である。まず、測定装置1の構成について説明する。測定装置1は、入力端子10と、前処理装置20と、アナログ・デジタル変換装置30と、記憶装置40と、ゲートアレイ50と、制御装置60と、出力端子70とを備える。本書では、アナログ・デジタル変換装置をA/D変換装置と略称する。

#### 【0027】

入力端子10は、被測定信号 $S_{IN}$ を受信するための端子である。被測定信号 $S_{IN}$ は、CDMA方式の信号であって、疑似雑音符号(PN符号)を含む信号である。被測定信号 $S_{IN}$ の例としては、IS-95方式の信号、W-CDMA方式の信号、またはCDMA2000方式の信号などがある。前処理装置20は、入力端子10で受信する信号 $S_{IN}$ に所定の信号処理を施す装置である。前処理装置20は、例えば、被測定信号 $S_{IN}$ に含まれる測定対象外の信号を除去したり、後続する装置が被測定信号 $S_{IN}$ を処理しやすくなるために被測定信号 $S_{IN}$ に周波数変換やレベル変換を施す。前処理装置20により処理された被測定信号 $S_{IN}$ は、前処理装置20から被測定信号 $S_{IF}$ として出力される。A/D変換装置30は、前処理装置20から出力される信号 $S_{IF}$ を所定の時間間隔で標本化し、標本化した信号をデジタル変換し、変換結果を出力する装置である。標本化速度は、被測定信号 $S_{IN}$ のチップレートに等しい。もちろん、チップレートの2倍以上の速度でオーバーサンプリングしても良い。なお、チップは、被測定信号 $S_{IN}$ に含まれる疑似雑音符号のビットである。また、チップレートとは、被測定信号 $S_{IN}$ に含まれる疑似雑音符号が変化する速度、すなわち、ビットレートである。A/D変換装置30によりデジタル変換された信号 $S_{IF}$ は、A/D変換装置30からデータ $D_s$ として出力される。記憶装置40は、A/D変換装置30の変換結果 $D_s$ を格納するための装置である。記憶装置40は、データ $D_s$ を遅滞なく格納できるアクセス能力を有する。記憶装置40には、例えば、DRAMやSRAMなどの半導体メモリが用いられる。ゲートアレイ50は、制御装置60からのデータの書き込みにより所定の処理回路が構成されるゲートアレイであって、FPGAなどのように再構成が可能なゲートアレイである。処理回路の例としては、同期捕捉装置や復調装置やBER測定装置などがある。ゲートアレイ50は、記憶装置40に格納されたデータ $D_s$ を処理する。記憶装置40に格納されたデータ $D_s$ は、ゲートアレイ50自身が記憶装

置 4 0 から読み出しても良いし、ゲートアレイ 5 0 のために制御装置 6 0 が記憶装置 4 0 から読み出しても良い。ここで、記憶装置 5 0 は、ある一定量のデータをためてからゲートアレイ 5 0 に蓄積したデータを送るようにしてもいいし、または、A / D 変換装置 3 0 の出力レートとゲートアレイ 5 0 との処理速度の差を吸収するようなバッファとして用いてもよい。一定量のデータとは、例えば、 $n$  フレーム分のデータである。一定量のデータは、拡散符号の周期が 3 8 4 0 0 チップである W - C D M A の場合、 $n \times 3 8 4 0 0$  チップ分である。なお、 $n$  は、自然数である。A / D 変換装置 3 0 の出力データ速度とゲートアレイ 5 0 の動作周波数が異なる場合が多いので、記憶装置 4 0 を用いることは、測定装置の設計の柔軟性向上に貢献する。制御装置 6 0 は、いわゆるコンピュータであって、プログラムを実行することにより所定の演算または処理を行う装置である。制御装置 6 0 は、上記のデータアクセスの他に、例えば、同一測定装置内の他の装置の制御を行う。なお、制御装置 6 0 は、コンピュータに相当する機能を有するデバイスであれば良いので、周辺機器やディスプレイなどを含んだコンピュータシステムに限らず、C P U やD S P などのプロセッサ、または、コンピュータボードなどであっても良い。出力端子 7 0 は、ゲートアレイ 5 0 の処理結果が出力される端子である。

10

20

30

## 【 0 0 2 8 】

ゲートアレイ 5 0 は、復調装置 1 0 0 と、同期捕捉装置 2 0 0 とを含む。復調装置 1 0 0 および同期捕捉装置 2 0 0 は、制御装置 6 0 がゲートアレイ 5 0 をプログラムすることにより、ゲートアレイ 5 0 内に構成されたものである。制御装置 6 0 によるゲートアレイ 5 0 へのプログラミングは、制御装置 6 0 によるゲートアレイ 5 0 への直接的なデータの書き込み、または、ゲートアレイ 5 0 に外部接続された図示しないメモリへの制御装置 6 0 によるデータの書き込みにより、行われる。また、制御装置 6 0 によるゲートアレイ 5 0 へのプログラミングは、制御装置 6 0 自身の動作を指示するプログラムを制御装置 6 0 が実行することにより、実施される。制御装置 6 0 自身の動作を指示するプログラムは、制御装置 6 0 内に固定的に備えられた記憶媒体、または、制御装置 6 0 に着脱可能な記憶媒体、または、制御装置 6 0 に有線接続あるいは無線接続された外部記憶媒体などに格納されている。これらの記憶媒体の例としては、制御装置 6 0 内のハードディスクドライブや半導体メモリ、または、制御装置 6 0 に着脱可能な半導体メモリデバイスやC D R O M やフレキシブルディスク、または、制御装置 6 0 にU S B やネットワークなどの伝送媒体を介して接続されたハードディスクドライブやダウンロード用サーバーなどがある。さて、同期捕捉装置 2 0 0 は、被測定信号  $S_{IN}$  に含まれる疑似雑音符号の位相を検出する装置である。復調装置 1 0 0 は、同期捕捉装置 2 0 0 が検出した位相に基づき、被測定信号  $S_{IN}$  ( 実際にはデータ  $D_s$  ) を復調する装置である。

30

40

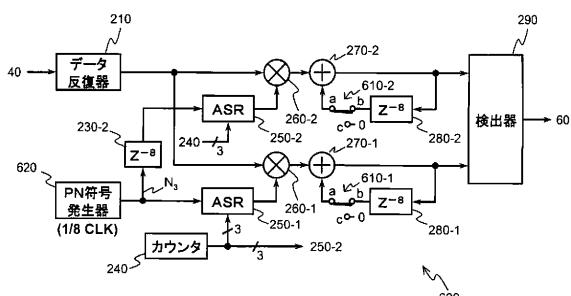

## 【 0 0 2 9 】

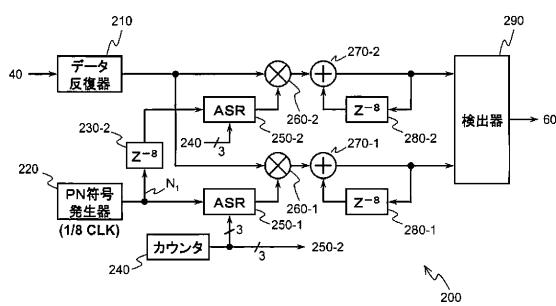

ここで、図 2 を参照する。図 2 は、同期捕捉装置 2 0 0 の内部構成を示すブロック図である。同期捕捉装置 2 0 0 は、データ反復器 2 1 0 と、P N 符号発生器 2 2 0 と、遅延器 2 3 0 - 2 と、カウンタ 2 4 0 と、A S R 2 5 0 - 1 と、A S R 2 5 0 - 2 と、乗算器 2 6 0 - 1 と、乗算器 2 6 0 - 2 と、加算器 2 7 0 - 1 と、加算器 2 7 0 - 2 と、遅延器 2 8 0 - 1 と、遅延器 2 8 0 - 2 と、検出器 2 9 0 とを備える。

50

## 【 0 0 3 0 】

データ反復器 2 1 0 は、ゲートアレイ 5 0 内に供給されているクロック信号 C L K またはクロック信号 C L K を分周した信号に応じて動作し、記憶装置 4 0 から読み出されたデータ  $D_s$  を、クロック信号 C L K の 1 周期  $T_c$  の 8 倍の時間、出力し続ける装置である。なお、クロック信号 C L K の速度は、被測定信号  $S_{IN}$  のチップレートよりも高く、例えば、数 1 0 0 M H z などである。一般に、クロック信号 C L K の最高速度は、ゲートアレイ 5 0 等のハードウェア部品の最大動作クロック周波数によって決まる。P N 符号発生器 2 2 0 は、 $8 T_c$  每に 1 ビットずつ疑似雑音符号  $N_1$  を発生する装置である。疑似雑音符号  $N_1$  は、M 系列やゴールド符号など、各通信方式に必要とされる疑似雑音符号である。P N 符号発生器 2 2 0 が発生する疑似雑音符号  $N_1$  は、被測定信号  $S_{IN}$  に含まれる疑似雑音符号の 1 周期分の全部もしくは一部を繰り返し発生する。全相關の場合に当該 1 周期分の全部

50

が発生され、部分相関の場合に当該 1 周期分の一部が発生される。本実施形態では、説明を簡便にするために、相関長 16 ビットの全相関を行うものとし、被測定信号  $S_{IN}$  に含まれる疑似雑音符号の符号長が 16 ビットであり、PN 符号発生器 220 が 16 ビット長の疑似雑音符号を繰り返し発生するものとする。遅延器 230-2、遅延器 280-1、および、遅延器 280-2 は、入力信号または入力データに  $8 T_c$  の時間遅延を附加して出力する素子である。遅延器 230-2、遅延器 280-1、および、遅延器 280-2 は、例え、シフトレジスタまたは FIFO 形のメモリまたは所定長の伝送線路などである。カウンタ 240 は、3 ビット幅の 2 進アップカウンタであり、0 から 7 までの数を順に出力する。カウンタ 240 は、クロック信号 CLK に応答してクロック信号 CLK の 1 周期間隔で計数する。カウンタ 240 の計数結果は、アドレス情報として、ASR250-1 および ASR250-2 のそれぞれに与えられる。ASR250-1 および ASR250-2 のそれぞれは、アドレス可能なシフトレジスタである。なお、ASR は、Addressable Shift Register の略称である。

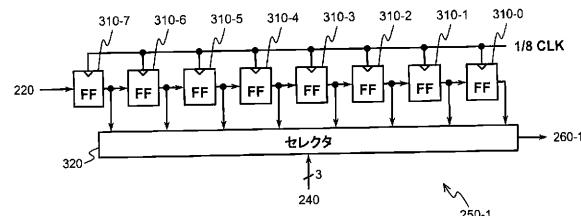

### 【0031】

ここで、図 3 を参照する。図 3 は、ASR250-1 の内部構成を示すブロック図である。ASR250-1 は、8 個のフリップフロップ 310-0~7 と、セレクタ 320 を備える。8 個のフリップフロップ 310-0~7 は、シフトレジスタを構成する。フリップフロップ 310-7 は、クロック信号 CLK を 8 分周した信号に応答して、PN 符号発生器 220 の出力データを取り込み、取り込んだデータを出力する。フリップフロップ 310-0~6 のそれぞれは、クロック信号 CLK を 8 分周した信号に応答して、前段のフリップフロップの出力データを取り込み、取り込んだデータを出力する。セレクタ 320 は、カウンタ 240 から 3 ビット幅のアドレス情報を受信する。セレクタ 320 は、カウンタ 240 からのアドレス情報に基づいて、フリップフロップ 310-0~7 の出力データのいずれか 1 つを選択し、選択したデータを出力する。カウンタ 240 からのアドレス情報（アドレス値）は、選択されるフリップフロップに付された参照番号の枝番号に対応する。例えば、カウンタ 240 からのアドレス情報が 1 である時は、フリップフロップ 310-1 が選択される。以上のように、固定された順序およびタイミングで周期的に繰り返し疑似雑音符号が選択される。選択されたデータは、ASR250-1 の出力として、乗算器 260-1 へ供給される。

### 【0032】

ここで、図 2 を参照する。ASR250-2 は、ASR250-1 と同一構成および同一機能を有するので、詳細な説明は省略する。乗算器 260-1 は、ASR250-1 の出力データとデータ反復器 210 の出力データとを乗じ、乗算結果を出力する装置である。乗算器 260-2 は、ASR250-2 の出力データとデータ反復器 210 の出力データとを乗じ、乗算結果を出力する装置である。加算器 270-1 は、乗算器 260-1 の出力データと遅延器 280-1 の出力データとを加算し、加算結果を出力する装置である。加算器 270-2 は、乗算器 260-2 の出力データと遅延器 280-2 の出力データとを加算し、加算結果を出力する装置である。加算器 270-1 と遅延器 280-1 は、累積加算器を構成している。また、加算器 270-2 と遅延器 280-2 は、累積加算器を構成している。検出器 290 は、加算器 270-1 および加算器 270-2 の出力データを参照して、被測定信号  $S_{IN}$  に含まれる疑似雑音符号の位相を検出する装置である。

### 【0033】

次に、測定装置 1 の全体動作について説明する。ここで、図 1 を参照する。被測定信号  $S_{IN}$  は、前処理装置 20 により処理された後、A/D 変換装置 30 によりデジタル変換され、記憶装置 40 に格納される。同期捕捉装置 200 は、記憶装置 40 に格納されたデータ  $D_s$  に基づき、被測定信号  $S_{IN}$  に含まれる疑似雑音符号の位相を検出する。最後に、復調装置 100 は、同期捕捉装置 200 が検出した位相に基づき、被測定信号  $S_{IN}$ （実際にはデータ  $D_s$ ）を復調する。

### 【0034】

次に、同期捕捉装置 200 の動作について説明する。ここで、図 2 と図 4 を参照する。

10

20

30

40

50

図4は、データ反復器210の出力データおよびASR250-1の出力データおよびASR250-2の出力データを示すタイミングチャートである。図4において、横軸は時間である。また、図4における縦破線は、クロック信号CLKの周期間隔で並んでいる。下付数字を有するアルファベット記号「S」は、タイムスロットを表している。タイムスロットの時間間隔は、 $T_c$ である。下付数字を有するアルファベット記号「X」は、データ反復器210の出力データを表している。データ反復器210の出力データは、 $8T_c$ 毎に新たなビットデータが出力される。下付数字を有するアルファベット記号「C」は、疑似雑音符号 $N_1$ の各ビットデータを示している。アルファベット記号「C」の下付数字は、PN符号発生器220から出力されるビットデータの順番を表している。すなわち、 $C_0, C_1, C_2, \dots$ の順に出力される。なお、疑似雑音符号 $N_1$ は繰り返し発生されるので、 $C_{15}$ の次は $C_0$ が出力される。さて、ASR260-1およびASR260-2は、位相が異なる8種類の疑似雑音符号を時分割多重して出力する。ASR260-1から出力される8種の疑似雑音符号は、ASR260-2から出力される8種の疑似雑音符号と位相が異なる。言うまでもないが、この場合の位相とは、疑似雑音符号 $N_1$ の位相である。乗算器260-1および乗算器260-2では、順次、乗算処理が行われる。そして、加算器270-1は、乗算器260-1の乗算結果に、 $8T_c$ 前の加算器270-1の出力データを加算して、加算結果を出力する。すなわち、加算器270-1は、タイムスロットごとに、乗算器260-1の乗算結果を累積加算する。一方、加算器270-2は、乗算器260-2の乗算結果に、 $8T_c$ 前の加算器270-2の出力データを加算して、加算結果を出力する。すなわち、加算器270-2は、タイムスロットごとに、乗算器260-2の乗算結果を累積加算する。

#### 【0035】

上記の演算を開始してから一定時間経過後、疑似雑音符号 $N_1$ の全16ビットについての乗算結果の累積加算結果が、疑似雑音符号 $N_1$ の位相ごとに、加算器270-1および加算器270-2のそれぞれから出力される。例えば、加算器270-1から、 $X_0 \cdot C_0 + X_1 \cdot C_1 + X_2 \cdot C_2 + X_3 \cdot C_3 + X_4 \cdot C_4 + X_5 \cdot C_5 + X_6 \cdot C_6 + X_7 \cdot C_7 + X_8 \cdot C_8 + X_9 \cdot C_9 + X_{10} \cdot C_{10} + X_{11} \cdot C_{11} + X_{12} \cdot C_{12} + X_{13} \cdot C_{13} + X_{14} \cdot C_{14} + X_{15} \cdot C_{15}$ の結果 $Y_0$ が出力される。なお、 $Y_0$ は、疑似雑音符号 $N_1$ の先頭チップの位相を最初の入力データ $X_0$ と一致させた時の演算結果である。また、疑似雑音符号 $N_1$ の先頭チップの位相を最初の入力データ $X_0$ に対してnチップ分シフトした時の乗算結果の累積加算結果を $Y_n$ とする。さて、演算結果 $Y_0$ の出力開始から $9T_c$ 後、 $X_1 \cdot C_0 + X_2 \cdot C_1 + X_3 \cdot C_2 + X_4 \cdot C_3 + X_5 \cdot C_4 + X_6 \cdot C_5 + X_7 \cdot C_6 + X_8 \cdot C_7 + X_9 \cdot C_8 + X_{10} \cdot C_9 + X_{11} \cdot C_{10} + X_{12} \cdot C_{11} + X_{13} \cdot C_{12} + X_{14} \cdot C_{13} + X_{15} \cdot C_{14} + X_{16} \cdot C_{15}$ の結果、すなわち、演算結果 $Y_1$ が出力される。このように演算結果 $Y_1 \sim Y_7$ が、 $9T_c$ 毎に順次、加算器270-1から出力される。演算結果 $Y_7$ が出力された後に続けて、加算器270-2からは、 $X_8 \cdot C_0 + X_9 \cdot C_1 + X_{10} \cdot C_2 + X_{11} \cdot C_3 + X_{12} \cdot C_4 + X_{13} \cdot C_5 + X_{14} \cdot C_6 + X_{15} \cdot C_7 + X_{16} \cdot C_8 + X_{17} \cdot C_9 + X_{18} \cdot C_{10} + X_{19} \cdot C_{11} + X_{20} \cdot C_{12} + X_{21} \cdot C_{13} + X_{22} \cdot C_{14} + X_{23} \cdot C_{15}$ の結果 $Y_8$ が出力される。上記と同様に、演算結果 $Y_8 \sim Y_{15}$ が、 $9T_c$ 毎に順次、加算器270-2から出力される。ちなみに、 $Y_{15} = X_{15} \cdot C_0 + X_{16} \cdot C_1 + X_{17} \cdot C_2 + X_{18} \cdot C_3 + X_{19} \cdot C_4 + X_{20} \cdot C_5 + X_{21} \cdot C_6 + X_{22} \cdot C_7 + X_{23} \cdot C_8 + X_{24} \cdot C_9 + X_{25} \cdot C_{10} + X_{26} \cdot C_{11} + X_{27} \cdot C_{12} + X_{28} \cdot C_{13} + X_{29} \cdot C_{14} + X_{30} \cdot C_{15}$ である。

#### 【0036】

疑似雑音符号 $N_1$ の全16ビットについての乗算結果を累積加算した結果は、被測定信号 $S_{IN}$ (実際にはデータ $D_S$ )と疑似雑音符号 $N_1$ との相關値として利用することができる。そして最終的には、疑似雑音符号 $N_1$ の位相ごとの相關値として、全部で16個の累積加算結果 $Y_0 \sim Y_{15}$ が得られる。本実施形態では、関連する疑似雑音符号 $N_1$ の位相がそれぞれ異なる16種類の相關演算を、並列化しかつ時間的に多重化して処理している(並列度2、時分割多重度8)。ここで、本方式を従来のスライディング相関器と比較してみると、回路規模は並列化により2倍になるが、処理速度はクロック信号CLKが入力データ

レートと同じであると仮定した場合 1 / 2 に短縮されている。また、本方式を従来のマッチトフィルタと比較してみると、回路規模は多重化により 1 / 8 になり、処理速度はクロック信号 C L K が入力データレートと同じであると仮定した場合 8 倍になる。なお、本実施形態のように、クロック信号 C L K を入力データレートよりも高速にすれば、従来の方法より同等あるいはそれ以上に高速に上記処理を行うことができる。

### 【 0 0 3 7 】

検出器 290 は、加算器 270 - 1 および加算器 270 - 2 から出力される上記 16 個の累積加算結果のうち絶対値が最大のものを検出する。検出された累積加算結果に関連する疑似雑音符号  $N_1$  の位相が、復調装置 100 へ出力される。そして、復調装置 100 は、同期捕捉装置 200 が出力した位相情報に基づき、被測定信号  $S_{IN}$  ( 実際にはデータ  $D_s$  ) を復調する。

### 【 0 0 3 8 】

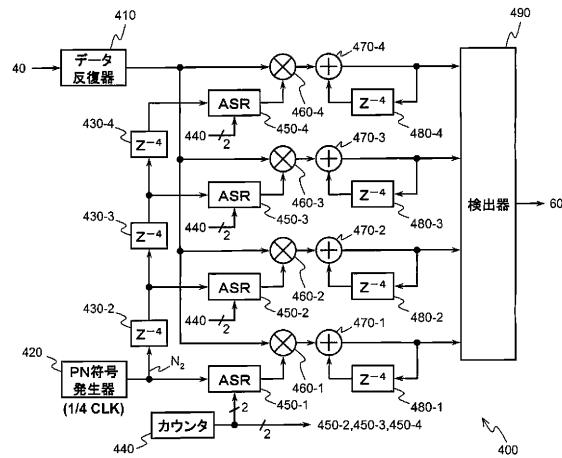

次に、本発明の第二の実施形態について説明する。本発明の第二の実施形態は、被測定信号である CDMA 方式の信号を測定する測定装置 2 である。ここで、図 1 を参照する。測定装置 2 は、測定装置 1 において同期捕捉装置 200 が同期捕捉装置 400 に置き換わったものである。すなわち、構成要素の点から見れば、測定装置 1 と測定装置 2 とに相違はない。制御装置 60 によりゲートアレイ 50 内で実現される装置が異なるのみである。従って、測定装置 2 の構成要素のうち、測定装置 1 と共通する要素については、説明を省略する。

### 【 0 0 3 9 】

同期捕捉装置 400 は、制御装置 60 がゲートアレイ 50 をプログラムすることにより、ゲートアレイ 50 内に構成されたものである。同期捕捉装置 400 は、被測定信号  $S_{IN}$  に含まれる疑似雑音符号の位相を検出する装置である。復調装置 100 は、同期捕捉装置 400 が検出した位相に基づき、被測定信号  $S_{IN}$  ( 実際にはデータ  $D_s$  ) を復調する装置である。

### 【 0 0 4 0 】

ここで、図 5 を参照する。図 5 は、同期捕捉装置 400 の内部構成を示すブロック図である。同期捕捉装置 400 は、データ反復器 410 と、PN 符号発生器 420 と、遅延器 430 - 2 と、遅延器 430 - 3 と、遅延器 430 - 4 と、カウンタ 440 と、ASR 450 - 1 と、ASR 450 - 2 と、ASR 450 - 3 と、ASR 450 - 4 と、乗算器 460 - 1 と、乗算器 460 - 2 と、乗算器 460 - 3 と、乗算器 460 - 4 と、加算器 470 - 1 と、加算器 470 - 2 と、加算器 470 - 3 と、加算器 470 - 4 と、遅延器 480 - 1 と、遅延器 480 - 2 と、遅延器 480 - 3 と、遅延器 480 - 4 と、検出器 490 とを備える。

### 【 0 0 4 1 】

データ反復器 410 は、ゲートアレイ 50 内に供給されているクロック信号 C L K またはクロック信号 C L K を分周した信号に応じて動作し、記憶装置 40 から読み出されたデータ  $D_s$  を、クロック信号 C L K の 1 周期  $T_c$  の 4 倍の時間、出力し続ける装置である。なお、クロック信号 C L K の速度は、被測定信号  $S_{IN}$  のチップレートよりも高く、例えば、数 100 MHz などである。一般に、クロック信号 C L K の最高速度は、ゲートアレイ 50 などのハードウェア部品の最大動作クロック周波数によって決まる。PN 符号発生器 420 は、 $4 T_c$  毎に 1 ビットずつ疑似雑音符号  $N_2$  を発生する装置である。疑似雑音符号  $N_2$  は、M 系列やゴールド符号など、各通信方式に必要とされる疑似雑音符号である。PN 符号発生器 420 が発生する疑似雑音符号  $N_2$  は、被測定信号  $S_{IN}$  に含まれる疑似雑音符号の 1 周期分の全部もしくは一部を繰り返し発生する。全相關の場合に当該 1 周期分の全部が発生され、部分相關の場合に当該 1 周期分の一部が発生される。本実施形態では、説明を簡便にするために、相關長 16 ビットの全相關を行うものとし、被測定信号  $S_{IN}$  に含まれる疑似雑音符号の符号長が 16 ビットであり、PN 符号発生器 420 が 16 ビット長の疑似雑音符号を繰り返し発生するものとする。遅延器 430 - 2 ~ 4 および遅延器 480 - 1 ~ 4 は、入力信号または入力データに  $4 T_c$  の時間遅延を付加して出力する素子で

10

20

30

40

50

ある。遅延器 430 - 2 ~ 4 および遅延器 480 - 1 ~ 4 は、例えば、シフトレジスタまたは FIFO 形のメモリまたは所定長の伝送線路などである。カウンタ 440 は、2 ビット幅の 2 進アップカウンタであり、0 から 3 までの数を順に出力する。カウンタ 440 は、クロック信号 CLK に応答してクロック信号 CLK の 1 周期間隔で計数する。カウンタ 440 の計数結果は、アドレス情報として、ASR450 - 1 ~ 4 のそれぞれに与えられる。ASR450 - 1 ~ 4 は、アドレス可能なシフトレジスタである。

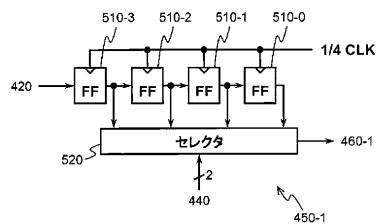

#### 【0042】

ここで、図 6 を参照する。図 6 は、ASR450 - 1 の内部構成を示すブロック図である。ASR450 - 1 は、4 個のフリップフロップ 510 - 0 ~ 3 と、セレクタ 520 を備える。4 個のフリップフロップ 510 - 0 ~ 3 は、シフトレジスタを構成する。フリップフロップ 510 - 3 は、クロック信号 CLK を 4 分周した信号に応答して、PN 符号発生器 420 の出力データを取り込み、取り込んだデータを出力する。フリップフロップ 510 - 0 ~ 2 のそれぞれは、クロック信号 CLK を 4 分周した信号に応答して、前段のフリップフロップの出力データを取り込み、取り込んだデータを出力する。セレクタ 520 は、カウンタ 440 から 2 ビット幅のアドレス情報を受信する。セレクタ 520 は、カウンタ 440 からのアドレス情報に基づいて、フリップフロップ 510 - 0 ~ 3 の出力データのいずれか 1 つを選択し、選択したデータを出力する。選択されたデータは、ASR450 - 1 の出力として、乗算器 460 - 1 へ供給される。なお、カウンタ 440 からのアドレス情報（アドレス値）は、選択されるフリップフロップに付された参照番号の枝番号に対応する。例えば、カウンタ 440 からのアドレス情報が 1 である時は、フリップフロップ 510 - 1 が選択される。10

#### 【0043】

ここで、図 5 を参照する。ASR450 - 2 ~ 4 のそれぞれは、ASR450 - 1 と同一構成および同一機能を有するので、詳細な説明は省略する。乗算器 460 - 1 は、ASR450 - 1 の出力データとデータ反復器 410 の出力データとを乗じ、乗算結果を出力する装置である。乗算器 460 - 2 は、ASR450 - 2 の出力データとデータ反復器 410 の出力データとを乗じ、乗算結果を出力する装置である。乗算器 460 - 3 は、ASR450 - 3 の出力データとデータ反復器 410 の出力データとを乗じ、乗算結果を出力する装置である。乗算器 460 - 4 は、ASR450 - 4 の出力データとデータ反復器 410 の出力データとを乗じ、乗算結果を出力する装置である。加算器 470 - 1 は、乗算器 460 - 1 の出力データと遅延器 480 - 1 の出力データとを加算し、加算結果を出力する装置である。加算器 470 - 2 は、乗算器 460 - 2 の出力データと遅延器 480 - 2 の出力データとを加算し、加算結果を出力する装置である。加算器 470 - 3 は、乗算器 460 - 3 の出力データと遅延器 480 - 3 の出力データとを加算し、加算結果を出力する装置である。加算器 470 - 4 は、乗算器 460 - 4 の出力データと遅延器 480 - 4 の出力データとを加算し、加算結果を出力する装置である。加算器 470 - 1 と遅延器 480 - 1 は、累積加算器を構成している。また、加算器 470 - 2 と遅延器 480 - 2 は、累積加算器を構成している。加算器 470 - 3 と遅延器 480 - 3 は、累積加算器を構成している。加算器 470 - 4 と遅延器 480 - 4 は、累積加算器を構成している。検出器 490 は、加算器 470 - 1 ~ 4 のそれぞれの出力データを参照して、被測定信号 S<sub>IN</sub> に含まれる疑似雑音符号の位相を検出する装置である。20

#### 【0044】

次に、測定装置 2 の全体動作について説明する。ここで、図 1 を参照する。被測定信号 S<sub>IN</sub> は、前処理装置 20 により処理された後、A/D 変換装置 30 によりデジタル変換され、記憶装置 40 に格納される。同期捕捉装置 400 は、記憶装置 40 に格納されたデータ D<sub>S</sub> に基づき、被測定信号 S<sub>IN</sub> の疑似雑音符号の位相を検出する。最後に、復調装置 100 は、同期捕捉装置 400 が検出した位相に基づき、被測定信号 S<sub>IN</sub>（実際にはデータ D<sub>S</sub>）を復調する。30

#### 【0045】

次に、同期捕捉装置 400 の動作について説明する。ここで、図 5 と図 7 を参照する。40

図7は、データ反復器410の出力データおよびASR450-1~4のそれぞれの出力データを示すタイミングチャートである。図7において、横軸は時間である。また、図7における縦破線は、クロック信号CLKの周期間隔で並んでいる。下付数字を有するアルファベット記号「S」は、タイムスロットを表している。タイムスロットの時間間隔は、 $T_c$ である。下付数字を有するアルファベット記号「X」は、データ反復器410の出力データを表している。データ反復器410の出力データは、 $4T_c$ 毎に新たなビットデータが出力される。下付数字を有するアルファベット記号「C」は、疑似雑音符号 $N_2$ の各ビットデータを示している。アルファベット記号「C」の下付数字は、PN符号発生器420から出力されるビットデータの順番を表している。すなわち、 $C_0, C_1, C_2 \dots$ の順に出力される。なお、疑似雑音符号 $N_2$ は繰り返し発生されるので、 $C_{15}$ の次は $C_0$ が出力される。さて、ASR460-1~4のそれぞれは、位相が異なる4種類の疑似雑音符号を時分割多重して出力する。あるASRから出力される4種の疑似雑音符号は、他の3つのASRから出力される4種の疑似雑音符号と位相が異なる。この場合の位相とは、疑似雑音符号 $N_2$ の位相である。乗算器460-1~4のそれぞれにおいて、順次、乗算処理が行われる。そして、加算器470-1は、乗算器460-1の乗算結果に、 $4T_c$ 前の加算器470-1の出力データを加算して、加算結果を出力する。すなわち、加算器470-1は、タイムスロットごとに、乗算器460-1の乗算結果を累積加算する。加算器470-2は、乗算器460-2の乗算結果に、 $4T_c$ 前の加算器470-2の出力データを加算して、加算結果を出力する。すなわち、加算器470-2は、タイムスロットごとに、乗算器460-2の乗算結果を累積加算する。加算器470-3は、乗算器460-3の乗算結果に、 $4T_c$ 前の加算器470-3の出力データを加算して、加算結果を出力する。すなわち、加算器470-3は、タイムスロットごとに、乗算器460-3の乗算結果を累積加算する。加算器470-4は、乗算器460-4の乗算結果に、 $4T_c$ 前の加算器470-4の出力データを加算して、加算結果を出力する。すなわち、加算器470-4は、タイムスロットごとに、乗算器460-4の乗算結果を累積加算する。

## 【0046】

上記の演算を開始してから一定時間経過後、疑似雑音符号 $N_2$ の全16ビットについての乗算結果の累積加算結果が、疑似雑音符号 $N_2$ の位相ごとに、加算器470-1~4のそれぞれから順次出力される。例えば、加算器470-1から、 $X_0 \cdot C_0 + X_1 \cdot C_1 + X_2 \cdot C_2 + X_3 \cdot C_3 + X_4 \cdot C_4 + X_5 \cdot C_5 + X_6 \cdot C_6 + X_7 \cdot C_7 + X_8 \cdot C_8 + X_9 \cdot C_9 + X_{10} \cdot C_{10} + X_{11} \cdot C_{11} + X_{12} \cdot C_{12} + X_{13} \cdot C_{13} + X_{14} \cdot C_{14} + X_{15} \cdot C_{15}$ の結果 $Y_0$ が出力される。なお、 $Y_0$ は、疑似雑音符号 $N_1$ の先頭チップの位相を最初の入力データ $X_0$ と一致させた時の演算結果である。また、疑似雑音符号 $N_1$ の先頭チップの位相を最初の入力データ $X_0$ に対してnチップ分シフトした時の乗算結果の累積加算結果を $Y_n$ とする。さて、演算結果 $Y_0$ の出力開始から $5T_c$ 後に、 $X_1 \cdot C_0 + X_2 \cdot C_1 + X_3 \cdot C_2 + X_4 \cdot C_3 + X_5 \cdot C_4 + X_6 \cdot C_5 + X_7 \cdot C_6 + X_8 \cdot C_7 + X_9 \cdot C_8 + X_{10} \cdot C_9 + X_{11} \cdot C_{10} + X_{12} \cdot C_{11} + X_{13} \cdot C_{12} + X_{14} \cdot C_{13} + X_{15} \cdot C_{14} + X_{16} \cdot C_{15}$ の結果、すなわち、演算結果 $Y_1$ が出力される。演算結果 $Y_0 \sim Y_3$ は、 $5T_c$ 毎に順次、加算器470-1から出力される。 $Y_3$ が出力された後に続けて、加算器470-2からは、 $X_4 \cdot C_0 + X_5 \cdot C_1 + X_6 \cdot C_2 + X_7 \cdot C_3 + X_8 \cdot C_4 + X_9 \cdot C_5 + X_{10} \cdot C_6 + X_{11} \cdot C_7 + X_{12} \cdot C_8 + X_{13} \cdot C_9 + X_{14} \cdot C_{10} + X_{15} \cdot C_{11} + X_{16} \cdot C_{12} + X_{17} \cdot C_{13} + X_{18} \cdot C_{14} + X_{19} \cdot C_{15}$ の結果 $Y_4$ が出力される。上記同様に、演算結果 $Y_4 \sim Y_7$ は、 $5T_c$ 毎に順次、加算器470-2から出力される。 $Y_7$ が出力された後に続けて、加算器470-3からは、 $5T_c$ 毎に、演算結果 $Y_8 \sim Y_{11}$ が順次出力される。 $Y_{11}$ が出力された後に続けて、加算器470-4からは、 $5T_c$ 毎に演算結果 $Y_{12} \sim Y_{15}$ が順次出力される。

## 【0047】

疑似雑音符号 $N_2$ の全16ビットについての乗算結果を累積加算した結果は、被測定信号 $S_{IN}$ (実際にはデータ $D_S$ )と疑似雑音符号 $N_2$ との相關値として利用することができる。そして最終的には、疑似雑音符号 $N_1$ の位相ごとの相關値として、全部で16個の累積加算結果 $Y_0 \sim Y_{15}$ が得られる。本実施形態では、関連する疑似雑音符号 $N_1$ の位相がそれ

10

20

30

40

50

それ異なる 16 種類の相関演算を、並列化しつつ時間的に多重化して処理している（並列度 4、時分割多重度 4）。ここで、本方式を従来のスライディング相関器と比較してみると、回路規模は並列化により 4 倍になるが、処理速度はクロック信号 C L K が入力データレートと同じであると仮定した場合 1 / 4 に短縮されている。また、本方式を従来のマッチトフィルタと比較してみると、回路規模は多重化により 1 / 4 になり、処理速度はクロック信号 C L K が入力データレートと同じであると仮定した場合 4 倍になる。なお、本実施形態のように、クロック信号 C L K を入力データレートよりも高速にすれば、従来の方法より同等あるいはそれ以上に高速に上記処理を行うことができる。

#### 【0048】

検出器 490 は、加算器 470-1 ~ 4 のそれぞれから出力される上記 16 個の累積加算結果のうち絶対値が最大のものを検出する。検出された累積加算結果に関連する疑似雑音符号  $N_2$  の位相が、復調装置 100 へ出力される。そして、復調装置 100 は、同期捕捉装置 400 が出力した位相情報に基づき、被測定信号  $S_{IN}$  を復調する。

#### 【0049】

ところで、上記の各実施形態は、いずれも全相関が採用されている。本発明は、同期捕捉のために、全相関のみならず部分相関も採用しうる。そこで、部分相関による同期捕捉を行う、本発明の第三の実施形態について以下に説明する。

#### 【0050】

本発明の第三の実施形態は、被測定信号である C D M A 方式の信号を測定する測定装置 3 である。ここで、図 1 を参照する。測定装置 3 は、測定装置 1 において同期捕捉装置 200 が同期捕捉装置 600 に置き換わったものである。すなわち、構成要素の点から見れば、測定装置 1 と測定装置 2 とに相違はない。制御装置 60 によりゲートアレイ 50 内で実現される装置が異なるのみである。従って、測定装置 3 の構成要素のうち、測定装置 1 と共に通する要素については、説明を省略する。

#### 【0051】

同期捕捉装置 600 は、制御装置 60 がゲートアレイ 50 をプログラムすることにより、ゲートアレイ 50 内に構成されたものである。同期捕捉装置 600 は、被測定信号  $S_{IN}$  に含まれる疑似雑音符号の位相を検出する装置である。復調装置 100 は、同期捕捉装置 600 が検出した位相に基づき、被測定信号  $S_{IN}$ （実際にはデータ  $D_s$ ）を復調する装置である。

#### 【0052】

ここで、図 8 を参照する。図 8 は、同期捕捉装置 600 の内部構成を示すブロック図である。同期捕捉装置 600 は、同期捕捉装置 200 の構成要素に加えて、加算器 270-1 と遅延器 280-1 との間にスイッチ 610-1 を、加算器 270-2 と遅延器 280-2 との間にスイッチ 610-2 を備える。スイッチ 610-1 およびスイッチ 610-2 は、单極双投形（S P D T 形）のスイッチである。また、同期捕捉装置 600 は、P N 符号発生器 220 の代わりに P N 符号発生器 620 を備える。さらに、図 8 において、図 2 と同じ構成要素については、同一の参照符号を付して詳細な説明を省略する。

#### 【0053】

スイッチ 610-1 およびスイッチ 610-2 において、端子 a が共通端子である。スイッチ 610-1 の端子 a は、加算器 270-1 に接続されている。スイッチ 610-1 の端子 b は、遅延器 280-1 に接続され、遅延器 280-1 の出力データが供給される。スイッチ 610-1 の端子 c は、ゼロが供給されている。スイッチ 610-2 の端子 a は、加算器 270-2 に接続されている。スイッチ 610-2 の端子 b は、遅延器 280-2 に接続され、遅延器 280-2 の出力データが供給される。スイッチ 610-1 の端子 c は、ゼロが供給されている。加算器 270-1 は、乗算器 260-1 の出力データとスイッチ 610-1 の端子 a に現れるデータとを加算し、加算結果を出力する。加算器 270-2 は、乗算器 260-2 の出力データとスイッチ 610-2 の端子 a に現れるデータとを加算し、加算結果を出力する。

#### 【0054】

10

20

30

40

50

P N 符号発生器 620 は、 $8 T_c$  毎に 1 ビットずつ疑似雑音符号  $N_3$  を発生する装置である。疑似雑音符号  $N_3$  は、M 系列やゴールド符号など、各通信方式に必要とされる疑似雑音符号である。ただし、この疑似雑音符号  $N_3$  は、ある疑似雑音符号の一部分である。本実施形態において、P N 符号発生器 620 が発生する疑似雑音符号  $N_3$  は、拡散符号の周期が 38400 チップである W - C D M A を例にとり、符号長 38400 ビットの疑似雑音符号の先頭から 16 ビット分の符号とする。疑似雑音符号  $N_3$  は、P N 符号発生器 620 により繰り返し発生される。疑似雑音符号  $N_3$  は、A S R 250 - 1 に、および、遅延器 230 - 2 を介して A S R 250 - 2 に供給される。

#### 【0055】

次に、測定装置 3 の全体動作について説明する。ここで、図 1 を参照する。被測定信号  $S_{IN}$  は、前処理装置 20 により処理された後、A / D 変換装置 30 によりデジタル変換され、記憶装置 40 に格納される。同期捕捉装置 600 は、記憶装置 40 に格納されたデータ  $D_s$  に基づき、被測定信号  $S_{IN}$  に含まれる疑似雑音符号の位相を検出する。最後に、復調装置 100 は、同期捕捉装置 600 が検出した位相に基づき、被測定信号  $S_{IN}$  ( 実際にはデータ  $D_s$  ) を復調する。

#### 【0056】

次に、同期捕捉装置 600 の動作について説明する。ここで、図 8 と図 9 を参照する。図 9 は、データ反復器 210 の出力データおよび A S R 250 - 1 ~ 4 のそれぞれの出力データを示すタイミングチャートである。図 9 において、横軸は時間である。また、図 9 における縦破線は、クロック信号 C L K の周期間隔で並んでいる。図 9 の下図は、図 9 の上図に時間的に後続するチャートである。下付数字を有するアルファベット記号「S」は、タイムスロットを表している。タイムスロットの時間間隔は、 $T_c$  である。下付数字を有するアルファベット記号「X」は、データ反復器 210 の出力データを表している。データ反復器 210 の出力データは、 $8 T_c$  毎に新たなビットデータが出力される。下付数字を有するアルファベット記号「C」は、疑似雑音符号  $N_3$  の各ビットデータを示している。アルファベット記号「C」の下付数字は、P N 符号発生器 220 から出力されるビットデータの順番を表している。すなわち、 $C_0, C_1, C_2, \dots$  の順に出力される。なお、疑似雑音符号  $N_3$  は繰り返し発生されるので、 $C_{15}$  の次は  $C_0$  が出力される。また、疑似雑音符号  $N_3$  が疑似雑音符号の一部であるので、 $C_0$  との乗算結果から順に累積加算することを要し、 $C_0$  が現れるまでのビットデータおよび当該ビットデータに関連する演算は全て無効となる。そのような無効なビットデータは、タイミングチャート ( 図 9 ) において記号「-」として表示されている。

#### 【0057】

さて、乗算器 260 - 1 ~ 2 のそれぞれ、および、加算器 270 - 1 ~ 2 のそれぞれは、継続的に演算を繰り返している。スイッチ 610 - 1 およびスイッチ 610 - 2 は、無効なビットデータに係る乗算結果が累積加算処理に反映されないように選択動作を行う。すなわち、スイッチ 610 - 1 は、加算器 270 - 1 に入力されるデータ ( 乗算結果 ) に関連する A S R 250 - 1 の出力データが  $C_0$  である時、端子 c を選択する。これにより、加算器 270 - 1 に係る累積加算値が初期化される。一方、スイッチ 610 - 1 は、加算器 270 - 1 に入力されるデータ ( 乗算結果 ) に関連する A S R 250 - 1 の出力データが  $C_0$  以外である時、端子 b を選択する。また、スイッチ 610 - 2 は、加算器 270 - 2 に入力されるデータ ( 乗算結果 ) に関連する A S R 250 - 2 の出力データが  $C_0$  である時、端子 c を選択する。これにより、加算器 270 - 2 に係る累積加算値が初期化される。一方、スイッチ 610 - 2 は、加算器 270 - 2 に入力されるデータ ( 乗算結果 ) に関連する A S R 250 - 2 の出力データが  $C_0$  以外である時、端子 b を選択する。より具体的な例を挙げると、データ反復器 210 の出力データが  $X_0$  である時のタイムスロット  $S_0$  、および、データ反復器 210 の出力データが  $X_1$  である時のタイムスロット  $S_1$  においてスイッチ 610 - 1 の端子 c が選択され、加算器 270 - 1 にゼロが供給される。そして、データ反復器 210 の出力データが  $X_1$  である時のタイムスロット  $S_0$  、および、データ反復器 210 の出力データが  $X_2$  である時のタイムスロット  $S_1$  において、スイッチ

10

20

30

40

50

610-1の端子bが選択され、加算器270-1に遅延器280-1の出力データが供給される。また、例えば、データ反復器210の出力データが $X_8$ である時のタイムスロット $S_0$ 、および、データ反復器210の出力データが $X_9$ である時のタイムスロット $S_1$ において、スイッチ610-2の端子cが選択され、加算器270-2にゼロが供給される。そして、データ反復器210の出力データが $X_9$ である時のタイムスロット $S_0$ 、および、データ反復器210の出力データが $X_{10}$ である時のタイムスロット $S_1$ において、スイッチ610-2の端子bが選択され、加算器270-2に遅延器280-2の出力データが供給される。

#### 【0058】

第一の実施形態と同様に、リセットから一定時間経過すると、疑似雑音符号 $N_3$ の全16ビットについての乗算結果の累積加算結果が、疑似雑音符号 $N_3$ の位相ごとに、加算器270-1および加算器270-2のそれぞれから順次出力される。ここで、疑似雑音符号 $N_3$ の先頭チップの位相を最初の入力データ $X_0$ に対してnチップ分シフトした時の乗算結果の累積加算結果を $Y_n$ とする。各累積加算結果が出力されるタイミングは、第一の実施形態と同様に、加算器270-1から $9T_c$ 毎に順次、演算結果 $Y_0 \sim Y_7$ が出力される。 $Y_7$ が出力された後に続いて、加算器270-2から $9T_c$ 毎に順次、 $Y_8 \sim Y_{15}$ が出力される。

#### 【0059】

前述の通り、スイッチ610-1は、加算器280-1に入力されるデータ(乗算結果)に関連するASR250-1の出力データが $C_0$ である時、端子cを選択する。また、スイッチ610-2は、加算器280-1に入力されるデータ(乗算結果)に関連するASR250-1の出力データが $C_0$ である時、端子cを選択する。これらの動作により、随时、累積加算値が初期化されていく。従って、演算結果 $Y_0 \sim Y_{15}$ のそれぞれが出力された後、演算結果 $Y_0 \sim Y_{15}$ のそれぞれに関連する累積加算値が初期化され、新たに累積加算が開始される。そして、加算器270-1から $9T_c$ 毎に順次、演算結果 $Y_{16} \sim Y_{23}$ が出力される。 $Y_{23}$ が出力された後に続いて、加算器270-2から $9T_c$ 毎に順次、 $Y_{24} \sim Y_{31}$ が出力される。新たな累積加算を1つ開始すると、1チップ分だけサーチ区間が広がる。このようにしてサーチ区間を広げることにより、例えば、W-CDMAで信号拡散に用いられる疑似雑音符号の全長38400チップの区間における部分相関処理を実施することができる。

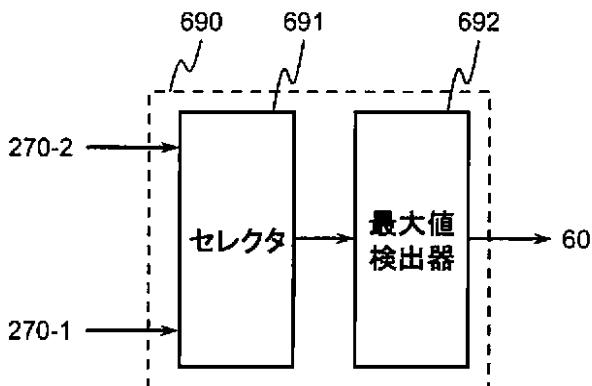

#### 【0060】

さて、各累積加算結果は異なる時間に出力されるので、検出器290を図10に示される検出器690に置き換えることができる。ここで、図10を参照する。図10は、検出器690の内部構成の一例を示す図である。検出器690は、加算器270-1の出力データと加算器270-2の出力データのいずれかを選択して出力するセレクタ691と、セレクタ691の出力データから絶対値が最大のものを検出し、当該最大値に対応する疑似雑音符号 $N_3$ の位相を出力する最大値検出器692を備える。このような検出器690は、加算器に対応して2つの最大値検出器を備える必要がない分だけ構成が簡易であり、ゲートアレイ・リソースの消費が少ない。

#### 【0061】

また、本第三の実施形態において、累積加算値を初期化する手段はスイッチに限定されない。加算器に供給される乗算結果に対応する疑似雑音符号のデータが当該疑似雑音符号の先頭データである時に、当該乗算結果とともに加算器に入力されるデータをゼロにする手段であれば何でも良い。例えば、加算器に接続される遅延器が、対応するASRに内蔵されるものと同じ段数のシフトレジスタで構成される場合、乗算器に供給される疑似雑音符号に基づいてシフトレジスタの所定のフリップフロップを適当な時期にリセットするような制御装置をスイッチの代わりに利用できる。

#### 【0062】

なお、第二の実施形態の同期捕捉装置400についても、第三の実施形態と同じく、部分的な疑似雑音符号を用いた相関処理を行うように変形させる事ができる。加えて、第三

10

20

30

40

50

の実施形態に関する他の変形も施すことができる。

#### 【0063】

また、上記の各実施形態において、相関処理の時分割多重度および並列度のそれぞれは、任意に選択することができる。すなわち、第一の実施形態のように、時分割多重度が8かつ並列度が2あることに限定されない。また、第二の実施形態のように、時分割多重度が4かつ並列度が4あることに限定されない。また、相関長も16ビットに限定されない。例えば、相関長を256ビットとした場合、並列度16かつ時分割多重度16の構成、並列度8かつ時分割多重度32の構成、あるいは、並列度4かつ時分割多重度64の構成などが採用できる。加えて、相関処理の時分割多重度および並列度のそれぞれは、ゲートアレイ50のプログラム毎に任意の値を選択することができる。このような時分割多重度と並列度の変更は、被測定信号S<sub>IN</sub>による制限を受けない。例えば、被測定信号S<sub>IN</sub>に対する同期処理中に、分割多重度または並列度を変更して、同期処理をやり直すことができる。ところで、ゲートアレイ50のクロック速度（もしくは処理速度）が、チップレートまたは被測定信号S<sub>IF</sub>（もしくはS<sub>IN</sub>）の標本化速度より高速であれば時分割多重度を増やすことができ、ゲートアレイ50のリソース消費量を減らすことができる。逆に、ゲートアレイ50のクロック速度（もしくは処理速度）が比較的遅い場合は、ゲートアレイ50のリソースを多く使うことにより並列度を高めて、必要な処理を必要な時間内に行うような選択をすることができる。従って、相関処理時間に制約がある状況下で、被測定信号の信号対雑音比が悪化し相関長を長くする必要がある場合に、同一ゲートアレイ内に構成される他の装置の規模を勘案しながら、同期捕捉装置の時分割多重度および並列度のいずれか、または、それらの両方を変化させてさせる目的を達成することができる。相関処理の時分割多重度および並列度は、第一の実施形態および第二の実施形態ならびに上記の説明を参照して明らかなように、同一のハードウェア構成において、変更可能であって、時分割多重度および並列度の複数の組み合わせから任意あるいは所定のルールに従って手動あるいは自動的に選択される。なお、時分割多重度は、ある乗算器に被測定信号の同一データが供給されている間に、同乗算器に供給される疑似雑音符号の位相の種類に等しい。また、並列度は、乗算器の個数に等しい。

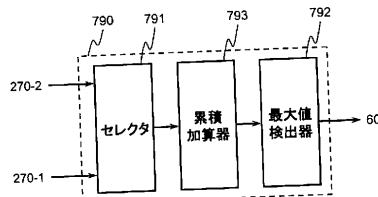

#### 【0064】

さらに、上記の実施形態において、被測定信号S<sub>IN</sub>の信号対雑音比（SNR）が小さいような場合、雑音成分の方の影響が大きく、被測定信号S<sub>IN</sub>に含まれる疑似雑音符号の正しい位相を検出できない場合がある。また、第三の実施形態では、部分相関の相関長を増やすことができるが、それでもなお正しい位相を検出できない場合がある。そのような問題を緩和するには、各実施形態において、PN符号発生器が発生する疑似雑音符号の位相ごとに得られる相関値（累積加算結果）を、被測定信号S<sub>IN</sub>に含まれる疑似雑音符号の1周期ごとに、さらに累積加算する回路を追加することが有効である。これにより、相関値のSNRが高まり、正しい位相を検出するようになる。例えば、第三の実施形態を変形する場合、図8における検出器690を、図11に示す検出器790に置き換えばよい。図11は、検出器790の内部構成の一例を示す図である。検出器790は、加算器270-1の出力データと加算器270-2の出力データのいずれかを選択して出力するセレクタ791と、セレクタ791の出力データを被測定信号S<sub>IN</sub>に含まれる疑似雑音符号N<sub>3</sub>の1周期ごとに累積加算する累積加算器793と、累積加算器793から出力されるデータ（累積相関値）のうち絶対値が最大のものを検出し、当該最大値に対応する疑似雑音符号N<sub>3</sub>の位相を出力する最大値検出器792を備える。第一の実施形態および第二の実施形態においても同様である。

#### 【0065】

またさらに、上記の各実施形態において、検出器は、加算器の出力データを参照するように構成されているが、累積のために加算器に接続されている遅延器の出力データを参照するようにしても良い。

#### 【0066】

また、上記の各実施形態において、検出器は、被測定信号に含まれる疑似雑音符号の位

10

20

30

40

50

相を検出するために累積加算結果の絶対値の最大値を検出しているが、最大値の検出に代えて所定の閾値レベルを超える累積加算結果を検出するようにしても良い。

#### 【0067】

さらに、上記の各実施形態において、相関長、または、被測定信号  $S_{IN}$  に含まれる疑似雑音符号の長さ、または、各符号発生装置が発生する疑似雑音符号の長さは、16ビットに限定されない。例えば、それらは、16ビットより短くても良いし、16ビットより長くても良い。例えば、38400チップの疑似雑音符号で拡散された被測定信号に対する128ビット長の部分相関であっても良い。

#### 【0068】

またさらに、上記の各実施形態において、PN符号発生器をゲートアレイ50内の記憶領域（不図示）やゲートアレイ50に接続されゲートアレイ50内と同等以上の速度でデータの読み出しが可能な記憶装置に置き換えることができる。すなわち、所望の疑似雑音符号データを当該記憶領域に予め格納しておき、その格納された疑似雑音符号を当該記憶領域から1ビットずつ順に繰り返し取り出すようにすれば良い。

#### 【0069】

また、上記の各実施形態において、各構成要素は、1つの筐体に備えられても良いし、2以上の筐体に分かれて備えられても良い。例えば、制御装置60が市販のコンピュータであって、その他の構成要素が、当該コンピュータに接続された1つの測定装置に備えられても良い。また、当該他の構成要素が当該市販のコンピュータに内蔵可能なボードあるいはカードに備えられても良い。

#### 【産業上の利用可能性】

#### 【0070】

本発明は、FPGAのような再構成可能なゲートアレイに限らず、ASICのような力スタムLSIタイプのゲートアレイに対しても有益である。

#### 【図面の簡単な説明】

#### 【0071】

【図1】測定装置1、測定装置2、および測定装置3の構成を示す図である。

【図2】同期捕捉装置200の構成を示す図である。

【図3】ASR250-1の構成を示す図である。

【図4】同期捕捉装置200内のデータに関するタイミングチャートである。

【図5】同期捕捉装置400の構成を示す図である。

【図6】ASR450-1の構成を示す図である。

【図7】同期捕捉装置400内のデータに関するタイミングチャートである。

【図8】同期捕捉装置600の構成を示す図である。

【図9】同期捕捉装置600内のデータに関するタイミングチャートである。

【図10】検出器690の構成を示す図である。

【図11】検出器790の構成を示す図である。

#### 【符号の説明】

#### 【0072】

1, 2, 3 測定装置

10 入力端子

20 前処理装置

30 変換装置

40 記憶装置

50 ゲートアレイ

60 制御装置

70 出力端子

100 復調装置

200, 400, 600 同期捕捉装置

210, 410 データ反復器

10

20

30

40

50

220, 420 PN符号発生器

230-2 遅延器

240, 440 カウンタ

250-1, 250-2 ASR

260, 460 乗算器

270, 470 加算器

280, 480 遅延器

290, 490, 690, 790 検出器

310-0, 310-1, 310-2, 310-3 フリップフロップ

310-4, 310-5, 310-6, 310-7 フリップフロップ

320, 520 セレクタ

430-2, 430-3, 430-4 遅延器

450-1, 450-2, 450-3, 450-4 ASR

510-0, 510-1, 510-2, 510-3 フリップフロップ

610-1, 610-2 スイッチ

620 符号発生器

691, 791 セレクタ

692, 792 最大値検出器

793 累積加算器

10

【図1】

【図2】

【図3】

【図4】

|                | S <sub>0</sub> | S <sub>1</sub>  | S <sub>2</sub>  | S <sub>3</sub>  | S <sub>4</sub>  | S <sub>5</sub>  | S <sub>6</sub>  | S <sub>7</sub> | S <sub>8</sub> | S <sub>1</sub> | S <sub>2</sub>  | S <sub>3</sub>  | S <sub>4</sub>  | S <sub>5</sub>  | S <sub>6</sub>  | S <sub>7</sub>  | S <sub>8</sub> |

|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|

| データ復器210の出力データ | X <sub>0</sub> | X <sub>0</sub>  | X <sub>0</sub>  | X <sub>0</sub>  | X <sub>0</sub>  | X <sub>0</sub>  | X <sub>0</sub>  | X <sub>1</sub> | X <sub>1</sub> | X <sub>1</sub> | X <sub>1</sub>  | X <sub>1</sub>  | X <sub>1</sub>  | X <sub>1</sub>  | X <sub>1</sub>  | X <sub>2</sub>  | X <sub>2</sub> |

| ASR250-1の出力データ | C <sub>0</sub> | C <sub>15</sub> | C <sub>14</sub> | C <sub>13</sub> | C <sub>12</sub> | C <sub>11</sub> | C <sub>10</sub> | C <sub>9</sub> | C <sub>1</sub> | C <sub>0</sub> | C <sub>15</sub> | C <sub>14</sub> | C <sub>13</sub> | C <sub>12</sub> | C <sub>11</sub> | C <sub>10</sub> | C <sub>2</sub> |

| ASR250-2の出力データ | C <sub>0</sub> | C <sub>7</sub>  | C <sub>6</sub>  | C <sub>5</sub>  | C <sub>4</sub>  | C <sub>3</sub>  | C <sub>2</sub>  | C <sub>1</sub> | C <sub>0</sub> | C <sub>6</sub> | C <sub>7</sub>  | C <sub>8</sub>  | C <sub>5</sub>  | C <sub>4</sub>  | C <sub>3</sub>  | C <sub>2</sub>  | C <sub>1</sub> |

【図5】

【図6】

【図7】

|                 | S <sub>0</sub>  | S <sub>1</sub>  | S <sub>2</sub>  | S <sub>3</sub>  | S <sub>4</sub>  | S <sub>5</sub>  | S <sub>6</sub>  | S <sub>7</sub>  | S <sub>8</sub>  | S <sub>9</sub>  | S <sub>10</sub> | S <sub>11</sub> | S <sub>12</sub> | S <sub>13</sub> | S <sub>14</sub> | S <sub>15</sub> | S <sub>16</sub> | S <sub>17</sub> | S <sub>18</sub> | S <sub>19</sub> | S <sub>20</sub> |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| データ反復器410の出力データ | X <sub>0</sub>  | X <sub>1</sub>  | X <sub>1</sub>  | X <sub>1</sub>  | X <sub>1</sub>  | X <sub>2</sub>  | X <sub>2</sub>  | X <sub>2</sub>  | X <sub>3</sub>  | X <sub>3</sub>  | X <sub>3</sub>  | X <sub>3</sub>  | X <sub>4</sub>  | X <sub>4</sub>  | X <sub>4</sub>  | X <sub>4</sub>  |

| ASR450-1の出力データ  | C <sub>0</sub>  | -               | C <sub>13</sub> | C <sub>14</sub> | C <sub>13</sub> | C <sub>14</sub> | C <sub>1</sub>  | C <sub>0</sub>  | -               | C <sub>15</sub> | C <sub>14</sub> | C <sub>2</sub>  | C <sub>1</sub>  | C <sub>0</sub>  | C <sub>15</sub> | C <sub>14</sub> | C <sub>2</sub>  | C <sub>1</sub>  | C <sub>0</sub>  | C <sub>13</sub> | C <sub>12</sub> |

| ASR450-2の出力データ  | C <sub>12</sub> | C <sub>11</sub> | C <sub>10</sub> | C <sub>9</sub>  | C <sub>13</sub> | C <sub>12</sub> | C <sub>11</sub> | C <sub>10</sub> | C <sub>14</sub> | C <sub>13</sub> | C <sub>12</sub> | C <sub>11</sub> | C <sub>10</sub> | C <sub>9</sub>  | C <sub>8</sub>  | C <sub>7</sub>  | C <sub>6</sub>  | C <sub>5</sub>  | C <sub>4</sub>  | C <sub>3</sub>  | C <sub>2</sub>  |

| ASR450-3の出力データ  | C <sub>8</sub>  | C <sub>7</sub>  | C <sub>6</sub>  | C <sub>5</sub>  | C <sub>9</sub>  | C <sub>8</sub>  | C <sub>7</sub>  | C <sub>6</sub>  | C <sub>10</sub> | C <sub>9</sub>  | C <sub>8</sub>  | C <sub>7</sub>  | C <sub>6</sub>  | C <sub>5</sub>  | C <sub>4</sub>  | C <sub>3</sub>  | C <sub>2</sub>  | C <sub>1</sub>  | C <sub>0</sub>  | C <sub>11</sub> | C <sub>10</sub> |

| ASR450-4の出力データ  | C <sub>4</sub>  | C <sub>3</sub>  | C <sub>2</sub>  | C <sub>1</sub>  | C <sub>5</sub>  | C <sub>4</sub>  | C <sub>3</sub>  | C <sub>2</sub>  | C <sub>6</sub>  | C <sub>5</sub>  | C <sub>4</sub>  | C <sub>3</sub>  | C <sub>2</sub>  | C <sub>1</sub>  | C <sub>0</sub>  | C <sub>6</sub>  | C <sub>5</sub>  | C <sub>4</sub>  | C <sub>3</sub>  | C <sub>2</sub>  | C <sub>1</sub>  |

【図8】

【図9】

|                 | S <sub>0</sub> | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub> | S <sub>7</sub> | S <sub>8</sub> | S <sub>9</sub> | S <sub>10</sub> | S <sub>11</sub> | S <sub>12</sub> | S <sub>13</sub> | S <sub>14</sub> | S <sub>15</sub> | S <sub>16</sub> | S <sub>17</sub> | S <sub>18</sub> | S <sub>19</sub> | S <sub>20</sub> |   |

|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---|

| データ反復器210の出力データ | X <sub>0</sub> | X <sub>1</sub> | X <sub>1</sub> | X <sub>1</sub> | X <sub>1</sub> | X <sub>2</sub>  | X <sub>2</sub>  | X <sub>2</sub>  | X <sub>3</sub>  | X <sub>3</sub>  | X <sub>3</sub>  | X <sub>3</sub>  | X <sub>4</sub>  | X <sub>4</sub>  | X <sub>4</sub>  | X <sub>4</sub>  |   |

| ASR250-1の出力データ  | C <sub>0</sub> | -              | -              | -              | -              | -              | -              | C <sub>1</sub> | C <sub>0</sub> | -              | -               | -               | -               | -               | -               | -               | -               | -               | -               | C <sub>2</sub>  | -               |   |

| ASR250-2の出力データ  | -              | -              | -              | -              | -              | -              | -              | -              | -              | -              | -               | -               | -               | -               | -               | -               | -               | -               | -               | -               | -               | - |

| データ反復器210の出力データ | X <sub>0</sub> | X <sub>1</sub> | X <sub>2</sub> | X <sub>3</sub> | X <sub>4</sub> | X <sub>5</sub> | X <sub>6</sub> | X <sub>7</sub> | X <sub>8</sub> | X <sub>9</sub> | X <sub>10</sub> | X <sub>11</sub> | X <sub>12</sub> | X <sub>13</sub> | X <sub>14</sub> | X <sub>15</sub> | X <sub>16</sub> | X <sub>17</sub> | X <sub>18</sub> | X <sub>19</sub> | X <sub>20</sub> |   |

| ASR250-1の出力データ  | C <sub>6</sub> | C <sub>7</sub> | C <sub>6</sub> | C <sub>5</sub> | C <sub>4</sub> | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | C <sub>0</sub> | C <sub>9</sub> | C <sub>8</sub>  | C <sub>7</sub>  | C <sub>6</sub>  | C <sub>5</sub>  | C <sub>4</sub>  | C <sub>3</sub>  | C <sub>2</sub>  | C <sub>1</sub>  | C <sub>0</sub>  | C <sub>10</sub> | C <sub>9</sub>  |   |

| ASR250-2の出力データ  | C <sub>0</sub> | -              | -              | -              | -              | -              | -              | -              | -              | C <sub>1</sub> | C <sub>0</sub>  | -               | -               | -               | -               | -               | -               | -               | -               | -               | C <sub>2</sub>  | - |

【図10】

【図11】

---

フロントページの続き

(72)発明者 生駒 哲昭

東京都八王子市高倉町9番1号 アジレント・テクノロジー・インターナショナル株式会社内

F ターム(参考) 5K022 EE02 EE14 EE36

5K047 AA11 BB01 CC01 HH11

5K067 AA41 BB04 CC10 DD11 DD25 EE12 FF02 HH22 HH23 HH24

LL11