(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5763682号

(P5763682)

(45) 発行日 平成27年8月12日(2015.8.12)

(24) 登録日 平成27年6月19日(2015.6.19)

|                      |            |

|----------------------|------------|

| (51) Int.Cl.         | F 1        |

| B81B 7/02 (2006.01)  | B81B 7/02  |

| B81C 3/00 (2006.01)  | B81C 3/00  |

| H04R 19/04 (2006.01) | H04R 19/04 |

請求項の数 13 (全 15 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2012-550407 (P2012-550407)  |

| (86) (22) 出願日 | 平成23年1月24日 (2011.1.24)        |

| (65) 公表番号     | 特表2013-517953 (P2013-517953A) |

| (43) 公表日      | 平成25年5月20日 (2013.5.20)        |

| (86) 國際出願番号   | PCT/EP2011/050902             |

| (87) 國際公開番号   | W02011/092137                 |

| (87) 國際公開日    | 平成23年8月4日 (2011.8.4)          |

| 審査請求日         | 平成25年8月27日 (2013.8.27)        |

| (31) 優先権主張番号  | 102010006132.8                |

| (32) 優先日      | 平成22年1月29日 (2010.1.29)        |

| (33) 優先権主張国   | ドイツ (DE)                      |

|           |                                                                                    |

|-----------|------------------------------------------------------------------------------------|

| (73) 特許権者 | 510263560<br>エプコス アーゲー<br>E P C O S AG<br>ドイツ国 81669 ミュンヘン セン<br>ト・マーティン・シュトラーセ 53 |

| (74) 代理人  | 100147485<br>弁理士 杉村 憲司                                                             |

| (74) 代理人  | 100165696<br>弁理士 川原 敬祐                                                             |

| (74) 代理人  | 100169823<br>弁理士 吉澤 雄郎                                                             |

| (72) 発明者  | グレゴル フェイエルタック<br>ドイツ国 80689 ミュンヘン ヴィ<br>ルヘルム マイヤー シュトラッセ 21                        |

最終頁に続く

(54) 【発明の名称】MEMS及びASICを備える小型化した電気的デバイス及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

MEMSセンサデバイス(EB)であって、該MEMSセンサデバイスは、

・電気的接点(EK)を有するMEMSチップ(MC)と、

・電気的接点(EK)を有するASICチップ(AC)と、

・前記MEMSチップ(MC)及び前記ASICチップ(AC)を接続する内部接続部(IV)と、

・前記MEMSチップ(MC)又は前記ASICチップ(AC)を貫通するビア(DK)と

を備え、

前記MEMSチップ(MC)及び前記ASICチップ(AC)は互いに上下に配置し、

・前記内部接続部(IV)は、前記MEMSチップの前記電気的接点(EK)を前記ASICチップ(AC)の前記電気的接点(EK)に直接接続する接続部を含み、

・前記内部接続部(IV)又は前記チップ(MC, AC)における少なくとも一方の前記電気的接点(EK)は、前記ビア(DK)を介して前記デバイスの電気的外部接続端子(EEA)に接続し、該電気的外部接続端子(EEA)は、前記ASICチップ(AC)における前記MEMSチップ(MC)に対面する側の側面に、又は前記MEMSチップにおける前記ASICチップ(AC)に対面する側の側面に配置し、

・前記MEMSチップ(MC)と前記ASICチップ(AC)との間には隙間(S)を設け、

10

20

- ・該隙間( S )にフレーム( R )を配置し、

- ・前記MEMSチップ( MC )はセンサ電極を有するものとし、また

- ・前記フレーム( R )は、完全には閉じておらず、フレームの欠落している箇所により側面にセンサ開口( O )を形成した

- MEMSセンサデバイス。

**【請求項2】**

請求項1記載のMEMSセンサデバイスにおいて、前記MEMSチップ( MC )は下側面( USM )を有し、前記ASICチップ( AC )は上側面( OSA )及び下側面( USA )を有し、前記ASICチップ( AC )の前記上側面( OSA )は、前記MEMSチップ( MC )の前記下側面( USM )に対面し、前記ビア( DK )は前記ASICチップ( AC )を貫通し、前記電気的外部接続端子( EEA )は前記ASICチップの前記下側面( USA )に配置したMEMSセンサデバイス。 10

**【請求項3】**

請求項1記載のMEMSセンサデバイスにおいて、前記ASICチップ( AC )は前記下側面( USA )を有し、前記MEMSチップ( MC )は前記上側面( OSM )及び前記下側面( USM )を有し、前記MEMSチップ( MC )の前記上側面( OSM )は、前記ASICチップ( AC )の下側面( USA )に対面し、前記ビア( DK )は前記MEMSチップ( MC )を貫通し、前記電気的外部接続端子( EEA )は前記MEMSチップの前記下側面( USM )に配置したMEMSセンサデバイス。 20

**【請求項4】**

請求項1～3のいずれか一項記載のMEMSセンサデバイスにおいて、前記MEMSチップ( MC )又は前記ASICチップ( AC )の基板はシリコンを含有するものとしたMEMSセンサデバイス。

**【請求項5】**

請求項1～4のいずれか一項記載のMEMSセンサデバイスにおいて、前記MEMSチップ( MC )の前記電気的接点( EK )を、前記ASICチップ( AC )の前記電気的接点( EK )に対し、はんだ付け、又は導電性を有する接着剤による接着、ボンディングによる接続又は溶着により、接続したMEMSセンサデバイス。 30

**【請求項6】**

請求項1～5のいずれか一項記載のMEMSセンサデバイスにおいて、該MEMSセンサデバイス( EB )は電気的接続端子を有する取付プレート( MP )の上側面に配置し、前記電気的外部接続端子( EEA )を前記取付プレート( MP )における前記電気的接続端子に接続したMEMSセンサデバイス。 30

**【請求項7】**

請求項1～6のいずれか一項記載のMEMSセンサデバイスにおいて、前記MEMSチップ( MC )は中空空間( H )、可動の薄膜( M )、対向電極( RP )、及び前記中空空間( H )に至る前記センサ開口( O )を有し、

前記薄膜( M )は前記対向電極( RP )に対して平行に配置し、該対向電極( RP )と共に静電容量素子( KE )を構成し、前記ASICチップ( AC )は容量を測定するための回路又は前記容量素子の容量変化を測定するための回路を有する構成としたMEMSセンサデバイス。 40

**【請求項8】**

請求項1～5のいずれか一項記載のMEMSセンサデバイスにおいて、前記MEMSチップ( MC )は気圧、湿度又はガス組成を測定・検出するためのデバイス構造( BS )を有し、該デバイス構造( BS )は前記デバイス( BE )に対する周囲の環境に接触するものとしたMEMSセンサデバイス。

**【請求項9】**

請求項1～8のいずれか一項記載のMEMSセンサデバイスにおいて、少なくともそれぞれ2個の前記MEMSチップ( MC )、前記ASICチップ( AC )及び前記フレームが側方方向に面一に整列するよう連結したMEMSセンサデバイス。 50

**【請求項 10】**

請求項 1 ~ 9 のいずれか一項記載の M E M S センサデバイスにおいて、前記 M E M S チップはマイクロフォンとして構成すると共に、前記対向電極 ( R P ) としての固定電極及び前記薄膜 ( M ) を有する構成とした M E M S センサデバイス。

**【請求項 11】**

M E M S センサデバイス ( B E ) を製造するための方法であって、該方法は、

・電気的接点 ( E K ) を有する A S I C チップ ( A C ) 及び電気的接点 ( E K ) を有する M E M S チップ ( M C ) を用意するステップと、

・前記 M E M S チップ又は前記 A S I C チップ ( A C ) にビア ( D K ) を設けるステップと、

・前記 A S I C チップ ( A C ) 及び前記 M E M S チップ ( M C ) の間に隙間を ( S ) を設けるように互いに上下に配置するステップと、

・前記デバイスの側面にセンサ開口 ( O ) を形成するフレーム ( R ) を介して前記 A S I C チップ ( A C ) 及び前記 M E M S チップを結合するステップと、

・前記 A S I C チップ ( A C ) 及び前記 M E M S チップ ( M C ) の前記電気的接点 ( E K ) 相互を接続するステップと

を有し、

前記 A S I C チップ ( A C ) 内、又は該 A S I C チップ ( A C ) と前記 M E M S チップ ( M C )との間で外部に開口するセンサ開口を設ける方法。

**【請求項 12】**

請求項 11 記載の方法において、前記 A S I C チップ ( A C ) 又は前記 M E M S チップ ( M C ) を多面取り用にウェハ ( W ) 上に設ける方法。

**【請求項 13】**

請求項 11 又は 12 記載の方法において、前記 A S I C チップ ( A C ) 及び前記 M E M S チップ ( M C ) は、多面取り用にそれぞれ 1 個の前記ウェハ ( W ) 上に設け、また各前記 A S I C チップ ( A C ) がそれぞれに対応する前記 M E M S チップ ( M C ) に結合しました接続するよう前記ウェハ ( W ) を貼り合わせる方法。

**【発明の詳細な説明】**

30

**【技術分野】****【0001】**

本発明は、M E M S チップ及び A S I C チップを備える小型化した M E M S センサデバイスに関する。

**【背景技術】****【0002】**

M E M S ( Micro-Electro-Mechanical-Systems ) はセンサとして多くの用途がある。 M E M S は、例えば、湿度センサ、加速度センサのような慣性センサ、圧力センサ又はマイクロフォンセンサとして使用されている。

**【0003】**

40

A S I C ( Application-Specific-Integrated-Circuits : 特定用途向け集積回路 ) は、 M E M S センサに接続した場合、一般的にスイッチ回路、例えば論理回路又はアナログ回路として構成することができ、これにより M E M S から供給されるセンサ信号を処理する。 例えば M E M S マイクロフォンが 2 個のコンデンサ電極であって、受信した音波の圧力変動によって互いの間隔が変わる 2 個のコンデンサ電極を有する場合、 A S I C はアナログ又はデジタル回路として構成することができる。 これらアナログ又はデジタル回路は、 M E M S コンデンサの経時的に可変である容量を電子的に更に処理可能な信号に変換する。 このようにして M E M S マイクロフォンが構成される。

**【0004】**

特許文献 1 ( 米国特許第 6,781,231 号 ) に開示されている M E M S マイクロフォ

50

ンにおいては、MEMSチップを基板上に取り付け、キャップ状のカバーで被覆する。

**【0005】**

特許文献2（米国特許第6,522,762号）に開示されているMEMSマイクロフォンにおいては、そのMEMSチップ及びASICチップを支持基板における一方の側に互いに隣接して取り付けている。

**【0006】**

特許文献3（米国特許出願公開第6,088,463号）に開示されているMEMSマイクロフォンにおいては、シリコンを含有するMEMSチップ及びASICチップを支持基板（中間層）の互いに背反する側面に取り付けている。

**【0007】**

特許文献4（米国特許出願公開第2009/0001553号）に開示されているMEMSパッケージにおいては、MEMSチップ及びASICチップを互いに隣接させて又は互いに上下に取り付け、また金属層により被覆している。

**【0008】**

上述したそれぞれの電気的デバイスは、取り付けのための支持基板を必要とする。

**【0009】**

電子デバイス、特に例えばモバイル電子機器に使用されるMEMSデバイスの市場においては、モバイル機器（例えばモバイル通信機器）に対してより多くの機能を組み込むため、デバイスの小型化に対する要請がますます高まっている。

**【先行技術文献】**

**【特許文献】**

**【0010】**

**【特許文献1】**米国特許第6,781,231号明細書

**【特許文献2】**米国特許第6,522,762号明細書

**【特許文献3】**米国特許出願公開第6,088,463号明細書

**【特許文献4】**米国特許出願公開第2009/0001553号明細書

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0011】**

本発明の課題は、有利に製造できかつ信号分解能を向上させた小型のMEMSセンサデバイスを得ることにある。本発明におけるさらなる課題は、このようなMEMSセンサデバイスの製造方法を提供することにある。

**【課題を解決するための手段】**

**【0012】**

本発明によるMEMSセンサデバイスは、電気的接点を有するMEMSチップ及び電気的接点を有するASICチップを備える。さらに本発明によるデバイスは、MEMSチップ及びASICチップの内部接続部並びに電気的外部接続端子を備える。電気的デバイスはこれに加えて、MEMSチップ又はASICチップを貫通するビアを備える。MEMSチップ及びASICチップは、互いに上下に配置する。内部接続部は、MEMSチップにおける電気的接点をASICチップの電気的接点に直接接続する接続部を含む。内部接続部又は両チップにおける電気的接点の少なくとも一方は、ビアを介して電気的外部接続端子に接続する。

**【0013】**

ビアはデバイスの電気的外部接続端子に接続し、この電気的外部接続端子は、ASICチップにおけるMEMSチップに対面する側の側面に、又はMEMSチップにおけるASICチップに対面する側の側面に配置する。MEMSチップとASICチップとの間には隙間を設け、この隙間にフレームを配置する。このフレームは、MEMSセンサデバイス内部を側方方向に遮蔽する。MEMSチップは少なくとも1個のセンサ電極を有し、このセンサ電極は可動電極及び固定電極を含む。センサ開口は、ASICチップ内に直接配置する、又はASICチップを貫通するよう配置する、又は側面からMEMSチップと

10

20

30

40

50

A S I C チップとの間で隙間の側面に通するよう設ける。センサ開口は、周囲からデバイス内部に進入する分析すべき測定量（例えば音響エネルギー、圧力、ガス、湿度）の入口として機能する。

【 0 0 1 4 】

シリコンチップに形成するビアは、例えればいわゆる T S V s ( Through-Silicon Vias: スルーサイリコンビア ) とすることができます。

【 0 0 1 5 】

本発明による M E M S センサデバイスは、M E M S チップ及びA S I C チップを互いに上下に配置することにより、小型化することができる。特にデバイスに必要な占有面積は、基本的にM E M S チップ又はA S I C チップのうち、より大きいチップに必要な占有面積とほぼ同一である。10

【 0 0 1 6 】

多数の同一のM E M S チップは第1のウェハに、また多数の同一のA S I C チップは第2のウェハに実装することができる。それぞれのウェハを製造した後、多数あるM E M S チップのそれぞれ1個を多数あるA S I C チップのそれぞれ1個に結合することができる。このような多面取りによる製造は、電気的デバイスの簡単かつ安価な製造を可能とする。。

【 0 0 1 7 】

ただし代替的には、A S I C チップ及びM E M S チップの一方のみを多面取り用に1個のウェハに実装し、個別に切り出した他方のチップに結合してもよい。20

【 0 0 1 8 】

M E M S チップ及びA S I C チップを互いに上下に配置し、両チップをM E M S チップ又はA S I C チップを貫通するビアを介して互いに接続するため、電気的配線は極力短く形成できる。このことは有利であり、なぜならM E M S チップにより検波された信号は内部接続部を介してA S I C チップに伝送され、基本的にはM E M S チップからA S I C チップへの電気的接続が長いほど妨害されるからである。従って、電気的配線を短くすることにより信号の妨害を低減することが可能となる。

【 0 0 1 9 】

このように、従来技術の電気的デバイスに比べて、本発明は相当程度向上させたデバイスを提供する。30

【 0 0 2 0 】

一実施形態において、M E M S チップは下側面を有し、A S I C チップは上側面及び下側面を有する。A S I C チップの上側面は、M E M S チップの下側面に対面する。ビアは、A S I C チップを貫通するよう設ける。電気的外部接続端子は、A S I C チップの下側面に配置する。

【 0 0 2 1 】

代替的には、電気的外部接続端子をM E M S チップの下側面に設け、A S I C チップをM E M S チップの上側面に配置することもできる。

【 0 0 2 2 】

電気的外部接続端子をM E M S チップのデバイス構造又はA S I C チップのデバイス構造に接続するため、両チップのうち電気的外部接続端子を配置する側のチップにビアを設ける。40

【 0 0 2 3 】

M E M S チップのデバイス構造及びA S I C チップの回路は、これらチップの上側面だけでなく下側面に配置してもよい。ただし、M E M S チップのデバイス構造及びA S I C チップの回路は、それぞれのチップ内に配置することもできる。適切に設けたビアにより、電気的接続部を電気回路素子間又はデバイス構造間において確実に短い経路で延在させることができる。

【 0 0 2 4 】

M E M S チップ及びA S I C チップを備える電気的デバイスは、特にこの電気的デバイ50

スのための支持基板又はデバイス支持体上に配置する必要はない。電気的デバイスは外部接点を備え、この外部接点により電気的デバイスを外部における任意の周辺回路に集積することが可能となる。

#### 【0025】

本発明においては、MEMSチップの機能（例えば音響的な背面容積確保による）、又はASICチップの機能（例えば付加的な集積回路による）を支援する支持基板は必要ない。

#### 【0026】

一実施形態において、MEMSチップ又はASICチップの基板はシリコンを含有する。シリコンは高純度かつ単結晶で精製可能な元素であり、その精製及び加工は半導体技術における豊富な経験により習熟されている。従って半導体技術において既知の方法により、MEMSチップ及び／又はASICチップに関して信頼性の高い加工又は製造が可能となる。

10

#### 【0027】

一実施形態において、MEMSチップの電気的接点はASICチップの電気的接点にはんだ付けする。代案としては、導電性を有する合成物質による接着、ボンディング又は当該チップ相互の溶着による接続を行うこともできる。

#### 【0028】

導電性を有する接着剤の場合、導電性に関して異方性がある接着剤を使用することができる。この接着剤は、両チップにおける互いに対面する側面の大部分に、又は構造体化した接着剤フレームとして塗布することができ、MEMSチップ及びASICチップとの間における隙間の外部に対する密封だけでなく、両チップ間における電気的接触をも可能とする。

20

#### 【0029】

一実施形態において、両チップ間には隙間を設ける。この隙間は環状フレーム、例えば接着剤によるフレーム又は別のシールリングを使用することにより、ハーメチック又は音響的に遮蔽することができる。従って、合成物質、ガラス、セラミック又は金属で構成される環状フレームは、上側チップ及び下側チップと共にこれら両チップ間に中空空間を形成し、しかも環状の密封部として機能する。中空空間内には、MEMSチップのデバイス構造又はASICチップの回路素子を配置することができる。

30

#### 【0030】

電気的なMEMSセンサデバイスにおける密封は、両チップの結合後にもよい。環状密封は、例えば両チップのうち小さい方のチップにフォイル積層体を設ける、又はポリマー材料で同一箇所を被覆することにより行うことができる。両チップは、フリップチップ構造で互いに結合し、接続することができる。

#### 【0031】

この密封は、例えば両チップにおける側方方向の寸法が同一である場合、両チップ上にフォイル積層体を設けることにより行う、又は同一箇所をポリマー材料で被覆することにより行うこともできる。

#### 【0032】

40

フレームは、構造体化したポリマーフレームとすることができる。このフレームは、両チップを互いに結合する前にMEMSチップ又はASICチップ若しくはこれらチップの一部に配置することができ、これにより両チップを互いに結合した後に形成される隙間を外部に対して密封する。ウェハレベルで加工をする場合、ポリマーフレームを一方又は両方のウェハに予め設けてもよい。

#### 【0033】

フレームには、両チップにおける電気的な接続部と同一材料を含有することができる。フレームは特に、はんだ、いわゆる固液相互拡散はんだ、導電性を有する接着剤、又は両チップに分布させた2つの部分金属フレームであって、加圧及び加熱作用の下に互いに接合した部分金属フレームとすることができます。

50

## 【0034】

MEMSチップのデバイス構造は、外的影響受けないようカプセル封入することができる。これにより、デバイス構造は例えば製造時の汚染に対して、プリント基板／取付プレートへのはんだ付け又は接続若しくは結合に対して、又はASICチップとの結合による汚染に対して保護される。

## 【0035】

デバイスのカプセル封入化、又はMEMSチップとASICチップとの間における隙間の外部に対する密封にはフォイルを使用することができ、このフォイルは上側チップの上側面及び側面を被覆し、また例えばチップの周囲に完全に当接した状態で下側チップの上側面又は側面に密着して閉塞する。このようなフォイルは、例えば部分的に相互結合されたエポキシ樹脂又はBステージ材を含有することができ、付加的に部分的又は完全にメタライジング層で被覆してもよい。10

## 【0036】

このフォイルの代わりとして、又は上述したメタライジング層を形成する前の電気絶縁層の付加として、誘電体層を形成することができる。この誘電体層は、例えばラッカーの吹付けにより、又は酸化物、窒化物若しくはパリレン等のポリマーによる蒸着により形成する。

## 【0037】

一実施形態において、デバイスは電気的接続端子を有する取付プレートの上側面に配置する。デバイスの電気的外部接続端子は、取付プレートの電気的接続端子に接続する。この取付プレートは、外部周辺回路における任意の取付プレートとすることができる。取付プレートは、電気的デバイスの機能を発揮する上で必ずしも必要ではない。20

## 【0038】

MEMSチップ又はASICチップはその下側面に接点パッドを有することができ、これら接点パッドは例えば取付プレートに接触するよう機能する。

## 【0039】

一実施形態において、MEMSチップは中空空間と、この中空空間を一方の側で閉鎖し、かつ電極を設けた可動薄膜と、好適には中空空間における薄膜に対して平行に、かつ対面する側に配置した対向電極とを有する。可動薄膜は、対向電極と共に静電容量素子を構成する。ASICチップは、静電容量素子の容量を測定するための回路又は容量変化を検出するための回路を有する。このような電気的デバイスは、MEMSマイクロフォンとして構成することができる。可動薄膜は、受信音波による経時に変化する空気圧力に反応する。対向電極と薄膜との間における間隔が進入する音波の周波数に応じて変化することで、静電容量素子間の間に依存する容量（キャパシタンス）により音波として伝送される音響が符号化される。30

## 【0040】

ASICチップは回路を有することができ、この回路は静電容量素子における2個の電極において、例えば高い抵抗値を有する抵抗器及び電荷ポンプにより、静電容量素子内の蓄積電荷をほぼ一定に保ち、これによりバイアス電圧を発生させる。ASICチップにおける別の回路は、静電容量素子において降圧し、かつ経時に可変の電圧を検出すると共に、アナログ・デジタル変換器によりデジタル信号に変換することができる。このデジタル信号は、外部周辺回路、例えば電気的デバイスの電気的外部接続端子に出力することができる。40

## 【0041】

この場合、MEMSチップの対向電極はASICチップと薄膜との間に配置することができるが、薄膜はASICチップと対向電極との間に配置してもよい。

## 【0042】

薄膜は、センサ開口を介して外部環境に触れる。

## 【0043】

一実施形態において、MEMSチップは、気圧、湿度又はガス組成を測定・検出するデ50

バイス構造を有する。これらデバイス構造は、デバイスの周囲における大気に触れる。気圧を測定するための電気的デバイスは、例えば特定の内圧を有する閉塞された中空空間を有することができる。この閉塞された中空空間は壁で包囲し、この壁は少なくともその一部が弾性的に変形可能とする。電気的デバイスの周囲における気圧が変化すると、弹性壁が内外における異なる力関係により、中空空間の正圧又は負圧に対して弹性変形を示す。弹性壁におけるこのような弹性変形は、例えば弹性壁に配置した抵抗構造部又はこの抵抗構造部における電気抵抗の変化により検出することができる。このような構成としたデバイスにより、海面を基準にした約1デシメートルの高低差に対応する気圧変化が測定可能となる。

## 【0044】

10

本発明による電気的デバイスは、ガスセンサとして構成することもできる。

## 【0045】

両チップ又は電気的デバイスは、外部に形成するメタライジング層を有することができ、このようなメタライジング層は保護として、電磁的な遮蔽として又はハーメチック（気密）シールとして機能する。このメタライジング層により、例えば機械的損傷又は無線周波妨害に対する保護が可能となる。メタライジング層は、フォイルの積層及びスパッタにより又は電気めっきにより形成することができる。

## 【0046】

この保護メタライジング層は、チップ本体に対して電気的に絶縁させることが必須である。しかし、保護メタライジング層は、通常、適切な電位（例えばグランド電位）を接続したデバイス又は外部端子に付与する。

20

## 【0047】

一実施形態において、両チップのうち小さい方のチップは、成形プロセスによりその幾何学的形状、例えば側方方向における寸法又は体積を拡大することができる。この目的のために、両チップは、例えば格子状に配置してフォイルに接着し、チップ間に成形材料を充填する。このように製造した新たなウェハには、ビア及び配線面を設ける。この「拡大した」ウェハはその後、上述した成形工程の1つに使用する。

## 【0048】

30

このようなチップ拡大化の場合、第1ステップにおいて、有利に配置した個々のチップから成形により、あたかも新しいウェハを製造することができる。後続のステップにおいて、ビア、又は開口、例えば音波開口を成形体領域に配置することができる。ビア又は開口は、代案として、成形時に設けることもでき、これらは例えば成形型にピンを配置することにより設ける。チップの寸法を拡大することにより、上述したような開口、ビア又は付加的な配線をそれぞれのチップ上に配置することが容易になる。

## 【0049】

類似する一実施形態においては、複数個のASICチップをビア及び配線構造を設けた有機プリント基板に積層することにより、新たな多面取り基板が得られる。

## 【0050】

代替的には、1個のデバイスのために複数個のMEMSチップを1個のASICチップ上に、又は複数個のASICチップを1個のMEMSチップ上に取り付けることもできる。

40

## 【0051】

MEMSチップ及びASICチップの材料は、チップ間に加わる機械的応力であって、チップ間の結合又は電気的接続に負荷を与える機械的応力を低減するよう選択することができる。特に、MEMSチップの基板及びASICチップの基板は、同一材料を含有するものとする。

## 【0052】

一実施形態において、電気的デバイスはマイクロフォンとして構成する。MEMSチップとASICチップとの間には、隙間を設ける。この隙間には、デバイス内部を音響的に密封する環状に閉じたフレームを配置する。MEMSチップは、対向電極及び薄膜を有す

50

る。ASICチップ又はフレームには、音波進入口を配置する。MEMSチップ及びASICチップにおける側方方向の寸法は、同一とすることができます。ASICチップにおけるMEMSチップに對面する側の側面には、電気的外部接続端子を配置する。MEMSチップ、ASICチップ及び好適にはフレームも、互いにマイクロフォンの側方方向に面で整列するようとする。

#### 【0053】

ASICチップ又はフレームに設ける1つの音波進入口に加えて、例えば直径が約30μmの音波進入口を付加的に配置してもよい。多数のより小さく形成した開口は、良好な音波進入だけでなく、塵埃粒子に対する防護を向上させる。

#### 【0054】

本発明による電気的デバイスを製造するための方法は以下のステップを有する。すなわち、

電気的接点を有するASICチップ及び電気的接点を有するMEMSチップを用意するステップと、

MEMSチップ又はASICチップを貫通するビアを設けるステップと、

ASICチップ及びMEMSチップを互いに上下に配置するステップと、

ASICチップ及びMEMSチップを結合するステップと、

ASICチップ及びMEMSチップの電気的接点相互を接続するステップと、

ASICチップ内、又はASICチップとMEMSチップとの間にセンサ開口を設けるステップとを有する。

#### 【0055】

本発明方法における一実施形態においては、ASICチップ又はMEMSチップを多面取り用にウェハに設け、個別の第2チップに結合する。特にウェハによる量産は、本発明による電気的デバイスを効率的に、容易に、かつ安価に製造することを可能とする。

#### 【0056】

一実施形態では、ASICチップ及びMEMSチップを多面取り用にそれぞれ1個のウェハに設ける。これらウェハは、それぞれ1個のASICチップがそれぞれ1個のMEMSチップに結合、接続するよう接合する。電気的デバイスの切り出しは、ウェハを接合及び接続した後、例えばレーザー又はソーイングにより行う。

#### 【0057】

一実施形態においては、ASICチップを貫通する開口、例えば音波進入口をエッティングにより設ける。代案として、1つの大きな開口の代わりに多数の小さな開口をエッティングにより設けてもよい。エッティングにより複数の小さな開口を設けることには、プロセス工学上の利点がある。フレームに設ける1つ以上のセンサ開口は、フレーム形成時に設ける又は後からフレームを構造体として形成することにより設けることができる。フレームが互いに對面する両チップの表面上に配置する2個の部分フレームで構成される場合、2個の部分フレームの一方にのみセンサ開口を設けてもよい。

#### 【0058】

さらにMEMSチップ、ASICチップ、又はこれら両チップ間に生ずる応力は、可撓性がある固定部及び/又は接続部により低減することができる。このために、特にコイル状の銅線を有するポリマーバンプ、ACA接続部(Anisotropic Conductive Adhesive-Verbindungen:異方性導電接着剤)又は可撓性ICA接続部(Isotropic Conductive Adhesive-Verbindungen:等方性導電接着剤)を使用することができる。

#### 【0059】

電気的デバイスのチップを取付プレートに結合した場合、この取付プレートに對面するチップの側面においても機械的な応力負荷を軽減するための手段を講じることができる。特に取付プレートに對面するデバイスの側面には、関連する温度領域で取付プレートに適合するCTE(= coefficient of thermal expansion = thermischer Ausdehnungskoeffizient: 熱膨張係数)、又は関連する温度領域で取付プレートに適合する低い弾性係数を有する可撓性の高いポリマー層を塗布することができる。チップ間、又はデバイスと取付

10

20

30

40

50

プレートとの間の結合及び接続としては、LGA (land grid array: ランド・グリッド・アレイ) 又はBGA (ball grid array: ボール・グリッド・アレイ) による結合部及び接続部を使用することができ、これらは可撓性を有するものとして形成することができる。

#### 【0060】

ASICチップには電荷ポンプ設けることができ、これにより供給電圧よりも高い電圧を得ることが可能となる。特にMEMSマイクロフォンの静電容量素子を充電する電圧は通常の作動電圧よりも明らかに高い約10ボルトであり、ASICチップで発生させることができることができる。

#### 【0061】

MEMSチップ又はASICチップを貫通するビアにより、デバイス構造又は集積回路を両チップにおける任意かつ異なる箇所に配置し、接続することができる。すなわち、電気的デバイスを設計する際の自由度が大幅に高まる。

10

#### 【0062】

以下、本発明による電気的デバイスを、実施形態及び添付図面につきより詳細に説明する。

#### 【図面の簡単な説明】

#### 【0063】

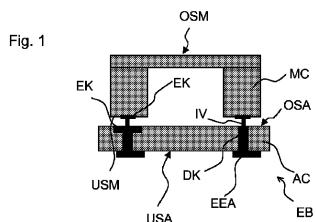

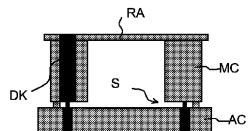

【図1】MEMSチップ及びASICチップを備える電気的デバイスを示す説明図である。

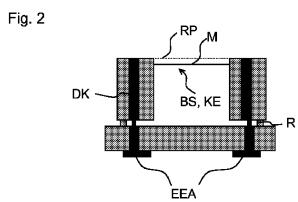

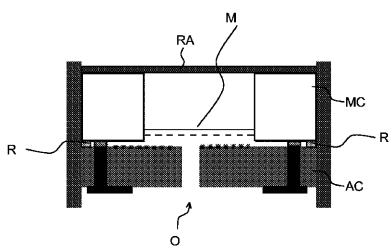

【図2】デバイス構造としての対向電極及び薄膜を備える電気的デバイスを示す説明図である。

20

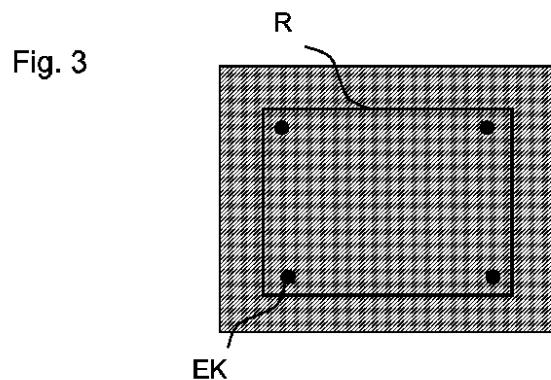

【図3】電気的接点を包囲するフレームを備える電気的デバイス示す平面図である。

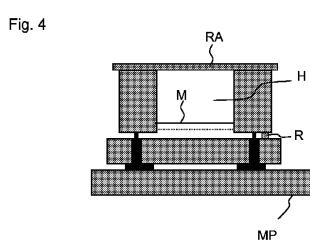

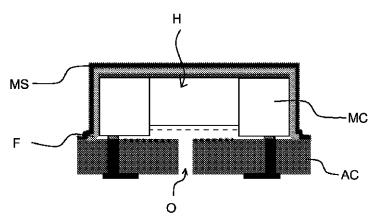

【図4】取付プレート上に配置した電気的デバイスを示す説明図である。

【図5】カバー又は弾性壁を有するMEMSチップを備える電気的デバイスを示す説明図である。

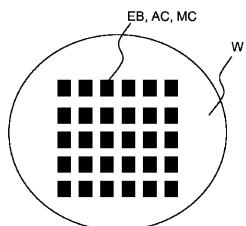

【図6】電気的デバイス、ASICチップ又はMEMSチップを配置したウェハを示す説明図である。

【図7】上側チップを被覆するフォイルを備える電気的デバイスを示す説明図である。

【図8】ASICチップに配置した開口を備える電気的デバイスを示す説明図である。

#### 【発明を実施するための形態】

30

#### 【0064】

図1は、MEMSチップMC及びASICチップACを備える電気的なMEMSセンサデバイスEBを示す。MEMSチップMCは、上側面OSM及び下側面USMを有する。図示の実施形態及び他の実施形態において、下側面とはデバイスの電気的外部接続端子EEAに指向する側の側面を指すものであり、これら電気的外部接続端子EEAは、図面の下側チップの下側面に存在する。ASICチップACも同様に上側面OSA及び下側面USAを有する。MEMSチップMCは、その下側面USMがASICチップACの上側面OSAに対面するよう配置する。MEMSチップMCはその下側面に配置した電気的接点EKを有し、ASICチップはその上側面OSAに配置した電気的接点EKを有する。MEMSチップの下側面における電気的接点は、ASICチップの上側面における電気的接点に接続し、電気的デバイスEBにおける集積回路IVの少なくとも一部を構成する。

40

#### 【0065】

ASICのデバイス構造は、図示の実施形態だけでなく他の実施形態においても電気的外部接続端子EEAを有する側の側面、又は好適にはMEMSチップに対面する側の側面に配置することができる。

#### 【0066】

ASICチップACの内部にはビアDKを配置する。これらビアDKは、電気的接点の1個又は複数個、又は内部接続部をASICチップの下側面に配置した電気的外部接続端子EEAに接続する。デバイスEBは、1個又は複数個の電気的外部接続端子を備えることができる。これら1個以上の電気的外部端子により、デバイスEBを外部周辺回路(図

50

示せず)に接続することができる。

**【0067】**

MEMSチップMC及びASICチップACの電気的接点EKは、できるだけ最短経路で互いに接続する。これにより、電気的デバイスにおける妨害感受性が低減する。さらに、上述したMEMSチップMC及びASICチップACの配置及び接続により、構造寸法が小さいコンパクトな電気的デバイスが得られる。

**【0068】**

図2は、電気的デバイスの一実施形態を示し、この場合の電気的デバイスは、デバイス構造として対向電極RP(英語では"Backplate"とも称する)及び薄膜Mを備える。さらに図示の実施形態においては、MEMSチップを貫通するビアを設け、これにより、MEMSチップの上側面に配置したデバイス構造BSが、内部接続部及びASICチップを貫通するビアを介して、ASICチップの下側面におけるデバイスの電気的外部端子EEAに接続される。

**【0069】**

MEMSチップMCとASICチップACとの間に隙間を設け、この隙間の高さは、MEMSデバイスとASICチップとの間における距離を決定する。環状に閉じたフレームRは、チップ間で隙間を包囲する。例えば対向電極RP及び薄膜MがMEMSマイクロフォンの容量素子における2個の電極として機能する場合、フレームRによりハーメック(気密)シールされた背面容積部がMEMSチップ内部、及びMEMSチップとASICチップとの間に生ずる。

**【0070】**

MEMSチップは、デバイス構造BSとして可動薄膜M及び対向電極RPとしてのバックプレートを有し、これら可動薄膜M及びバックプレートが一緒にマイクロフォンの容量素子KEを構成する。

**【0071】**

図3は、ASICチップの上側面に対して平行に切断した電気的デバイスの横断面を示す。図示の実施形態における電気的デバイスにおいては、フレームRにより電気的デバイスにおける内部接続部の一部を構成する電気的接点EKが環状に包囲される。この場合の「環状」という表現は、フレームの幾何学的形状に関連するものではなく、閉じた曲げ線に関連する。

**【0072】**

図4は電気的デバイスを示し、この場合の電気的デバイスは取付プレートMP上に配置し、電気的接点により取付プレートMPの上側面に接続する。このような配置により、電気的デバイスを外部接続部に接続することが可能となる。

**【0073】**

MEMSチップ内部には、中空空間Hを配置する。この中空空間Hを一方の側面をデバイス構造で区切り、例えば、薄膜Mを配置する。マイクロフォンの中空空間における他方の側面は、背面側のカバーRA、例えばPIフォイルで被覆する。この背面側のカバーRAには、例えばセラミック、シリコン、金属又はガラス製のプレートを使用してもよい。

**【0074】**

図示の実施形態においては、完全には閉じていないフレームを上側チップと下側チップとの間に配置する。図面の右側にフレームの縦断面を示す。図面の左側はフレームの一部が欠落しているため、この箇所にはセンサ開口、例えば音波進入口が形成される。これにより、音波がチップ間における電気的接続部の間からデバイス内又は両チップが形成する中空空間内に進入できる。このようにして側面にセンサ開口(例えば音波進入口としての)を有する電気的デバイスが構成される。

**【0075】**

図5が示す電気的デバイスにおいては、MEMSチップMCとASICチップACとの間に隙間Sを設ける。図示の実施形態において、ビアDKはMEMSチップだけでなく、このMEMSチップMCの背面側におけるカバーRAをも貫通している。カバーRAは弾

10

20

30

40

50

性変形可能と共に電気的な抵抗素子を有することができ、これら電気的な抵抗素子の電気抵抗は背面側のカバーのに依存する。これら抵抗素子は、カバーの上側面に取り付けるか又はカバーの上側面内に埋設することができる。ピア D K はカバーを貫通するため、抵抗素子を内部接続部に接続することができる。

#### 【0076】

図6はウェハWを示し、ウェハWの上側面に多数の電気的デバイス、ASICチップAC又はMEMSチップMCを互いに隣接して配置する。電気的デバイス、ASICチップ又はMEMSチップはウェハに取り付けるか、又は共に平行に製造しウェハに組み込むことができる。個々のチップは、同時に量産することができる。ASICチップを配置したウェハはその製造後、MEMSチップMCを配置したウェハに結合することができ、この結合においては、各1個のASICチップが各1個のMEMSチップに結合される。個々のチップは、対応するチップに結合する前に又は結合した後にばらばらに切り出すことができる。有利には、先ず他のチップを有するウェハを結合し、その後完成した電気的デバイスを切り出す。

10

#### 【0077】

図7に示す実施形態において、上側チップMCは、フォイルF及びメタライジング層MSによる封入カプセルを有する。フォイルは上側チップの上側面及び側面を被覆し、下側チップの上側面の領域で密封する又は下側チップの側面で密封する。フォイルは、積層により形成することができる。MEMSチップMC内部の中空空間は、フォイルを積層する前に背面側のカバーRPで被覆してもよく、これにより積層フォイルが積層に際して中空空間H内に入り込むのを回避する。封入カプセルは、チップ間に設けた隙間をハーメチック（気密）シールする又は少なくとも外部に対して音響的に遮音する。このような被覆は、両チップを互いに結合した後に行うことができる。

20

#### 【0078】

図示の実施形態において、センサ開口OはASICウェハを貫通して設けるが、代替的にはセンサ開口はフォイルF及びメタライジング層MSを貫通して封入カプセルに設けてもよく、この場合、センサ開口は特に事後に設ける。両チップ間にはフレームRを設けることができ、このフレームRは両チップ間における距離、従って両チップ間における容積をも決定する。

30

#### 【0079】

図8は、マイクロフォンとしての電気的デバイスの実施形態を示し、MEMSチップMCはASICチップACの上方に配置する。両チップMC, AC間には、隙間を設ける。この隙間にはフレームRを配置し、フレームRはデバイス内部を少なくとも側方方向を音響的に遮蔽する。MEMSチップのデバイス構造は、有孔対向電極（Backplate）及び薄膜を含む。開口OはASICチップを貫通し、音波流入開口として機能する。ASICチップの上側にはデジタル回路及び/又はアナログ回路を配置し、MEMSチップのデバイス構造に接続する。

#### 【0080】

MEMSチップ、ASICチップ及び場合によってはこれらチップ間に配置するフレームは、側方方向に面一となるように配置する。このような「平坦な」側壁は、多数のMEMSチップ及びASICチップを多面取り用に製造した後、個々のデバイスを例えばソーリングにより切り出す前に両チップを互いに結合することによって形成することができる。図示の実施形態においても、付加的に保護金属層及び場合によってはこの金属層の下に配置する絶縁層を設けることができる。

40

#### 【0081】

本発明による電気的デバイスは上述した実施形態に限定されるものではなく、例えば付加的なチップ、別のデバイス構造又は別の電気的接点を含む代替案、及びこれらを任意に組み合わせた代替案も、本発明による実施形態に含まれるものである。

#### 【符号の説明】

#### 【0082】

50

|              |                              |    |

|--------------|------------------------------|----|

| A C          | A S I C チップ                  |    |

| B S          | デバイス構造                       |    |

| R A          | カバー                          |    |

| D K          | ビア                           |    |

| E B          | M E M S センサデバイス              |    |

| E E A        | 電気的外部接続端子                    |    |

| E K          | 電気的接点                        |    |

| I C          | 集積回路                         |    |

| I V          | 内部接続部                        |    |

| K E          | 静電容量素子                       | 10 |

| M            | 薄膜                           |    |

| M C          | M E M S チップ                  |    |

| M P          | 取付プレート                       |    |

| O            | 開口                           |    |

| O S M, O S A | M E M S チップ及びA S I C チップの上側面 |    |

| R            | フレーム                         |    |

| R P          | 対向電極 ( Backplate )           |    |

| S            | 隙間                           |    |

| H            | 中空空間                         |    |

| W            | ウェハ                          | 20 |

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

Fig. 5

【図6】

Fig. 6

【図7】

Fig. 7

【図8】

Fig. 8

---

フロントページの続き

(72)発明者 ハンス クルガー

ドイツ国 81737 ミュンヘン ペラローシュトラッセ 13

(72)発明者 ウォルフガング ポール

ドイツ国 81379 ミュンヘン ルーベルト マイヤー シュトラッセ 6

(72)発明者 アントン ライドル

ドイツ国 85662 ホーエンブルン ブレンネライシュトラッセ 16

審査官 間中 耕治

(56)参考文献 米国特許出願公開第2009/0101998(US,A1)

(58)調査した分野(Int.Cl., DB名)

B 81 B 1 / 00 - 7 / 04

B 81 C 1 / 00 - 99 / 00

H 04 R 19 / 04