(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特願2004-40701

(P2004-40701A)

(43) 公開日 平成16年2月5日(2004.2.5)

(51) Int.C1.<sup>7</sup>

F 1

テーマコード(参考)

H03M 13/29

H03M 13/29

5B001

G06F 11/10

G06F 11/10 320C

5J065

H03M 13/23

G06F 11/10 330N

H03M 13/41

G06F 11/10 330S

H03M 13/23

審査請求有 請求項の数 7 O L (全 14 頁) 最終頁に続く

(21) 出願番号

特願2002-198435 (P2002-198435)

(22) 出願日

平成14年7月8日(2002.7.8)

(71) 出願人 301022471

独立行政法人通信総合研究所

東京都小金井市貫井北町4-2-1

(74) 代理人 100090893

弁理士 渡邊 敏

(72) 発明者 季 還幫

東京都小金井市貫井北町4-2-1 独立行政法人通信総合研究所内

F ターム(参考) 5B001 AA01 AA10 AA13 AB05 AC02

AE07

5J065 AA01 AB01 AC01 AD01 AE06

AF03 AG05 AH01 AH06

(54) 【発明の名称】 トレス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法

## (57) 【要約】

【課題】ビット誤り率の改善を図りながら、計算量・メモリ量を抑制したトレス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法を提供する。

【解決手段】トレスに基づくビタビ復号と、パリティ検査に基づく繰り返し復号とからなり、パリティ検査においてエラーが検出された時に、該エラーの生じたブランチを通るすべてのパスを削除し、再び該エラーの生じたブランチの直前のスタートからパスの決定処理を行う。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

トレリスに基づくビタビ復号と、パリティ検査に基づく繰り返し復号とからなる、トレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法において、

該ビタビ復号が、

該トレリス構造のパスの決定に、最大尤度を用いて生き残りパスの決定処理を行うと共に、該生き残りパスを記憶する構成であって、

パリティ検査においてエラーが検出された時に、

該エラーの生じたブランチを通るすべてのパスを削除し、

再び該エラーの生じたブランチの直前のスタートからパスの決定処理を行う

ことを特徴とするトレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法。

**【請求項 2】**

前記トレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法において、

パリティ検査においてエラーが検出された時に、

該エラーの生じたブランチのブランチメトリックを重み付けすることによって

該ブランチを通るすべてのパスを削除する

請求項 1 に記載のトレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法。

**【請求項 3】**

前記ブランチメトリックに 2 乗ユークリッド距離を用いると共に、ブランチのブランチメトリックを増加させてエラーブランチを通るすべてのパスを削除する請求項 2 に記載のトレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法。

**【請求項 4】**

前記トレリス構造を有する符号化方式が、

時間と共に変化する単位デジタル信号に対応する要素の集合からなる符号ブロック構造を有する

請求項 1 ないし 3 に記載のトレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法。

**【請求項 5】**

前記符号ブロックの要素を X 方向に配列すると共に、異なる符号ブロックを Y 方向に配列することによって形成される行列であって、

X 方向のブロックについては、ブロック符号化変調の操作を行い、

異なる符号ブロックの要素を 1 つずつ含む列のビット列については当該列についてのパリティ検査符号をさらに付加し、

該パリティ検査符号を用いたエラー検出を行う

請求項 4 に記載のトレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法。

**【請求項 6】**

前記符号ブロック構造におけるパリティ検査符号の付加を、

ブロック符号化変調 (B C M) 方式に対して付加する

請求項 4 又は 5 に記載のトレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法。

**【請求項 7】**

前記符号ブロック構造におけるパリティ検査符号の付加を、

多重ブロック符号化変調 (M B C M) 方式に対して付加する

請求項 4 又は 5 に記載のトレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法。

10

20

30

40

50

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、トレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法に係り、より詳しくは生き残りパスの決定後、エラーが検出されたときに再度次の生き残りパスを決定する手法に特徴を有するトレリスに基づくビタビ復号とパリティ検査に基づく繰り返し復号の連接復号の方法に関するものである。

**【0002】****【従来の技術】**

近年、デジタル信号の符号化変調方式の1つとして、パーシャルレスポンス方式によって波形等化を行い、最尤復号方式によってデータの検出を行うトレリス符号化変調方式などのトレリス構造も持つ符号化方式が開発されている。10

このような符号化変調方式は、特に磁気ディスク装置や磁気テープ装置などの磁気記録再生装置や、デジタル通信での誤り率特性を改善することができる極めて重要な技術である。。

**【0003】**

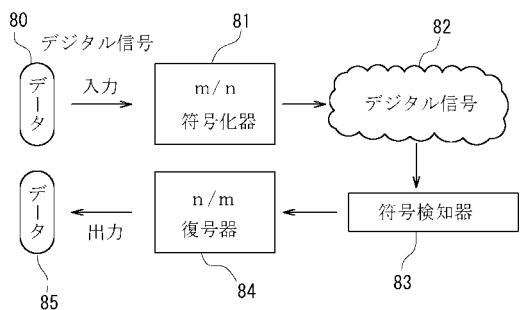

トレリス符号化変調などのトレリス構造も持つ符号化方式は、ガウス雑音通信路において、最尤復号として効率の良いビタビ復号が行える特徴を有する。図8には一般的なデジタル通信における信号処理の構成を示す。

デジタル信号の入力データ(80)は、 $m/n$ 符号化器(81)で符号化される。該符号化器(81)において、入力データ(80)のデータビット長をm、符号のデータビット長をnとすると、このとき、 $m:n$ の比で出力される。20

**【0004】**

デジタル通信(82)においてデジタル信号は伝送された後、例えば最尤検出器などの符号検出器(83)により符号検出される。さらに、 $n/m$ 復号器(84)において前記 $m/n$ 符号化器(81)と逆に $n:m$ の比で復号される。

出力データ(85)が該復号器(84)から出力されることで、一連の信号処理が終了する。

**【0005】**

上記符号検出器(83)における尤度計算を利用する手法として、符号化規則を用いるのが、トレリス符号化変調方式であり、該方式によれば、信号の最尤検出を行う際のプランチメトリックを上昇させることにより符号誤り率を低減させることができる。30

**【0006】**

また、上記 $n/m$ 復号器ではビタビ復号方法により復号処理が行われる。ビタビ復号では、復号候補系列はトレリス上のパスと1対1の関係にあり、復号系列を特定することはトレリス上のパスを特定することになる。パスを特定するために、パスの間でパスメトリックを比較することによって、生き残りパスを決定する。ビタビ復号方法は符号化利得の向上を図る上で有効な方法である。

**【0007】**

このようなビタビ復号方法を用いたブロック符号化変調の誤り率特性を改善する手法として、例えば本件出願人による特願2000-382212に開示された方法がある。40

すなわち、パリティ失敗したときに、パリティ検査符号の特徴からいはずれか1つのブロックで誤りが生じたことが判る。各ブロックにおいて現在の生き残りパスに続くパスメトリックを有するパス(次候補パス)を求め、現在の生き残りパスと次候補パスのメトリックの差を求める。

この差が一番小さいものは誤りを起こした確率が一番大きいので、誤りを起こしたブロックと特定する。

**【0008】**

次候補パスを選ぶ際、パリティ失敗した縦の列の各ブランチの直後のステートにおいて、1つのステートに入るすべてのパス(BCMでは4、MBCMでは8)から、誤った現在50

の生き残りパスに代わるパスを選ぶ必要がある。

ここで、該開示によれば、代わりのパスを選ぶ際、例えばB C Mでは4つ(M B C Mでは8つ)のパス全てをあらかじめ記憶しておき(これを冗長ビタビ復号と呼ぶ。)、1番目が誤ったら2番目、2番目が誤ったら3番目といった簡単な作業で、誤ったブランチでの代わりのパスが得る方法を提供している。

そして次ステートから冗長ビタビ復号を行い、次復号候補系列を得る。

#### 【0009】

このような従来の手法では、符号化利得の向上と共に、復号に要する時間の短縮を図ることができる一方、1つのブランチに入るすべてのパスをメトリックの順に記憶する必要があるため、余分の計算量と記憶領域(メモリ)が要される問題があった。

10

#### 【0010】

##### 【発明が解決しようとする課題】

本発明は上記従来の技術が有する問題に鑑みて創出されたものであって、ビット誤り率の改善を図りながら、計算量・メモリ量を抑制したトレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法を提供することを目的とする。

#### 【0011】

##### 【問題を解決するための手段】

上記の目的を達成するために、本発明のトレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法は、以下の特徴を備える。

20

まず本発明が対象とするのは、トレリスに基づくビタビ復号と、パリティ検査に基づく繰り返し復号とからなる、トレリス構造を有する符号化方式とパリティ検査符号による連接符号化方式の復号方法である。

そして、このビタビ復号が、トレリス構造のパスの決定に、最大尤度を用いて生き残りパスの決定処理を行うと共に、該生き残りパスを記憶する構成であって、パリティ検査を用いてエラーが検出された時に、該エラーの生じたブランチを通るすべてのパスを削除し、再び該エラーの生じたブランチの直前のステートからパスの決定処理を行う。

#### 【0012】

ここで、トレリス構造のパスの決定に、最大尤度を用いて生き残りパスの決定処理を行うと共に、該生き残りパスを記憶する構成であって、パリティ検査を用いてエラーが検出された時に、該エラーの生じたブランチのブランチメトリックを重み付けすることによって該ブランチを通るすべてのパスを削除し、再び該エラーの生じたブランチの直前のステートからパスの決定処理を行う構成をとることもできる。

30

#### 【0013】

上記いずれかの構成において、ブランチメトリックとして、2乗ユークリッド距離(Euclidean squared distance)を用いることもできる。

#### 【0014】

本発明が対象とするトレリス符号化変調方式などのトレリス構造を有する符号化方式が、時間と共に変化する単位デジタル信号に対応する要素の集合からなる符号ブロック構造を有する構成でもよい。

40

#### 【0015】

前記符号ブロックの要素をX方向に配列すると共に、異なる符号ブロックをY方向に配列することによって形成される行列であって、X方向のブロックについては、ブロック符号化変調の操作を行い、異なる符号ブロックの要素を1つずつ含む列のビット列については当該列についてのパリティ検査符号をさらに付加し、該パリティ検査符号を用いたエラー検出を行う構成でもよい。

#### 【0016】

本発明が対象とする前記トレリス構造を有する符号化方式が、時間と共に変化する単位デジタル信号に対応する要素の集合からなり、パリティ検査符号が、ブロック符号化変調(B C M)方式に対して付加された構成でもよい。

50

#### 【0017】

あるいは、符号ブロックのパリティ検査符号が前記B C M方式によるものであって、符号ブロックの要素をX方向に配列すると共に、異なる符号ブロックをY方向に配列することによって形成される行列であって、X方向のブロックについては、ブロック符号化変調の操作を行い、異なる符号ブロックの要素を1つずつ含む列のビット列については当該列についてのパリティ検査符号をさらに付加し、該パリティ検査符号を用いたエラー検出を行う構成でもよい。

#### 【0018】

前記符号ブロック構造におけるパリティ検査符号の付加が、上記ブロック符号化変調（B C M）方式ではなく、多重ブロック符号化変調（M B C M）方式である構成でもよい。

#### 【0019】

**【発明の実施の形態】**

本発明の実施形態を図面に示した実施例に基づいて説明する。なお、実施形態は、本発明の主旨から逸脱しないかぎり適宜変更可能なものである。

ここでは、本発明の1実施形態として、トレリス構造を有するブロック符号化変調における符号の復号を示す。まず、一般的なブロック符号化変調について説述する。

#### 【0020】

ブロック符号化変調は予め決められたビット数ごとにまとめてブロック化し、それぞれのブロックごとにブロック符号化変調の操作を行うものである。

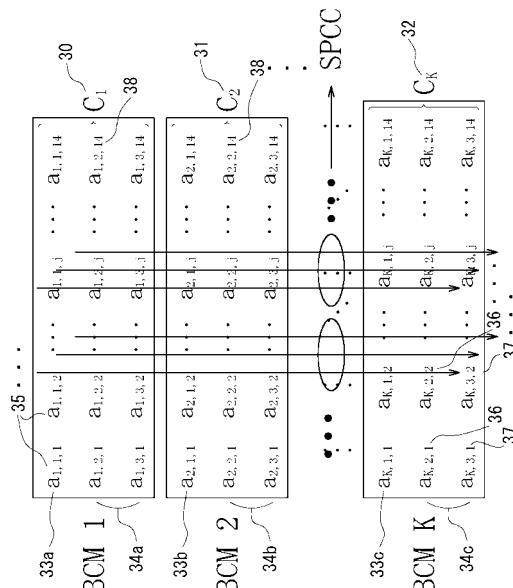

図1には符号長が7のブロック符号化変調（B l o c k - c o d e d m o d u l a t i o n s o f t r e l l i s s t r u c t u r e、B C M - T S）の符号化器（図8において示される81）のビットマトリクス及びシンボルの生成方法を示す。ブロック符号化変調（B C M - T S）では、まず入力ビットを所定の符号化規則に従ってマトリクス状（10）に配列する。

本ビットマトリクス（10）において、それぞれの行<sub>1</sub>（11）、<sub>2</sub>（12）、<sub>3</sub>（13）を符号レベルと呼ぶ。

#### 【0021】

ビットマトリクス（10）の縦の一列を1つのシンボルに対応させる。シンボルの伝送に、例えばP S K（P h a s e S h i f t K e y i n g）方式を用いると、3ビットのシンボルの変調であるから、8-P S Kを用いることになる。

図1においてシンボル（14）はS<sub>1</sub>からS<sub>7</sub>である。

#### 【0022】

また、本実施例における上記符号化規則によると、データビットa<sub>1</sub>～a<sub>14</sub>（15）（15）…は図1のように配列されており、C（16）はl<sub>2</sub>（12）におけるパリティ検査ビット（パリティ検査符号）である。パリティとしては公知のように偶数パリティ・奇数パリティがあり、例えば偶数パリティにおいては、数式1を満たすようにC（16）が決定される。

#### 【0023】

#### 【数式1】

$$C = a_2 \oplus a_3 \oplus a_4 \oplus a_5 \oplus a_6 \oplus a_7$$

但し、⊕ は排他的論理和

#### 【0024】

l<sub>1</sub>とl<sub>2</sub>はそれぞれ符号長7の重複符号であるものと、パリティ検査符号を用いたものであるため、それぞれの符号レベルにおける7ビットについてのハミング距離を<sub>1</sub>と<sub>2</sub>で表すと、<sub>1</sub>=7、<sub>2</sub>=2となる。

10

20

30

40

50

$l_3$  は符号操作を行わないとき、そのハミング距離  $d_3 = 1$  である。

【0025】

8-P SKに対するセット分割を用いたときに  $l_1 \sim l_3$  に対応する信号点セットにおける最小信号点間の距離の2乗は、それぞれ  $d_1 = 4 \sin^2(\pi/4)$ 、 $d_2 = 2$  及び  $d_3 = 4.0$  で与えられる。また、各符号レベルにおける最小2乗ユークリッド距離は数式2により求められる。

【0026】

【数式2】

$$\begin{cases} D_1^2 = \delta_1 \times d_1 \approx 4.1 \\ D_2^2 = \delta_2 \times d_2 = 4.1 \\ D_3^2 = \delta_3 \times d_3 = 4.0 \end{cases}$$

10

【0027】

従って、このブロック符号化変調 (BCM-TS) の最小2乗ユークリッド距離は 4.0 である。ここで、図1の7つのシンボル(14)の中に、14のデータビット(15)・・が含まれているので、伝送効率は 2 bits / symbol である。

20

また、同じ伝送効率を有するQPSK変調(4-P SK変調)と比較すると、このブロック符号化変調(BCM-TS)は 3dB の漸近符号化利得(2乗ユークリッド距離の比)を得ている。

【0028】

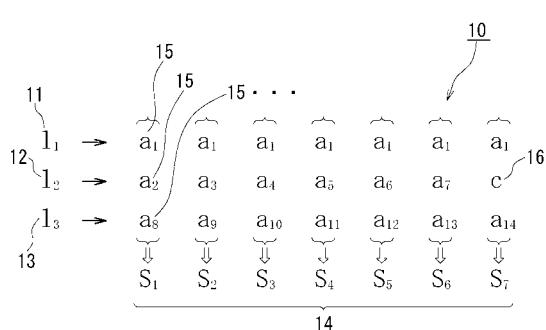

図1のブロック符号化変調に対応するトレリス線図を図2に示す。トレリスの各ブランチのラベルを示している数値 0, 1, 2, ..., 7 (20) (20) ... は 8-P SK の 8 つの信号点を表す。

このトレリス線図は自動的に収束(21)しているので、打ち切りなどの終結操作が必要としないビタビ復号が行える。

【0029】

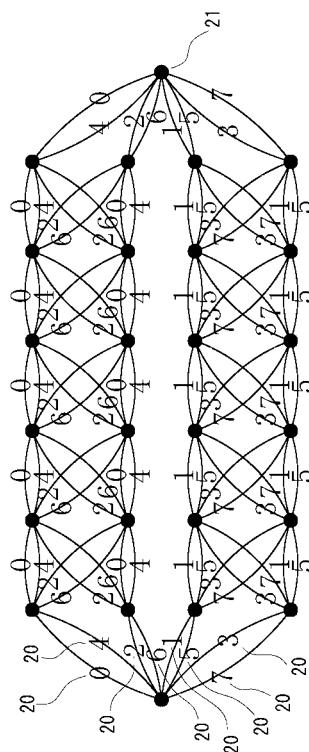

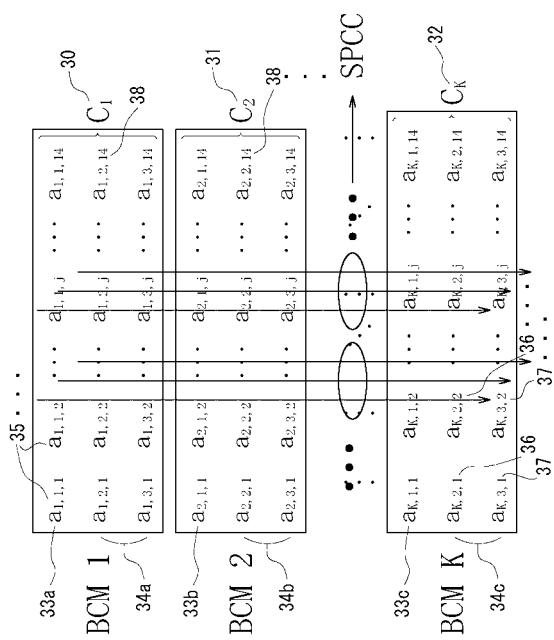

ここで、ブロック符号化変調の誤り率特性を改善するために、図3に示すように上記のブロック符号化変調を以下に説明する様にブロック符号化変調とパリティ検査符号による連接符号を構成する。ブロック符号化変調 (BCM-single parity check codes 以下、単に BCM-SPCC と呼ぶ。) ものを K 個用い、その図3横方向の BCM と縦方向のパリティ検査符号とを行うように組み合わせた 2 次元的な符号化構成を用いたものを考える。

30

【0030】

図3の構成において、横の各符号化変調  $C_1, C_2, \dots, C_K$  をそれぞれ 1 つの符号ブロック(30)(31) ... (32) と呼ぶ。これらの符号ブロック(30)(31) ... (32) は全て同じ構造を持ち、また、符号長を 2 倍にしたことを除いて上記例のブロック符号化変調のビットマトリクス(10)と同じ構造を有する。すなわち、各符号ブロック  $C_k$  ( $k = 1, 2, \dots, K$ ) において、次の数式3の関係が成立する。

40

【0031】

【数式3】

$$\begin{cases} a_{k,1,1} = a_{k,1,2} = \cdots = a_{k,1,14} \\ b_{k,2,14} = b_{k,2,1} \oplus b_{k,2,2} \oplus \cdots \oplus b_{k,2,13} \end{cases}$$

## 【0032】

したがって、各符号ブロック(30)(31)…(32)における一番上の符号レベル

$l_{k,1}$  ( $k = 1, 2, \dots, K$ ) (33a) (33b) (33c) に長さ14の重複符号が用いられ、ハミング距離は14である。よって、各符号レベル $l_{k,1}$  (33a) (33b) (33c) の2乗ユークリッド距離は元ブロック符号化変調における符号レベル $l_1$  (11)のその2倍となった。一方、各符号ブロックにおける他の2つの符号レベル(34a) (34b) (34c)は、元ブロック符号化変調の対応する符号レベル(12) (13)と同じ2乗ユークリッド距離を有する。10

## 【0033】

各符号ブロックにおいて、符号レベル $l_{k,1}$  (33a) (33b) (33c) は符号レベル $l_{k,2}$  および符号レベル $l_{k,3}$  (34a) (34b) (34c) よりも大きい2乗ユークリッド距離を有することは、符号レベル $l_{k,1}$  (33a) (33b) (33c) にあるビットが符号レベル $l_{k,2}$  および符号レベル $l_{k,3}$  (34a) (34b) (34c) にあるビットよりも信頼度が高いことを意味する。このことを利用して、以下に述べる縦方向のパリティ検査を行うとき、符号レベル $l_{k,1}$  にあるビット(35)…をパリティ検査から外すことができ、パリティビット当たりの効果を高くすることができる。20

## 【0034】

ここで、以下の数式4と数式5で示される縦方向のパリティ検査符号(36)…(37)…を考える。縦の1列に対して2つのパリティ検査ビットを用いるものとする。たとえば、図3において、第K個の符号ブロックの符号レベル $l_{k,2}$ と $l_{k,3}$ にあるビットをパリティ検査ビットとして用いることにする。ただし、符号レベル $l_{k,2}$ と $l_{k,3}$ にあるビットはそれぞれ各符号ブロック(30)(31)…(32)の $l_{k,2}$ と $l_{k,3}$  ( $k = 1, 2, \dots, K$ )にあるビットに対して、パリティ検査符号の操作を数式4と数式5で示されるように行う。30

## 【0035】

## 【数式4】

$$a_{k,2,j} = a_{1,2,j} \oplus \cdots \oplus a_{K-1,2,j}; \quad j = 1, 2, \dots, 13$$

40

## 【0036】

## 【数式5】

$$a_{k,3,j} = a_{1,3,j} \oplus \cdots \oplus a_{k-1,3,j}; \quad j=1, 2, \dots, 14$$

## 【0037】

ここで、数式4は前13列においてパリティ検査符号の操作を行っているが、第14列目ではパリティ検査符号の操作が行われていない。これに対して、数式5は全ての14列においてパリティ検査符号の操作を行っていることに注意されたい。これは符号レベル $l_{k,2}$ の最後のビット $a_{k,2,14}$ (38)(38)…は第K個の符号ブロックにおけるブロック符号化変調の条件を満たすために、符号レベル $l_{k,2}$ のパリティ検査ビットとして用いられる必要があるからである。すなわち、これらは次の数式6の関係を持っている。

## 【0038】

## 【数式6】

10

$$a_{k,2,14} = a_{k,2,1} \oplus a_{k,2,2} \oplus \cdots \oplus a_{k,2,13}$$

20

## 【0039】

次に本発明によるブロック符号化変調とパリティ検査符号による連接符号化方式の復号方法について説述する。

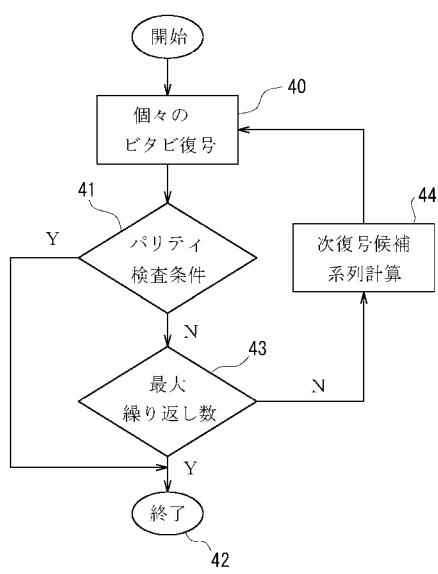

図4には提案するビタビ復号とパリティ検査に基づく繰り返し復号による連接復号のフロー チャートを示す。まず、各符号ブロック(30)(31)…(32)において横方向のビタビ復号を行う(40)。

ビタビ復号は、図2のトレリス線図の長さを7シンボルから14シンボルに増やしたものを使って行われる。以下でも、説明の簡略化のために7シンボルのトレリス線図を用いて説述する。

## 【0040】

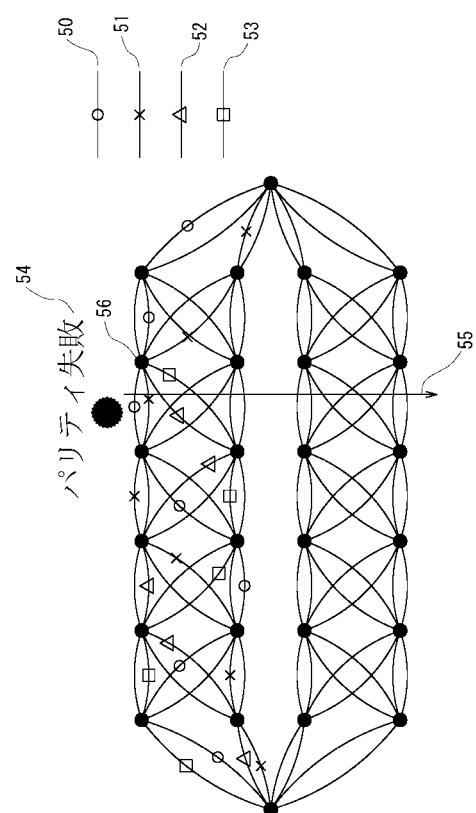

ここで、本件出願人が特願2000-382212に開示した方法では、図5に示すようにビタビ復号を行うときに、各々のステートに入るすべてのパスのパスメトリックを記録しておき、例えばステート(56)において最大尤度を有するパス(50)だけでなく、2番目のパス(51)、3番目のパス(52)、4番目のパス(53)を記録していた。(この方法を冗長ビタビ復号と呼ぶ。)

一方、本件発明によれば記憶するのは最尤パス(50)だけで十分であり、全てのパスを記憶する必要はない。

## 【0041】

ビタビ復号方法において、復号を行ったとき、各符号ブロックC1、C2、…CK(30)(31)…(32)で得られた最初の復号系列は全て最尤系列である。該最尤系列から復号後のビット系列が得られ、それは図1における変調前のビットマトリクス(10)と同様の行列である。

## 【0042】

ここで、このビット系列において縦方向における2つのパリティ検査ビットによる符号操

30

40

50

作に対するパリティ検査を行う。該検査については上記数式4と数式5に示した式を満たすか否かにより判定する。

全ての列におけるパリティ検査条件(41)が満たされれば、上記最尤系列を最終の復号結果とし、終了(42)する。

#### 【0043】

ここで、図5においてパリティ失敗(54)が生じ、あるj列目(55)を最初に検出されたパリティ検査条件が満たされない列と仮定すると、用いられたパリティ検査符号は全て単一パリティ検査符号なので、一般性を失うことなく、そのパリティ検査符号に含まれているビットの中は、1つのビットだけが誤っていると推測できる。従って、エラービットがある符号ブロックを検出することは正しく復号する上で極めて重要である。

10

#### 【0044】

従来の方法によれば、まず、各符号ブロックにおいて、それぞれパリティ失敗したプランチの直後のステート(56)において、記憶した複数個のパス(51)(52)(53)から現パス(50)に続くメトリックを有するパス(51)を選び、これをもって残りの冗長ビタビ復号を行い、次復号候補系列を得る。

次に、各符号ブロックにおいて得られた、それぞれの次復号候補系列(51、長さ7)と先の復号候補系列(50、長さ7)のパスメトリックの差を求め、この差が最も小さいものが、最も誤っている可能性が高く、該符号ブロックが誤ったビットを含んでいるとする。該符号ブロックは次復号候補系列(51、長さ7)を新たな復号系列として用い、再びパリティ検査を行う。この組み合わせを最大N回(Nは任意)まで繰り返し、その間に、1つの復号過程において縦方向のパリティ検査条件が全て満たされればその次点で復号を終了させる。

20

#### 【0045】

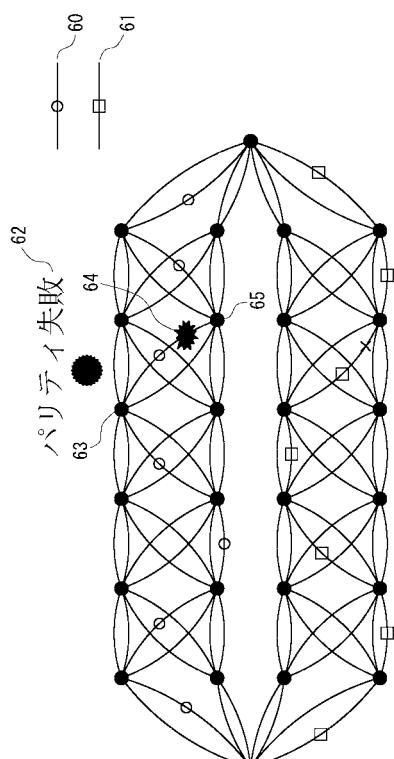

これに対し、本発明では2番目のパス以降について記憶することなく、図6に示すトレリス線図のように、最尤系列(60)の途上でパリティ失敗(62)が発生したとき、その直前のステート(63)に戻り、最尤系列(60)におけるパリティ失敗プランチ(64)を削除した上で再計算を行うようにする。

30

#### 【0046】

削除する方法は、符号化変調方法により任意に決めることができるが、例えば本実施例で2乗ユークリッド距離をプランチメトリックとして用いた場合、単にプランチ(64)のプランチメトリックを大きくして、該プランチ(64)を通らないような次復号候補系列(61)を求めればよい。

30

この次復号候補系列計算(44)及びビタビ復号(40)、パリティ検査(41)を最大N回(Nは任意)まで繰り返し(43)、その間に、1つの復号過程において縦方向のパリティ検査条件が全て満たされればその次点で復号を終了(42)させる。

40

#### 【0047】

本発明は上記の通りBCMに用いることもできるが、多重ブロック符号化変調(multicode BCM、以下、MBCMと呼ぶ。)方式に用いてもよい。BCMにおいては図1に示されるように、パリティ検査ビットC(16)が数式1によって決められ、符号レベル<sub>12</sub>のみにパリティ検査ビットを用いているが、MBCMにおいては、図9に示すように符号レベル<sub>12</sub>ないし<sub>14</sub>に同様の算出方法によるパリティ検査ビットを配置する。

#### 【0048】

BCMとMBCMの違いは、1つのプランチにおいてMBCMではBCMの2倍のシンボルが生成される点であり、図2のようにBCMでは4つのプランチを有するステートが、MBCMでは8つのプランチを有するステートから構成されるトレリス線図を得ることができる。

#### 【0049】

なお、本発明の実施においては任意のトレリス構造を持つ任意の符号化方式を用いることができることは明らかであり、上記と同様の手順により実現できる。ただし、周知のように、トレリス変調(TCM)を用いた場合、TCMに対するビタビ復号では、トレリスの

50

終結操作が必要である。このように、符号の特徴に応じた追加的な処理を行うことはできるのは言うまでもない。

#### 【0050】

ここで、本発明と従来の復号方法を比較してみる。例えば、本発明では、 $j$ 列目の1つのステートに入るブランチの数がMのとき、最大尤度を有する生き残りパスの決定には $M - 1$ 回の比較演算が必要である。

一方、上記冗長ビタビ復号を用いた従来の方法によると、1つのステートに入るすべてのパスを尤度の順に記憶する必要があるため、所要の比較演算の総回数は、 $M(M - 1) / 2$ 回となる。

#### 【0051】

従って、本発明では従来の $2 / M$ 倍の比較演算で済むため、計算にかかる負荷を抑制することができる。また、従来の方法では、1つのステートに入るすべてのパスとそれらのパスメトリックおよびパスが通る直前のステートを記憶しておく必要があるのに対し、本発明では、最尤パスとそのパスメトリックのみを記憶すればよいので、必要な記憶ユニットが $2 / 3 M$ 倍で済む。

例えば、図2で示したような4つのブランチを有する4・ステートトレリス線図で比較してみると、1つのステートにおいて、比較演算は従来の方法では6回、本発明では3回となる。また、各ステートにおいて従来の方法では6倍の記憶領域が必要となる。

#### 【0052】

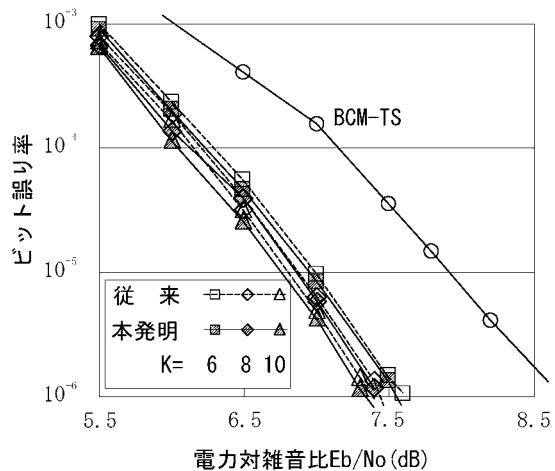

図7には符号ブロックの数Kとビット誤り率の関係をグラフで表す。複数のグラフは、符号ブロックが1つである従前のブロック符号化変調(BCM-TS)と、上記冗長ビタビ復号を用いた従来の方法(符号ブロック数Kが6, 8, 10の各場合)と、BCM方式で本発明を用いた復号方法(符号ブロック数Kが6, 8, 10の各場合)を示している。

#### 【0053】

図7において、縦軸はビット誤り率、横軸はデータビット当たりの電力対雑音比 $E_b / N_0$ である。いずれのグラフにおいても $E_b / N_0$ が大きいとき、ビット誤り率の改善がみられるが、冗長ビタビ復号方法・本発明による復号方法がともに、小さいビット誤り率を与えることがわかる。

#### 【0054】

また、特筆すべきは従来の冗長ビタビ復号と本発明による復号方法が、ビット誤り率特性において変わらないか、又は改善が見られる点であり、本発明が計算量、必要な記憶領域を抑制しながらも、同等の復号性能を得られることが見て取れる。

ここで本発明において冗長ビタビ復号を用いた場合よりもビット誤り率が向上するのは、冗長ビタビ復号ではエラーの発生によって一度避けたパスを次の繰り返し処理によって復活させてしまうことがあるからであり、本発明が排除法を用いた点はこの点にも効果として表れている。

#### 【0055】

##### 【発明の効果】

以上説述したように、本発明によれば、本件出願人らによって開示された冗長ビタビ復号を用いた復号方法と同等かそれ以上のビット誤り率の改善を図りながら、計算量・メモリ量を抑制したトレリス構造を有する符号化とパリティ検査符号による連接符号化方式の復号方法を提供することができる。

##### 【図面の簡単な説明】

【図1】BCM-TSにおけるビットマトリクス及びシンボルの生成方法である。

【図2】ブロック符号化変調に対応するトレリス線図である。

【図3】本発明に係るブロック符号化変調とパリティ検査符号による連接符号化方式である。

【図4】本発明提案のビタビ復号とパリティ検査に基づく繰り返し復号による連接復号のフローチャートである。

【図5】従来の冗長ビタビ復号による復号過程を説明するためのトレリス線図である。

10

20

30

40

50

【図6】本発明による復号過程を説明するためのトレリス線図である。

【図7】様々な復号方法によるビット誤り特性を示すグラフである。

【図8】デジタル通信における信号処理の構成を示す説明図である。

【図9】MBCMにおけるパリティ検査ビットを配置を説明する図である。

【符号の説明】

3 0 符号ブロック  $C_1$

3 1 符号ブロック  $C_2$

3 2 符号ブロック  $C_K$

3 3 a ~ c 符号レベル  $l_{k+1}$

3 4 a ~ c 各符号ブロックにおける他の2つの符号レベル

3 5 ビット

3 6 縦方向のパリティ検査符号

3 7 縦方向のパリティ検査符号

3 8 符号レベル  $l_{k+2}$  の最後のビット  $a_{k+2,14}$

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

$$\begin{aligned} l_1 &\rightarrow a_{1,1} \ a_{1,2} \ \dots \ a_{1,j} \ \dots \ a_{1,T} \\ l_2 &\rightarrow a_{2,1} \ a_{2,2} \ \dots \ a_{2,j} \ \dots \ c_1 \\ l_3 &\rightarrow a_{3,1} \ a_{3,2} \ \dots \ a_{3,j} \ \dots \ c_2 \\ l_4 &\rightarrow a_{4,1} \ a_{4,2} \ \dots \ a_{4,j} \ \dots \ c_3 \end{aligned}$$

【図8】

---

フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 03M 13/41