RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 504 730**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21) **N° 81 08440**

(54) Procédé de fabrication de circuits intégrés MOS à plusieurs types d'interconnexions.

(51) Classification internationale (Int. Cl.<sup>3</sup>). H 01 L 21/82.

(22) Date de dépôt..... 28 avril 1981.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 43 du 29-10-1982.

(71) Déposant : SOCIETE POUR L'ETUDE ET LA FABRICATION DES CIRCUITS INTEGRES SPECIAUX (EFCIS), société anonyme, résidant en France.

(72) Invention de : Guy Dubois et Jean-Pierre Brevignon.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Thomson-CSF, SCPI,

173, bd Haussmann, 75360 Paris Cedex 08.

PROCEDE DE FABRICATION DE CIRCUITS INTEGRES MOS A PLUSIEURS

TYPES D'INTERCONNEXIONS.

La présente invention concerne les circuits intégrés incorporant des transistors MOS et des interconnexions entre eux, et plus particulièrement des circuits intégrés dans lesquels les interconnexions sont de plusieurs types différents et situées à plusieurs niveaux différents.

Il est souhaitable en effet, d'une part, d'avoir plusieurs niveaux d'interconnexion pour que celles-ci puissent se croiser sans court-circuit, et, d'autre part, d'avoir, éventuellement dans chaque niveau, des interconnexions de résistivités différentes : 10 des interconnexions à basse résistivité permettent de réaliser des liaisons conductrices entre divers points du circuit, tandis que des interconnexions, ou tout simplement des régions de plus grande résistivité, permettent de réaliser par exemple des charges pour des mémoires statiques, des ponts diviseurs, etc...

15 La présente invention cherche donc à proposer un procédé de fabrication qui permette de réaliser ces interconnexions de différentes résistivités, réparties en plusieurs niveaux.

Bien entendu, il faut tenir compte de ce qu'un procédé de fabrication n'a d'intérêt en pratique que s'il minimise le nombre 20 d'opérations successives nécessaires à la fabrication du circuit intégré, et notamment s'il minimise le nombre de masques à concevoir et à utiliser dans la fabrication. On pourrait en effet concevoir un procédé de fabrication fournissant autant de niveaux d'interconnexion et autant de résistivités différentes que l'on souhaite en multipliant le nombre d'opérations de fabrication et 25 d'opérations de masquage, mais tel n'est pas le but de l'invention qui cherche, au contraire, à établir un procédé qui optimise à la fois le nombre de possibilités d'interconnexions et le nombre d'opérations de traitement et de masques différents à dessiner et 30 à utiliser.

Un autre but de l'invention est de rendre ce procédé compatible avec la fabrication sur le même circuit intégré de tran-

sistors ayant des tensions de seuil différentes, c'est-à-dire en pratique des transistors ayant des dopages de canal différents (transistors à canal naturel, transistors à canal enrichi, transistors à canal déplét<sup>e</sup> et transistors à canal fortement déplét<sup>e</sup>). Cette variété de transistors, associée à la variété d'inter-connexions possibles, offre de larges possibilités de réalisation de circuits complexes.

Un autre but encore de l'invention est de réaliser des transistors MOS dont la région de canal se situe précisément à 10 l'aplomb de la grille de commande, avec une très faible avancée latérale des régions de source et de drain au-dessous de la grille.

Pour atteindre ces buts, la présente invention propose un procédé de fabrication dont les étapes essentielles vont être données maintenant, en mentionnant quelques variantes d'exécution possibles, le détail du procédé étant donné dans la suite de la description en référence aux dessins.

Le procédé de fabrication selon l'invention comprend donc essentiellement les opérations consistant à :

20 a) créer de manière connue dans un substrat de silicium monocristallin des zones d'oxyde de champ, notamment pour isoler les transistors les uns des autres,

25 b) former ensuite sur le substrat une couche isolante mince destinée à constituer l'isolant de la grille des transistors, sur tout ou partie du substrat, et doper le substrat en fonction des valeurs désirées de déplétion ou d'enrichissement des différents transistors,

c) former sur l'ensemble du substrat une couche de silicium polycristallin dopé,

30 d) graver sélectivement la couche de silicium polycristallin pour laisser un motif comprenant les grilles des transistors MOS et des interconnexions en silicium polycristallin dopé,

35 e) doper le substrat à faible profondeur et faible concentration, par implantation ionique à travers la couche isolante mince, pour délimiter les extrémités des canaux des transistors MOS par auto-alignement avec les bords des grilles de

silicium polycristallin, tout en dopant le silicium polycristallin là où il n'est pas protégé éventuellement par une couche d'oxyde, et pour créer des régions d'interconnexion résistives implantées,

f) effectuer un recuit du substrat,

5 g) former une couche de protection sur l'ensemble du substrat et la graver selon un motif tel que la couche de protection recouvre totalement, en débordant légèrement tout autour, les grilles des transistors MOS et des régions de silicium polycristallin devant présenter une grande résistivité, mais ne recouvre 10 pas des régions de silicium polycristallin ou monocristallin dont on veut réduire la résistivité,

15 h) doper les régions de silicium monocristallin ou polycristallin non recouvertes par la couche de protection, pour créer des régions d'accès aux sources et drains des transistors, des régions d'interconnexion peu résistives en silicium monocristallin fortement dopé, et éventuellement des régions de silicium polycristallin fortement dopées,

20 i) déposer un oxyde épais sur le substrat et effectuer classiquement une gravure de cet oxyde, pour exposer des régions de silicium monocristallin et polycristallin dopées, éventuellement un nouveau dopage, puis un dépôt de métal et une gravure du métal déposé.

Dans la description générale du procédé selon l'invention qui vient d'être donnée, on peut déjà mentionner que la couche de 25 protection de l'opération g) peut être une couche d'oxyde de silicium, ou bien une couche de résine, auquel cas le dopage qui suit se fait par implantation ionique.

En ce qui concerne l'opération b), elle peut consister à oxyder la surface du substrat tout entière et à déposer le silicium polycristallin immédiatement après, ou alors elle peut consister à oxyder la surface du substrat, à graver sélectivement l'oxyde pour créer des zones découvertes de silicium monocristallin, dans le but de créer des interconnexions faiblement résistantes constituées par du silicium polycristallin en contact avec du 35 silicium monocristallin ; cette deuxième possibilité nécessite évidemment un masque spécial.

Le dépôt du silicium polycristallin peut se faire avec dopage "in situ", mais il peut se faire aussi après dépôt, par exemple par implantation ionique. De préférence, le dépôt du silicium polycristallin est suivi d'une oxydation, éventuellement 5 d'une implantation ionique d'impuretés à travers l'oxyde formé, pour ajuster la résistivité du silicium polycristallin déposé, d'une gravure de l'oxyde pour définir des régions de silicium polycristallin recouvertes d'oxyde et d'autres exposées, et enfin d'un dopage avec une impureté de type de conductivité opposé à ce-10 lui du substrat, créant ainsi, d'une part, des régions d'interconnexion de haute résistivité formées par le silicium polycristallin là où il est recouvert d'oxyde, d'autre part, des régions de silicium polycristallin dopé donc de plus faible résistivité.

15 Selon une caractéristique particulièrement intéressante de l'invention, si on effectue cette gravure de l'oxyde après 1'opération c), on pourra parfois utiliser ensuite le même masque ou deux masques qui se déduisent facilement l'un de l'autre pour cette opération et pour l'opération g) qui comprend également une 20 gravure d'oxyde ou de résine. Bien que l'opération doive donc être répétée dans le procédé de fabrication, on aboutit à une simplification de la conception des circuits puisqu'on dessine un seul masque au lieu de deux.

L'opération d), par laquelle on détermine le motif de si-25 licium polycristallin qui doit rester, comprend une étape de masquage définissant les régions de silicium polycristallin à conserver pour former, d'une part, les grilles de transistors et, d'autre part, les diverses régions d'interconnexion utilisant le silicium polycristallin ; cette étape est suivie d'une étape de 30 développement d'une résine photosensible pour recouvrir uniquement ces régions et les conserver, d'une étape de gravure de l'oxyde recouvrant éventuellement le silicium polycristallin en dehors de ces régions, et enfin une étape de gravure du silicium polycristallin également en dehors de ces régions : un seul masque sert à 35 graver à la fois l'oxyde et le silicium polycristallin qui est en-dessous.

Par ailleurs, il faut noter que l'opération g), par laquelle on protège du dopage les régions immédiatement à l'aplomb des grilles des transistors, se fait en utilisant un masque qui peut aussi se déduire facilement du masque utilisé à l'opération 5 d) : le masque de l'opération g) peut correspondre essentiellement à la définition des mêmes régions d'oxyde, mais légèrement dilatées, que le masque de l'opération d). Toutefois, dans certains cas, on peut préférer utiliser comme masque, non pas le premier masque dilaté, mais plus précisément un masque qui correspond 10 à la réunion des intersections du masque de l'opération d) dilaté avec un masque correspondant à la définition des régions actives entre les zones d'oxyde de champ du substrat et avec un masque correspondant à la gravure faite à l'opération c). Quel que soit 15 le choix effectué, on voit que l'opération de conception du masque de l'opération g) peut se faire avec un travail extrêmement réduit, et peut même se faire automatiquement dans la plupart des ordinateurs d'assistance à la conception.

L'exemple que l'on donnera dans la suite montrera que le procédé de fabrication selon l'invention permet par exemple de 20 réaliser un circuit intégré comportant des transistors à quatre tensions de seuil différentes, quatre niveaux d'interconnexion, et six valeurs différentes de résistivité des interconnexions (en comptant les interconnexions d'aluminium qui doivent de toute façon être prévues). On montrera cependant quelles sont les étapes 25 qui ne sont pas strictement essentielles pour la généralité du procédé selon l'invention et quelles modifications des possibilités du circuit intégré sont introduites par ces étapes.

La description détaillée qui suit est faite en référence aux dessins annexés dans lesquels :

- 30 - les figures 1 à 5 montrent des étapes classiques de début de fabrication d'un circuit intégré à transistors MOS ayant différentes tensions de seuil ;

- les figures 6 à 10 montrent plus spécialement les différentes étapes correspondant à l'invention ;

- 35 - les figures 11 et 12 représentent les étapes de métallisation ;

- la figure 13 représente de manière schématique une structure avec les différents niveaux d'interconnexion et les natures des différentes régions d'interconnexion.

On peut partir d'un substrat de silicium monocristallin 5 d'orientation (1,0,0) dopé avec une impureté de type P.

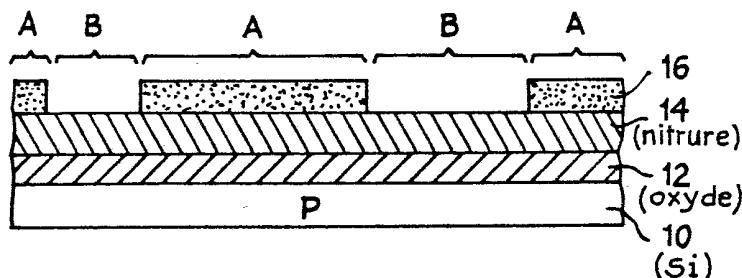

La figure 1 représente ce substrat 10 auquel on a fait subir une oxydation thermique qui a créé une couche superficielle 12 d'oxyde de silicium  $\text{SiO}_2$ . Sur cette couche d'oxyde, on a déposé une couche 14 de nitrure de silicium (dépôt en phase vapeur à basse pression), la couche d'oxyde 12 servant notamment de tampon entre la couche 14 et le substrat afin que le dépôt du nitrure ne détériore pas la structure cristalline du substrat 10.

Une première phase de photogravure est appliquée alors par dépôt, sur la couche de nitrure 14, d'une couche de résine 16 15 qui est exposée à un rayonnement à travers un premier masque qui définit dans la résine deux types de zones, des zones A où la résine subsiste après développement et des zones B où la résine est éliminée par le développement. Les zones A définissent les zones actives du substrat, dans lesquelles on formera notamment les 20 transistors à effet de champ ; les zones B sont prévues pour la formation de l'oxyde épais entourant les zones actives ; les zones B sont appelées classiquement zones de champ.

La figure 2 représente les étapes suivantes qui sont, d'une part, une étape de gravure par plasma du nitrure exposé dans 25 les zones B, la résine 16 protégeant le nitrure dans les zones A, et d'autre part, une implantation ionique d'une impureté de type P (par exemple du bore) toujours dans les zones B qui ne sont protégées ni par le nitrure, ni par la résine 16. L'implantation est effectuée avec une énergie suffisante pour que les impuretés traversent la couche d'oxyde 12. On obtient ainsi dans les zones de champ B du substrat 10 des régions 18 fortement enrichies (de type  $P^+$ ) qui servent à neutraliser la couche d'inversion de type N qui pourrait se créer sous l'oxyde de champ.

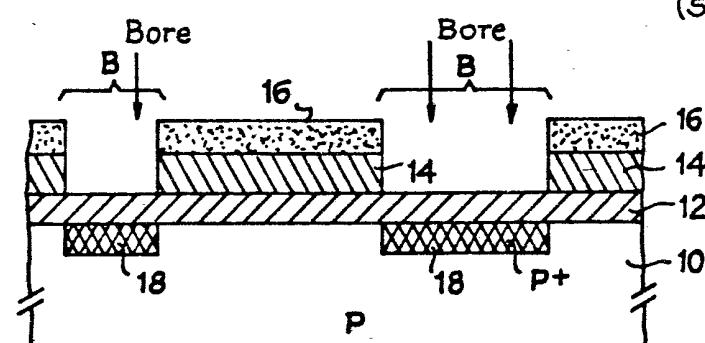

La figure 3 montre l'étape d'oxydation de champ, c'est-à-dire celle par laquelle on fait croître l'oxyde épais dans les zones B. Après retrait de la résine 16, on oxyde thermiquement le

silicium, ce qui produit la croissance de l'oxyde de champ 20 dans les zones non protégées par le nitrure 14. L'oxyde épais qui se forme dans les zones de champ B a une épaisseur de l'ordre de 1 micron.

5 Cette étape d'oxydation de champ est suivie d'une désoxydation superficielle qui a pour but d'éliminer une couche superficielle 22 d'oxyde de silicium qui s'est formée sur le nitrure 14. La dissolution du nitrure permet d'éliminer ensuite celui-ci, après quoi on désoxyde à nouveau pour éliminer l'oxyde 12 formé 10 durant la première étape de fabrication.

On fait croître alors à nouveau une couche d'oxyde superficielle d'épaisseur bien contrôlée qui est destinée à former notamment l'oxyde de grille des transistors MOS du circuit intégré. Cette oxydation est obtenue par voie thermique, de préférence dans 15 un mélange d'oxygène et d'acide chlorhydrique gazeux avec environ 1 à 5 % d'acide chlorhydrique.

La figure 4 montre l'oxyde de grille 24 obtenu par cette oxydation contrôlée. L'épaisseur de cet oxyde 24 est d'environ 70 nanomètres.

20 Le substrat ainsi oxydé est recouvert d'une couche de résine photosensible 26 qui est exposée à un rayonnement de photons à travers un deuxième masque qui définit des régions C où la résine subsiste après développement et des régions D où la résine est éliminée. Les régions D se situent à l'intérieur des zones actives 25 A. Dans les zones C, la résine sert d'écran protecteur lors de l'implantation ionique qui suit.

On implante dans le substrat de silicium monocristallin, à travers l'oxyde de grille 24, dans les zones D non protégées par la résine, une impureté de type de conductivité opposée au substrat, à savoir N. Il peut s'agir d'une implantation de phosphore ou d'arsenic. On crée ainsi des régions 28 qui correspondent essentiellement à des canaux déplétés de transistors MOS.

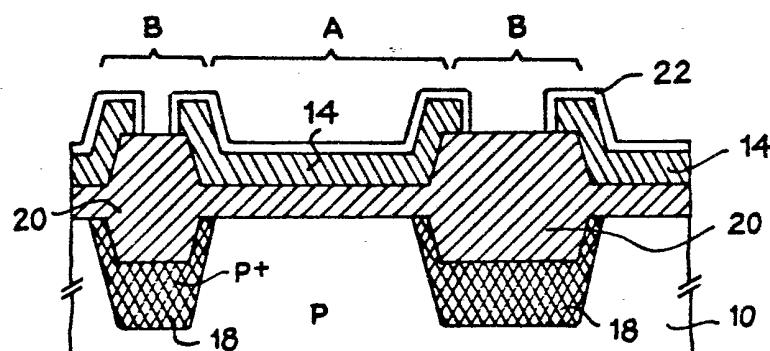

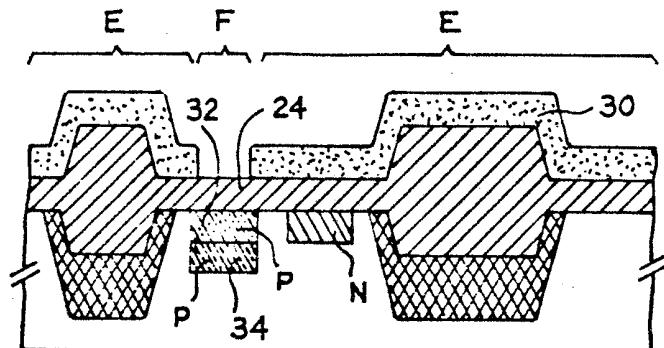

Après enlèvement de la couche de résine 26, on effectue une nouvelle opération de photogravure, consistant à déposer 35 d'abord une nouvelle couche de résine 30 (figure 5) et à l'exposer à un rayonnement de photons à travers un troisième masque qui dé-

finit dans la résine des zones E et des zones F ; dans les zones E, la résine subsiste après développement, tandis que dans les zones F, qui se situent à l'intérieur des zones actives A ou de certaines d'entre elles, la résine est éliminée après développement.

5 La figure 5 montre les zones E et F. On effectue alors deux implantations successives d'impuretés dans les zones F, la résine protégeant les régions E durant ces implantations. Il s'agit d'une implantation dite d'enrichissement et d'une implantation dite de perçage consistant à introduire des impuretés de même type (P) que le substrat, d'une part, à une faible profondeur (définissant des régions 32) et, d'autre part, à une profondeur plus importante (définissant des régions 34). L'impureté utilisée peut être du bore dans le cas de substrat de type P. Les régions 32 et 34 servent à définir des canaux enrichis de transistors 10 MOS.

Le deuxième masque, définissant les emplacements d'implantation de déplétion (D), et le troisième masque définissant les implantations d'enrichissement (F), permettent d'obtenir quatre cas de dopage de canal des transistors MOS.

20 En effet, on peut protéger toute une zone active A à la fois durant l'implantation de déplétion (figure 4) et durant les implantations d'enrichissement (figure 5), de sorte qu'on aboutit à une région de canal dite "naturelle" qui a le même dopage que le substrat.

25 On peut aussi protéger la future zone de canal durant l'implantation de déplétion et la découvrir durant les implantations d'enrichissement, de sorte qu'on aboutit à un canal enrichi.

On peut encore découvrir la future zone de canal durant 30 l'implantation de déplétion et durant les deux implantations d'enrichissement, le canal devenant en pratique déplété compte tenu des dopages utilisés.

Enfin, on peut découvrir la zone durant l'implantation de déplétion et la protéger durant les implantations d'enrichissement, pour aboutir à des transistors à canal fortement déplété.

Bien entendu, on pourrait fabriquer un circuit intégré

ayant un seul type de transistors, auquel cas les deuxième et troisième masques sont inutiles, ou encore deux types de transistors seulement, auquel cas l'un des deux masques peut être supprimé.

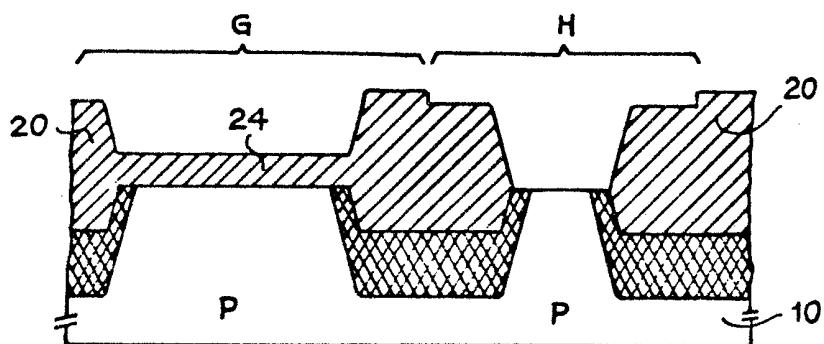

5 A la figure 6 est représentée une étape de gravure de l'oxyde de grille 24 dans certaines des zones actives, qui sont plus précisément des zones actives où l'on n'envisage pas de faire des transistors à effet de champ. Un quatrième masque permet de définir des zones G où subsiste l'oxyde 24, et des zones H où cet 10 oxyde a été éliminé. Bien entendu, cette opération de désoxydation n'attaque que faiblement l'oxyde de champ épais 20.

Cette opération de gravure d'oxyde n'est pas obligatoire, mais elle permet de définir, en dehors des zones où l'on prévoit des transistors à effet de champ dont la grille sera constituée 15 par une couche de silicium polycristallin, des zones où la même couche de silicium polycristallin sera directement en contact avec le substrat 10, en vue d'établir certaines interconnexions. Dans les zones G, qui restent recouvertes par l'oxyde 24, on peut aussi former des capacités pour le circuit intégré.

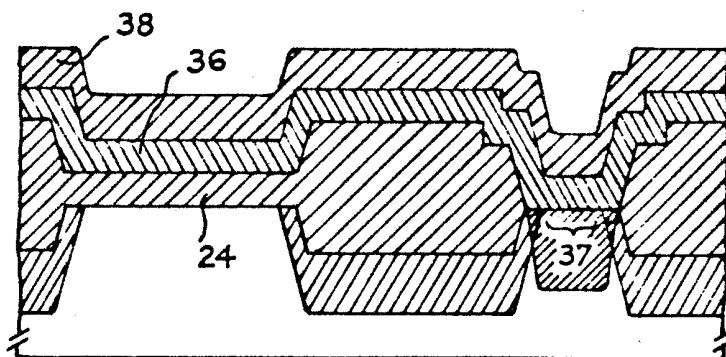

20 La figure 7 montre le dépôt de silicium polycristallin en couche 36 sur toute la surface du substrat, dépôt effectué en phase vapeur. L'épaisseur de silicium polycristallin est d'environ 0,5 micron. Ce dépôt est suivi d'une oxydation thermique créant une couche d'oxyde 38 d'environ 100 nanomètres. L'échelle des 25 épaisseurs ne correspond pas à la réalité sur les figures.

On peut alors si on le désire effectuer une implantation ionique d'impuretés telles que du phosphore (conductivité opposée au substrat) pour doper le silicium polycristallin. L'énergie d'implantation doit être suffisante pour que les ions traversent 30 l'oxyde 38. Le silicium pourrait également être dopé in situ lors de son dépôt, mais l'intérêt du dopage par implantation ionique est de permettre l'ajustement de la résistivité du silicium polycristallin, surtout dans le cas où il s'agit d'une haute résistivité.

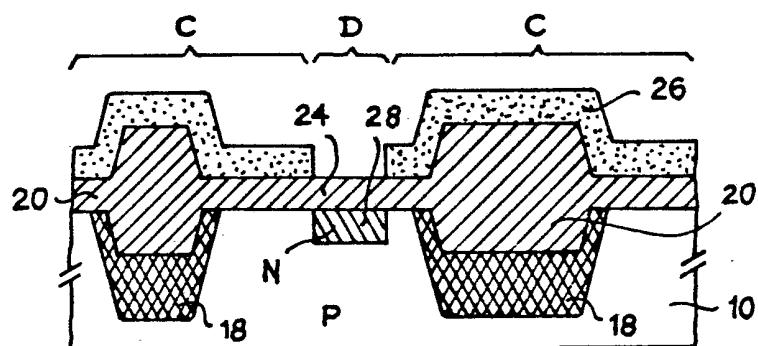

35 La figure 8 montre comment on peut, facultativement, utiliser un cinquième masque qui définit des zones I où on laisse

subsister l'oxyde de la couche supérieure 38, et des zones J où on élimine cet oxyde par gravure chimique en phase liquide ou par plasma. L'opération de photogravure avec résine photosensible n'est pas représentée.

5 On effectue alors un dopage du silicium polycristallin, par exemple par prédépôt et diffusion de phosphore à une température de l'ordre de 900°C. Les zones J sont dopées alors que les zones I sont protégées par l'oxyde, ce qui permet de définir des zones de silicium polycristallin de faible résistivité (à l'intérieur des zones J), et des zones de silicium polycristallin de forte résistivité (à l'intérieur des zones I). L'oxyde 38 est alors éliminé.

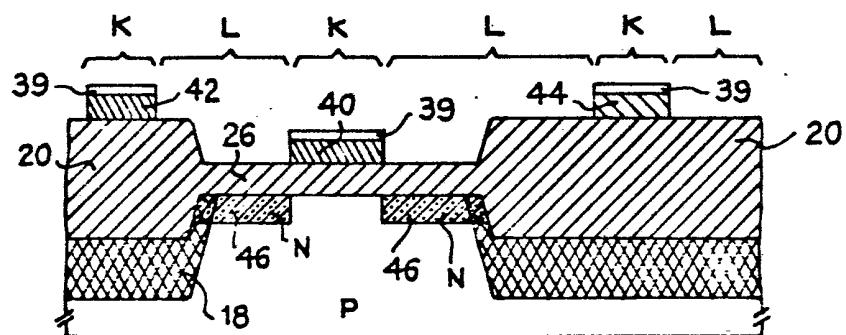

10 Un sixième masque définit, après dépôt, exposition sélective et développement d'une résine photosensible 39, des régions K protégées et des régions L découvertes (figure 9). Le silicium polycristallin est gravé dans les régions L, par exemple par un plasma gazeux formé par un champ à haute fréquence dans un mélange gazeux de CF<sub>4</sub> et de O<sub>2</sub>. Il subsiste alors plusieurs types de zones de silicium polycristallin recouvertes de la résine de masquage 15 39 : d'abord des zones 40 de silicium polycristallin situées en plein milieu des zones actives A définies par le premier masque. Ces zones 40 servent essentiellement de grilles pour les transistors MOS. Ces zones peuvent comprendre du silicium polycristallin de faible résistivité si lors de l'opération de la figure 8 elles 20 ont subi le dopage au phosphore. Elles peuvent aussi être de forte résistivité si elles sont restées recouvertes de l'oxyde 38 pendant le dopage. Ensuite, on a représenté sur la figure 9 des zones 25 42 de silicium polycristallin de faible résistivité situées, non pas dans les zones actives, mais sur l'oxyde de champ 20. Ces zones 30 42, initialement dans les régions J dopées, servent d'interconnexions. Enfin, des zones 44 de silicium polycristallin de forte résistivité, initialement situées dans les régions I moins dopées, se trouvent également de préférence au-dessus de l'oxyde de champ et servent d'interconnexions à haute résistivité.

35 Sans utiliser de nouveau masque, on effectue alors une implantation d'ions d'énergie suffisante pour traverser l'oxyde de

grille 26. Les zones K comportant du silicium polycristallin servent d'écran lors de l'implantation, de même d'ailleurs que l'oxyde épais d'isolement 20. Dans les régions actives non recouvertes par le silicium polycristallin, l'impureté implantée, de 5 préférence de l'arsenic, crée des zones fortement dopées 46 de type de conductivité opposée au substrat. Les doses implantées peuvent être de  $10^{15}$  à  $10^{16}$  atomes par  $\text{cm}^3$ .

Les zones 46 sont auto-alignées par rapport aux grilles de silicium 40 et par rapport aux régions de champ 18.

10 On remarque que l'implantation se fait à profondeur modérée et à concentration modérée pour que l'arsenic des régions 46 diffuse peu sous les grilles 40 lors des traitements thermiques ultérieurs.

Il est nécessaire ensuite de procéder à un recuit afin de 15 restaurer la qualité cristalline du silicium (par exemple, à  $900^\circ\text{C}$  pendant une heure sous azote), puis à une désoxydation.

A la figure 10, on a représenté les étapes suivantes qui consistent d'abord à créer sur la plaquette une couche de protection 48 qui est de préférence une couche d'oxyde formé thermiquement et d'épaisseur comprise entre 50 et 100 nanomètres, mais qui peut être aussi une couche de résine, comme on le verra plus loin.

Dans le cas où la couche 48 est une couche d'oxyde, on effectue à nouveau une opération de photogravure de l'oxyde à 25 l'aide d'un septième masque qui définit des régions M où subsiste la couche d'oxyde 48 et des régions N où cette couche est éliminée. Les régions M recouvrent notamment les zones de silicium polycristallin qui doivent garder une haute résistivité (régions définies par les zones K du sixième masque à l'intérieur des zones 30 I du cinquième masque), ainsi que les grilles des transistors MOS à l'intérieur des zones actives du substrat. Comme on le voit sur la figure 10, l'oxyde 48 qui reste en place recouvre avec débordement latéral les grilles 40 des transistors MOS ainsi que les zones 44 de silicium polycristallin à haute résistivité. Les régions 35 N, quant à elles, où l'oxyde 48 a été éliminé, recouvrent des régions de silicium polycristallin 42 ainsi que des régions 50 du

substrat monocristallin, ces régions 50 se situant entre l'oxyde de champ et les drains ou sources 46 des transistors MOS, pour constituer des connexions vers ces sources et drains.

L'étape suivante consiste à doper à nouveau, avec une impureté de conductivité opposée au substrat, les régions N non recouvertes par l'oxyde 48. Ce dopage peut se faire par exemple par prédépôt et diffusion de phosphore à une température de l'ordre de 900°C. Il en résulte que les régions 50 du substrat sont fortement dopées, ainsi que les régions 42 de silicium polycristallin non recouvert d'oxyde.

On a donc créé ainsi des régions d'interconnexions 50 dopées fortement au phosphore, aboutissant notamment aux drains et aux sources 46 des transistors MOS, ceux-ci présentant des régions de source et de drain ne débordant pratiquement pas sous la grille 15 compte tenu de la faible concentration de ces régions et donc de la faible diffusion latérale des impuretés lors des traitements thermiques. On a aussi constitué des régions de silicium polycristallin 42 fortement dopées qui peuvent d'ailleurs inclure notamment du silicium polycristallin directement en contact avec le substrat (dans les régions H définies en référence à la figure 6).

On a dit que la couche de protection 48 qui subsiste dans les régions M pouvait être une couche d'oxyde de silicium. Elle peut être aussi une couche de résine subsistant après exposition et développement ; dans ce cas, l'opération de dopage des régions N s'effectue par implantation ionique, la résine formant écran de protection. Le résultat est exactement le même, à savoir essentiellement la formation des régions d'interconnexions 50 fortement dopées.

On peut mentionner à ce propos que le septième masque et le cinquième masque peuvent être identiques, si toutefois on accepte que les grilles des transistors MOS soient moins dopées. Si on veut des transistors dont l'électrode de grille est plus dopée, on peut également définir facilement le cinquième masque à partir du septième puisque le cinquième masque comportera essentiellement les mêmes motifs que le septième sauf dans les régions où on veut des électrodes de grille plus dopées. Le cinquième masque, s'il

n'est pas exactement identique au septième, peut par conséquent s'en déduire de manière extrêmement simple, permettant une grande économie de temps de conception.

Enfin, si on veut que tous les transistors aient leur grille assez dopée, le septième masque peut être défini à partir du sixième de manière assez simple et surtout automatiquement : sur le sixième masque qui définit les régions K, on élimine les régions 42 de silicium polycristallin destinées à former des interconnexions de faible résistivité, puis on dilate légèrement les régions K restantes, ce qui peut se faire entièrement par informatique, réduisant encore une fois considérablement le temps de conception. Le septième masque est donc alors la réunion des intersections du sixième masque (dilaté) avec le premier définissant les régions actives A (figure 1) et avec le cinquième définissant les régions d'interconnexion de haute résistivité I (figure 8). Il peut être fait de manière entièrement informatique (ou réciproquement, le cinquième masque peut être défini de manière informatique à partir des septième, sixième et premier masques).

Parmi les multiples possibilités du procédé de fabrication selon l'invention, on constate l'intérêt particulier des étapes que l'on vient de mentionner en référence aux figures 8, 9 et 10 : avec trois masques qui se déduisent facilement les uns des autres, on peut réaliser un transistor MOS auto-aligné de manière très satisfaisante, et trois sortes d'interconnexions s'étendant sur deux niveaux.

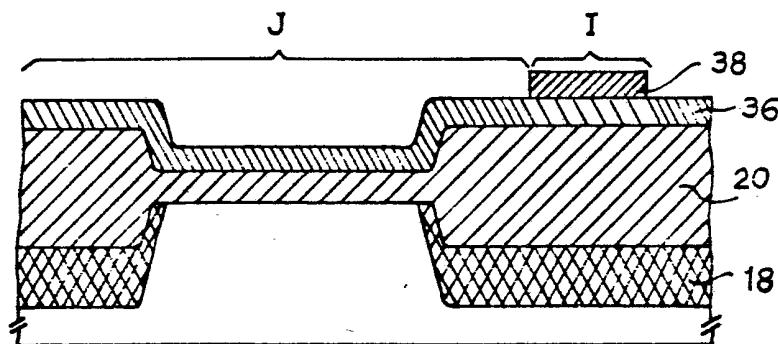

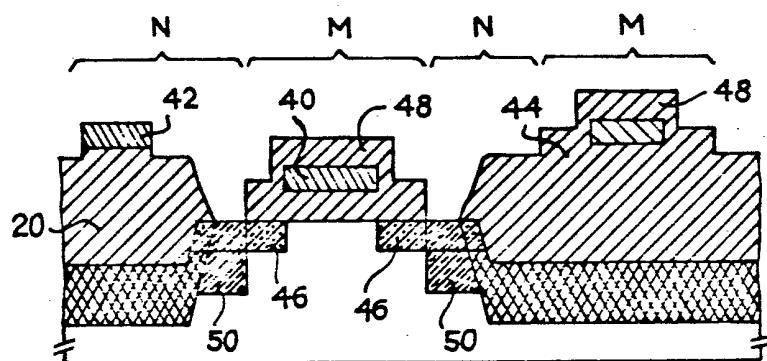

Les figures 11 et 12 ne sont pas représentées à la même échelle longitudinale que les précédentes et servent à représenter très schématiquement les étapes suivantes qui sont relativement classiques.

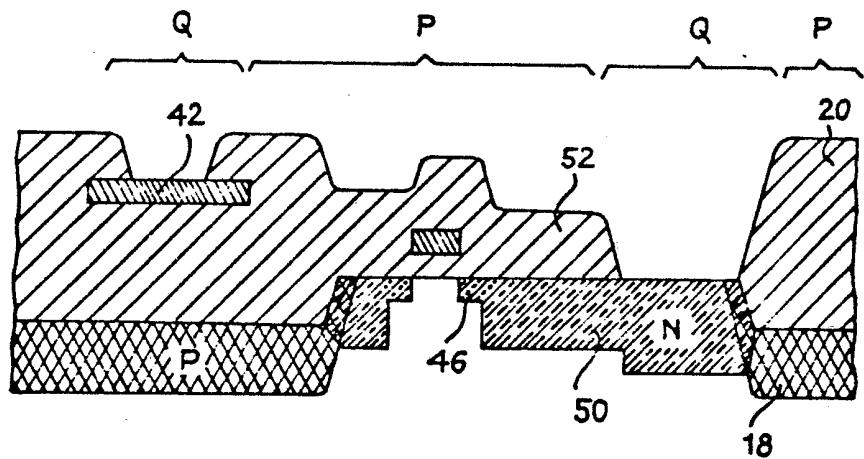

La figure 11 montre l'étape suivante qui consiste d'abord à former sur l'ensemble du substrat une couche d'oxyde 52 d'une épaisseur d'environ 1 micron, cette couche contenant de préférence du phosphore dans des concentrations molaires de l'ordre de 5 à 10% . Cet oxyde peut être déposé à basse température en phase vapeur et il est souhaitable de faire suivre le dépôt d'une opéra-

tion de fluage à température élevée, de manière à obtenir un profil d'oxyde qui ne présente pas des marches aussi abruptes que celles que lui donne au départ le relief tel qu'il se présente à la figure 10.

5                 Après ce dépôt d'oxyde, un huitième masque de photogravure définit des régions P où l'oxyde subsiste sur le substrat, et des régions Q où l'oxyde est éliminé sélectivement, par exemple par voie chimique ou par plasma ; les régions Q se situent au-dessus de zones 42 de silicium polycristallin fortement dopé, et 10 aussi au-dessus de régions 50 d'interconnexions au silicium monocristallin fortement dopé, et ces zones Q définissent de manière générale des ouvertures de contact en vue de la métallisation.

Un dopage est alors de préférence effectué pour renforcer encore la concentration en impuretés de la partie de région 50 15 située dans une région Q.

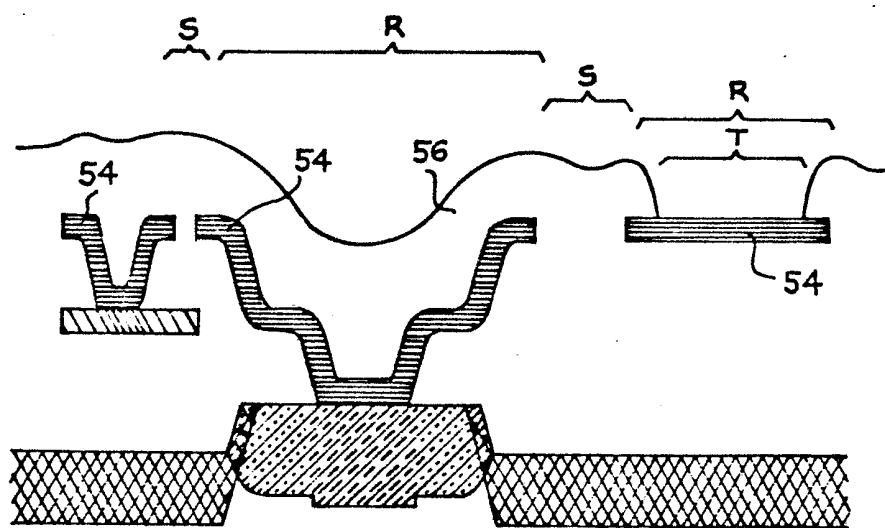

La figure 12 représente les étapes de métallisation : après dépôt sous vide d'une couche 54 de métal, de préférence de l'aluminium contenant de 1% à 2% de silicium, sur le substrat tel qu'il se présente à la figure 11, un neuvième masque de photogravure définit des régions R où le métal 54 subsiste, et des régions S où le métal est éliminé sélectivement par voie chimique ou par plasma. Le motif de gravure du métal 54 correspond aux interconnexions métalliques à effectuer entre les différents éléments du circuit intégré, c'est-à-dire entre les transistors, et les inter-25 connexions résistives des différentes catégories déjà mentionnées.

Un recuit est alors effectué vers 450°C dans un mélange d'azote et d'hydrogène pour améliorer la qualité électrique des contacts.

Enfin, un dépôt d'oxyde ou de nitrure 56 est effectué à 30 basse température en vue de la passivation du circuit intégré.

Un dixième masque de photogravure est alors utilisé pour définir l'ouverture des plots de contact constituant les bornes d'accès extérieur au circuit intégré. A l'aide de ce dixième masque, on élimine le dépôt de passivation dans les régions cor-35 respondant aux plots de contact.

Sur la figure 12, on a représenté une zone T d'ouverture

de plots de contact au-dessus d'une région d'aluminium qui a sub-

sisté après gravure selon le huitième masque.

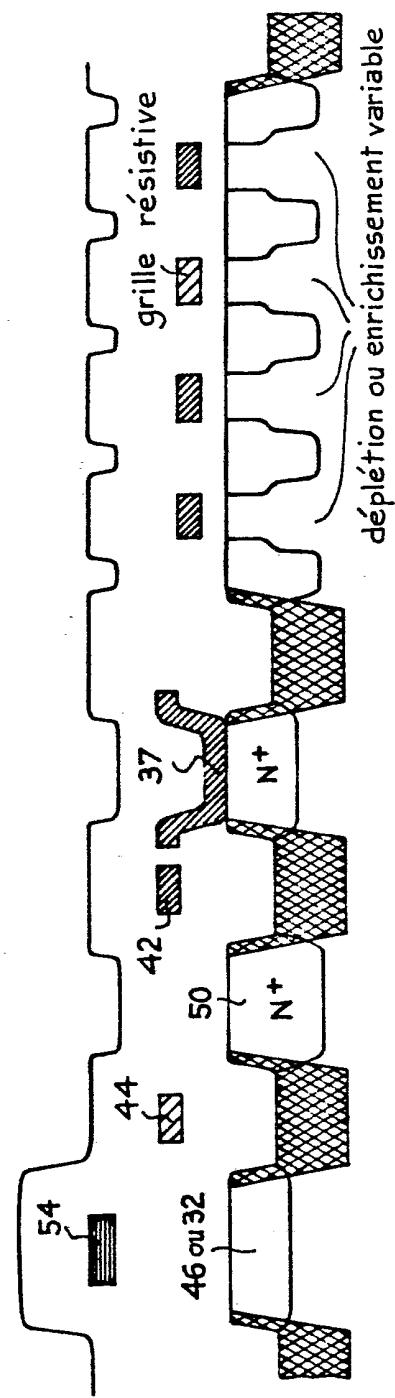

La figure 13 représente symboliquement une coupe du cir-

cuit intégré où sont représentées les différentes possibilités ap-

portées par le procédé selon l'invention, et en particulier les

divers types d'interconnexions pouvant être employés.

Sur cette figure, on a gardé pour les différentes régions

les mêmes références que celles qui ont été données en référence

aux figures qui précédent.

10 Un premier type d'interconnexion est constitué par des

régions 54 d'aluminium ; il s'agit du niveau supérieur d'inter-

connexion.

Un deuxième type d'interconnexion est constitué par des

zones 44 de silicium polycristallin de haute résistivité, sur un

15 deuxième niveau d'interconnexion.

Toujours sur le deuxième niveau, on rencontre des zones

42 de silicium polycristallin de faible résistivité, noyées dans

l'oxyde.

Sur le deuxième niveau encore, on trouve des zones 37 de

20 silicium polycristallin de faible résistivité en contact avec du

silicium monocristallin dopé avec une impureté du même type que le

silicium polycristallin.

Sur un troisième niveau, on rencontre d'abord des régions

46 ou 32 qui sont des interconnexions résistives de silicium mono-

25 cristallin ayant subi une implantation d'arsenic.

On rencontre aussi des zones 50 de silicium monocristal-

lin ayant subi une ou plusieurs diffusions de phosphore.

Par ailleurs, sur la partie droite de la figure 13, on a

représenté symboliquement plusieurs transistors dont les possibi-

30 lités sont les suivantes :

1°) quatre tensions de seuil différentes sont possibles

comme on l'a déjà dit ;

2°) certains transistors peuvent avoir une grille de si-

licium polycristallin de haute résistivité ;

35 3°) sauf exception, tous les transistors présentent une

très faible avancée latérale des jonctions sous la grille de

commande.

Outre les avantages déjà mentionnés pour le procédé selon l'invention, on peut signaler que ce procédé est particulièrement intéressant du point de vue industriel car il peut s'adapter à des 5 cas simples de circuits intégrés comme à des cas complexes, les cas simples se déduisant des cas complexes par élimination de certaines étapes. Par exemple, si on désire que tous les transistors du circuit aient le même dopage de canal, on peut éliminer les deuxième et troisième masques.

10 De même, on peut supprimer l'opération d'oxydation du silicium polycristallin après son dépôt (figure 7), supprimer l'opération de photogravure mentionnée à la figure 8 et l'opération de dopage qui suit cette gravure. On dispose alors de circuits dans lesquels les grilles de commande des transistors sont toutes 15 résistives.

On peut aussi éviter l'opération d'oxydation thermique du silicium polycristallin juste après son dépôt et ne pas effectuer non plus l'opération d'implantation ionique qui suit ce dépôt (implantation ionique pour ajuster la résistivité du silicium 20 polycristallin). On supprime aussi l'opération de masquage par le cinquième masque. Ceci est valable lorsqu'on n'a pas besoin de disposer à la fin de régions de silicium polycristallin de haute résistivité. Ceci montre l'intérêt industriel du procédé selon 25 l'invention car on n'a pas toujours besoin de silicium polycristallin de haute résistivité et il est bien utile que le même procédé serve dans les cas où l'on en a besoin et dans les cas où l'on n'en a pas besoin.

A titre indicatif, on peut mentionner aussi que le procédé selon l'invention permet aussi, sans modification de déroulement, de disposer de transistors MOS dont les régions de source et drain ont une profondeur importante : il suffit d'éliminer la couche de protection 48 (voir description de la figure 10), par exemple dans des portions de circuits admettant des tensions élevées.

35 Les variantes qui précèdent ne sont données que pour montrer comment la succession des étapes du procédé selon l'invention

permet non seulement d'atteindre un excellent résultat en ce qui concerne le nombre de possibilités d'interconnexions obtenues avec un déroulement simple d'opération, mais aussi permet, par des simplifications ne perturbant pas l'ordre des opérations, d'atteindre 5 des résultats plus simples et plus classiques, c'est-à-dire notamment avec un nombre de types d'interconnexions différentes plus réduit.

## REVENDICATIONS.

1. Procédé de fabrication d'un circuit intégré incorporant des transistors à effet de champ du type MOS et des interconnexions à plusieurs niveaux et de plusieurs résistivités différentes, caractérisé par les opérations consistant à :

5 a) créer de manière connue dans un substrat (10) de silicium monocristallin des zones actives entourées d'oxyde épais (20), notamment pour isoler les transistors les uns des autres,

b) former ensuite sur le substrat une couche isolante mince (24) destinée à constituer l'isolant de la grille des 10 transistors, sur tout ou partie du substrat, et doper le substrat en fonction des valeurs désirées de déplétion ou d'enrichissement des différents transistors,

c) former sur l'ensemble du substrat une couche (36) de silicium polycristallin dopé,

15 d) graver sélectivement la couche de silicium polycristallin pour laisser un motif comprenant les grilles (40) des transistors MOS et des interconnexions (42, 44), en silicium polycristallin dopé,

e) doper le substrat à faible profondeur et faible 20 concentration, par implantation ionique à travers la couche isolante mince, pour délimiter les extrémités des canaux des transistors MOS par autoalignement avec les bords des grilles de silicium polycristallin, tout en dopant le silicium polycristallin là où il n'est pas protégé éventuellement par une couche d'oxyde et pour 25 créer des régions d'interconnexion résistives implantées,

f) effectuer un recuit du substrat,

g) former une couche de protection (48) sur l'ensemble du substrat et la graver à l'aide d'un masque selon un motif tel que la couche de protection recouvre totalement, en débordant légèrement tout autour, les grilles (40) des transistors MOS, et des régions (44) de silicium polycristallin devant présenter une grande résistivité, mais ne recouvre pas des régions (42, 50) de silicium

polycristallin ou monocristallin dont on veut réduire la résistivité,

5 h) doper les régions monocristallines ou polycristallines non recouvertes par la couche de protection pour créer des régions 5 (50) d'accès aux sources et drains des transistors, des régions d'interconnexion résistives en silicium monocristallin fortement dopé, et éventuellement des régions (42) de silicium polycristallin fortement dopées,

10 i) déposer un oxyde épais (52) sur le substrat et effec- tuer classiquement une gravure de cet oxyde, pour exposer des ré- gions de silicium monocristallin et polycristallin dopées, éventuellement un nouveau dopage, puis un dépôt de métal (54) et une gravure du métal déposé.

15 2. Procédé selon la revendication 1 caractérisé par le fait que l'opération b) consiste à oxyder la surface du substrat et à graver sélectivement l'oxyde pour créer des zones découvertes de silicium monocristallin dans le but de créer des intercon- nexions résistives (37) constituées par du silicium polycristallin en contact avec du silicium monocristallin.

20 3. Procédé selon l'une des revendications 1 et 2 caracté- risé par le fait que dans l'opération c), le silicium polycristal- lin est dopé "in situ" selon un type de conductivité opposé à celui du substrat.

25 4. Procédé selon l'une des revendications 1 à 3 caracté- risé par le fait que l'opération d) comprend une étape de masquage définissant les régions de silicium polycristallin à conserver pour former les grilles de transistors et les diverses régions d'interconnexion utilisant le silicium polycristallin, une étape de développement d'une résine photosensible pour recouvrir unique- 30 ment ces régions à conserver, une étape de gravure de l'oxyde re- couvrant éventuellement le silicium polycristallin en dehors de ces régions, suivie d'une étape de gravure du silicium également en dehors de ces régions.

35 5. Procédé selon l'une des revendications 1 à 4 caracté- risé par le fait que l'opération d) et l'opération g) se font en utilisant deux masques qui se déduisent facilement l'un de

l'autre, le second correspondant essentiellement à la définition de certaines des régions du premier, mais légèrement dilatées.

6. Procédé selon l'une des revendication 1 à 5 caractérisé par le fait que dans l'opération c), le silicium polycristallin est dopé par implantation ionique d'une impureté de type de conductivité opposé à celui du substrat.

7. Procédé selon l'une des revendications 1 à 6 caractérisé par le fait que l'opération c) inclut :

- la formation d'une couche d'oxyde,

10 - éventuellement une implantation ionique d'impuretés à travers l'oxyde formé pour ajuster la résistivité du silicium polycristallin,

- une gravure de l'oxyde à l'aide d'un masque pour définir des régions (I) de silicium polycristallin recouvertes d'oxyde 15 et d'autres (J) exposées,

- et enfin un dopage avec une impureté de type de conductivité opposé à celui du substrat, créant ainsi d'une part des régions (44) d'interconnexion de haute résistivité formées par le silicium polycristallin là où il est recouvert d'oxyde, d'autre 20 part des régions (42) de silicium polycristallin dopé.

8. Procédé selon la revendication 7 caractérisé par le fait que le masque utilisé à l'opération g) correspond à la réunion des intersections du masque de l'opération d), dilaté, avec le masque de gravure de l'opération c) et avec un masque correspondant à la définition des régions actives du substrat.

9. Procédé selon la revendication 7 caractérisé par le fait que dans l'étape de gravure de l'oxyde prévue à l'opération c) et dans l'étape de gravure de la couche de protection prévue à l'opération g), on utilise un masque commun.

30 10. Procédé selon l'une des revendications 1 à 9 caractérisé par le fait que la couche de protection de l'opération g) est une couche de résine et que le dopage de l'opération h) se fait par implantation ionique.

11. Procédé selon l'une des revendications 1 à 9 caractérisé par le fait que la couche de protection de l'opération g) est une couche d'oxyde de silicium formée thermiquement et que le dopage se fait par diffusion.

1/5

Fig. 1

Fig. 2

Fig. 3

Fig. 4

2/5

Fig.5

Fig.6

Fig.7

3/5

Fig. 8

Fig. 9

Fig. 10

4 / 5

Fig. 11

Fig. 12

5 / 5

Fig. 13