(19) 日本国特許庁 (JP)

(12) 公表特許公報(A)

(11) 特許出願公表番号

特表2017-523640

(P2017-523640A)

(43) 公表日 平成29年8月17日(2017.8.17)

(51) Int.Cl.

H04L 25/02 (2006.01)

F 1

HO 4 L 25/02

HO 4 L 25/02

テーマコード

V 5K029

R

### テーマコード（参考）

審查請求 未請求 予備審查請求 有 (全 32 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2016-570081 (P2016-570081) |

| (86) (22) 出願日 | 平成27年5月11日 (2015. 5. 11)     |

| (85) 翻訳文提出日   | 平成28年11月29日 (2016. 11. 29)   |

| (86) 國際出願番号   | PCT/US2015/030209            |

| (87) 國際公開番号   | W02015/187307                |

| (87) 國際公開日    | 平成27年12月10日 (2015. 12. 10)   |

| (31) 優先権主張番号  | 14/298, 718                  |

| (32) 優先日      | 平成26年6月6日 (2014. 6. 6)       |

| (33) 優先権主張國   | 米国 (US)                      |

(71) 出願人 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ミンハン・チェン

アメリカ合衆国・カリフォルニア・921

21-1714・サン・ディエゴ・モアハ

ウス・ドライブ・5775

最終頁に続く

(54) 【発明の名称】 低電力および高性能レシーバに関するオフセット較正

(57)【要約】

本明細書では、低電力および高性能レシーバに関するオフセット較正を実行するためのシステムおよび方法について説明する。一実施形態では、オフセット較正のための方法は、サンプルラッチの第1の入力に第1の電圧を入力するステップと、サンプルラッチの第2の入力に第2の電圧およびオフセット相殺電圧を入力するステップとを含む。本方法はまた、オフセット相殺電圧を調整するステップと、オフセット相殺電圧が調整されるときにサンプルラッチの出力を観測するステップと、サンプルラッチの出力においてメタステークル状態が観測されたオフセット相殺電圧の値を記録するステップとを含む。本方法は、各電圧レベルに関するオフセット相殺電圧を決定するために第1の電圧に関する複数の異なる電圧レベルの各々について実行されてもよい。

**【特許請求の範囲】****【請求項 1】**

オフセット較正のための方法であって、

サンプルラッチの第1の入力に第1の電圧を入力するステップと、

前記サンプルラッチの第2の入力に第2の電圧およびオフセット相殺電圧を入力するステップと、

前記オフセット相殺電圧を調整するステップと、

前記オフセット相殺電圧が調整されるときに前記サンプルラッチの出力を観測するステップと、

前記サンプルラッチの前記出力においてメタステーブル状態が観測された前記オフセット相殺電圧の値を記録するステップと

を含む、方法。

10

**【請求項 2】**

前記第1の電圧と前記第2の電圧とが、ほぼ同じ振幅と互いに逆の極性とを有する、請求項1に記載の方法。

**【請求項 3】**

前記第1の電圧は、振幅が少なくとも50mVである、請求項2に記載の方法。

**【請求項 4】**

前記オフセット相殺電圧を調整するステップは、前記オフセット相殺電圧を生成するのに使用されるデジタルアナログ変換器(DAC)に複数の異なるオフセットコードをシーケンシャルに入力するステップを含む、請求項1に記載の方法。

20

**【請求項 5】**

前記オフセット相殺電圧の前記値を記録するステップは、前記複数のオフセットコードのうちの、前記メタステーブル状態が前記サンプルラッチの前記出力において観測されるオフセットコードを記録するステップを含む、請求項4に記載の方法。

**【請求項 6】**

オフセット較正のための装置であって、

サンプルラッチの第1の入力に第1の電圧を入力するための手段と、

前記サンプルラッチの第2の入力に第2の電圧およびオフセット相殺電圧を入力するための手段と、

前記オフセット相殺電圧を調整するための手段と、

前記オフセット相殺電圧が調整されるときに前記サンプルラッチの出力を観測するための手段と、

前記サンプルラッチの前記出力においてメタステーブル状態が観測された前記オフセット相殺電圧の値を記録するための手段と

を備える、装置。

30

**【請求項 7】**

前記第1の電圧と前記第2の電圧とが、ほぼ同じ振幅と互いに逆の極性とを有する、請求項6に記載の装置。

**【請求項 8】**

前記第1の電圧は、振幅が少なくとも50mVである、請求項7に記載の装置。

40

**【請求項 9】**

前記オフセット相殺電圧を調整するための手段は、前記オフセット相殺電圧を生成するのに使用されるデジタルアナログ変換器(DAC)に複数の異なるオフセットコードをシーケンシャルに入力するための手段を備える、請求項6に記載の装置。

**【請求項 10】**

前記オフセット相殺電圧の前記値を記録するための手段は、前記複数のオフセットコードのうちの、前記メタステーブル状態が前記サンプルラッチの前記出力において観測されるオフセットコードを記録するための手段を備える、請求項9に記載の装置。

**【請求項 11】**

10

20

30

40

50

データ信号を受信するように構成される入力と、出力とを有する加算増幅器と、前記加算増幅器の前記出力に結合される第1の入力と、第2の入力とを有する第1のサンプルラッチと、

前記第1のサンプルラッチの前記第2の入力に結合される出力を有する第1のデジタルアナログ変換器(DAC)であって、第1のオフセットコードを受信し、前記第1のオフセットコードを第1のオフセット相殺電圧に変換し、かつ前記第1のオフセット相殺電圧を前記第1のサンプルラッチの前記第2の入力に出力するように構成される第1のデジタルアナログ変換器と、

前記加算増幅器の前記出力に結合される第1の入力と、第2の入力とを有する第2のサンプルラッチと、

前記第2のサンプルラッチの前記第2の入力に結合される出力を有する第2のDACであって、第2のオフセットコードを受信し、前記第2のオフセットコードを第2のオフセット相殺電圧に変換し、かつ前記第2のオフセット相殺電圧を前記第2のサンプルラッチの前記第2の入力に出力するように構成される第2のDACとを、備えるレシーバ。

【請求項 1 2】

前記第2のサンプルラッチの前記第1の入力における前記データ信号に関する目標電圧レベルを決定し、かつ前記決定された目標電圧レベルに基づいて異なる電圧レベルに対応する複数のオフセットコードから前記第2のオフセットコードを選択するように構成されるプロセッサをさらに備える、請求項11に記載のレシーバ。

【請求項 1 3】

前記第2のDACは、しきい値電圧に対応するコードを受信し、前記受信されたコードを前記しきい値電圧に変換し、前記しきい値電圧を前記第2のサンプルラッチの前記第2の入力に出力するようにさらに構成され、前記しきい値電圧は、前記データ信号に関する目標電圧レベルに対応する、請求項11に記載のレシーバ。

【請求項 1 4】

前記しきい値電圧は、前記目標電圧レベルとほぼ同じ振幅を有する、請求項13に記載のレシーバ。

【請求項 1 5】

前記しきい値電圧は、振幅が少なくとも50mVである、請求項14に記載のレシーバ。

【請求項 1 6】

前記第2のサンプルラッチの出力を観測し、前記第2のサンプルラッチの前記出力においてメタステーブル状態が観測されるまで前記レシーバのパラメータを調整するように構成されるプロセッサをさらに備える、請求項13に記載のレシーバ。

【請求項 1 7】

前記プロセッサは、前記レシーバ内のイコライザのパラメータおよび前記レシーバ内の増幅器の利得のうちの少なくとも一方を調整することによって前記レシーバの前記パラメータを調整するように構成される、請求項15に記載のレシーバ。

【請求項 1 8】

前記第1のサンプルラッチの出力に結合される判定帰還型イコライザ(DFE)であって、前記第1のサンプルラッチの前記出力からの1つまたは複数のビットに基づいてシンボル間干渉(ISI)除去値を算出し、かつISI除去値に対応するISI除去コードを出力するように構成される判定帰還型イコライザと、

前記ISI除去コードをISI除去電圧に変換し、かつ前記ISI除去電圧を前記加算増幅器に出力するように構成される第3のDACであって、前記加算増幅器は、前記1つまたは複数のビットに対応するISIを除去するために前記データ信号に前記ISI除去電圧を印加する、第3のDACとをさらに備える、請求項11に記載のレシーバ。

【請求項 1 9】

受信データバスに結合される第1の入力と、第2の入力とを有するサンプルラッチと、前記サンプルラッチの前記第2の入力に結合される出力を有する第1のデジタルアナログ

10

20

30

40

50

変換器(DAC)と、

出力を有する第2のDACと、

前記第2のDACの前記出力を前記第2のサンプルラッチの前記第1の入力に選択的に結合するよう構成されるスイッチと、

データモードにおいて、前記スイッチを開くように構成され、較正モードにおいて、前記第2のDACの前記出力を前記サンプルラッチの前記第1の入力に結合するために前記スイッチを閉じるように構成される較正コントローラと

を備え、

前記データモードにおいて、前記サンプルラッチの前記第1の入力が、前記受信データバスからデータ信号を受信し、前記較正モードにおいて、前記較正コントローラが前記第2のDACにコードを入力し、前記第2のDACが、前記受信されたコードを較正電圧に変換し、かつ前記較正電圧における前記サンプルラッチのオフセットを較正するために前記較正電圧を前記サンプルラッチの前記第1の入力に出力するレシーバ。

10

【請求項 2 0】

前記較正電圧は、振幅が少なくとも50mVである、請求項19に記載のレシーバ。

【請求項 2 1】

前記較正コントローラは、前記較正モードにおいて、前記第1のDACに複数の異なるオフセットコードを入力することによって、前記第1のDACによって出力されたオフセット相殺電圧を前記サンプルラッチの前記第2の入力に調整し、前記オフセット相殺電圧が調整されるときに前記サンプルラッチの出力を観測し、かつ前記複数のオフセットコードのうちの、メタステーブル状態が前記サンプルラッチの前記出力において観測されるオフセットコードを記録するように構成される、請求項19に記載のレシーバ。

20

【請求項 2 2】

前記データモードにおいて、前記データ信号に関する目標電圧レベルが前記較正電圧に対応する場合に前記第1のDACに前記記録されたオフセットコードを入力するように構成されるプロセッサをさらに備える、請求項21に記載のレシーバ。

【請求項 2 3】

前記データモードにおいて、しきい値電圧に対応するしきい値コードを前記第1のDACに入力するように構成されるプロセッサをさらに備え、前記第1のDACは、前記しきい値コードを前記しきい値電圧に変換し、かつ前記しきい値コードを前記サンプルラッチの前記第2の入力に出力し、前記しきい値電圧は、前記データ信号に関する目標電圧レベルに対応する、請求項19に記載のレシーバ。

30

【請求項 2 4】

前記プロセッサは、前記データモードにおいて、前記第2のサンプルラッチの出力を観測し、かち前記第2のサンプルラッチの前記出力においてメタステーブル状態が観測されるまで前記レシーバのパラメータを調整するように構成される、請求項23に記載のレシーバ。

【請求項 2 5】

前記プロセッサは、前記データモードにおいて、前記レシーバ内のイコライザのパラメータおよび前記レシーバ内の増幅器の利得のうちの少なくとも一方を調整することによって前記レシーバの前記パラメータを調整するように構成される、請求項24に記載のレシーバ。

40

【請求項 2 6】

前記データ信号を増幅し、かつ前記増幅されたデータ信号を前記サンプルラッチの前記第1の入力に出力するように構成される増幅器をさらに備え、前記較正コントローラは、前記較正モードにおいて前記増幅器を無効化するように構成される、請求項19に記載のレシーバ。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本開示の態様は、概してレシーバに関し、より詳細には、低電力および高性能レシーバに関するオフセット較正に関する。

#### 【背景技術】

##### 【0002】

(たとえば、シリアルライザ/デシリアルライザ(SerDes)通信システムにおいて)チャネルを介して高速データ信号を受信するためにレシーバが使用される場合がある。レシーバは、受信されたデータ信号を複数のデータパス間で分割する場合があり、ここで、各データパスは(たとえば、データ信号からデータをサンプリングするための)サンプルラッチを備える。サンプルラッチにおけるオフセット電圧は、(たとえば、レシーバにおける構成要素の不整合に起因して)高電圧である場合があり、各サンプルラッチのオフセット電圧が異なる場合があり、それによってレシーバの性能が悪影響を受ける(たとえば、サンプルラッチにおけるデータアイを閉ざす)。したがって、レシーバの性能を向上させるには各サンプルラッチにおけるオフセット電圧を相殺(cancel)することが望ましい。

10

#### 【発明の概要】

##### 【課題を解決するための手段】

##### 【0003】

以下に、1つまたは複数の実施形態を基本的に理解できるようにそのような実施形態を簡略的に要約する。この概要は、すべての考察された実施形態の包括的な概要ではなく、すべての実施形態の主要な要素または重要な要素を識別するものではなく、いずれかの実施形態またはすべての実施形態の範囲を定めるものでもない。その唯一の目的は、後に提示されるより詳細な説明の導入として、1つまたは複数の実施形態のいくつかの概念を簡略化された形で提示することである。

20

##### 【0004】

第1の態様に従って、オフセット較正のための方法について説明する。本方法は、サンプルラッチの第1の入力に第1の電圧を入力するステップと、サンプルラッチの第2の入力に第2の電圧およびオフセット相殺電圧を入力するステップとを含む。本方法はまた、オフセット相殺電圧を調整するステップと、オフセット相殺電圧が調整されるときにサンプルラッチの出力を観測するステップと、サンプルラッチの出力においてメタステーブル状態が観測されたオフセット相殺電圧の値を記録するステップとを含む。

30

##### 【0005】

第2の態様は、オフセット較正のための装置に関する。本装置は、サンプルラッチの第1の入力に第1の電圧を入力するための手段と、サンプルラッチの第2の入力に第2の電圧およびオフセット相殺電圧を入力するための手段とを含む。本装置はまた、オフセット相殺電圧を調整するための手段と、オフセット相殺電圧が調整されるときにサンプルラッチの出力を観測するための手段と、サンプルラッチの出力においてメタステーブル状態が観測されたオフセット相殺電圧の値を記録するための手段とを備える。

##### 【0006】

第3の態様は、レシーバに関する。本レシーバは、データ信号を受信するように構成される入力と、出力とを有する加算増幅器を備える。レシーバはまた、加算増幅器の出力に結合される第1の入力と、第2の入力とを有する第1のサンプルラッチと、第1のサンプルラッチの第2の入力に結合される出力を有する第1のデジタルアナログ変換器(DAC)であって、第1のオフセットコードを受信し、第1のオフセットコードを第1のオフセット相殺電圧に変換し、第1のオフセット相殺電圧を第1のサンプルラッチの第2の入力に出力するように構成される第1のデジタルアナログ変換器とを備える。レシーバは、加算増幅器の出力に結合される第1の入力と、第2の入力と、を有する第2のサンプルラッチと、第2のサンプルラッチの第2の入力に結合される出力を有する第2のDACであって、第2のオフセットコードを受信し、第2のオフセットコードを第2のオフセット相殺電圧に変換し、第2のオフセット相殺電圧を第2のサンプルラッチの第2の入力に出力するように構成される第2のDACとをさらに備える。

40

##### 【0007】

50

第4の態様は、レシーバに関係する。本レシーバは、レシーバデータパスに結合される第1の入力と、第2の入力と、を有するサンプルラッチと、サンプルラッチの第2の入力に結合される出力を有する第1のデジタルアナログ変換器(DAC)とを備える。レシーバはまた、出力を有する第2のDACと、第2のDACの出力を第2のサンプルラッチの第1の入力に選択的に結合するように構成されるスイッチとを備える。レシーバは、データモードにおいて、スイッチを開くように構成され、較正モードにおいて、第2のDACの出力をサンプルラッチの第1の入力に結合するためにスイッチを閉じるように構成される較正コントローラをさらに備える。データモードにおいて、サンプルラッチの第1の入力が、受信データパスからデータ信号を受信し、較正モードにおいて、較正コントローラが第2のDACにコードを入力し、第2のDACが、受信されたコードを較正電圧に変換し、較正電圧におけるサンプルラッチのオフセットを較正するために較正電圧をサンプルラッチの第1の入力に出力する。

10

#### 【0008】

上記および関連する目的を達成するために、1つまたは複数の実施形態は、以下において完全に記載され、特許請求の範囲において特に指摘される特徴を備える。以下の説明および添付の図面は、1つまたは複数の実施形態のいくつかの例示的な態様を詳細に説明する。しかしながら、これらの態様は、様々な実施形態の原理が採用され得る様々な方法のうちのほんのいくつかしか示しておらず、記載される実施形態は、そのようなすべての態様およびそれらの均等物を含むものとする。

20

#### 【図面の簡単な説明】

#### 【0009】

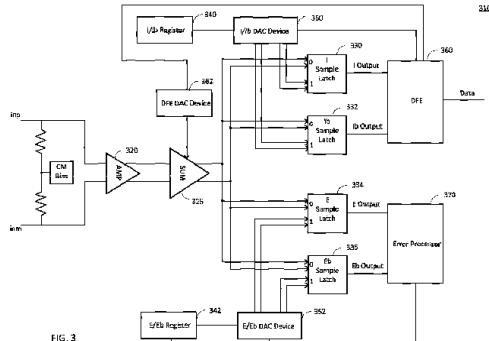

【図1】複数のデータパスと各データパスの別個の加算増幅器とを有するレシーバの例を示す図である。

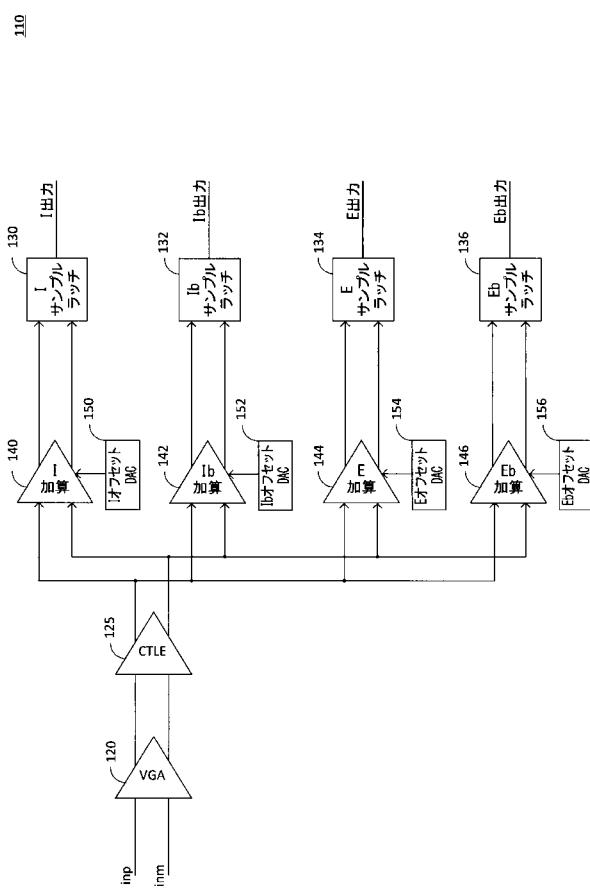

【図2】入力信号レベルの関数としてのラッチにおけるオフセットを示すプロットである。

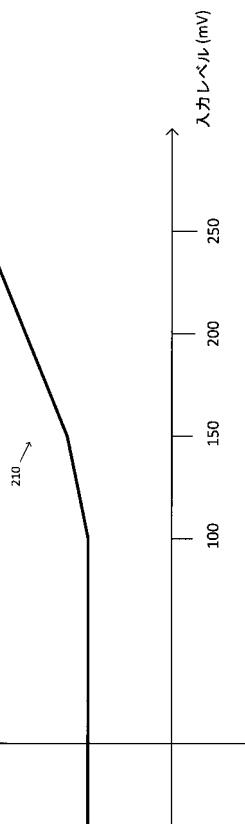

【図3】本開示の一実施形態による複数のデータパスを駆動する加算増幅器を備えるレシーバを示す図である。

30

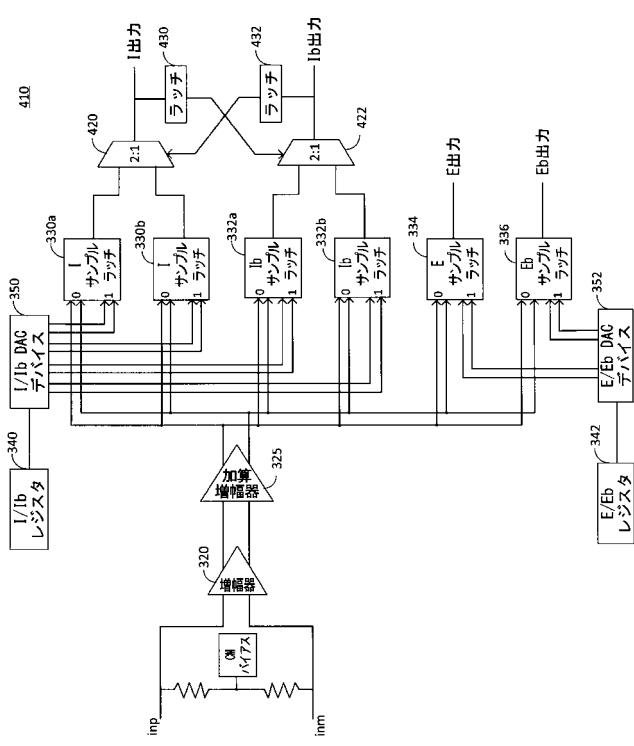

【図4】本開示の一実施形態による、ループ展開を行うレシーバを示す図である。

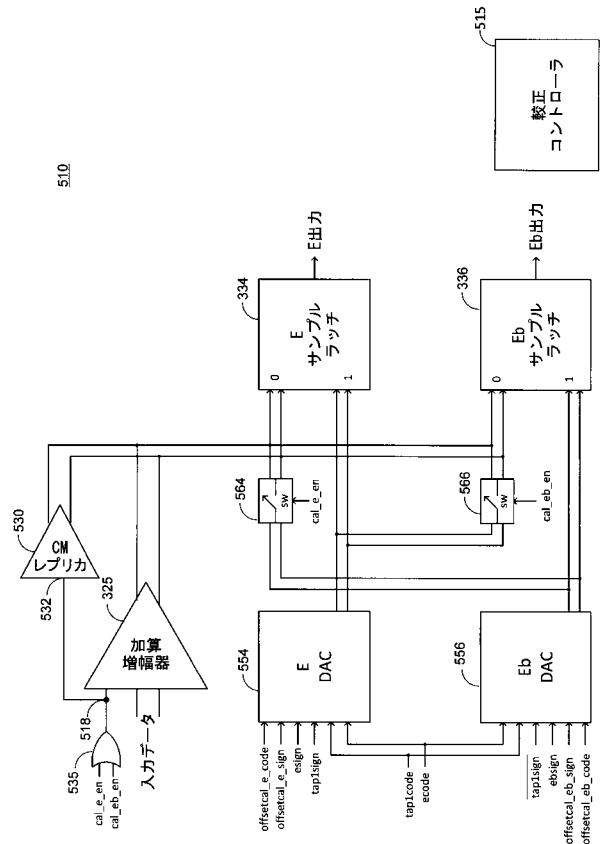

【図5】本開示の一実施形態による、大信号条件においてオフセット較正を実行するためのシステムを示す図である。

40

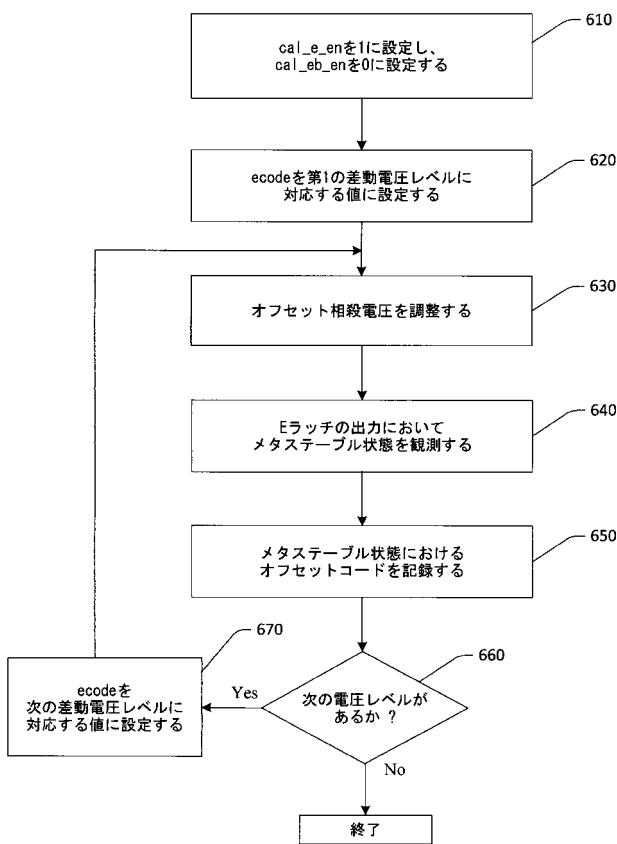

【図6】本開示の一実施形態による、エラー(E)ラッチに関する大信号条件においてオフセット較正を実行するための方法を示すフローチャートである。

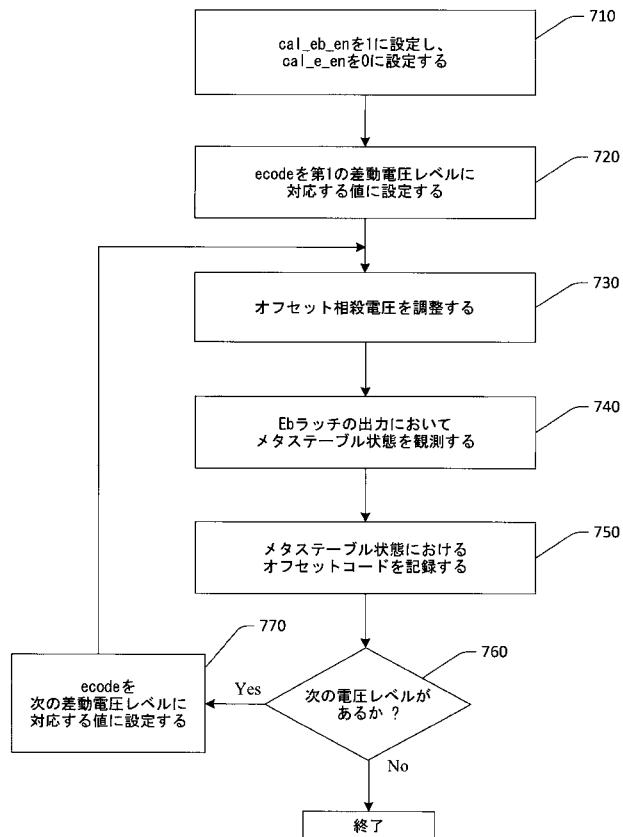

【図7】本開示の一実施形態による、Ebラッチに関する大信号条件においてオフセット較正を実行するための方法を示すフローチャートである。

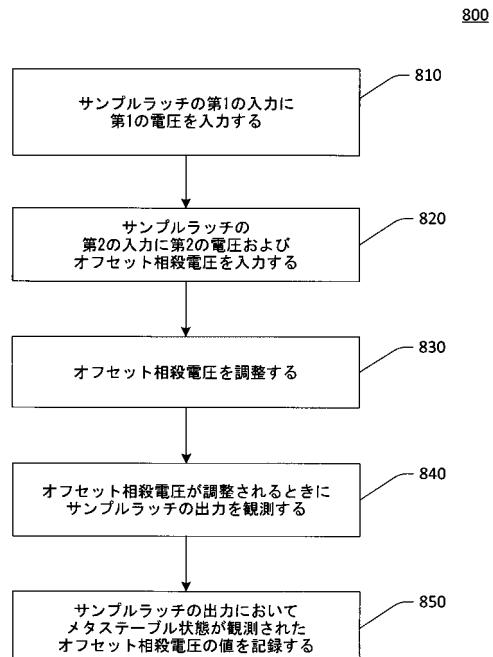

【図8】本開示の一実施形態による、オフセット較正のための方法を示すフローチャートである。

#### 【発明を実施するための形態】

#### 【0010】

添付の図面に関して以下に記載する詳細な説明は、様々な構成の説明として意図されており、本明細書において説明する概念が実践される場合がある唯一の構成を表すことは意図されていない。詳細な説明は、様々な概念を十分に理解できるようにするための具体的な詳細を含む。しかしながら、これらの具体的な詳細なしにこれらの概念が実施される場合があることは当業者には明らかであろう。場合によっては、そのような概念を曖昧にするのを避けるために、よく知られている構造および構成要素がブロック図の形で示される。

#### 【0011】

図1は、高速通信用のSerDesシステムにおいて使用される場合があるレシーバ110の例を示す。SerDesシステムでは、トランスマッタにおけるパラレルデータがシリアル高速差動信号として直列化され、差動チャネルを介してレシーバに送信されてもよい。レシーバは、信号からデータ(たとえば、データビット)を回復するために信号を増幅し信号をサンプリングしてもよい。回復されたデータは、さらに処理できるようにパラレルデータとして

50

デシリアルライズされてもよい。図1の例では、レシーバ110は、チャネルから高速差動信号("inp"および"inm"として示される)を受信する。トランスマッタとレシーバ110は、同じチップ上に位置してもあるいは異なるチップ上に位置してもよい。チップ間通信では、チャネルは、差動ワイヤ対、ケーブル、光ファイバーなどを備えてよい。

#### 【0012】

レシーバ110は、可変利得増幅器(VGA)120と連続時間線形イコライザ(CTLE)125とを備える。VGA120は、受信された差動信号を可変利得によって増幅するよう構成され、CTLE125は、チャネルによる信号の高周波減衰に起因する信号のひずみを相殺するよう構成される。

#### 【0013】

CTLE125の後、差動信号は、レシーバ110内の4つのデータバス間で分割される。各データバスは、サンプルラッチ130～136と、加算増幅器140～146と、デジタルアナログ変換器(DAC)150～156とを備える。各DAC150～156は、デジタルオフセットコードを受信し、受信されたオフセットコードをオフセット相殺電圧に変換し、オフセット相殺電圧がそれぞれの加算増幅器140～146に出力される。各加算増幅器140～146は、それぞれのDAC150～156からのオフセット相殺電圧をそれぞれのデータバスにおける信号に印加する。オフセット相殺電圧は、たとえば、それぞれのラッチにおける構成要素(たとえば、トランジスタ)不整合および/またはその他の原因によるそれぞれのラッチの入力におけるオフセット電圧を相殺するのに使用される。オフセット電圧はラッチごとに異なってよい。したがって、各データバスにおけるオフセット相殺電圧は、それぞれのDAC150～156へのそれぞれのオフセットコード入力によって個々に制御される。各データバスのオフセット相殺電圧を決定するためのオフセット較正プロセスについて以下にさらに説明する。

10

20

30

40

50

#### 【0014】

サンプルラッチは、同相(I)サンプルラッチ130と180度位相外れIbサンプルラッチ132とを含む。Iサンプルラッチ130およびIbサンプルラッチ132の各々は、入力データ信号のレートの2分の1のレートで入力信号からデータをサンプリングする。より詳細には、各ラッチ130および132は、入力データ信号を1データビットおきにサンプリングする。たとえば、Iラッチサンプルラッチ130が偶数データビットをサンプリングし、Ibサンプルラッチ132が奇数データビットをサンプリングしてもよく、あるいはIラッチサンプルラッチ130が奇数データビットをサンプリングし、Ibサンプルラッチ132が偶数データビットをサンプリングしてもよい。したがって、IラッチとIbラッチは協働して、入力データ信号からデータビットを回復する。この例では、Iラッチ130およびIbラッチ132の各々が2分の1レートクロックを使用してデータをサンプリングしてもよく、Iラッチ130が、クロックの立上りエッジ上でデータをサンプリングし、Ibラッチ132が、クロックの立下りエッジ上でデータをサンプリングするか、あるいはIラッチ130が、クロックの立下りエッジ上でデータをサンプリングし、Ibラッチ132が、クロックの立上りエッジ上でデータをサンプリングする。

#### 【0015】

一態様では、Iサンプルラッチ130およびIbサンプルラッチ132の各々は、約0ボルトのしきい値電圧に基づいてデータ信号のサンプル(データサンプル)のビット値を決定してもよい。たとえば、ビット値1が正極を有する差動電圧に対応し、ビット値0が負極を有する差動電圧に対応してもよい。この場合、差動電圧は、差動入力の2つのライン間の電圧である。この例では、Iラッチ130およびIbラッチ132の各々は、データサンプルの差動電圧が0ボルトよりも高い場合には1のビット値を、データサンプルの差動電圧が0ボルトよりも低い場合には0のビット値を決定してもよい。

#### 【0016】

サンプルラッチは、エラー(E)サンプルラッチ134とEbサンプルラッチ136とを含んでもよく、Eサンプルラッチ134とEbサンプルラッチ136は、以下にさらに説明するように差動データ信号の電圧レベル(すなわち、差動入力の2つのライン間の電圧レベル)を検出するのに使用される。Eサンプルラッチ134は、Iサンプルラッチ130と同相のデータ信号をサン

プリングし、Ebサンプルラッチ136は、Ibサンプルラッチ132と同相のデータ信号をサンプリングする。データ信号の電圧レベルを検出するため、EサンプルラッチおよびEbサンプルラッチの各々は、目標電圧レベル(たとえば、少なくとも50mVの差動電圧レベル)に対応するしきい値電圧に基づいてデータサンプルに関するビット値判定を下す。たとえば、Eラッチ134およびEbラッチ136の各々は、データサンプルの電圧レベルが目標電圧レベルよりも高い場合には1のビット値を、データサンプルの電圧レベルが目標電圧レベルよりも低い場合には0のビット値を決定してもよい。したがって、この例では、ビット値1は、データ信号の電圧レベルが目標電圧レベルよりも高いことを示し、ビット値0は、データ信号の電圧レベルが目標電圧レベルよりも低いことを示す。目標電圧レベルは、レシーバ110の増幅器(たとえば、加算増幅器140～146)の線形範囲内である間にデータ信号を良好に検出するのを可能にする電圧レベルに対応してよい。

10

## 【0017】

Eラッチ134におけるデータ信号の電圧レベルが目標電圧レベルよりも高いかそれとも低いかを正確に検出するにはオフセット電圧相殺が重要である。この理由としては、データ信号の電圧レベルが目標電圧レベルであるとき、Eラッチ134の出力はメタステーブル状態であるべき(0と1の間でトグルすべき)であることが挙げられる。しかし、オフセット電圧に起因して、データ信号の電圧レベルが目標電圧レベルからずれているときにEラッチ134の出力がメタステーブル状態になり、Eラッチ134の精度が低下する。これは、以下にさらに説明するようにオフセット電圧を相殺することによって相殺される。上記の説明はEbラッチ136にも当てはまる。

20

## 【0018】

この実施形態では、エラープロセッサ(図1には示されていない)は、Eラッチ134およびEbラッチ136の出力がメタステーブル状態に達する(0と1の間でトグルする)まで、Eラッチ134およびEbラッチ136の出力を観測し、レシーバ110内のイコライザ(たとえば、CTLE125)の1つまたは複数のパラメータおよび/または増幅器(たとえば、VGA120)の利得を調整してもよい。これは、データ信号の電圧レベルが目標電圧レベルにほぼ等しいときに行われる。したがって、エラープロセッサは、Eラッチ134およびEbラッチ136の出力を使用してデータ信号の所望の電圧レベルを実現してもよい。

## 【0019】

次に、ラッチに関するオフセット相殺電圧を決定するためのオフセット較正プロセスについて以下に説明する。まず、データパスへの差動入力信号が約0ボルトに設定される。各ラッチについて、それぞれのオフセット相殺電圧の大きさおよび/または極性は、ラッチの出力がメタステーブル状態に達する(0と1の間でトグルする)までオフセットコードをそれぞれのDACに調整することによって調整される。これは、オフセット相殺電圧がラッチにおけるオフセット電圧を相殺したときに行われる。したがって、各ラッチのオフセット相殺電圧は、約0ボルトの差動入力信号におけるそれぞれのオフセット電圧を相殺する電圧である。このオフセット較正プロセスでは、小信号条件(すなわち、小差動入力電圧レベル)におけるオフセットを較正する。

30

## 【0020】

この較正手法に関する問題は、オフセット較正が小信号(small signal)条件(小差動入力電圧レベル)において実行されている間、データ信号の電圧レベルを検出するためにEサンプルラッチ134およびEbサンプルラッチ136が大信号(large signal)条件(大差動入力電圧レベル)において使用されることである。大信号条件におけるラッチのオフセット電圧は、たとえば、ラッチの線形性に起因して小信号条件におけるラッチのオフセット電圧と著しく異なる場合がある。この点に関して、図2は、入力信号レベル(差動入力電圧レベル)の関数としてのラッチの入力におけるオフセット電圧210の例を示す。図2の例に示すように、小信号条件におけるオフセット電圧(たとえば、約0ボルト)は、大信号条件におけるオフセット電圧(たとえば、200mV)と著しく異なる場合がある。その結果、小信号条件において決定されたEラッチ134およびEbラッチ136に関するオフセット相殺電圧は、大信号条件におけるEラッチ134およびEbラッチ136のオフセット電圧を適切に相殺せず、レシ

40

50

ーバ110の性能に悪影響を及ぼす。

【0021】

レシーバ110は、電力消費量が多くなる場合もある。この理由としては、レシーバ110が各サンプルラッチ130～136に別個の加算増幅器140～146を備え、各加算増幅器140～146が比較的大量の電力を消費することが挙げられる。

【0022】

図3は、本開示の一実施形態による、低電力高性能レシーバ310を示す図である。レシーバ310は、増幅器320と、加算増幅器325と、Iサンプルラッチ330およびIbサンプルラッチ332と、Eサンプルラッチ334およびEbサンプルラッチ336とを備える。

【0023】

レシーバ310は、各ラッチ330～336に関するオフセット相殺電圧が対応する加算増幅器ではなくラッチに注入されるという点で図1のレシーバ110と異なる。これによって、加算増幅器320は複数のラッチ330～336を駆動することができ、それによって、レシーバにおける加算増幅器の数が少なくなり、したがって、電力消費量が低減する。

【0024】

以下にさらに説明するように、Eサンプルラッチ334およびEbサンプルラッチ336に関するオフセット較正は大信号条件において実行され、Eラッチ334およびEbラッチ336について従来の手法と比べてずっと正確なオフセット相殺電圧が得られ、オフセット較正は、すべてのラッチについて小信号条件において実行される。これによって、Eラッチ334およびEbラッチ336についてずっと良好なオフセット相殺が行われ、レシーバ310の性能が大幅に向上する。

【0025】

以下の説明では、レシーバは、「較正モード」または「データモード」において動作するものとして説明する。本明細書で使用する「較正モード」いう用語は、ラッチのうちの1つまたは複数についてオフセット相殺電圧が決定される動作モードを指してもよい。「データモード」という用語は、レシーバがレシーバ110の入力において受信されたデータ信号を処理する動作モードを指してもよい。

【0026】

データモードにおいて、増幅器320は差動入力データ信号("inp"および"inm"と示される)を増幅する。加算増幅器325は、以下にさらに説明するようにシンボル間干渉 ISI)を補償するために入力データバスに電圧を印加する。加算増幅器325の出力は、複数のデータバス間で分割され、各データバスはラッチ330～336のうちの1つに対応する。その結果、加算増幅器325はラッチ330～336を駆動する。各データバスは、それぞれのラッチ330～336の第1の差動入力("0"と示される)に結合される。

【0027】

レシーバ310はまた、Iラッチ330およびIbラッチ332の出力に結合される判定帰還型イコライザ(DFE)360と、Eラッチ334およびEbラッチ336の出力に結合されるエラーブロセッサ370とを備える。DFE360およびエラーブロセッサ370の動作については、以下にさらに説明する。

【0028】

レシーバ310は、I/Ibレジスタ340とI/Ib DACデバイス350とをさらに備える。I/Ib DACデバイス350は、Iサンプルラッチ330の第2の差動入力("1"と示される)に結合される第1の差動出力と、Ibサンプルラッチ332の第2の差動入力("1"と示される)に結合される第2の差動出力とを有する。I/Ib DACデバイス350の第1の出力は、Iラッチ330におけるオフセット電圧を相殺するためにIラッチ330の第2の差動入力(1)にオフセット相殺電圧を出力し、ここで、オフセット相殺電圧は、第2の差動入力(1)の2つのライン間の電圧である。同様に、I/Ib DACデバイス350の第2の出力は、Ibラッチ332におけるオフセット電圧を相殺するためにIbラッチ332の第2の差動入力(1)にオフセット相殺電圧を出力し、ここで、オフセット相殺電圧は、第2の差動入力(1)の2つのライン間の電圧である。

【0029】

10

20

30

40

50

各ラッチ330および332のオフセット相殺電圧は、I/Ibレジスタ340に記憶された対応するデジタルオフセットコードによって指定されてもよい。この実施形態では、I/Ibレジスタ340は、対応するオフセット相殺電圧を生成するためにI/Ib DACデバイス350に各ラッチ330および332のオフセットコードを入力する。I/Ib DACデバイス350は、各ラッチの別個のDACを備えててもよく、ここで、各ラッチのDACは、I/Ibレジスタ340からラッチに関するオフセットコードを受信し、対応するオフセット相殺電圧をラッチに出力する。小信号条件におけるIラッチ330およびIbラッチ332に関するオフセット相殺電圧を決定するためのオフセット較正プロセスについて以下にさらに説明する。

#### 【0030】

レシーバ310は、E/Ebレジスタ342とE/Eb DACデバイス352とをさらに備える。E/Eb DACデバイス352は、Eサンプルラッチ334の第2の差動入力("1"と示される)に結合される第1の差動出力と、Ebサンプルラッチ336の第2の差動入力("1"と示される)に結合される第2の差動出力とを有する。E/Eb DACデバイス352の第1の出力は、Eラッチ334におけるオフセット電圧を相殺するためにEラッチ334の第2の差動入力(1)にオフセット相殺電圧を出力し、ここで、オフセット相殺電圧は、第2の差動入力(1)の2つのライン間の電圧である。同様に、E/Eb DACデバイス352の第2の出力は、Ebラッチ336におけるオフセット電圧を相殺するためにEbラッチ336の第2の差動入力(1)にオフセット相殺電圧を出力し、ここで、オフセット相殺電圧は、第2の差動入力(1)の2つのライン間の電圧である。以下にさらに説明するように、Eラッチ334およびEbラッチ336へのオフセット相殺電圧は、データ信号に関する目標電圧レベルに応じて調整されてもよい。

10

20

30

40

50

#### 【0031】

一実施形態では、E/Ebレジスタ342は、Eラッチ334に関する複数のデジタルオフセットコードを記憶し、ここで、各オフセットコードは、データ信号に関する異なる目標電圧レベルに対応する。同様に、E/Ebレジスタ342は、Ebラッチ336に関する複数のデジタルオフセットコードを記憶し、ここで、各オフセットコードは、データ信号に関する異なる目標電圧レベルに対応する。この実施形態では、E/Ebレジスタ342は、特定の目標電圧レベルに関して、Eラッチ334およびEbラッチ336に関する対応するオフセットコードをE/Eb DACデバイス352に出力する。E/Eb DACデバイス352は、オフセットコードを対応するオフセット相殺電圧に変換し、オフセット相殺電圧をEラッチ334およびEbラッチ336に出力する。E/Eb DACデバイス352は、各ラッチの別個のDACを備えててもよく、ここで、各ラッチのDACは、E/Ebレジスタ342からラッチに関するオフセットコードを受信し、対応するオフセット相殺電圧をラッチに出力する。大信号条件におけるEラッチ334およびEbラッチ336に関するオフセット相殺電圧を決定するためのオフセット較正プロセスについて以下にさらに説明する。

#### 【0032】

次に、本開示の実施形態によるDFE360の動作について説明する。DFE360は、入力データ信号におけるシンボル間干渉(ISI)を補償するのに使用される。例示的な一実施形態では、DFE360は5タップDFE360である。この実施形態では、DFE360は、各データサンプルについて、直近の5つのデータビットからISIを除去するために直近に判定された5つのビットに基づいてISI除去値を算出する。ISI除去値は5つのタップ値を含んでもよい。各タップ値は、直近に判定された5つのビットのうちの異なる1ビットに基づいて算出され、それぞれのビットからISIを除去するのに使用される。たとえば、タップ値のうちの第1のタップ値(タップ1値と示される)は、現在のデータサンプルの直前のビットからISIを除去するために直近に判定されたビットに基づいて算出されてもよい。各タップ値は、タップ振幅(magnitude)とタップ符号を含んでもよく、タップ振幅は、タップ値の振幅を指定し、タップ符号は、タップ値の極性を指定する。

#### 【0033】

DFE360は、データサンプルに関するタップ値を算出した後、対応するタップコードをDFE DACデバイス362に出力してもよい。DFE DACデバイス362は、タップコードをタップ値に対応するタップ電圧に変換し、タップ電圧を加算増幅器325に出力する。加算増幅器325は

、入力データ信号にタップ電圧を印加して ISI を除去する。

【 0 0 3 4 】

図4は、別の実施形態によるレシーバ410を示す。レシーバ410は、1ラッチ330aおよび330bの対と1bラッチ332aおよび332bの対とを備えることを除いて図3のレシーバ310と同様である。説明しやすいように、DFE360およびエラープロセッサ370は図4に示されていない。1ラッチ330aおよび330bの対および1bラッチ332aおよび332bの対は、以下にさらに説明するように、ループ展開による判定フィードバック等化を可能にする。

【 0 0 3 5 】

高速レシーバにおいて判定フィードバック等化を使用する場合の問題は、直前のビットを現在のデータサンプルに使用されるように短時間(たとえば、2分の1クロックサイクル)で判定する必要があることである。ループ展開では、レシーバは直前のビットを判定するのにより長い時間をかけることができ、一方、直前のビットに関してISI除去を行うこともできる。ループ展開ではこれを実現するのに、1つのラッチでは直前のビットが1であると仮定し、別のラッチでは直前のビットが0であると仮定することによってデータサンプルのISI除去を実行する。直前のビットの値が判定された後、正しいビット値に対応するラッチの出力が選択される。したがって、ループ展開は、直前のビットの両方の可能な値についてISI除去を実行することと、正しい値が判明した後、正しいビット値に対応するラッチの出力を選択することとを含む。ループ展開では、データサンプルのビット値を判定するためのタイミング制約を緩和することによって電力消費量を低減させる。

【 0 0 3 6 】

動作時には、DFE360は、DFEの第2のタップ～第5のタップに関するタップ値(タップ2値～タップ5値と示される)を算出し、対応するタップコードをDFE DACデバイス362に出力する。DFE DACデバイス362は、タップコードを第2のタップ値～第5のタップ値に対応するタップ電圧に変換し、タップ電圧を加算増幅器325に出力する。加算増幅器325は、入力データ信号にタップ電圧を印加する。したがって、この実施形態では、DFEの第2のタップ～第5のタップに関するISI除去が加算増幅器325において実行される。第1のタップに関するISI除去は、以下にさらに説明するように第1のタップのループ展開を可能にするためにラッチにおいて実行される。一般に、nタップDFEに関しては、第2のタップ～第nのタップに関するISI除去が加算増幅器325において実行されてもよい。

【 0 0 3 7 】

I/Ib DACデバイス350は、直前のビットが1であると仮定されるタップ1値に対応するIラッチ330aにタップ電圧を出力し、直前のビットが0であると仮定されるタップ1値に対応するIラッチ330bにタップ電圧を出力するか、あるいは直前のビットが0であると仮定されるタップ1値に対応するIラッチ330aにタップ電圧を出力し、直前のビットが1であると仮定されるタップ1値に対応するIラッチ330bにタップ電圧を出力する。Iラッチ330aおよび330bに関するタップ1値は、同じタップ振幅と互いに逆のタップ符号(すなわち、同じ振幅と互いに逆の極性)とを有してもよい。したがって、Iラッチ330aでは、直前のビットが1であると仮定してISI除去が実行され、Iラッチ330bでは、直前のビットが0であると仮定してISI除去が実行され、あるいはIラッチ330aでは、直前のビットが0であると仮定してISI除去が実行され、Iラッチ330bでは、直前のビットが1であると仮定してISI除去が実行される。

〔 0 0 3 8 〕

同様に、I/Ib DACデバイス350は、直前のビットが1であると仮定されるタップ1値に対応するIbラッチ332aにタップ電圧を出力し、直前のビットが0であると仮定されるタップ1値に対応するIbラッチ332bにタップ電圧を出力するか、あるいは直前のビットが0であると仮定されるタップ1値に対応するIbラッチ332aにタップ電圧を出力し、直前のビットが1であると仮定されるタップ1値に対応するIbラッチ332bにタップ電圧を出力する。Ibラッチ332aおよび332bに関するタップ1値は、同じタップ振幅と逆のタップ符号とを有してもよい。したがって、Ibラッチ332aでは、直前のビットが1であると仮定してISI除去が実行され、Ibラッチ332bでは、直前のビットが0であると仮定してISI除去が実行され、あるいは

はIbラッチ332aでは、直前のビットが0であると仮定してISI除去が実行され、Ibラッチ332bでは、直前のビットが1であると仮定してISI除去が実行される。

【0039】

Iラッチ330aおよび330bの出力は第1のマルチプレクサ420に入力される。データサンプルに関して直前のビットの値が判明した後、第1のマルチプレクサ420は、正しいビット値に対応するIラッチ330aおよび330bの出力を選択し、選択された出力(I出力と示される)をDFE360に出力する。同様に、Ibラッチ332aおよび332bの出力は第2のマルチプレクサ422に入力される。データサンプルに関して直前のビットの値が判明した後、第2のマルチプレクサ422は、正しいビット値に対応するIbラッチ332aおよび332bの出力を選択し、選択された出力(Ib出力と示される)をDFE360に出力する。

10

【0040】

第1のマルチプレクサ420に関しては、Iラッチが偶数ビットをサンプリングし、Ibラッチが奇数ビットをサンプリングするため、第2のマルチプレクサ422の出力(Ib出力)によって直前のビットの値が得られる。第2のマルチプレクサ422の出力(Ib出力)は、前のビットの値の判定に関するタイミング制約が満たされるように、第1のマルチプレクサ420に出力される前にラッチ432によってラッチされる。第2のマルチプレクサ422では、第1のマルチプレクサ420の出力(I出力)によって直前のビットの値が得られる。第1のマルチプレクサ420の出力(I出力)は、前のビットの値の判定に関するタイミング制約が満たされるように、第2のマルチプレクサ422に出力される前にラッチ430によってラッチされる。

20

【0041】

したがって、この実施形態では、I/Ib DACデバイス350によるIラッチおよびIbラッチ330a～332bの各々への電圧出力は、それぞれのオフセット相殺電圧とそれぞれのタップ1値に対応するタップ電圧との和を含む。

【0042】

次に、本開示の一実施形態による、較正モードにおけるIラッチおよびIbラッチ330a～332bに関するオフセット相殺電圧を決定するためのオフセット較正プロセスについて説明する。

【0043】

較正モードにおけるIラッチおよびIbラッチ330a～332bのオフセットを較正するために、加算増幅器325の差動出力電圧(差動出力の2つのライン間の電圧)は約0ボルトに設定される。たとえば、加算増幅器325の出力状態を制御するために制御信号が使用されてもよい。制御信号がアサートされると、加算増幅器325の差動出力電圧が0ボルトに設定され、一方、同相モード電圧(差動出力の2つのラインに共通する電圧)は変更されない。

30

【0044】

加算増幅器325の差動出力が0ボルトに設定された後、IラッチおよびIbラッチ330a～332bが較正される。各ラッチに関して、ラッチの出力がメタステーブル状態に達する(1と0の間でトグルする)まで、それぞれのオフセット相殺電圧、すなわち、第2の差動入力(1)の2つのライン間の電圧の振幅および/または極性が調整される。これは、ラッチに対してI/Ib DACデバイス350に異なるオフセットコードをシーケンシャルに入力し、ラッチの出力を観測することによって行われる。ラッチの出力は、オフセット相殺電圧がラッチの入力においてオフセット電圧を相殺したときにメタステーブル状態に達する。ラッチに関してオフセット相殺電圧によってメタステーブル状態が得られたことが判定された後、ラッチに関してI/Ibレジスタ340に対応するオフセットコードが記録される。

40

【0045】

較正プロセスの終了時に、I/Ibレジスタ340は、IラッチおよびIbラッチ330a～332bの各々に関するオフセットコードを含む。データモードにおいて、I/Ibレジスタ340内の各ラッチに関するオフセットコードがI/Ib DACデバイス350に入力される。I/Ib DACデバイス350は、各ラッチに関するオフセットコードを対応するオフセット相殺電圧に変換し、オフセット相殺電圧をラッチに出力する。

【0046】

50

次に、本開示の実施形態による、データモードにおけるEサンプルラッチ334およびEbサンプルラッチ336の動作について説明する。上述のように、Eラッチ334およびEbラッチ336の各々の出力は、データ信号の電圧レベルが目標電圧レベルよりも高いかそれとも低いかを示す。一実施形態では、E/Eb DACデバイス352は、目標電圧レベルに対応するEラッチ334の第2の差動入力(1)にしきい値電圧を入力する。以下にさらに説明するように、しきい値電圧は、目標電圧レベルとほぼ同じ振幅および逆の極性を有する場合がある。E/Eb DACデバイス352も、Eラッチ334におけるオフセット電圧を相殺するためにEラッチ334の第2の差動入力(1)にオフセット相殺電圧を入力する。以下にさらに説明するように、オフセット相殺電圧は目標電圧レベルの関数であってもよい。したがって、E/Eb DACデバイス352は、第2の差動入力(1)にしきい値電圧とオフセット相殺電圧の和を入力する。第1の差動入力(0)におけるデータ信号の電圧レベルが目標電圧レベルとほぼ等しい場合、Eラッチ334におけるオフセット電圧がオフセット相殺電圧によって相殺されると仮定すると、Eラッチ334の出力はメタステーブル状態である。以下にさらに説明するように、目標電圧レベルはタップ1値を組み込んでもよい。

10

## 【0047】

この実施形態では、エラープロセッサ370は、データ信号の電圧レベルが目標電圧レベルと等しいかどうかを判定するためにEラッチ334の出力を観測する。データ信号の電圧レベルが目標電圧レベルと等しくない(すなわち、Eラッチ334の出力がメタステーブル状態ではない)場合、エラープロセッサ370は、データ信号の電圧レベルが目標電圧レベルとほぼ等しくなる(すなわち、Eラッチ334の出力がメタステーブル状態に達する)までDFE360の1つまたは複数のタップの振幅および/または増幅器(たとえば、増幅器320)の利得を調整してもよい。

20

## 【0048】

同様に、E/Eb DACデバイス352は、目標電圧レベルに対応するEbラッチ336の第2の差動入力(1)にしきい値電圧を入力する。しきい値電圧は、目標電圧レベルとほぼ同じ振幅および逆の極性を有する場合がある。Ebラッチ336に関するしきい値電圧は、Eラッチ334に関するしきい値電圧とほぼ同じであってもよい。たとえば、Eラッチ334およびEbラッチ336は、同じ極性(たとえば、"1"ビットに対応する極性)におけるデータ信号の電圧レベルを測定してもよい。代替的に、Ebラッチ336に関するしきい値電圧について、振幅をEラッチ334に関するしきい値電圧とほぼ同じにし、極性を逆にしてもよい。これは、たとえば、データ信号の異なる極性におけるデータ信号の電圧レベルを測定するためにEラッチ334およびEbラッチ336が使用されるときに行われてもよい。

30

## 【0049】

E/Eb DACデバイス352も、Ebラッチ336におけるオフセット電圧を相殺するためにEbラッチ336の第2の差動入力(1)にオフセット相殺電圧を入力する。以下にさらに説明するように、オフセット相殺電圧は目標電圧レベルの関数であってもよい。したがって、E/Eb DACデバイス352は、第2の差動入力(1)にしきい値電圧とオフセット相殺電圧の和を入力する。第1の差動入力(0)におけるデータ信号入力の電圧レベルが目標電圧レベルとほぼ等しい場合、Ebラッチ336におけるオフセット電圧がオフセット相殺電圧によって相殺されると仮定すると、Ebラッチ336の出力はメタステーブル状態である。以下にさらに説明するように、目標電圧レベルはタップ1値を組み込んでもよい。

40

## 【0050】

エラープロセッサ370は、データ信号の電圧レベルが目標電圧レベルと等しいかどうかを判定するためにEbラッチ336の出力を観測する。データ信号の電圧レベルが目標電圧レベルと等しくない(すなわち、Ebラッチ336の出力がメタステーブル状態ではない)場合、エラープロセッサ370は、データ信号の電圧レベルが目標電圧レベルとほぼ等しくなる(すなわち、Ebラッチ336の出力がメタステーブル状態に達する)までDFE360の1つまたは複数のタップの振幅および/または増幅器(たとえば、増幅器320)の利得を調整してもよい。

## 【0051】

次に、大信号条件におけるEラッチ334およびEbラッチ336に関するオフセット相殺電圧

50

を決定するためのオフセット較正プロセスについて以下にさらに説明する。

【0052】

図5は、一実施形態によるEラッチ334およびEbラッチ336に関するオフセット較正を実行するためのシステム510を示す。システム510は、加算増幅器325と、同相モード(CM)レプリカ回路530と、ORゲート535と、Eラッチ334およびEbラッチ336と、第1のスイッチ564と、第2のスイッチ566とを備える。システム510はまた、E DAC554とEb DAC556を備え、E DAC554とEb DAC556はどちらもE/Eb DACデバイス352に含まれる場合がある。システム510は、以下にさらに説明するようにオフセット相殺プロセスを制御するための較正コントローラ515をさらに備える。

【0053】

この実施形態では、加算増幅器325は、加算増幅器325を選択的に有効化するための制御入力518を含む3状態加算増幅器325である。制御入力518に論理0が入力されると、加算増幅器325が有効化される。この場合、加算増幅器325は、チャネルからの入力データ信号を増幅し、増幅されたデータ信号をラッチ330～336に出力する。制御入力518に論理1が入力されると、加算増幅器325が無効化される。この場合、入力データ信号が加算増幅器325の出力から遮断され、加算増幅器325の出力インピーダンスがハイになる。

10

【0054】

CMレプリカ回路530は、加算増幅器325の出力CM電圧を複製した同相モード(CM)電圧を生成するように構成される。以下にさらに説明するように、オフセット較正の間に加算増幅器325が無効化されると、CMレプリカ回路530は、ラッチ330～336のデータパスにレプリカCM電圧を印加し、ここで、CM電圧は、各ラッチの第1の差動入力(0)の2つのラインに共通する。CMレプリカ回路530は、CMレプリカ回路530を選択的に有効化するための制御入力532を有する。制御入力532に論理1が入力されると、CMレプリカ回路530が有効化され、制御入力532に論理0が入力されると、CMレプリカ回路530が無効化される。

20

【0055】

ORゲート535は、第1の入力においてEラッチ334に関する較正イネーブル信号(cal\_e\_enと示される)を受信し、第2の入力においてEbラッチ336に関する較正イネーブル信号(cal\_eb\_enと示される)を受信する。ORゲート535の出力は、加算増幅器325の制御入力518およびCMレプリカ回路530の制御入力532に結合される。

30

【0056】

データモードにおいて、較正コントローラ515が両方の較正イネーブル信号(cal\_e\_enおよびcal\_eb\_en)を0に設定してもよい。これによって、ORゲート535は、加算増幅器325の制御入力518およびCMレプリカ回路530の制御入力532に論理0を出力する。その結果、加算増幅器325が有効化され、CMレプリカ回路530が無効化される。説明しやすいように、較正コントローラ515とORゲート535との間の接続は図5には示されていない。

【0057】

較正モードにおいて、較正コントローラ515は、所与の時間にEラッチ334とEbラッチ336のうちのどちらが較正されるかに応じて、較正イネーブル信号(cal\_e\_enおよびcal\_eb\_en)の一方を1に設定してもよい。たとえば、較正コントローラ515は、Eラッチ334に関してオフセット較正が実行されている場合にはEラッチ334に関する較正イネーブル信号(cal\_e\_en)を1に設定してもよく、Ebラッチ336に関してオフセット較正が実行されている場合にはEbラッチ336に関する較正イネーブル信号(cal\_eb\_en)を1に設定してもよい。いずれの場合も、ORゲート535は、加算増幅器325の制御入力518およびCMレプリカ回路530の制御入力532に論理1を出力する。その結果、加算増幅器325が無効化され、CMレプリカ回路530が有効化される。CMレプリカ回路530は、(無効化された)加算増幅器325の出力CM電圧のレプリカをラッチ330～336のデータパスに印加する。

40

【0058】

E DAC554は、Eラッチ334の第2の差動入力(1)に結合される出力を有し、Eb DAC556は、Ebラッチ336の第2の差動入力(1)に結合される出力を有する。第1のスイッチ564は、Eラッチ334に関する較正イネーブル信号(cal\_e\_en)の制御下でEb DAC556の出力をEラッチ334の

50

第1の差動入力(0)に選択的に結合するように構成されてもよい。較正イネーブル信号(cal\_e\_en)が1になると、第1のスイッチ564が閉じられ、第1のスイッチ564がEb DAC556の出力をEラッチ334の第1の差動入力(0)に結合(ルーティング)し、較正イネーブル信号(cal\_e\_en)が0になると、第1のスイッチ564が開かれる。同様に、第2のスイッチ566は、Ebラッチ336に関する較正イネーブル信号(cal\_eb\_en)の制御下でEb DAC554の出力をEbラッチ336の第1の差動入力(0)に選択的に結合するように構成されてもよい。較正イネーブル信号(cal\_e\_en)が1になると、第2のスイッチ566が閉じられ、第2のスイッチ566がEb DAC554の出力をEbラッチ336の第1の差動入力(0)に結合(ルーティング)し、較正イネーブル信号(cal\_eb\_en)が0になると、第2のスイッチ566が開かれる。

【0059】

10

データモードにおいて、Eラッチ334およびEbラッチ336に関する較正イネーブル信号(cal\_e\_enおよびcal\_eb\_en)が0になり、第1のスイッチ564と第2のスイッチ566の両方が開く。このモードにおいて、Eラッチ334の第1の差動入力(0)とEbラッチ336の第1の差動入力(0)が、加算增幅器325の出力からデータ信号を受信する。較正モードにおけるスイッチ564および566の動作について以下にさらに説明する。

【0060】

20

図5の例では、Eb DAC554は、Eラッチ334に印加すべきオフセット相殺電圧を指定するオフセットコードを受信する。オフセットコードは、オフセット相殺電圧の振幅を指定する振幅コード(offsetcal\_e\_codeと示される)とオフセット相殺電圧の極性を指定する符号ビット(offsetcal\_e\_signと示される)とを含む。Eb DAC554は、Eラッチ334に印加すべきタップ1電圧を指定するコードも受信する。このコードは、タップ1電圧の振幅を指定する振幅コード(tap1\_codeと示される)とタップ1電圧の極性を指定する符号ビット(tap1signと示される)とを含む。Eb DAC554は、Eラッチ334の第1の差動入力(0)における電圧レベルを測定するのに使用される電圧を指定するコードも受信する。このコードは、電圧の振幅を指定する振幅コード(ecodeと示される)と電圧の極性を指定する符号ビット(esignと示される)とを含む。したがって、Eb DAC554は、オフセット相殺電圧、タップ1電圧、および第1の差動入力(0)における電圧レベルを測定するのに使用される電圧の和である電圧をEラッチ334の第2の差動入力(1)に出力する。

【0061】

30

Eb DAC556は、Ebラッチ336に印加すべきオフセット相殺電圧を指定するオフセットコードを受信する。オフセットコードは、オフセット相殺電圧の振幅を指定する振幅コード(offsetcal\_eb\_codeと示される)とオフセット相殺電圧の極性を指定する符号ビット(offsetcal\_eb\_signと示される)とを含む。Eb DAC556は、Ebラッチ336に印加すべきタップ1電圧を指定するコードも受信する。このコードは、タップ1電圧の振幅を指定する振幅コード(tap1\_codeと示される)とタップ1電圧の極性を指定する符号ビット(

【数1】

tap1sign

40

と示される)とを含む。Eb DAC556は、Ebラッチ336の第1の差動入力(0)における電圧レベルを測定するのに使用される電圧を指定するコードも受信する。このコードは、電圧の振幅を指定する振幅コード(ecodeと示される)と電圧の極性を指定する符号ビット(esignと示される)とを含む。したがって、Eb DAC556は、オフセット相殺電圧、タップ1電圧、および第1の差動入力(0)における電圧レベルを測定するのに使用される電圧の和である電圧をEbラッチ336の第2の差動入力(1)に出力する。

【0062】

図5の例では、Eb DAC554およびEb DAC556は、タップ1電圧の振幅と同じコード(tap1\_code)およびタップ1電圧の極性と逆の符号ビット(tap1signおよび

【数2】

### tap1sign

)を受信する。E DAC554とEb DAC556は同じecodeを受信する。

【0063】

次に、本開示の一実施形態による、大信号条件におけるEラッチ334に関するオフセット較正の一例について説明する。較正コントローラ515は、Eラッチ334に関するオフセットを較正するために、Eラッチ334に関する較正イネーブル信号(cal\_e\_en)を1に設定し、Eb ラッチ336に関する較正イネーブル信号(cal\_eb\_en)を0に設定する。これによって、第1のスイッチ564は、Eb DAC556の出力をEラッチ334の第1の差動入力(0)に結合(ルーティング)する。E DAC554の出力は、Eラッチ334の第2の差動入力(1)に結合される。

10

【0064】

較正コントローラ515は、タップ1コードを0に設定し、かつタップ1符号ビットを0に設定してもよい。したがって、較正の間タップ1値はEラッチ334に適用されない。較正コントローラ515は、esignビットおよびebsign符号を逆の論理値に設定してもよい。したがって、E DAC554とEb DAC556は、(ecodeによって指定される)同じ振幅と互いに逆の極性とを有する電圧を出力する。ebsignビットの論理値は、Eラッチ334の第1の差動入力(0)における電圧の所望の極性に依存する。

20

【0065】

較正コントローラ515は、第1の差動入力電圧レベル(たとえば、200mV)に関するオフセット較正を実行してもよい。これを実行するために、較正コントローラ515は、ecodeを第1の入力電圧レベルに対応する値に設定する。これによって、Eb DAC556は、Eラッチ334の第1の差動入力(0)に第1の電圧レベル(たとえば、200mV)を出力し、E DAC554は、Eラッチ334の第2の差動入力(1)に第1の電圧レベル(たとえば、-200mV)の負数を出力する。この例では、Eb DAC556の出力は、第1の電圧レベル(たとえば、200mV)と等しい差動電圧レベルを有するデータ信号をシミュレートし、ここで、差動電圧レベルは、Eラッチ334の第1の差動入力(0)の2つのライン間のレベルである。CMレプリカ回路530によって供給されるCM電圧は、Eラッチ334の第1の差動入力(0)の両方のラインに共通する。

30

【0066】

Eラッチ334の出力は、等しい振幅と互いに逆の極性とを有する電圧がEラッチ334の第1の差動入力(0)および第2の差動入力(1)に印加され、Eラッチ334のオフセット電圧が相殺されたときにメタステーブル状態に入る(0と1の間でトグルする)。したがって、この例では、Eラッチ334の出力は、Eラッチ334に印加されたオフセット相殺電圧がオフセット電圧を相殺したときにメタステーブル状態に入る。

【0067】

この点に関して、較正コントローラ515は、Eラッチ334の出力を観測しつつ、オフセット相殺電圧の振幅および/または極性をEラッチ334の第2の差動入力(1)に調整する。較正コントローラ515は、異なるオフセットコード(offset\_e\_codeおよび/またはoffset\_e\_sig\_n)をE DAC554にシーケンシャルに入力することによってオフセット相殺電圧の振幅および/または極性を調整する。較正コントローラ515は、Eラッチ334の出力がメタステーブル状態に達するまでオフセット相殺電圧を調整する。メタステーブル状態に達すると、較正コントローラ515は、メタステーブル状態を生じさせたオフセットコードをE/Ebレジスタ342に記録し、ここで、オフセットコードは、E/Ebレジスタ342において第1の電圧レベル(たとえば、200mV)に関連付けられる。したがって、オフセットコードは第1の電圧レベル(たとえば、200mV)に関して較正される。

40

【0068】

較正コントローラ515は、他の入力電圧レベルの各々に関するオフセット相殺電圧を決定するために複数の他の差動入力電圧レベル(たとえば、150mV、180mV、220mV、および25

50

0mV)の各々に関して上記のプロセスを繰り返してもよい。較正コントローラ515は、各入力電圧レベルに関して、得られたオフセット相殺電圧をE/Ebレジスタ342に記録してもよい。たとえば、較正コントローラ515は、Eラッチ334に関するオフセットルックアップテーブルを生成してもよく、ここで、ルックアップテーブルは、異なる入力電圧レベル(たとえば、150mV、180mV、200mV、220mV、および250mV)を対応するオフセット相殺電圧にマッピングする。較正コントローラ515は、ルックアップテーブルをE/Ebレジスタ342に記憶してもよい。

#### 【0069】

図6は、上述のEラッチ334に関するオフセット相殺方法を要約するフローチャートである。本方法は、較正コントローラ515によって実行されてよい。

10

#### 【0070】

ステップ610では、Eラッチ334に関する較正イネーブル信号(cal\_e\_en)が1に設定され、Ebラッチ336に関する較正イネーブル信号(cal\_eb\_en)が0に設定される。これによって、第1のスイッチ564は、Eb DAC556の出力をEラッチ334の第1の差動入力(0)に結合(ルーティング)する。

#### 【0071】

ステップ620では、ecodeは第1の差動電圧レベル(たとえば、200mV)に対応する値に設定される。Eb DAC556は、Eラッチ334の第1の差動入力(0)に差動電圧レベルを出力し、E DAC554は、Eラッチ334の第2の差動入力(1)に第1の電圧レベルの負数を出力する。

20

#### 【0072】

ステップ630では、オフセット相殺電圧が調整される。これは、たとえば、異なるオフセットコード(offset\_e\_codeおよび/またはoffset\_e\_sign)をE DAC554に入力することによって行われてもよい。オフセット相殺電圧が調整される間、Eラッチ334の出力がメタステーブル状態に関して観測される。ステップ640において、Eラッチ334の出力においてメタステーブル状態が観測される。ステップ650において、メタステーブル状態を生じさせたオフセットコードが記録される。たとえば、オフセットコードは、E/Ebレジスタ342に記録され、E/Ebレジスタ342において第1の電圧レベルに関連付けられてもよい。

#### 【0073】

ステップ660において、オフセット較正を実行すべき別の差動電圧レベルがあるかどうかが判定される。オフセット較正を実行すべき別の差動電圧レベルがない場合、本方法は終了する。オフセット較正を実行すべき別の差動電圧レベルがある場合、本方法はステップ670に進み、ecodeが、オフセット較正を実行すべき次の差動電圧レベルに対応する値に設定される。本方法は次いで、ステップ630に戻り、次の電圧レベルに関するオフセット較正を実行する。

30

#### 【0074】

異なる電圧レベルにおけるEラッチ334に関するオフセットコードが、E/Ebレジスタ342内のオフセットルックアップテーブルに記憶されてもよく、各オフセットコードは対応する電圧レベルにマッピングされる。以下にさらに説明するように、データモードにおいて、データ信号に関する目標電圧レベルに対応するオフセットコードが、対応するオフセット相殺電圧をEラッチ334に印加するためにE DAC554に入力される。

40

#### 【0075】

大信号条件におけるEbラッチ336に関するオフセット較正は、Eラッチ334に関して上記において説明したのと同様に実行されてもよい。一実施形態では、較正コントローラ515が、Ebラッチ336に関するオフセットを較正するために、Eラッチ334に関する較正イネーブル信号(cal\_e\_en)を0に設定し、Ebラッチ336に関する較正イネーブル信号(cal\_eb\_en)を1に設定する。これによって、第2のスイッチ566は、E DAC554の出力をEbラッチ336の第1の差動入力(0)に結合(ルーティング)する。Eb DAC556の出力は、Ebラッチ336の第2の差動入力(1)に結合される。

#### 【0076】

較正コントローラ515は、タップ1コードを0に設定しタップ1符号ビットを0に設定して

50

もよい。較正コントローラ515はさらに、ebsignビットおよびesignビットを逆の論理値に設定してもよい。したがって、E DAC554とEb DAC556は、(ecodeによって指定される)同じ振幅と互いに逆の極性とを有する電圧を出力する。esignビットの論理値は、Ebラッチ336の第1の差動入力(0)における電圧の所望の極性に依存する。

【0077】

較正コントローラ515は、第1の差動入力電圧レベル(たとえば、200mV)に関するオフセット較正を実行してもよい。これを実行するために、較正コントローラ515は、ecodeを第1の入力電圧レベルに対応する値に設定する。これによって、E DAC554は、Ebラッチ336の第1の差動入力(0)に第1の電圧レベル(たとえば、200mV)を出力し、Eb DAC556は、Ebラッチ336の第2の差動入力(1)に第1の電圧レベル(たとえば、-200mV)の負数を出力する。この例では、E DAC554の出力は、第1の電圧レベル(たとえば、200mV)とほぼ等しい差動電圧レベルを有するデータ信号をシミュレートし、ここで、差動電圧レベルは、Ebラッチ336の第1の差動入力(0)の2つのライン間のレベルである。CMレプリカ回路530によって供給されるCM電圧は、Ebラッチ336の差動入力(0)の両方のラインに共通する。Ebラッチ336に関するオフセット較正において使用される第1の電圧レベルがEラッチ334に関するオフセット較正において使用される第1の電圧レベルと異なってもよいことを了解されたい。

10

【0078】

較正コントローラ515は、Ebラッチ336の出力を観測しつつ、オフセット相殺電圧の振幅および/または極性をEbラッチ336の第2の差動入力(1)に調整する。較正コントローラ515は、異なるオフセットコード(offset\_eb\_codeおよび/またはoffset\_eb\_sign)をEb DAC556に入力することによってオフセット相殺電圧の振幅および/または極性を調整する。較正コントローラ515は、Ebラッチ336の出力がメタステーブル状態に達するまでオフセット相殺電圧を調整する。メタステーブル状態に達すると、較正コントローラ515は、メタステーブル状態を生じさせたオフセットコードをE/Ebレジスタ342に記録し、オフセットコードは、E/Ebレジスタ342において第1の電圧レベルに関連付けられる。

20

【0079】

較正コントローラ515は、他の入力電圧レベルの各々に関するオフセット相殺電圧を決定するために複数の他の差動入力電圧レベルの各々に関して上記のプロセスを繰り返してもよい。較正コントローラ515は、各入力電圧レベルに関して、得られたオフセット相殺電圧をE/Ebレジスタ342に記録してもよい。たとえば、較正コントローラ515は、Ebラッチ336に関するオフセットルックアップテーブルを生成してもよく、、ルックアップテーブルは、異なる入力電圧レベルを対応するオフセット相殺電圧にマッピングする。較正コントローラ515は、ルックアップテーブルをE/Ebレジスタ342に記憶してもよい。

30

【0080】

図7は、上述のEbラッチ336に関するオフセット相殺方法を要約するフローチャートである。本方法は、較正コントローラ515によって実行されてよい。

【0081】

ステップ710では、Ebラッチ336に関する較正イネーブル信号(cal\_eb\_en)が1に設定され、Eラッチ334に関する較正イネーブル信号(cal\_e\_en)が0に設定される。これによって、第2のスイッチ566は、E DAC554の出力をEbラッチ336の第1の差動入力(0)に結合(ルーティング)する。

40

【0082】

ステップ720では、ecodeは第1の差動電圧レベルに対応する値に設定される。E DAC554は、Ebラッチ336の第1の差動入力(1)に差動電圧レベルを出力し、Eb DAC556は、Ebラッチ336の第2の差動入力(1)に第1の電圧レベルの負数を出力する。

【0083】

ステップ730では、オフセット相殺電圧が調整される。これは、たとえば、異なるオフセットコード(offset\_eb\_codeおよび/またはoffset\_eb\_sign)をEb DAC556に入力することによって行われてもよい。オフセット相殺電圧が調整される間、Ebラッチ336の出力がメタステーブル状態に関して観測される。ステップ740において、Ebラッチ336の出力におい

50

てメタステーブル状態が観測される。ステップ750において、メタステーブル状態を生じさせたオフセットコードが記録される。たとえば、オフセットコードは、E/Ebレジスタ342に記録され、E/Ebレジスタ342において第1の電圧レベルに関連付けられてもよい。

#### 【0084】

ステップ760において、オフセット較正を実行すべき別の差動電圧レベルがあるかどうかが判定される。オフセット較正を実行すべき別の差動電圧レベルがない場合、本方法は終了する。オフセット較正を実行すべき別の差動電圧レベルがある場合、本方法はステップ770に進み、ecodeが、オフセット較正を実行すべき次の差動電圧レベルに対応する値に設定される。本方法は次いで、ステップ730に戻り、次の電圧レベルに関するオフセット較正を実行する。

10

#### 【0085】

異なる電圧レベルにおけるEbラッチ336に関するオフセットコードが、E/Ebレジスタ342内のオフセットルックアップテーブルに記憶されてもよく、各オフセットコードは対応する電圧レベルにマッピングされる。以下にさらに説明するように、データモードにおいて、データ信号に関する目標電圧レベルに対応するオフセットコードが、対応するオフセット相殺電圧をEbラッチ336に印加するためにEb DAC556に入力される。

#### 【0086】

次に、本開示の実施形態による、データモードにおけるEラッチ334に関するオフセット相殺電圧を設定するための動作について説明する。エラープロセッサ370が、ecode、tap1code、esignビット、およびtap1signビットに基づいてEラッチ334の第1の差動入力(0)におけるデータ信号に関する目標差動電圧レベルを決定する。たとえば、ecodeおよびesignが電圧レベル-120mVに対応し、tap1codeおよびtap1signビットが電圧レベル-40mVに対応する場合、データ信号に関する目標電圧レベルは160mVであってもよい。この例では、Eラッチ334の第2の入力(1)に印加されるしきい値電圧は、ecodeおよびesignに対応する電圧レベルとtap1codeおよびtap1signビットに対応する電圧レベルとの和であり、データ信号に関する目標電圧レベル(たとえば、160mV)と同じ振幅および逆の極性を有する(すなわち、データ信号の電圧レベルが目標電圧レベルに等しく、かつオフセットが相殺されたときにEラッチ334の出力をメタステーブル状態に入らせる)。

20

#### 【0087】

目標差動電圧レベルが決定された後、エラープロセッサ370は、目標電圧レベルに対応するE/Ebレジスタ342内のオフセットコードを取り出す。たとえば、エラープロセッサ370は、E/Ebレジスタ342内のEラッチ334に関するオフセットルックアップテーブルを参照し、目標電圧レベルに対応するオフセットコードを選択してもよい。たとえば、目標電圧レベルが160mVである場合、エラープロセッサは、電圧レベル160mVに対応するオフセットコードを取り出す。

30

#### 【0088】

エラープロセッサ370は次いで、選択されたオフセットコードをE DAC554に入力する。E DAC554は、オフセットコードを対応するオフセット相殺電圧に変換し、目標電圧レベルに対してEラッチ334におけるオフセット電圧を相殺するためにオフセット相殺電圧をEラッチ334の第2の差動入力(1)に出力する。

40

#### 【0089】

一態様では、tap1codeおよびtap1signビットは、直前のビットが1または0であると仮定する一定のタップ1値に応じて設定されてもよい。この態様では、エラープロセッサ370は、Eラッチ334からE出力ビットを受信するたびに、第1のマルチプレクサ420から前のビットの値を受信し、受信されたビット値を仮定されたビット値と比較してもよい。ビット値が一致する場合、エラープロセッサ370は、E出力ビットが有効であると仮定し、E出力ビットを使用してデータ信号の電圧レベルを検出してもよい。ビット値が一致しない場合、エラープロセッサ370は、E出力ビットが無効であると仮定し、E出力ビットを破棄してもよい。データ信号における1の数と0の数がほぼ等しいと仮定すると、E出力ビットの約2分の1は有効である。この態様では、レシーバが簡略化され、2つではなく1つのEラッチを使

50

用できるようにすることによって電力消費量が低減する。

【0090】

次に、本開示の一実施形態による、データモードにおけるEbラッチ336に関するオフセット相殺電圧を設定するための動作について説明する。エラープロセッサ370が、ecode、tap1code、ebsignビット、および

【数3】

tap1sign

10

ビットに基づいてEbラッチ334の第1の差動入力(0)におけるデータ信号に関する目標差動電圧レベルを決定する。この例では、Ebラッチ336の第2の入力(1)に印加されるしきい値電圧は、ecodeおよびebsignに対応する電圧レベルとtap1codeおよび

【数4】

tap1sign

20

ビットに対応する電圧レベルとの和であり、データ信号に関する目標電圧レベルと同じ振幅および逆の極性を有する(すなわち、データ信号の電圧レベルが目標電圧レベルに等しく、かつオフセットが相殺されたときにEbラッチ336の出力をメタステーブル状態に入らせる)。

【0091】

目標差動電圧レベルが決定された後、エラープロセッサ370は、目標電圧レベルに対応するE/Ebレジスタ342内のオフセットコードを取り出す。たとえば、エラープロセッサ370は、E/Ebレジスタ342内のEbラッチ336に関するオフセットルックアップテーブルを参照し、目標電圧レベルに対応するオフセットコードを選択してもよい。エラープロセッサ370は次いで、選択されたオフセットコードをEb DAC556に入力する。Eb DAC556は、オフセットコードを対応するオフセット相殺電圧に変換し、目標電圧レベルに対してEbラッチ336におけるオフセット電圧を相殺するためにオフセット相殺電圧をEbラッチ336の第2の入力(1)に出力する。

【0092】

一態様では、tap1codeおよび

【数5】

tap1sign

30

ビットは、直前のビットが1または0であると仮定する一定のタップ1値に応じて設定されてもよい。この態様では、エラープロセッサ370は、Ebラッチ336からEb出力ビットを受信するたびに、第2のマルチプレクサ422から前のビットの値を受信し、受信されたビット値を仮定されたビット値と比較してもよい。ビット値が一致する場合、エラープロセッサ370は、Eb出力ビットが有効であると仮定し、Eb出力ビットを使用してデータ信号の電圧レベルを検出してもよい。ビット値が一致しない場合、エラープロセッサ370は、Eb出力ビットが無効であると仮定し、E出力ビットを破棄してもよい。

40

【0093】

図8は、本開示の一実施形態による、オフセット較正のための方法800を示すフローチャートである。方法800は、較正コントローラ515によって実行されてもよい。

【0094】

ステップ810では、第1の電圧がサンプルラッチの第1の入力に入力される。たとえば、E

50

ラッチ334に関するオフセット較正を実行するために、第1の電圧がEラッチ334の第1の差動入力(0)に入力されてもよい。第1の電圧は、オフセットが第1の電圧に関して較正される場合があるので較正電圧と呼ばれることがある。第1の電圧は、振幅が少なくとも50mVである差動電圧であってもよい。

ステップ820では、第2の電圧とオフセット相殺電圧がサンプルラッチの第2の入力に入力される。たとえば、Eラッチ334に関するオフセット較正を実行するために、第2の電圧とオフセット相殺電圧の和がEラッチ334の第2の差動入力(1)に入力されてもよい。第2の電圧は、第1の電圧とほぼ同じ振幅および逆の極性を有する場合がある。

ステップ830では、オフセット相殺電圧が調整される。たとえば、オフセット相殺電圧は、オフセット相殺電圧を生成するのに使用されるDAC(たとえば、E DAC554)に異なるオフセットコードを入力することによって調整されてもよい。

ステップ840では、オフセット相殺電圧が調整されるときにサンプルラッチの出力が観測される。ステップ850では、サンプルラッチの出力においてメタステーブル状態が観測されたオフセット相殺電圧の値が記録される。たとえば、メタステーブル状態が観測されたオフセットコードは、E/Ebレジスタ342に記録されてもよい。データモードにおいて、記録されたオフセットコードは、データ信号に関する目標電圧レベルが第1の電圧に対応するときにオフセット相殺に使用されてもよい。方法800は、各電圧レベルに関するオフセット相殺電圧を決定するために複数の異なる電圧レベルの各々について繰り返されてもよい。

#### 【0095】

本明細書において開示された実施形態に関連して説明された様々な例示的な論理ブロック、回路、およびステップが、電子ハードウェア、コンピュータソフトウェア、または両者の組合せとして実装されてもよいことを当業者は了解されよう。ハードウェアとソフトウェアのこの互換性を明確に示すために、種々の例示的な構成要素、ブロック、回路、およびステップが、概してそれらの機能に関して上記において説明した。そのような機能がハードウェアとして実現されるか、ソフトウェアとして実現されるかは、特定の用途およびシステム全体に課せられる設計制約によって決まる。当業者は、説明された機能を特定の適用例ごとに様々な方法で実装してもよいが、そのような実装の決定は、本開示の範囲からの逸脱をもたらすものと解釈されるべきではない。

#### 【0096】

本開示の上述の説明は、当業者が本開示を実施するかまたは使用することを可能にするために提供される。本開示に対する様々な修正は、当業者に容易に明らかになり、本明細書で定義する一般原理は、本開示の趣旨または範囲を逸脱することなく、他の変形形態に適用される場合がある。したがって、本開示は本明細書で説明する例に限定されるものではなく、本明細書で開示する原理および新規の特徴と一致する最も広い範囲を与えるべきである。

#### 【符号の説明】

#### 【0097】

110 レシーバ

40

120 VGA

125 CTLE

130 Iラッチ

132 Ibサンプルラッチ

134 Eサンプルラッチ

136 Ebサンプルラッチ

140 加算増幅器

142 Ib加算増幅器

144 E加算増幅器

146 Eb加算増幅器

150 IオフセットDAC

50

10

20

30

|     |              |    |

|-----|--------------|----|

| 152 | IbオフセットDAC   |    |

| 154 | EオフセットDAC    |    |

| 156 | EbオフセットDAC   |    |

| 210 | オフセット電圧      |    |

| 310 | 低電圧高性能レシーバ   |    |

| 320 | 増幅器          |    |

| 325 | 加算増幅器        |    |

| 330 | Iサンプルラッチ     |    |

| 332 | Ibサンプルラッチ    | 10 |

| 334 | Eサンプルラッチ     |    |

| 336 | Ebサンプルラッチ    |    |

| 340 | I/Ibレジスタ     |    |

| 342 | E/Ebレジスタ     |    |

| 350 | I/Ib DACデバイス |    |

| 352 | E/Eb DACデバイス |    |

| 360 | DFE          |    |

| 362 | DFE DACデバイス  |    |

| 370 | エラープロセッサ     |    |

| 410 | レシーバ         |    |

| 420 | 第1のマルチプレクサ   | 20 |

| 422 | 第2のマルチプレクサ   |    |

| 510 | システム         |    |

| 515 | 較正コントローラ     |    |

| 518 | 制御入力         |    |

| 530 | CMレプリカ回路     |    |

| 532 | 制御入力         |    |

| 535 | ORゲート        |    |

| 554 | E DAC        |    |

| 556 | Eb DAC       |    |

| 564 | 第1のスイッチ      | 30 |

| 566 | 第2のスイッチ      |    |

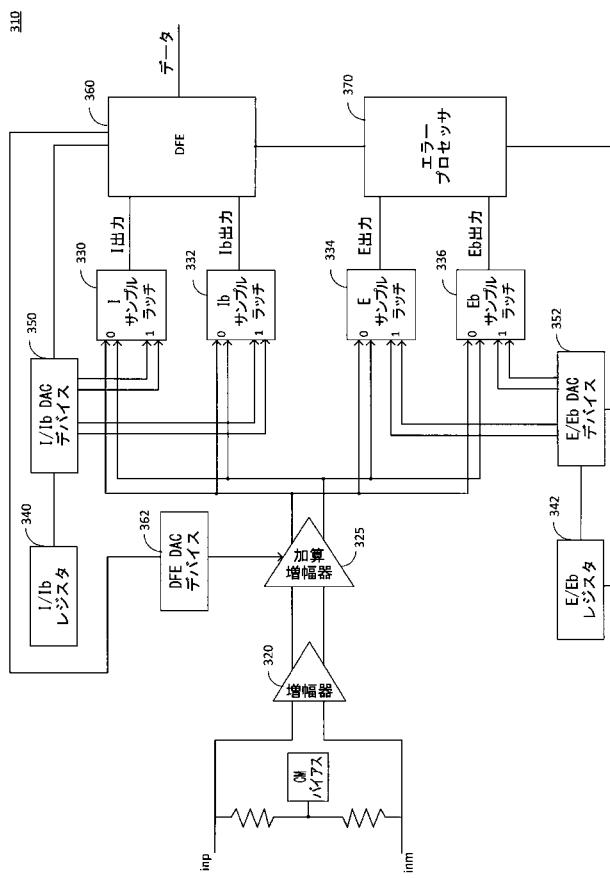

【 図 1 】

【 四 2 】

〔 図 3 〕

【 図 4 】

【図5】

【図6】

【図7】

【図8】

**【手続補正書】**

【提出日】平成28年12月7日(2016.12.7)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

オフセット較正のための方法であって、

較正モードにおいて、

サンプルラッチの第1の入力に第1の電圧を入力するステップと、

前記サンプルラッチの第2の入力に第2の電圧およびオフセット相殺電圧を入力するステップと、

前記オフセット相殺電圧を調整するステップと、

前記オフセット相殺電圧が調整されるときに前記サンプルラッチの出力を観測するステップと、

前記サンプルラッチの前記出力においてメタステーブル状態が観測された前記オフセット相殺電圧の値をメモリに記憶するステップと

を実行するステップと、

データモードにおいて、

前記メモリに記憶された前記オフセット相殺電圧の前記値に応じて前記オフセット相殺電圧を設定するステップと、

前記サンプルラッチの前記第2の入力に前記第2の電圧および前記設定されたオフセット相殺電圧を入力するステップと、

前記サンプルラッチの前記第1の入力にデータ信号を入力するステップと

を実行するステップと

を含む、方法。

**【請求項2】**

前記第1の電圧と前記第2の電圧とが、ほぼ同じ振幅と互いに逆の極性とを有する、請求項1に記載の方法。

**【請求項3】**

前記第1の電圧は、振幅が少なくとも50mVである、請求項2に記載の方法。

**【請求項4】**

前記オフセット相殺電圧を調整するステップは、前記オフセット相殺電圧を生成するのに使用されるデジタルアナログ変換器(DAC)に複数の異なるオフセットコードをシーケンシャルに入力するステップを含む、請求項1に記載の方法。

**【請求項5】**

前記オフセット相殺電圧の前記値を前記メモリに記憶するステップは、前記複数のオフセットコードのうちの、前記メタステーブル状態が前記サンプルラッチの前記出力において観測されるオフセットコードを記憶するステップを含む、請求項4に記載の方法。

**【請求項6】**

オフセット較正のための装置であって、

較正モードにおいて、サンプルラッチの第1の入力に第1の電圧を入力するための手段と、

前記較正モードにおいて、前記サンプルラッチの第2の入力に第2の電圧およびオフセット相殺電圧を入力するための手段と、

前記較正モードにおいて、前記オフセット相殺電圧を調整するための手段と、

前記較正モードにおいて、前記オフセット相殺電圧が調整されるときに前記サンプルラッチの出力を観測するための手段と、

前記サンプルラッチの前記出力においてメタステーブル状態が観測された前記オフセット相殺電圧の値をメモリに記憶するための手段と、

データモードにおいて、前記オフセット相殺電圧の前記値を前記メモリから取り出すための手段と、

前記データモードにおいて、前記取り出された値に応じて前記オフセット相殺電圧を設定するための手段と、

前記データモードにおいて、前記サンプルラッチの前記第2の入力に前記第2の電圧および前記オフセット相殺電圧を入力するための手段と、

前記データモードにおいて、前記サンプルラッチの前記第1の入力にデータ信号を入力するための手段と

を備える、装置。

#### 【請求項 7】

前記第1の電圧と前記第2の電圧とが、ほぼ同じ振幅と互いに逆の極性とを有する、請求項6に記載の装置。

#### 【請求項 8】

前記第1の電圧は、振幅が少なくとも50mVである、請求項7に記載の装置。

#### 【請求項 9】

前記オフセット相殺電圧を調整するための手段は、前記オフセット相殺電圧を生成するに使用されるデジタルアナログ変換器(DAC)に複数の異なるオフセットコードをシーケンシャルに入力するための手段を備える、請求項6に記載の装置。

#### 【請求項 10】

前記オフセット相殺電圧の前記値を記憶するための手段は、前記複数のオフセットコードのうちの、前記メタステーブル状態が前記サンプルラッチの前記出力において観測されるオフセットコードを記憶するための手段を備える、請求項9に記載の装置。

#### 【請求項 11】

データ信号を受信するように構成される入力と、出力とを有する加算増幅器と、

前記加算増幅器の前記出力に結合される第1の入力と、第2の入力とを有する第1のサンプルラッチと、

前記第1のサンプルラッチの前記第2の入力に結合される出力を有する第1のデジタルアナログ変換器(DAC)であって、第1のオフセットコードを受信し、前記第1のオフセットコードを第1のオフセット相殺電圧に変換し、かつ前記第1のオフセット相殺電圧を前記第1のサンプルラッチの前記第2の入力に出力するように構成される第1のデジタルアナログ変換器と、

前記加算増幅器の前記出力に結合される第1の入力と、第2の入力とを有する第2のサンプルラッチと、

前記第2のサンプルラッチの前記第2の入力に結合される出力を有する第2のDACであって、第2のオフセットコードおよびしきい値電圧に対応するコードを受信し、前記第2のオフセットコードを第2のオフセット相殺電圧に変換し、前記しきい値電圧に対応する前記コードを前記しきい値電圧に変換し、かつ前記第2のオフセット相殺電圧および前記しきい値電圧を前記第2のサンプルラッチの前記第2の入力に出力するように構成され、前記しきい値電圧は前記データ信号に関する目標電圧レベルに対応する、第2のDACとを備える、レシーバ。

#### 【請求項 12】

前記第2のサンプルラッチの前記第1の入力における前記データ信号に関する前記目標電圧レベルを決定し、かつ前記決定された目標電圧レベルに基づいて異なる電圧レベルに対応する複数のオフセットコードから前記第2のオフセットコードを選択するように構成されるプロセッサをさらに備える、請求項11に記載のレシーバ。

#### 【請求項 13】

前記しきい値電圧は、前記目標電圧レベルとほぼ同じ振幅を有する、請求項11に記載のレシーバ。

**【請求項 14】**

前記しきい値電圧は、振幅が少なくとも50mVである、請求項13に記載のレシーバ。

**【請求項 15】**

前記第2のサンプルラッチの出力を観測し、前記第2のサンプルラッチの前記出力においてメタステーブル状態が観測されるまで前記レシーバのパラメータを調整するように構成されるプロセッサをさらに備える、請求項11に記載のレシーバ。

**【請求項 16】**

前記プロセッサは、前記レシーバ内のイコライザのパラメータおよび前記レシーバ内の増幅器の利得のうちの少なくとも一方を調整することによって前記レシーバの前記パラメータを調整するように構成される、請求項14に記載のレシーバ。

**【請求項 17】**

前記第1のサンプルラッチの出力に結合される判定帰還型イコライザ(DFE)であって、前記第1のサンプルラッチの前記出力からの1つまたは複数のビットに基づいてシンボル間干渉(ISI)除去値を算出し、かつ前記ISI除去値に対応するISI除去コードを出力するように構成される判定帰還型イコライザと、

前記ISI除去コードをISI除去電圧に変換し、かつ前記ISI除去電圧を前記加算増幅器に出力するように構成される第3のDACであって、前記加算増幅器は、前記1つまたは複数のビットに対応するISIを除去するために前記データ信号に前記ISI除去電圧を印加する、第3のDACと

をさらに備える、請求項11に記載のレシーバ。

**【請求項 18】**

受信データパスに結合される第1の入力と、第2の入力とを有するサンプルラッチと、

前記サンプルラッチの前記第2の入力に結合される出力を有する第1のデジタルアナログ変換器(DAC)と、

出力を有する第2のDACと、

前記第2のDACの前記出力を前記第2のサンプルラッチの前記第1の入力に選択的に結合するように構成されるスイッチと、

データモードにおいて、前記スイッチを開くように構成され、較正モードにおいて、前記第2のDACの前記出力を前記サンプルラッチの前記第1の入力に結合するために前記スイッチを閉じるように構成される較正コントローラと

を備え、

前記データモードにおいて、前記サンプルラッチの前記第1の入力が、前記受信データパスからデータ信号を受信し、前記較正モードにおいて、前記較正コントローラが前記第2のDACにコードを入力し、前記第2のDACが、前記受信されたコードを較正電圧に変換し、かつ前記較正電圧における前記サンプルラッチのオフセットを較正するために前記較正電圧を前記サンプルラッチの前記第1の入力に出力し、前記較正電圧は、前記データ信号に関する目標電圧レベルと同じ振幅を有する、レシーバ。

**【請求項 19】**

前記較正電圧は、振幅が少なくとも50mVである、請求項18に記載のレシーバ。

**【請求項 20】**

前記較正コントローラは、前記較正モードにおいて、前記第1のDACに複数の異なるオフセットコードを入力することによって、前記第1のDACによって出力されたオフセット相殺電圧を前記サンプルラッチの前記第2の入力に調整し、前記オフセット相殺電圧が調整されるときに前記サンプルラッチの出力を観測し、かつ前記複数のオフセットコードのうちの、メタステーブル状態が前記サンプルラッチの前記出力において観測されるオフセットコードを記録するように構成される、請求項18に記載のレシーバ。

**【請求項 21】**

前記データモードにおいて、前記第1のDACに前記記録されたオフセットコードを入力するように構成されるプロセッサをさらに備える、請求項20に記載のレシーバ。

**【請求項 22】**

前記データモードにおいて、しきい値電圧に対応するしきい値コードを前記第1のDACに入力するように構成されるプロセッサをさらに備え、前記第1のDACは、前記しきい値コードを前記しきい値電圧に変換し、かつ前記しきい値コードを前記第2のサンプルラッチの前記第2の入力に出力し、前記しきい値電圧は、前記データ信号に関する前記目標電圧レベルに対応する、請求項18に記載のレシーバ。

【請求項 2 3】

前記プロセッサは、前記データモードにおいて、前記サンプルラッチの出力を観測し、かつ前記サンプルラッチの前記出力においてメタステーブル状態が観測されるまで前記レシーバのパラメータを調整するように構成される、請求項22に記載のレシーバ。

【請求項 2 4】

前記プロセッサは、前記データモードにおいて、前記レシーバ内のイコライザのパラメータおよび前記レシーバ内の増幅器の利得のうちの少なくとも一方を調整することによって前記レシーバの前記パラメータを調整するように構成される、請求項23に記載のレシーバ。

【請求項 2 5】

前記データ信号を増幅し、かつ前記増幅されたデータ信号を前記サンプルラッチの前記第1の入力に出力するように構成される増幅器をさらに備え、前記較正コントローラは、前記較正モードにおいて前記増幅器を無効化するように構成される、請求項18に記載のレシーバ。

【請求項 2 6】

前記第2の電圧は、前記データ信号に関する目標レベルに対応するしきい値電圧であり

、前記第1の電圧と前記第2の電圧とはほぼ同じ振幅を有する、請求項1に記載の方法。

【請求項 2 7】

前記第2の電圧は、前記データ信号に関する目標レベルに対応するしきい値電圧であり

、前記第1の電圧と前記第2の電圧とはほぼ同じ振幅を有する、請求項6に記載の装置。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                          | International application No<br>PCT/US2015/030209            |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |   |  |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------|------------------------------------------------------------------------------------|-----------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|--|-----|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>INV. H04L25/02 H04L25/06 H04L25/03<br>ADD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |   |  |     |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |   |  |     |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>H04L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |   |  |     |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |   |  |     |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>EPO-Internal, WPI Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |   |  |     |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="text-align: left; padding: 2px;">Category*</th> <th style="text-align: left; padding: 2px;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="text-align: left; padding: 2px;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td style="text-align: center; padding: 2px;">X</td> <td style="padding: 2px;">         US 2009/146722 A1 (CHEN MINHAN [US] ET AL)<br/>         11 June 2009 (2009-06-11)<br/>         abstract<br/>         paragraph [0001] - paragraph [0005]<br/>         paragraph [0008] - paragraph [0009]<br/>         paragraph [0019] - paragraph [0030]<br/>         paragraph [0034] - paragraph [0042]<br/>         figures 1,2<br/>         -----<br/>         US 8 385 496 B1 (CHAN ALLEN [US] ET AL)<br/>         26 February 2013 (2013-02-26)<br/>         abstract<br/>         column 1, line 36 - column 5, line 60<br/>         figures 4,5<br/>         -----<br/>         -/-/       </td> <td style="text-align: center; padding: 2px;">1-26</td> </tr> <tr> <td style="text-align: center; padding: 2px;">X</td> <td style="padding: 2px;"></td> <td style="text-align: center; padding: 2px;">1,6</td> </tr> </tbody> </table> |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                              | Category* | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | X | US 2009/146722 A1 (CHEN MINHAN [US] ET AL)<br>11 June 2009 (2009-06-11)<br>abstract<br>paragraph [0001] - paragraph [0005]<br>paragraph [0008] - paragraph [0009]<br>paragraph [0019] - paragraph [0030]<br>paragraph [0034] - paragraph [0042]<br>figures 1,2<br>-----<br>US 8 385 496 B1 (CHAN ALLEN [US] ET AL)<br>26 February 2013 (2013-02-26)<br>abstract<br>column 1, line 36 - column 5, line 60<br>figures 4,5<br>-----<br>-/-/ | 1-26 | X |  | 1,6 |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                       | Relevant to claim No.                                        |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |   |  |     |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | US 2009/146722 A1 (CHEN MINHAN [US] ET AL)<br>11 June 2009 (2009-06-11)<br>abstract<br>paragraph [0001] - paragraph [0005]<br>paragraph [0008] - paragraph [0009]<br>paragraph [0019] - paragraph [0030]<br>paragraph [0034] - paragraph [0042]<br>figures 1,2<br>-----<br>US 8 385 496 B1 (CHAN ALLEN [US] ET AL)<br>26 February 2013 (2013-02-26)<br>abstract<br>column 1, line 36 - column 5, line 60<br>figures 4,5<br>-----<br>-/-/ | 1-26                                                         |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |   |  |     |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1,6                                                          |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |   |  |     |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                          | <input checked="" type="checkbox"/> See patent family annex. |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |   |  |     |

| * Special categories of cited documents :<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |   |  |     |

| *T* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>*X* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>*Y* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art<br>*&* document member of the same patent family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |   |  |     |