# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2007-103681 (P2007-103681A)

(43) 公開日 平成19年4月19日(2007.4.19)

(51) Int.C1.

FI

テーマコード (参考)

HO 1 L 25/10 (2006.01) HO 1 L 25/11 (2006.01) HO 1 L 25/18 (2006.01) HO1L 25/14

Z

審査請求 未請求 請求項の数 5 〇L (全 11 頁)

(21) 出願番号 (22) 出願日 特願2005-291825 (P2005-291825) 平成17年10月5日 (2005.10.5) (71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74)代理人 100113859

弁理士 板垣 孝夫

(74) 代理人 100068087

弁理士 森本 義弘

(74)代理人 100096437

弁理士 笹原 敏司

|(74)代理人 100100000

弁理士 原田 洋平

(72) 発明者 伊藤 史人

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

# (57)【要約】

【課題】半導体パッケージを積層する際に、パッケージ に反りがある場合でも、パッケージ同士を接続する電極 同士を接続する各導電性突起電極に発生する応力の均一 化を図るようにして破壊が起こらないようにする半導体 装置を提供する。

【解決手段】それぞれ配線基板 2 , 1 2 の表面に半導体素子 3 , 1 3 が配置されてなる 2 個の半導体パッケージ 1 , 1 1 を、これら両配線基板の対向する面にそれぞれ複数ずつ設けられた第 1 接続電極 5 および第 2 接続電極 1 4 同士間に配置される導電性突起電極 1 5 を介して、積層してなる半導体装置であって、前記各第 1 接続電極 5 における導電性突起電極 1 5 との接続部面積をそれぞれ同一にするとともに、前記各第 2 接続電極 1 4 における導電性突起電極 1 5 との接続部面積をそれぞれ同一になし、さらに第 1 接続電極 5 の接続部面積を第 2 接続電極 1 4 の接続部面積よりも大きくしたものである。

【選択図】図1

#### 【特許請求の範囲】

## 【請求項1】

それぞれ配線基板の表面に半導体素子が配置されてなる2個の半導体パッケージを、これら両配線基板の対向する面にそれぞれ複数ずつ設けられた第1接続電極および第2接続電極同士間に配置される導電性突起電極を介して、積層してなる半導体装置であって、

前記各第1接続電極における導電性突起電極との接続部面積をそれぞれ同一にするとともに、前記各第2接続電極における導電性突起電極との接続部面積をそれぞれ同一になし

さらに前記第1接続電極の接続部面積と第2接続電極の接続部面積とが互いに異なるようにしたことを特徴とする半導体装置。

### 【請求項2】

第 1 接続電極の接続部面積を第 2 接続電極の接続部面積よりも大きくしたことを特徴とする請求項 1 に記載の半導体装置。

## 【請求項3】

それぞれ配線基板の表面に半導体素子が配置されてなる2個の半導体パッケージを、これら両配線基板の対向する面にそれぞれ複数ずつ設けられた第1接続電極および第2接続電極同士間に配置される導電性突起電極を介して、積層してなる半導体装置であって、

前記各第1接続電極および前記各第2接続電極の接続部面積を全て同一になし、

さらに前記第1接続電極および前記第2接続電極の各配線基板に対する形成位置を、両半導体パッケージを積層した際に、前記両接続電極の投影中心が一致するような位置にしたことを特徴とする半導体装置。

#### 【請求項4】

第1配線基板の表面に半導体素子およびそれぞれ同一の接続部面積を有する複数の第1接続電極を配置して第1半導体パッケージを形成する工程と、

第2配線基板の表面に半導体素子が配置されるとともに裏面の前記各第1接続電極に対向する位置に、これら各第1接続電極と異なる接続部面積でしかもそれぞれ同一の接続部面積を有する第2接続電極を複数配置して第2半導体パッケージを形成する工程と、

前記各第2接続電極に導電性突起電極を形成する工程と、

これら各導電性突起電極を前記各第1接続電極に接続することにより、前記第1半導体 パッケージと前記第2半導体パッケージとを積層する工程と

を具備したことを特徴とする半導体装置の製造方法。

## 【請求項5】

第1配線基板の表面に半導体素子およびそれぞれ同一の接続部面積を有する複数の第1接続電極を配置して第1半導体パッケージを形成する工程と、

第2配線基板の表面に半導体素子が配置されるとともに裏面の前記各第1接続電極に対向する位置に、これら各第1接続電極と同一の接続部面積を有する第2接続電極を複数配置して第2半導体パッケージを形成する工程と、

前記各第2接続電極に導電性突起電極をそれぞれ形成する工程と、

これら各導電性突起電極を前記各第1接続電極に接続することにより、前記両半導体パッケージ同士を積層する工程とを具備し、

かつ前記第1接続電極および前記第2接続電極の各配線基板に対する形成位置を、両半導体パッケージを積層した際に、前記両接続電極の投影中心が一致するような位置にした ことを特徴とする半導体装置の製造方法。

# 【発明の詳細な説明】

### 【技術分野】

# [0001]

本発明は、半導体パッケージが積層されてなる半導体装置およびその製造方法に関し、 特に、半導体パッケージ同士の電気的接続を行なう接続電極に関するものである。

## 【背景技術】

[0002]

20

10

30

40

近年、半導体集積回路装置の高集積化、高機能化およびマザーボードへの実装面積の縮小化に伴って、複数の半導体パッケージを積層(所謂、3次元実装である)した半導体装置が提供されている。

[0003]

しかしながら、複数の半導体パッケージを積層する場合、各半導体パッケージが半田接 続時の熱による反り挙動の相違により、良好な接続を得るのが困難となる。

そこで、半導体パッケージの反り挙動に合わせて、積層に用いる接続電極の接続部面積を、パッケージ中心から外側に向けて徐々に変化させていくことにより、積層時に両接続電極間に配置される導電性の突起電極の高さを変化させ、安定した接続を可能とする構造および工法が提案されている(例えば、特許文献 1 参照)。

[0004]

以下、特許文献 1 に開示された半導体パッケージの反りを考慮しつつ 3 次元実装時の接続信頼性の向上を図った半導体装置を、図 5 に基づき説明する。なお、図 5 においては、分かり易くするためにその構成を簡略化して図示している。

[0005]

この半導体装置は、表面に第1半導体チップ51が実装された第1キャリア基板52の 裏面に第1接続用ランド53が配置されるとともにこの第1キャリア基板52の表面に第 2接続用ランド54が複数配置されてなる第1半導体パッケージ55と、表面に複数の第 2半導体チップ61(61A,61B)が配置された第2キャリア基板62の裏面に第3 接続用ランド64が複数配置されてなる第2半導体パッケージ65とが、しかも前記第2 接続用ランド54と前記第3接続用ランド64とが互いに対向するように、両接続用ランド54,64間に配置される突起電極66を介して接続されたものである。

[0006]

そして、さらに上記第2接続用ランド54および第3接続用ランド64の接続部面積( 絶縁膜が設けられている場合には、その開口部の面積である)が、反りが大きくなる方向 で徐々に小さくなるように、すなわち突起電極66の径が小さくなるようにされている。 なお、図5中、56は絶縁性樹脂、67は封止樹脂である。

[0007]

この構成によると、半導体パッケージの反りに伴い間隔が広くなるにしたがって、突起電極の径を細くしてその高さを高くすることができ、したがって半導体パッケージに反りがある場合でも、3次元実装時における接続の安定性を高めることができる。

【特許文献1】特開2004-289002

【発明の開示】

【発明が解決しようとする課題】

[0008]

しかしながら、反りを有する半導体パッケージの3次元実装を行う際に、特許文献1に開示された構成によると、前記第2接続用ランド54および第3接続用ランド64は、半導体パッケージの反りに伴い間隔が広くなるにしたがって徐々に接続部面積が小さくなるように形成されているため、3次元実装後の各接続部分に発生する応力が均等でなく、すなわち接続部面積の小さい接続用ランドに発生する応力が大きくなり、破壊を起こしやすいという問題がある。

[0009]

そこで、本発明は、半導体パッケージを積層する際に、パッケージに反りがある場合で も、パッケージ同士を接続する電極同士を接続する各導電性突起電極に発生する応力の均 一化を図るようにして破壊が起こらないようにする半導体装置およびその製造方法を提供 することを目的とする。

【課題を解決するための手段】

[0010]

前記課題を解決するため、本発明の請求項1に係る半導体装置は、それぞれ配線基板の表面に半導体素子が配置されてなる2個の半導体パッケージを、これら両配線基板の対向

10

20

30

40

10

20

30

40

50

する面にそれぞれ複数ずつ設けられた第 1 接続電極および第 2 接続電極同士間に配置される導電性突起電極を介して、積層してなる半導体装置であって、

前記各第1接続電極における導電性突起電極との接続部面積をそれぞれ同一にするとともに、前記各第2接続電極における導電性突起電極との接続部面積をそれぞれ同一になし

さらに前記第1接続電極の接続部面積と第2接続電極の接続部面積とが互いに異なるようにしたものである。

## [0011]

また、請求項2に係る半導体装置は、請求項1に記載の半導体装置における第1接続電極の接続部面積を第2接続電極の接続部面積よりも大きくしたものである。

また、請求項3に係る半導体装置は、それぞれ配線基板の表面に半導体素子が配置されてなる2個の半導体パッケージを、これら両配線基板の対向する面にそれぞれ複数ずつ設けられた第1接続電極および第2接続電極同士間に配置される導電性突起電極を介して、積層してなる半導体装置であって、

前記各第1接続電極および前記各第2接続電極の接続部面積を全て同一になし、

さらに前記第1接続電極および前記第2接続電極の各配線基板に対する形成位置を、両半導体パッケージを積層した際に、前記両接続電極の投影中心が一致するような位置にしたものである。

### [0012]

また、請求項4に係る半導体装置の製造方法は、第1配線基板の表面に半導体素子およびそれぞれ同一の接続部面積を有する複数の第1接続電極を配置して第1半導体パッケージを形成する工程と、

第2配線基板の表面に半導体素子が配置されるとともに裏面の前記各第1接続電極に対向する位置に、これら各第1接続電極と異なる接続部面積でしかもそれぞれ同一の接続部面積を有する第2接続電極を複数配置して第2半導体パッケージを形成する工程と、

前記各第2接続電極に導電性突起電極を形成する工程と、

これら各導電性突起電極を前記各第1接続電極に接続することにより、前記第1半導体パッケージと前記第2半導体パッケージとを積層する工程とを具備した方法である。

## [0013]

さらに、請求項5に係る半導体装置の製造方法は、第1配線基板の表面に半導体素子およびそれぞれ同一の接続部面積を有する複数の第1接続電極を配置して第1半導体パッケージを形成する工程と、

第2配線基板の表面に半導体素子が配置されるとともに裏面の前記各第1接続電極に対向する位置に、これら各第1接続電極と同一の接続部面積を有する第2接続電極を複数配置して第2半導体パッケージを形成する工程と、

前記各第2接続電極に導電性突起電極をそれぞれ形成する工程と、

これら各導電性突起電極を前記各第1接続電極に接続することにより、前記両半導体パッケージ同士を積層する工程とを具備し、

かつ前記第1接続電極および前記第2接続電極の各配線基板に対する形成位置を、両半導体パッケージを積層した際に、前記両接続電極の投影中心が一致するような位置にした方法である。

#### 【発明の効果】

## [0014]

上述した半導体装置およびその製造方法によると、一方の半導体パッケージの第1接続電極と他方の半導体パッケージの第2接続電極とは、反りの無い平坦な状態において、互いの中心位置が同一にされるとともに、第1接続電極および第2接続電極の接続部面積が互いに異なるようにされているため、より具体的には、第1接続電極の接続部面積の方が第2接続電極のそれよりも大きくされているため、半導体パッケージに反りが生じている場合でも、その積層時において、いずれか一方の接続電極を他方の配線基板側に投影した際に、例えば一方の接続電極の接続部面積内に他方の接続電極の略接続部全体が入ること

になり、したがって両接続電極の接続を安定して行うことができるとともに、それぞれの 半導体パッケージにおける各導電性突起電極における接続電極との接続部面積が均一にな るため、それぞれの接続部分に発生する応力の均一化を図ることができ、したがって破壊 が発生するのを防止することができる。

#### [ 0 0 1 5 ]

また、本発明の他の構成によると、少なくとも、第1接続電極および第2接続電極については、それぞれの接続部面積が同一の大きさで、かつ両半導体パッケージの積層時に、互いに対向する接続電極同士の投影位置(投影中心位置)が同一となるようにされているので、やはり、安定した状態で接続を行うことができるとともに、その接続は垂直方向で行われるため(斜め方向ではなく)、各導電性突起電極と接続電極との接続部分には応力集中が起こりにくくなり、したがって破壊が発生するのを防止することができる。

【発明を実施するための最良の形態】

### [0016]

### [実施の形態1]

以下、本発明の実施の形態1に係る半導体装置およびその製造方法について、図1および図2を参照しながら説明する。

#### [ 0 0 1 7 ]

本実施の形態 1 に係る半導体装置は、それぞれ半導体素子を有する半導体パッケージが 2 個積層されるとともに、それぞれに設けられた接続電極を介して互いに電気的に接続されたものである。

#### [ 0 0 1 8 ]

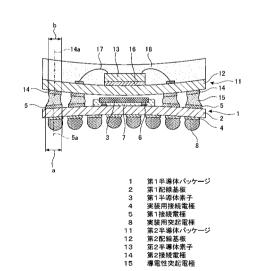

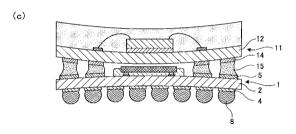

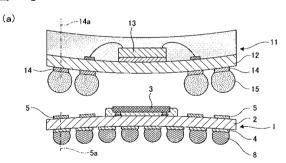

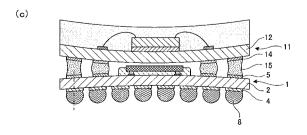

すなわち、図1に示すように、この半導体装置は、第1配線基板2の表面(上面)に第1半導体素子3が配置されるとともに、その裏面(下面)に実装用接続電極4が複数配置され、また前記表面に第1接続電極5が複数配置されてなる第1半導体パッケージ1と、第2配線基板12の表面(上面)に第2半導体素子13が配置されるとともに、その裏面(下面)に第2接続電極14が複数配置されてなる第2半導体パッケージ11とが具備され、さらにこれら両半導体パッケージ1,11同士が、第1接続電極5および第2接続電極14間に配置される導電性突起電極15を介して積層されたものである。

## [0019]

前記第1半導体素子3は第1配線基板2の表面に、フリップチップ法により実装されており、すなわちこの第1半導体素子3は、第1配線基板2の表面に配置された接続用端子である金属電極6に接続されるとともに、その周縁は絶縁性樹脂7により覆われている。なお、前記実装用接続電極4には、他の実装基板(図示せず)に接続するための導電性の実装用突起電極8が接続されており、また両半導体パッケージ1,11の積層前の段階においては、上記突起電極15は第2接続電極14に接続されている。

#### [0020]

さらに、第2半導体素子13は第2配線基板12の表面に絶縁性接着剤16を介して配置されるとともに、金属細線17を介して第2接続電極14側に電気的に接続された後、封止樹脂18にて覆われ保護されている。

### [0021]

そして、前記各実装用接続電極4同士、各第1接続電極5同士、および各第2接続電極14同士については、それぞれ同一の接続部面積にされており、また各第1接続電極5の接続部面積の方が各第2接続電極14の接続部面積よりも大きく(広く)、言い換えれば、各第1接続電極5の端部接続面の径aが各第2接続電極14の端部接続面の径bよりも大きくされている。

# [0022]

勿論、これら各第1接続電極5と各第2接続電極14とは、互いに対向する位置で且つ両配線基板2,12同士が互いに平行である状態のときに、水平面上で同一(または、ほぼ同一)の位置となるように(正確には、一方の配線基板側から他方の配線基板上への投影中心位置同士が同一となるように)配置されている。

20

30

40

#### [ 0 0 2 3 ]

ところで、通常、半導体パッケージ、すなわち配線基板に半導体素子および接続電極が 実装された場合には所定方向に反った状態になる。例えば、図1に示す本実施の形態1の 場合には、第1配線基板2の中央が上方に突出するように反り、第2配線基板12の中央 が下方に突出するように互いに逆方向に反ることになる。

#### [0024]

次に、前記半導体装置の製造方法を図2に基づき説明する。

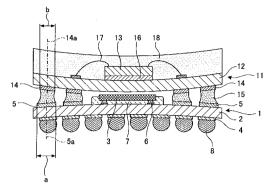

まず、図2(a)に示すように、第1配線基板2の裏面に実装用接続電極4が複数配置されるとともにその表面に所定の端子径aを有する第1接続電極5が複数配置され且つ表面中央に第1半導体素子3がフリップフロップにて実装され、さらに前記実装用接続電極4に実装用突起電極8が接続されてなる第1半導体パッケージ1、および第2配線基板12の裏面に第1接続電極5よりも小さい端子径bを有する第2接続電極14が複数配置されるとともに表面に第2半導体素子13が実装され、また前記各第2接続電極14に導電性突起電極15が接続されてなる第2半導体パッケージ2を準備する。

#### [0025]

なお、上述したように、これら半導体パッケージ1,11は、反らない平行な状態のときに、第1接続電極5と第2接続電極14との中心位置が一致しているが、反った状態では、図2(a)に示すように、両中心位置5a,14a同士に位置ずれ が生じていることになる。

## [0026]

次に、前記第1半導体パッケージ1の第1接続電極5上に導電性突起電極15を介して第2半導体パッケージ11を載置した後、リフロー工程により、当該導電性突起電極15を加熱すれば、第1接続電極5と第2接続電極14とが電気的に接続されて半導体装置が得られる。

#### [0027]

ところで、第1半導体パッケージ1に第2半導体パッケージ11を積層した場合、第1接続電極5と第2接続電極14とには、位置ずれ が生じるが、第1接続電極5の接続部面積の方が、第2接続電極14の接続部面積よりも大きくされているため、両者の接続は支障なく行われ、したがって確実な接続状態が得られる。

#### [0028]

なお、各接続電極 5 , 1 4 の大きさについて説明すれば、各半導体パッケージ 1 , 1 1 に反りが生じた状態でも、第 2 接続電極 1 4 を、第 2 配線基板 1 2 の上面から第 1 配線基板 2 上に投影した場合に、その投影面積が、第 1 配線基板 2 上の第 1 接続電極 5 の接続部面積内に入るような(カバーするような)大きさ(サイズ)にされている。

## [0029]

上述した半導体装置の構成によると、第1半導体パッケージ1の第1接続電極5と第2半導体パッケージ11の第2接続電極14とは、反りの無い平坦な状態において、互いの中心位置が同一となるようにされるとともに、第1接続電極5の接続部面積の方が第2接続電極14のそれよりも大きくされているため、各半導体パッケージ1,11に反りが生じている場合でも、第1接続電極5の接続部面積内に第2接続電極14の接続部全体が入ることになるため、両接続電極5,14同士の接続を確実に行うことができる。

#### [0030]

また、少なくとも、各第1接続電極5同士および各第2接続電極14同士については、それぞれの接続部面積が同一の大きさにされているため、従来のように、反りの拡がりに応じて、接続部面積が小さくなっているものに比べて、発生する応力の均一化を図ることができ、したがって導電性突起電極と接続電極との接続部分に破壊が生じるのを防止することができる。

## 「実施の形態21

以下、本発明の実施の形態2に係る半導体装置およびその製造方法について、図3および図4を参照しながら説明する。

10

20

30

40

20

30

40

50

#### [0031]

なお、本実施の形態 2 における半導体装置の構成部材は、上述した実施の形態 1 にて説明した半導体装置の構成部材と、基本的には同一構成であるため、同一部材には同一番号を付して説明する。

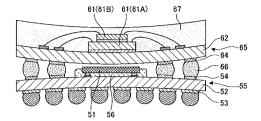

## [0032]

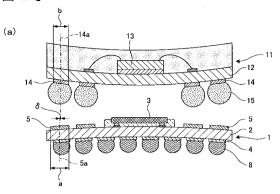

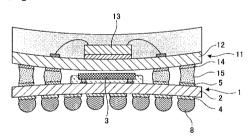

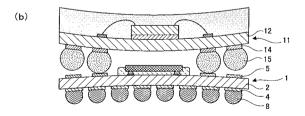

すなわち、図3に示すように、本実施の形態に係る半導体装置は、第1配線基板2の表面(上面)に第1半導体素子3が配置されるとともに、その裏面(下面)に実装用接続電極4が複数配置され、また前記表面に第1接続電極5が複数配置されてなる第1半導体パッケージ1と、第2配線基板12の表面(上面)に第2半導体素子13が配置されるとともに、その裏面(下面)に第2接続電極14が複数配置されてなる第2半導体パッケージ11とが具備され、さらにこれら両半導体パッケージ1,11同士が、第1接続電極5および第2接続電極14同士間に配置される導電性突起電極15を介して積層されたものである。

# [ 0 0 3 3 ]

前記第1半導体素子3は第1配線基板2の表面に、フリップチップ法により実装されており、すなわちこの第1半導体素子3は、第1配線基板2の表面に配置された接続用端子である金属電極6に接続されるとともに、その周縁は絶縁性樹脂7により覆われている。なお、前記実装用接続電極4には、例えば実装基板(図示せず)に接続するための導電性の実装用突起電極8が接続されており、また両半導体パッケージ1,11の積層前の段階においては、上記導電性突起電極15は第2接続電極14に接続されている。

#### [0034]

さらに、前記第2半導体素子13は第2配線基板12の表面に絶縁性接着剤16を介して配置されるとともに、金属細線17を介して第2接続電極14側に電気的に接続された後、封止樹脂18にて覆われ保護されている。

## [0035]

そして、前記各実装用接続電極4、各第1接続電極5、および各第2接続電極14については、全て、同一の接続部面積(同一の大きさ)にされている。

通常、半導体パッケージ、すなわち配線基板に半導体素子および接続電極が実装された場合には所定方向に反った状態になる。例えば、図3に示す本実施の形態2の場合には、第1配線基板2の中央が上方に突出するように反り、第2配線基板12の中央が下方に突出するように互いに逆方向に反ることとなる。

## [0036]

さらに、これら各第1接続電極5と各第2接続電極14とは、互いに対向する位置で配置されるとともに、両配線基板2,12同士が反った状態のときに、水平面上で同一(または、ほぼ同一)の位置となるように(正確には、一方の配線基板側から他方の配線基板上への投影中心位置同士が同一になるように)配置されている。したがって、両配線基板2,12同士が反っていない互いに平行な状態においては、両接続電極5,14の中心位置がずれていることになる。

## [0037]

次に、前記半導体装置の製造方法を図4に基づき説明する。

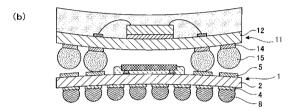

まず、図4(a)に示すように、第1配線基板2の裏面に実装用接続電極4が複数配置されるとともにその表面に第1接続電極5が複数配置され且つ表面中央に第1半導体素子3がフリップフロップにて実装され、さらに前記実装用接続電極4に導電性の実装用突起電極8が接続されてなる第1半導体パッケージ1、および第2配線基板12の裏面に第2接続電極14が複数配置されるとともに表面に第2半導体素子13が実装され、また前記各第2接続電極14に導電性突起電極15が接続されてなる第2半導体パッケージ11を準備する。

## [0038]

なお、上述したように、これら半導体パッケージ1,11は、反らない平行な状態のときに、第1接続電極5と第2接続電極14との中心位置がずれているが、反った状態では

、図4(a)に示すように、互いの中心位置5a,14aが一致している。

## [0039]

次に、前記第1半導体パッケージ1の第1接続電極5上に導電性突起電極15を介して第2半導体パッケージ11を載置した後、リフロー工程により、当該導電性突起電極15 を加熱すれば、第1接続電極5と第2接続電極14とが電気的に接続されて半導体装置が得られる。

#### [0040]

上述したように、互いに対向する第1接続電極および第2接続電極の接続部面積が全て同一の大きさにされるとともに、両半導体パッケージを積層した際に、両接続電極同士の位置(投影中心位置)が一致するように、配線基板に配置されているため、両半導体パッケージを互いに積層した際に、しかも両配線基板同士が互いに反っている場合でも、第1接続電極と第2接続電極とは、互いにその中心位置が一致するため(より詳しくは、配線基板が互いに平行な状態のときには、接続電極同士がずれるように配置されている)、両者の接続は垂直方向で支障なく且つ安定して行われ、しかも、両接続電極の接続部面積が同一面積にされているため、従来のように、接続部面積を変化させるようにしたものに比べて、各接続部分には応力集中が起こりにくくなり、したがって破壊の発生を防止することができる。

### [0041]

また、上記各実施の形態においては、2個の半導体パッケージを積層する場合について適用したが、勿論、3個以上の半導体パッケージが積層されてなる半導体装置を得る場合にも適用することができる。

【産業上の利用可能性】

## [0042]

以上、説明したように、複数の半導体パッケージを積層してなる半導体装置を製造する際に、これら半導体パッケージが互いに反っている場合でも、両半導体パッケージを接続する導電性突起電極による接続を安定した状態で行うことができるとともに、それぞれの接続部分に発生する応力の均一化を図ることができ、特に、半導体素子が実装された配線基板を積層されてなる半導体装置およびその製造に有用である。

【図面の簡単な説明】

[ 0 0 4 3 ]

- 【図1】本発明の実施の形態1に係る半導体装置の断面図である。

- 【図2】同実施の形態1に係る半導体装置の製造方法を説明する断面図である。

- 【図3】本発明の実施の形態2に係る半導体装置の断面図である。

- 【図4】同実施の形態2に係る半導体装置の製造方法を説明する断面図である。

- 【図5】従来の半導体装置の断面図である。

【符号の説明】

# [0044]

- 1 第 1 半 導 体 パ ッ ケ ー ジ

- 2 第 1 配 線 基 板

- 3 第 1 半 導 体 素 子

- 4 実装用接続電極

- 5 第 1 接 続 電 極

- 8 実装用突起電極

- 1 1 第 2 半 導 体 パ ッ ケ ー ジ

- 1 2 第 2 配 線 基 板

- 1 3 第 2 半 導 体 素 子

- 1 4 第 2 接 続 電 極

- 15 導電性突起電極

30

20

10

# 【図1】

- 第1半導体パッケージ 第1配線基核 第1半導体素子 実装用接続電極 第1装を表電極 第2半配線基体パッケージ 第2半配線基体 第2半配線基体 第2半配線基 第2半配線基 第2半配線基 第2半線基 第2半線基 第2半線基 第2半線基 第2半線基 第2半線基 第2半線

- 1 2 3 4 5 8 11 12 13 14 15

# 【図2】

【図3】

# 【図4】

【図5】

# フロントページの続き

(72)発明者 川端 毅

大阪府門真市大字門真1006番地 松下電器産業株式会社内