(12)发明专利

(10)授权公告号 CN 105849908 B

(45)授权公告日 2019.05.07

(21)申请号 201480068356.7

(73)专利权人 亚托·奥罗拉

(22)申请日 2014.11.04

地址 芬兰埃斯波

(65)同一申请的已公布的文献号

(72)发明人 亚托·奥罗拉

申请公布号 CN 105849908 A

(74)专利代理机构 北京市金杜律师事务所

(43)申请公布日 2016.08.10

11256

(30)优先权数据

代理人 王茂华 董典红

20130320 2013.11.04 FI

(51)Int.Cl.

20136170 2013.11.22 FI

H01L 27/146(2006.01)

(85)PCT国际申请进入国家阶段日

(56)对比文件

2016.06.15

CN 101015063 A, 2007.08.08,

(86)PCT国际申请的申请数据

CN 101356646 A, 2009.01.28,

PCT/FI2014/050826 2014.11.04

CN 101356654 A, 2009.01.28,

(87)PCT国际申请的公布数据

JP 2007-103578 A, 2007.04.19,

W02015/063375 EN 2015.05.07

审查员 朱永全

权利要求书1页 说明书10页 附图10页

(54)发明名称

改进的半导体辐射探测器

(57)摘要

一种半导体辐射探测器器件包括半导体衬底(100)。在衬底的一个表面上具有：MIG层(241)，其是第二导电类型的半导体；势垒层(251)，其是第一导电类型的半导体；以及像素掺杂(921、922)，其是第二导电类型的半导体。像素掺杂被适配为耦合至至少一个像素电压，以创建像素特定的晶体管的源极和漏极。该器件还包括第一导电类型的第一接触，使得所述像素电压是像素掺杂之一与第一导电类型的第一接触之间的电位差。主栅极(983)的位置至少部分地对应于源极和漏极之间的沟道的位置。该器件包括从主栅极(983)水平偏移的至少一个额外栅极(981、982)。

1. 一种半导体辐射探测器器件，包括至少一个像素，其中所述至少一个像素包括半导体衬底并且在所述衬底的一个表面上以以下顺序包括：

-第一层，其是第二导电类型的半导体，以下称为MIG层，

-势垒层，其是第一导电类型的半导体，被配置为在所述器件的操作期间形成用于累积在所述MIG层中的信号电荷的势能势垒，

-像素掺杂，其是所述第二导电类型的半导体，所述像素掺杂被适配为耦合至至少一个像素电压以创建像素特定的晶体管的源极和漏极；

其中，所述器件还包括第一导电类型的第一接触和主栅极，所述像素电压被定义为在所述像素掺杂之一与所述第一导电类型的第一接触之间的电位差，并且所述主栅极的位置至少部分地对应于所述源极和所述漏极之间的沟道的位置，

其特征在于：

-所述至少一个像素还包括与所述主栅极相邻的至少一个额外栅极，并且所述至少一个额外栅极至少部分地对应于所述源极和所述漏极之间的沟道的位置，并且其中所述至少一个额外栅极在所述第一导电类型和所述第二导电类型的所述半导体材料外部。

2. 根据权利要求1所述的半导体辐射探测器器件，包括两个额外栅极，第一额外栅极的位置从所述主栅极朝向所述源极，而另一额外栅极的位置从所述主栅极朝向所述漏极。

3. 根据权利要求1或2所述的半导体辐射探测器器件，其中，每个额外栅极都位于对应的MIG边界区域上方，所述沟道的一部分在所述MIG边界区域处与所述MIG层的边缘竖直对齐。

4. 根据权利要求1所述的半导体辐射探测器器件，其中，所述沟道穿过掩埋沟道层而非所述MIG层，所述掩埋沟道层连接所述势垒层的相对侧上的所述源极和所述漏极。

5. 根据权利要求1所述的半导体辐射探测器器件，包括将所述主栅极和所述额外栅极与所述沟道分离的电绝缘材料。

6. 根据权利要求5所述的半导体辐射探测器器件，其中，电绝缘材料的公共层包封所述主栅极和所述额外栅极二者。

7. 根据权利要求1所述的半导体辐射探测器器件，在所述MIG层中包括一个区域，所述区域的净掺杂高于环绕所述区域的剩余MIG层的净掺杂，其中所述区域与所述主栅极竖直对齐。

8. 根据权利要求1所述的半导体辐射探测器器件，包括重置栅极，所述MIG层和所述势垒层在所述重置栅极下方的掺杂弱于在所述主栅极下方的掺杂。

9. 根据权利要求8所述的半导体辐射探测器器件，其中，所述重置栅极从所述主栅极水平偏移，并且其中所述重置栅极和所述主栅极都位于分离所述源极和所述漏极的间隙上方。

10. 根据权利要求8所述的半导体辐射探测器器件，其中：

-所述晶体管是所述器件中的像素的第一场效应晶体管，所述像素还包括第二场效应晶体管，所述第二场效应晶体管包括第二源极和第二漏极，

-所述重置栅极同时是位于分离所述像素的场效应晶体管的间隙上方的传送栅极。

11. 根据权利要求1所述的半导体辐射探测器器件，包括具有不同阈值电压的至少两个像素特定的选择晶体管。

## 改进的半导体辐射探测器

### 技术领域

[0001] 本发明涉及半导体辐射探测器，具体地涉及具有经修改的内栅极(modified internal gate)的半导体辐射探测器。辐射探测器在此被定义为检测光子和/或高能带电或中性粒子的器件。

### 背景技术

[0002] 专利US 7,816,653、US 8,148,760和US 8,288,837(它们均结合于此作为参考)公开了具有所谓的经修改的内栅极(MIG)的半导体辐射探测器。MIG是半导体辐射探测的内部部件，其中收集辐射引起的信号电荷，使得所得到的MIG中的净电荷在位于其上方的像素的电特性中引起可测量的效应。这种效应的实例是像素特定的晶体管的沟道或基极的电流承载能力的变化。势垒层将MIG与所述像素分离。当适当偏置时，其组成势能势垒，这保持MIG层中累积的信号电荷不与像素中的电荷载流子(诸如流动组成通过所述沟道或基极的电流的电荷载流子)混合。还在互联网页面www.pixpolar.com/technology和www.pixpolar.com/blog及博客www.image-sensors-world.blogspot.com的多个讨论中公开了附加的信息。

[0003] 在半导体辐射探测器中，辐射引起通过电场分离的电子空穴对。被测量的电子空穴对的电荷类型被称为信号电荷，并且相反的电荷类型被称为次级电荷。

[0004] MIG探测器通常包括MIG像素的矩阵，其相对于传统的辐射探测器(如互补金属氧化物半导体(CMOS)图像传感器)具有多种优势。首先，在MIG像素中，界面生成电荷不与信号电荷混合。第二，在沟道底部和界面之间具有大电位差的掩埋沟道可用于显著降低1/f噪声。这种低1/f噪声的掩埋沟道使得读取噪声非常低。第三，可以容易地设计具有100%填充因数的背侧照明(BSI)MIG像素。第四，容易设计完全耗尽的MIG像素，避免信号电荷的扩散，这能够使像素之间的串扰非常低。第五，固有地包括垂直抗模糊(anti-blooming)机制的MIG像素意味着模糊不是问题。第六，厚的完全耗尽MIG像素能够实现红色和近红外(NIR)光的非常好的量子效率，同时串扰保持在最小等级。第七，信号电荷与上述读出晶体管的最低沟道阈值良好对齐。第八，MIG像素能够实现线性的电流模式读出。

[0005] 第九个优点是MIG像素与模拟CMOS工艺非常兼容。原因是通过栅极氧化物的泄漏不是问题，因为信号电荷没有被带至外栅极。另一个原因是不像传统的CMOS图像传感器一样要求钉扎光电二极管。钉扎光电二极管难以设计并且实际上由电荷耦合器件(CCD)改变而成，并且在标准CMOS工艺中并不是固有存在的。此外，如传统CMOS图像传感器中那样，界面质量不是问题。这些事实的结果是，必须开发独立的CMOS图像传感器工艺来用于制造传统的CMOS图像传感器，而现有的标准模拟CMOS工艺可用于制造MIG图像传感器。

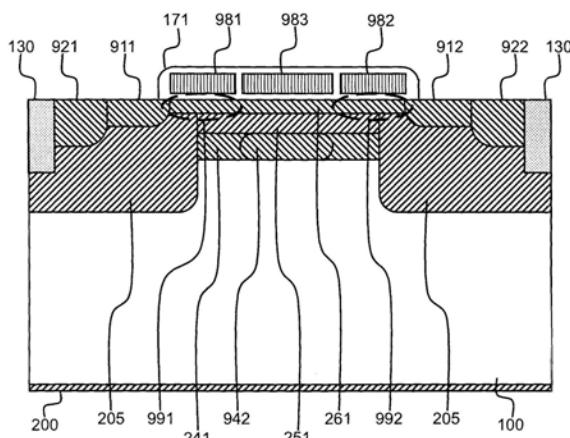

[0006] 图1示出了典型的CMOS晶体管的示意性截面图，其包括第一或第二导电类型的半导体衬底100，并且在器件的前侧上包括浅沟槽隔离(STI)130、栅极181、环绕栅极的氧化物层(或者更一般地，电绝缘材料层)171以及第一导电类型的阱掺杂105。此外，CMOS晶体管在前表面上包括源极掺杂111、漏极掺杂112、源极接触掺杂121以及漏极接触掺杂122，它们都

是第二导电类型的。

[0007] 掺杂区域是物理实体,而术语像素更类似于功能元件,这表示至少按字面来说,像素仅在上电时出现在半导体辐射探测器中。尽管通常使用如图1示为121和122的独立接触掺杂,但它们不是必需的。可以在CMOS工艺中创建像素特定的场效应晶体管,使得源极掺杂和漏极掺杂如此出现,而不具有独立的接触掺杂。在本说明书中,使用一般指定像素掺杂,以表示可以直接耦合外部电压和/或电流的掺杂区域,从而创建半导体辐射探测器的像素。因此,在如图1的结构中,像素掺杂是源极接触掺杂121和漏极接触掺杂122。在不具有独立接触掺杂的结构中,术语像素掺杂将表示源极掺杂和漏极掺杂。

[0008] 第一导电类型和第二导电类型对应于n型和p型,或反之亦然。此外,在图1中还示出了相同导电类型的另一CMOS晶体管,其具有源极113、漏极114、源极接触掺杂123、漏极接触掺杂124和栅极182。此外,在图1中示出了两个相邻像素的源极接触掺杂127和漏极接触掺杂128的部分。

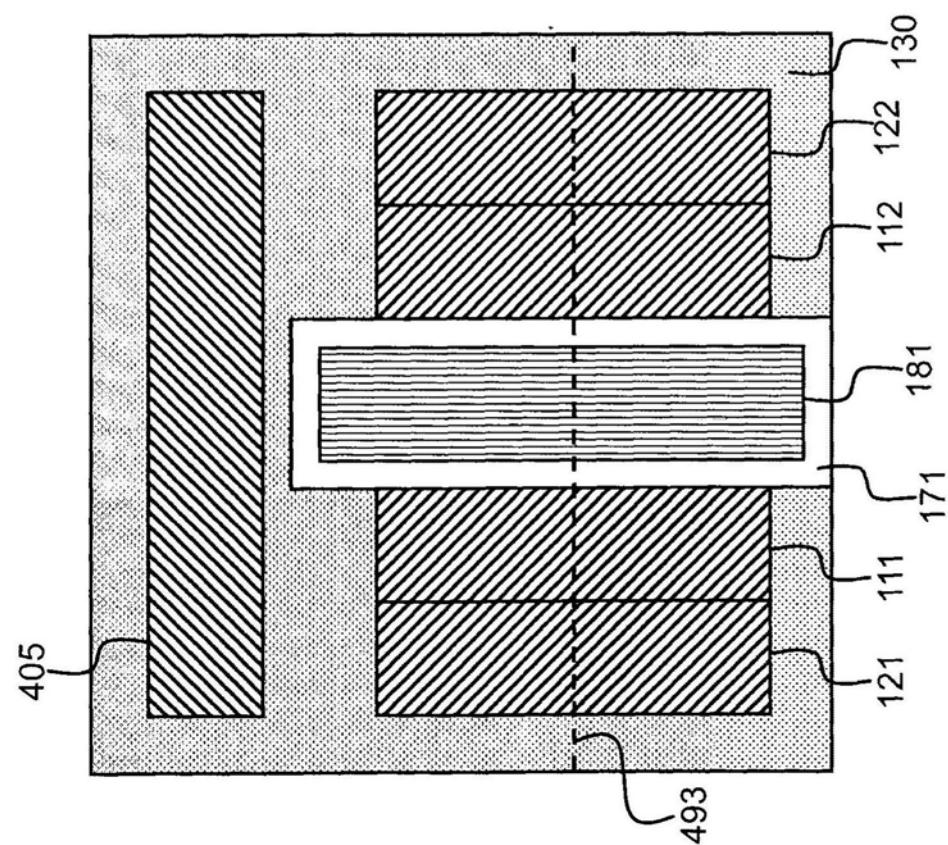

[0009] 图4示出了CMOS晶体管的示意性前侧布局,其中沿着线493的截面对应于图1所示的截面。第一类型的接触掺杂405是对第一类型阱掺杂105的接触掺杂。通过在CMOS晶体管的栅极下方设置分层结构来形成掩埋沟道MIG像素。由于阱掺杂的掺杂剂浓度通常远大于分层结构的最佳掺杂剂浓度的事实,阱掺杂105防止图1的晶体管的外栅极下方分层结构的适当形成。因此,阱掺杂105中的开口必须设置在外栅极181下方。

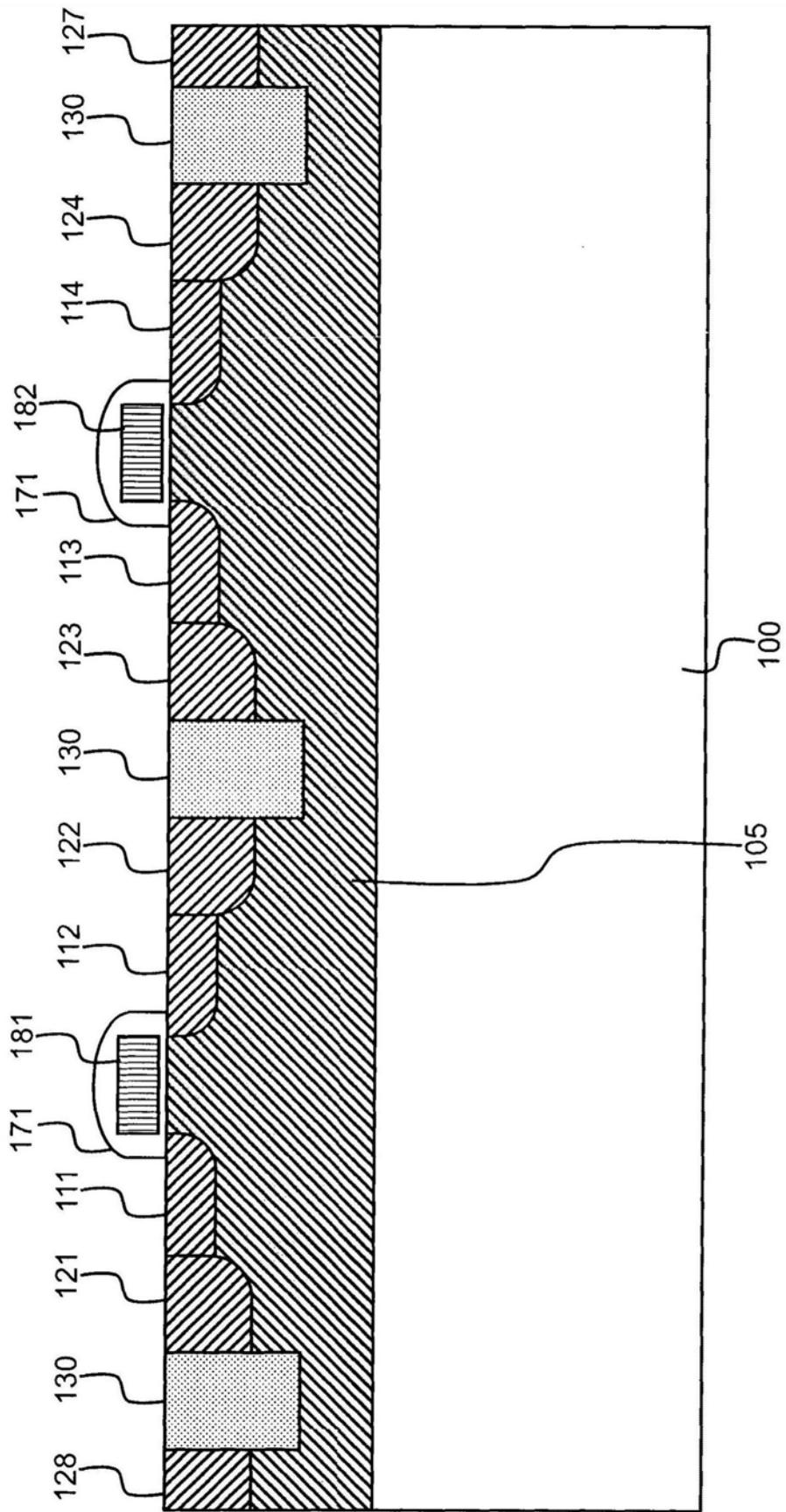

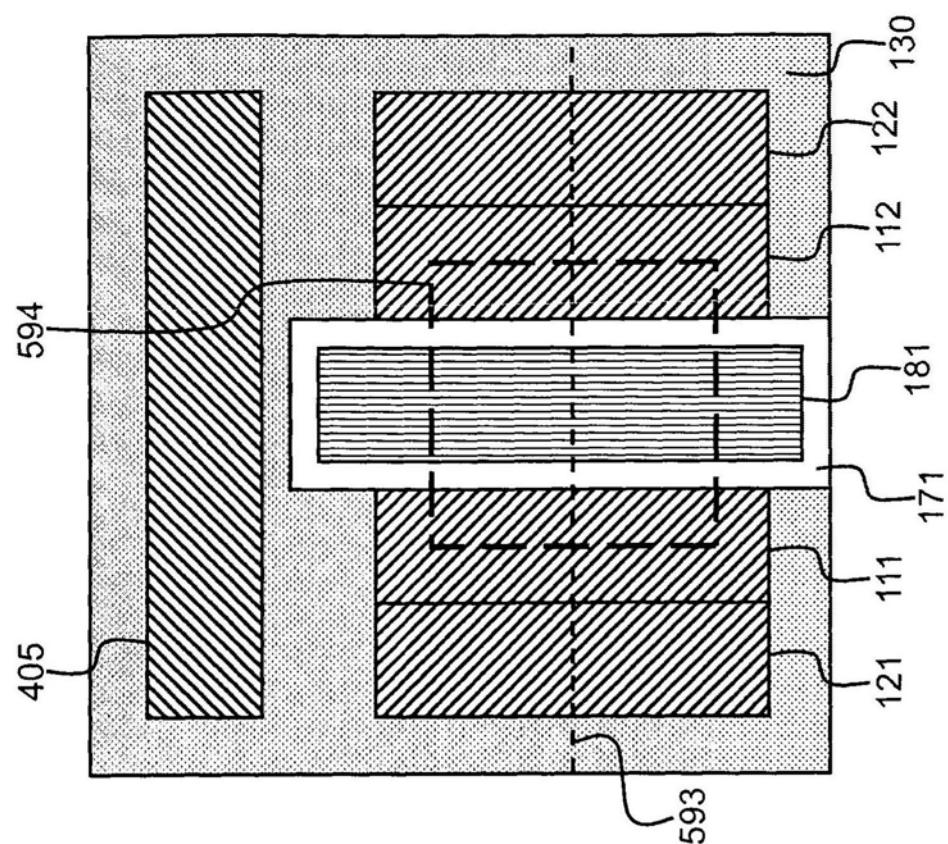

[0010] 图5示出了利用CMOS工艺制造的最基本的掩埋沟道MIG像素的示意性前侧布局。通过虚线示出了局部位于栅极区域下方的阱掺杂594中的开口。在图2中示出了沿着线593的截面,其中阱掺杂205包括位于外栅极181和182下方的开口。在开口中,MIG层241用作收集信号电荷的内栅极,该信号电荷调整上述读出晶体管的掩埋沟道261中流动的电流。势垒层251用作MIG层和掩埋沟道之间的势垒。在图2中,还示出了MIG层242、势垒层252以及相邻像素的掩埋沟道层262。在器件的背侧上还具有第一导电类型的任选导电背侧层200,其可以被偏置或者可以不被偏置。在操作中,在源极/漏极接触掺杂与阱掺杂和/或导电背侧层之间施加反向偏置。

[0011] 掩埋沟道261、262不是MIG探测器的强制要求。然而,低 $1/f$ 噪声的掩埋沟道为MIG探测器/像素提供了显著的优势,因为这能够显著降低读取噪声并提供制造的优势。后者的事实在于界面质量不太重要,这因为界面和沟道之间较大的电位差。因此,掩埋沟道是有利的选择。从噪声角度来说,非常重要的事情也是当像素被重置时,应该能够从MIG层241去除所有信号电荷,即在重置之后,MIG层应该完全耗尽。在读出期间,在信号电荷存储在MIG层中的位置处,势垒层应该完全耗尽。如果这不是信号电荷不能适当调整沟道的阈值电压和/或沟道中流动的电流的情况,则意味着读出失效或者至少不精确。

[0012] 阵掺杂205中开口594的配置被认为仅仅是由于以下明显的原因的合理选择。STI和接触掺杂被阱掺杂环绕的事实意味着,分层结构241、251和261可以制成更薄,这利于信号电荷耦合至沟道以及像素缩小到更小的像素尺寸。为了能够进一步减薄分层结构,可以通过沿着虚线295配置阱掺杂的开口,使得分层结构甚至更薄,因为源极213掺杂和漏极214掺杂将完全被阱掺杂205所环绕。然而,从操作的观点来看这是不推荐的,因为最高的阈值电压或最高的沟道电阻将位于虚线椭圆293和294的区域中,其中MIG层的信号电荷将由于阱掺杂的遮蔽而仅具有非常小的效果。

[0013] 从上面列出的原因来看,在阱掺杂中构建开口被认为是最好的,或者仅仅是图2和图5所示的可选方式。然而,这种配置的问题在于,为了在源极111掺杂/漏极112掺杂与MIG层241之间创建合理的势垒,势垒层251必须显著深于源极掺杂和漏极掺杂,如图2中的虚线椭圆291和292的位置所示。换句话说,通过利用足够深的分层结构,必须注意到源极掺杂和漏极掺杂未“吃掉”太多远离势垒层。然而,事实上源极掺杂和漏极掺杂是相对重掺杂,意味着它们还将由于随后的热处理而相对向下扩散得更深,这同样需要使用相对较深的分层结构,从而阻碍像素缩放。

[0014] 在单个MIG层的外栅极181必需支持三个不同的电压级(读取、积分和重置)的情况下,可以存储在MIG层中的信号电荷的量可以非常有限。该问题的一个容易的解决方案在于,可以向源极添加选择晶体管。以这种方式,仅需要利用位于外栅极181上的两个不同电压,即读出和重置。这提高了存储容量,也称为MIG层的满阱容量(FWC)。

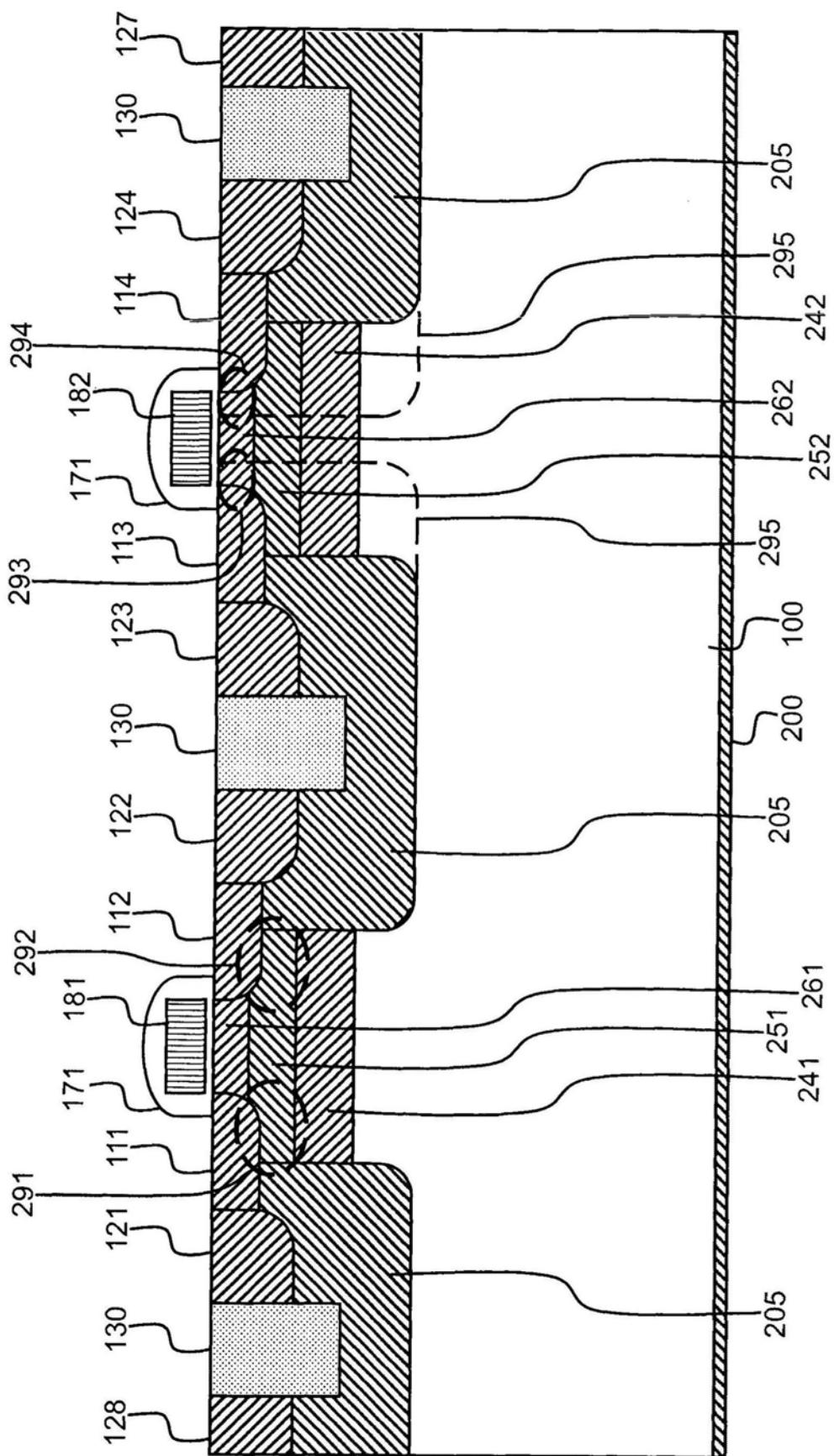

[0015] 在图3中示出了提高FWC以及串扰的另一种方式,图3示出了利用非标准CMOS工艺制造的更加先进的MIG像素,其中深沟槽隔离包括衬底301、302、303和304的每个像素。图3的沟槽包括电绝缘材料的任选像素特定的壁335、336、337和338,与其相邻的是材料的任选像素特定壁395、396、397和398,其优选是导电、透明和良好反射器。在后者壁之间,具有对所有像素公用的沟槽填充330。事实上,每个像素中的阱掺杂305、306、307和308是隔离的,意味着可以通过增加阱掺杂和源极/漏极掺杂之间的反向偏置来辅助重置。实际上利用沟槽仅分离像素的行将是足够的,但是如果利用像素特定的重置,则如图3所示每个像素都将需要被沟槽分离。在壁395、396、397和398是导电的情况下,仍然可以通过对壁395、396、397和398以及壁掺杂305、306、307和308利用同时重置脉冲来改进像素重置。换句话说,在对包括栅极182的像素将执行重置的情况下,重置脉冲可以同时耦合至壁396和对应的壁掺杂306。

[0016] 例如在半导体材料是硅,电绝缘材料335、336、337和338是二氧化硅,并且第一导电类型是n型且第二导电类型是p型的情况下,使壁395、396、397和398接触至相应的阱掺杂305、306、307和308是有利的。以这种方式,在壁395、396、397和398与阱掺杂305、306、307和308之间不要求偏置以在衬底301、302、303和304与隔离壁335、336、337和338之间的界面处形成电子的累积或反转层。原因在于,二氧化硅中的正氧化物电荷足够创建电子的累积或反转层。累积或反转层的优点是在突出穿过壁掺杂305、306、307和308的深沟槽的界面处,抑制形成泄漏电流,否则泄漏电流将与MIG层中的信号电荷混合(在图2的像素中,沟槽不突出穿过中性阱掺杂,因此沟槽界面处的泄漏不是问题,即通过源极和漏极收集界面泄漏)。

[0017] 在衬底材料为硅,第一导电类型是n型,并且背侧层300由二氧化硅形成的情况下,由于二氧化硅中存在的正氧化物电荷,电子的累积或反转层也形成在背侧层300与衬底301、302、303和304之间的背侧界面处。这种配置的巨大优势在于,背侧二氧化硅层在背侧上自发形成,意味着在背侧减薄之后,不需要背侧注入或背侧激光退火,这简化了处理并减少了源于背侧的暗电流。然而,应该注意,即使背侧层300自发地由二氧化硅形成并且仅使用简单沟槽330而没有附加的壁335、336、337和338以及395、396、397和398,由于要求高纵横比沟槽的事实,处理仍然是苛刻的任务,因为否则填充因数将需要妥协。另一个问题自然就是,这些工艺将不是标准CMOS工艺。

[0018] 在上面列出的专利(US 7,816,653、US 8,148,760和US 8,288,837,它们结合于此

作为参考)中,也可以存在不同类型的重置结构,这需要更大的FWC。然而,这些重置结构的问题是它们通常降低填充因数。

[0019] 此外,专利公开W02007/077286公开了用于探测可见光的半导体辐射探测器。该半导体辐射探测器包括一种结构,其中第一导电类型的第一接触被适配为从作为第一导电类型材料的体层收集次级电荷。

[0020] 文献US2009/001435又公开了一种半导体辐射探测器器件,其包括用于使用浮置栅极配置来从经修改的内栅极层读取信号电荷的装置,其中读出晶体管的栅极在所述像素电压方面是浮置的。

## 发明内容

[0021] 以下提供简单的总结以提供对本发明各个实例的一些方面的基本理解。这种总结不是本发明的广泛概述。既不用于识别本发明的关键或决定性的元件,也不用于界定本发明的范围。以下总结仅以简化形式来呈现本发明的一些概念来作为更详细描述本发明实施例的序幕。

[0022] 根据本发明的一个方面,提供了一种包括经修改的内栅极的半导体辐射探测器,其中,分层结构(MIG层、势垒层以及可能的掩埋沟道)可以制成更薄,这利于像素的缩放。根据本发明的另一方面,提供了一种重置结构,其能够实现100%填充因数并且还可以潜在地用于电荷传送。

[0023] 本发明的有利目标利用半导体辐射探测器来实现,该半导体辐射探测器包括:半导体衬底;经修改的内栅极层,其是第二导电类型的半导体;势垒层,其是第一导电类型的半导体;像素掺杂,其是第二导电类型的半导体,被适配为耦合至至少一个像素电压以创建对应于像素掺杂的像素;第一导电类型的第一接触,所述像素电压被定义为像素掺杂和第一导电类型的第一接触之间的电位差;主栅极;以及至少一个额外栅极,从主栅极水平偏移。

[0024] 根据本发明的教导可用于例如构建三栅极MIG晶体管,其中,阱掺杂完全环绕源极掺杂和漏极掺杂。利用两个额外栅极的帮助,可以在额外栅极下方创建伪源极和漏极,以确保沟道的最高阈值电压或电阻与MIG层中存在的信号电荷对齐。

[0025] 为了提供能够实现高FWC而不减小填充因数的重置结构,可以在重置栅极下方设置更弱掺杂的分层结构。有利地,重置栅极还可以用于信号电荷的传送。

[0026] 在本专利申请中呈现的本发明的示例性实施例不对所附权利要求的适用性提出限制。本专利申请中使用的词语“包括”是开放性限制,其不排除未引用的特征的存在。从属权利要求中引用的特征相互自由组合,除非另有明确指定。

[0027] 具体在权利要求中阐述作为本发明特性的新颖特征。然而,本发明本身的构建及其操作方法以及附加的目的和优势将在结合附图阅读时从以下具体实施例的描述中得到更好的理解。

## 附图说明

[0028] 图1示出了典型CMOS晶体管的示意性截面。

[0029] 图2示出了利用标准CMOS工艺制造的最基本的掩埋沟道MIG像素的示意性截面。

- [0030] 图3示出了利用非标准CMOS工艺制造的更先进的掩埋沟道MIG像素的示意性截面。

- [0031] 图4示出了图1的典型CMOS晶体管的示意性布局。

- [0032] 图5示出了利用标准CMOS工艺制造的最基本的掩埋沟道MIG像素的示意性布局。

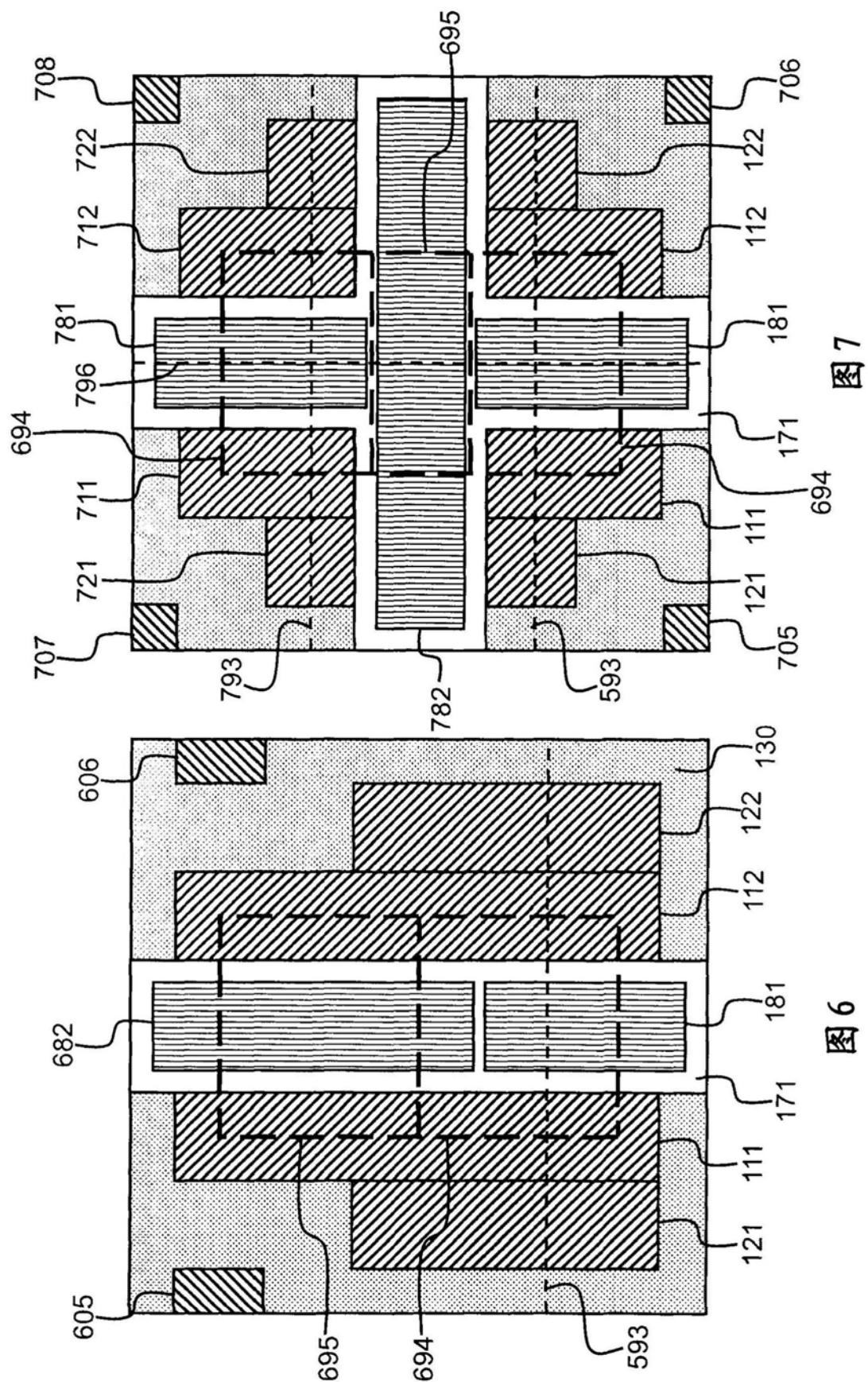

- [0033] 图6示出了本发明实施例的示意性布局,其包括具有额外重置栅极的掩埋沟道MIG像素。

- [0034] 图7示出了本发明实施例的示意性布局,其中掩埋沟道双MIG像素包括用于传送和重置的额外栅极。

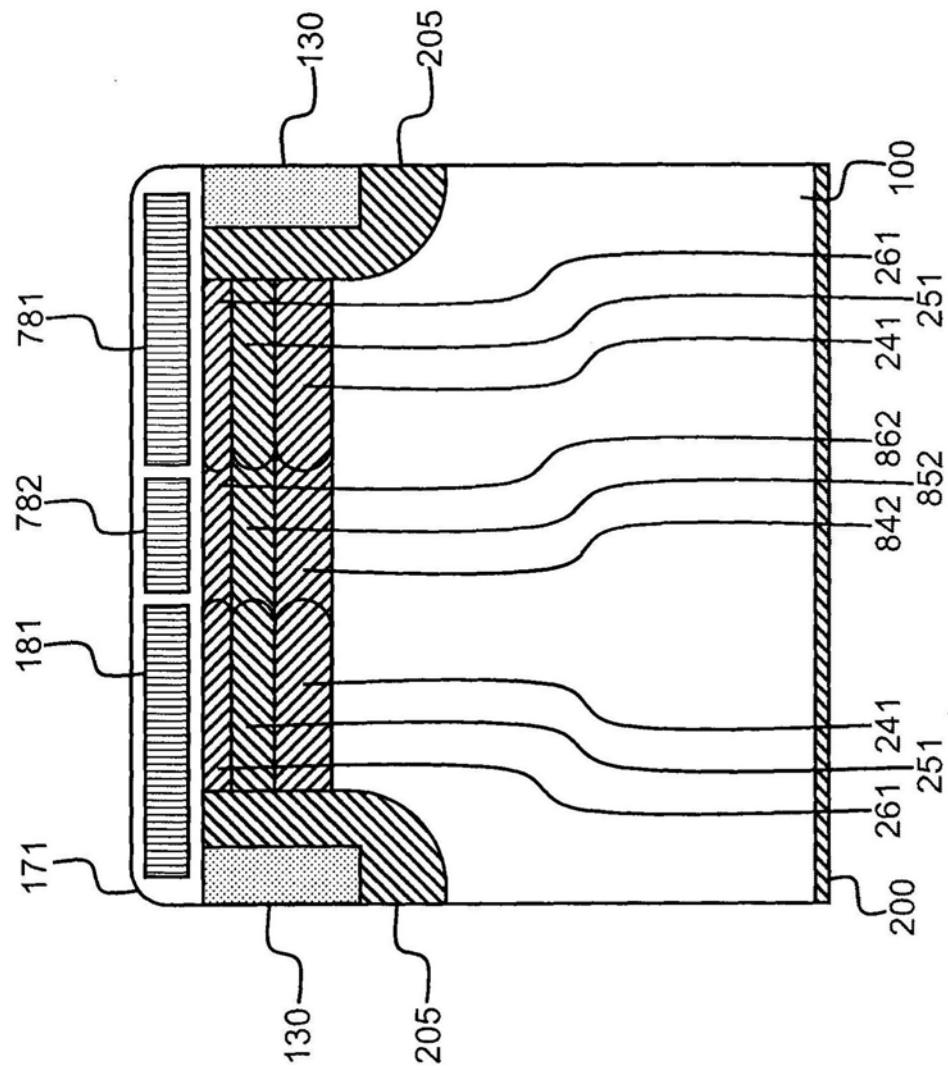

- [0035] 图8示出了沿着图7所示MIG像素的线796的示意性截面。

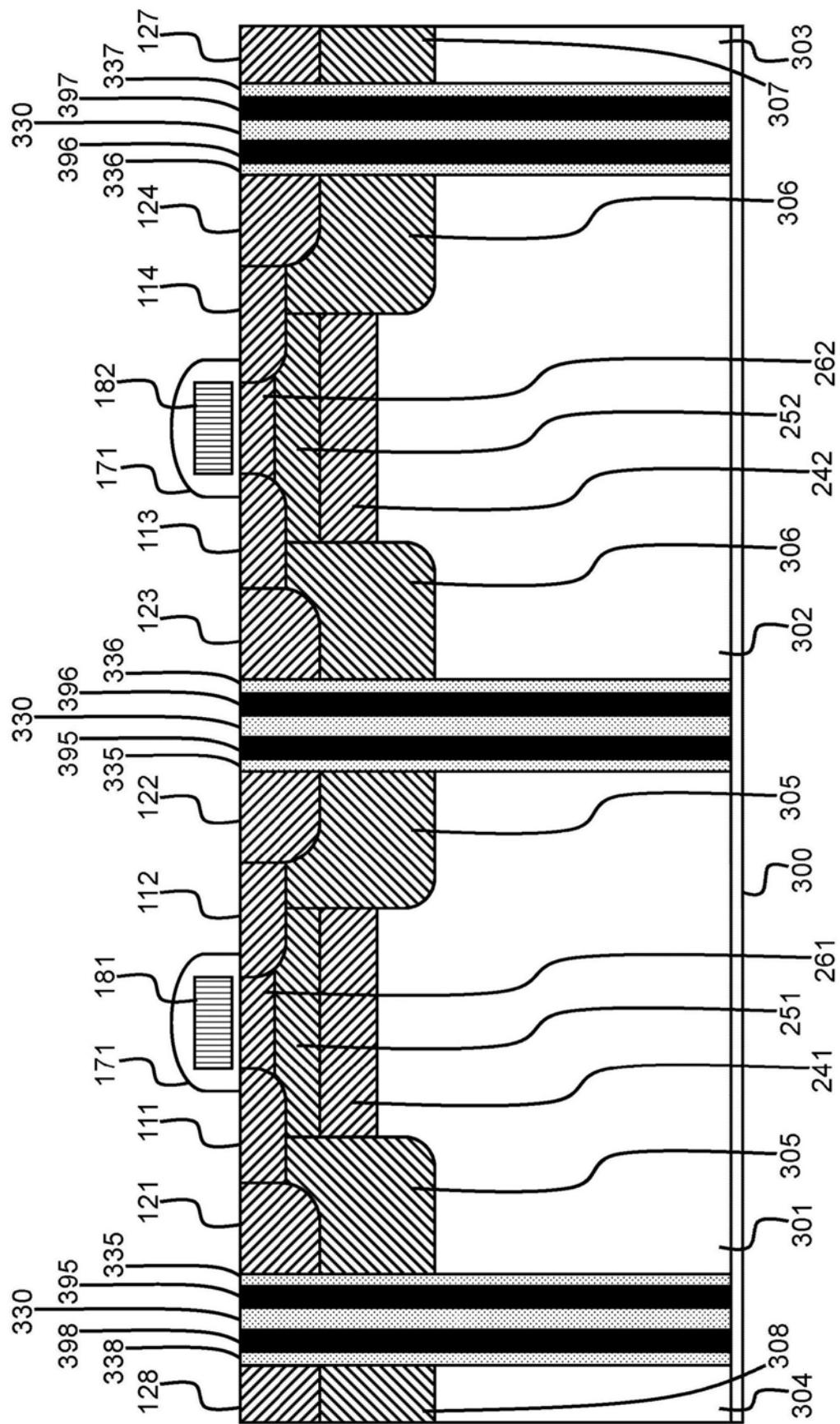

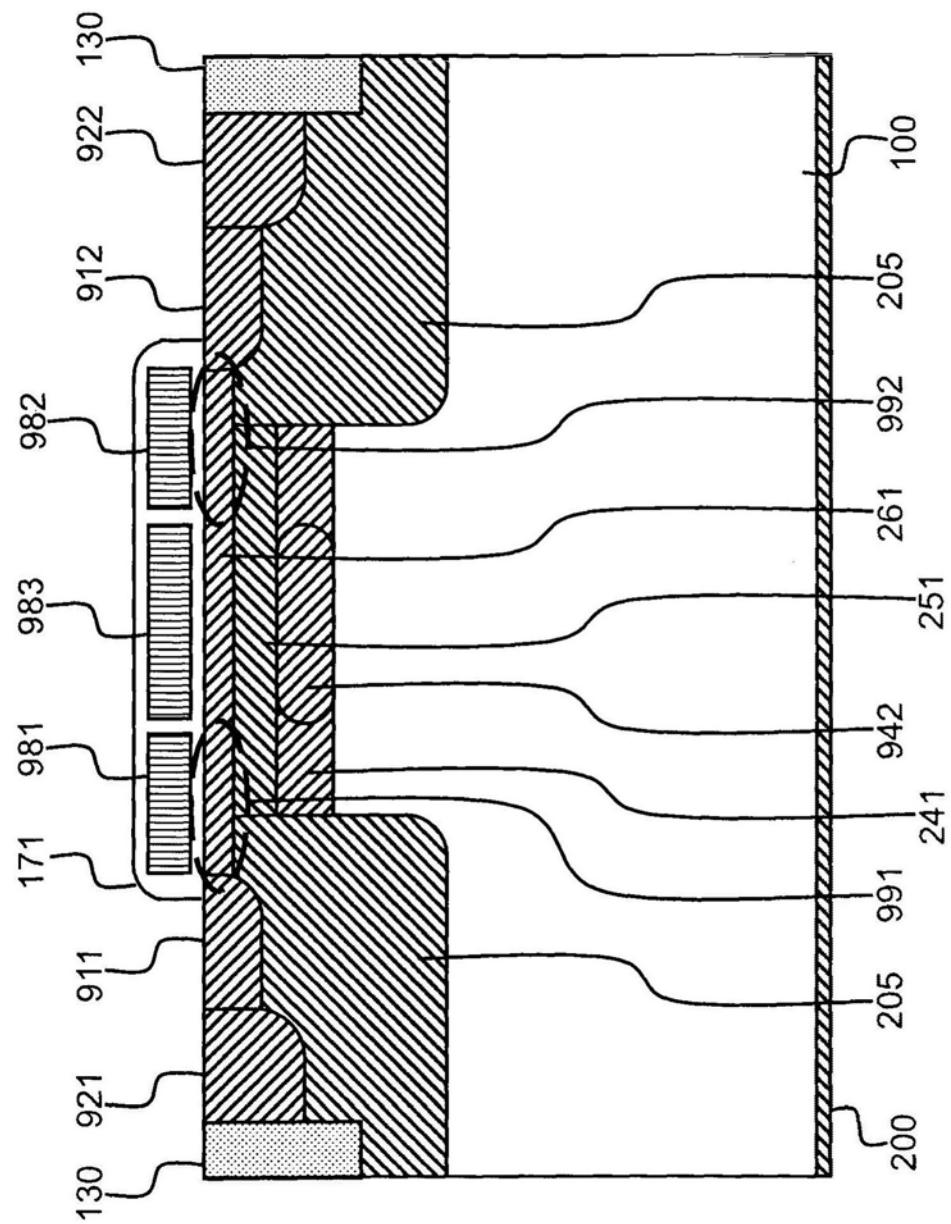

- [0036] 图9示出了包括三栅极掩埋沟道MIG像素的本发明实施例的示意性截面。

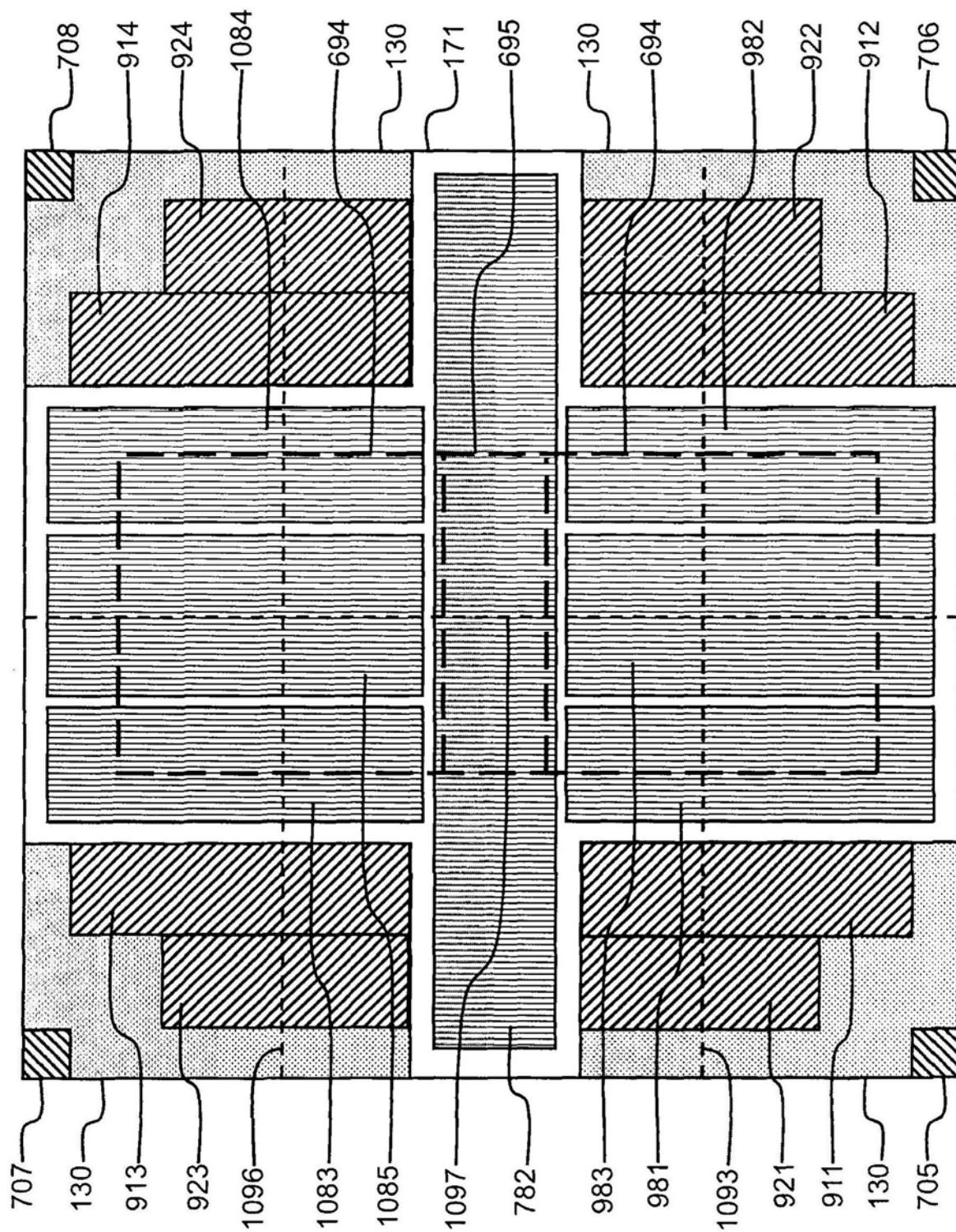

- [0037] 图10示出了本发明实施例的示意性布局,其中,掩埋沟道三栅极双MIG像素包括用于传送和重置的额外栅极。

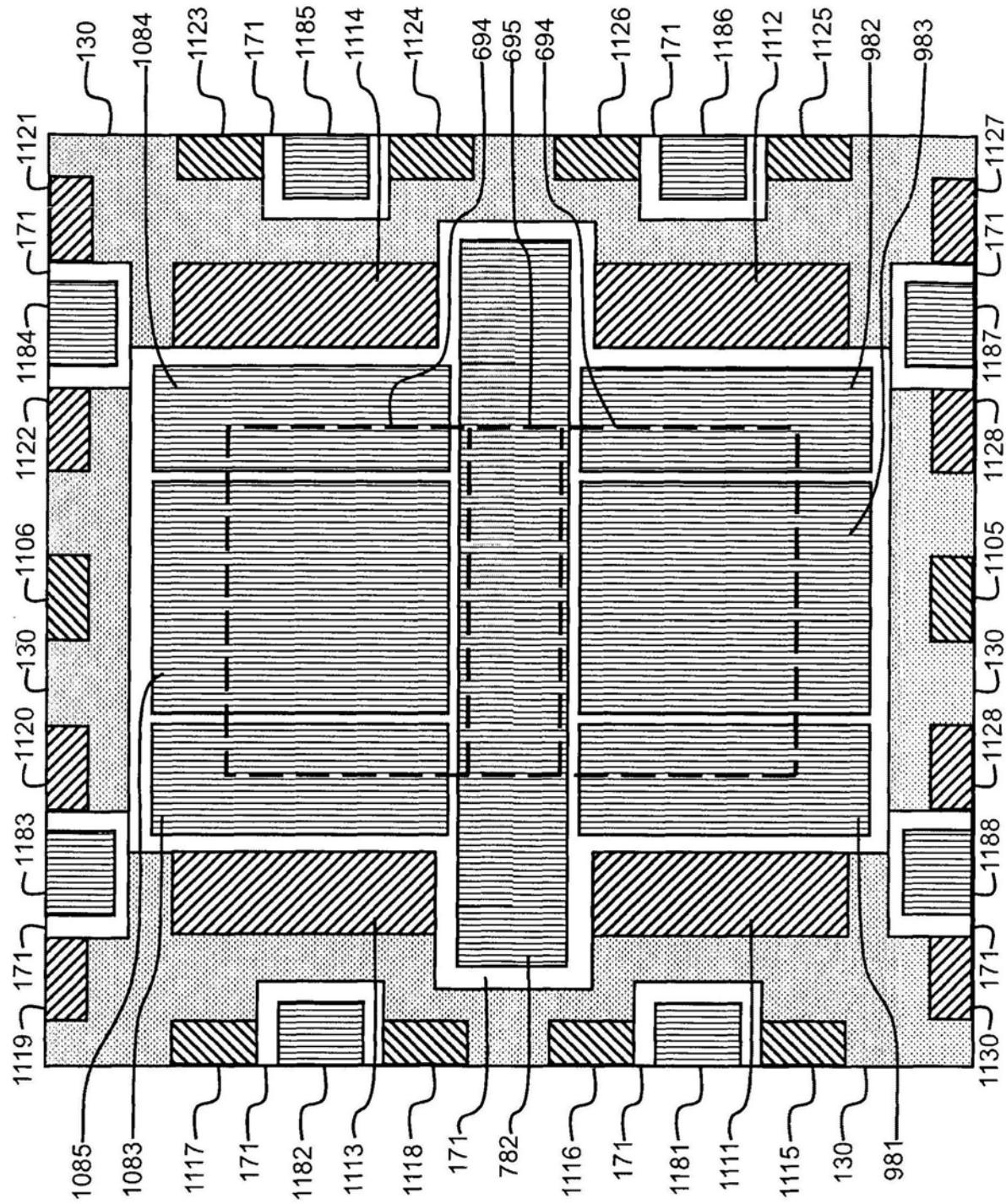

- [0038] 图11示出本发明实施例的示意性布局,其中,掩埋沟道三栅极双MIG像素包括用于传送和重置的额外栅极以及四个附加的选择晶体管。

- [0039] 在所有附图中,通过相同的参考标号来表示具有类似技术功能的部分所示结构。

## 具体实施方式

[0040] 在以下描述中使用半导体辐射探测器的特定基本词汇,其中,利用一个或多个像素特定的晶体管检测累积在像素内的辐射引起的信号电荷的量。晶体管是半导体器件,其中,称为沟道或基极的半导体材料的区域位于两个电极(在场效应晶体管中为源极和漏极,而在双极结晶体管中为发射极和集电极)之间。场效应晶体管的栅极是与沟道电绝缘的第三电极,使得栅极相对于源极和漏极(以及半导体探测器的块或衬底)的电位确定沟道的电流承载能力。为了称为栅极,场效应晶体管的电极必须适当地位于结构中,使得其引起的电场对沟道的至少一部分具有可测量的效应。

[0041] 关于以示意性截面表示示出半导体辐射探测器的方式,还使用传统的选择。截面的下边缘表示探测器芯片的所谓的背侧,而在截面的顶部找到所谓的前侧。如此,本发明不以任何方式限于背侧和前侧的限定;通常,以下描述的基于MIG的晶体管结构在衬底的一个表面或一些表面上。

[0042] 图9示出了背侧照明的掩埋沟道三栅极MIG像素的示意性截面,其在前侧上具有源极接触掺杂920、源极掺杂911、漏极接触掺杂922和漏极掺杂921,它们都是第二导电类型。根据应用于这种情况的指定,在该结构中,接触掺杂921和922是像素掺杂。MIG层241、势垒层251和掩埋沟槽261可以类似于先前图2所述结构中的对应标号部分,并且MIG层241还可以更一般地仅称为半导体材料的第一层。应该注意,指定“第一”不表示任何配置顺序中的第一;这仅仅是一个名称,并且是参照MIG层的便利方式。

[0043] 此外,存在任选的第二导电类型MIG层增强掺杂942。其是如下一个区域,其净掺杂高于该区域周围的剩余MIG层的净掺杂;MIG层中较高净掺杂的区域与栅极983垂直对齐。增强掺杂还可以存在于势垒层251和掩埋沟道261中;这种增强掺杂可以都利用同一掩模注入。此外,利用同一掩模注入还可以是MIG层增强掺杂942下方的掺杂,其优选是第一导电类型。MIG层增强掺杂942的目的是对齐主(“外”)栅极983下方的信号电荷。将栅极983称为“外”栅极强调其与MIG层241的差异,MIG层241组成(如其名称指示的)内栅极或者更适当地

为经修改的内栅极。为了用作栅极，主栅极983处于至少部分地与像素特定的场效应晶体管的源极和漏极之间的沟道的位置相对应的位置处。

[0044] 在图9的结构中，在主栅极983的两侧具有额外的栅极981和982。位于外栅极983的一侧上的额外栅极意味着所述额外栅极从外栅极983水平偏移。例如，可以朝向源极掺杂911(作为第一额外栅极981)或朝向漏极掺杂912(作为第二额外栅极982)水平偏移，但是其他方向也是可以的，这在以下进行解释。电绝缘材料171将主栅极983和额外栅极981和982与沟道261隔开，在该结构中，沟道261穿过连接位于势垒层251而非MIG层241的相对侧上的源极911和漏极912的掩埋沟道层。在该具体实施例中，电绝缘材料的公共层包封主栅极983以及额外栅极981和982，但是可以呈现其中每个栅电极都具有其自身的电绝缘的实施例。

[0045] 操作角度的期望特征是，最高的沟道阈值电压和/或最高的沟道电阻位于主栅极983下方，MIG层中的信号电荷利用主栅极983来对齐。为了实现该目的，额外栅极981和982最有利地被偏置，使得阈值电压和/或沟道电阻在额外栅极981和982下方远低于在主栅极983下方。可以表征额外栅极的位置，使得每个额外栅极都位于对应的MIG边界区域上方，像素特定的晶体管中的沟道的一部分在该边界区域处与MIG层的边缘垂直对齐。以这种方式，通过虚线椭圆991示出的伪源极被创建在栅极981下方，而由虚线椭圆992示出的伪漏极被创建在栅极982下方。这里使用的术语“伪”是指以下事实：将晶体管的结构划分为掺杂区域，利用椭圆991和992示出的区域仍然属于沟道，尽管操作性地采取外栅极981和982的适当偏置，它们的行为如同它们分别是源极和漏极的延伸一样。这种配置能够实现MIG层中存在的信号电荷的精确读出。

[0046] 在图9中，假设第二导电类型的掩埋沟道261的掺杂浓度大于与硅界面相邻的第一导电类型的阱掺杂205的掺杂浓度。这自然不是强制条件。实际上，可以省略整个掩埋沟道，但是这将自然地显著增加1/f噪声。

[0047] 图10示出了背侧照明的掩埋沟道三栅极双MIG像素的示意性前侧布局，其包括用于传送和重置的额外栅极。沿着线1093的截面对应于图9，并且沿着线1096的截面导致类似于图9所示的截面。沿着线1097的截面基本类似于图8的截面(唯一的区别是在图8中不存在MIG层的增强掺杂)。第一导电类型的接触掺杂705、706、707和708用于创建针对第一导电类型的阱掺杂205的接触。双MIG像素还包括第二场效应晶体管，其包括附加源极掺杂913、附加源极接触掺杂923、附加漏极掺杂914和附加漏极接触掺杂924，它们都是第二导电类型。此外，还具有属于双MIG像素的上部的两个额外栅极1083、1084以及另一主栅极1085。为了利于MIG像素的上部与下部之间的信号电荷传送和重置，还具有位于将像素的两个场效应晶体管分离的间隙上方的传送和重置栅极782。

[0048] 双MIG像素的想法在于，信号电荷可以在主栅极983、1085下方的两个MIG之间传送，以能够实现非破坏性相关双采样(NDCDC)读出。阱掺杂的开口包括三个部分：下部694、中部695和上部694。下部和上部类似标为694的原因是，其中的分层结构是相同的。如图8所示，在阱掺杂中的开口的中部695中，MIG层842、势垒层852和掩埋沟道层862有利地均比上部和下部694具有更弱的掺杂，这样利于重置。该配置的另一优势是，当不施加重置电位时，在势垒层中形成势垒，使得来自耗尽界面的界面泄漏电流朝向源极和/或漏极掺杂流入掩埋沟道层而不是MIG层。另一个特征是，被传送和重置栅极下方的MIG层收集的信号电荷将流向MIG层的位于一个主栅极下方的部分而不是掩埋沟道层。以这种方式，保持100%填充

因数,同时信号电荷与界面泄漏电流隔离,这是本发明的一个目的。有利地,利用两个注入掩模形成分层结构842、852、862以及241、251、261;第一掩模对应于抗蚀剂覆盖区域694和695中的开口,以及第二掩模对应于覆盖标为694的两个区域的抗蚀剂中的开口。

[0049] 源极和漏极接触掺杂921、923、922和924可以分别连接至按列的线,而栅极782、781、982、983、1083、1084、1085分别连接至按行的线。在假设电压跨度过为3.3V,第一导电类型为p型,第二导电类型为n型,并且利用源极电流模式读出的情况下,例如可以以下方式来操作像素。首先,像素处于积分级,其中,两个主栅极983、1085保持在+2.5V,与漏极相邻的额外栅极982、1084保持在+3.3V,与源极相邻的额外栅极981、1083例如保持在0V(或+1V),并且传送和重置栅极782保持在0V。通常,可以说采用上述假设,得到以下关系:

$$V_{rg,i}, V_{es,i} < V_{mg,i} < V_{ed,i}$$

[0051] 其中, $V_{rg,i}$ 是积分期间的重置和传送栅极的电位,

[0052]  $V_{es,i}$ 是积分期间的源极侧额外栅极的电位,

[0053]  $V_{mg,i}$ 是积分期间的主栅极的电位,以及

[0054]  $V_{ed,i}$ 是积分期间的漏极侧额外栅极的电位。接下来,通过首先例如将+3.3V连接至与上部主栅极1085相邻定位的源极侧额外栅极1083,然后将+1.5V连接至传送和重置栅极782,像素的下部的MIG层中存在的信号电荷被传送至像素上部的MIG层。然后,下主栅极983和与漏极相邻的额外栅极982连接至0V,此后传送和重置栅极连接回到0V。通常,可以说简单地创建条件

$$V_{mg,tr}, V_{ed,tr} < V_{rg,tr}$$

[0056] 其中

[0057]  $V_{mg,tr}$ 是传送期间的一个主栅极的电位,

[0058]  $V_{ed,tr}$ 是传送期间的对应漏极侧额外栅极的电位,以及

[0059]  $V_{rg,tr}$ 是传送期间的重置和传送栅极的电位,

[0060] 并且随后将传送和重置栅极拉回到低电位。以这种方式利用这些信号电荷,它们原始累积在特定主栅极下方的MIG层中,首先在重置和传送栅极中然后镶嵌在MIG层中水平迁移,使得它们最终加入原始累积在像素的另一晶体管的主栅极下方的MIG层中的那些信号电荷。

[0061] 此后,主栅极983连接至+2.5V,并且额外栅极981和982连接至+3.3V。更一般地,晶体管中主栅极(其下方的MIG层不具有信号电荷)的电位保持在比任何直接相邻的额外栅极低的电位,并且如果读取像素中的其他晶体管,其也保持低于像素中其他晶体管的源极侧额外栅极的电位。最后提到的不是强制的;其他晶体管还可以通过将所述额外电极保持在低电位来保持闭合。目的是在任何情况下确保所述主栅极下方的空MIG层也暂时保持为空。然后,通过测量源极接触掺杂921上的源极电流来进行对应于空MIG的第一CDS(相关双采样)测量。

[0062] 在像素的下晶体管中执行空MIG测量之后,通过首先将+1.5V连接至传送和重置电极782来将信号电荷从像素的上部传送至下部。然后,上主栅极1085和上额外栅极1083、1084连接至0V,此后传送和重置栅极782被连接回到0V。该过程是上述的镜像,其中,信号电荷首先从下晶体管下方的MIG层传送至上晶体管下方的MIG层,除了信号电荷现在移动的量包括在先前的积分阶段累积在像素中的所有信号电荷,上面解释的第一信号电荷传送仅移

动原始累积在一个晶体管下方的那些信号电荷。

[0063] 接下来,上主栅极1085连接回到+2.5V,并且上额外栅极1083、1084连接至+3.3V。然后,通过测量源极接触掺杂921上的源极电流来进行与像素中存在的信号电荷的总量相对应的第二CDS测量。同时,可以对上源极接触掺杂923进行第一CDS测量。通过从第一CDS结果中减去第二CDS读出结果来得到源极接触掺杂921上的最终CDS读出结果。

[0064] 在信号电荷进一步从像素的下部传送至像素上部的情况下,可以得到另一CDS读出结果。有利地,来自像素的上部和下部的CDS读出结果利用不同的增益设置来得到,使得可以提供具有不同灵敏度(ISO值:ISO是国际标准组织的首字母缩略表示)的两个读出结果。通过多次执行这种NDCDS读出,可以自然地得到对应于不同ISO设置的若干读出结果。

[0065] 应该注意,在电荷传送状态期间,主栅极和相邻的额外栅极可以首先连接至0V,此后在该主栅极被带至+2.5V且所述额外栅极被带至+3.3V之前,传送和重置栅极被短暂偏置为+1.5V并回到0V。还应该注意,这里解释的传送过程仅仅是实例,本领域技术人员在阅读这种解释之后能够实现其他过程,其想法是利用主栅极、额外栅极以及传送和重置栅极的适当电位简单地控制收集的信号电荷的移动。

[0066] 额外栅极可用作非常实际的选择方式:如前面简单说明的,任何像素中的任何晶体管可以通过将这种晶体管中的额外栅极保持为使得所述晶体管中的沟道保持闭合的电位(例如,充分低的电位)来保持闭合。因此,适当使用额外栅极能够省去像素特定的选择晶体管,这简化了探测器的结构。

[0067] 通过将+0V连接至主栅极983、1085以及额外栅极981、982、1083、1084以及通过将+3.3V(或例如+2.8V)连接至传送和重置栅极782来执行像素的重置。通常,可以表征重置阶段,使得重置(和传送)栅极的电位高到与像素中的所有其他栅极的电位相关,半导体材料内得到的电场足以将所有先前累积的信号电荷驱动出整个像素下方的MIG层。

[0068] 应该注意,例如通过在两行的读出过程中使与源极相邻的上额外栅极1083在下行中闭合(例如,0V)且与源极相邻的下额外栅极981在上行中闭合,例如在源极电流读出模式中,还可以同时读出两个不同行。这也适用于源极跟随器读出模式。在使用漏极电流读出模式的情况下,前面描述的过程可用于栅极982和1084(代替981和1083)。

[0069] 图11示出了背侧照明的掩埋沟道三栅极双MIG像素的示意性前侧布局,每个像素都具有传送和重置栅极以及四个附加的选择晶体管。第一导电类型的接触掺杂1105、1106连接至第一类型阱掺杂。在该设计中,假设相互相邻的源极和源极接触掺杂对(例如参照图10中的参考标号911和921示出)被单个源极掺杂取代:例如参见源极掺杂1111和1113。类似地,先前描述的相互相邻的漏极和漏极接触掺杂对被单个漏极掺杂取代,如漏极掺杂1112和1114。图11中的源极掺杂和漏极掺杂在该结构中称为像素掺杂,因为不存在独立的接触掺杂。类似地,在具有最小尺寸的栅极1181、1182、1183、1184、1185、1186、1187和1188的选择晶体管中,仅具有一个源极掺杂1115、1117、1119、1121、1123、1125、1127和1129以及一个漏极掺杂1116、1118、1120、1122、1124、1126、1128和1130。

[0070] 重要地,注意,像素特定的选择晶体管的栅极下方的掺杂结构可以不同。例如,像素特定的选择晶体管可具有栅极下方的掺杂结构,其包括以下的任何组合:

[0071] -第一导电类型的阱掺杂205(在栅极下方不存在阱的情况下,在阱掺杂中必须具有开口),

[0072] -分层结构241、251、261(参见图2),以及

[0073] -分层结构842、852、862(参见图8)。

[0074] 以这种方式,可以根据特定的需求调整各个选择晶体管的阈值电压。换句话说,一个像素可以包括至少两个选择晶体管,它们具有不同的阈值电压。例如,如果选择晶体管的漏极连接至额外栅极,则具有尽可能小的阈值电压将是有利的,因为这利于额外栅极下方的伪源极和漏极的形成。进行选择晶体管下方的阱延伸也是有利的,因为这种方式不存在信号电荷将不利地在选择晶体管下方的MIG层中被收集的风险,这里它们将不用于任何测量。

[0075] 图11的像素以与图10的像素的类似方式进行操作。唯一的差别在于,选择晶体管能够进行像素特定的重置。在最简单的结构中,两个像素特定的选择晶体管的漏极分别连接至传送和重置栅极782以及例如至上主栅极1085。在另一像素特定的重置配置中,下主栅极983的栅极也连接至选择晶体管的漏极。此外,可以使用更复杂的像素特定的重置方案,其中涉及所有四个选择晶体管。在像素特定的重置中,选择晶体管的栅极应该按列独立或非独立地连接,而像素特定的选择晶体管的源极应该按行独立连接。实际的三栅极MIG晶体管的源极1111、1113和漏极1112、1114应该在独立的线上按列连接,以及没有连接至选择晶体管的实际的三栅极MIG晶体管的所有栅极都应该按行独立连接。以这种方式,在0V连接至主栅极和额外栅极以及+3.3V连接至传送和重置栅极线之前,通过将0V连接至按列的选择晶体管栅极,按列的电子器件可判定是否执行像素特定的重置(例如,当信号电荷的量为NDCDC FWC的50%时)。

[0076] 图7示出了能够进行NDCDS读出的背侧照明的掩埋沟道双MIG像素的前侧示意布局。在图7的像素中,去除图10的三栅极结构的额外栅极但保留传送和重置栅极,其在该图的中心由参考标号782来表示。沿着线593的截面对应于图2,以及沿着线793的截面对应于图2所示的类似截面。另一方面,沿着线796的截面对应于图8。在图7中,像素上部中的源极掺杂711、源极接触掺杂721、漏极掺杂712和漏极接触掺杂722都是第二导电类型。源极接触掺杂721和漏极接触掺杂722称为像素掺杂。当与图10和图11中的主栅极的操作相比时,像素下部中的栅极181以及像素上部中的栅极781的操作具有差异:需要利用积分电压,除非选择晶体管被例如提供用于源极接触掺杂121、721。否则,该操作非常类似于图10的像素。图7的像素中与所有现有配置具有显著差异的特征是,传送和重置栅极配置在其下方具有比在实际栅极181、781下方更少掺杂的分层结构;参见在图8中利用参考标号842、852和862表示的较少掺杂的分层结构。

[0077] 图6示出了背侧照明的掩埋沟道MIG像素的示意性前侧布局,其中沿着线593的截面对应于图2。第一导电类型的接触掺杂605、606形成到达第一类型阱掺杂下方的接触。在这种情况下,重置栅极682仅用于重置。其从主栅极181水平偏移,使得重置栅极682和主栅极181位于分离源极111和漏极112的间隙上方。然而,重置栅极682下方的分层结构类似于图7、图10和图11的栅极782下方的分层结构,即,重置栅极682下方的分层结构中的层的掺杂浓度小于实际栅极181下方的分层结构的层中的掺杂浓度。以与图7、图10和图11相同的方式,在图6中利用表示为694和695的虚线矩形来示出这种差异。

[0078] 适当的MIG探测器/像素操作需要在像素掺杂与第一导电类型的第一接触(其可以是阱掺杂的第一导电类型的接触掺杂(707、1105)、接触任选的第一导电类型的背侧导电层

的第一导电类型的接触掺杂(200)或针对背侧的第一导电类型的累积或反转层的第一导电类型的接触)之间施加反向偏置。

[0079] 至此示出了示例性实施例的变形和修改,它们都不背离由权利要求限定的保护范围。以下展示一些实例。

[0080] 即使至此所描述的结构在主栅极的两侧具有额外栅极,但可以通过仅在主栅极的源极侧或漏极侧使用额外栅极来得到至少一些优势。仅使用一个额外栅极的非对称实施例要求源极、漏极和栅极电位之间的适当关系,这需要考虑非对称性。

[0081] 即使布局图将各种掺杂图案示出为矩形,但这仅仅是为了图形清楚的目的;优选地,可以在掺杂区域具有一些其他形状(例如,六角形)的结构中利用相同的原理。此外,混合实施例也是可以的,其中一些掺杂图案是矩形而其他是三角形、曲面形状和/或多边形。

[0082] 所描述层的净有效掺杂中的局部变化(如MIG层的净掺杂的局部变化)在各个位置是可能的,并且它们可用于成形控制信号电荷在结构内的流动的电场。

[0083] 可以用三维结构代替所讨论的至少一些平面的基本为二维的分层结构,其中三维是指一些结构在各个深度处沿着其水平维度具有功能的显著变化。

[0084] 代替源极电流模式读出,可以利用诸如漏极电流读出和源极跟随器读出的其他读出机制。

[0085] 衬底可以是任何导电类型。

[0086] 用于创建注入图案的掩模的数量不受本发明限制。在上面的描述中,例如指出多个堆叠层中的掺杂增强可以利用同一掩模来实现,但还可以使用不同的掩模。

[0087] 掩埋沟道改善了伪源极和漏极的操作,因为如果不使用掩埋沟道,则主栅极和额外栅极之间的间隙将会更大。原因在于,在存在掩埋沟道的情况下,间隙下方的阈值电压小于直接在栅极下方的阈值电压。如果失去掩埋沟道,则间隙下方的阈值电压将会大于栅极下方的阈值电压。

图1

图2

图3

图4

图5

图8

图9

图10

图11