(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4259738号

(P4259738)

(45) 発行日 平成21年4月30日(2009.4.30)

(24) 登録日 平成21年2月20日(2009.2.20)

(51) Int.Cl.

F 1

H04L 25/02 (2006.01)

H04L 25/02

R

H03K 19/0175 (2006.01)

H03K 19/00

101 L

H04L 5/14 (2006.01)

H04L 5/14

請求項の数 8 (全 18 頁)

(21) 出願番号

特願2000-302788 (P2000-302788)

(22) 出願日

平成12年10月2日 (2000.10.2)

(65) 公開番号

特開2002-111749 (P2002-111749A)

(43) 公開日

平成14年4月12日 (2002.4.12)

審査請求日

平成18年8月15日 (2006.8.15)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100077517

弁理士 石田 敬

(74) 代理人 100092624

弁理士 鶴田 準一

(74) 代理人 100100871

弁理士 土屋 繁

(74) 代理人 100082898

弁理士 西山 雅也

(74) 代理人 100081330

弁理士 樋口 外治

最終頁に続く

(54) 【発明の名称】 双方向信号伝送用レシーバ

## (57) 【特許請求の範囲】

## 【請求項 1】

信号を信号伝送路の双方向に送受信する双方向信号伝送用のレシーバであって、前記信号伝送路に接続された信号線と、

レプリカ電圧を出力するレプリカドライバと、

該信号線の電圧をバッファする信号線電圧バッファ回路と、

該バッファ回路でバッファされた信号線電圧から受信信号を分離出力するハイブリッド回路であって、該ハイブリッド回路は、信号を保持するホールド回路、前記レプリカドライバに接続された第1のスイッチ回路および前記バッファ回路に接続された第2のスイッチ回路を含むハイブリッド回路と、

該ハイブリッド回路から出力された受信信号の論理値を判定する判定回路と、を備え、前記ハイブリッド回路から分離出力された受信信号の論理値を判定する時点の信号値と、それより一定時間前の信号値に係数を乗じた値との和を生成し、該生成された和の値を用いて判定を行うことを特徴とする双方向信号伝送用レシーバ。

## 【請求項 2】

請求項1に記載のレシーバにおいて、前記バッファ回路は電圧バッファ回路であり、前記ハイブリッド回路は容量結合ハイブリッド回路であることを特徴とするレシーバ。

## 【請求項 3】

請求項1に記載のレシーバにおいて、

前記バッファ回路は、電圧・電流変換を行うトランスコンダクタであり、

前記ハイブリッド回路は、前記信号線の電圧およびレプリカドライバの信号電圧をそれぞれトランスコンダクタで電圧・電流変換し、該各変換された電流の差に相当する電流を負荷デバイスに流すことで該信号線の電圧と該レプリカドライバの信号電圧との差を求め、前記受信信号を分離出力することを特徴とするレシーバ。

**【請求項 4】**

信号を信号伝送路の双方向に送受信する双方向信号伝送用のレシーバであって、

前記信号伝送路に接続された信号線と、

レプリカ電圧を出力するレプリカドライバと、

該信号線の電圧をバッファする信号線電圧バッファ回路と、

該バッファ回路でバッファされた信号線電圧から受信信号を分離出力するハイブリッド回路であって、該ハイブリッド回路は、信号を保持するホールド回路、前記レプリカドライバに接続された第1のスイッチ回路および前記バッファ回路に接続された第2のスイッチ回路を含むハイブリッド回路と、

該ハイブリッド回路から出力された受信信号の論理値を判定する判定回路と、を備え、

前記バッファ回路は電圧バッファ回路であり、前記ハイブリッド回路は容量結合ハイブリッド回路であり、

前記電圧バッファ回路の電圧ゲインを約1とし、該電圧バッファ回路と前記信号線との間を容量で結合し、該電圧バッファ回路の非動作期間には該容量の入力側ノードを当該電圧バッファ回路の出力に繋ぎ、且つ、該電圧バッファ回路の入力ノードを所定電位にブリッヂすることで当該電圧バッファ回路のオフセット電圧を補償することを特徴とする双方向信号伝送用レシーバ。

**【請求項 5】**

信号を信号伝送路の双方向に送受信する双方向信号伝送用のレシーバであって、

前記信号伝送路に接続された信号線と、

レプリカ電圧を出力するレプリカドライバと、

該信号線の電圧をバッファする信号線電圧バッファ回路と、

該バッファ回路でバッファされた信号線電圧から受信信号を分離出力するハイブリッド回路であって、該ハイブリッド回路は、信号を保持するホールド回路、前記レプリカドライバに接続された第1のスイッチ回路および前記バッファ回路に接続された第2のスイッチ回路を含むハイブリッド回路と、

該ハイブリッド回路から出力された受信信号の論理値を判定する判定回路と、を備え、

前記バッファ回路は、電圧・電流変換を行うトランスコンダクタであり、

前記ハイブリッド回路は、前記信号線の電圧およびレプリカドライバの信号電圧をそれぞれトランスコンダクタで電圧・電流変換し、該各変換された電流の差に相当する電流を負荷デバイスに流すことで該信号線の電圧と該レプリカドライバの信号電圧との差を求め、前記受信信号を分離出力することを特徴とする双方向信号伝送用レシーバ。

**【請求項 6】**

請求項5に記載のレシーバにおいて、

前記ハイブリッド回路における前記トランスコンダクタの電流を印加する負荷デバイスに対して、さらに、第1のトランジスタおよび第2のホールド容量を有するオフセット補償回路を接続し、

該オフセット補償回路において、前記バッファ回路の非動作時には、前記第1のトランジスタがダイオード接続構造となるように接続されると共に当該第1のトランジスタのゲートに前記第2のホールド容量が接続され、該バッファ回路の動作時には、該第2のホールド容量の電圧が該第1トランジスタのゲート電圧を保持することを特徴とするレシーバ。

**【請求項 7】**

信号を信号伝送路の双方向に送受信する双方向信号伝送用のレシーバであって、

前記信号伝送路に接続された信号線と、信号を保持する第1のホールド容量と、該信号線の電圧から受信信号を分離出力するハイブリッド回路と、該ハイブリッド回路の入力ノ

10

20

30

40

50

ードを駆動する基準電圧をドライバの出力シーケンスに応じて出力する基準電圧出力回路と、該ハイブリッド回路から分離出力された受信信号の論理値を判定する判定回路とを備えることを特徴とする双方向信号伝送用レシーバ。

**【請求項 8】**

請求項 7 に記載のレシーバにおいて、前記基準電圧出力回路は、前記ドライバが送っている信号系列のデータに応じた複数の制御電圧を発生する制御電圧発生回路と、該各制御電圧を受け取ってそれぞれ基準電圧を発生する複数の基準電圧用バッファと、該信号系列のデータに応じて該複数の基準電圧用バッファの出力のいずれかを選択する選択回路とを備えることを特徴とするレシーバ。

**【発明の詳細な説明】**

10

**【0001】**

**【発明の属する技術分野】**

本発明は複数の L S I チップ間や 1 つのチップ内における複数の素子や回路ブロック間の信号伝送、或いは、複数のボード間や複数の匡体間の信号伝送を高速に行うための信号伝送技術に関し、特に、これらの信号伝送を同時に双方向で行う双方向信号伝送用レシーバおよびハイブリッド回路に関する。

**【0002】**

近年、コンピュータやその他の情報処理機器を構成する部品の性能は大きく向上しており、例えは、D R A M ( Dynamic Random Access Memory ) 等の半導体記憶装置やプロセッサ等の性能向上は目を見張るものがある。そして、この半導体記憶装置やプロセッサ等の性能向上に伴って、各部品或いは要素間の信号伝送速度を向上させなければ、システムの性能を向上させることができないという事態になって来ている。具体的に、例えは、D R A M 等の主記憶装置とプロセッサとの間 ( L S I 間 ) の信号伝送速度がコンピュータ全体の性能向上の妨げになりつつある。さらに、サーバと主記憶装置或いはネットワークを介したサーバ間といった匡体やボード ( プリント配線基板 ) 間の信号伝送だけでなく、半導体チップの高集積化並びに大型化、および、電源電圧の低電圧化 ( 信号振幅の低レベル化 ) 等により、チップ間の信号伝送やチップ内における素子や回路ブロック間での信号伝送においても信号伝送速度の向上が必要になって来ている。そこで、高速伝送が可能な双方向信号伝送用レシーバおよびハイブリッド回路 ( Hybrid : ハイブリッド ) の提供が要望されている。

20

**【0003】**

**【従来の技術】**

L S I やボード間、或いは、匡体間のデータ伝送量の増加に対応するためには、1 ピン当たりの信号伝送速度を増大させる必要がある。これは、ピン数を増やすことによるパッケージ等のコストの増大を避けるためである。その結果、近年では、例えは、L S I 間の信号伝送速度が 1 G b p s を超え、将来 ( 3 ~ 8 年程度先 ) には、4 G b p s 或いは 10 G b p s といった極めて高い値 ( 高速の信号伝送 ) になることが予想されている。

**【0004】**

このような高い信号周波数では、信号の伝送路がその高い周波数に対して表皮効果による損失を与えること、および、寄生インダクタや寄生容量の影響で高周波成分が反射されること等に起因して伝送路の帯域に制限が生じる。この伝送路の帯域の制限は、例えは、芯線の太いケーブルを使うことで緩和されるが、大容量の伝送で多数の信号線を並列に束ねる必要がある場合には、ケーブル束の太さにも限界が生じることになる。

30

**【0005】**

前述したように、伝送周波数が高くなると、伝送路自体が信号伝送のボトルネックになる事態が発生する。

40

このようなボトルネックを解決するために、伝送路の双方向に同時に信号を送る双方向伝送や 1 つの符号で多数のビットを送る多値伝送などが行われる。双方向伝送においては、自分のドライバが送っている信号を信号線の信号電圧から差し引き、正味の信号電圧を分離して出力するためのハイブリッド回路が用いられる。

50

## 【0006】

## 【発明が解決しようとする課題】

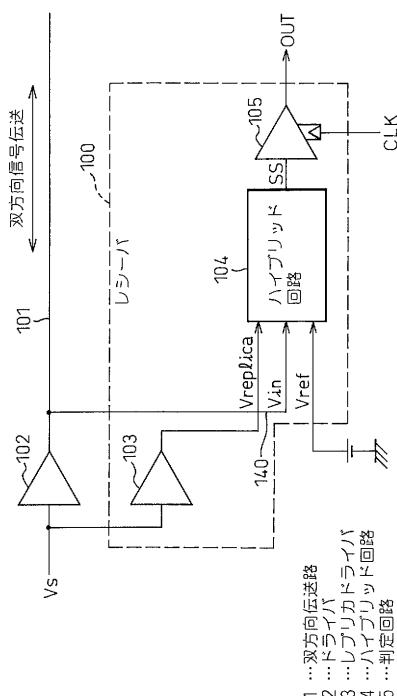

図1は双方向信号伝送システムの一例を概略的に示す図である。図1において、参照符号100はレシーバ、101は信号伝送路(双方向信号伝送路)、102はドライバ、103はレプリカドライバ、104はハイブリッド回路、そして、105は判定回路(Clocked Amplifier)を示している。ここで、図1では、シングルエンドの双方向信号伝送システムを示しているが、差動のシステムも同様である。なお、本発明は、シングルエンドおよび差動(相補信号)の両方に適用することができ、後述する各実施例では、シングルエンド或いは差動の構成が適宜選択して説明される。

## 【0007】

10

図1に示されるように、信号伝送路101の一端には、相手方へ伝えるべき信号(送信信号) $V_s$ を増幅してその信号伝送路101に出力するドライバ102、および、相手方から送られてきた信号(受信信号)を受け取るレシーバ100が設けられている。なお、信号伝送路101の他端(相手方)にも同様のドライバ102およびレシーバ100が設けられている。

## 【0008】

レシーバ100は、レプリカドライバ103、ハイブリッド回路104、および、判定回路105を備えている。レプリカドライバ103は、送信信号 $V_s$ を増幅して信号伝送路101に供給するドライバ102の出力に相当する信号を出力するもので、このレプリカドライバ103の出力電圧(出力信号)は、 $V_{replica}$ としてハイブリッド回路104に入力される。

20

## 【0009】

ハイブリッド回路104には、信号伝送路101の信号線電圧(入力信号) $V_{in}$ が信号線140を介して入力され、さらに、基準電圧(所定の直流電圧) $V_{ref}$ も入力される。ここで、判定回路105は、供給されるクロック信号CLKのタイミングで入力信号の論理レベルを判定するようになっている。

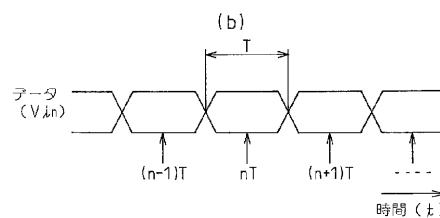

図2は従来の双方向信号伝送用ハイブリッド回路(容量結合ハイブリッド回路)の一例を説明するための図であり、図2(a)はハイブリッド回路104を概略的に示す回路図であり、図2(b)はデータ(入力信号 $V_{in}$ )と時間tとの関係を示す図である。図2(a)において、参照符号141~143はスイッチを示し、また、144はホールド容量を示している。

30

## 【0010】

図2(a)に示すハイブリッド回路104において、まず、スイッチ141および142をオン状態とし、スイッチ143をオフ状態とする。これにより、ホールド容量144の両端には、信号伝送路101の信号線電圧 $V_{in}$ およびレプリカドライバ103の出力電圧(レプリカ電圧) $V_{replica}$ が印加され、時間 $t = nT$ とすると(図2(b)参照)、ホールド容量144には、 $V_{replica}(nT) - V_{in}(nT)$ が充電(保持)される。

## 【0011】

次に、スイッチ141および142をオフ状態とし、スイッチ143をオン状態にすると、ハイブリッド回路104の出力(分離出力された受信信号)SSは、 $V_{ref} + [V_{replica}(nT) - V_{in}(nT)]$ となり、信号伝送路101の信号線電圧(入力信号) $V_{in}$ からドライバ102の出力の影響が除かれた信号となり、この信号SSを判定回路105で論理判定することで相手方から送られてきた信号を認識する。

40

## 【0012】

このように、ハイブリッド回路として、例えば、容量結合を用いて信号線電圧 $V_{in}$ とレプリカ電圧 $V_{replica}$ との差を取ることで受信信号を取り出す容量結合ハイブリッド回路104が知られている。この容量結合ハイブリッド回路104は、線型性が優れている利点がある反面、入力端子から容量を充放電するための充放電電流が流れ、この充放電電流が入力側にキックバック・ノイズ(kick-back noise)を発生させるという課題がある。また、キックバック・ノイズは、回路方式によっては、判定回路105からのノイズにより生

50

じることもある。

**【0013】**

すなわち、従来の双方向信号伝送においては、信号伝送路101の信号線電圧（入力信号） $V_{in}$ がハイブリッド回路104に直接入力されているため、ホールド容量144による充放電電流等の影響がそのまま信号伝送路101に伝えられ、伝送される信号波形に影響を与えて信号伝送に誤りが生じる危険があった。

本発明は、上述した従来の双方向信号伝送技術が有する課題に鑑み、ハイブリッド回路の持つ入力へのキックバック・ノイズの問題を解消した双方向信号伝送用レシーバおよびハイブリッド回路の提供を目的とする。

**【0014】**

**【課題を解決するための手段】**

本発明の第1の形態によれば、信号を信号伝送路の双方向に送受信する双方向信号伝送用のレシーバであって、前記信号伝送路に接続された信号線と、レプリカ電圧を出力するレプリカドライバと、該信号線の電圧をバッファする信号線電圧バッファ回路と、該バッファ回路でバッファされた信号線電圧から受信信号を分離出力するハイブリッド回路であって、該ハイブリッド回路は、信号を保持するホールド回路、前記レプリカドライバに接続された第1のスイッチ回路および前記バッファ回路に接続された第2のスイッチ回路を含むハイブリッド回路と、該ハイブリッド回路から出力された受信信号の論理値を判定する判定回路と、を備え、前記ハイブリッド回路から分離出力された受信信号の論理値を判定する時点の信号値と、それより一定時間前の信号値に係数を乗じた値との和を生成し、該生成された和の値を用いて判定を行うことを特徴とする双方向信号伝送用レシーバが提供される。

10

**【0015】**

本発明の第2の形態によれば、信号を信号伝送路の双方向に送受信する双方向信号伝送用のレシーバであって、前記信号伝送路に接続された信号線と、レプリカ電圧を出力するレプリカドライバと、該信号線の電圧をバッファする信号線電圧バッファ回路と、該バッファ回路でバッファされた信号線電圧から受信信号を分離出力するハイブリッド回路であって、該ハイブリッド回路は、信号を保持するホールド回路、前記レプリカドライバに接続された第1のスイッチ回路および前記バッファ回路に接続された第2のスイッチ回路を含むハイブリッド回路と、該ハイブリッド回路から出力された受信信号の論理値を判定する判定回路と、を備え、前記バッファ回路は電圧バッファ回路であり、前記ハイブリッド回路は容量結合ハイブリッド回路であり、前記電圧バッファ回路の電圧ゲインを約1とし、該電圧バッファ回路と前記信号線との間を容量で結合し、該電圧バッファ回路の非動作期間には該容量の入力側ノードを当該電圧バッファ回路の出力に繋ぎ、且つ、該電圧バッファ回路の入力ノードを所定電位にプリチャージすることで当該電圧バッファ回路のオフセット電圧を補償することを特徴とする双方向信号伝送用レシーバが提供される。

20

**【0016】**

本発明の第3の形態によれば、信号を信号伝送路の双方向に送受信する双方向信号伝送用のレシーバであって、前記信号伝送路に接続された信号線と、レプリカ電圧を出力するレプリカドライバと、該信号線の電圧をバッファする信号線電圧バッファ回路と、該バッファ回路でバッファされた信号線電圧から受信信号を分離出力するハイブリッド回路であって、該ハイブリッド回路は、信号を保持するホールド回路、前記レプリカドライバに接続された第1のスイッチ回路および前記バッファ回路に接続された第2のスイッチ回路を含むハイブリッド回路と、該ハイブリッド回路から出力された受信信号の論理値を判定する判定回路と、を備え、前記バッファ回路は、電圧 - 電流変換を行うトランスクンダクタであり、前記ハイブリッド回路は、前記信号線の電圧およびレプリカドライバの信号電圧をそれぞれトランスクンダクタで電圧 - 電流変換し、該各変換された電流の差に相当する電流を負荷デバイスに流すことで該信号線の電圧と該レプリカドライバの信号電圧との差を求め、前記受信信号を分離出力することを特徴とする双方向信号伝送用レシーバが提供される。

30

40

50

本発明の第4の形態によれば、信号を信号伝送路の双方向に送受信する双方向信号伝送用のレシーバであって、前記信号伝送路に接続された信号線と、信号を保持する第1のホールド容量と、該信号線の電圧から受信信号を分離出力するハイブリッド回路と、該ハイブリッド回路の入力ノードを駆動する基準電圧をドライバの出力シーケンスに応じて出力する基準電圧出力回路と、該ハイブリッド回路から分離出力された受信信号の論理値を判定する判定回路とを備えることを特徴とする双方向信号伝送用レシーバが提供される。

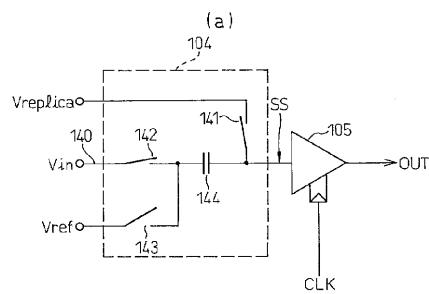

#### 【0017】

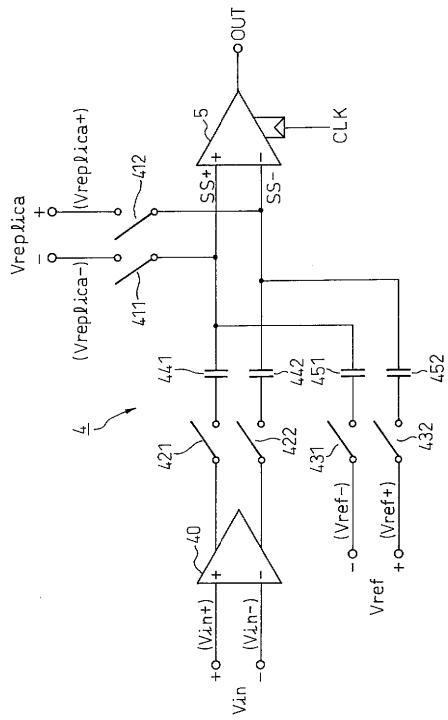

図3は本発明に係る双方向信号伝送用ハイブリッド回路の原理構成を示す回路図である。図3において、参照符号4はハイブリッド回路、5は判定回路、40はバッファ回路、411, 412; 421, 422; 431, 432はスイッチ、そして、441, 442; 451, 452は容量を示している。なお、図3では、差動の双方向信号伝送システムを示しているが、本発明は、シングルエンドのシステムに対しても同様に適用することができるはいうまでもない。10

#### 【0018】

図3に示されるように、本発明のハイブリッド回路4において、サンプリング容量（ホールド容量）441, 442の充放電は、入力バッファ回路（バッファ回路）40により行われるため、入力Vin側（信号伝送路101側）へ充放電電流が流れず、キックバック（キックバック・ノイズ）が低減される。

ここで、バッファ回路40が電圧バッファ回路の場合には、この電圧バッファ回路（40）の出力電圧が直接容量441, 442を充電する。また、バッファ回路40が電圧を電流に変換するトランスクンダクタの場合には、後に詳述するように、このトランスクンダクタの出力電流が負荷としてダイオード接続されたトランジスタと並列に容量が接続されたホールド回路に入力され、この容量の電圧がサンプルされることになる。20

#### 【0019】

いずれの場合もホールド手段（ホールド容量またはホールド回路）の充電電流は、バッファ回路或いはトランスクンダクタから供給されるためキックバックは低減することになる。

なお、バッファ回路を用いることによりバッファ回路のオフセット電圧が問題になるが、これはバッファ回路の非動差時に入力をゼロとし（入力を基準電圧に接続し）、その出力（オフセット出力）を出力容量に蓄積することで補償することができる。例えば、蓄積したオフセット出力を反転して（差動の場合は、信号線を交差させるだけでよい）基準電圧として使うことで補償することができる。30

#### 【0020】

このように、本発明によれば、ハイブリッド回路およびその後段のイコライザを構成するのに必要なサンプリング容量はバッファ回路により充放電されるため、キックバック・ノイズ低減することができ、例えば、レシーバを多数並列運転することが容易になる。

#### 【0021】

##### 【発明の実施の形態】

以下、本発明に係る双方向信号伝送用レシーバおよびハイブリッド回路の実施例を図面を参照して詳述する。40

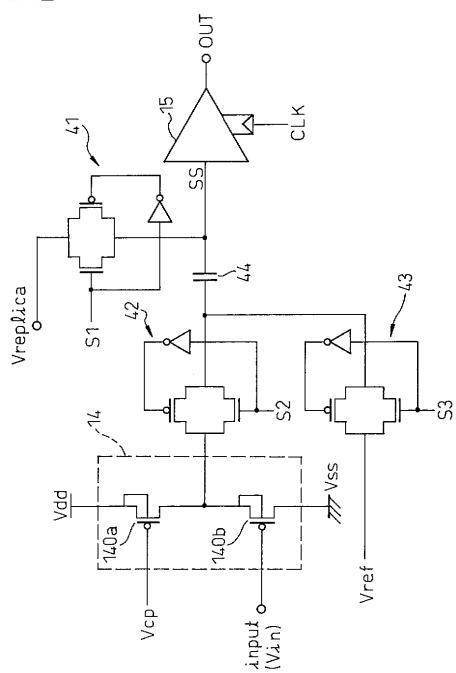

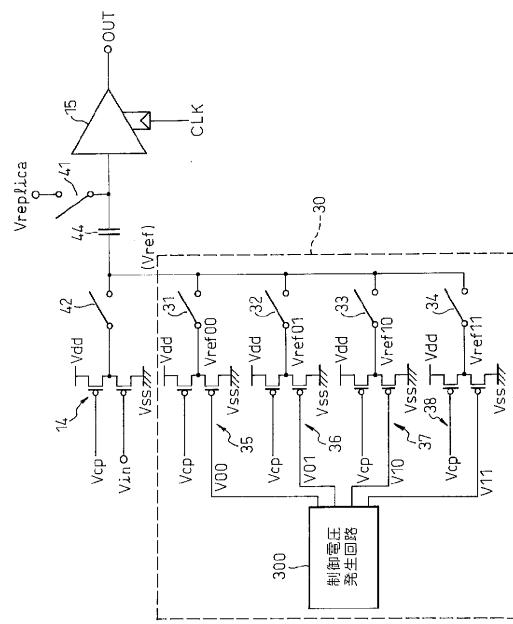

図4は本発明の第1実施例としての双方向信号伝送用ハイブリッド回路を示す回路図である。図4において、参照符号14はバッファ回路（ソースフォロワ回路：電圧バッファ回路）、15は判定回路、41～43はスイッチ回路、そして、44はホールド容量を示している。なお、本第1実施例は、シングルエンドの構成を示しているが差動の場合も同様である。

#### 【0022】

図4に示されるように、バッファ回路14は、ゲートにバイアス電圧Vcpが印加されたpチャネル型MOSトランジスタ（pMOSトランジスタ）140aと、ゲートに入力input（入力信号Vin）が供給されたpMOSトランジスタ140bとが電源線VddおよびVssの間に直列に接続されたソースフォロワ回路として構成され、その出力は、スイッ50

チ回路 4 2 を介してホールド容量 4 4 に供給されている。このソースフォロワ回路 1 4 は、その電圧ゲインがほぼ 1 となるように負荷デバイス ( 1 4 0 a ) と入力デバイス ( 1 4 0 b ) の n チャネル型ウェル ( n - w e l l ) が分離されるようになっている。

#### 【 0 0 2 3 】

各スイッチ回路 4 1 , 4 2 , 4 3 は、それぞれ並列接続された p M O S トランジスタおよび n M O S トランジスタとインバータとから成るトランスファゲート型スイッチとして構成され、ホールド容量 4 4 の端子に対して、信号線電圧 ( V in ) 、レプリカドライバの出力電圧 ( レプリカ電圧 ) V replica 、および、基準電圧 ( V ref ) を制御して印加するため 10 に用いられる。なお、スイッチ回路 4 1 ~ 4 3 は、前述した図 2 ( a ) におけるスイッチ 1 4 1 ~ 1 4 3 に対応する。そして、本第 1 実施例においては、図 2 ( a ) に示す従来のハイブリッド回路 1 0 4 に対して、信号線電圧 V in ( 入力 i n p u t ) が供給されたソースフォロワ回路 1 4 を設けるようにしたものである。

#### 【 0 0 2 4 】

本第 1 実施例のハイブリッド回路の動作を説明する。まず、サンプルに先立って、スイッチ回路 4 1 および 4 2 をオン状態 ( 各スイッチ回路 4 1 , 4 2 に供給する制御信号 S 1 , S 2 を高レベル “ H ” ) とし、スイッチ回路 4 3 をオフ状態 ( スイッチ回路 4 3 に供給する制御信号 S 3 を低レベル “ L ” ) とする。そして、サンプル時点において、スイッチ回路 4 1 をオフ状態 ( 制御信号 S 1 を低レベル “ L ” ) とする。これにより、その時点 ( サンプル時点 ) での信号線電圧 V in とレプリカ電圧 V replica との差がホールド容量 4 4 に蓄積される。

10

#### 【 0 0 2 5 】

次の判定期間において、スイッチ回路 4 2 をオフ状態 ( 制御信号 S 2 を低レベル “ L ” ) とし、次いで、スイッチ回路 4 3 をオン状態 ( 制御信号 S 3 を高レベル “ H ” ) として基準電圧 V ref をホールド容量 4 4 の一端に印加する。これにより、判定回路 ( 判定用コンパレータ回路 ) 1 5 の入力 S S ( ホールド容量 4 4 の他端 ) には、信号線電圧 V in とレプリカ電圧 V replica との差に基準電圧 V ref を加えた電圧が印加される。この値 S S を判定回路 1 5 で判定することにより、受信信号を正しく判定することができる。

20

#### 【 0 0 2 6 】

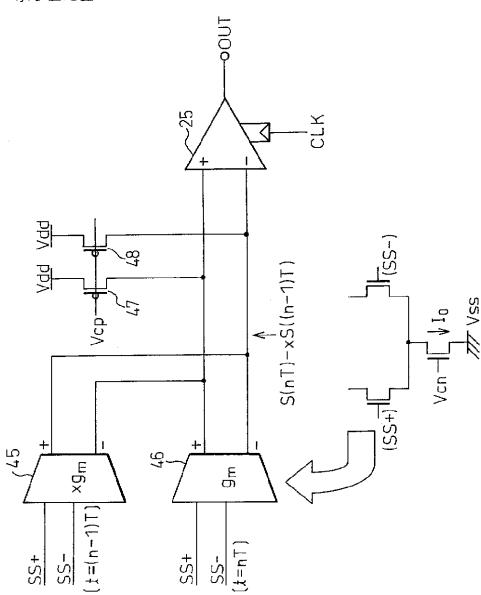

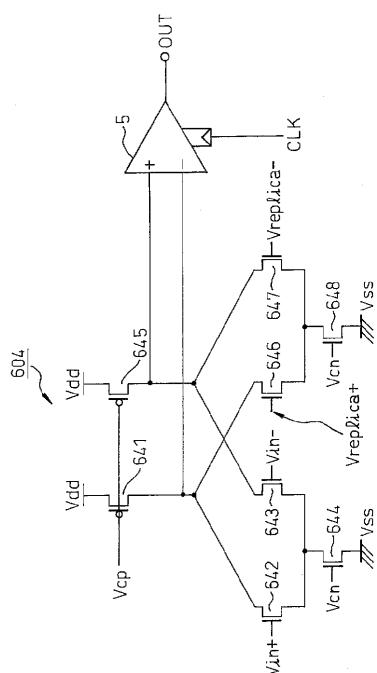

図 5 は本発明の第 2 実施例としての双方向信号伝送用ハイブリッド回路を示す回路図である。

30

図 5 に示されるように、本第 2 実施例は、判定用コンパレータ 2 5 ( 例えば、図 3 における判定回路 5 に対応 ) の前段に、電圧 - 電流変換を行うトランスコンダクタ 4 5 , 4 6 、および、負荷デバイス 4 7 , 4 8 を設けるようになっている。

#### 【 0 0 2 7 】

トランスコンダクタ 4 5 , 4 6 は、通常の n M O S トランジスタによる差動対として構成され、また、負荷デバイス 4 7 , 4 8 は、定電流モードにバイアスされた p M O S トランジスタとして構成されている。ここで、トランスコンダクタは、メインのトランスコンダクタ 4 6 ( t = n T ) 、および、イコライズのためのサブのトランスコンダクタ 4 5 ( t = ( n - 1 ) T ) で構成され、次のビットタイムから現在の値の係数倍 ( x ) を差し引いて [ S ( n T ) - x S (( n - 1 ) T ) ] を求め、ハイブリッド回路で分離した受信信号 ( 図 3 における信号 S S + , S S - ) における符号間干渉を補償することで、信号の判定をより正確に、或いは、信号の伝送距離をより長くすることが可能になる。なお、参照符号 V cp および V cn は、それぞれ p M O S および n M O S トランジスタのバイアス電圧を示している。また、係数 x の値は、n M O S 差動対のテイル電流で調整されるようになっている。

40

#### 【 0 0 2 8 】

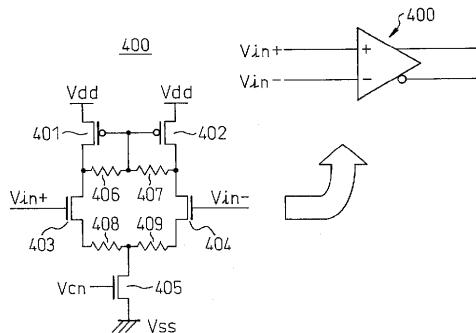

図 6 は本発明の第 3 実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路 4 0 0 を示す回路図である。

図 6 に示されるように、本第 3 実施例のバッファ回路 4 0 0 は、p M O S トランジスタ 4 0 1 , 4 0 2 、n M O S トランジスタ 4 0 3 ~ 4 0 5 、および、ポリシリコン抵抗 4 0 6

50

～409を備え、ポリシリコン抵抗408, 409を負荷と共にポリシリコン抵抗406, 407をソース側のディジェネレーション(degeneration)に用いた電圧バッファ回路として構成されている。

#### 【0029】

ここで、例えば、本第3実施例のバッファ回路400のゲインは3であり、このゲインの値は、ポリシリコン抵抗の抵抗比により正確に決めることができる。なお、本第3実施例では、初段のバッファ回路(400)のゲインが3であるため、次段の判定回路(図3の判定回路5を参照)の入力オフセットは初段の入力に換算するとその分小さくなるという利点がある。また、初段のバッファ回路に関しては、例えば、その信号伝送路のインピーダンスが50オーム程度の低インピーダンスであるため、入力デバイスの寸法を大きく(トランジスタ403, 404のゲート長およびゲート幅を大きく)することができ、その結果、入力オフセットを比較的小さくすることが可能になる。10

#### 【0030】

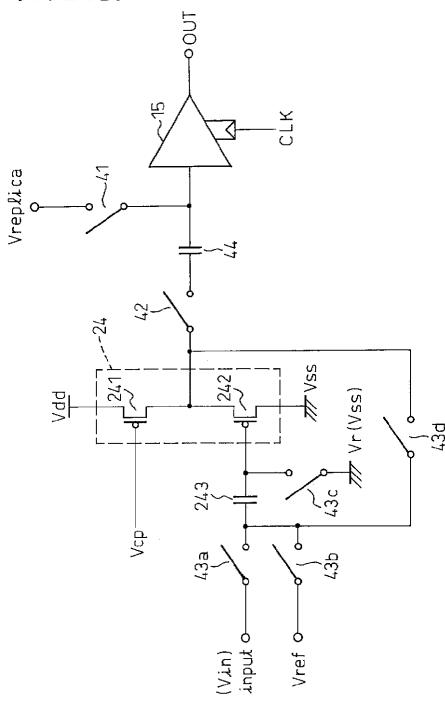

図7は本発明の第4実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図である。ここで、本第4実施例のバッファ回路は、電圧ゲイン1のソースフォロワ回路(24)で構成されており、入力オフセットの影響をキャンセルするために入力側に結合容量(243)を用いるようになっている。

#### 【0031】

まず、バッファ回路(ソースフォロワ回路)24の非動作期間(リセット期間)においては、スイッチ43cおよび43dがオン状態でスイッチ43aおよび43bがオフ状態とされ、結合容量243の入力側は入力端子から切り離されてバッファ回路24の出力に接続される。このとき結合容量243のバッファ回路入力端子側(トランジスタ242のゲート)は基準電圧Vr(例えば、低電位の電源電圧Vss)にチャージされる。このときのバッファ回路の出力電圧をVoffとすると、結合容量243に印加される電圧はVr - Voffになる。ここで、基準電圧Vrとしては、低電位の電源電圧Vssの他に、例えば、Vdd/2の電圧等を使用することができる。20

#### 【0032】

次に、バッファ回路の動作時には、スイッチ43cおよび43dがオフ状態でスイッチ43aがオン状態とされ、入力input(入力信号Vin)に対して容量243が直列に入ることになる。ここで、バッファ回路24のゲインはほぼ1であるから、このバッファ回路24の出力に現れるオフセット電圧は容量243に蓄積されたオフセット電圧でキャンセルされる。なお、トランジスタ241のゲートには、バイアス電圧Vcpが印加されている。また、スイッチ41、42および43bは、ハイブリッド動作のためのスイッチである。30

#### 【0033】

このように、本第4実施例によれば、バッファ回路(ソースフォロワ回路)24の電圧ゲインは1と小さいが、そのオフセット電圧が結合容量243でキャンセルされるため、バッファ回路全体としてのオフセット電圧は無視できる程度に小さくなる利点がある。また、結合容量243を使ってはいるが、信号線入力Vin(入力input)側からの負荷は結合容量243とソースフォロワ入力容量44の直列接続されたものが見えるので、入力容量も十分小さくなり、キックバック・ノイズ等の問題は発生しないことになる。40

#### 【0034】

図8は本発明の第5実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図である。

図4と図8との比較から明らかなように、本第5実施例は、第1実施例における基準電圧Vrefを出力する基準電圧出力回路30を備えている。基準電圧出力回路30は、容量結合ハイブリッド回路で判定期間に接続される基準電圧Vrefとして、レシーバと同じ側についているドライバが送っている信号系列の最新の2ビットが『00』、『01』、『10』または『11』かに応じて、基準電圧Vref00, Vref01, Vref10またはVref11のいずれかを選択して出力し、レプリカドライバ(図1の103参照)と実際に信号を出力す50

るドライバ(図1の102参照)との出力信号の差を補償するようになっている。

#### 【0035】

すなわち、基準電圧出力回路30は、ドライバが送っている信号系列のデータ(例えば、2ビット)に応じた複数(例えば、4つ)の制御電圧V00, V01, V10, V11を発生する制御電圧発生回路300と、各制御電圧V00, V01, V10, V11を受け取ってそれぞれ基準電圧Vref00, Vref01, Vref10, Vref11を発生する複数の基準電圧用バッファ35, 36, 37, 38と、信号系列のデータに応じて複数の基準電圧用バッファの出力(Vref00, Vref01, Vref10, Vref11)のいずれかを選択するスイッチ31, 32, 33, 34を備えている。なお、制御電圧発生回路300は、例えば、D/Aコンバータにより構成することができる。また、制御電圧発生回路300が出力する制御電圧V00, V01, V10, V11は、例えば、レシーバ(装置)をパワーオンした後に自動的に設定することができる。10

#### 【0036】

このように、本第5実施例によれば、レプリカドライバの信号と実際に除去すべきドライバの寄与電圧との差(これは伝送されている信号系列に依存する)を補償して、より正確な受信信号を分離出力することが可能になる。この場合も基準電圧はホールド容量に直接接続せずにバッファ回路を通して行うことで、レシーバ間の相互干渉のない良好な信号受信を行うことができる。

#### 【0037】

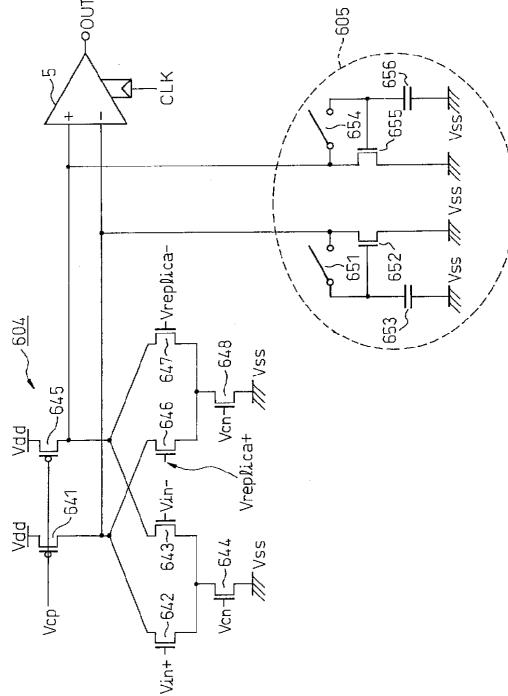

図9は本発明の第6実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図である。20

本第6実施例は、ハイブリッド回路(バッファ回路)604として電圧出力バッファ回路ではなく、電圧を電流に変換するトランスコンダクタを使用するものである。

#### 【0038】

すなわち、図9に示されるように、トランスコンダクタはnMOS差動対(トランジスタ642, 643および646, 647)を用いて構成され、差動(相補)の入力信号Vin+, Vin-で駆動されるトランスコンダクタ(トランジスタ642, 643)と、差動のレプリカ電圧(レプリカドライバの出力)Vreplica+, Vreplica-で駆動されるトランスコンダクタ(トランジスタ646, 647)の電流を1組のpMOS負荷641, 645に接続することで、両者の電流を差し引きして、ハイブリッド回路の動作を行うようになっている。なお、電圧VcpはpMOSトランジスタ641および645をバイアスするための電圧であり、また、電圧VcnはnMOSトランジスタ644および648をバイアスするための電圧である。30

#### 【0039】

このように、本第6実施例では、容量の充放電を行う必要が一切ないのでキックバック・ノイズは非常に小さくなるという利点がある。

図10は本発明の第7実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図である。

本第7実施例は、上述した第6実施例と同様に、ハイブリッド回路(バッファ回路)604としてトランスコンダクタを使用するものであるが、入力オフセットを補償するために負荷デバイスと並列にオフセット補償回路605を設けるようになっている。40

#### 【0040】

図10に示されるように、オフセット補償回路605は、スイッチ651, 654、nMOSトランジスタ652, 655、および、ホールド容量653, 656を備えて構成されている。

ここで、バッファ回路の非動作時には、例えば、全ての入力(Vin+, Vin-; Vreplica+, Vreplica-)を基準電圧(例えば、高電位の電源電圧Vdd)として、そのときのバッファ回路604の出力電流(オフセットに相当)をオフセット補償回路605に流す。このとき、スイッチ651および654はオン状態とされ、トランジスタ652および655のゲート電圧(ソース-ゲート間電圧)は、ホールド容量653および656に蓄積される50

。

#### 【0041】

そして、実際に判定回路5で受信信号の判定を行う場合には、スイッチ651および654をオフ状態とし、トランジスタ652および655のゲートとドレインの接続を切り離す。すると、各トランジスタ652, 655のゲート電圧は、それぞれホールド容量653, 656から供給され、オフセット補償回路605による電流はバッファ回路の非動作時のオフセット電流に等しいことになる。その結果、オフセット電流が負荷デバイスから差し引かれることになり、トランスコンダクタのオフセットを補償することができる。

#### 【0042】

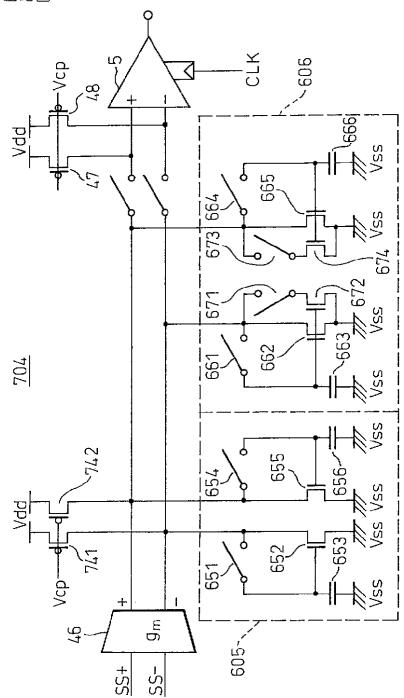

本第7実施例では、入力側に対するキックバック・ノイズの影響を受けることなく、バッファ回路のオフセットを補償することができるため、より正確な信号受信が可能になる。図11は本発明の第8実施例としての双方向信号伝送用ハイブリッド回路を示す回路図である。

#### 【0043】

図11に示されるように、本第8実施例において、トランスコンダクタ46の出力電流は、いわゆるカスコード接続となってpMOS負荷デバイス741, 742に導かれ、フォールデッド構造によりnMOS素子を用いたホールド回路606に接続される。なお、オフセット補償回路605は、図10の第7実施例と同様のものであるので、その説明は省略する。

#### 【0044】

ホールド回路606は、オフセット補償回路605と同様なスイッチ661, 664、トランジスタ662, 665および容量663, 666を備えている。さらに、ホールド回路606は、トランジスタ662のソース-ドレイン間に接続されたスイッチ671およびトランジスタ672、並びに、トランジスタ666のソース-ドレイン間に接続されたスイッチ673およびトランジスタ674を備えている。

#### 【0045】

まず、サンプリング期間において、ホールド回路606の全てのスイッチ661, 664; 671, 673をオン状態とし、サンプリングを終了するタイミングで全てのスイッチ661, 664; 671, 673をオフ状態とする。これにより、前のビットタイム $t = (n - 1)T$ のサンプリング終了時点における電流値が容量663, 666に蓄積される。なお、このサンプリング終了時点における電流値は、pMOS負荷デバイス(トランジスタ741, 742)に接続され、判定期間において、判定回路5で判定される信号電圧を作りだすことになる。

#### 【0046】

そして、ホールド回路606の全てのスイッチ661, 664; 671, 673をオフ状態として、次のビットタイム $t = nT$ の信号値から、前のビットタイム $t = (n - 1)T$ の信号値 $((n - 1)T)$ の係数倍を差し引いてイコライズを行う。すなわち、ホールド回路606において、トランジスタ662, 665のサイズとトランジスタ672, 674のサイズを調整することで、上記の係数の値を規定して受信信号のイコライズを行うことができる。

#### 【0047】

このように、本第8実施例は、キックバック・ノイズの影響の小さなトランスコンダクタ方式のバッファ回路を用いてオフセット補償および受信信号のイコライズを行うことができ、オフセットおよび符号間干渉が小さく良好な信号受信が可能になる。

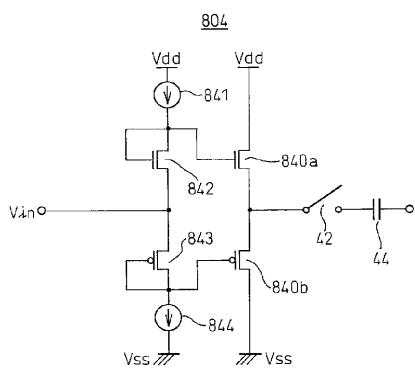

図12は本発明の第9実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図である。図12において、参照符号841, 844は電流源、842, 840aはnMOSトランジスタ、そして、843および840bはpMOSトランジスタを示している。

#### 【0048】

本第9実施例では、バッファ回路がnMOSトランジスタ840aおよびpMOSトラン

10

20

30

40

50

ジスタ 840b のプッシュプル出力になっている。ところで、一般に、プッシュプルのソースフォロワ出力段は、出力振幅が制限されるため使われることが少ないが、本実施例のように入力段で使用する場合には何の問題もない。

このように、本第 9 実施例は、プッシュプルであるため、通常のソースフォロワのように定電流バイアスによる充放電のスルーレートの制限が発生せず高速で動作する利点がある。

#### 【 0049 】

このように、本発明の各実施例によれば、信号伝送路の帯域を有効に利用することが可能な双方向伝送に用いるハイブリッド回路をキックバック・ノイズを伴わずに実現することができる。

(付記 1) 信号を信号伝送路の双方向に送受信する双方向信号伝送用のレシーバであつて、

前記信号伝送路に接続された信号線と、信号を保持する第 1 のホールド容量と、該信号線の電圧をバッファする信号線電圧バッファ回路と、該バッファ回路でバッファされた信号線電圧から受信信号を分離出力するハイブリッド回路と、該ハイブリッド回路から分離出力された受信信号の論理値を判定する判定回路とを備える双方向信号伝送用レシーバ。

(付記 2) 付記 1 に記載のレシーバにおいて、前記判定回路は、前記ハイブリッド回路から分離出力された受信信号の論理値を判定する時点の信号値と、それより一定時間前の信号値に係数を乗じた値との和を生成し、該生成された和の値を用いて判定を行うことを特徴とするレシーバ。

(付記 3) 付記 1 に記載のレシーバにおいて、前記バッファ回路は電圧バッファ回路であり、前記ハイブリッド回路は容量結合ハイブリッド回路であることを特徴とするレシーバ。

(付記 4) 付記 3 に記載のレシーバにおいて、前記電圧バッファ回路の電圧ゲインを約 1 とし、該電圧バッファ回路と前記信号線との間を容量で結合し、該電圧バッファ回路の非動作期間には該容量の入力側ノードを当該電圧バッファ回路の出力に繋ぎ、且つ、該電圧バッファ回路の入力ノードを所定電位にプリチャージすることで当該電圧バッファ回路のオフセット電圧を補償することを特徴とするレシーバ。

(付記 5) 付記 3 に記載のレシーバにおいて、さらに、前記容量結合ハイブリッド回路の入力ノードを駆動する基準電圧をドライバの出力シーケンスに応じて制御する基準電圧出力回路を備えたことを特徴とするレシーバ。

(付記 6) 付記 5 に記載のレシーバにおいて、前記基準電圧出力回路は、前記ドライバが送っている信号系列のデータに応じた複数の制御電圧を発生する制御電圧発生回路と、該各制御電圧を受け取ってそれぞれ基準電圧を発生する複数の基準電圧用バッファと、該信号系列のデータに応じて該複数の基準電圧用バッファの出力のいずれかを選択する選択回路とを備えることを特徴とするレシーバ。

(付記 7) 付記 1 に記載のレシーバにおいて、

前記バッファ回路は、電圧 - 電流変換を行うトランスコンダクタであり、

前記ハイブリッド回路は、前記信号線の電圧およびレプリカドライバの信号電圧をそれぞれトランスコンダクタで電圧 - 電流変換し、該各変換された電流の差に相当する電流を負荷デバイスに流すことで該信号線の電圧と該レプリカドライバの信号電圧との差を求め、前記受信信号を分離出力することを特徴とするレシーバ。

(付記 8) 付記 7 に記載のレシーバにおいて、

前記ハイブリッド回路における前記トランスコンダクタの電流を印加する負荷デバイスに対して、さらに、第 1 のトランジスタおよび第 2 のホールド容量を有するオフセット補償回路を接続し、

該オフセット補償回路において、前記バッファ回路の非動作時には、前記第 1 のトランジスタがダイオード接続構造となるように接続されると共に当該第 1 のトランジスタのゲートに前記第 2 のホールド容量が接続され、該バッファ回路の動作時には、該第 2 のホールド容量の電圧が該第 1 トランジスタのゲート電圧を保持することを特徴とするレシーバ。

10

20

30

40

50

(付記 9) 付記 8 に記載のレシーバにおいて、前記トランスコンダクタの電流を、フォールデッド構成による第 3 のホールド容量および第 2 のトランジスタを有するホールド回路で保持し、該ホールド回路の第 3 のホールド容量はサンプリング時にはダイオード接続された該第 2 のトランジスタのゲートと接続されると共にホールド時にはゲートから切り離され、該ホールド回路の出力電流を次段の負荷デバイスに接続することで前後するサンプル時間の間での信号の重み付き和を形成した後に判定を行うことを特徴とするレシーバ。

(付記 10) 付記 1 に記載のレシーバにおいて、前記バッファ回路は、nMOS デバイスおよび pMOS デバイスの双方を用いたブッシュブルのソースフォロワ段を出力に持つことを特徴とするレシーバ。 10

(付記 11) 信号を信号伝送路の双方向に送受信する双方向信号伝送用のレシーバであって、

前記信号伝送路に接続された信号線と、信号を保持する第 1 のホールド容量と、該信号線の電圧から受信信号を分離出力するハイブリッド回路と、該ハイブリッド回路の入力ノードを駆動する基準電圧をドライバの出力シーケンスに応じて出力する基準電圧出力回路と、該ハイブリッド回路から分離出力された受信信号の論理値を判定する判定回路とを備えることを特徴とするレシーバ。

(付記 12) 付記 11 に記載のレシーバにおいて、前記基準電圧出力回路は、前記ドライバが送っている信号系列のデータに応じた複数の制御電圧を発生する制御電圧発生回路と、該各制御電圧を受け取ってそれぞれ基準電圧を発生する複数の基準電圧用バッファと、該信号系列のデータに応じて該複数の基準電圧用バッファの出力のいずれかを選択する選択回路とを備えることを特徴とするレシーバ。 20

(付記 13) 信号を信号伝送路の双方向に送受信する双方向信号伝送用のハイブリッド回路であって、

該ハイブリッド回路は信号を保持するホールド容量を備えた容量結合ハイブリッド回路であり、前記信号伝送路からの入力信号をバッファ回路を介して該ホールド容量に供給し、該バッファ回路でバッファされた信号線電圧から受信信号を分離出力することを特徴とするハイブリッド回路。

(付記 14) 付記 13 に記載のハイブリッド回路において、さらに、前記容量結合ハイブリッド回路の入力ノードを駆動する基準電圧をドライバの出力シーケンスに応じて制御する基準電圧出力回路を備えたことを特徴とするハイブリッド回路。 30

(付記 15) 付記 14 に記載のハイブリッド回路において、前記基準電圧出力回路は、前記ドライバが送っている信号系列のデータに応じた複数の制御電圧を発生する制御電圧発生回路と、該各制御電圧を受け取ってそれぞれ基準電圧を発生する複数の基準電圧用バッファと、該信号系列のデータに応じて該複数の基準電圧用バッファの出力のいずれかを選択する選択回路とを備えることを特徴とするハイブリッド回路。

(付記 16) 付記 13 に記載のハイブリッド回路において、該ハイブリッド回路は、信号を増幅して前記信号伝送路に供給するドライバの出力に相当する信号を出力するレプリカドライバの出力信号と、前記信号伝送路の入力信号と、基準電圧とを受け取って受信信号の分離出力をを行うことを特徴とするハイブリッド回路。 40

(付記 17) 付記 16 に記載のハイブリッド回路において、

前記ハイブリッド回路は、前記信号伝送路の電圧および前記レプリカドライバの出力電圧をそれぞれトランスコンダクタで電圧 - 電流変換し、該各変換された電流の差に相当する電流を負荷デバイスに流すことで該信号伝送路の電圧と該レプリカドライバの出力電圧との差を求め、前記受信信号の分離出力をを行うことを特徴とするハイブリッド回路。

(付記 18) 付記 17 に記載のハイブリッド回路において、

前記ハイブリッド回路における前記トランスコンダクタの電流を印加する負荷デバイスに対して、さらに、第 1 のトランジスタおよび第 1 のホールド容量を有するオフセット補償回路を接続し、

該オフセット補償回路において、前記バッファ回路の非動作時には、前記第 1 のトランジ 50

スタがダイオード接続構造となるように接続されると共に当該第1のトランジスタのゲートに前記第1のホールド容量が接続され、該バッファ回路の動作時には、該第1のホールド容量の電圧が該第1トランジスタのゲート電圧を保持することを特徴とするハイブリッド回路。

(付記19) 付記18に記載のハイブリッド回路において、前記トランスコンダクタの電流を、フォールデッド構成による第2のホールド容量および第2のトランジスタを有するホールド回路で保持し、該ホールド回路の第2のホールド容量はサンプリング時にはダイオード接続された該第2のトランジスタのゲートと接続されると共にホールド時にはゲートから切り離され、該ホールド回路の出力電流を次段の負荷デバイスに接続することで前後するサンプル時間の間での信号の重み付き和を形成した後に判定を行うことを特徴とするハイブリッド回路。 10

#### 【0050】

#### 【発明の効果】

以上、詳述したように、本発明によれば、容量結合ハイブリッド回路の持つ入力へのキックバック・ノイズの問題を解消した双方向信号伝送用レシーバおよびハイブリッド回路を提供することができる。

#### 【図面の簡単な説明】

【図1】双方向信号伝送システムの一例を概略的に示す図である。

【図2】従来の双方向信号伝送用ハイブリッド回路の一例を説明するための図である。

【図3】本発明に係る双方向信号伝送用ハイブリッド回路の原理構成を示す回路図である。 20

【図4】本発明の第1実施例としての双方向信号伝送用ハイブリッド回路を示す回路図である。

【図5】本発明の第2実施例としての双方向信号伝送用ハイブリッド回路を示す回路図である。

【図6】本発明の第3実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図である。

【図7】本発明の第4実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図である。

【図8】本発明の第5実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図である。 30

【図9】本発明の第6実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図である。

【図10】本発明の第7実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図である。

【図11】本発明の第8実施例としての双方向信号伝送用ハイブリッド回路を示す回路図である。

【図12】本発明の第9実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図である。

#### 【符号の説明】

4, 104, 604, 704...ハイブリッド回路

5, 15, 105...判定回路

40, 400, 804...バッファ回路

14, 24...ソースフォロワ回路(電圧バッファ回路)

30...基準電圧出力回路

41~43, 411, 412; 421, 422; 431, 432...スイッチ

44, 441, 442; 451, 452...容量(ホールド容量)

45, 46...トランスコンダクタ

100...レシーバ

101...双方向信号伝送路

40

50

102 ... ドライバ

103 ... レプリカドライバ

300 ... 制御電圧発生回路

605 ... オフセット補償回路

606 ... ホールド回路

SS, SS+, SS- ... ハイブリッド回路の出力 ( 分離出力された受信信号 )

V<sub>in</sub>; V<sub>in+</sub>, V<sub>in-</sub> ... 信号線電圧 ( 入力信号 )

V<sub>ref</sub>; V<sub>ref+</sub>, V<sub>ref-</sub> ... 基準電圧

V<sub>replica</sub>; V<sub>replica+</sub>, V<sub>replica-</sub> ... レプリカドライバの出力電圧 ( レプリカ電圧 )

【図1】

図1 双方向信号伝送システムの一例を概略的に示す図

【図2】

図2 従来の双方向信号伝送用ハイブリッド回路の一例を説明するための図

【図3】

図3

本発明に係る双方向信号伝送用ハイブリッド回路の原理構成を示す回路図

【図4】

図4

本発明の第1実施例としての双方向信号伝送用ハイブリッド回路を示す回路図

【図5】

図5

本発明の第2実施例としての双方向信号伝送用ハイブリッド回路を示す回路図

【図6】

図6

本発明の第3実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図

【図7】

図 7

本発明の第4実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図

〔 四 8 〕

本発明の第5実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図

【図9】

図 9

本発明の第6実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図

【図10】

図10

本発明の第7実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図

【図 1 1】

図 11

本発明の第 8 実施例としての双方向信号伝送用ハイブリッド回路を示す回路図

【図 1 2】

図 12

本発明の第 9 実施例としての双方向信号伝送用ハイブリッド回路におけるバッファ回路を示す回路図

---

フロントページの続き

(72)発明者 田村 泰孝

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 高橋 祐治

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

審査官 小曳 満昭

(56)参考文献 特開昭53-073019(JP,A)

特開2000-196680(JP,A)

特開2001-103097(JP,A)

特開昭51-117503(JP,A)

特開昭56-058345(JP,A)

特開昭56-098052(JP,A)

特開昭58-017744(JP,A)

特開昭58-115957(JP,A)

特開平05-122201(JP,A)

特開2001-027919(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04B 1/38- 1/58、 1/76- 3/44、

3/50- 3/60、 7/005- 7/015、

H04L 5/14- 5/18、 25/00-25/66