(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6093409号

(P6093409)

(45) 発行日 平成29年3月8日(2017.3.8)

(24) 登録日 平成29年2月17日(2017.2.17)

(51) Int.Cl.

F 1

|              |           |      |       |      |

|--------------|-----------|------|-------|------|

| HO1L 21/336  | (2006.01) | HO1L | 29/78 | 619A |

| HO1L 29/786  | (2006.01) | HO1L | 27/08 | 102A |

| HO1L 21/8234 | (2006.01) | HO1L | 29/78 | 618B |

| HO1L 27/088  | (2006.01) | HO1L | 29/78 | 616V |

| HO1L 27/08   | (2006.01) | HO1L | 29/78 | 616U |

請求項の数 4 (全 47 頁) 最終頁に続く

(21) 出願番号 特願2015-148440 (P2015-148440)

(22) 出願日 平成27年7月28日 (2015.7.28)

(62) 分割の表示 特願2014-145936 (P2014-145936)

原出願日 平成21年10月27日 (2009.10.27)

(65) 公開番号 特開2016-1745 (P2016-1745A)

(43) 公開日 平成28年1月7日 (2016.1.7)

審査請求日 平成27年8月21日 (2015.8.21)

(31) 優先権主張番号 特願2008-281449 (P2008-281449)

(32) 優先日 平成20年10月31日 (2008.10.31)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 岩本 勉

最終頁に続く

(54) 【発明の名称】 駆動回路

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のエンハンスマント型トランジスタと第2のエンハンスマント型トランジスタを含むインバータ回路を有し、

前記第1のエンハンスマント型トランジスタの第1の酸化物半導体膜と前記第2のエンハンスマント型トランジスタの第2の酸化物半導体膜とに接して上方に膜中にOH基を含む酸化珪素膜を有し、

前記酸化珪素膜に接して上方に窒化珪素膜を有し、

前記第1のエンハンスマント型トランジスタと前記第2のエンハンスマント型トランジスタはそれぞれボトムゲート型トランジスタであり、

前記第1の酸化物半導体膜は、前記第1のエンハンスマント型トランジスタのチャネル形成領域を有し、

前記第2の酸化物半導体膜は、前記第2のエンハンスマント型トランジスタのチャネル形成領域を有することを特徴とする駆動回路。

## 【請求項 2】

請求項1において、

前記第1のエンハンスマント型トランジスタのゲート端子及び第1の端子は、高電源電位を供給する配線に接続され、

前記第2のエンハンスマント型トランジスタのゲート端子は、入力信号が供給され、

前記第2のエンハンスマント型トランジスタの第1の端子は、前記第1のエンハンスマント型トランジスタの第2の端子と接続され、

10

20

ント型トランジスタの第2の端子に電気的に接続され、

前記第2のエンハンスメント型トランジスタの第2の端子は、低電源電位を供給する配線に接続されていることを特徴とする駆動回路。

**【請求項3】**

請求項2において、

前記高電源電位を供給する配線と前記第1の酸化物半導体膜との間に第3の酸化物半導体膜を有し、

前記低電源電位を供給する配線と前記第2の酸化物半導体膜との間に第4の酸化物半導体膜を有することを特徴とする駆動回路。

**【請求項4】**

10

請求項1乃至3のいずれか一において、

前記第1の酸化物半導体膜および前記第2の酸化物半導体膜は、インジウム、ガリウム及び亜鉛を含むことを特徴とする駆動回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、酸化物半導体を用いる駆動回路及びその作製方法、当該駆動回路を具備する表示装置、及び当該表示装置を具備する電子機器に関する。

**【背景技術】**

**【0002】**

20

液晶表示装置に代表されるように、ガラス基板等の平板に形成される薄膜トランジスタは、アモルファスシリコン、多結晶シリコンによって作製されている。アモルファスシリコンを用いた薄膜トランジスタは、電界効果移動度が低いもののガラス基板の大面積化に対応することができ、一方、多結晶シリコンを用いた薄膜トランジスタは電界効果移動度が高いものの、レーザアニール等の結晶化工程が必要であり、ガラス基板の大面積化には必ずしも適応しないといった特性を有している。

**【0003】**

これに対し、酸化物半導体を用いて薄膜トランジスタを作製し、電子デバイスや光デバイスに応用する技術が注目されている。例えば、酸化物半導体として酸化亜鉛、In-Ga-Zn-O系酸化物半導体を用いて薄膜トランジスタを作製し、画像表示装置のスイッチング素子などに用いる技術が特許文献1及び特許文献2で開示されている。

30

**【先行技術文献】**

**【特許文献】**

**【0004】**

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

酸化物半導体にチャネル形成領域を設ける薄膜トランジスタは、アモルファスシリコンを用いた薄膜トランジスタよりも高い電界効果移動度が得られている。酸化物半導体膜はスパッタ法などによって300℃以下の温度で膜形成が可能であり、酸化物半導体を用いた薄膜トランジスタは、多結晶シリコンを用いた薄膜トランジスタよりも製造工程が簡単である。

40

**【0006】**

このような酸化物半導体を用いてガラス基板上、プラスチック基板上等に薄膜トランジスタを形成し、液晶ディスプレイ、エレクトロルミネセンスディスプレイ又は電子ペーパー等への応用が期待されている。

**【0007】**

表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及びソース線数が増加する。

50

ゲート線数、及びソース線数が増加すると、それらを駆動するための駆動回路を有するICチップをポンディング等により実装することが困難となり、製造コストが増大するという問題がある。そのため駆動回路は、ガラス基板上、プラスチック基板上等に単極性の薄膜トランジスタで形成することが好ましい。しかしながら、アモルファスシリコンを用いて構成された単極性の駆動回路では、薄膜トランジスタの劣化に伴うしきい値電圧のシフトの問題がある。また、ポリシリコンを用いて構成された単極性の駆動回路では、しきい値電圧のばらつきが顕著になってしまう問題がある。そのため、アモルファスシリコンを用いた単極性の駆動回路及びポリシリコンを用いた単極性の駆動回路では、しきい値電圧のシフトまたはしきい値電圧のばらつきの補正回路を構築することにより、回路が占める面積が増大してしまう。

10

#### 【0008】

一方、酸化物半導体を用いた薄膜トランジスタによって単極性の駆動回路を構成する場合、アモルファスシリコン及びポリシリコンを用いた薄膜トランジスタほど、しきい値電圧のシフトまたはしきい値電圧のばらつきの問題は顕著ではないものの、酸化物半導体が経時に劣化することによる、しきい値電圧のばらつきの問題は残る。こういった諸問題を解決することは、表示装置での映像の質を高めること、または駆動回路の動作の安定性の向上させることにも重要である。また一方で酸化物半導体を用いた薄膜トランジスタでは、消費電力を低減するために、薄膜トランジスタをオフにした際に流れる電流を小さくすることが望まれる。

20

#### 【0009】

そこで本発明の一態様は、酸化物半導体にチャネル形成領域を設ける薄膜トランジスタで構成された駆動回路を有する表示装置において、回路が占める面積を大きくすることなく、酸化物半導体が経時に劣化することによる薄膜トランジスタのしきい値電圧のシフトを低減し、且つ薄膜トランジスタをオフにした際にソースとドレインの間を流れる電流（以下、オフ電流ともいう）を低減することを課題の一とする。

#### 【課題を解決するための手段】

#### 【0010】

本発明の一態様としては、複数のインバータ回路及び複数のスイッチを有し、前記インバータ回路は、第1の酸化物半導体膜を有し、ゲート端子及び第1端子が高電源電位を供給する配線に接続された第1の薄膜トランジスタと、第2の酸化物半導体膜を有し、前記第1の薄膜トランジスタの第2端子が第1端子に接続され、第2端子が低電源電位を供給する配線に接続され、ゲート端子に入力信号が供給される第2のトランジスタと、を有し、前記第1の薄膜トランジスタ及び前記第2の薄膜トランジスタは、エンハンスマント型であり、前記第1の酸化物半導体膜及び前記第2の酸化物半導体膜上に接してOH基を有する酸化珪素膜が設けられ、前記酸化珪素膜上に接して窒化珪素膜が設けられている表示装置の駆動回路である。

30

#### 【発明の効果】

#### 【0011】

本発明の一態様により、回路が占める面積を大きくすることなく、薄膜トランジスタのしきい値電圧のシフトを低減し、且つオフ電流を低減することができる。

40

#### 【図面の簡単な説明】

#### 【0012】

- 【図1】実施の形態1について説明する図。

- 【図2】実施の形態1について説明する図。

- 【図3】実施の形態1について説明する図。

- 【図4】実施の形態1について説明する図。

- 【図5】実施の形態1について説明する図。

- 【図6】実施の形態1について説明する図。

- 【図7】実施の形態1について説明する図。

- 【図8】実施の形態1について説明する図。

50

- 【図9】実施の形態1について説明する図。

- 【図10】実施の形態1について説明する図。

- 【図11】実施の形態1について説明する図。

- 【図12】実施の形態1について説明する図。

- 【図13】実施の形態1について説明する図。

- 【図14】実施の形態2について説明する図。

- 【図15】実施の形態2について説明する図。

- 【図16】実施の形態3について説明する図。

- 【図17】実施の形態3について説明する図。

- 【図18】実施の形態3について説明する図。

- 【図19】実施の形態3について説明する図。

- 【図20】実施の形態3について説明する図。

- 【図21】実施の形態3について説明する図。

- 【図22】実施の形態3について説明する図。

- 【図23】実施の形態3について説明する図。

- 【図24】実施の形態4について説明する図。

- 【図25】実施の形態4について説明する図。

- 【図26】実施の形態4について説明する図。

- 【図27】実施の形態6について説明する図。

- 【図28】実施の形態6について説明する図。

- 【図29】実施の形態5について説明する図。

10

**【発明を実施するための形態】**

**【0013】**

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

20

**【0014】**

30

**(実施の形態1)**

本実施の形態では、単極性の駆動回路を構成する酸化物半導体で構成した薄膜トランジスタとして、nチャネル型の薄膜トランジスタを用いる。そして画素部を駆動するための駆動回路として、ソース線駆動回路、及びノーマルゲート線駆動回路について一例を挙げて説明し、本発明の一形態の利点について述べていくこととする。

**【0015】**

40

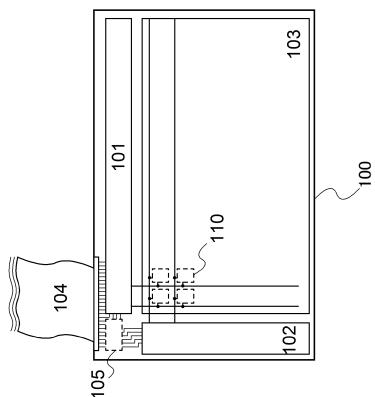

まず図1には、表示装置の全体概略図について示している。基板100上に、ソース線駆動回路101、ゲート線駆動回路102、および画素部103を一体形成している。画素部103において、点線枠110で囲まれた部分が1画素である。図1の例で、ゲート線駆動回路102は、一方の端部に設けられる構成について示したが、複数有する構成としてもよい。また、表示装置の画素では、薄膜トランジスタ(以下、TFTと表記する)によって表示素子の制御を行っている。ソース線駆動回路101、ゲート線駆動回路102を駆動する信号(クロック信号、スタートパルス等)は、フレキシブルプリント基板(Flexible Print Circuit: FPC)104を介して、外部より入力される。なお基板上にロジック回路、電源回路及び発振回路等の回路105を設け、駆動回路を制御するための信号を基板上で生成し、ソース線駆動回路101、ゲート線駆動回路102に供給する構成としてもよい。

**【0016】**

画素部を駆動するためのソース線駆動回路101、ゲート線駆動回路102は、インバータ回路、容量素子、TFT等の素子を用いたスイッチ、抵抗素子などを用いて構成する。

50

単極性の TFT を備えた駆動回路として、2つの n チャネル型 TFT を組み合わせてインバータ回路を形成する場合、エンハンスマント型トランジスタとデプレッション型トランジスタとを組み合わせて形成する場合（以下、E DMOS 回路という）と、エンハンスマント型トランジスタ同士で形成する場合（以下、E EMOS 回路という）と、エンハンスマント型トランジスタと抵抗素子とを組み合わせて形成する場合（以下、E RMOS 回路という）がある。一方、駆動回路と同じ基板上に形成される画素部に設ける薄膜トランジスタとして、エンハンスマント型トランジスタを用いることが好適である。エンハンスマント型トランジスタはしきい値電圧が正であるため、ゲートとソースの間にかかる電圧によって流れる電流を、デプレッション型トランジスタより小さくすることができ、低消費電力化を図ることができるからである。

10

#### 【 0017 】

そのため、画素部を駆動するための駆動回路のインバータ回路として、画素部と同じエンハンスマント型の TFT で構成される、E EMOS 回路を用いることが好適である。駆動回路に用いるインバータ回路として、E EMOS 回路を用いることにより、画素部及び駆動回路を作製する際のトランジスタの種類を一種類とするため、作製工程の短縮化を図ることができる。なお本実施の形態で説明するエンハンスマント型トランジスタは、酸化物半導体を用いており、その電気特性は、ゲート電圧  $\pm 20\text{ V}$  において、オンオフ比が  $10^9$  以上であるため、ソースとドレイン間をリークする電流が少なく、低消費電力駆動を実現することができる。

20

#### 【 0018 】

なお、n チャネル型 TFT のしきい値電圧が正の場合は、エンハンスマント型トランジスタと定義し、n チャネル型 TFT のしきい値電圧が負の場合は、デプレッション型トランジスタと定義し、本明細書を通してこの定義に従うものとする。

#### 【 0019 】

なお、本明細書中で用いる酸化物半導体は、 $\text{InMO}_3 (\text{ZnO})_m$  ( $m > 0$ ) で表記される薄膜を形成し、その薄膜を半導体層として用いた薄膜トランジスタを作製する。なお、M は、ガリウム (Ga)、鉄 (Fe)、ニッケル (Ni)、マンガン (Mn) 及びコバルト (Co) から選ばれた一の金属元素又は複数の金属元素を示す。例えば M として、Ga の場合の他、Ga と Ni 又は Ga と Fe など、Ga と上記金属元素が含まれる場合がある。また、上記酸化物半導体において、M として含まれる金属元素の他に、不純物元素として Fe、Ni その他の遷移金属元素、又は該遷移金属の酸化物が含まれているものがある。本明細書においてはこの薄膜を In - Ga - Zn - O 系非単結晶膜とも呼ぶ。

30

#### 【 0020 】

In - Ga - Zn - O 系非単結晶膜の結晶構造は、スパッタ法で成膜した後、200 ~ 500 、代表的には 300 ~ 400 で 10 分 ~ 100 分熱処理を行っても、アモルファス構造が XRD (X 線回折) の分析で観察することができる。また、TFT の電気特性もゲート電圧  $\pm 20\text{ V}$  において、オンオフ比が  $10^9$  以上、移動度が 10 以上のものを作製することができる。このような電気特性を有する酸化物半導体膜を用いて作製した薄膜トランジスタは、アモルファスシリコンを用いて作製した薄膜トランジスタに比べ高い移動度を有し、当該薄膜トランジスタを具備するシフトレジスタで構成される駆動回路を高速駆動させることができる。

40

#### 【 0021 】

なお本明細書において、A と B とが接続されている、とは、A と B とが直接接続されているものの他、電気的に接続されているものを含むものとする。ここで、A と B とが電気的に接続されているとは、A と B との間に何らかの電気的作用を有する対象物が存在するとき、対象物を介して A と B とが概略同一ノードとなる場合を表すものとする。

#### 【 0022 】

具体的には、A と B とが接続されている、とは、トランジスタのようなスイッチング素子を介して A と B とが接続され、該スイッチング素子の導通によって、A と B とが概略同電位となる場合や、抵抗素子を介して A と B とが接続され、該抵抗素子の両端に発生する電

50

位差が、AとBとを含む回路の動作に影響しない程度となっている場合など、回路動作を考えた場合、AとBとが同一ノードとして捉えて差し支えない状態である場合を表す。

【0023】

なお、表示装置とは、発光素子または液晶素子等の表示素子を有する装置のことを言う。なお、表示装置は、複数の画素を駆動させる周辺駆動回路を含んでいても良い。なお、複数の画素を駆動させる周辺駆動回路は、複数の画素と同一基板上に形成される。なお、表示装置は、フレキシブルプリント基板（FPC）を含んでもよい。なお、表示装置は、フレキシブルプリント基板（FPC）などを介して接続され、ICチップ、抵抗素子、容量素子、インダクタ、トランジスタなどが取り付けられたプリント配線基板（PWB）を含んでいても良い。なお、表示装置は、偏光板または位相差板などの光学シートを含んでいても良い。なお、表示装置は、照明装置、筐体、音声入出力装置、光センサなどを含んでいても良い。

10

【0024】

なお、一画素とは、明るさを制御できる要素一つ分を示すものとする。よって、一例としては、一画素とは、一つの色要素を示すものとし、その色要素一つで明るさを表現する。従って、そのときは、RGBの色要素からなるカラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素との三画素から構成されるものとする。

【0025】

なお本明細書にて用いる第1、第2、第3、乃至第N（Nは自然数）という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

20

【0026】

次にインバータ回路としてEMOS回路を用いたゲート線駆動回路、及びソース線駆動回路の回路図、並びに上面図と断面図について一例を示し、説明する。

【0027】

次に、インバータ回路としてEMOS回路を用いたソース線駆動回路の構成について説明を行う。

【0028】

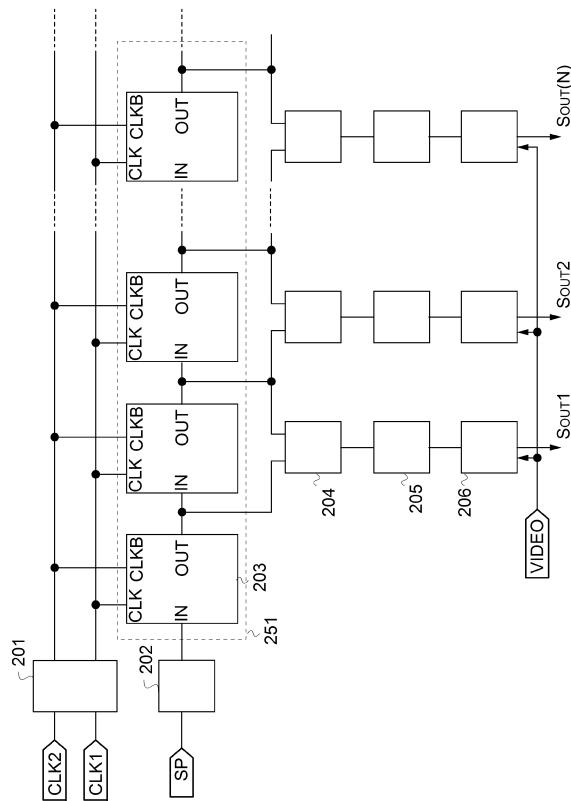

図2は、図1に示した表示装置における、ソース線駆動回路101の構成を示した図である。ソース線駆動回路は、クロック信号用レベルシフタ201、スタートパルス用レベルシフタ202、シフトレジスタ251を構成するパルス出力回路203、NAND回路204、バッファ205、サンプリングスイッチ206を有しており、外部より入力される信号は、第1のクロック信号（CLK1）、第2のクロック信号（CLK2）、スタートパルス（SP）、アナログ映像信号（Video）である。この中で、第1のクロック信号（CLK1）、第2のクロック信号（CLK2）、およびスタートパルス（SP、または入力信号ともいう）に関しては、外部から駆動回路に低電圧振幅の信号として入力された直後、クロック信号用レベルシフタ201又はスタートパルス用レベルシフタ202によって振幅変換を受け、高電圧振幅の信号となる。また、本実施の形態の表示装置におけるソース線駆動回路は、一例として、シフトレジスタ中の1段のパルス出力回路より出力されるサンプリングパルスが、サンプリングスイッチ206を駆動することによって、ソース線Sout1乃至Sout（N）列分のアナログ映像信号を同時にサンプリングしているものを説明する。なお、他にも走査方向を切り替えるための走査方向切り替え信号等を入力する構成としても良い。また本実施の形態では、第1のクロック信号（CLK1）、第2のクロック信号（CLK2）の2相のクロック信号により駆動する例を示すが、2相以外のクロック信号の入力により駆動回路を駆動する構成としてもよい。

30

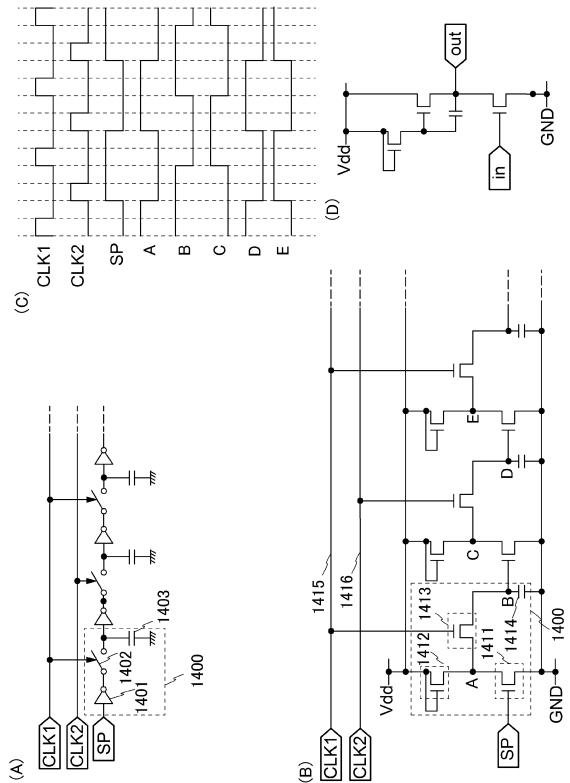

【0029】

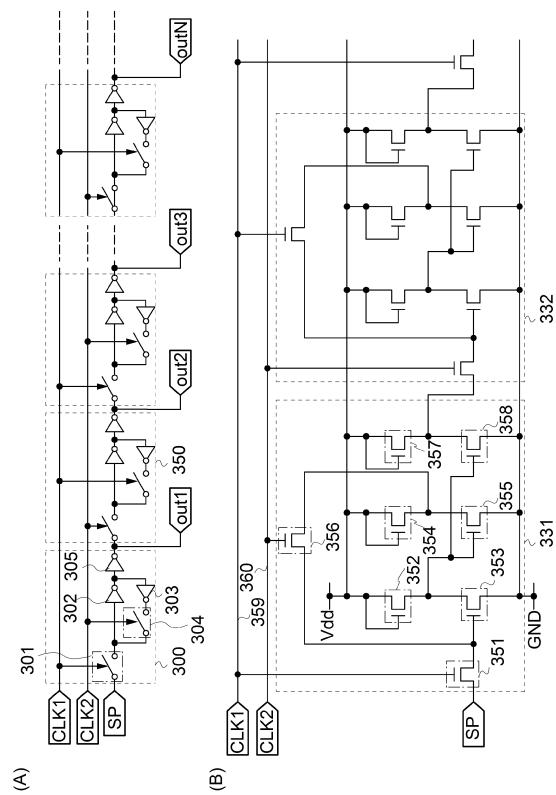

図3（A）、（B）に、図2で示したシフトレジスタ251が有するパルス出力回路203の構成を示す。なお本実施の形態では、スタティック回路のシフトレジスタについて一例を示し、説明するものである。パルス出力回路300は、一例として、スタートパルスSPが入力される端子に接続された第1のスイッチ301と、第1のスイッチ301を介

40

50

して入力される信号を反転して出力する第1のインバータ回路302と、第1のインバータ回路302で反転された信号を反転して出力する第2のインバータ回路303と、第2のインバータ回路303で反転された信号が入力される端子に接続された第2のスイッチ304及び第3のインバータ回路305と、で構成される。図3(A)に示した回路図において、点線350で示したブロックが1段分のサンプリングパルスを出力するパルス出力回路であり、図3(A)のシフトレジスタは、N段( $n$ は自然数、 $1 < N$ )のパルス出力回路によって構成されている。N段のパルス出力回路からは、それぞれの第3のインバータ回路305の出力端子より、出力信号out1乃至outNが出力される。なお、上記説明した1段目(奇数段目)の次段である2段目(偶数段目)のパルス出力回路では、第1のスイッチ301と第2のスイッチ304との間で、入力される第1のクロック信号と第2のクロック信号とを入力する配線が切り替わって接続される。以下3段目以降、交互に第1のクロック信号と第2のクロック信号とを入力する配線が、第1のスイッチ301と第2のスイッチ304との間に交互に切り替わって接続される。

10

### 【0030】

図3(B)は、パルス出力回路の回路構成を詳細に示したものである。パルス出力回路本体は、TFT351、TFT352、TFT353、TFT354、TFT355、TFT356、TFT357、TFT358を有する。また奇数段目のパルス出力回路331及び偶数段目のパルス出力回路332は、第1のクロック信号CLK1を供給するための配線359、及び第2のクロック信号CLK2を供給するための配線360に接続されている。一段目のパルス出力回路331において、TFT351の第1端子はスタートパルスSPが入力される端子に接続され、ゲート端子は配線359が接続され、第2端子はTFT353のゲート端子及びTFT356の第2端子に接続される。TFT352の第1端子及びゲート端子は高電源電位VDDが供給される配線に接続され、第2端子はTFT353の第1端子、TFT355のゲート端子、TFT358のゲート端子に接続される。TFT353の第2端子は低電源電位VSS(GNDともいう)が供給される配線に接続される。TFT354の第1端子及びゲート端子は高電源電位VDDが供給される配線に接続され、第2端子はTFT355の第1端子及びTFT356の第1端子に接続される。TFT355の第2端子は低電源電位VSSが供給される配線に接続される。TFT356のゲート端子は配線360に接続される。TFT357の第1端子及びゲート端子は高電源電位VDDが供給される配線に接続され、第2端子はTFT358の第1端子に接続される。なお、1段目のパルス出力回路331におけるTFT357の第2端子は、2段目のパルス出力回路332におけるTFT351の第1端子に接続される。同様に、パルス出力回路におけるTFTの第2端子には、順次次の段のパルス出力回路が接続される。

20

### 【0031】

図3(B)において、TFT352及びTFT353は、図3(A)で示した第1のインバータ回路302に相当し、EEMOS回路を構成する。また、TFT354及びTFT355は、図3(A)で示した第2のインバータ回路303に相当し、EEMOS回路を構成する。TFT351は、図3(A)で示した第1のスイッチ301に相当する。TFT356は、図3(A)で示した第2のスイッチ304に相当する。なおTFT351及びTFT356は、TFT352乃至TFT355と同様に、エンハンスマント型トランジスタで構成することが好ましい。スイッチとしてエンハンスマント型トランジスタを用いることにより、トランジスタのオフ電流を低減することができるため、低消費電力化が図れるとともに、作製プロセスを簡略することができる。

30

### 【0032】

なお、nチャネル型トランジスタまたはpチャネル型トランジスタのようなトランジスタは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル形成領域を有しており、ドレイン領域とチャネル形成領域とソース領域とを介して電流を流すことができる。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるために、いずれがソースまたはド

40

レインであるかを限定することが困難な場合もある。そこで、本実施の形態においては、ソース及びドレンとして機能する領域のそれぞれを、第1端子、第2端子と表記するものとする。またゲートとして機能する端子については、ゲート端子と表記するものとする。

【0033】

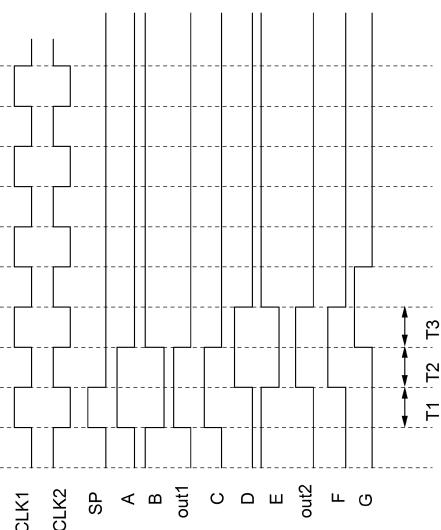

ここで、図3(A)、(B)で示した回路の回路動作について説明する。図4に示すタイミングチャートを参照する。なお図4では説明のため、図3(B)で示す回路でのノードとして1段目のパルス出力回路において、TFT351の第2端子をノードA(図4中、Aと示す)、TFT352の第2端子をノードB(図4中、Bと示す)、TFT354の第2端子をノードC(図4中、Cと示す)、TFT357の第2端子をノードout1(図4中、out1と示す)とする。また図3(B)で示す回路でのノードとして2段目のパルス出力回路において、TFT351の第2端子をノードD(図4中、Dと示す)、TFT352の第2端子をノードE(図4中、Eと示す)、TFT354の第2端子をノードF(図4中、Fと示す)、TFT357の第2端子をノードout2(図4中、out2と示す)とする。また図3(B)で示す回路でのノードとして3段目のパルス出力回路において、TFT351の第2端子をノードG(図4中、Gと示す)とする。

【0034】

図4中、期間T1で、スタートパルスSPがHレベル、第1のクロック信号CLK1がHレベル、第2のクロック信号がLレベルの際の動作について説明する。第1のクロック信号CLK1がHレベルになることで、1段目のパルス出力回路のTFT351がオン状態となる。そして、スタートパルスの電圧レベルであるHレベルが、ノードAの電圧レベルをHレベルに上昇させる。そして、ノードAの電圧レベルがHレベルに上昇することにより、1段目のパルス出力回路のTFT353がオン状態になる。そして、低電源電位の電圧レベルであるLレベルが、ノードBの電圧レベルをLレベルに下降させる。そして、ノードBの電圧レベルがLレベルに下降することにより、1段目のパルス出力回路のTFT355がオフ状態となる。そして、高電源電位の電圧レベルであるHレベルが、ノードCの電圧レベルをHレベルに上昇させる。また、ノードBの電圧レベルがLレベルに下降することにより、1段目のパルス出力回路のTFT358がオフ状態となる。そして、高電源電位の電圧レベルであるHレベルが、ノードout1の電圧レベルをHレベルに上昇させる。なお、第2のクロック信号CLK2は、Lレベルであるため、1段目のパルス出力回路のTFT356及び2段目のパルス出力回路のTFT351はオフ状態となる。

【0035】

次に図4中、期間T2で、スタートパルスSPがLレベル、第1のクロック信号CLK1がLレベル、第2のクロック信号がHレベルの際の動作について説明する。第1のクロック信号がLレベルになることで、1段目のパルス出力回路のTFT351がオフ状態となる。一方、第2のクロック信号CLK2は、Hレベルであるため、1段目のパルス出力回路のTFT356はオン状態となる。そのため、期間T1でHレベルにあったノードCの電圧レベルにより、ノードAの電圧レベルがHレベルを保持することとなる。そして、1段目のパルス出力回路では、期間T1と同じ動作を行うこととなる。期間T2では、第2のクロック信号CLK2がHレベルになることで、2段目のパルス出力回路のTFT351がオン状態となる。そして、ノードout1の電圧レベルであるHレベルが、ノードDの電圧レベルをHレベルに上昇させる。そして、ノードDの電圧レベルがHレベルに上昇することにより、2段目のパルス出力回路のTFT353がオン状態になる。そして、低電源電位の電圧レベルであるLレベルが、ノードEの電圧レベルをLレベルに下降させる。そして、ノードEの電圧レベルがLレベルに下降することにより、2段目のパルス出力回路のTFT355がオフ状態となる。そして、高電源電位の電圧レベルであるHレベルが、ノードFの電圧レベルをHレベルに上昇させる。また、ノードEの電圧レベルがLレベルに下降することにより、2段目のパルス出力回路のTFT358がオフ状態となる。そして、高電源電位の電圧レベルであるHレベルが、ノードout2の電圧レベルをHレベルに上昇させる。なお、第1のクロック信号CLK1は、Lレベルであるため、2段目

10

20

30

40

50

のパルス出力回路のTFT356及び3段目のパルス出力回路のTFT351はオフ状態となる。

【0036】

次に図4中、期間T3で、スタートパルスSPがLレベル、第1のクロック信号CLK1がHレベル、第2のクロック信号がLレベルの際の動作について説明する。第1のクロック信号がHレベルになることで、1段目のパルス出力回路のTFT351がオン状態となる。一方、第2のクロック信号CLK2は、Lレベルであるため、1段目のパルス出力回路のTFT356はオフ状態となる。そのため、ノードAの電圧レベルがLレベルに下降することとなる。そして、ノードAの電圧レベルがLレベルに下降することにより、1段目のパルス出力回路のTFT353がオフ状態になる。そして、高電源電位の電圧レベルであるHレベルが、ノードBの電圧レベルをHレベルに上昇させる。そして、ノードBの電圧レベルがHレベルに上昇することにより、1段目のパルス出力回路のTFT355がオン状態となる。そして、低電源電位の電圧レベルであるLレベルが、ノードCの電圧レベルをLレベルに下降させる。また、ノードBの電圧レベルがHレベルに上昇することにより、1段目のパルス出力回路のTFT358がオン状態となる。そして、低電源電位の電圧レベルであるLレベルが、ノードout1の電圧レベルをLレベルに下降させる。なお、第2のクロック信号CLK2は、Lレベルであるため、1段目のパルス出力回路のTFT356及び2段目のパルス出力回路のTFT351はオフ状態となる。また、期間T2での1段目のパルス出力回路と同様に、2段目のパルス出力回路のTFT356はオン状態となっており、期間T2でHレベルにあったノードFの電圧レベルにより、ノードFの電圧レベルがHレベルを保持することとなる。そして、2段目のパルス出力回路では、期間T2と同じ動作を行うこととなる。期間T3では、第1のクロック信号CLK1がHレベルになることで、3段目のパルス出力回路のTFT351がオン状態となる。そして、ノードout2の電圧レベルであるHレベルが、ノードGの電圧レベルをHレベルに上昇させる。そして、ノードGの電圧レベルがHレベルに上昇することにより、3段目のパルス出力回路のTFT353がオン状態になる。以下、順次トランジスタのオンまたはオフが制御されることにより、パルス出力回路を複数段組み合わせたシフトレジスタとして駆動することができる。

【0037】

なお、図3(A)、図3(B)、図4で説明したパルス出力回路において、ノードAとノードCとの間に第2のスイッチ304が設けられている構成について示している。これは、高電源電位VDDに接続されたTFT354により制御されるノードCの電圧レベルが(VDD - VthN)以下(VthNはTFT354のしきい値電圧)となるためである。第2のスイッチ304によって、ノードAとノードCとの接続を切り離して駆動することによって、ノードAの電位によるTFT353の駆動能力を高めることができるため好適である。なお、第2のスイッチ304を設けない構成としても、本実施の形態の発明をなし得ることができる。

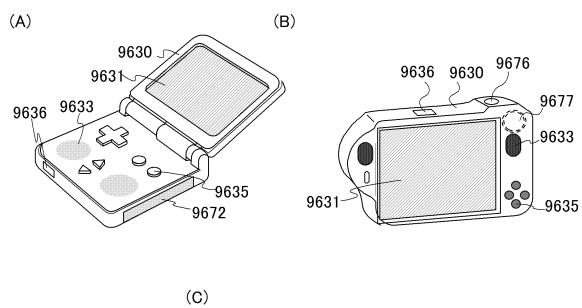

【0038】

また、ソース線駆動回路の構成では、各パルス出力回路から出力される信号の否定論理積(NAND)をとって、各ソース線を駆動するための信号を生成している。そのため、最終段のパルス出力回路においては、ソース線の数より多いパルス出力回路を設けておいて、ソース線に出力するための信号を生成する構成とすることが好ましい。

【0039】

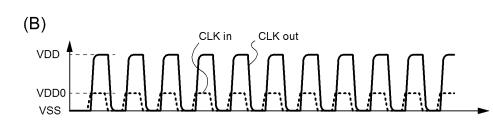

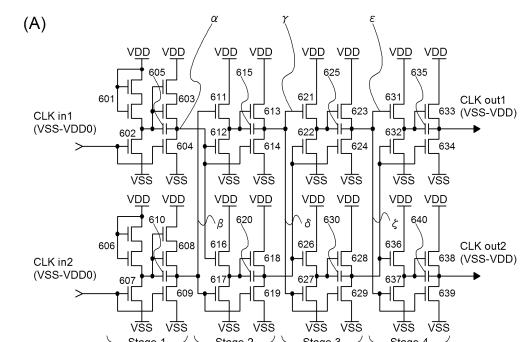

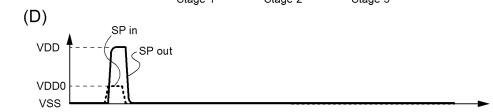

図5(A)は、図2で示したクロック信号用レベルシフタ201の構成を示している。これは、互いに逆の極性を有するクロック信号(CLK1とCLK2)を、1入力型のレベルシフタ回路を並列に配置してそれぞれ振幅変換を行い(Stage1)、以後のバッファ段(Stage2~Stage4)では、互いの出力をそれぞれの反転入力信号として用いる構成をとっている。

【0040】

図5(A)に示した回路の動作について説明する。なお、ここで用いている電源の電位

10

20

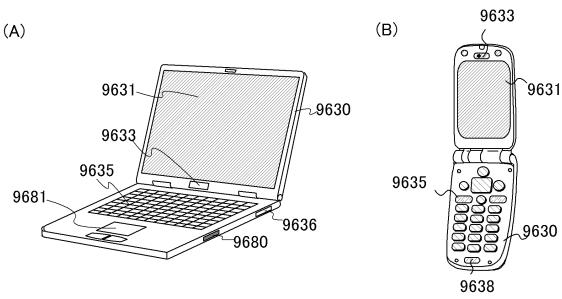

30

40

50

は、VSS、VDD0、VDDの3電位であり、VSS < VDD0 < VDDとする。クロック信号の振幅をソース線駆動回路入力部でレベルシフトすることで、低消費電力化及びノイズの減少を図ることができる。また、図5(A)において、TFT601、TFT603、TFT606、TFT608はダブルゲート構造をとっているが、これらはシングルゲートでも良いし、3つ以上のゲート電極を有するマルチゲート構造であっても良い。その他のTFTに関しても、ゲート電極の数による制限は特に設けない。

#### 【0041】

信号入力部(CLK\_in1)より、Lレベル/Hレベル = VSS / VDD0の振幅を有する第1の入力クロック信号(CLK\_in1)が入力される。第1の入力クロック信号がHレベルのとき、TFT602、604がオン状態になり、TFT603のゲート電極の電圧レベルがLレベルとなってオフ状態になる。ここで、TFT602のオン抵抗は、TFT601のそれよりも十分に低く設計しておく。よってノードは、Lレベルとなる。第1の入力クロック信号がLレベルのとき、TFT602、604はオフ状態になる。よって、飽和動作しているTFT601を通じて、TFT603のゲート端子の電圧レベルはVDDに上昇し、その電位が(VDD - VthN)となったところでTFT601はオフ状態になり、TFT603のゲート電極が浮遊状態となる。これによりTFT603がオン状態になり、ノードの電位はVDDに上昇する。ここで、容量605により、ノードの電位上昇に伴って、浮遊状態となっているTFT603のゲート端子の電位が上昇し、その電位はVDDよりも高い電位をとり、(VDD + VthN)を上回ることによって、ノードに現れるHレベルはVDDに等しくなる。よって、出力信号のLレベルはVSS、HレベルはVDDとなり、振幅変換が完了する。

#### 【0042】

一方、信号入力部(CLK\_in2)より、同じくVSS / VDD0の振幅を有する第2の入力クロック信号(CLK\_in2)が入力される。前述と同様の動作によって、TFT606乃至TFT609および容量610で構成された1入力型のレベルシフタ回路によって振幅変換が行われ、ノードにはVSS / VDDの振幅を有する信号が出力される。なお、ノードに現れた信号は、入力された第1の入力クロック信号に対して極性が反転しており、ノードに現れた信号は、入力された第2の入力クロック信号に対して極性が反転している。

#### 【0043】

図5(A)で説明するレベルシフタは、振幅変換後のパルスに対する負荷を考慮して、レベルシフタ回路(Stage1)の後に、バッファ段を設けている(Stage2 ~ Stage4)。このバッファ段を構成するインバータ回路は2入力型であり、入力信号およびその反転信号を要する。2入力型を用いる理由は、低消費電力化である。前述のレベルシフタ回路において、TFT602がオン状態であるとき、TFT601乃至TFT602を通じて、VSS - VDD間に貫通電流が流れる。2入力型を用いることによって、動作中に貫通電流が流れないようにしている。

#### 【0044】

図5(A)では、Stage2のインバータ回路において、TFT611のゲート端子に入力される信号と、TFT612のゲート端子に入力される信号は、互いに逆の極性を有する信号である。そこで、第1の入力クロック信号および第2の入力クロック信号が、互いに極性の反転した信号であることを利用し、ノードに現れた出力信号と、ノードに現れた出力信号とを、互いの信号の反転入力信号として用いている。

#### 【0045】

インバータ回路の動作について説明する。ここでは、Stage2の一方である、TFT611乃至614および容量615でなるインバータ回路における動作について述べる。

Stage2の他方であるTFT616乃至TFT619及び容量620でなるインバータ回路、Stage3のTFT621乃至TFT624及び容量625でなるインバータ回路、Stage3のTFT626乃至TFT629及び容量630でなるインバータ回

10

20

30

40

50

路、Stage 4 の TFT631 乃至 TFT634 及び容量 635 でなるインバータ回路、Stage 4 の TFT636 乃至 TFT639 及び容量 640 でなるインバータ回路などの、他のインバータ回路に関しても動作は同様である。

【0046】

TFT611 のゲート端子に入力される信号が H レベルのとき、TFT611 がオン状態となり、TFT613 のゲート電極の電位は VDD に上昇し、その電位が (VDD - VthN) となったところで TFT611 がオフ状態となり、TFT613 のゲート端子は浮遊状態となる。一方、TFT612、614 のゲート電極に入力される信号は L レベルであるから、TFT612、614 は OFF する。TFT613 のゲート電極の電位は、(VDD - VthN) まで上昇しているから、TFT613 はオン状態になり、ノードの電位が VDD に上昇する。ここで、前述のレベルシフタ回路の動作と同様、容量 615 の働きにより、ノード の電位上昇に伴って、浮遊状態となっている TFT613 のゲート電極の電位が引き上げられ、その電位は VDD よりも高い電位をとり、(VDD + VthN) を上回ることによって、ノード に現れる H レベルは VDD に等しくなる。

【0047】

一方、TFT611 のゲート端子に入力される信号が L レベルのとき、TFT611 がオフ状態になり、TFT612、614 のゲート端子には H レベルが入力されてオン状態になる。したがって、TFT613 のゲート電極の電位は L レベルとなり、ノード には L レベルが現れる。

【0048】

同様の動作により、ノード にもパルスが出力される。このとき、ノード には、ノード に現れるパルスと極性が反転したパルスが出力される。

【0049】

以後、Stage 3、Stage 4 においても同様の動作が行われる。ノード には、ノード に現れるパルスと極性が反転したパルスが出力される。最終的に信号出力部 (CLK\_out1) および信号出力部 (CLK\_out2) にパルスが出力される。

【0050】

図 5 (B) は、クロック信号の振幅変換の様子を示したものである。入力信号の振幅は、L レベル / H レベル = VSS / VDD 0 であり、出力信号の振幅は、L レベル / H レベル = VSS / VDD となっている。

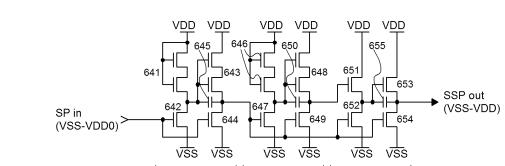

【0051】

図 5 (C) は、図 2 で示したスタートパルス (SP) 用のレベルシフタ 202 を示している。スタートパルスの場合、その反転信号を持たないことから、1 入力型のレベルシフタ回路 (Stage 1) の出力が、1 入力型のインバータ回路 (Stage 2) に入力され、さらに Stage 1 の出力と Stage 2 の出力を用いて、2 入力型のインバータ回路 (Stage 3) へと続く。回路動作に関しては、1 入力型のレベルシフタ回路はクロック信号の場合と同様である。1 入力型のインバータ回路に関しても、1 入力型のレベルシフタ回路と比較して、入力される信号の振幅が L レベル / H レベル = VSS / VDD であって、入出力パルス間の振幅変換がないことを除いて、回路内の動作は同様であるので、ここでは説明を省略する。なお、図 5 (C) において、1 入力型のインバータ回路 (Stage 1) は TFT641 乃至 644 及び容量 645 を有し、1 入力型のインバータ回路 (Stage 2) は TFT646 乃至 649 及び容量 650 を有し、2 入力型のインバータ回路 (Stage 3) は TFT651 乃至 654 及び容量 655 を有する。

【0052】

図 5 (D) は、スタートパルス (SP) の振幅変換の様子を示したものである。入力信号の振幅は、クロック信号と同様、L レベル / H レベル = VSS / VDD 0、出力信号の振幅は、L レベル / H レベル = VSS / VDD となっている。

【0053】

図 6 (A) は、図 2 で示した 2 入力型の NAND 回路 204 を示している。構成としては、1 入力型のインバータ回路と類似であり、1 入力インバータ回路における信号入力部

10

20

30

40

50

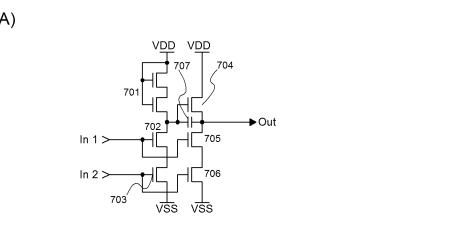

が2入力となり、TFT702、703およびTFT705、706が直列配置されている点のみが異なる。なお、図6(A)においてTFT701がダブルゲート構造をとっている例を示している。

【0054】

信号入力部( In1 )および信号入力部( In2 )に、ともにHレベルが入力されると、TFT702、703、705、706がONし、TFT704のゲート端子の電圧レベルがLレベルとなってオフ状態となり、信号出力部( Out )にはLレベルが現れる。信号入力部( In1 )および信号入力部( In2 )のいずれか一方あるいは両方にLレベルが入力されると、TFT704のゲート端子と低電源電位VSSとは導通しないため、TFT704のゲート端子の電圧レベルはVDDに上昇してオン状態となり、さらに容量707の働きによって、( VDD + VthN )よりも高い電位をとり、信号出力部( Out )には電位VDDのHレベルが現れる。

【0055】

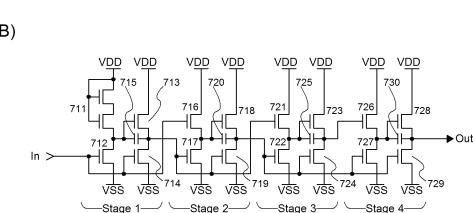

図6(B)は図2で示したバッファ205の構成を示しており、1入力型のインバータ回路( Stage1 )および2入力型のインバータ回路( Stage2 ~ Stage4 )によって構成されている。1入力型のインバータ回路、2入力型のインバータ回路とも、動作に関してはレベルシフタの項で説明したので、ここでは説明を省略する。なお、図6(B)において、1入力型のインバータ回路( Stage1 )はTFT711乃至714及び容量715を有し、2入力型のインバータ回路( Stage2 )はTFT716乃至719及び容量720を有し、2入力型のインバータ回路( Stage3 )はTFT721乃至724及び容量725を有し、2入力型のインバータ回路( Stage4 )はTFT726乃至729及び容量730を有する。

【0056】

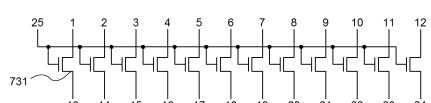

図6(C)は、図2で示したサンプリングスイッチ206の構成を示している。信号入力部( 25 )より、サンプリングパルスが入力され、並列配置された12個のTFT731が同時に制御される。12個のTFT731の入力電極( 1 )~( 12 )に、アナログ映像信号が入力され、サンプリングパルスが入力されたときの映像信号の電位を、ソース線に書き込む働きをする。

【0057】

本実施の形態にて示した表示装置は、画素部を駆動するための駆動回路のトランジスタを、画素TFTと同一の極性を有する単極性で、且つエンハンスマント型のTFTであるとする。これにより、相補型の回路構成とするための工程を省略することが可能となり、製造コストの削減や歩留まり向上に寄与することが出来る。

【0058】

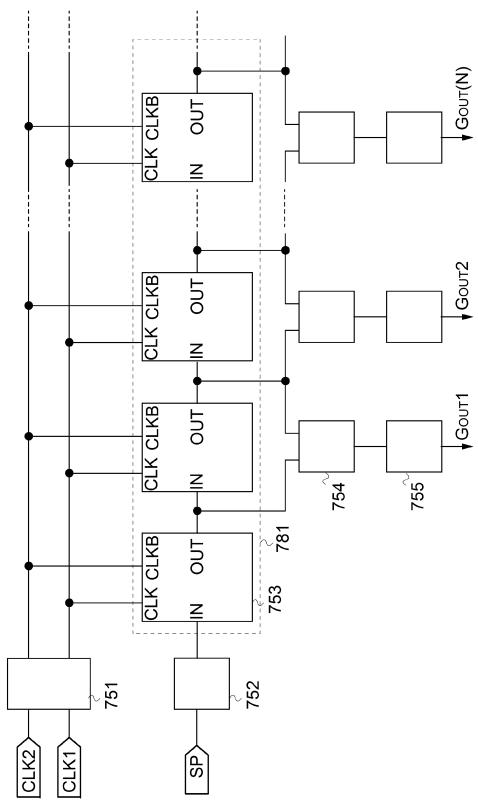

次に図7は、図1で示した表示装置における、ゲート線駆動回路102の回路構成を示した図である。クロック信号用レベルシフタ751、スタートパルス用レベルシフタ752、シフトレジスタ781を構成するパルス出力回路753、NAND回路754、バッファ755を有する。

【0059】

ゲート線駆動回路には、第1のクロック信号( CLK1 )、第2のクロック信号( CLK2 )、スタートパルス( SP )が入力される。これらの入力信号は、外部から低電圧振幅の信号として入力された直後、クロック信号用レベルシフタ751、スタートパルス用レベルシフタ752によって振幅変換を受け、高電圧振幅の信号として駆動回路に入力される。

【0060】

なお、パルス出力回路753、バッファ755、クロック信号用レベルシフタ751、スタートパルス用レベルシフタ752、及びNAND回路754の構成および動作に関しては、ソース線駆動回路に用いたものと同様であるので、ここでは説明を省略する。

【0061】

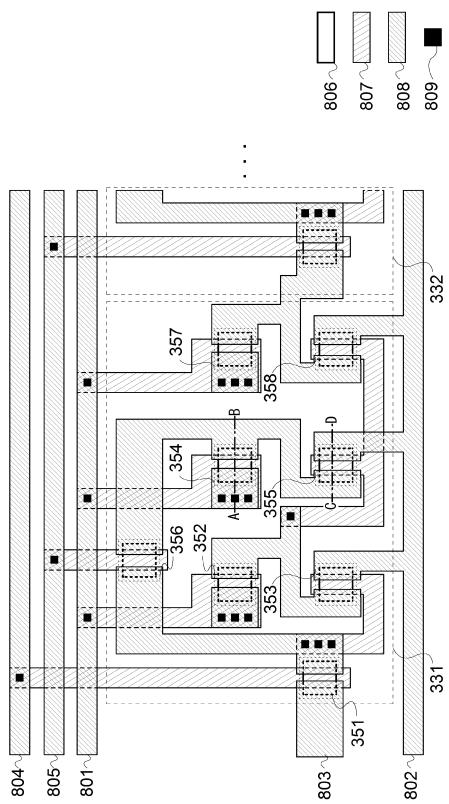

次に、図3(B)に示したパルス出力回路のレイアウト図( 上面図 )を図8に示す。なお

10

20

20

30

40

50

、図8では、複数段形成されるパルス出力回路のうち、一段目にあたるパルス出力回路について示すものである。

【0062】

図8のパルス出力回路は、電源電位VDDが供給される電源線801、電源電位GNDが供給される電源線802、制御信号線803、制御信号線804、制御信号線805、TFT351、TFT352、TFT353、TFT354、TFT355、TFT356、TFT357、TFT358で構成される。

【0063】

図8中では、酸化物半導体膜806、第1の配線層807、第2の配線層808、コンタクト孔809について示している。なお第1の配線層807は、ゲート電極を形成する層である。また、第2の配線層808は、トランジスタのソース電極またはドレイン電極を形成する層である。

10

【0064】

なお図8中での各回路素子の接続関係については、図3(B)と同様である。なお、図8中、制御信号線803はスタートパルスSPが供給される配線であり、制御信号線804は第1のクロック信号が供給される配線であり、制御信号線805は第2のクロック信号が供給される配線であり、電源線801は高電源電位VDDが供給される配線であり、電源線802は、低電源電位VSSが供給される配線である。

【0065】

図8のパルス出力回路のレイアウト図において、本実施の形態では、TFT351乃至TFT358をEEMOSで構成とするものである。そのため、TFTを流れるオフ電流を小さくすることができる。また酸化物半導体膜をチャネル形成領域に用いたTFTは、アモルファスシリコンをチャネル形成領域に用いたTFTに比べ、移動度等の電気的特性に優れるため、性能を落とすことなく、回路におけるTFTが占める面積を縮小することができる。

20

【0066】

なお、図8のパルス出力回路のレイアウト図において、TFT351乃至TFT358のチャネル形成領域の形状をU字型にしてもよい。また図中では各TFTのサイズについて同サイズとして示しているが、後段の負荷の大きさに応じてTFTの大きさを適宜変更しても良い。

30

【0067】

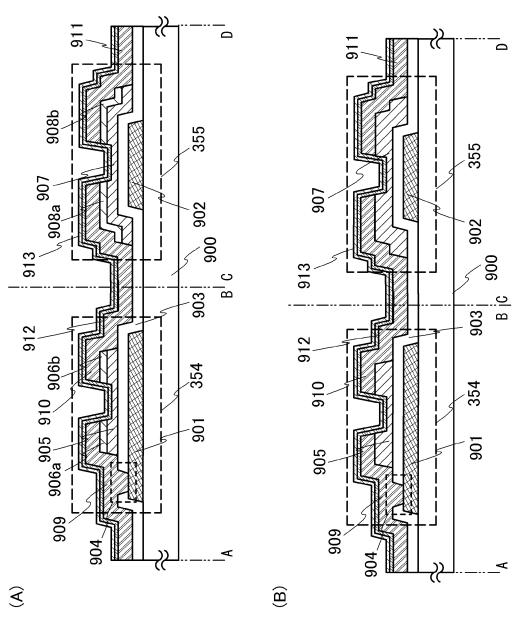

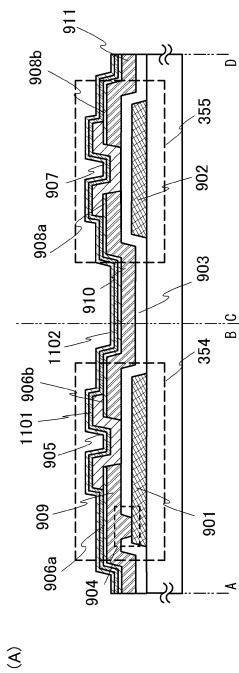

次に図8で説明したレイアウト図におけるTFTの作製工程について図9を用いて説明する。図9では、2つのnチャネル型の薄膜トランジスタを用いて駆動回路を構成するインバータ回路、例えば図8におけるTFT354及びTFT355の断面を示して、その作製を以下説明する。なお、TFT354及びTFT355の断面は、図8中の点線A-B、及びC-Dについて示すものである。

【0068】

なお、画素部と駆動回路は、同一基板上に形成し、画素部においては、マトリクス状に配置したエンハンスマント型トランジスタを用いて画素電極への電圧印加のオンオフを切り替える。この画素部に配置するエンハンスマント型トランジスタは、酸化物半導体を用いており、その電気特性は、ゲート電圧 $\pm 20V$ において、オンオフ比が $10^9$ 以上であるため、リーコンデンサ電流が少なく、低消費電力駆動を実現することができる。

40

【0069】

駆動回路のインバータ回路の断面構造を図9(A)に示す。なお、図9(A)に示すTFT354、TFT355は、半導体層下にゲート絶縁膜を介してゲート電極が設けられ、半導体層上に配線が設けられている薄膜トランジスタの例である。

【0070】

図9(A)において、基板900上に第1のゲート電極901及び第2のゲート電極902を設ける。第1のゲート電極901及び第2のゲート電極902の材料は、アルミニウム(A1)や銅(Cu)などの低抵抗導電性材料で形成することが望ましいが、A1単体

50

では耐熱性が劣り、また腐蝕しやすい等の問題点があるので耐熱性導電性材料と組み合わせて形成する。耐熱性導電性材料としては、チタン( Ti )、タンタル( Ta )、タンゲステン( W )、モリブデン( Mo )、クロム( Cr )、ネオジム( Nd )、スカンジウム( Sc )から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜、または上述した元素を成分とする窒化物で形成する。

#### 【 0 0 7 1 】

例えば、第1のゲート電極901及び第2のゲート電極902の2層の積層構造としては、アルミニウム層上にモリブデン層が積層された二層の積層構造、または銅層上にモリブデン層を積層した二層構造、または銅層上に窒化チタン層若しくは窒化タンタル層を積層した二層構造、窒化チタン層とモリブデン層とを積層した二層構造とすることが好ましい。3層の積層構造としては、タンゲステン層または窒化タンゲステン層と、アルミニウムと珪素の合金またはアルミニウムとチタンの合金と、窒化チタンまたはチタン層とを積層した積層とすることが好ましい。

10

#### 【 0 0 7 2 】

また、第1のゲート電極901及び第2のゲート電極902を覆うゲート絶縁層903上には、第1の酸化物半導体膜905と、第2の酸化物半導体膜907とを設ける。

#### 【 0 0 7 3 】

第1の酸化物半導体膜905上には、ゲート絶縁層903に形成されたコンタクトホール904を介して第1のゲート電極901と直接接続した第1配線909、及び第2の酸化物半導体膜907上に延在した第2配線910を設ける。また、第2の酸化物半導体膜907上には第3配線911を設ける。

20

#### 【 0 0 7 4 】

TFT354は、第1のゲート電極901と、ゲート絶縁層903を介して第1のゲート電極901と重なる第1の酸化物半導体膜905とを有し、第1配線909、第2配線910に接続される。

#### 【 0 0 7 5 】

また、TFT355は、第2のゲート電極902と、ゲート絶縁層903を介して第2のゲート電極902と重なる第2の酸化物半導体膜907とを有し、第2配線910、第3配線911に接続される。

#### 【 0 0 7 6 】

30

また、第1の酸化物半導体膜905と第1配線909との間にはn<sup>+</sup>層906aを設け、第1の酸化物半導体膜905と第2配線910との間にはn<sup>+</sup>層906bを設ける。また、第2の酸化物半導体膜907と第2配線910との間にはn<sup>+</sup>層908aを設け、第2の酸化物半導体膜907と第3配線911との間にはn<sup>+</sup>層908bを設ける。

#### 【 0 0 7 7 】

本実施の形態で説明する、ソース領域又はドレイン領域として機能できるn<sup>+</sup>層906a、906b、908a、908bは、In-Ga-Zn-O系非単結晶膜であり、第1の酸化物半導体膜905、第2の酸化物半導体膜907の成膜条件とは異なる成膜条件で形成され、より低抵抗な酸化物半導体膜である。なお、本実施の形態では、n<sup>+</sup>層906a、906b、908a、908bは、In-Ga-Zn-O系非単結晶膜であり、少なくともアモルファス成分を含んでいるものとする。n<sup>+</sup>層906a、906b、908a、908bは非晶質構造の中に結晶粒(ナノクリスタル)を含む場合がある。このn<sup>+</sup>層906a、906b、908a、908b中の結晶粒(ナノクリスタル)は直径1nm~10nm、代表的には2nm~4nm程度である。

40

#### 【 0 0 7 8 】

n<sup>+</sup>層906a、906b、908a、908bを設けることにより、金属層である第1配線909、第2配線910、第3配線911と、第1の酸化物半導体膜905、第2の酸化物半導体膜907との間を良好な接合としてショットキー接合に比べて熱的にも安定動作を有せしめることができる。また、チャネルのキャリアを供給する(ソース側)、またはチャネルのキャリアを安定して吸収する(ドレイン側)、または抵抗成分を配線との

50

界面に作らないためにも積極的に  $n^+$  層を設けると効果的である。また低抵抗化により、高いドレン電圧でも良好な移動度を保持することができる。

#### 【0079】

図9(A)に示すように、第1の酸化物半導体膜905に電気的に接続する第1の配線909は、ゲート絶縁層903に形成されたコンタクトホール904を介してTFT354の第1のゲート電極901と直接接続する。直接接続させることにより、良好なコンタクトを得ることができ、接触抵抗を低減することができる。第1のゲート電極901と第1配線909を他の導電膜、例えば透明導電膜を介して接続する場合に比べて、コンタクトホールの数の低減、コンタクトホールの数の低減による占有面積の縮小を図ることができる。

10

#### 【0080】

また、図9(A)に示すように、第1配線909、第2配線910、第3配線911、第1の酸化物半導体膜905、及び第2の酸化物半導体膜907上に、OH基を含む酸化珪素膜912、窒化珪素膜913を形成する。本実施の形態で、TEOS(化学式Si(O<sub>2</sub>H<sub>5</sub>)<sub>4</sub>)のようなOH基を有する化合物を用いて、配線層及び酸化物半導体膜上に酸化珪素膜を形成し、酸化珪素膜中がOH基を含んだ膜とすることが好適である。OH基を含む酸化珪素膜は、プラズマCVD法でTEOSとO<sub>2</sub>とを混合し、反応圧力40Pa、基板温度300~400とし、高周波(13.56MHz)電力密度0.5~0.8W/cm<sup>2</sup>で放電させて形成することができる。またOH基を含む酸化珪素膜912上には、窒化珪素膜913も同様にプラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>により、作製すればよい。本実施の形態で開示するように、第1の酸化物半導体膜905、及び第2の酸化物半導体膜907上に、OH基を含む酸化珪素膜912及び窒化珪素膜913を連続して成膜することにより、OH基による酸化物半導体膜中のダングリングボンドの終端化、及び酸化物半導体膜中の酸素が欠損することに伴う低抵抗化の防止を図ることができる。その結果、TFTのしきい値電圧のシフトを低減し、エンハンスマント型トランジスタであることによるオフ電流の低減の効果を持続することができる。

20

#### 【0081】

また、本実施の形態で開示するように、第1の酸化物半導体膜905、及び第2の酸化物半導体膜907上に、OH基を含む酸化珪素膜912及び窒化珪素膜913を連続して成膜することにより、パッシベーション膜としての機能を有する窒化珪素膜を酸化物半導体膜に直接接しない構成を取ることができる。すなわち、酸化物半導体膜が窒化珪素膜中にある窒素によって窒化されることによる低抵抗化を低減することができる。またOH基を含む酸化珪素膜を、窒化珪素膜と酸化物半導体膜との間に配置することにより、窒化珪素膜を成膜することに伴う応力を緩和し、酸化物半導体に応力によるストレスがかかることで生じる酸化物半導体の水素化(または還元化)を低減することができる。

30

#### 【0082】

なお図9(A)では、第1の酸化物半導体膜905上及び第2の酸化物半導体膜907上に $n^+$ 層906a、906b、908a、908bを設ける構成について示したが、図9(B)に示すように必ずしも設ける必要はない。またコンタクトホール904を介した配線層とゲート電極との接続は、回路構成に応じて適宜接続または非接続を選択して構成すればよい。

40

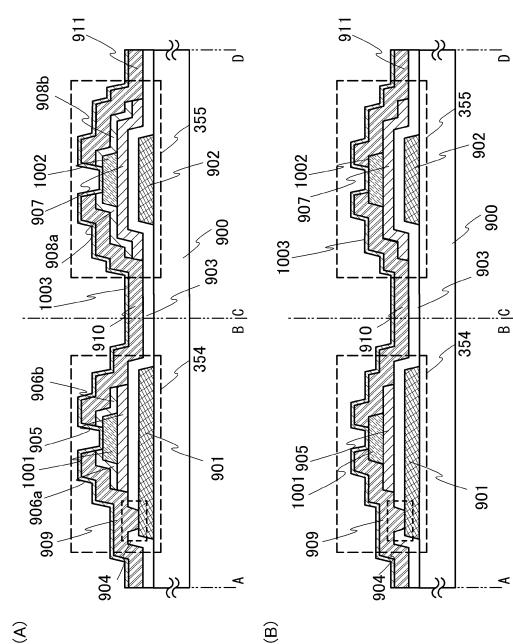

#### 【0083】

図9(A)、(B)では、第1の酸化物半導体膜905上及び第2の酸化物半導体膜907上に、OH基を含む酸化珪素膜912及び窒化珪素膜913を連続して成膜したが、他の構成でもよい。例えば、ソース領域及びドレン電圧を分離する際の、いわゆるチャネルトップ膜として、OH基を含む酸化珪素膜を形成し、その上に窒化珪素膜を設ける構成としてもよい。図10(A)、(B)に一例について示し説明する。図10(A)、(B)に示すTFTの断面構造においては、図9(A)、(B)と同じ構成のものについては、同じ符号を付している。

#### 【0084】

50

図10(A)において、第1の酸化物半導体膜905上及び第2の酸化物半導体膜907上には、図9(A)、(B)のOH基を含む酸化珪素膜912と同様にして形成された第1のチャネル保護層1001、第2のチャネル保護層1002を有する。また図10(A)では、第1のチャネル保護層1001及び第2のチャネル保護層1002を覆って、 $n^+$ 層906a、906b、908a、908bを形成し、エッティングすることでソース領域とドレイン領域とを分離している。 $n^+$ 層906a、906b、908a、908bを形成後、図10(A)に示すように、第1配線909、第2配線910、第3配線911を形成し、第1のチャネル保護層1001上、第2のチャネル保護層1002上、および第1配線909乃至第3配線911上に窒化珪素膜を形成する。第1の酸化物半導体膜905上及び第2の酸化物半導体膜907上で、図10(A)に示すように、OH基を含む酸化珪素膜及び窒化珪素膜を成膜することにより、パッシベーション膜としての機能を有する窒化珪素膜を酸化物半導体膜に直接接しない構成を取ることができる。すなわち、酸化物半導体膜が窒化珪素膜中にある窒素によって窒化されることによる低抵抗化を低減することができる。その結果、TFTのしきい値電圧のシフトを低減し、エンハンスメント型トランジスタであることによるオフ電流の低減の効果を持続することができる。

#### 【0085】

図10(A)に示すTFTの断面構造は、チャネルトップ膜として酸化珪素膜を形成しその上に窒化珪素膜を配置する構成としている。なお、図10(A)に示す構成では図9(A)と同様に $n^+$ 層を設ける構成について示したが、図9(B)と同様に $n^+$ 層を設けない図10(B)に示す構成としても良い。

#### 【0086】

図9(A)、(B)、図10(A)、(B)では、逆スタガ型のTFTについて説明したが、本実施の形態のTFTの構成は逆スタガ型のTFTに限らない。一例としては、コブレナー型のTFTにおいても同様の効果を奏するものである。図11(A)、(B)に断面構造の一例について示し、説明する。なお、図11(A)、(B)に示すTFTの断面構造においては、図9(A)、(B)と同じ構成のものについては、同じ符号を付している。

#### 【0087】

図11(A)において、ゲート絶縁層903上には、第1配線909、第2配線910、第3配線911が $n^+$ 層906a、906b、908a、908bとともに積層して形成されている。そして、第1の酸化物半導体膜905及び第2の酸化物半導体膜907は、 $n^+$ 層906a、906b、908a、908b積層された第1配線909乃至第3配線911の開口部に設けられている。そして図11(A)に示すように、 $n^+$ 層906a、906b、908a、908b上、並びに第1の酸化物半導体膜905及び第2の酸化物半導体膜907上にOH基を含む酸化珪素膜1101を形成する。OH基を含む酸化珪素膜1101上には、パッシベーション膜としての機能を有する窒化珪素膜1102を形成する。第1の酸化物半導体膜905上及び第2の酸化物半導体膜907上で、図11(A)に示すように、OH基を含む酸化珪素膜及び窒化珪素膜を成膜することにより、パッシベーション膜としての機能を有する窒化珪素膜を酸化物半導体膜に直接接しない構成を取ることができる。すなわち、酸化物半導体膜が窒化珪素膜中にある窒素によって窒化されることによる低抵抗化を低減することができる。またOH基を含む酸化珪素膜を、窒化珪素膜と酸化物半導体膜との間に配置することにより、窒化珪素膜を成膜することに伴う応力を緩和し、酸化物半導体に応力によるストレスがかかることで生じる酸化物半導体の水素化（または還元化）を低減することができる。その結果、TFTのしきい値電圧のシフトを低減し、エンハンスメント型トランジスタであることによるオフ電流の低減の効果を持続することができる。

#### 【0088】

図11(A)に示すTFTの断面構造は、コブレナー型のTFT上に酸化珪素膜を形成しその上に窒化珪素膜を配置する構成としている。なお、図11(A)に示す構成では図9(A)、図10(A)と同様に $n^+$ 層を設ける構成について示したが、図9(B)、図1

10

20

30

40

50

0 ( B ) と同様に  $n^+$  層を設けない図 11 ( B ) に示す構成としても良い。

【 0089 】

以上、図 9 ( A )、( B ) 乃至図 11 ( A )、( B ) では、酸化物半導体膜が窒化珪素膜中にある窒素によって窒化されることによる低抵抗化を低減し、且つ酸化物半導体の水素化（または還元化）を低減することができる。その結果、TFT のしきい値電圧のシフトを低減し、エンハンスマント型トランジスタであることによるオフ電流の低減の効果を持続することができる。そして、エンハンスマント型の TFT で、表示装置の画素を構成する TFT、及び駆動回路を構成する TFT を作製する際に、酸化物半導体膜の上下にゲート電極を設けてしきい値制御を行い、2 つのゲート電極に電圧を制御することでエンハンスマント型の TFT とする構成に比べ、簡単な構成でエンハンスマント型の TFT を形成することができる。 10

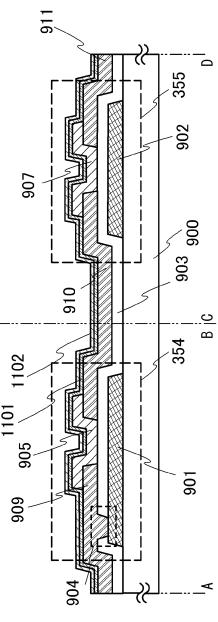

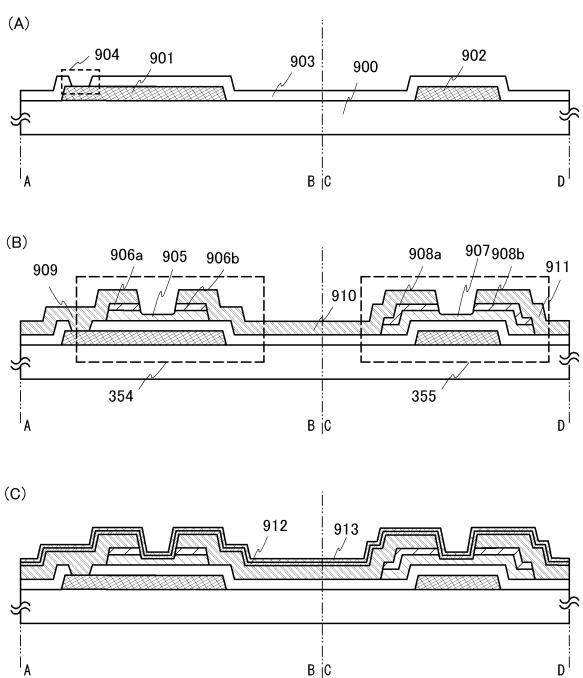

【 0090 】

次に、図 9 ( A )、( B ) 乃至図 11 ( A )、( B ) で示した、2 つの  $n$  チャネル型の薄膜トランジスタを用いて駆動回路を構成するインバータ回路の断面図について、図 9 ( A ) を例にして、その作製工程を以下図 12 ( A )、図 12 ( B )、及び図 12 ( C ) で説明する。なお、TFT 354 及び TFT 355 の断面は、図 8 中の点線 A - B、及び C - D について示すものである。

【 0091 】

基板 900 上に、スパッタ法により第 1 の導電膜を形成し、第 1 のフォトマスクを用いて選択的に第 1 の導電膜のエッチングを行い、第 1 のゲート電極 901 及び第 2 のゲート電極 902 を形成する。次いで、第 1 のゲート電極 901 及び第 2 のゲート電極 902 を覆うゲート絶縁層 903 をプラズマ CVD 法またはスパッタ法を用いて形成する。ゲート絶縁層 903 は、CVD 法又はスパッタ法等を用いて、酸化珪素層、窒化珪素層、酸化窒化珪素層又は窒化酸化珪素層を単層で又は積層して形成することができる。また、ゲート絶縁層 903 として、有機シランガスを用いた CVD 法により酸化珪素層を形成することも可能である。有機シランガスとしては、珪酸エチル (TEOS : 化学式  $Si(OCH_3)_4$  )、テトラメチルシラン (TMS : 化学式  $Si(CH_3)_4$  )、テトラメチルシクロテトラシロキサン (TMCTS)、オクタメチルシクロテトラシロキサン (OMCTS)、ヘキサメチルジシラザン (HMDS)、トリエトキシシラン ( $SiH(OCH_3)_3$  )、トリスジメチルアミノシラン ( $SiH(N(CH_3)_2)_3$  ) 等の珪素含有化合物を用いることができる。 20

【 0092 】

次いで、第 2 のフォトマスクを用いてゲート絶縁層 903 を選択的にエッチングして第 1 のゲート電極 901 に達するコンタクトホール 904 を形成する。ここまで段階での断面図が図 12 ( A ) に相当する。

【 0093 】

次いで、酸化物半導体膜をスパッタ法により成膜し、さらにその上に  $n^+$  層を成膜する。なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層 903 の表面及びコンタクトホール 904 の底面に付着しているゴミを除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に RF 電源を用いて電圧を印加して基板にプラズマを形成して表面を改質する方法である。なお、アルゴンに代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、水素、 $N_2O$ などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に  $Cl_2$ 、 $CF_4$ などを加えた雰囲気で行ってもよい。 40

【 0094 】

次いで、第 3 のフォトマスクを用いて選択的に、酸化物半導体膜及び  $n^+$  層のエッチングを行う。次いで、スパッタ法により第 2 の導電膜を形成し、第 4 のフォトマスクを用いて選択的に第 2 の導電膜のエッチングを行い、第 1 配線 909、第 2 配線 910、及び第 3 配線 911 を形成する。第 1 配線 909 は、コンタクトホール 904 を介して第 1 のゲー 50

ト電極 901 と直接接する。なお、第2の導電膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層 903 の表面、n<sup>+</sup>層の表面、及びコンタクトホール 904 の底面に付着しているゴミを除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板にプラズマを形成して表面を改質する方法である。なお、アルゴンに代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、水素、N<sub>2</sub>Oなどを加えた雰囲気で行ってもよい。また、アルゴン雰囲気にC<sub>12</sub>、CF<sub>4</sub>などを加えた雰囲気で行ってもよい。

#### 【0095】

なお、第2の導電膜のエッチングの際に、さらに、n<sup>+</sup>層及び酸化物半導体膜の一部をエッチングして、n<sup>+</sup>層 906a、906b、908a、908b、第1の酸化物半導体膜 905、第2の酸化物半導体膜 907 を形成する。このエッチングで第1のゲート電極及び第2のゲート電極と重なる部分の第1の酸化物半導体膜 905、第2の酸化物半導体膜 907 の厚さは薄くなる。このエッチングが終了した段階で TFT354 と TFT355 が完成する。ここまで段階での断面図が図 12 (B) に相当する。

#### 【0096】

次いで大気雰囲気下または窒素雰囲気下で 200 ~ 600 の加熱処理を行う。なお、この加熱処理を行うタイミングは限定されず、酸化物半導体膜の成膜後であればいつ行ってもよい。

#### 【0097】

次いで、有機シランガスを用いたCVD法により、OH基を含む酸化珪素膜 912 を形成する。有機シランガスとしては、珪酸エチル (TEOS: 化学式 Si(O<sub>2</sub>H<sub>5</sub>)<sub>4</sub>)、テトラメチルシラン (TMS: 化学式 Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン (TMCTS)、オクタメチルシクロテトラシロキサン (OMCTS)、ヘキサメチルジシラザン (HMDS)、トリエトキシシラン (SiH(O<sub>2</sub>H<sub>5</sub>)<sub>3</sub>)、トリスジメチルアミノシラン (SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>) 等の珪素含有化合物を用いることができる。OH基を含む酸化珪素膜 912 上には、窒化珪素膜 913 を形成する。OH基を含む酸化珪素膜 912 及び窒化珪素膜 913 により、パッシベーション膜としての機能を有する窒化珪素膜を酸化物半導体膜に直接接しない構成を取ることができる。また、酸化物半導体膜上に、OH基を含む酸化珪素膜及び窒化珪素膜を連続して成膜することにより、OH基による酸化物半導体膜中のダングリングボンドの終端化、及び酸化物半導体膜中の酸素が欠損することに伴う低抵抗化の防止を図ることができ、その結果、TFT のしきい値電圧のシフトを低減し、エンハンスマント型トランジスタであることによるオフ電流の低減の効果を持続することができる。ここまで段階での断面図が図 12 (C) に相当する。

#### 【0098】

なお、OH基を含む酸化珪素膜 912 及び窒化珪素膜 913 には、図示しないが、第5のフォトマスクを用いて、選択的にエッチングしてコンタクトホールを形成した後、画素電極と同じ材料を用いて第3の導電膜を形成する。そして、第6のフォトマスクを用いて第3の導電膜を選択的にエッチングして第1配線乃至第3配線と同じ層と電気的に接続するための接続配線を形成する。

#### 【0099】

発光素子を用いた発光表示装置においては、画素部に複数の薄膜トランジスタを有し、画素部においても、ある一つのTFTのゲート端子と他のトランジスタのソースまたはドレインとなる電極とを直接接続させるためのコンタクトホールを有している。このコンタクトホールは、第2のフォトマスクを用いてゲート絶縁膜にコンタクトホールを形成する際に同じマスクを用いて形成することができる。

#### 【0100】

また、液晶表示装置や電子ペーパーにおいては、FPCなどの外部端子と接続するための端子部において、ゲート配線に達するコンタクトホールを形成する際、第2のフォトマス

10

20

30

40

50

クを用いてゲート絶縁膜にコンタクトホールを形成する際に同じマスクを用いて形成することができる。

【0101】

なお、上述した工程順序は一例であって特に限定されない。例えば、フォトマスク数が1枚増えるが、第2の導電膜をエッチングするフォトマスクと、 $n^+$ 層及び酸化物半導体膜の一部をエッチングするフォトマスクを別々に用いてエッチングを行ってもよい。

【0102】

また図13に、図12とは異なる作製工程の例を説明する。

【0103】

基板900上に、スパッタ法により第1の導電膜を形成し、第1のフォトマスクを用いて選択的に第1の導電膜のエッチングを行い、第1のゲート電極901及び第2のゲート電極902を形成する。次いで、第1のゲート電極901及び第2のゲート電極902を覆うゲート絶縁層903をプラズマCVD法またはスパッタ法を用いて形成する。

10

【0104】

次いで、酸化物半導体膜をスパッタ法により成膜し、さらにその上に $n^+$ 層を成膜する。

【0105】

次いで、第2のフォトマスクを用いて選択的に、酸化物半導体膜及び $n^+$ 層のエッチングを行う。こうして、第1のゲート電極901とゲート絶縁層903を介して重なる酸化物半導体膜905、及び $n^+$ 層906が形成され、第2のゲート電極902とゲート絶縁層903を介して重なる酸化物半導体膜907、 $n^+$ 層908が形成される。ここまで段階での断面図が図13(A)に相当する。

20

【0106】

次いで、第3のフォトマスクを用いてゲート絶縁層903を選択的にエッチングして第2のゲート電極902に達するコンタクトホール904を形成する。ここまで段階での断面図が図13(B)に相当する。

【0107】

次いで、スパッタ法により第2の導電膜を形成し、第4のフォトマスクを用いて選択的に第2の導電膜のエッチングを行い、第1配線909、第2配線910、及び第3配線911を形成する。なお、第2の導電膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層903の表面、 $n^+$ 層906、908の表面、及びコンタクトホール904の底面に付着しているゴミを除去することが好ましい。なお、アルゴンに代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、水素、 $N_2O$ などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に $C_{12}$ 、 $CF_4$ などを加えた雰囲気で行ってもよい。

30

【0108】

図13(A)乃至(D)で説明する工程においては、コンタクトホール904を形成した後、他の成膜を行うことなく第2の導電膜を形成することができるため、図12で説明したコンタクトホールの底面が曝される工程数を少なくすることができ、ゲート電極の材料の材料選択の自由度が広げることができる。図13(A)乃至(D)で説明する工程においては、コンタクトホール904で露出しているゲート電極面に接して酸化物半導体膜が成膜されるため、酸化物半導体膜のエッチング工程でゲート電極の材料がエッチングされないエッチング条件またはゲート電極の材料を選択する必要がある。

40

【0109】

なお、第2の導電膜のエッチングの際に、さらに、 $n^+$ 層及び酸化物半導体膜の一部をエッチングして、 $n^+$ 層906a、906b、908a、908b、第1の酸化物半導体膜905、第2の酸化物半導体膜907を形成する。このエッチングで第1のゲート電極及び第2のゲート電極と重なる部分の第1の酸化物半導体膜905、第2の酸化物半導体膜907の厚さは薄くなる。このエッチングが終了した段階でTFT354とTFT355が完成する。

【0110】

50

ここまで段階での断面図が図13(C)に相当する。

【0111】

次いで大気雰囲気下または窒素雰囲気下で200～600の加熱処理を行う。なお、この加熱処理を行うタイミングは限定されず、酸化物半導体膜の成膜後であればいつ行ってもよい。

【0112】

次いで、有機シランガスを用いたCVD法により、OH基を含む酸化珪素膜912を形成する。有機シランガスとしては、珪酸エチル(TEOS:化学式Si(OCH<sub>3</sub>)<sub>4</sub>)、テトラメチルシラン(TMDS:化学式Si(CH<sub>3</sub>)<sub>4</sub>)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OCH<sub>3</sub>)<sub>3</sub>)、トリスジメチルアミノシラン(SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>)等の珪素含有化合物を用いることができる。OH基を含む酸化珪素膜912上には、窒化珪素膜913を形成する。OH基を含む酸化珪素膜912及び窒化珪素膜913により、パッシベーション膜としての機能を有する窒化珪素膜を酸化物半導体膜に直接接しない構成を取ることができる。また、酸化物半導体膜上に、OH基を含む酸化珪素膜及び窒化珪素膜を連続して成膜することにより、OH基による酸化物半導体膜中のダングリングボンドの終端化、及び酸化物半導体膜中の酸素が欠損することに伴う低抵抗化の防止を図ることができ、その結果、TFTのしきい値電圧のシフトを低減し、エンハンスマント型トランジスタであることによるオフ電流の低減の効果を持続することができる。ここまで段階での断面図が図13(D)に相当する。

【0113】

なお、OH基を含む酸化珪素膜912及び窒化珪素膜913には、図示しないが、第5のフォトマスクを用いて、選択的にエッチングしてコンタクトホールを形成した後、画素電極と同じ材料を用いて第3の導電膜を形成する。そして、第6のフォトマスクを用いて第3の導電膜を選択的にエッチングして第1配線乃至第3配線と同じ層と電気的に接続するための接続配線を形成する。

【0114】

発光素子を用いた発光表示装置においては、画素部に複数の薄膜トランジスタを有し、画素部においても、ある一つのTFTのゲート端子と他のトランジスタのソースまたはドレインとなる電極とを直接接続させるためのコンタクトホールを有している。このコンタクトホールは、第2のフォトマスクを用いてゲート絶縁膜にコンタクトホールを形成する際に同じマスクを用いて形成することができる。

【0115】

また、液晶表示装置や電子ペーパーにおいては、FPCなどの外部端子と接続するための端子部において、ゲート配線に達するコンタクトホールを形成する際、第2のフォトマスクを用いてゲート絶縁膜にコンタクトホールを形成する際に同じマスクを用いて形成することができる。

【0116】

なお、上述した工程順序は一例であって特に限定されない。例えば、フォトマスク数が1枚増えるが、第2の導電膜をエッチングするフォトマスクと、n<sup>+</sup>層及び酸化物半導体膜の一部をエッチングするフォトマスクを別々に用いてエッチングを行ってよい。

【0117】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

【0118】

(実施の形態2)

上記実施の形態においては、表示装置の駆動回路におけるシフトレジスタとして、スタティック回路によるシフトレジスタにおける一例について示した。本実施の形態では、ダイナミック回路によるシフトレジスタを用いて駆動回路を構成する一例について説明する

10

20

30

40

50

。

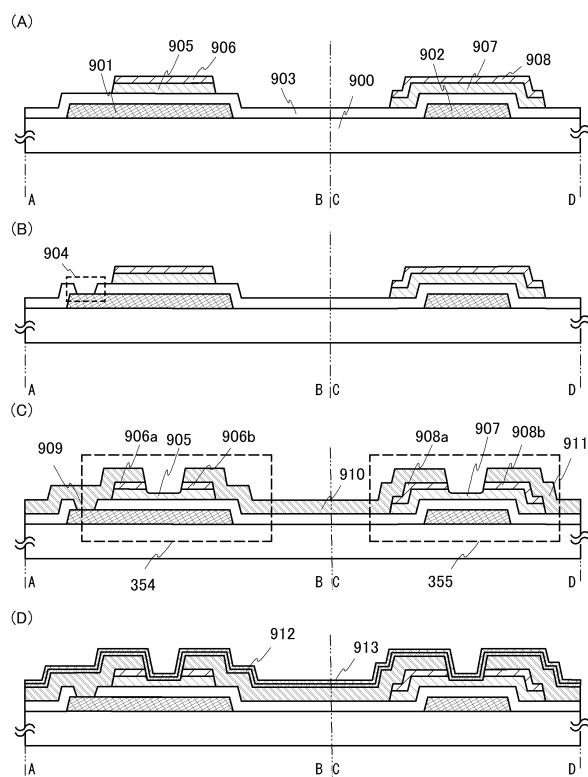

## 【0119】

図14(A)乃至(D)を用いて、ダイナミック回路によるシフトレジスタが有するパルス出力回路の構成を説明する。図14(A)に示すパルス出力回路1400は、一例として、スタートパルスSPが入力端子より入力されるインバータ回路1401と、インバータ回路1401の出力端子に一方の端子が接続されたスイッチ1402と、スイッチ1402の他方の端子に接続された容量素子1403と、で構成される。なお、奇数段目のパルス出力回路のスイッチ1402は、第1のクロック信号(CLK1)によってオンまたはオフは制御される。また偶数段目のパルス出力回路のスイッチ1402は、第2のクロック信号(CLK2)によってオンまたはオフが制御される。

10

## 【0120】

図14(B)は、パルス出力回路の回路構成を詳細に示したものである。パルス出力回路1400は、TFT1411、TFT1412、TFT1413、容量素子1414を有する。また奇数段目のパルス出力回路は、第1のクロック信号CLK1を供給するための配線1415、偶数段目のパルス出力回路は第2のクロック信号CLK2を供給するための配線1416に接続されている。パルス出力回路1400において、TFT1411及びTFT1412は、図14(A)で示したインバータ回路1401に相当し、EEMOS回路で構成される。また、TFT1413は、図14(A)で示したスイッチ1402に相当する。容量素子1414は、図14(A)で示した容量素子1403に相当する。なおTFT1413は、TFT1411及びTFT1412と同様に、エンハンスマント型トランジスタで構成することが好ましい。スイッチとしてエンハンスマント型トランジスタを用いることにより、トランジスタのオフ電流を低減することができるため、低消費電力化が図れるとともに、作製プロセスを簡略することができる。

20

## 【0121】

ここで、図14(A)、(B)で示した回路の回路動作について、図14(C)にタイミングチャートを示す。なお、図14(C)では、説明のため、図14(B)中の回路のノードについてA乃至Eの符号を付して説明するものとする。まず、スタートパルスSPがTFT1411に入力され、スタートパルスSPの反転した信号がノードAに現れる。ノードAの信号は、第1のクロック信号CLK1がHレベルのときノードBに移り、ノードBにノードAの信号が反映されて現れる。そして、ノードBの信号は、インバータ回路によって反転され、ノードCにノードBの反転した信号が現れる。ノードCの信号は、第2のクロック信号CLK2がLレベルにあってスイッチが閉じているため、ノードDには現れない。次に第1のクロック信号CLK1がLレベルにあって第2のクロック信号CLK2がHレベルになると、ノードCの信号はノードDに移り、ノードDにノードCの信号が反映されて現れる。そして、ノードDの信号は、インバータ回路によって反転され、ノードEにノードDの反転した信号が現れる。そして第1のクロック信号CLK1及び第2のクロック信号CLK2を交互にHレベルとすることで、図14(A)、(B)で示した回路をシフトレジスタとして機能させることができる。

30

## 【0122】

なお、図14(B)で説明したパルス出力回路の回路構成の例について、トランジスタのしきい値電圧の分、出力信号の電位が低下してしまうことがある。そのため、図14(D)に示すブートストラップ法を用いるインバータ回路でパルス出力回路を構成することで、信号の電位の低下を招くことなく、シフトレジスタとして機能させることができる。

40

## 【0123】

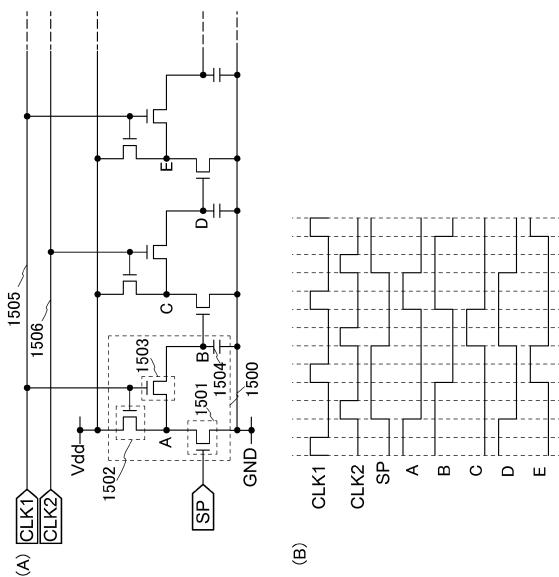

また図14(B)とは、別の回路構成について、図15(A)に示す。図15(A)に示すパルス出力回路1500は、TFT1501、TFT1502、TFT1503、容量素子1504を有する。また奇数段目のパルス出力回路は、第1のクロック信号CLK1を供給するための配線1505、偶数段目のパルス出力回路は第2のクロック信号CLK2を供給するための配線1506に接続されている。パルス出力回路1500において、TFT1501及びTFT1502は、図14(A)で示したインバータ回路1401に

50

相当し、EEMOS回路で構成される。また、TFT1503は、図14(A)で示したスイッチ1402に相当する。容量素子1504は、図14(A)で示した容量素子1403に相当する。なおTFT1503は、TFT1501及びTFT1502と同様に、エンハンスマント型トランジスタで構成することが好ましい。スイッチとしてエンハンスマント型トランジスタを用いることにより、トランジスタのオフ電流を低減することができるため、低消費電力化が図れるとともに、作製プロセスを簡略することができる。

【0124】

図15(A)に示すパルス出力回路が図14(B)と異なる点は、TFT1502のゲート端子に、第1のクロック信号CLK1を供給するため、配線1505が接続されている点にある。図15(A)に示すパルス出力回路1500は、図15(B)に示すタイミングチャートのように動作し、第1のクロック信号CLK1がHレベルにあるとき、スタートパルスSPがHレベルならばノードA、ノードB共にLレベルとなり、スタートパルスSPがLレベルならば、ノードA、ノードB共にHレベルとなる。そして、第1のクロック信号CLK1がLレベルにあるとき、ノードBの電位が保持することができる。すなわち、TFT1502を第1のクロック信号CLK1でオンまたはオフを制御することにより、TFT1503のオンまたはオフに同期して制御することができる。そのため、インバータ回路を構成するTFTが共に導通状態にある際、高電源電位が供給される配線と低電源電位が供給される配線の間を流れてしまう電流を低減することができ、低消費電力化を図ることができる。

【0125】

なお、本実施の形態で示すパルス出力回路を具備するシフトレジスタは、ソース線駆動回路、及びゲート線駆動回路に用いることができる。なおシフトレジスタより出力される信号を、論理回路等を介して出力することによって、所望の信号を得る構成としても良い。

【0126】

なお本実施の形態で説明したダイナミック回路を構成するインバータ回路においても、実施の形態1と同様に、TFTの第1の酸化物半導体膜、及び第2の酸化物半導体膜上に、OH基を含む酸化珪素膜及び窒化珪素膜を連続して成膜することにより、OH基による酸化物半導体膜中のダングリングボンドの終端化、及び酸化物半導体膜中の酸素が欠損することに伴う低抵抗化の防止を図ることができる。その結果、TFTのしきい値電圧のシフトを低減し、エンハンスマント型トランジスタであることによるオフ電流の低減の効果を持続することができる。

【0127】

また、実施の形態1で開示するように、パルス出力回路のインバータ回路を構成する第1の酸化物半導体膜、及び第2の酸化物半導体膜上に、OH基を含む酸化珪素膜及び窒化珪素膜を連続して成膜することにより、パッシベーション膜としての機能を有する窒化珪素膜を酸化物半導体膜に直接接しない構成を取ることができる。すなわち、酸化物半導体膜が窒化珪素膜中にある窒素によって窒化されることによる低抵抗化を低減することができる。またOH基を含む酸化珪素膜を、窒化珪素膜と酸化物半導体膜との間に配置することにより、窒化珪素膜を成膜することに伴う応力を緩和し、酸化物半導体に応力によるストレスがかかることで生じる酸化物半導体の水素化（または還元化）を低減することができる。また、酸化物半導体膜をチャネル形成領域に用いたTFTは、アモルファスシリコンをチャネル形成領域に用いたTFTに比べ、移動度等の電気的特性に優れるため、性能を落とすことなく、回路におけるTFTが占める面積を縮小することができる。

【0128】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

【0129】

（実施の形態3）

本実施の形態では、駆動回路を含む表示装置の作製工程について、図16乃至図23を用

10

20

30

40

50

いて説明する。

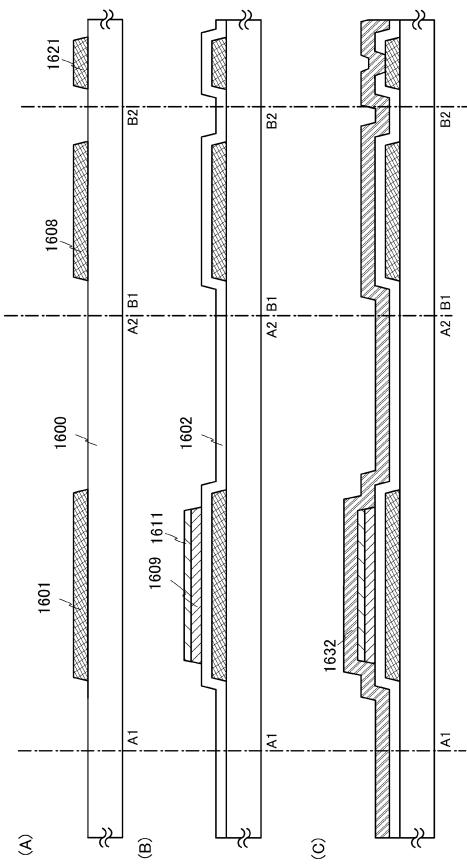

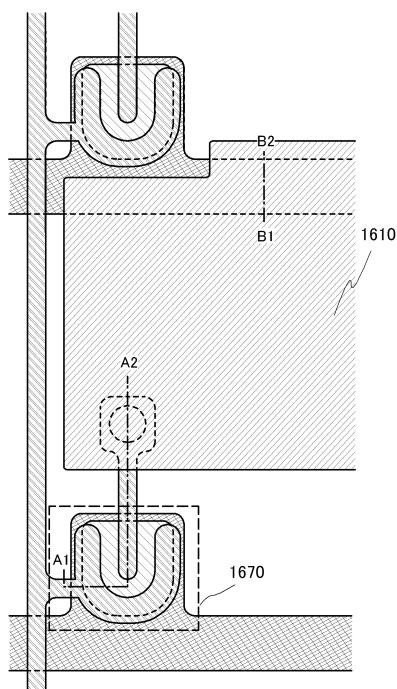

【0130】

図16(A)において、透光性を有する基板1600にはバリウムホウケイ酸ガラスやアルミニウムホウケイ酸ガラスなどのガラス基板を用いることができる。

【0131】

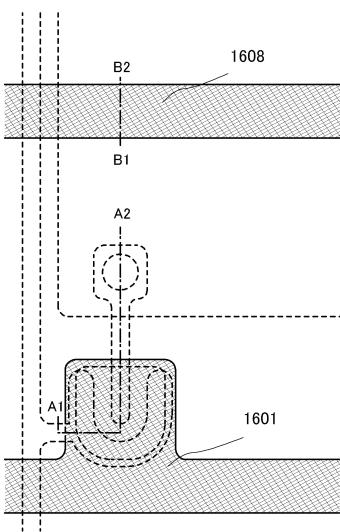

次いで、導電層を基板1600全面に形成した後、第1のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッチングにより不要な部分を除去して配線及び電極(画素薄膜トランジスタ部のゲート電極層1601を含むゲート配線、容量部の容量配線1608、及び端子部の第1の端子1621)を形成する。このとき少なくともゲート電極層1601の端部にテーパー形状が形成されるようにエッチングする。この段階での断面図を図16(A)に示した。なお、この段階での上面図が図18に相当する。

10

【0132】

ゲート電極層1601を含むゲート配線と容量配線1608、端子部の第1の端子1621は、アルミニウム(A1)や銅(Cu)などの低抵抗導電性材料で形成することが望ましい。A1単体では耐熱性が劣り、また腐蝕しやすい等の問題点があるので、耐熱性導電性材料と組み合わせて形成する。耐熱性導電性材料としては、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜、または上述した元素を成分とする窒化物で形成する。

20

【0133】

次いで、ゲート電極層1601上にゲート絶縁層1602を全面に成膜する。ゲート絶縁層1602はスパッタ法などを用い、膜厚を50~250nmとする。

【0134】

例えば、ゲート絶縁層1602として、スパッタ法により100nmの厚さで酸化珪素膜を形成する。勿論、ゲート絶縁層1602はこのような酸化珪素膜に限定されるものでなく、酸化窒化珪素膜、窒化珪素膜、酸化アルミニウム膜、酸化タンタル膜などの他の絶縁膜を用い、これらの材料から成る単層または積層構造として形成しても良い。

【0135】

なお、酸化物半導体膜を成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層1602の表面に付着しているゴミを除去することが好ましい。なお、アルゴンに代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、水素、N<sub>2</sub>Oなどを加えた雰囲気で行ってもよい。また、アルゴン雰囲気にC<sub>1</sub><sub>2</sub>、CF<sub>4</sub>などを加えた雰囲気で行ってもよい。

30

【0136】

次に、ゲート絶縁層1602上に、第1の酸化物半導体膜(本実施の形態では第1のIn-Ga-Zn-O系非単結晶膜)を成膜する。プラズマ処理後、大気に曝すことなく第1のIn-Ga-Zn-O系非単結晶膜を成膜することは、ゲート絶縁層1602と第1の酸化物半導体膜の界面にゴミや水分を付着させない点で有用である。ここでは、直径8インチのIn、Ga、及びZnを含む酸化物半導体ターゲット(In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:1)を用いて、基板とターゲットとの間の距離を170mm、圧力0.4Pa、直流(DC)電源0.5kW、アルゴン又は酸素雰囲気下で成膜する。なお、パルス直流(DC)電源を用いると、ゴミが軽減でき、膜厚分布も均一となるため好ましい。第1のIn-Ga-Zn-O系非単結晶膜の膜厚は、5nm~200nmとする。本実施の形態では第1のIn-Ga-Zn-O系非単結晶膜の膜厚は、100nmとする。

40

【0137】

次いで、大気に曝すことなく、第2の酸化物半導体膜(本実施の形態では第2のIn-Ga-Zn-O系非単結晶膜)をスパッタ法で成膜する。ここでは、In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:1としたターゲットを用い、成膜条件は、圧力を0.4Paとし、電力を500Wとし、成膜温度を室温とし、アルゴンガス流量40sccmを導入してス

50

パッタリング法により成膜を行う。 $In_2O_3 : Ga_2O_3 : ZnO = 1 : 1 : 1$ としたターゲットを意図的に用いているにも関わらず、成膜直後で大きさ  $1\text{ nm} \sim 10\text{ nm}$  の結晶粒を含む  $In - Ga - Zn - O$  系非単結晶膜が形成されることがある。なお、ターゲットの成分比、成膜圧力 ( $0.1\text{ Pa} \sim 2.0\text{ Pa}$ )、電力 ( $250\text{ W} \sim 3000\text{ W}$  : 8 インチ)、温度 (室温  $\sim 100^\circ\text{C}$ )、反応性スパッタの成膜条件などを適宜調節することで結晶粒の有無や、結晶粒の密度や、直径サイズは、 $1\text{ nm} \sim 10\text{ nm}$  の範囲で調節されうると言える。第2の  $In - Ga - Zn - O$  系非単結晶膜の膜厚は、 $5\text{ nm} \sim 20\text{ nm}$  とする。勿論、膜中に結晶粒が含まれる場合、含まれる結晶粒のサイズが膜厚を超える大きさとならない。本実施の形態では第2の  $In - Ga - Zn - O$  系非単結晶膜の膜厚は、 $5\text{ nm}$  とする。

10

#### 【0138】

第1の  $In - Ga - Zn - O$  系非単結晶膜は、第2の  $In - Ga - Zn - O$  系非単結晶膜の成膜条件と異ならせる。例えば、第2の  $In - Ga - Zn - O$  系非単結晶膜の成膜条件における酸素ガス流量とアルゴンガス流量の比よりも、第1の  $In - Ga - Zn - O$  系非単結晶膜の成膜条件における酸素ガス流量とアルゴンガス流量の比が大きい条件とする。具体的には、第2の  $In - Ga - Zn - O$  系非単結晶膜の成膜条件は、希ガス (アルゴン、又はヘリウムなど) 雰囲気下 (または酸素ガス 10% 以下、アルゴンガス 90% 以上) とし、第1の  $In - Ga - Zn - O$  系非単結晶膜の成膜条件は、酸素雰囲気下とする。

#### 【0139】

第2の  $In - Ga - Zn - O$  系非単結晶膜の成膜は、先に逆スパッタを行ったチャンバーと同一チャンバーを用いて行ってもよいし、先に逆スパッタを行ったチャンバーと異なるチャンバーで行ってもよい。

20

#### 【0140】

スパッタ法にはスパッタ用電源に高周波電源を用いる RF スパッタ法と、DC スパッタ法があり、さらにパルス的にバイアスを与えるパルス DC スパッタ法もある。RF スパッタ法は主に絶縁膜を成膜する場合に用いられ、DC スパッタ法は主に金属膜を成膜する場合に用いられる。

#### 【0141】

また、材料の異なるターゲットを複数設置できる多元スパッタ装置もある。多元スパッタ装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種類の材料を同時に放電させて成膜することもできる。

30

#### 【0142】

また、チャンバー内部に磁石機構を備えたマグнетロンスパッタ法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いる ECR スパッタ法を用いるスパッタ装置がある。

#### 【0143】

また、スパッタ法を用いる成膜方法として、成膜中にターゲット物質とスパッタガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタ法や、成膜中に基板にも電圧をかけるバイアススパッタ法もある。

#### 【0144】

次に、第2のフォトリソグラフィー工程を行い、レジストマスクを形成し、第1の  $In - Ga - Zn - O$  系非単結晶膜及び第2の  $In - Ga - Zn - O$  系非単結晶膜をエッティングする。ここでは ITO 07N (関東化学社製) を用いたウェットエッティングにより、不要な部分を除去して第1の  $In - Ga - Zn - O$  系非単結晶膜である酸化物半導体膜 1609、第2の  $In - Ga - Zn - O$  系非単結晶膜である酸化物半導体膜 1611 を形成する。なお、ここでのエッティングは、ウェットエッティングに限定されずドライエッティングを用いてもよい。この段階での断面図を図 16 (B) に示した。なお、この段階での上面図が図 19 に相当する。

40

#### 【0145】

次いで、第3のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッティング

50

により不要な部分を除去してゲート電極層と同じ材料の配線や電極層に達するコンタクトホールを形成する。このコンタクトホールは後に形成する導電膜と直接接続するために設ける。例えば、駆動回路部において、ゲート電極層とソース電極層或いはドレイン電極層とが直接接する薄膜トランジスタや、端子部のゲート配線と電気的に接続する端子を形成する場合にコンタクトホールを形成する。

【0146】

次に、酸化物半導体膜1609及び酸化物半導体膜1611上に金属材料からなる導電膜1632をスパッタ法や真空蒸着法で形成する。この段階での断面図を図16(C)に示した。

【0147】

導電膜1632の材料としては、Al、Cr、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、200～600の熱処理を行う場合には、この熱処理に耐える耐熱性を導電膜に持たせることが好ましい。Al単体では耐熱性が劣り、また腐蝕しやすい等の問題点があるので耐熱性導電性材料と組み合わせて形成する。Alと組み合わせる耐熱性導電性材料としては、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、モリブデン(Mo)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜、または上述した元素を成分とする窒化物で形成する。

【0148】

ここでは、導電膜1632としてチタン膜の単層構造とする。また、導電膜1632は、2層構造としてもよく、アルミニウム膜上にチタン膜を積層してもよい。また、導電膜1632としてTi膜と、そのTi膜上に重ねてNdを含むアルミニウム(Al-Nd)膜を積層し、さらにその上にTi膜を成膜する3層構造としてもよい。導電膜1632は、珪素を含むアルミニウム膜の単層構造としてもよい。

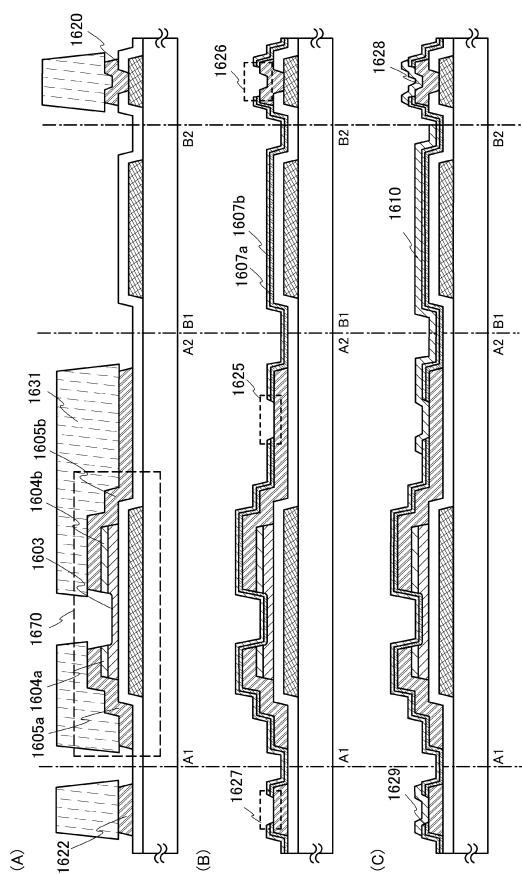

【0149】

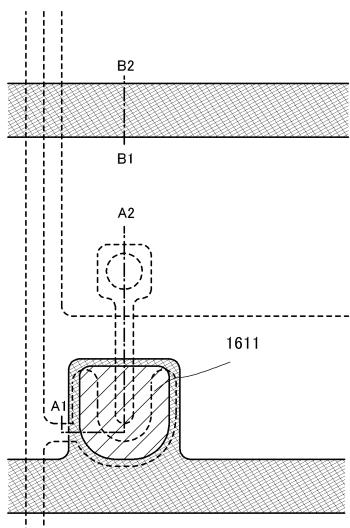

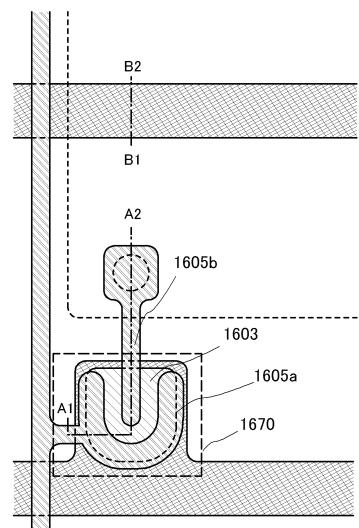

次に、第4のフォトリソグラフィー工程を行い、レジストマスク1631を形成し、エッチングにより不要な部分を除去してソース電極層又はドレイン電極層1605a、1605b、ソース領域又はドレイン領域として機能するn<sup>+</sup>層1604a、1604b、及び接続電極1620を形成する。この際のエッチング方法としてウェットエッチングまたはドライエッチングを用いる。例えば導電膜1632としてアルミニウム膜、又はアルミニウム合金膜を用いる場合は、磷酸と酢酸と硝酸を混ぜた溶液を用いたウェットエッチングを行うことができる。ここでは、アンモニア過水(過酸化水素:アンモニア:水=5:2:2)を用いたウェットエッチングにより、Ti膜の導電膜1632をエッチングしてソース電極層又はドレイン電極層1605a、1605bを、酸化物半導体膜1611をエッチングしてn<sup>+</sup>層1604a、1604bを形成する。このエッチング工程において、酸化物半導体膜1609の露出領域も一部エッチングされ、半導体層1603となる。よってn<sup>+</sup>層1604a、1604bの間の半導体層1603のチャネル形成領域は膜厚の薄い領域となる。図17(A)においては、ソース電極層又はドレイン電極層1605a、1605b、n<sup>+</sup>層1604a、1604bのエッチングをアンモニア過水をエッティング剤として用いることによって一度に行うため、ソース電極層又はドレイン電極層1605a、1605b及びn<sup>+</sup>層1604a、1604bの端部は一致し、連続的な構造となっている。またウェットエッティングを用いるために、エッティングが等方的に行われ、ソース電極層又はドレイン電極層1605a、1605bの端部はレジストマスク1631より後退している。以上の工程で半導体層1603をチャネル形成領域とする薄膜トランジスタ1670が作製できる。この段階での断面図を図17(A)に示した。なお、この段階での上面図が図20に相当する。

【0150】

次いで、200～600、代表的には300～500の熱処理を行うことが好ましい。ここでは炉に入れ、窒素雰囲気下で350、1時間の熱処理を行う。この熱処理

10

20

30

40

50

により In - Ga - Zn - O 系非単結晶膜の原子レベルの再配列が行われる。この熱処理によりキャリアの移動を阻害する歪が解放されるため、ここでの熱処理（光アニールも含む）は重要である。なお、熱処理を行うタイミングは、第2のIn - Ga - Zn - O 系非単結晶膜の成膜後であれば特に限定されず、例えば画素電極形成後に行ってもよい。

#### 【0151】

さらに、露出している半導体層1603のチャネル形成領域に、酸素ラジカル処理を行ってもよい。酸素ラジカル処理を行うことにより薄膜トランジスタをノーマリーオフとすることができる。また、ラジカル処理を行うことにより、半導体層1603のエッチングによるダメージを回復することができる。ラジカル処理はO<sub>2</sub>、N<sub>2</sub>O、好ましくは酸素を含むN<sub>2</sub>、He、Ar雰囲気下で行うことが好ましい。また、上記雰囲気にCl<sub>2</sub>、CF<sub>4</sub>を加えた雰囲気下で行ってもよい。なお、ラジカル処理は、無バイアスで行うことが好ましい。

10

#### 【0152】

また、この第4のフォトリソグラフィー工程において、ソース電極層又はドレイン電極層1605a、1605bと同じ材料である第2の端子1622を端子部に残す。なお、第2の端子1622はソース配線（ソース電極層又はドレイン電極層1605a、1605bを含むソース配線）と電気的に接続されている。

#### 【0153】

また、端子部において、接続電極1620は、ゲート絶縁膜に形成されたコンタクトホールを介して端子部の第1の端子1621と直接接続される。なお、ここでは図示しないが、上述した工程と同じ工程を経て駆動回路の薄膜トランジスタのソース配線あるいはドレイン配線とゲート電極が直接接続される。

20

#### 【0154】

また、多階調マスクにより形成した複数（代表的には二種類）の厚さの領域を有するレジストマスクを用いると、レジストマスクの数を減らすことができるため、工程簡略化、低コスト化が図れる。

#### 【0155】

次いで、レジストマスク1631を除去し、薄膜トランジスタ1670を覆うOH基を含む酸化珪素膜1607aを形成する。OH基を含む酸化珪素膜1607aは、有機シランガスを用いたCVD法により形成する。有機シランガスとしては、珪酸エチル（TEOS：化学式Si(O<sub>2</sub>H<sub>5</sub>)<sub>4</sub>）、テトラメチルシラン（TMS：化学式Si(CH<sub>3</sub>)<sub>4</sub>）、テトラメチルシクロテトラシロキサン（TMCTS）、オクタメチルシクロテトラシロキサン（OMCTS）、ヘキサメチルジシラザン（HMDS）、トリエトキシシラン（SiH(O<sub>2</sub>H<sub>5</sub>)<sub>3</sub>）、トリスジメチルアミノシラン（SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>）等の珪素含有化合物を用いることができる。OH基を含む酸化珪素膜1607a上には、窒化珪素膜1607bを形成する。OH基を含む酸化珪素膜1607a及び窒化珪素膜1607bにより、パッシベーション膜としての機能を有する窒化珪素膜を酸化物半導体膜に直接接しない構成を取ることができる。すなわち、酸化物半導体膜が窒化珪素膜中にある窒素によって窒化されることによる低抵抗化を低減することができる。またOH基を含む酸化珪素膜を、窒化珪素膜と酸化物半導体膜との間に配置することにより、窒化珪素膜を成膜することに伴う応力を緩和し、酸化物半導体に応力によるストレスがかかることで生じる酸化物半導体の水素化（または還元化）を低減することができる。その結果、TFTのしきい値電圧のシフトを低減し、エンハンスマント型トランジスタであることによるオフ電流の低減の効果を持続することができる。

30

#### 【0156】

次に、第5のフォトリソグラフィー工程を行い、レジストマスクを形成し、OH基を含む酸化珪素膜1607a及び窒化珪素膜1607b（以下、OH基を含む酸化珪素膜1607aと窒化珪素膜1607bを併せて保護絶縁膜ともいう）のエッチングによりソース電極層又はドレイン電極層1605bに達するコンタクトホール1625を形成する。また、ここでのエッチングにより第2の端子1622に達するコンタクトホール1627、接

40

50

続電極 1620 に達するコンタクトホール 1626 も形成する。この段階での断面図を図 17 (B) に示す。

【0157】

次いで、レジストマスクを除去した後、透明導電膜を成膜する。透明導電膜の材料としては、酸化インジウム ( $In_2O_3$ ) や酸化インジウム酸化スズ合金 ( $In_2O_3-SnO_2$ 、ITOと略記する)などをスパッタ法や真空蒸着法などを用いて形成する。このような材料のエッティング処理は塩酸系の溶液により行う。しかし、特にITOのエッティングは残渣が発生しやすいので、エッティング加工性を改善するために酸化インジウム酸化亜鉛合金 ( $In_2O_3-ZnO$ ) を用いても良い。

【0158】

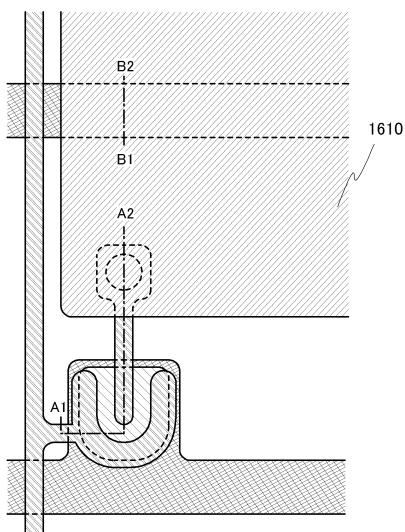

次に、第6のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッティングにより不要な部分を除去して画素電極層 1610 を形成する。

【0159】

また、この第6のフォトリソグラフィー工程において、容量部におけるゲート絶縁層 1602 及びOH基を含む酸化珪素膜 1607a 及び窒化珪素膜 1607b を誘電体として、容量配線 1608 と画素電極層 1610 とで保持容量が形成される。

【0160】

また、この第6のフォトリソグラフィー工程において、第1の端子及び第2の端子をレジストマスクで覆い端子部に形成された透明導電膜 1628、1629 を残す。透明導電膜 1628、1629 は FPC との接続に用いられる電極または配線となる。第1の端子 1621 と直接接続された接続電極 1620 上に形成された透明導電膜 1628 は、ゲート配線の入力端子として機能する接続用の端子電極となる。第2の端子 1622 上に形成された透明導電膜 1629 は、ソース配線の入力端子として機能する接続用の端子電極である。

【0161】

次いで、レジストマスクを除去し、この段階での断面図を図 17 (C) に示す。なお、この段階での上面図が図 21 に相当する。

【0162】

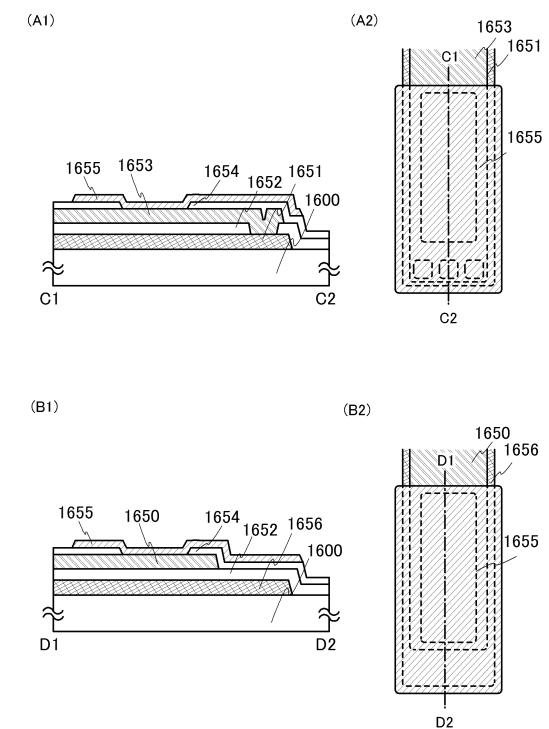

また、図 22 (A1)、図 22 (A2) は、この段階でのゲート配線が設けられた端子部の上面図及び断面図をそれぞれ図示している。図 22 (A1) は図 22 (A2) 中の C1 - C2 線に沿った断面図に相当する。図 22 (A1) において、保護絶縁膜 1654 上に形成される透明導電膜 1655 は、入力端子として機能する接続用の端子電極である。また、図 22 (A1) において、端子部では、ゲート配線と同じ材料で形成される第1の端子 1651 と、ソース配線と同じ材料で形成される接続電極 1653 とがゲート絶縁層 1652 を介して重なり、ゲート絶縁層 1652 に設けられたコンタクトホールを介して直接接して導通させている。また、接続電極 1653 と透明導電膜 1655 が保護絶縁膜 1654 に設けられたコンタクトホールを介して直接接して導通させている。

【0163】

また、図 22 (B1)、及び図 22 (B2) は、ソース配線が設けられた端子部の上面図及び断面図をそれぞれ図示している。また、図 22 (B1) は図 22 (B2) 中の D1 - D2 線に沿った断面図に相当する。図 22 (B1) において、保護絶縁膜 1654 上に形成される透明導電膜 1655 は、入力端子として機能する接続用の端子電極である。また、図 22 (B1) において、端子部では、ゲート配線と同じ材料で形成される電極 1656 が、ソース配線と電気的に接続される第2の端子 1650 の下方にゲート絶縁層 1652 を介して重なる。電極 1656 は第2の端子 1650 とは電気的に接続しておらず、電極 1656 を第2の端子 1650 と異なる電位、例えばフローティング、GND、0V などに設定すれば、ノイズ対策のための容量または静電気対策のための容量を形成することができる。また、第2の端子 1650 は、保護絶縁膜 1654 に設けられたコンタクトホールを介して透明導電膜 1655 と電気的に接続している。

【0164】

10

20

30

40

50

ゲート配線、ソース配線、及び容量配線は画素密度に応じて複数本設けられるものである。また、端子部においては、ゲート配線と同電位の第1の端子、ソース配線と同電位の第2の端子、容量配線と同電位の第3の端子などが複数並べられて配置される。それぞれの端子の数は、それぞれ任意な数で設ければ良いものとし、実施者が適宣決定すれば良い。

【0165】

こうして6回のフォトリソグラフィー工程により、6枚のフォトマスクを使用して、ボトムゲート型のnチャネル型薄膜トランジスタである薄膜トランジスタ1670を有する画素薄膜トランジスタ部、保持容量を有する容量部を完成させることができる。そして、これらを個々の画素に対応してマトリクス状に配置して画素部を構成することによりアクティブマトリクス型の表示装置を作製するための一方の基板とすることができる。本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

10

【0166】

アクティブマトリクス型の液晶表示装置を作製する場合には、アクティブマトリクス基板と、対向電極が設けられた対向基板との間に液晶層を設け、アクティブマトリクス基板と対向基板とを固定する。なお、対向基板に設けられた対向電極と電気的に接続する共通電極をアクティブマトリクス基板上に設け、共通電極と電気的に接続する第4の端子を端子部に設ける。この第4の端子は、共通電極を固定電位、例えばGND、0Vなどに設定するための端子である。

【0167】

また、図21の画素構成に限定されず、図21とは異なる上面図の例を図23に示す。図23では容量配線を設けず、画素電極を隣り合う画素のゲート配線と保護絶縁膜及びゲート絶縁層を介して重ねて保持容量を形成する例であり、この場合、容量配線及び容量配線と接続する第3の端子は省略することができる。なお、図23において、図20と同じ部分には同じ符号を用いて説明する。

20

【0168】

アクティブマトリクス型の液晶表示装置においては、マトリクス状に配置された画素電極を用いて駆動することによって、画面上に表示パターンが形成される。詳しくは選択された画素電極と該画素電極に対応する対向電極との間に電圧が印加されることによって、画素電極と対向電極との間に配置された液晶層の光学変調が行われ、この光学変調が表示パターンとして観察者に認識される。

30

【0169】

液晶表示装置の動画表示において、液晶分子自体の応答が遅いため、残像が生じる、または動画のぼけが生じるという問題がある。液晶表示装置の動画特性を改善するため、全面黒表示を1フレームおきに行う、所謂、黒挿入と呼ばれる駆動技術がある。

【0170】

また、通常の垂直同期周波数を1.5倍若しくは2倍以上にすることで動画特性を改善する、所謂、倍速駆動と呼ばれる駆動技術もある。

【0171】

また、液晶表示装置の動画特性を改善するため、バックライトとして複数のLED(発光ダイオード)光源または複数のEL光源などを用いて面光源を構成し、面光源を構成している各光源を独立して1フレーム期間内で間欠点灯駆動する駆動技術もある。面光源として、3種類以上のLEDを用いてもよいし、白色発光のLEDを用いてもよい。独立して複数のLEDを制御できるため、液晶層の光学変調の切り替えタイミングに合わせてLEDの発光タイミングを同期させることもできる。この駆動技術は、LEDを部分的に消灯することができるため、特に一画面を占める黒い表示領域の割合が多い映像表示の場合には、消費電力の低減効果が図れる。

40

【0172】

これらの駆動技術を組み合わせることによって、液晶表示装置の動画特性などの表示特性を従来よりも改善することができる。

【0173】

50

本実施の形態で得られる表示装置の画素を構成するnチャネル型のトランジスタは、ゲート線駆動回路またはソース線駆動回路を構成するインバータ回路のトランジスタと同様に、In-Ga-Zn-O系非単結晶膜をチャネル形成領域に用いており、良好な動特性を有し、上記で説明した駆動技術を組み合わせることができる。また上記実施の形態で説明するように、酸化物半導体膜上に、OH基を含む酸化珪素膜及び窒化珪素膜を連続して成膜することにより、OH基による酸化物半導体膜中のダングリングボンドの終端化、及び酸化物半導体中の酸素が欠損することに伴う低抵抗化の防止を図ることができる。その結果、TFTのしきい値電圧のシフトを低減し、エンハンスメント型トランジスタであることによるオフ電流の低減の効果を持続することができる。また、酸化物半導体膜をチャネル形成領域に用いたTFTは、アモルファスシリコンをチャネル形成領域に用いたTFTに比べ、移動度等の電気的特性に優れるため、性能を落とすことなく、回路におけるTFTが占める面積を縮小することができる。10

#### 【0174】

また、発光表示装置を作製する場合、有機発光素子の一方の電極（カソードとも呼ぶ）は、低電源電位、例えばGND、0Vなどに設定するため、端子部に、カソードを低電源電位、例えばGND、0Vなどに設定するための第5の端子が設けられる。また、発光表示装置を作製する場合には、ソース配線、及びゲート配線に加えて電源供給線を設ける。従って、端子部には、電源供給線と電気的に接続する第6の端子を設ける。

#### 【0175】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。20

#### 【0176】

##### （実施の形態4）

本実施の形態では、発光表示装置の例を示す。表示装置の有する表示素子としては、ここではエレクトロルミネッセンスを利用する発光素子を用いて示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

#### 【0177】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア（電子および正孔）が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。30

#### 【0178】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー-アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機EL素子を用いて説明する。40

#### 【0179】

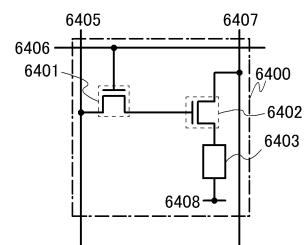

図24は、画素構成の一例を示す図である。

#### 【0180】

適用可能な画素の構成及び画素の動作について説明する。ここでは酸化物半導体膜（In-Ga-Zn-O系非単結晶膜）をチャネル形成領域に用いるnチャネル型のTFTを用いる例を示す。

#### 【0181】

図24における画素6400は、TFT6401、TFT6402、発光素子6403を有している。TFT6401はゲート端子がゲート線6406に接続され、第1端子がソ50

ース線 6405 に接続され、第 2 端子が TFT6402 のゲート端子に接続されている。 TFT6402 は、第 1 端子が電源線 6407 に接続され、第 2 端子が発光素子 6403 の第 1 電極（画素電極）に接続されている。発光素子 6403 の第 2 電極は共通電極 6408 に相当する。共通電極 6408 は、同一基板上に形成される共通電位線と電気的に接続される。

#### 【0182】

なお、発光素子 6403 の第 2 電極（共通電極 6408）には低電源電位が設定されている。なお、低電源電位とは、電源線 6407 に設定される高電源電位を基準にして低電源電位 < 高電源電位を満たす電位であり、低電源電位としては例えば GND、0V などが設定されていても良い。この高電源電位と低電源電位との電位差を発光素子 6403 に印加して、発光素子 6403 に電流を流して発光素子 6403 を発光させるため、高電源電位と低電源電位との電位差が発光素子 6403 の順方向しきい値電圧以上となるようにそれぞれの電位を設定する。

#### 【0183】

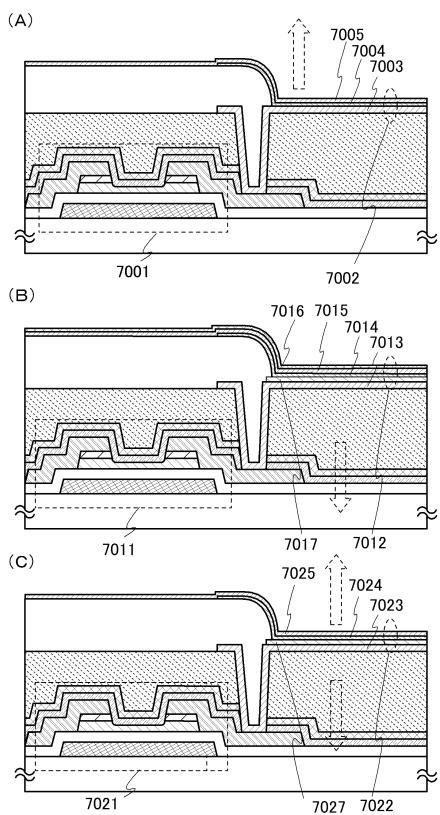

次に、発光素子の構成について、図 25 を用いて説明する。図 25 (A) 乃至 (C) の TFT7001、7011、7021 は、上記実施の形態で示す薄膜トランジスタと同様に作製でき、In-Ga-Zn-O 系非単結晶膜を半導体層として含む信頼性の高い薄膜トランジスタである。

#### 【0184】

発光素子は発光を取り出すために少なくとも陽極又は陰極の一方が透明であればよい。そして、基板上に薄膜トランジスタ及び発光素子を形成し、基板側とは反対側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側の面及び基板側とは反対側の面から発光を取り出す両面射出構造の発光素子があり、上記図 24 で述べた画素構成はどの射出構造の発光素子にも適用することができる。

#### 【0185】

上面射出構造の発光素子について図 25 (A) を用いて説明する。

#### 【0186】

図 25 (A) に、TFT7001 が n 型で、発光素子 7002 から発せられる光が陽極 7005 側に射出する（陽極 7005 を介して抜ける）場合の、画素の断面図を示す。図 25 (A) では、発光素子 7002 の陰極 7003 と TFT7001 が電気的に接続されており、陰極 7003 上に発光層 7004、陽極 7005 が順に積層されている。陰極 7003 は仕事関数が小さく、なおかつ光を反射する導電性材料であれば様々な材料を用いることができる。例えば、Ca、Al、CaF、MgAg、AlLi 等が望ましい。そして発光層 7004 は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。複数の層で構成されている場合、陰極 7003 上に電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層する。なおこれらの層を全て設ける必要はない。陽極 7005 は光を透過する透光性を有する導電性材料を用いて形成し、例えば酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物（以下、ITO と示す。）、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性導電膜を用いても良い。

#### 【0187】

陰極 7003 及び陽極 7005 で発光層 7004 を挟んでいる領域が発光素子 7002 に相当する。図 25 (A) に示した画素の場合、発光素子 7002 から発せられる光は、矢印で示すように陽極 7005 側に射出する。

#### 【0188】

次に、下面射出構造の発光素子について図 25 (B) を用いて説明する。TFT7011 が n 型で、発光素子 7012 から発せられる光が陰極 7013 側に射出する（陰極 7013 を介して抜ける）場合の、画素の断面図を示す。図 25 (B) では、TFT7011 と電気的に接続された透光性を有する導電膜 7017 上に、発光素子 7012 の陰極 7011

10

20

30

40

50

3が成膜されており、陰極7013上に発光層7014、陽極7015が順に積層されている。なお、陽極7015が透光性を有する場合、陽極上を覆うように、光を反射または遮蔽するための遮蔽膜7016が成膜されていてもよい。陰極7013は、図25(A)の場合と同様に、仕事関数が小さい導電性材料であれば様々な材料を用いることができる。ただしその膜厚は、光を透過する程度(好ましくは、5nm~30nm程度)とする。例えば20nmの膜厚を有するアルミニウム膜を、陰極7013として用いることができる。そして発光層7014は、図25(A)と同様に、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。陽極7015は光を透過する必要はないが、図25(A)と同様に、透光性を有する導電性材料を用いて形成することができる。そして遮蔽膜7016は、例えば光を反射する金属等を用いることができるが、金属膜に限定されない。例えば黒の顔料を添加した樹脂等を用いることもできる。

#### 【0189】

陰極7013及び陽極7015で発光層7014を挟んでいる領域が発光素子7012に相当する。図25(B)に示した画素の場合、発光素子7012から発せられる光は、矢印で示すように陰極7013側に射出する。

#### 【0190】

次に、両面射出構造の発光素子について、図25(C)を用いて説明する。図25(C)では、TFT7021と電気的に接続された透光性を有する導電膜7027上に、発光素子7022の陰極7023が成膜されており、陰極7023上に発光層7024、陽極7025が順に積層されている。陰極7023は、図25(A)の場合と同様に、仕事関数が小さい導電性材料であれば様々な材料を用いることができる。ただしその膜厚は、光を透過する程度とする。例えば20nmの膜厚を有するアルミニウム膜を、陰極7023として用いることができる。そして発光層7024は、図25(A)と同様に、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。陽極7025は、図25(A)と同様に、光を透過する透光性を有する導電性材料を用いて形成することができる。

#### 【0191】

陰極7023と、発光層7024と、陽極7025とが重なっている部分が発光素子7022に相当する。図25(C)に示した画素の場合、発光素子7022から発せられる光は、矢印で示すように陽極7025側と陰極7023側の両方に射出する。

#### 【0192】

なお、ここでは、発光素子として有機EL素子について述べたが、発光素子として無機EL素子を設けることも可能である。

#### 【0193】

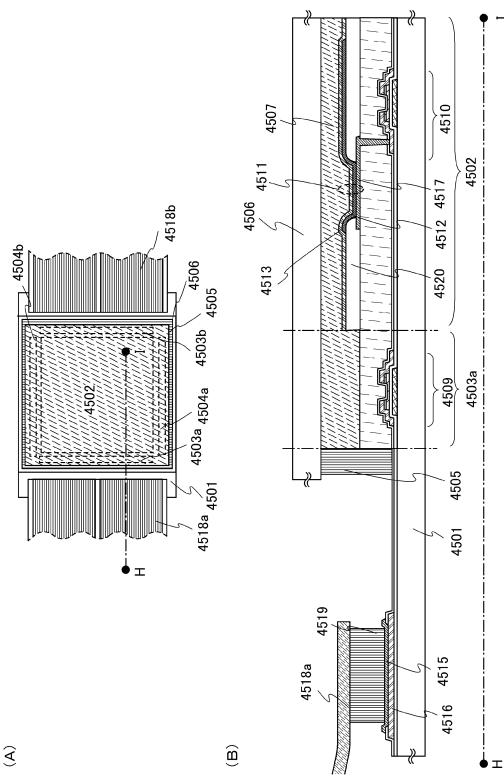

次に、表示装置の一形態に相当する発光表示パネル(発光パネルともいう)の外観及び断面について、図26(A)、26(B)を用いて説明する。図26(A)は、第1の基板上に形成された薄膜トランジスタ及び発光素子を、第2の基板との間にシール材によって封止した、パネルの上面図であり、図26(B)は、図26(A)のH-Iにおける断面図に相当する。

#### 【0194】

第1の基板4501上に設けられた画素部4502、ソース線駆動回路4503a、4503b、及びゲート線駆動回路4504a、4504bを囲むようにして、シール材4505が設けられている。また画素部4502、ソース線駆動回路4503a、4503b、及びゲート線駆動回路4504a、4504bの上に第2の基板4506が設けられている。よって画素部4502、ソース線駆動回路4503a、4503b、及びゲート線駆動回路4504a、4504bは、第1の基板4501とシール材4505と第2の基板4506とによって、充填材4507と共に密封されている。このように外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(貼り合わせフィルム、紫外線硬化樹脂フィルム等)やカバー材でパッケージング(封入)することが好ましい。

#### 【0195】

10

20

30

40

50

また第1の基板4501上に設けられた画素部4502、ソース線駆動回路4503a、4503b、及びゲート線駆動回路4504a、4504bは、薄膜トランジスタを複数有しており、図26(B)では、画素部4502に含まれる薄膜トランジスタ4510と、ソース線駆動回路4503aに含まれる薄膜トランジスタ4509とを例示している。

【0196】

薄膜トランジスタ4509、4510は、In-Ga-Zn-O系非単結晶膜を半導体層として含む上記実施の形態で説明した構成の薄膜トランジスタを適用することができる。

【0197】

また4511は発光素子に相当し、発光素子4511が有する画素電極である第1の電極層4517は、薄膜トランジスタ4510のソース電極層またはドレイン電極層と電気的に接続されている。なお発光素子4511の構成は、第1の電極層4517、電界発光層4512、第2の電極層4513の積層構造であるが、本実施の形態に示した構成に限定されない。発光素子4511から取り出す光の方向などに合わせて、発光素子4511の構成は適宜変えることができる。

【0198】

隔壁4520は、有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。特に感光性の材料を用い、第1の電極層4517上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することができる。

【0199】

電界発光層4512は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。

【0200】

発光素子4511に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の電極層4513及び隔壁4520上に保護膜を形成してもよい。保護膜としては、窒化珪素膜、窒化酸化珪素膜、DLC膜等を形成することができる。

【0201】

また、ソース線駆動回路4503a、4503b、ゲート線駆動回路4504a、4504b、または画素部4502に与えられる各種信号及び電位は、FPC4518a、4518bから供給されている。

【0202】

本実施の形態では、接続端子電極4515が、発光素子4511が有する第1の電極層4517と同じ導電膜から形成され、端子電極4516は、薄膜トランジスタ4509、4510が有するソース電極層及びドレイン電極層と同じ導電膜から形成されている。

【0203】

接続端子電極4515は、FPC4518aが有する端子と、異方性導電膜4519を介して電気的に接続されている。

【0204】

発光素子4511からの光の取り出し方向に位置する第2の基板4506は透光性でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透光性を有する材料を用いる。

【0205】

また、充填材4507としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。本実施の形態は充填材として窒素を用いる。

【0206】

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板(橢円偏光板を含む)、位相差板(1/4板、1/2板)、カラーフィルタなどの光学フィルムを適宜設けてよい。また、偏光板又は円偏光板に反射防止膜を設けてよい。例えば、表面の凹凸により

10

20

30

40

50

反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

【0207】

ソース線駆動回路 4503a、4503b、及びゲート線駆動回路 4504a、4504bとして、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜によって形成された駆動回路が実装されていてもよい。また、ソース線駆動回路のみ、或いは一部、又はゲート線駆動回路のみ、或いは一部のみを別途形成して実装しても良く、本実施の形態は図 26 の構成に限定されない。

【0208】

以上の工程により、発光表示装置（表示パネル）を作製することができる。なお本実施の形態で得られる表示装置の画素を構成するnチャネル型のトランジスタは、ゲート線駆動回路またはソース線駆動回路を構成するインバータ回路のトランジスタと同様に、In-Ga-Zn-O 系非単結晶膜をチャネル形成領域に用いており、良好な動特性を有する。また上記実施の形態で説明するように、酸化物半導体膜上に、OH 基を含む酸化珪素膜及び窒化珪素膜を連続して成膜することにより、OH 基による酸化物半導体膜中のダングリングボンドの終端化、及び酸化物半導体膜中の酸素が欠損することに伴う低抵抗化の防止を図ることができる。その結果、TFT のしきい値電圧のシフトを低減し、エンハンスマント型トランジスタであることによるオフ電流の低減の効果を持続することができる。また、酸化物半導体膜をチャネル形成領域に用いた TFT は、アモルファスシリコンをチャネル形成領域に用いた TFT に比べ、移動度等の電気的特性に優れるため、性能を落とすことなく、回路における TFT が占める面積を縮小することができる。

10

20

【0209】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

【0210】

（実施の形態 5）

本実施の形態では、上記実施の形態の構成を適用できる表示装置として電子ペーパーの例を示す。

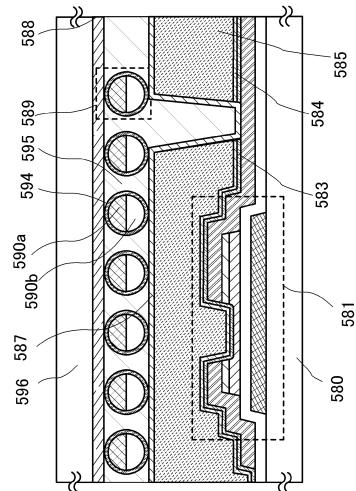

【0211】

図 29 は、表示装置の例としてアクティブマトリクス型の電子ペーパーを示す。TFT581 としては、実施の形態 4 で示す薄膜トランジスタと同様に作製でき、In-Ga-Zn-O 系非単結晶膜を半導体層として含む信頼性の高い薄膜トランジスタである。また、駆動回路を構成する TFT の酸化物半導体膜上に、OH 基を含む酸化珪素膜 583 及び窒化珪素膜 584 を連続して成膜することにより、OH 基による酸化物半導体膜中のダングリングボンドの終端化、及び酸化物半導体膜中の酸素が欠損することに伴う低抵抗化の防止を図っている。

30

【0212】

図 29 の電子ペーパーは、ツイストボール表示方式を用いた表示装置の例である。ツイストボール表示方式とは、白と黒に塗り分けられた球形粒子を、表示素子に用いる電極層である第 1 の電極層及び第 2 の電極層の間に配置し、第 1 の電極層及び第 2 の電極層に電位差を生じさせて球形粒子の向きを制御することにより、表示を行う方法である。

40

【0213】

TFT581 はボトムゲート構造の薄膜トランジスタであり、ソース電極層又はドレイン電極層が第 1 の電極層 587 と、絶縁層 585 に形成される開口で接しており、TFT581 と第 1 の電極層 587 とが電気的に接続している。第 1 の電極層 587 と第 2 の電極層 588 との間には黒色領域 590a と、白色領域 590b と、黒色領域 590a と白色領域 590b との間に設けられた液体で満たされているキャビティ 594 と、を有する球形粒子 589 が設けられており、球形粒子 589 の周囲は樹脂等の充填材 595 で充填されている（図 29 参照）。本実施の形態においては、第 1 の電極層 587 が画素電極に相当し、第 2 の電極層 588 が共通電極に相当する。第 2 の電極層 588 は、TFT581 と同じ基板 580 上に設けられる共通電位線と電気的に接続される。また、第 2 の電極層

50

588上に、基板596が設けられている。

【0214】

また、ツイストボールの代わりに、電気泳動素子を用いることも可能である。透明な液体と、正に帯電した白い微粒子と負に帯電した黒い微粒子とを封入した直径10μm～200μm程度のマイクロカプセルを用いる。第1の電極層と第2の電極層との間に設けられるマイクロカプセルは、第1の電極層と第2の電極層によって、電場が与えられると、白い微粒子と、黒い微粒子が逆の方向に移動し、白または黒を表示することができる。この原理を応用した表示素子が電気泳動表示素子であり、一般的に電子ペーパーとよばれている。電気泳動表示素子は、液晶表示素子に比べて反射率が高いため、補助ライトは不要であり、また消費電力が小さく、薄暗い場所でも表示部を認識することが可能である。また、表示部に電源が供給されない場合であっても、一度表示した像を保持することが可能であるため、電波発信源から表示機能付き半導体装置（単に表示装置、又は表示装置を具備する半導体装置ともいう）を遠ざけた場合であっても、表示された像を保存しておくことが可能となる。

【0215】

以上の工程により、信頼性の高い電子ペーパーを作製することができる。

【0216】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

【0217】

（実施の形態6）

本実施の形態においては、上記実施の形態で説明した表示装置を具備する電子機器の例について説明する。

【0218】

図27（A）は携帯型遊技機であり、筐体9630、表示部9631、スピーカ9633、操作キー9635、接続端子9636、記録媒体読込部9672、等を有することができる。図27（A）に示す携帯型遊技機は、記録媒体に記録されているプログラム又はデータを読み出して表示部に表示する機能、他の携帯型遊技機と無線通信を行って情報を共有する機能、等を有することができる。なお、図27（A）に示す携帯型遊技機が有する機能はこれに限定されず、様々な機能を有することができる。

【0219】

図27（B）はデジタルカメラであり、筐体9630、表示部9631、スピーカ9633、操作キー9635、接続端子9636、シャッターボタン9676、受像部9677、等を有することができる。図27（B）に示すテレビ受像機能付きデジタルカメラは、静止画を撮影する機能、動画を撮影する機能、撮影した画像を自動または手動で補正する機能、アンテナから様々な情報を取得する機能、撮影した画像、又はアンテナから取得した情報を保存する機能、撮影した画像、又はアンテナから取得した情報を表示部に表示する機能、等を有することができる。なお、図27（B）に示すテレビ受像機能付きデジタルカメラが有する機能はこれに限定されず、様々な機能を有することができる。

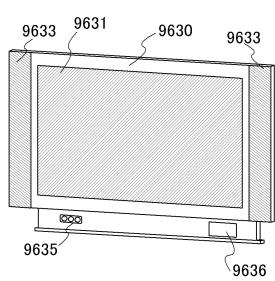

【0220】

図27（C）はテレビ受像器であり、筐体9630、表示部9631、スピーカ9633、操作キー9635、接続端子9636、等を有することができる。図27（C）に示すテレビ受像機は、テレビ用電波を処理して画像信号に変換する機能、画像信号を処理して表示に適した信号に変換する機能、画像信号のフレーム周波数を変換する機能、等を有することができる。なお、図27（C）に示すテレビ受像機が有する機能はこれに限定されず、様々な機能を有することができる。

【0221】

図28（A）はコンピュータであり、筐体9630、表示部9631、スピーカ9633、操作キー9635、接続端子9636、ポインティングデバイス9681、外部接続ポート9680等を有することができる。図28（A）に示すコンピュータは、様々な情報

10

20

30

40

50

(静止画、動画、テキスト画像など)を表示部に表示する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、無線通信又は有線通信などの通信機能、通信機能を用いて様々なコンピュータネットワークに接続する機能、通信機能を用いて様々なデータの送信又は受信を行う機能、等を有することができる。なお、図28(A)に示すコンピュータが有する機能はこれに限定されず、様々な機能を有することができる。

#### 【0222】

次に、図28(B)は携帯電話であり、筐体9630、表示部9631、スピーカ9633、操作キー9635、マイクロフォン9638等を有することができる。図28(B)に示した携帯電話は、様々な情報(静止画、動画、テキスト画像など)を表示部に表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。なお、図28(B)に示した携帯電話が有する機能はこれに限定されず、様々な機能を有することができる。

10

#### 【0223】

本実施の形態において述べた電子機器は、情報を表示するための表示部に上記実施の形態で説明した表示装置を具備するものである。すなわち、ゲート線駆動回路またはソース線駆動回路を構成するインバータ回路のトランジスタとして、In-Ga-Zn-O系非単結晶膜をチャネル形成領域に用いており、良好な動特性を有する。また上記実施の形態で説明するように、酸化物半導体膜上に、OH基を含む酸化珪素膜及び窒化珪素膜を連続して成膜することにより、OH基による酸化物半導体膜中のダンギングボンドの終端化、及び酸化物半導体膜中の酸素が欠損することに伴う低抵抗化の防止を図ることができる。その結果、TFTのしきい値電圧のシフトを低減し、エンハンスマント型トランジスタであることによるオフ電流の低減の効果を持続することができる。また、酸化物半導体膜をチャネル形成領域に用いたTFTは、アモルファスシリコンをチャネル形成領域に用いたTFTに比べ、移動度等の電気的特性に優れるため、性能を落とすことなく、回路におけるTFTが占める面積を縮小することができる。

20

#### 【0224】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【符号の説明】

30

#### 【0225】

- 100 基板

- 101 ソース線駆動回路

- 102 ゲート線駆動回路

- 103 画素部

- 104 フレキシブルプリント基板

- 105 回路

- 110 点線枠

- 170 薄膜トランジスタ

- 201 クロック信号用レベルシフタ

- 202 スタートパルス用レベルシフタ

- 203 パルス出力回路

- 204 NAND回路

- 205 バッファ

- 206 サンプリングスイッチ

- 251 シフトレジスタ

- 300 パルス出力回路

- 301 スイッチ

- 302 インバータ回路

- 303 インバータ回路

40

50

|       |                |    |

|-------|----------------|----|

| 3 0 4 | スイッチ           |    |

| 3 0 5 | インバータ回路        |    |

| 3 3 1 | パルス出力回路        |    |

| 3 3 2 | パルス出力回路        |    |

| 3 5 0 | 点線             |    |

| 3 5 1 | T F T          |    |

| 3 5 2 | T F T          |    |

| 3 5 3 | T F T          |    |

| 3 5 4 | T F T          |    |

| 3 5 5 | T F T          | 10 |

| 3 5 6 | T F T          |    |

| 3 5 7 | T F T          |    |

| 3 5 8 | T F T          |    |

| 3 5 9 | 配線             |    |

| 3 6 0 | 配線             |    |

| 5 8 1 | T F T          |    |

| 5 8 5 | 絶縁層            |    |

| 5 8 7 | 電極層            |    |

| 5 8 8 | 電極層            |    |

| 5 8 9 | 球形粒子           | 20 |

| 5 9 4 | キャビティ          |    |

| 5 9 5 | 充填材            |    |

| 6 0 1 | T F T          |    |

| 6 0 2 | T F T          |    |

| 6 0 3 | T F T          |    |

| 6 0 5 | 容量             |    |

| 6 0 6 | T F T          |    |

| 6 0 8 | T F T          |    |

| 6 0 9 | T F T          |    |

| 6 1 0 | 容量             | 30 |

| 6 1 1 | T F T          |    |

| 6 1 2 | T F T          |    |

| 6 1 3 | T F T          |    |

| 6 1 5 | 容量             |    |

| 7 0 2 | T F T          |    |

| 7 0 4 | T F T          |    |

| 7 0 5 | T F T          |    |

| 7 0 7 | 容量             |    |

| 7 3 1 | T F T          |    |

| 7 5 1 | クロック信号用レベルシフタ  | 40 |

| 7 5 2 | スタートパルス用レベルシフタ |    |

| 7 5 3 | パルス出力回路        |    |

| 7 5 4 | NAND回路         |    |

| 7 5 5 | バッファ           |    |

| 7 8 1 | シフトレジスタ        |    |

| 8 0 1 | 電源線            |    |

| 8 0 2 | 電源線            |    |

| 8 0 3 | 制御信号線          |    |

| 8 0 4 | 制御信号線          |    |

| 8 0 5 | 制御信号線          | 50 |

|         |          |    |

|---------|----------|----|

| 8 0 6   | 酸化物半導体膜  |    |

| 8 0 7   | 配線層      |    |

| 8 0 8   | 配線層      |    |

| 8 0 9   | コンタクト孔   |    |

| 9 0 0   | 基板       |    |

| 9 0 1   | ゲート電極    |    |

| 9 0 2   | ゲート電極    |    |

| 9 0 3   | ゲート絶縁層   |    |

| 9 0 4   | コンタクトホール |    |

| 9 0 5   | 酸化物半導体膜  | 10 |

| 9 0 6   | n + 層    |    |

| 9 0 7   | 酸化物半導体膜  |    |

| 9 0 8   | n + 層    |    |

| 9 0 9   | 配線       |    |

| 9 1 0   | 配線       |    |

| 9 1 1   | 配線       |    |

| 9 1 2   | 酸化珪素膜    |    |

| 9 1 3   | 窒化珪素膜    |    |

| 1 0 0 1 | チャネル保護層  |    |

| 1 0 0 2 | チャネル保護層  | 20 |

| 1 1 0 1 | 酸化珪素膜    |    |

| 1 1 0 2 | 窒化珪素膜    |    |

| 1 4 0 0 | パルス出力回路  |    |

| 1 4 0 1 | インバータ回路  |    |

| 1 4 0 2 | スイッチ     |    |

| 1 4 0 3 | 容量素子     |    |

| 1 4 1 1 | T F T    |    |

| 1 4 1 2 | T F T    |    |

| 1 4 1 3 | T F T    |    |

| 1 4 1 4 | 容量素子     | 30 |

| 1 4 1 5 | 配線       |    |

| 1 4 1 6 | 配線       |    |

| 1 5 0 0 | パルス出力回路  |    |

| 1 5 0 1 | T F T    |    |

| 1 5 0 2 | T F T    |    |

| 1 5 0 3 | T F T    |    |

| 1 5 0 4 | 容量素子     |    |

| 1 5 0 5 | 配線       |    |

| 1 5 0 6 | 配線       |    |

| 1 6 0 0 | 基板       | 40 |

| 1 6 0 1 | ゲート電極層   |    |

| 1 6 0 2 | ゲート絶縁層   |    |

| 1 6 0 3 | 半導体層     |    |

| 1 6 0 8 | 容量配線     |    |

| 1 6 0 9 | 酸化物半導体膜  |    |

| 1 6 1 0 | 画素電極層    |    |

| 1 6 1 1 | 酸化物半導体膜  |    |

| 1 6 2 0 | 接続電極     |    |

| 1 6 2 1 | 端子       |    |

| 1 6 2 2 | 端子       | 50 |

|         |          |    |

|---------|----------|----|

| 1 6 2 5 | コンタクトホール |    |

| 1 6 2 6 | コンタクトホール |    |

| 1 6 2 7 | コンタクトホール |    |

| 1 6 2 8 | 透明導電膜    |    |

| 1 6 2 9 | 透明導電膜    |    |

| 1 6 3 1 | レジストマスク  |    |

| 1 6 3 2 | 導電膜      |    |

| 1 6 5 0 | 端子       |    |

| 1 6 5 1 | 端子       |    |

| 1 6 5 2 | ゲート絶縁層   | 10 |

| 1 6 5 3 | 接続電極     |    |

| 1 6 5 4 | 保護絶縁膜    |    |

| 1 6 5 5 | 透明導電膜    |    |

| 1 6 5 6 | 電極       |    |

| 1 6 7 0 | 薄膜トランジスタ |    |

| 4 5 0 1 | 基板       |    |

| 4 5 0 2 | 画素部      |    |

| 4 5 0 5 | シール材     |    |

| 4 5 0 6 | 基板       |    |

| 4 5 0 7 | 充填材      | 20 |

| 4 5 0 9 | 薄膜トランジスタ |    |

| 4 5 1 0 | 薄膜トランジスタ |    |

| 4 5 1 1 | 発光素子     |    |

| 4 5 1 2 | 電界発光層    |    |

| 4 5 1 3 | 電極層      |    |

| 4 5 1 5 | 接続端子電極   |    |

| 4 5 1 6 | 端子電極     |    |

| 4 5 1 7 | 電極層      |    |

| 4 5 1 9 | 異方性導電膜   |    |

| 4 5 2 0 | 隔壁       | 30 |

| 6 4 0 0 | 画素       |    |

| 6 4 0 1 | TFT      |    |

| 6 4 0 2 | TFT      |    |

| 6 4 0 3 | 発光素子     |    |

| 6 4 0 5 | ソース線     |    |

| 6 4 0 6 | ゲート線     |    |

| 6 4 0 7 | 電源線      |    |

| 6 4 0 8 | 共通電極     |    |

| 7 0 0 1 | TFT      |    |

| 7 0 0 2 | 発光素子     | 40 |

| 7 0 0 3 | 陰極       |    |

| 7 0 0 4 | 発光層      |    |

| 7 0 0 5 | 陽極       |    |

| 7 0 1 1 | TFT      |    |

| 7 0 1 2 | 発光素子     |    |

| 7 0 1 3 | 陰極       |    |

| 7 0 1 4 | 発光層      |    |

| 7 0 1 5 | 陽極       |    |

| 7 0 1 6 | 遮蔽膜      |    |

| 7 0 1 7 | 導電膜      | 50 |

|           |             |    |

|-----------|-------------|----|

| 7 0 2 1   | T F T       |    |

| 7 0 2 2   | 発光素子        |    |

| 7 0 2 3   | 陰極          |    |

| 7 0 2 4   | 発光層         |    |

| 7 0 2 5   | 陽極          |    |

| 7 0 2 7   | 導電膜         |    |

| 9 6 3 0   | 筐体          |    |

| 9 6 3 1   | 表示部         |    |

| 9 6 3 3   | スピーカ        |    |

| 9 6 3 5   | 操作キー        | 10 |

| 9 6 3 6   | 接続端子        |    |

| 9 6 3 8   | マイクロフォン     |    |

| 9 6 7 2   | 記録媒体読込部     |    |

| 9 6 7 6   | シャッターボタン    |    |

| 9 6 7 7   | 受像部         |    |

| 9 6 8 0   | 外部接続ポート     |    |

| 9 6 8 1   | ポインティングデバイス |    |

| 4 5 0 3 a | ソース線駆動回路    |    |

| 4 5 0 4 a | ゲート線駆動回路    |    |

| 4 5 1 8 a | F P C       | 20 |

【図1】

【図2】

【図3】

【図4】

【図5】

(C)

【図6】

(C)

【 义 7 】

【 义 8 】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図 1 5】

【図 1 6】

【図 1 7】

【図 1 8】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

## フロントページの続き

## (51)Int.Cl.

|         |       | F I       |                       |

|---------|-------|-----------|-----------------------|

| H 0 1 L | 51/50 | (2006.01) | H 0 1 L 29/78 6 1 3 Z |

| H 0 5 B | 33/14 | (2006.01) | H 0 1 L 27/08 3 3 1 E |

|         |       |           | H 0 5 B 33/14 A       |

|         |       |           | H 0 5 B 33/14 Z       |

## (56)参考文献 特開2006-165532 (JP, A)

特開2007-096129 (JP, A)

特開2008-227517 (JP, A)

特開2007-194594 (JP, A)

特開2008-010440 (JP, A)

特開2005-327797 (JP, A)

米国特許出願公開第2008/0176364 (US, A1)

特開2005-340802 (JP, A)

特開2008-091896 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 9 / 7 8 6

H 0 1 L 2 1 / 3 3 6