# **DEUTSCHE DEMOKRATISCHE REPUBLIK**

(12) Wirtschaftspatent

Erteilt gemäß § 18 Absatz 2 Patentgesetz

# **PATENTSCHRIFT**

(19) DD (11) 266 719 A3

4(51) G 05 B 19/02

### AMT FÜR ERFINDUNGS- UND PATENTWESEN

| (72) Sobottka, Dietmar, DiplIng., Meier, Frank-Günter, DiplIng., DD                  | Dollide: Ottabo 200, Rait-Marx-Otaat, 0010, t |

|--------------------------------------------------------------------------------------|-----------------------------------------------|

| (71) VEB Numerik "Karl-Marx" Karl-Marx-Stadt, Bornaer Straße 205, Karl-Marx-Stadt, 9 |                                               |

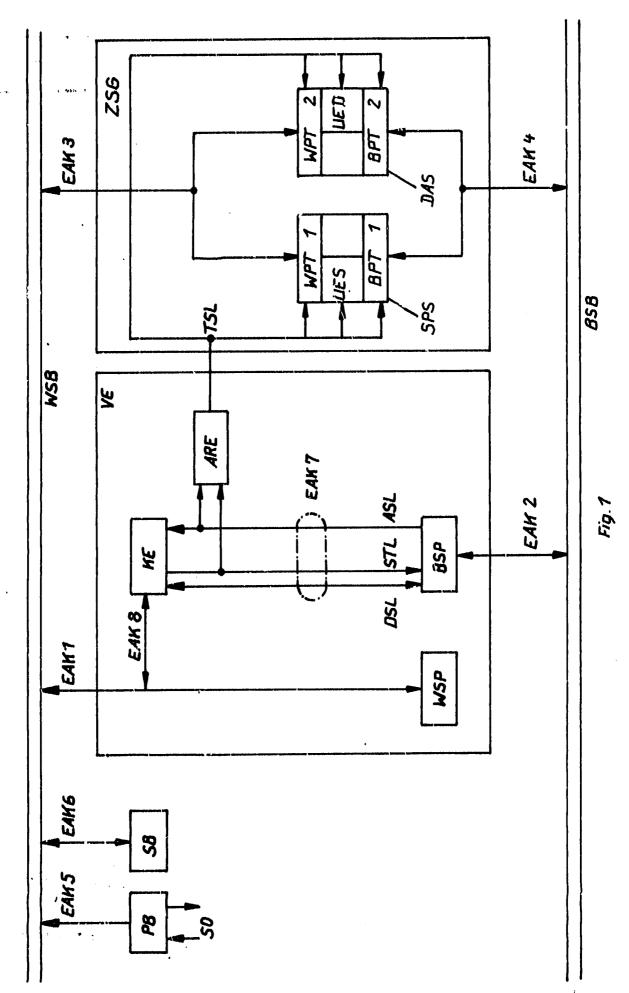

(57) Die Erfindung beinhaltet eine Programmsteueranordnung zur Steuerung von Maschinen und Prozessen und bezieht sich auf das Gebiet der elektrischen Steuerungstechnik. Ziel der Erfindung ist es, mit minimalem Aufwand ein breites Anwendungsgebiet für elektrische Programmsteueranordnungen zu erreichen. Durch die Erfindung wird die Aufgabe gelöst, eine Programmsteueranordnung mit einer mehrere Prozessoren enthaltenden Verarbeitungseinheit zu schaffen, wobei jeder dieser Prozessoren eine optimale Realisierung von Steuerprogrammen mit unterschiedlichen Operationen und unterschiedlicher Informationsbreite der zu verarbeitenden Informationen ermöglicht. Das Wesen der Erfindung besteht darin, daß eine Verarbeitungseinheit und eine Zweitorspeichergruppe über Ein-/Ausgabekanäle mit einem Spezialprozessorbus und einem Standardprozessorbus verbunden sind. Die Verarbeitungseinheit enthält einen als Wortprozessor eingesetzten Standardprozessor und einen als Bitprozessor eingesetzten Spezialprozessor. Die Zweitorspeichergruppe ist aus einem Steuerprogrammspeicher und einem Daten- und Abbildspeicher aufgebaut. An den Standardprozessor sind gleichzeitig über weitere Ein-/Ausgabekanäle mit dem Steuerobjekt verbundene Peripherie- sowie Speicherbaugruppen angeschlossen. Die in Fig. 1 am besten dargestellte Erfindung kann zweckmäßig für Maschinen- und Prozeßsteueranordnungen verwendet werden. Fig. 1

# Erfindungsanspruch

1. Elektrische Programmsteueranordnung zur Steuerung von Maschinen und Prozessen mit mehreren Prozessoren und Schnittstellen, die als Grundausrüstung mindestens einen bitorientierten und einen wortorientierten mit einem Wortspeicher gekoppelten Prozessor enthält, und bei der an eine als Binärschnittstelle ausgeführte zum Bitprozessor gehörige Busleitung binäre Ein-/Ausgabeeinheiten und Speichereinheiten sowie an eine als digitale Schnittstelle ausgeführte zum Wortprozessor gehörige Busleitung über einen Koordinator der Bitprozessor, ein Programmspeicher, eine Standardperipherie, eine Prozeßperipherie und ein zusätzlicher Rechner angeschlossen sind, gekennzeichnet dadurch, daß als Zentraleinheit eine aus einem als Bitprozessor eingesetzten Spezialprozessor (BSP) und einem als Wortprozessor eingesetzten Standardprozessor (WSP) bestehende Verarbeitungseinheit 'VE) und eine aus einem Steuerprogrammspeicher (SPS) und einem Daten- und Abbildspeicher (DAS) aufgebaute Zweitorspeichergruppe (ZSG) über Ein-/Ausgabekanäle (EAK 1; EAK 2; EAK 3; EAK 4) mit einem Spezialprozessorbus (BSB) und einem Standardprozessorbus (WSB) verbunden sind, wobei un den Standardprozessorbus (WSB) gleichzeitig über weitere Ein-/Ausgabekanäle (EAK 5; EAK 6) mit dem Steuerobjekt SO verbundene Peripheriebaugruppen und Speicherbaugruppen (SB) ungeschlossen sind, und vom durch den zweiten Ein-/Ausgabekanal (EAK 2) mit dem Spezialprozessorbus (BSB) verbundenen Spezialprozessor (BSP) über einen aus einer Daten- und Steuerleitung (DSL), einer Steuersignalleitung (STL) und aus einer Aufrufsignalleitung (ASL) bestehenden siebenten Ein-/Ausgabekanal (EAK 7) einerseits über eine Koppeleinheit (KE), einen achten Ein-/Ausgabekanal (EAK 8) und den ersten Ein-/Ausgabekanal (EAK 1) ein Anschluß an den Standardprozessor (WSP) vorhanden ist, sowie andererseits eine mit der Steuersignalleitung (STL) und der Aufrufsignalleitung (ASL) verbundene Aufrufeinheit (ARE) durch eine von deren Ausgang abgehende Torsteuersignalleitung (TSL) an Wortprozessorkoppeltore (WPT1; WPT2), an Datenbreiteumschalteinheiten (UES; UED) und Spezialprozessorkoppeltore (BPT1; BPT2) des Steuerprogrammspeichers (SPS) und des Daten- und Abbildspeichers (DAS) angeschlossen sind, die beide über den dritten und vierten Ein-/Ausgabekanal (EAK3; EAK4) sowohl mit dem Standardprozessorbus (WSB) als auch mit dem Spezialprozessorbus (BSB) gekoppelt sind.

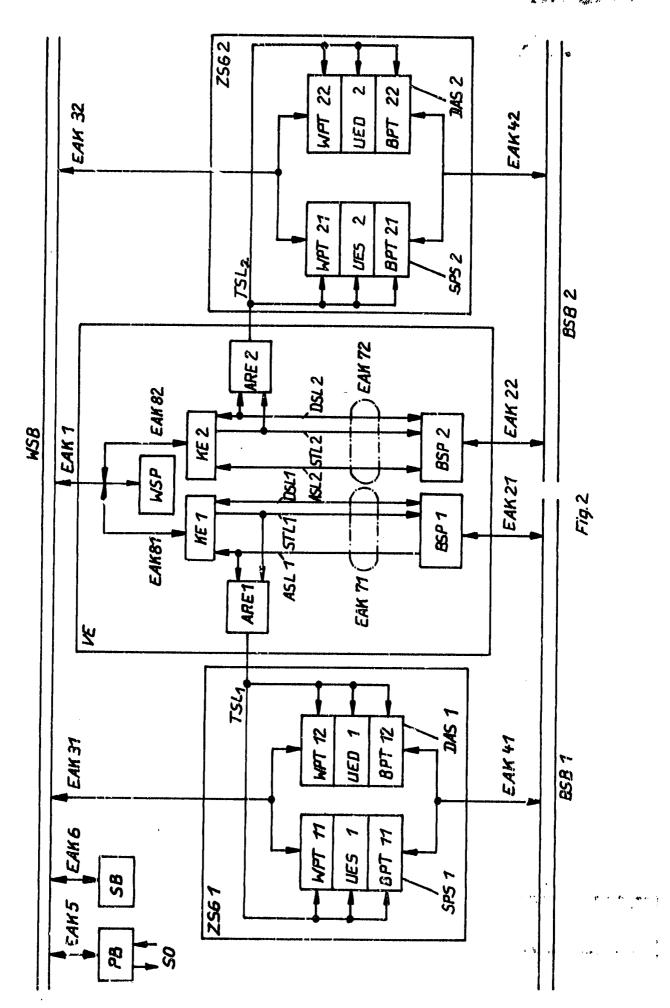

2. Elektrische Programmsteueranordnung zur Steuerung von Maschinen und Prozessen nach Punkt 1, gekennzeichnet dadurch, daß als Zentraleinheit eine aus einem ersten Spezialprozessor (BSP1) und einem zweiten Spezialprozessor (BSP2) sowie einem Standardprozessor (WSP) bestehende Verarbeitungseinheit (VE) und eine erste und zweite aus jeweils einem Steuerprogrammspeicher (SPS1; SPS2) und einem Daten- und Abbildspeicher (DAS1; DAS2) aufgebaute Zweitorspeichergruppe (ZSG1; ZSG2) über Ein-/Ausgabekanäle (EAK1; EAK21; EAK22; EAK31; EAK32; EAK41; EAK42) mit einem ersten und zweiten Spezialprozessorbus (BSB1; BSB2) und einen Standardprozessorbus (WSB) verbunden sind, wobei vom durch die zweiten Ein-/Ausgabekanäle (EAK21; EAK22) mit dem ersten und zweiten Spezialprozessorbus (BSB1; BSB2) verbundenen ersten und zweiten Spezialprozessor (BSP1; BSP2) über einen aus einer Daten- und Steuerleitung (DSL1; DSL2), einer Steuer signalleitung (STL1; STL2) und aus einer Aufrufsignalleitung (ASL1; ASL2) bestehenden siebenten Ein-/ Ausgabekanälen (EAK71; EAK72) einerseits über eine erste und zweite Koppeleinheit (KE1; KE2), über achte Ein-/Ausgabekanäle (EAK81; EAK82) und den ersten Ein-/Ausgabekanal (EAK1) ein Anschluß an den Standardprozessor (WSP) vorhanden ist, sowie andererseits eine erste und zweite

mit den dazugehörigen Steuersignalleitungen (STL 1; STL 2) und Aufrufsignalleitungen (ASL 1; ASL 2) verbundene Aufrufeinheit (ARE 1; ARE 2) durch ausganysseitig vorhandene Torsteuersignalleitung (TSL 1; TSL 2) an die Wortprozessorkoppeltore (WPT 11; WPT 12; WPT 21; WPT 22), an die Datenbreiteumschalteinheiten (UES 1; UED 1; UES 2, UED 2) und die Spezialprozessorkoppeltore (BPT 11; BPT 12; BPT 21; BPT 22) der Steuerprogrammspeicher (SPS 1; SPS 2) und Daten- und Abbildspeicher (DAS 1; DAS 2) angeschlossen sind, die über dritte und vierte Ein-/Ausgabekanäle (EAK 31; EAK 32; EAK 41; EAK 42) sowohl mit dem Standardprozessorbus (BSB 1; BSB 2) gekoppelt sind.

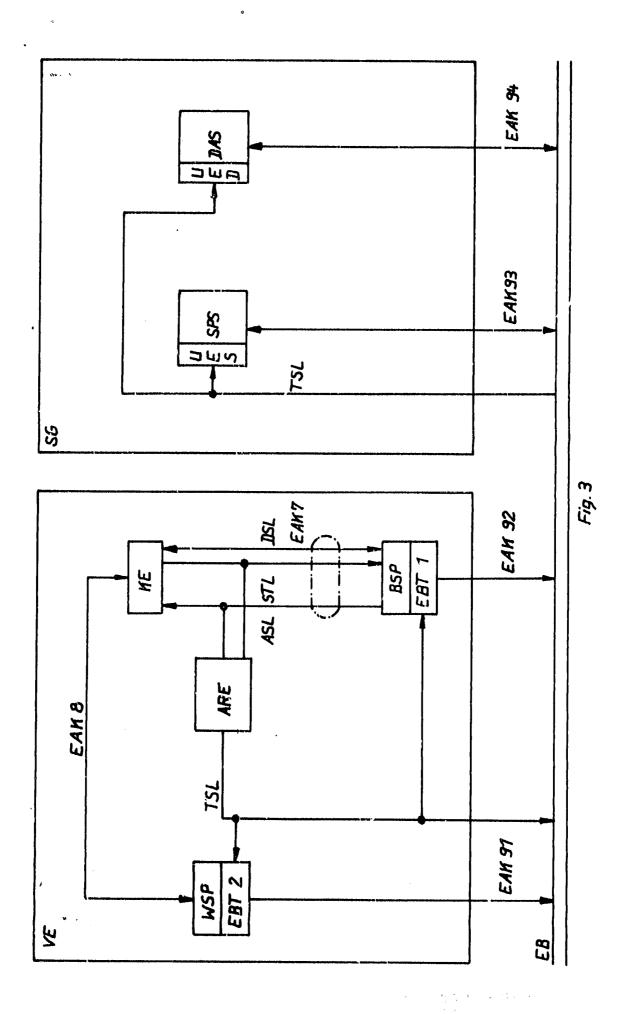

3. Elektrische Programmsteueranordnung zur Steuerung von Maschinen und Prozessen nach Punkt 1 und 2, ge' net dadurch, daß als Zentraleinheit eine aus einem Spezialprozessor (BSP) und einem Standardprozessor (WSP) bestehende Verarbeitungseinheit (VE) und eine aus einem Steuerprogramm- und einem Daten- und Abbildspeicher (SPS; DAS) aufgebaute Speichergruppe (SG) über Ein-/Ausgabekanäle (EAK 91; EAK 92; EAK 93; EAK 94) mit einem Einheitsbus (EB) verbunden sind, wobei von dem durch einen Ein-/ Ausgabekanal (EAK 92) mit dem Einheitsbus (EB) verbundenen und mit einem Einheitsbuskoppeltor (EBT 2) versehenen Spezialprozessor (BSP) der siebente Ein-/Ausgabekanal (EAK 7) einerseits über die Koppeleinheit (KE) und den achten Ein-/Ausgabekanal (EAK 8) zum mit einem Einheitsbuskoppeltor (EBT 1) versehenen Standardprozessor (WSP) führt, sowie andererseits die mit der Steuersignalleitung (STL) und der Aufrufsignalleitung (ASL) verbundene Aufrufeinheit (ARE) durch die ausgangsseitig vorhandene Torsteuersignalleitung (TSL) direkt an die Einheitsbuskoppeltore (EBT 1; EBT 2) und über den Einheitsbus (EB) an die Datenbreiteumschalteinheiten (UES; UED) des Steuerprogrammspeichers (SPS) und des Daten- und Abbildspeichers (DAS) angeschlossen sind, die beide über Ein-/Ausgabekanäle (EAK 93; EAK 94;) mit dem Einheitsbus (EB) gekoppelt sind.

- Hierzu 3 Blatt Zeichnung -

### Titel der Erfindung

Programmsteueranordnung zur Steuerung von Maschinen und Prozessen

Anwendungsgebiet der Erfindung

Die Erfindung bezieht sich auf das Gebiet der elektrischen Steuerungstechnik und ihre Anwendung ist für Maschinen- und Prozeßsteuereinrichtungen möglich und zweckmäßig.

Charakteristik der bekannten technischen Lösungen

Die steuerungstechnische Realisierung komplexer Steuerungsaufgaben erfordert in der Regel die Lösung unterschiedlicher, durch typische Operationen gekennzeichneter Steuerfunktionen bzw. Steueralgorithmen. Neben der Erfassung, Verarbeitung und Bereitstellung rein binärer Informationen, wodurch die benötigten binären Algorithmen realisiert werden, ist die Erfassung und Verarbeitung von Mehrbitinformationen, als auch von in digitale Werte umgewandelten Analoginformationen, mittels wortorientierter Algorithmen für viele Steuerprobleme durchzuführen.

Eine optimale Umsetzung der Steueralgorithmen bezüglich Zeit- und Speicherplatzbedarf wird dann erreicht, wenn die zur Realisierung dieser eingesetzten Verarbeitungseinheiten in ihrem Operations- bzw. Befehlsspektrum den in den Algorithmen auftretenden Operationen, zumindestens den dominierenden Operationen angepaßt sind.

Aus der DE-OS 25 22 343; G 05 B 19/00, ist eine Anordnung zum Steuern und/oder Regeln von Verfahrensabläufen bekannt, bei der Prozessoren, die Daten jeweils unterschiedlichen Informationsgehalts von peripheren Geräten empfangen, aufgrund eines Programms verarbeiten und an periphere Geräte senden, die über einen Programmspeicher miteinander verbunden sind. In diesem Programmspeicher ist das aus den Prozessoren zugeordneten Befehlen bestehende Programm für den Verfahrensablauf gespeichert, zu dem ein Koordinierer den Prozessoren nacheinander Zugriff gibt. Zwischen den beiden Prozessoren besteht programmtechnisch eine klare Trennung, und sie können weitestgehend zeitlich unabhängig voneinander arbeiten, wobei eine Kopplung der beiden Prozessoren ausschließlich über den Programmspeicher erfolgt. Eine besonders günstige Ausführungsform entsteht durch das Anordnen eines Wort- und eines Bitprozessors, wobei der Wortprozessor nur Daten mit einem Informationsgehalt von mehreren Bit (Wörter) von peripheren Geräten empfängt, verarbeitet und aussendet und der Bitprozessor nur Daten mit einem Informationsgehalt von 1 Bit von peripheren Geräten empfängt, verarbeitet und an periphere Geräte aussendet. Für beide Prozessoren sind im Programmspeicher sowohl Wort- als auch

Bitbefehle entweder unabhängig von der Reihenfolge der Abarbeitung oder in getrennten Speicherbereichen untergebracht.

Es können auch nur jeweils Kennzeichen für bestimmte Unterprogramme enthalten sein, die in weiteren, den einzelnen

Prozessoren zugeordneten Speichern abgelegt sind. Von den

Prozessoren hat immer jeweils ein einziger Zugriff zum Speicher.

Nachteilig bei dieser Anordnung ist, daß die Adressierung des Steuerprogrammspeichers ausschließlich mit Hilfe des Wortprozessors erfolgen und auf diese Weise der Wortprozessor nicht für die Realisierung anderer Programmschritte genutzt werden Kann. Der Bit-Prozessor stellt allein eine Verarbeitungseinheit für ausgewählte Befehle dar und hat keinen direkten Zugriff zum Steuerprogrammspeicher.

Weiterhin müssen für jeden Prozessor separate Speicher zur Abspeicherung der von den Prozessoren verarbeitbaren Informationen vorgesehen sein, und die Peripheriebaugruppen sind prozessorbezogen un die jeweiligen Prozessorbusse anzuschliessen. Als Befehlszuordner wird ein besonderer Koordinator benötigt.

# Ziel der Erfindung

Es ist Ziel der Erfindung, mit minimalem Aufwand ein breites Anwendungsgebiet für elektrische Programmsteueranordnungen zu erreichen.

Darlegung des Wesens der Erfindung

Durch die Erfindung wird die Aufgabe gelöst, eine Programmsteuereinrichtung zur Steuerung von Maschinen und Prozessen einer mehrere Prozessoren enthaltenden Verarbeitungseinheit zu schaffen, wobei jeder dieser Prozessoren eine optimale Realisierung von Steuerprogrammen mit unterschiedlichen Operationen und unterschiedlicher Informationsbreite der zu verarbeitenden Informationen ermöglicht.

Das Wesen der Erfindung besteht darin, daß als Zentraleinheit eine Verarbeitungseinheit und eine Zweitorspeichergruppe über Ein-/Ausgabekanäle mit einem Spezialprozessorbus und einem Standardprozessorbus verbunden sind. Die dabei verwendete Verarbeitungseinheit enthält einen als Wortprozessor eingesetzten Standardprozessor und einen als Bitprozessor eingesetzten Spezialprozessor, und die Zweitorspeichergruppe ist aus einem Steuerprogrammspeicher und einem Daten- und Abbildspeicher aufgebaut. An den Standardprozessorbus sind gleichzeitig über weitere Ein-/Ausgabekanäle mit dem Steuerobjekt verbundene Peripheriebaugruppen sowie Speicherbaugruppen angeschlossen. Vom Spezialprozessor, der durch den zweiten Ein-/Ausgabekanal mit dem Spezialprozessorbus gekoppelt ist, besteht über einen siebenten Ein-/Ausgabekanal, eine Koppeleinheit, einen achten und einen ersten Ein-/Ausgabekanal eine Verbindung zum Standardprozessor. Der siebente Ein-/ Ausgabekanal enthält eine Daten- und Steuerleitung, eine Steuersignalleitung und eine Aufrufsignalleitung, wobei an die Steuersignalleitung und an die Aufrufsignalleitung eine Aufrufeinheit angeschlaßen ist. Von dieser Aufrufeinheit führt eine Torsteuersignalleitung zu Wortprozessorkoppeltoren des Steuerprogramm- und des Daten- und Abbildspeichers, die beide über den dritten und vierten Ein-/Ausgabekanal sowohl mit dem Standardprozessor als auch mit dem Spezialprozessorbus gekoppelt sind.

Eine vorteilhafte Erweiterung der Anordnung wird durch den Einsatz eines zweiten Spezialprozessors in der Verarbeitungseinheit erreicht. Weiterhin sind über Ein-/Ausgabekanäle eine erste Zweitorspeichergruppe an einen ersten Spezialprozessorbus und eine zweite Zweitorspeichergruppe an einen zweiten Spezialprozessorbus angeschlossen, wobei beide Zweitorspeichergruppen ebenfalls über Ein-/Ausgabekanäle mit dem Standardprozessor gekoppelt sind. Die beiden Spezialprozessoren besitzen über siebente Ein-/Ausgabekanäle, eine erste und zweite Koppeleinheit, über achte Ein-/Ausgabekanäle sowie den ersten Ein-/Ausgabekanal einen Anschluß an den Standardprozessor.

An den Ausgängen der Ansteuereinheiten führen Torsteuersignalleitungen zu den Wortprozessorkoppeltoren, an die Datenbreiteumschalteinheiten und die Spezialprozessorkoppeltore der Steuerprogramm- und Daten- und Abbildspeicher, die über bin-/Ausgabekanäle sowohl mit dem Standardprozessorbus verbunden sind.

Eine weitere günstige Vereinfachung der Anordnung ergibt sich durch die Verwendung nur eines einzigen Einheitsbusses anstelle des jedem Prozessor getrennt zugeordneten Busses. Als Zentraleinheit sind eine Verarbeitungseinheit mit einem Standard- und einem Spezialprozessor und eine Speichergruppe mit einem Steuerprogramm und einem Daten- und Abbildspeicher über Ein-/Ausgabekanäle mit dem Einheitsbus verbunden. Vom Spezialprozessor, der durch ein ausgangsseitig vorhandenes Einheitsbuskoppeltor und über einen Ein-/Ausgabekanal mit dem Einheitsbus gekoppelt ist, gibt es über den siebenten Ein-/Ausgabekanal, die Koppeleinheit und den achten Ein-/Ausgabekanal einen Anschluß an den Standardprozessor, der ebenfalls durch ein ausgangsseitig vorhandenes Einheitsbuskoppeltor und einen Ein-/Ausgabekanal mit dem Einheitsbus verbunden ist.

Weiterhin führt von der Aufrufeinheit eine Torsteuersignalleitung direkt an die Einheitsbuskoppeltore und über den Einheitsbus an die Datenbreiteumschalteinheiten des Steuerprogramm- und des Daten- und Abbildspeichers, die beide über Ein-/ Ausgabekanäle an den Einheitsbus angeschlossen sind.

# Ausführungsbeispiel

ţ

1

Die Erfindung soll nachstehend an einem Ausführungsbeispiel näher erläutert werden. In der zugehörigen Zeichnung zeigen:

- Fig. 1: das Blockschaltbild der Zentraleinheit der elektrischen Programmsteueranordnung

- Fig. 2: ein Blockschaltbild der Erweiterung der Anordnung

- Fig. 3: eine Anordnung mit einem gemeinsamen Bus

In Fig. 1 ist das Blockschaltbild einer elektrischen Programmsteueranordnung zur Steuerung von Maschinen und Prozessen dargestellt, die mehrere Prozessoren und Schnittstellen enthält. An einem Standardprozessorbus WSB und an einen Spezialprozessorbus BSB sind über Ein-/Ausgabekanäle EAK 1; EAK 2; EAK 3; EAK 4 eine Verarbeitungseinheit VE und eine Zweitorspeichergruppe ZSG angschlossen, wobei der erste Ein-/Ausgabekanal EAK 1 den Standardprozessorbus WSB mit einem als Wortprozessor eingesetzten Standardprozessor WSP, der zweite Ein-/Ausgabekanal EAK 2 den Spezialprozessorbus BSB mit einem als Bitprozessor eingesetzten Spezialprozessor BSP, der dritte Ein-/Ausgabekanal EAK 3 den Standprozessorbus WSB mit einem Steuerprogramm- und einem Daten- und Abbildspeicher SPS; DAS und der vierte Ein-/Ausgahekanal EAK 4 den Spezialprozessorbus BSB mit dem Steuerprogramm- und dem Daten- und Abbildspeicher DAS verbindet. Ober fünfte und sechste Ein-/Ausgabekanäle EAK 5; EAK 6 sind an den Standardprozessorbus WSB mit dem Steuerobjekt SO verbundene Peripheriebaugruppen PB und zusätzliche Speicherbaugruppen SB angeschlossen, zu denen nur der Standardprozessor WSP Zugriff hat. In der Verarbeitungseinheit VE ist der Spezialprozessor BSP über einen siebenten Ein-/Ausgabekanal EAK 7, eine Koppeleinheit KE und einem achten Ein-/Ausgabekanal EAK 8, der mit dem Standardprozessorbus WSB identisch sein kann, an den Standardprozessor WSP angeschlossen.

Der siebente Ein-/Ausgabekanal EAK 7 besteht aus einer Daten- und Steuerleitung DSL zum Zugriff und zum Datentransport des Standardprozessors WSP zum Programmzähler des Spezialprozessors BSP, einer Steuersignalieitung STL zur Zustandssetzung des Spezialprozessors BSP durch den Standardprozessor WSP bezüglich START/STOP und einer Aufrufsignalleitung ASL zum Aufruf des Standardprozessors WSP, wobei an die Steuersignal- und die Aufrufsignalleitung STL; ASL eine Aufrufeinheit ARE angeschlossen ist. Zum Übertragen des Torsteuersignales TSS führt eine Leitung TSL vor der Aufrufeinheit ARE zu den Standardprozessorkoppeltoren WPT 1; WPT 2 zu den Spezialprozessorkoppeltoren BPT 1; BPT 2 und an die Datenbreiteumschalteinheiten UES; DAS, die über den dritten und vierten Ein-/Ausgabekanal EAK 3, EAK 4 sowohl mit dem Standardprozessorbus WSB als auch mit dem Spezialprozessorbus BSB verbunden sind. Die Koppeleinheit KE bildes ein adressierbares Ein-/Ausgabetor für den Standardprozessor WSP und ist weiterhin so ausgelegt, daß sie beim Aufruf des Standardprozessors WSP über die Aufrufsignalleitung ASK ein Interruptanforderungssignal als Bestandteil des achten Ein-/ Ausgabekanals EAK 8 für den Standardprozessor WSP erzeugt.

In Fig. 2 ist als Blockschaltbild eine Möglichkeit zur Erweiterung der Programmsteueranordnung dargestellt. Die Verarbeitungseinheit VE enthält dazu einen ersten und zweiten Spezialprozessor BSP 1; BSP 2, die einerseits über getrennte Ein-/Ausgabekanäle EAK 21; EAK 22 mit einem ersten und einem zweiten Spezialprozessorbus BSB 1; BSB 2 und andererseits über Ein-/Ausgabekanäle EAK 81; EAK 82 und einer ersten und zweiten Koppeleinheit KE 1; KE 2 mit dem ersten Ein-/Ausgabekanal EAK 1 verbunden sind. An die Steuersignal- und die Aufrufleitungen ASL 1; ASL 2; STL 1; STL 2 sind eine erste und zweite Aufrufeinheit ARE 1; ARE 2 angeschlossen. Weiterhin sind in der erweiterten Anordnung eine erste und zweite Zweitorspeichergruppe ZSG 1; ZSG 2 vorhanden, die über Ein-/Ausgabekanäle EAK 31; EAK 32; EAK 41; EAK 42 mit dem Stan-

dardprozessorbus WSB und dem ersten bzw. zweiten Spezialprozessorbus BSB 1; BSB 2 gekoppelt sind. Von den Aufrufeinheiten ARE 1; ARE 2 führen zum Übertragen der Torsteuersignale TSS 1; TSS 2 Leitungen zu den Standardprozessorkoppeltoren WPT 11; WPT 12; WPT 21; WPT 22 zu den Spezialprozessorkoppeltoren BPT 11; BPT 12; BPT 21; BPT 22 und zu den Datenbreiteumschalteinheiten UES 1; UED 1; UES 2; UED 2 der ersten und zweiten Zweitorspeichergruppe ZSG 1; ZSG 2.

Fig. 3 zeigt eine Lösungsvariante, bei der nur ein einziger Einheitsbus EB verwendet wird. An diesen Einheitsbus EB sind direkt die Aufrufeinheit ARE, der Standardprozessor WSP und der Spezialprozessor BSP angeschlossen, wobei die Verbindung der Prozessoren zum Bus über in diesen ausgangsseitig enthaltenen Einheitsbuskoppeltore EBT 1; EBT 2 erfolgt. Weiterhin ist eine Speichergruppe SG angeordnet, deren Steuerprogrammspeicher SPS und Daten- und Abbildspeicher DAS mit dem Einheitsbus EB verbunden sind. Über den Einheitsbus EB sind die in Steuerprogramm- und Daven- und Abbildspeicher SPS; DAS enthaltenen Datenbreitumschalteinheiten UES; UED an die Aufrufeinheit ARE angeschlossen.

Die Anordnung arbeitet auf folgende Weise:

Mit der Zuschaltung bzw. dem Start der Anordnung wird über eine Einschaltroutine des Standardprozessors WSP ein Grundzustand der Anordnung initialisiert, der unter anderem den Spezialprozessor BSP über die Steuersignalleitung STL mit STOP beauflagt und damit das Torsteuersignal TSS so festlegt, daß über das erste und zweite Standardprozessorkoppeltor WPT 1; WPT 2 und das erste und zweite Spezialprozessorkoppeltor BPT 1; BPT 2 der Zweitorspeichergruppe ZSG der Standardprozessor WSP zugeordnet wird. Die Bildung des Torsteuersignales TSS erfolgt gleichzeitig über den Zustand der Aufrufsignale AS und der Steuersignale ST. Wenn beispielsweise das Torsteuer-

signal TSS den Zustand "High" annimmt, dann sind die Standar Jprozessorkoppeltore WPT 1; WPT 2 auf Durchgang geschaltet und die Spezialprozessorkoppeltore BPT 1; BPT 2 hochohmig. In diesem Zustand hat der Standardprozessor WSP Zugriff zur Zweitorspeichergruppe ZSG und der Spezialprozessor BSP ist abgetrennt. Wenn sich das Torsteuersignal TSS danach im "Low" - Zustand befindet, dann kehren sich die Verhältnisse an den Koppeltoren um und der Spezialprozessor SP hat Zugriff zur Zweitorspeichergruppe ZSG. Parallel dazu werden mit Hilfe des Torsteuersignales TSS auch die Datenbreiteumschalteinheiten UES; UED in der Zweitorspeichergruppe ZSG angesteuert und die Speicherorganisation der Datenbreite des Prozessors angepaßt, der in dieser Zeit Zugriff zur Zweitorspeichergruppe ZSG besitzt. Nach dem Durchführen dieses Umschaltens der Zentraleinheit von wortorientiert auf bitorientiert durch den Wechsel des Zugriffes der einzelnen Prozessoren zur Zweitorspeichergruppe ZSG, kann der Standardprozessor WSP in seiner Datenbreite den Daten- und Abbildspeicher DAS mit aktuellen Informationen des Steuerobjektes SO füller und anschließend über die Daten- und Steuerleitung OSL dem Spezialprozessor BSP eine Anfangsadresse zur Abarbeitung des im Steuerprogrammspeichers abgelegten Steuerprogrammes vorgeben. Mit einem über die Steuersignalleitung STL ausgelöstem START des Spezialprozessors BSP sowie der damit über das Torsteuersignal TSS verbundenen Zuordnung des Steuerprogrammund des Daten- und Abbildspeichers SPS; DAS zum Spezialprozessor, beginnt der Spezialprozessor BSP mit der Umsetzung des Steuerprogrammes. In diesem Zustand kann dann gleichzeitig der Standardprozessor WSP in Verbindung mit der ihm zugeordneten Speicherbaugruppe SB und den ihm zugeordneten Peripheriebaugruppen PB parallel zum aktiven Spezialprozessor BSP noch zusätzliche Programme bzw. Aufgaben realisieren. Mit der Decodierung eines Zusatzbefehles, der als Folge im Steuerprogramm des Steuerprogrammspeichers SPS Programmkomplexe oder Anweisungen anzeigt, die vom Standardprozessor WSP effektiv realisierbar sind, geht der Spezialprozessor BSP in den HALT und über die

(

Aufrufsignalleitung ASL und die Koppeleinheit KE erfolgt ein Aufruf des Standardprozessors WSP im Sinne einer Interruptanforderung. Parallel dazu wird über die Torsteuerleitung TSL die Zustandssteuerung der Standardprozessorkoppeltore WPT 1; WPT 2 und der Spezialprozessorkoppeltore BPT 1; BPT 2 sowie mittels der Datenbreiteumschalteinheiten UES; UED die Umschaltung der Speicherorganisation der Zweitorspeichergrupp: ZSG durchgeführt, so daß diese vom Spezialprozessorbus BSB und damit vom Spezialprozessor BSP abgetrennt wird und der Standardprozessor WSP entsprechend seiner Datenbreite Zugriff zur Zweitorspeichergruppe ZSG hat. Mit der Interruptanforderung über die Aufrufleitung ASL unterbricht der Standardprozessor WSP sein Eigenprogramm, hebt über die Daten- und Steuerleitung DSL die aktuelle Adresse der Programmabarbeitung des Steuerprogrammspeichers ab und übernimmt die Abarbeitung der ihm zugewiesenen Programmkomplexe bzw. Anweisungen des Steuerprogrammspeichers SPS bis zum nächsten Zusatzbefehl. In diesem Regime wird das Steuerprogramm des Steuerprogrammspeichers SPS, das entsprechend des zu lösenden Steuerungsproblems sowohl Anweisungen bzw. Programmkomplexe für den Standardprozessor WSP als auch Anweisung bzw. Programmkomplexe für den Spezialprozessor BSP enthält, verschachtet und sequentiell durch den Standard- und den Spezialprozessor WSP; BSP umgesetzt. Nach der vollständigen Abarbeitung des Programmes, das durch eine dem Standardprozessor WSP zugeordnete Anweisung wie Programmende oder Ein-/Ausgaberoutine gekennzeichnet ist, führt der Standardprozessor WSP über die Peripheriebaugruppen PB einen Informationsaustausch mit dem Steuerobjekt SO durch, und der Zyklus wird nun gestartet. Zu den Peripheriebaugruppen können auch eigenständige Funktionsbaugruppen, wie beispielsweise Zähler, Reglerbaugruppen und Anschlußsteuerungen zur Kopplung mit Rechner und/oder anderen Automatisierungseinrichtungen, gehören. Die Kommunikation des Standardprozessors WSP mit den Peripheriebaugruppen PB kann sowohl mittels zyklischer Abfrage als auch auf Interruptbasis erfolgen. Noch effektiver kann der Funktionsablauf durch die in Fig. 2 dargestellte Erweiterungsmöglichkeit dieser Grundanordnung gestaltet werden, die

aus der Kombination des Standardprozessors WSP mit zwei Spezialprozessoren BSP 1, BSP 2 besteht. Dabei können die Spezialprozessoren BSP 1, BSP 2 vom gleichen Typ oder für unterschiedliche Algorithmen ausgelegt sein. Den Spezialprozessoren BSP 1, BSP 2 werden nur die Programmkomplexe entzogen, die vom Standardprozessor WSP effektiver realisierbar sind. Jedem Spezialprozessor BSP 1, BSP 2 sind getrennt eine Zweitorspeichergruppe ZSG 1, ZSG 2 mit den zugehörigen Steuerspeichern SPS 1, SPS 2 und Daten- und Abbildspeichern DAS 2, DAS 2 zugeordnet, zu denen sowohl der Standardprozessor WSP über den Standardprozessorbus WSB als auch die Spezialprozessoren BSP 1, BSP 2 über die zugehörigen Spezialprozessorbusse BSB 1, BSB 2 Zugriff haben. Die Steuerung der Speicherzuordnung über die Koppeltore WPT 11, WPT 12, WPT 21, WPT 22 bzw. BPT 11, BPT 12, BPT 21, BPT 22 und das Zusammenwirken des Standardprozessors WSP mit den Spezialprozessoren BSP 1, BSP 2 können analog wie für die Grundanordnung beschrieben durchgeführt werden, wobei vorteilhafterweise der Aufruf des Standardprozessors WSP über die Aufrufsignalleitung ASL 1, ASL 2 auf Interruptbasis durch Prioritätssteuerung erfolgen sollte.

Bei der in Fig. 3 dargestellten Variante der Grundanordnung erfolgt sowohl der Zugriff des Standardprozessors WSP als auch des Spezialprozessors BSP zur Speichergruppe SG über einen einzigen Einheitsbus EB. Im Steuerprogrammspeicher SPS sind ebenfalls solche Algorithmenkomplexe enthalten, die vom Standardprozessor WSP und vom Spezialprozessor BSP wechselweise abgearbeitet werden. Die Zuordnung der Speichergruppe SG über den Einheitsbus EB zum Wort- und Spezialprozessor WSP, BSP wird durch die ausgangsseitig in den Prozessoren vorhandenen Einheitsbustore EBT 1, EBT 2 gesteuert. Parallel dazu geschieht die Anpassung der Speicherorganisatoren an die Datenbreite der Prozessoren WSP, BSP mit Hilfe der Torsteuersignalleitung TSL über den Einheitsbus EB.

Durch die wechselweise Abarbeitung des Steuerprogrammes in einem Standardprozessor und einem Spezialprozessor ist eine optimale Umsetzung von unterschiedlichen Algorithmen bzw. Anweisungen möglich. Besonders vorteilhaft ist es, daß ein gemeinsames Abspeichern der prozeßabbildenden Informationen und der im Verlaufe der Steuerprogrammumsetzung gewonnenen Zwischen- und Ergebnisinformationen durchgeführt wird und jeder Prozessor zu diesen Informationen uneingeschränkt Zugriff hat, wobei der Informationsaustausch zu den Peripheriebaugruppen mit der Datenbreite des Standardprozessors und nur von diesem erfolgen kann. Eine Unterteilung und Zuordnung der Peripheriebaugruppen und damit der externen Informationen zu den einzelnen Prozessoren ist nicht erforderlich. Ein weiterer wesentlicher Vorteil liegt in der möglichen Parallelarbeit beider Prozessoren. Aufgrund der autonomen, ohne Hilfeleistung des Standardprozessors möglichen Umsetzung von zugewiesenen Programmkomplexen im SPezialprozessor kann der Standardprozessor Zusatzaufgaben in Form von Hintergrundprogrammen übernehmen, wobei ein Unterbrechen nur bei notwendigen Aktivitäten am gemeinsam umzusetzenden Steuerprogramm erfolgen muß.