(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

G11C 16/06 (2006.01)

(45) 공고일자

2007년04월04일

(11) 등록번호

10-0704028

(24) 등록일자

2007년03월29일

(21) 출원번호 10-2005-0094848

(22) 출원일자 2005년10월10일

심사청구일자 2005년10월10일

(65) 공개번호 10-2006-0052142

(43) 공개일자 2006년05월19일

(30) 우선권주장 1020040086450 2004년10월28일 대한민국(KR)

1020040086451 2004년10월28일 대한민국(KR)

(73) 특허권자 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 이성수

경기 성남시 분당구 금곡동 분당두산위브아파트 109-1304

임영호

경기 용인시 구성면 보정리 1161번지 삼성수지5차 아파트 512동1201

호

채동혁

서울 관악구 신림9동 건영3차아파트 1동 405호

조현철

경기 용인시 풍덕천동 신정마을 현대성우아파트 808동 101호

(74) 대리인 곽덕영

(56) 선행기술조사문현

KR1019960042756 A

KR1019970008206 A

KR1020020080917 A

KR1020040004976 A

KR1020050095191 A

US5761131 A

US6614691 B2

\* 심사관에 의하여 인용된 문현

심사관 : 조명관

전체 청구항 수 : 총 81 항

(54) 페이지 버퍼 및 페이지 버퍼를 포함하는 불휘발성 메모리장치

(57) 요약

본 발명의 일면에서, 프로그램 모드 및 독출 모드에서 실시 가능한 불휘발성 메모리 장치가 게시된다. 상기 메모리 장치는 복수개의 불휘발성 메모리 셀들, 복수개의 워드라인들 및 복수개의 비트라인들을 가지는 메모리셀 어레이를 구비한다. 상기 메모리 장치는 상기 메모리 어레이의 상기 비트라인들로부터 독출되는 데이터를 출력하기 위한 내부 데이터 출력 라인 및 상기 메모리셀 어레이의 비트라인과 상기 내부 데이터 출력 라인 사이에 기능적으로 연결되는 페이지 버퍼를 더 구비한다. 상기 페이지 버퍼는 상기 비트라인에 선택적으로 연결되는 센싱 노드, 상기 센스노드에 선택적으로 연결되는 래치 노드를 가지는 래치회로, 프로그래밍 모드 및 독출 모드에서 상기 래치 노드의 논리전압을 설정하는 래치입력패스 및 상기 래치입력패스와 격리되며, 상기 래치 노드의 상기 논리전압에 따라서 상기 내부 데이터 출력 라인의 논리전압으로 설정하는 래치출력패스를 구비한다.

## 대표도

도 11

### 특허청구의 범위

#### 청구항 1.

프로그램 모드 및 독출 모드로 동작 가능한 불휘발성 메모리 장치에 있어서,

복수개의 불휘발성 메모리셀들, 복수개의 워드라인들 및 복수개의 비트라인들을 가지는 메모리셀 어레이;

상기 메모리셀 어레이의 비트라인들로부터 독출(read)되는 데이터를 출력하기 위한 내부 데이터 출력 라인; 및

상기 메모리셀 어레이와 상기 내부 데이터 출력 라인 사이에 전송되는 데이터를 임시적으로 저장하는 연결되는 페이지 버퍼를 구비하며,

상기 페이지 버퍼는

상기 비트라인에 선택적으로 연결되는 센싱 노드;

상기 센싱 노드에 선택적으로 연결되는 래치 노드를 가지는 래치 회로;

상기 래치 노드의 논리 전압을 설정하는 래치 입력 패스; 및

상기 래치 입력 패스로부터 격리되며, 상기 래치 노드의 상기 논리 전압에 따른 상기 내부 데이터 출력 라인의 논리 전압을 설정하는 래치 출력 패스를 구비하는 것을 특징으로 하는 불휘발성 메모리 장치.

#### 청구항 2.

제1 항에 있어서, 상기 내부 데이터 출력 라인은 상기 래치 노드로부터 전기적으로 분리되는 것을 특징으로 하는 불휘발성 메모리 장치.

#### 청구항 3.

제2 항에 있어서, 상기 내부 데이터 출력 라인은 상기 래치 노드의 논리 전압에 따라서 제1 기준 전위에 선택적으로 연결되는 것을 특징으로 하는 불휘발성 메모리 장치.

#### 청구항 4.

제3 항에 있어서, 상기 제1 기준 전위와 상기 내부 데이터 출력 라인 사이에 직렬적으로 연결되는 제1 트랜지스터를 더 구비하며, 상기 제1 트랜지스터의 게이트는 상기 래치 노드에 연결되는 것을 특징으로 하는 것을 불휘발성 메모리 장치.

### 청구항 5.

제4 항에 있어서, 상기 제1 트랜지스터와 상기 내부 데이터 출력 라인 사이에 직렬적으로 연결되는 제2 트랜지스터를 더 구비하는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 6.

제5 항에 있어서, 글로벌 데이터 버스를 더 구비하며,

상기 내부 데이터 출력 라인은 제3 트랜지스터를 통하여, 상기 글로벌 데이터 버스에 선택적으로 연결되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 7.

제6 항에 있어서, 상기 제2 및 제3 트랜지스터의 각각의 도전 상태들은 비트라인 어드레스 신호들에 의해 제어되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 8.

제4 항에 있어서, 상기 래치 입력 패스는 상기 래치 노드와 제2 기준 전위 사이에 직렬적으로 연결되는 제2 트랜지스터에 의해 적어도 부분적으로 정의되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 9.

제8 항에 있어서, 상기 제2 트랜지스터의 도전 상태는 데이터 입력 신호에 의해 제어되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 10.

제9 항에 있어서,

상기 데이터 입력 신호는 내부 데이터 입력 신호이고,

상기 메모리 장치는 비트라인 어드레스 신호와 외부 데이터 입력신호를 수신하고, 상기 내부 데이터 신호를 출력하는 디코더 회로를 더 구비하는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 11.

제10 항에 있어서, 글로벌 데이터 버스를 더 구비하며,

상기 내부 데이터 출력 라인은 제3 트랜지스터를 통하여, 상기 글로벌 데이터 버스에 선택적으로 연결되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 12.

제11 항에 있어서, 상기 제3 트랜지스터의 도전 상태는 상기 디코더 회로의 출력에 의해 제어되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 13.

제10 항에 있어서,

상기 내부 데이터 입력 신호는 상기 디코더 회로에 의해 내부 데이터 입력 라인 상에 출력되며,

상기 내부 데이터 입력 라인은 상기 내부 데이터 출력 라인으로부터 전기적으로 분리되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 14.

제1 항에 있어서, 불휘발성 메모리 셀들은 플래시 메모리 셀들인 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 15.

제1 항에 있어서, 상기 메모리 셀 어레이는 낸드(NAND) 타입의 플래시 메모리 셀 어레이인 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 16.

불휘발성 메모리 장치에 있어서,

복수개의 불휘발성 메모리 셀들을 포함하는 메모리 셀 어레이;

상기 메모리 셀 어레이의 상기 불휘발성 메모리 셀들로부터 독출(read)되는 데이터 및 상기 메모리 셀 어레이의 상기 불휘발성 메모리 셀들에 프로그램되는 데이터를 임시적으로 저장하기 위한 래치 회로를 포함하는 페이지 버퍼;

상기 메모리 셀 어레이로부터 독출(read)되어 상기 페이지 버퍼에 임시적으로 저장되는 데이터를 출력하는 내부 데이터 출력 라인; 및

상기 내부 데이터 출력 라인으로부터 격리되는 래치 입력 패스로서, 데이터가 상기 메모리 셀 어레이의 상기 불휘발성 메모리 셀들로 프로그램될 때 및 상기 메모리 셀 어레이의 상기 불휘발성 메모리 셀들로부터 독출(read) 될 때, 상기 래치 회로를 설정하는 상기 래치 입력 패스를 구비하는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 17.

제16 항에 있어서, 상기 래치 입력 패스는 상기 내부 데이터 출력 라인으로부터 전기적으로 분리되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 18.

제16 항에 있어서, 상기 내부 데이터 출력 라인은 상기 래치 노드의 논리 전압에 따라서 제1 기준 전위에 선택적으로 연결되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 19.

제18 항에 있어서, 글로벌 데이터 버스를 더 구비하며,

상기 내부 데이터 출력 라인은 어드레스 신호에 따라서 상기 글로벌 데이터 버스에 선택적으로 연결되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 20.

제19 항에 있어서, 상기 메모리셀 어레이에는 복수개의 비트라인들을 구비하며, 상기 어드레스 신호는 비트라인 어드레스 신호인 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 21.

제20 항에 있어서, 상기 비트라인 어드레스 신호를 수신하며, 상기 글로벌 데이터 버스의 상기 내부 데이터 출력 라인으로의 선택적인 연결을 제어하는 디코더 회로를 더 구비하는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 22.

제21 항에 있어서, 상기 디코더 회로는 외부 데이터 입력신호를 더 수신하고, 내부 데이터 입력신호를 출력하며,

상기 래치 입력 패스는 상기 내부 데이터 입력 신호에 의해 제어되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 23.

제16 항에 있어서, 상기 불휘발성 메모리 셀들은 플래시 메모리 셀들인 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 24.

제16 항에 있어서, 상기 메모리셀 어레이에는 낸드(NAND) 타입의 플래시 메모리셀 어레이인 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 25.

불휘발성 메모리 장치에 있어서,

복수개의 불휘발성 메모리 셀들을 포함하는 메모리셀 어레이;

상기 메모리 셀 어레이의 불휘발성 메모리 셀들로 프로그램되는 데이터를 입력하는 입력 데이터 버스;

상기 입력 데이터 버스로부터 격리되며, 상기 메모리 셀 어레이의 상기 불휘발성 메모리 셀들로부터 독출(read)되는 출력 데이터 버스;

상기 메모리 셀 어레이의 상기 불휘발성 메모리 셀들로부터 독출(read)되는 데이터 및 상기 불휘발성 메모리 셀들로 프로그램되는 데이터를 일시적으로 저장하기 위한 래치 회로;

상기 출력 데이터 버스에 연결되는 내부 데이터 출력 라인;

상기 입력 데이터 버스에 연결되는 래치 입력 버스로서, 데이터가 상기 메모리 셀 어레이의 상기 불휘발성 메모리 셀들로 프로그램될 때, 상기 래치 회로를 설정하는 상기 래치 입력 패스; 및

상기 래치 회로에 일시적으로 저장된 독출 데이터(read data)를 상기 내부 데이터 출력 라인으로 전송하는 출력 드라이브 회로를 구비하는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 26.

제25 항에 있어서, 상기 출력 드라이브 회로는 상기 래치 회로의 래치 노드에 의해 게이팅되는 스위칭 회로를 포함하는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 27.

제26 항에 있어서,

상기 래치 입력 패스는 내부 데이터 입력 라인의 내부 데이터 입력신호들에 의해 제어되며,

상기 내부 데이터 입력 라인은 상기 내부 데이터 출력 라인으로부터 전기적으로 분리되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 28.

제25 항에 있어서, 상기 메모리 셀은 플래시 메모리 셀들인 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 29.

제25 항에 있어서, 상기 메모리 셀 어레이는 낸드(NAND) 타입의 플래시 메모리 셀 어레이인 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 30.

불휘발성 메모리 장치에 있어서,

복수개의 불휘발성 메모리 셀들, 복수개의 워드라인들 및 복수개의 비트라인들을 포함하는 메모리 셀 어레이;

내부 데이터 출력 라인; 및

상기 메모리셀 어레이와 상기 내부 데이터 출력 라인에 연결되는 복수개의 페이지 버퍼들로서, 복수개의 병치(並置)되는 페이지 버퍼들을 정의하기 위해 순차적으로 배열되는 상기 복수개의 페이지 버퍼들을 구비하며,

상기 페이지 버퍼들의 각각은

상기 메모리셀 어레이로부터 독출(read)되는 데이터를 임시적으로 저장하는 래치 회로; 및

상기 래치 회로와 상기 내부 데이터 출력 라인 사이에 연결되는 어드레스 케이트를 포함하며,

상기 어드레스 케이트는 상기 내부 데이터 출력 라인으로 상기 각 페이지 버퍼의 래치 회로로부터의 데이터를 선택적으로 출력하기 위하여 어드레스 신호에 응답하는 것을 특징으로 하는 불휘발성 메모리 장치.

**청구항 31.**

제30 항에 있어서, 상기 페이지 버퍼영역은 주어진 방향에 순차적으로 적층되며, 상기 내부 데이터 출력 라인은 상기 주어진 방향으로 길게 확장되는 것을 특징으로 하는 불휘발성 메모리 장치.

**청구항 32.**

제31 항에 있어서, 상기 비트라인들은 상기 주어진 방향으로 길게 확장되는 것을 특징으로 하는 불휘발성 메모리 장치.

**청구항 33.**

제31 항에 있어서, 상기 어드레스 신호는 상기 페이지 버퍼의 어드레스 케이트로 직접적으로 인가되는 것을 특징으로 하는 불휘발성 메모리 장치.

**청구항 34.**

제31 항에 있어서, 상기 페이지 버퍼들에 연결되는 복수개의 내부 데이터 입력 라인들을 더 구비하며,

상기 내부 데이터 입력 라인들은 상기 내부 데이터 출력 라인으로부터 전기적으로 분리되는 것을 특징으로 하는 불휘발성 메모리 장치.

**청구항 35.**

제31 항에 있어서, 상기 메모리 셀들은 플래시 메모리 셀들인 것을 특징으로 하는 불휘발성 메모리 장치.

**청구항 36.**

제31 항에 있어서, 상기 메모리셀 어레이는 낸드(NAND) 타입의 플래시 메모리셀 어레이로 이루어진 것을 특징으로 하는 불휘발성 메모리 장치.

**청구항 37.**

불휘발성 메모리 장치에 있어서,

복수개의 불휘발성 메모리 셀들, 복수개의 워드라인들 및 제1 방향으로 길게 확장되는 복수개의 비트라인들을 포함하는 메모리 셀 어레이;

상기 메모리 셀 어레이로부터 독출(read)되는 데이터를 출력하는 공유된 내부 데이터 출력 라인; 및

상기 메모리 셀 어레이와 상기 공유된 내부 데이터 출력 라인 사이에 각각 기능적으로 연결되는 복수개의 페이지 버퍼들로서,

상기 복수개의 페이지 버퍼들은 제1 방향으로 병치(竝置)된 대응하는 복수개의 페이지 버퍼 영역들을 정의하기 위해 순차적으로 배열되고, 상기 내부 데이터 출력 라인은 인접한 상기 복수개의 페이지 버퍼들의 상기 제1 방향으로 길게 확장되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 38.

제37 항에 있어서, 상기 복수개의 내부 데이터 입력 라인들과 상기 공유된 내부 데이터 출력 라인에 연결되는 디코더 회로를 더 구비하는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 39.

제38 항에 있어서, 상기 디코더 회로는

어드레스 신호 및 데이터 입력 신호를 수신하고, 상기 어드레스 신호 및 상기 데이터 입력 신호에 따라서 상기 내부 입력 데이터를 상기 복수개의 내부 데이터 입력 라인들 상에 출력하는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 40.

제39 항에 있어서, 상기 디코더 회로는

상기 어드레스 신호에 따라 상기 공유된 내부 데이터 출력 라인을 글로벌 출력 라인에 선택적으로 연결하는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 41.

제37 항에 있어서, 상기 메모리 셀들은 플래시 메모리 셀들인 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 42.

제37 항에 있어서, 상기 메모리 셀 어레이는 낸드(NAND) 타입의 플래시 메모리 셀 어레이인 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 43.

불휘발성 메모리 장치에 있어서,

복수개의 불휘발성 메모리 셀들을 포함하는 메모리셀 어레이;

로컬(local) 데이터 입력 라인과 래치 회로를 포함하는 페이지 버퍼로서, 상기 래치 회로는 상기 메모리셀 어레이의 상기 불휘발성 메모리 셀들로부터의 독출(read)되는 데이터 및 상기 불휘발성 메모리셀에 프로그램되는 데이터를 임시적으로 저장하도록 상기 로컬 데이터 입력 라인에 응답하는 상기 페이지 버퍼;

외부 입력신호들을 공급하는 글로벌 데이터 입력 라인으로서, 상기 외부 입력 신호들은 상기 메모리셀 어레이를 프로그램하기 위한 프로그래밍 신호들과 상기 메모리셀 어레이를 독출(read)하기 위한 제어신호들을 포함하는 상기 글로벌 데이터 입력 라인; 및

게이트 회로로서, 상기 게이트 회로에 공급되는 어드레스 신호에 따라 상기 로컬 데이터 입력 라인으로 상기 외부 입력 신호들을 선택적으로 출력하는 상기 게이트 회로를 구비하는 것을 특징으로 하는 불휘발성 메모리 장치.

#### 청구항 44.

제43 항에 있어서, 상기 로컬 데이터 입력 라인은 상기 페이지 버퍼의 상기 래치 회로의 래치 상태를 제어하는 것을 특징으로 하는 불휘발성 메모리 장치.

#### 청구항 45.

제44 항에 있어서,

상기 로컬 데이터 입력 라인은 상기 래치 회로의 제1 래치 노드와 기준 전위 사이에 직렬적으로 연결되는 제1 트랜지스터의 게이트에 연결되는 제1 로컬 입력 라인과, 상기 래치 회로의 제2 패치 노드와 상기 기준 전위 사이에 직렬적으로 연결되는 제2 트랜지스터의 게이트에 연결되는 제2 로컬 입력 라인을 포함하는 것을 특징으로 하는 불휘발성 메모리 장치.

#### 청구항 46.

제45 항에 있어서, 상기 기준 전위와 상기 제1 및 제2 트랜지스터들 각각 사이에 직렬적으로 연결되는 제3 트랜지스터를 더 구비하며,

상기 제3 트랜지스터의 게이트는 제1 어드레스 신호 라인에 연결되는 것을 특징으로 하는 불휘발성 메모리 장치.

#### 청구항 47.

제46 항에 있어서, 상기 게이트 회로는 제2 어드레스 신호 라인에 연결되는 디코더 회로의 일부를 형성하는 것을 특징으로 하는 불휘발성 메모리 장치.

#### 청구항 48.

제44 항에 있어서, 상기 메모리 셀은 플래시 메모리셀들인 것을 특징으로 하는 불휘발성 메모리 장치.

#### 청구항 49.

제44 항에 있어서, 상기 메모리셀 어레이는 낸드(NAND) 타입의 플래시 메모리셀 어레이인 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 50.

불휘발성 메모리 장치에 있어서,

복수개의 불휘발성 메모리 셀들, 복수개의 워드라인들 및 복수개의 비트라인들을 가지는 메모리셀 어레이;

상기 메모리셀 어레이로부터 독출(read)되는 데이터를 출력하는 내부 데이터 출력 라인;

상기 메모리셀 어레이와 상기 내부 데이터 출력 라인 사이에 기능적으로 연결되는 복수개의 페이지 버퍼들; 및

상기 복수개의 페이지 버퍼들의 적어도 하나의 게이트 회로에 기능적으로 연결되는 복수개의 어드레스 라인들을 구비하는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 51.

제50 항에 있어서, 상기 적어도 하나의 게이트 회로는 제1 어드레스 게이트를 포함하며,

상기 페이지 버퍼들 각각은 상기 메모리셀 어레이로부터 독출(read)되는 데이터를 일시적으로 저장하는 래치 회로와, 제1 기준전위와 상기 내부 데이터 출력 라인 사이에 연결되는 어드레스 게이트를 포함하며,

각 페이지 버퍼를 통해 확장되는 상기 어드레스 라인은 상기 각 페이지 버퍼의 상기 제1 어드레스 게이트에 연결되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 52.

제51 항에 있어서,

상기 적어도 하나의 게이트 회로는 상기 래치 회로와 제2 기준전위 사이에 연결된 제2 어드레스 게이트를 더 구비하며,

각 페이지 버퍼를 통해 확장되는 상기 어드레스 라인은 상기 각 페이지 버퍼의 상기 제2 어드레스 게이트에 더 연결되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 53.

제50 항에 있어서,

상기 페이지 버퍼들은 제1 방향으로 병치(竝置)된 대응하는 복수의 페이지 버퍼 영역들에 순차적으로 배열되며,

상기 복수개의 어드레스 라인들은 상기 제1 방향과 수직되는 제2 방향으로 길게 확장되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 54.

제53 항에 있어서,

상기 복수개의 페이지 버퍼들은 제1 페이지 버퍼블락을 정의하며,

상기 불휘발성 메모리 장치는 제2 방향으로 상기 제1 페이지 버퍼블락에 인접되어 위치되는 제2 페이지 버퍼블락을 더 구비하며,

상기 복수개의 어드레스 라인들은 더 확장되어, 상기 제2 페이지 버퍼블락의 제2 복수개의 페이지 버퍼들의 대응하는 게이트 회로들에 연결되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 55.

제54 항에 있어서, 상기 내부 데이터 출력 라인은 상기 제1 방향으로 길게 확장되는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 56.

제55 항에 있어서,

인접한 상기 제2 페이지 버퍼블락의 상기 제1 방향의 길게 확장되는 제2 내부 데이터 출력 라인들을 더 구비하는 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 57.

제55 항에 있어서, 상기 메모리 셀들은 플래시 메모리 셀들인 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 58.

제50 항에 있어서, 상기 메모리 셀 어레이에는 낸드(NAND) 타입의 플래시 메모리 셀 어레이인 것을 특징으로 하는 불휘발성 메모리 장치.

### 청구항 59.

불휘발성 메모리 장치의 페이지 버퍼에 있어서,

래치 노드를 포함하는 래치 회로;

상기 래치 노드의 전압을 제어하는 내부 데이터 입력 라인;

상기 래치 노드로부터 전기적으로 분리되는 내부 데이터 출력 라인; 및

상기 래치 노드의 상기 전압에 따라 상기 내부 출력 라인의 전압을 제어하는 출력 드라이브 회로를 구비하는 것을 특징으로 하는 불휘발성 메모리 장치의 페이지 버퍼.

### 청구항 60.

제59 항에 있어서, 상기 출력 드라이브 회로는

상기 래치 노드의 전압에 따라 상기 내부 데이터 출력 라인을 상기 제1 기준전위에 선택적으로 연결하는 것을 특징으로 하는 불휘발성 메모리 장치의 페이지 버퍼.

**청구항 61.**

제59 항에 있어서,

상기 래치 노드와 상기 제2 기준 전위 사이에 직렬적으로 연결되는 적어도 하나의 트랜지스터로서, 상기 내부 데이터 입력 라인에 연결되는 게이트를 포함하는 상기 적어도 하나의 트랜지스터를 더 구비하는 것을 특징으로 하는 불휘발성 메모리 장치의 페이지 버퍼.

**청구항 62.**

제61 항에 있어서, 상기 적어도 하나의 트랜지스터는 상기 래치 노드와 상기 제2 기준 전위 사이에 직렬적으로 연결되는 제1 및 제2 트랜지스터를 구비하며,

상기 제1 트랜지스터의 도전 상태(conductive state)는 상기 내부 입력 라인에 의해 제어되며, 상기 제2 트랜지스터의 도전 상태(conductive state)는 어드레스 라인에 의해 제어되는 것을 특징으로 하는 불휘발성 메모리 장치의 페이지 버퍼.

**청구항 63.**

불휘발성 반도체 메모리 장치에 있어서,

전기적으로 프로그램 및 소거될 수 있는 복수개의 메모리 셀들, 복수개의 워드라인들, 그리고 복수개의 비트라인들을 가지는 메모리 셀 어레이; 및

복수개의 페이지 버퍼들과 내부 데이터 출력 라인을 가지는 적어도 하나의 페이지 버퍼블락으로서, 상기 페이지 버퍼들은 각자 비트라인들에 연결되며, 복수개의 버퍼선택신호들 중의 적어도 어느 하나에 응답하여 인에이블되고, 상기 페이지 버퍼들 각각은 비트라인 상의 데이터에 대응하여, 자신의 래치 노드에 저장하며, 상기 내부 데이터 출력 라인은 상기 복수개의 페이지 버퍼들에 공유되고, 인에이블되는 페이지 버퍼의 래치 노드 상의 데이터에 의하여 드라이빙되며, 상기 내부 데이터 출력 라인은 상기 페이지 버퍼들의 래치 노드들로부터 전기적으로 분리되는 상기 적어도 하나의 페이지 버퍼블락을 구비하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

**청구항 64.**

제63 항에 있어서, 상기 페이지 버퍼들 각각은

상기 래치 노드를 가지는 래치 유닛; 및

상기 버퍼선택 어드레스들 중의 상기 적어도 하나에 응답하여 인에이블되는 출력 드라이빙 유닛으로서, 상기 래치 노드에 저장된 데이터에 대응하여 상기 내부 데이터 출력 라인으로 드라이빙하는 상기 출력 드라이빙 유닛을 구비하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

**청구항 65.**

제64 항에 있어서, 상기 페이지 버퍼들 각각은

제1 및 제2 내부 데이터 라인들; 및

상기 제1 및 제2 내부 입력 라인들에 각각 게이팅되는 제1 및 제2 래치 전송 트랜지스터를 포함하는 래치 전송 유닛을 더 구비하며,

상기 제1 및 제2 래치 전송 트랜지스터들은 상기 페이지 버퍼의 상기 래치 노드 및 반전된 래치 노드의 각자의 전압을 설정하도록 상기 제1 및 제2 내부 데이터 입력 라인에 각각 응답하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

### 청구항 66.

제65 항에 있어서, 상기 페이지 버퍼들 각각은

상기 버퍼선택 어드레스에 응답하여 게이팅되며, 소정의 버퍼입력패스를 통하여, 외부에서 인가되는 데이터와 독립적인 래치 드라이빙 전압을 상기 래치 전송 유닛으로 제공하도록 채용되는 래치 드라이빙 유닛을 더 구비하며,

상기 버퍼입력패스는 상기 내부 데이터 출력 라인으로부터 전기적으로 분리되는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

### 청구항 67.

제66 항에 있어서, 상기 페이지 버퍼들 각각은

상기 비트라인 상의 데이터에 응답하여 소정의 센싱 응답 전압을 상기 래치 전송 유닛에 제공하는 센싱응답 유닛을 구비하며,

상기 센싱 응답 전압은 상기 래치 노드에 저장되는 데이터의 플립을 유발하기에 충분한 전압인 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

### 청구항 68.

제67 항에 있어서, 상기 래치 전송 유닛은

상기 제1 내부 데이터 입력 라인 상의 상기 데이터에 응답하여 상기 래치 유닛으로 상기 래치 드라이빙 전압 또는 상기 센싱 응답 전압을 선택적으로 제공하는 제1 래치 전송 트랜지스터; 및

상기 제2 내부 데이터 입력 라인 상의 데이터에 응답하여 상기 래치 유닛으로 상기 래치 드라이빙 전압 또는 상기 센싱 응답 전압을 선택적으로 제공하는 제2 래치 전송 트랜지스터를 구비하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

### 청구항 69.

제68 항에 있어서, 상기 센싱응답 유닛은

상기 비트라인 상의 데이터에 응답하여 게이팅되는 센싱 응답 트랜지스터; 및

상기 센싱 응답 트랜지스터와 직렬적으로 연결되는 출력 센싱 트랜지스터를 구비하며,

상기 출력 센싱 트랜지스터는

상기 페이지 버퍼를 선택하는데 사용되는 독출(read) 래치 신호에 응답하여, 상기 래치 노드에 저장되는 상기 비트라인 상의 데이터에 대응하는 데이터를 제어하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

**청구항 70.**

제68 항에 있어서, 상기 페이지 버퍼들 각각은

상기 비트라인 상의 상기 데이터에 대응하는 데이터를 상기 센싱응답 유닛으로 제공하는 상기 비트라인에 연결되는 센싱 노드; 및

상기 센싱 노드를 셋팅 전압으로 조절하기 위한 센싱셋팅 유닛을 더 구비하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

**청구항 71.**

제70 항에 있어서, 상기 페이지 버퍼들 각각은

상기 센싱 노드로의 상기 비트라인의 연결을 제어하기 위한 비트라인 차단 유닛을 더 구비하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

**청구항 72.**

제71 항에 있어서, 상기 비트라인 차단 유닛은

상기 비트라인을 상기 센싱 노드에 연결하도록, 비트라인 차단 신호에 응답하여 게이팅되는 비트라인 차단 트랜지스터를 구비하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

**청구항 73.**

제72 항에 있어서, 상기 페이지 버퍼들 각각은

상기 센싱 노드와 상기 래치 노드의 연결을 제어하는 버퍼선택 유닛을 더 구비하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

**청구항 74.**

제73 항에 있어서, 상기 버퍼 선택 유닛은

상기 센싱 노드로의 상기 래치 노드의 연결을 제어하는 버퍼 선택 신호에 응답하여 게이팅되는 버퍼 선택 트랜지스터를 구비하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

**청구항 75.**

제63 항에 있어서, 동일한 페이지 버퍼 블락 안에 포함되는 상기 복수개의 페이지 버퍼들은 제1 방향으로 병치(並置)되며,

상기 내부 데이터 출력 라인은 상기 제1 방향으로 길게 확장되는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

## 청구항 76.

제63 항에 있어서,

제1 글로벌 입력 라인;

주어진 동작 구간 동안에서, 상기 제1 글로벌 입력 라인의 논리 상태와 반대되는 논리 상태를 가지는 제2 글로벌 입력 라인; 및

메인선택 어드레스 및 서브선택 어드레스에 응답하여 인에이블되는 페이지 버퍼 디코더를 더 구비하며,

상기 페이지 버퍼 디코더는, 인에이블될 때, 상기 제1 및 제2 글로벌 입력 라인 상의 데이터에 대응하는 데이터를 각각 상기 제1 및 제2 내부 데이터 입력 라인으로 제공하는 상기 페이지 버퍼 디코더를 더 구비하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

## 청구항 77.

제76 항에 있어서, 상기 페이지 버퍼 디코더는

상기 메인선택 어드레스와 상기 서브선택 어드레스의 논리 연산을 수행하고, 상기 메인선택 어드레스와 상기 서브선택 어드레스가 모두 액티브 상태일 때, 액티브되는 블락 디코딩 신호를 출력하는 제1 디코더 논리 게이트;

상기 블락 디코딩 신호에 응답하여 인에이블되고, 논리 연산 결과를 상기 제1 글로벌 입력 라인의 데이터에 응답하여 상기 제1 내부 데이터 입력 라인으로 제공하도록 채용되는 제2 디코더 논리 게이트; 및

상기 블락 디코딩 신호에 응답하여 인에이블되고, 상기 제2 글로벌 입력 라인 상의 데이터에 응답하여 논리 연산 결과를 상기 제2 내부 데이터 입력 라인으로 제공하도록 채용되는 제3 디코더 논리 게이트를 구비하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

## 청구항 78.

제77 항에 있어서,

상기 제1 디코더 논리 게이트는 낸드(NAND) 게이트이고,

상기 제2 및 제3 디코더 논리 게이트들은 노아(NOR) 게이트들인 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

## 청구항 79.

제63 항에 있어서,

글로벌 출력 라인; 및

메인선택 어드레스와 서브선택 어드레스에 응답하여 인에이블되는 페이지 버퍼 디코더를 더 구비하며,

상기 페이지 버퍼 디코더는, 인에이블될 때, 상기 내부 데이터 출력 라인 상의 데이터를 상기 글로벌 출력 라인으로 제공하는 것을 특징으로 하는 불휘발성 반도체 메모리 장치.

## 청구항 80.

제79 항에 있어서, 상기 페이지 버퍼 디코더는

상기 메인선택 어드레스와 상기 서브선택 어드레스의 논리 연산을 수행하고 상기 메인선택 어드레스와 상기 서브선택 어드레스가 모두 액티브 상태일 때, 액티브되는 블락 디코딩 신호를 출력하기 위한 제1 디코더 논리 게이트; 및

상기 블락 디코딩 신호에 응답하여 상기 내부 출력 데이터 라인 상의 데이터를 상기 글로벌 출력 라인으로 제공하기 위한 디코더 트랜지스터를 구비하는 것을 특징으로 하는 블록발성 반도체 메모리 장치.

## 청구항 81.

제63 항에 있어서, 상기 메모리 셀 어레이에는 낸드(NAND) 타입의 플래시 메모리 셀 어레이로 이루어진 것을 특징으로 하는 블록발성 반도체 메모리 장치.

명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 반도체 메모리 장치에 관한 것으로서, 특히 블록발성 메모리 장치에서 사용되는 페이지 버퍼 회로 및 다른 회로들에 관한 것이다.

최근, 전기적으로 프로그램(program)과 전기적으로 소거(erase)가 가능한 블록발성 반도체 메모리 장치에 대한 수요가 급격히 증가하고 있다. 이러한 장치들은 적어도 공급 전원이 없는 상태에서 저장된 데이터를 유지할 수 있는 능력에 의하여 부분적인 특징이 지워진다. 이른바, 플래시 메모리는, 디지털 카메라, 셀폰들(cell phones), PDA들(personal data assistants), 그리고 랩탑 컴퓨터들(laptop computers)과 같은 휴대용 장치에서, 특별히 그러나 비(非)배터적으로 널리 이용되고 있다. 플래시 메모리, 예컨대, 낸드(NAND) 타입의 플래시 메모리는 상대적으로 작은 면적에 많은 양의 데이터를 저장할 수 있다.

종래기술을 논의함에 있어서, 플래시 메모리 셀들과 플래시 메모리 장치들의 기초를 이루는 기본적 동작 원리들은 아래에 제시된다. 그러나, 아래에 제시된 논의는 단지 일례일 뿐이며, 본 발명의 범위를 어떠한 방법으로 제한 및/또는 한정하는 것이 아님을 명확히 이해해야만 한다.

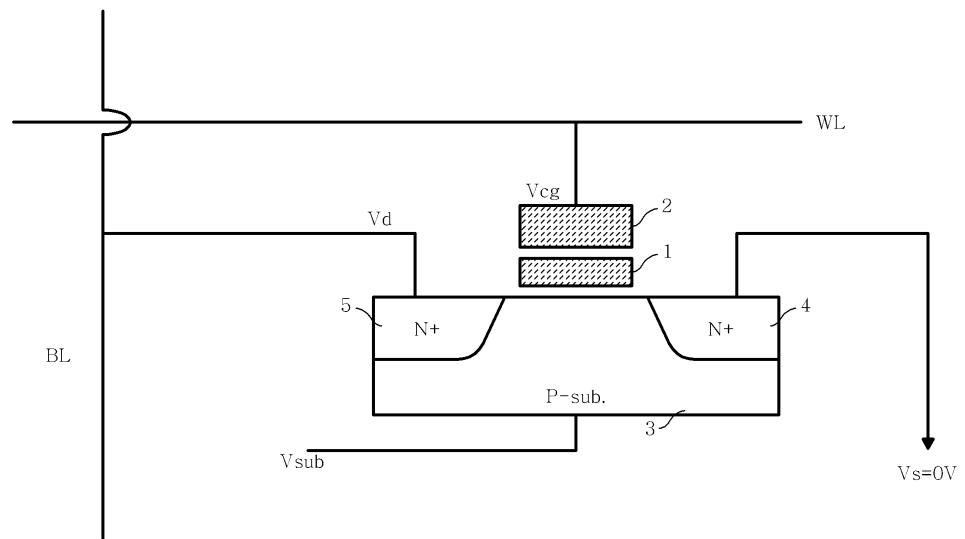

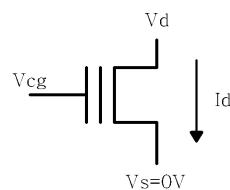

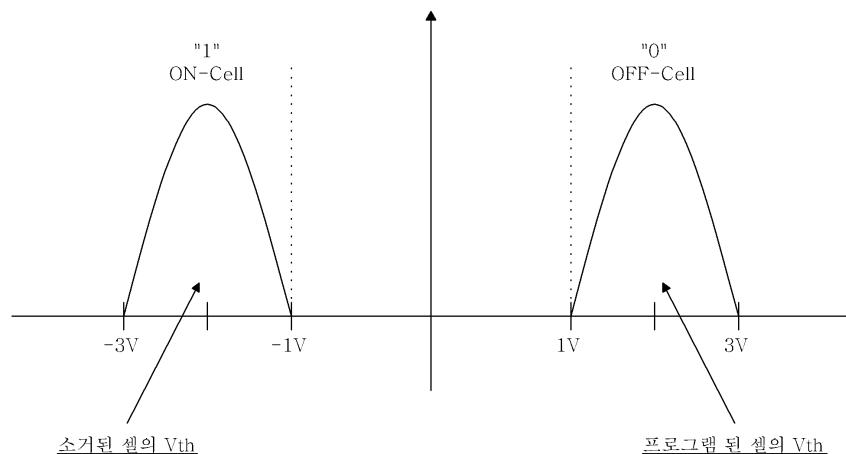

먼저 플래시 메모리 셀(flash memory cell)의 동작 원리가 도 1a 내지 도 1c를 참조하여 기술된다. 도 1a는 메모리 장치의 워드라인과 비트라인에 연결되는 하나의 플래시 메모리 셀 트랜지스터의 전형적인 구조를 나타내며, 도 1b는 하나의 플래시 메모리 셀 트랜지스터의 등가 회로도를 나타내며, 그리고, 도 1c는 하나의 플래시 메모리 셀 트랜지스터의 문턱전압(threshold voltage) 특성을 나타낸다.

도 1a 내지 도 1c를 함께 참조하면, 하나의 플래시 메모리 셀 트랜지스터는 기판(substrate, 3)의 표면상에 위치되는 소오스 영역(source region, 4)과 드레인 영역(drain region, 5)을 포함한다. 본 예에서, 상기 기판(3)은 P형이고, 상기 소오스 영역(4)과 상기 드레인 영역(5)은 N+ 형이다. 게이트 구조(gate structure)는 상기 소오스 영역(4)과 상기 드레인 영역(5) 사이로 정의되는 채널 영역(channel region)의 상부에 정렬된다. 상기 게이트 구조는 플로팅 게이트(1; floating gate)와 제어 게이트(2; control gate)를 포함한다. 미도시되었지만, 터널링 유전체층(tunneling dielectric layer)이 상기 플로팅 게이트와 기판의 표면 사이에 삽입되고, 다른 박막 산화층(thin oxide layer)(혹은, 제어 유전체층)이 상기 플로팅 게이트(1)와 상기 제어 게이트(2) 사이에 삽입된다. 도시된 예에서, 드레인 전압(Vd)은 비트라인(BL)으로부터 공급되고, 제어 게이트 전압(Vcg)은 워드라인(WL)으로부터 공급되며, 소오스 전압(Vs)는 접지와 같은 기준전위에 연결된다.

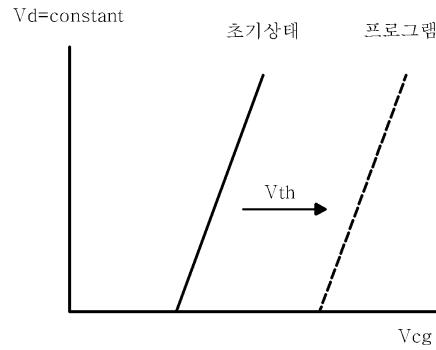

상기 플래시 메모리 셀 트랜지스터의 문턱전압은 그것의 저장된 논리값을 정의한다. 즉, 상기 플래시 메모리 셀 트랜지스터가 초기 상태(또한 '소거' 상태로 불림)에 있는 경우에는, 상기 문턱전압(Vth)은 도 1c에 도시된 바와 같이 상대적으로 낮

다. 이러한 상태에서, 셀 트랜지스터는 논리값 "1"을 가지는 것으로 정의되며, 일반적으로 통상적인 트랜지스터 소자의 온(ON) 상태에 해당한다. 반면에 셀 트랜지스터가 프로그램된 상태(PGM)에 있는 경우에는, 상기 문턱전압(Vth)은 상대적으로 높다. 이러한 높은 문턱전압 상태는 논리값 "1"을 가지는 것으로 정의되며, 일반적으로 통상적인 트랜지스터 소자의 오프(OFF) 상태에 해당한다.

셀 트랜지스터를 초기 상태에서 프로그램된 상태로 변환(프로그램)하기 위하여, 파울러-노드하임 터널링(Fowler-Nordheim tunneling, 이하 'FN 터널링'이라 함)으로 널리 알려진 프로세스가 이용된다. 이 프로세스를 간략히 설명하면, 비교적 큰 양(+)의 전위차가 제어 게이트(2)와 기판(Psub) 사이에서 생성되고, 기판(Psub) 상의 채널 내에 여기된 전자들(excited electrons)은 투과되어 상기 플로팅 게이트(1)에 트랩(trapped)된다. 이러한 음(−)으로 차아지된(charged) 전자들은 상기 제어 게이트(2)와 상기 기판(Psub) 사이의 장벽으로 작용하며, 그리하여 도 1c에 나타난 바와 같이, 셀 트랜지스터의 문턱전압을 증가시킨다. 상기 제어 게이트(2)와 상기 기판(Psub) 사이에 큰 음(−)의 전위차를 형성함에 의하여 상기 셀 트랜지스터는 초기 상태로 복원될 수 있다. 그리하여 결과적으로 생기는 FN 터널링은 트랩된 전자들을 박막 산화층을 가로 질러 상기 플로팅 게이트(1)와 상기 기판(Psub)에 되돌려 보내어서, 전자 장벽을 제거하고 문턱전압(Vth)를 감소시킨다.

도 2를 참조하면, 플래시 메모리 장치 내에 발견되는 상당수의 플래시 셀 트랜지스터들의 상기 온(ON) 및 오프(OFF) 문턱전압(Vth)은 일반적으로 벨커브(bell curve) 분포를 나타낸다. 예를 들면, 소거된 셀 트랜지스터들(논리값 "1"을 가짐)의 문턱전압들(Vth)은  $-3\text{V}$ 와  $-1\text{V}$  사이에 분포될 것이며, 반면에 프로그램된 셀 트랜지스터들(논리값 "0"을 가짐)의 문턱전압들(Vth)은  $+1\text{V}$ 와  $+3\text{V}$  사이에 분포될 것이다.

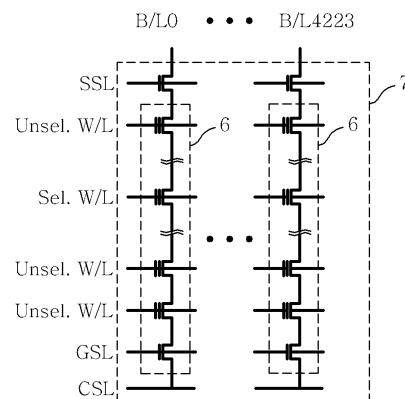

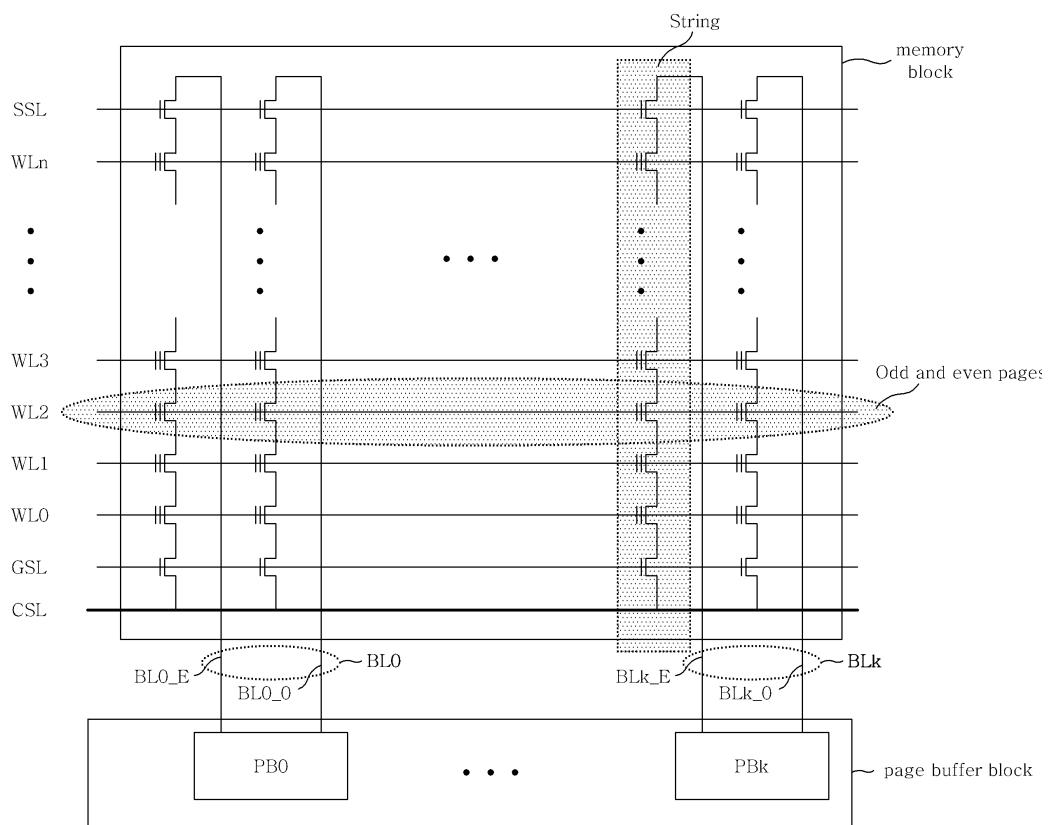

도 3a를 참조하면, 낸드(NAND) 플래시 메모리들은 직렬적으로 연결되는 플래시 메모리 셀 트랜지스터들의 "스트링(6)"에 의하여 특징 지워지는데, 여기서 다수의 병렬 스트링들(6)이 플래시 메모리의 메모리 블락(7)을 구성한다. 도시된 바와 같이, 각 스트링(6)은 상기 메모리 블락(7)의 비트라인(BL)을 따라 직렬적으로 연결된 복수개의 플래시 메모리 셀 트랜지스터들로 구성된다. 워드라인(WL)은 상기 메모리 블락(7)에서 셀 트랜지스터들의 각각의 대응하는 행(row)의 제어 게이트에 연결된다. 예를 들면, 플래시 메모리 장치는 각각의 스트링(6) 내에 16개 내지 32개의 셀 트랜지스터들을 포함하고, 각각의 메모리 블락(7) 내에 4224개의 스트링들(B/L0, ..., B/L4223)을 포함한다.

각 스트링(6)의 양쪽 끝단에는 스트링 선택 신호(SSL) 및 그라운드 선택 신호(GSL)를 수신하는 제어 게이트들을 가지는 스트링 선택 트랜지스터(string select transistor)들이 있다. 일반적으로, 상기한 선택 신호들(SSL 및 GSL)은 셀 트랜지스터들의 독출(reading)과 프로그래밍(programming)에 이용된다. 더욱이, 각각의 스트링 끝단에는 각 메모리 블락(7)의 상기 셀 트랜지스터 스트링(6)들의 소오스 라인 전압을 안내하는 공통 소오스 라인(CSL)이 있다.

도 3b의 표는 소거, 프로그램 및 독출 동작에 대하여, 도 3a에 도시된 신호들의 다양한 전압조건들을 일반적으로 나타낸다. 상기한 표에서, "Sel.W/L"은 프로그램 또는 독출 동작이 수행되는 선택된 워드라인(selected word line)을 의미하며, "Unsel.W/L"은 상기 메모리 블락의 나머지 워드라인들을 의미한다. 소거동작의 경우, "Sel.W/L"은 소거동작이 수행되는 선택된 메모리 블락의 워드라인을 의미하고, "Unsel.W/L"은 메모리 셀 어레이 내에 나머지 메모리 블락들의 워드라인들을 의미한다.

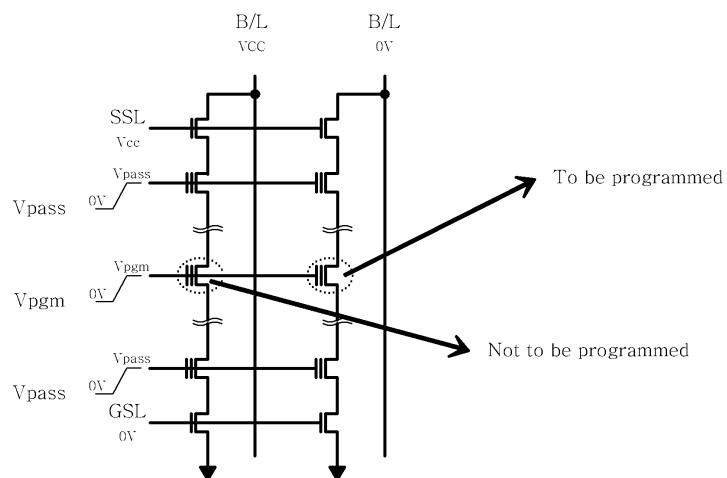

다음으로 낸드(NAND) 플래시 프로그래밍 동작이 도 3b와 도 4를 참조하여 기술된다. 여기서, 스트링 선택 신호(SSL)는 전원전압(VDD)으로 설정되고, 그라운드 선택 신호(GSL)는 0V로 설정되고, 공통 소오스 라인(CSL) 전압은 접지전압(VSS)에서 전원전압(VDD) 사이(예컨대, 1.5V)로 설정되며, 벌크(bulk) 전압은 0V로 설정된다. 일반적으로, 프로그래밍은 1회에 하나의 워드라인에서 일어나고, 따라서, 각 프로그래밍 동작에 대해 하나의 메모리 블락당 1개의 워드라인이 선택된다. 여기서, 선택된 워드라인(W/L)은 프로그래밍 전압(Vpgm)을 수신하고, 반면에 나머지 비선택된 워드라인(W/L)들은 패스 전압(Vpass)을 수신한다. 여기서, 프로그래밍 전압(Vpgm)은 패스 전압(Vpass)보다 크다. 프로그래밍 전압(Vpgm)은 선택된 워드라인의 어떠한 셀 트랜지스터의 비트라인(BL) 전압이 0V일 때, FN 터널링이 결과로 생기는 충분히 높은 전압(이를테면, 18V)이다. 즉, 선택된 워드라인의 어떠한 셀 트랜지스터의 비트라인(B/L) 전압이 0V일 때, 프로그램 전압(Vpgm)은 FN 터널링을 시작하기에 충분한 전압차를 생성하여서, 셀 트랜지스터를 프로그래밍 상태에 놓이게 한다. 반면에, 어떠한 셀 트랜지스터의 비트라인(B/L) 전압이 전원전압(VDD)일 때, FN 터널링은 불충분한 전압차(예컨대, 10V)의 결과로서 억제된다. 이와 같은 것으로, 셀은 "프로그램 금지"라 불린다. 한편, 패스전압(Vpass)은 비선택된 트랜지스터가 도전 상태에 놓여 지도록 충분히 높으나, FN 터널링을 일으킬 만큼 높지는 않다.

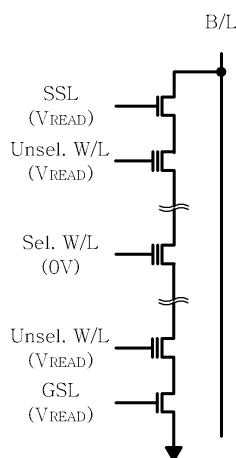

도 3b 및 도 5를 참조하여, 독출 동작(read operation)이 계속 기술된다. 이 경우, 스트링 선택 신호(SSL)은 독출전압(Vread), 그라운드 선택 신호(GSL)는 독출전압(Vread), 공통 소오스 라인(CSL) 전압은 0V, 그리고, 벌크(bulk) 전압은 0V로 설정된다. 프로그래밍 동작과 마찬가지로, 독출 동작은 1회에 전형적으로 하나의 워드라인에 일어나며, 따라서, 각

독출 동작에 대해 각 메모리 블락당 1개의 워드라인이 선택된다. 여기서, 선택된 워드라인(W/L)은 0V로 설정된다. 반면에, 나머지 비선택된 워드라인이 독출전압(Vread)을 수신한다. 본 예에서, 독출전압(Vread)은 4.5V로서, "1"과 "0" 셀 트랜지스터들의 문턱전압 분포를 초과하는 4.5V이다. 그러므로, 비선택된 워드라인들에 커플드된 셀 트랜지스터들은 도전상태가 된다. 반면에, 선택된 워드라인에 인가된 0V전압은 "1"과 "0" 셀 트랜지스터의 문턱전압 분포 사이이다. 그리하여, 선택된 워드라인에 연결된 상기 "1" 셀 트랜지스터는 도전성으로 되고, 반면에, 선택된 워드라인의 나머지 셀 트랜지스터들은 비도전성으로 된다. 그 결과는 상기 메모리 블락의 비트라인(B/L)들 사이의 전압차이다.

도 3b의 표에 주어진 예에서, 대략 1.2V의 비트라인(B/L)전압은 선택된 워드라인에서 "0" 상태의 셀 트랜지스터를 가지는 것으로 읽혀지고, 0.8V보다 작은 비트라인 전압은 선택된 워드라인에서 "1" 상태의 셀 트랜지스터를 가지는 것으로 읽혀진다.

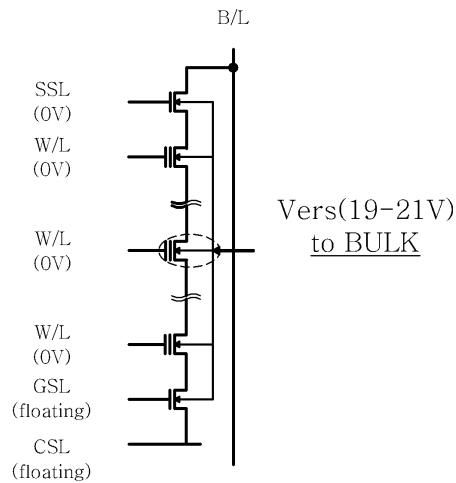

도 3b 및 도 6을 참조하여, 소거 동작이 계속 기술된다. 이 경우, 비트라인(B/L), 스트링 선택 신호(SS), 그라운드 선택 신호(GS), 공통 소스 라인(CS), 그리고, 비선택된 메모리 블락들의 워드라인들은 모두 플로팅 상태로 설정된다. 반면에, 선택된 워드라인 전압은 0V로 설정되고, 별크 전압은 Verase(이를 테면, 19 ~ 21V)로 설정된다. 그리하여, 네거티브 전압 차가 제어 게이트와 별크 사이에 형성되고, 그 결과 플로팅 게이트와 기판 사이의 게이트 산화층에 걸쳐 FN 터널링이 발생된다. 결과적으로, 문턱전압 분포는 프로그램된 "0" 상태에서 소거된 "1" 상태로 감소된다. 소거동작 후에는, 선택된 메모리 블락의 모든 셀 트랜지스터들은 상기 소거된 "1" 상태 임을 유념해야 한다.

전술한 바와 같이, 상기 메모리 블락의 독출(reading) 및 프로그래밍(programming)은 1회에 한개의 워드라인에서 실행된다. 그러나, 어떤 응용에서는, 이러한 동작들이 메모리 블락 내의 페이지마다("page by page") 실행된다고 하는 것이 보다 정확하다. 이러한 개념은 도 7에 일반적으로 도시된다. 도시된 예에서, 상기 비트라인들(BL<k:0>)은 이븐(even) 및 오드(odd) 비트라인들(BL\_E<k:0> 및 BL\_O<k:0>)으로 나누어진다. 각 워드라인의 셀 트랜지스터들은 메모리 블락의 페이지들을 구성하고, 도 7의 예에서, 각 워드라인은 메모리 블락의 이븐 페이지 및 오드 페이지에 연결된다. 아래에서 더욱 상세히 설명되는 바와 같이, 페이지 버퍼 블록에 포함되는 페이지 버퍼들(PB<k:0>)은 플래시 메모리 블록으로부터의 독출(read) 데이터를 전송하고, 플래시 메모리 블록으로 프로그램 데이터를 전송하기 위해 이용된다. 통상적으로, 1개의 페이지 버퍼(PB)는 각각 오드 및 이븐 비트라인쌍에 마련된다.

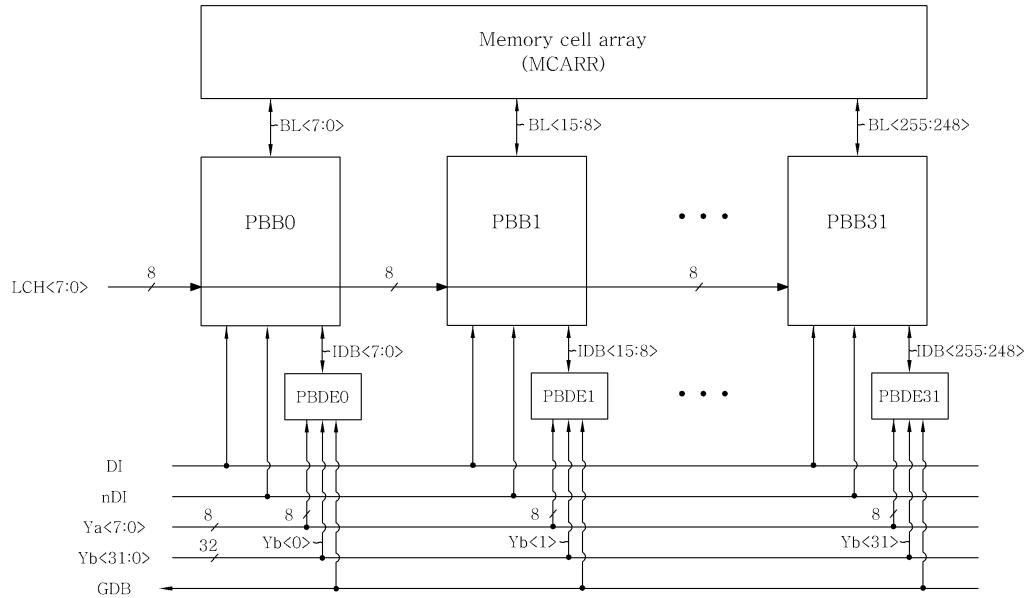

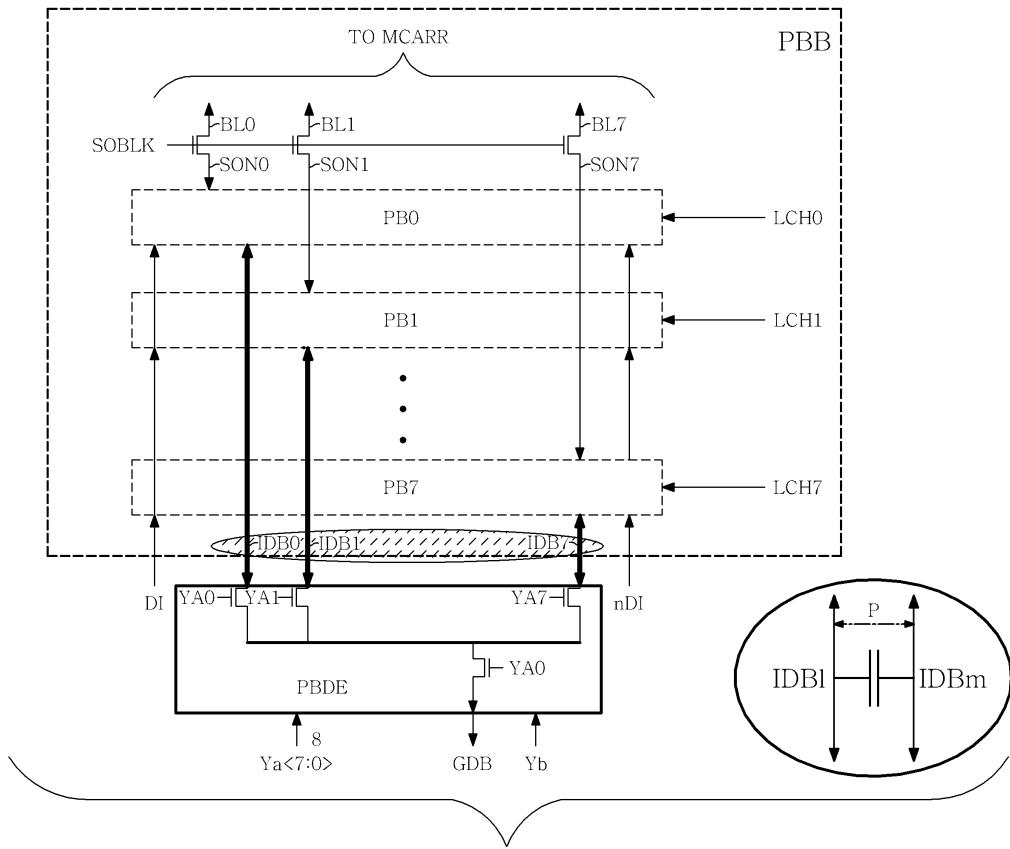

도 8은 일 예의 낸드(NAND) 탑 플래시 메모리의 코어(core) 요소들(elements)를 나타내는 블락도로서, 상기 메모리의 비트라인을 억세스하기 위하여 소위 "Y-gating" 기술이 이용된다. 도시된 바와 같이, 복수개의 페이지 버퍼블락들(PBB<31:0>)이 비트라인(BL<255:0>)을 통해 메모리 셀 어레이(MCARR)에 연결된다. 각각의 페이지 버퍼블락(PBB)은 8개의 비트라인들과 인터페이스 한다. 도 8에는 도시되지 않았으나, 도 7과 관련하여 전술한 바와 같이, 각 비트라인(BL)은 실제로 한쌍의 오드 및 이븐 비트 라인으로 이루어진다.

복수개의 페이지 버퍼 디코더들(PBDE<31:0>)은 대응하는 페이지 버퍼블락들(PBB<31:0>), y 어드레스 라인들(Ya<7:0>), y 어드레스 라인들(Yb<31:0>), 그리고 글로벌 데이터 버스(GDB)들에 실효적으로(operatively) 커플드(coupled)된다. 하기에서 보다 자세히 설명하는 바와 같이, y 어드레스 라인들(Ya<7:0>)은 공통적으로 모든 페이지 버퍼 디코더들(PBDE<31:0>)에 인가되며, 반면에, y 어드레스 라인들(Yb<31:0>)의 각자는 대응하는 페이지 버퍼 디코더들(PBDE<31:0>)에 인가된다. 즉, 페이지 버퍼 디코더(PBDE0)은 y 어드레스(Ya<7:0> 및 Yb0)를 수신하며, 페이지 버퍼 디코더(PBDE1)은 y 어드레스(Ya<7:0> 및 Yb1)를 수신한다. 그리고, 나머지 페이지 버퍼들에 대해서도, 같은 방식으로 이루어진다. 내부 데이터 라인들(IDB<255:0>)은 페이지 버퍼블락들(PBB<31:0>)과 페이지 버퍼 디코더들(PBDE<31:0>) 사이에 커플드(coupled)된다. 도 8의 예에서는, 8개의 내부 데이터 라인들(IDB)은 각각 대응하는 페이지 버퍼블락(PBB) 쌍과 페이지 버퍼 디코더(PBDE) 사이에 제공된다.

또한, 데이터 입력 선택 신호들(DI 및 nDI)과 래치신호들(LCH<7:0>)이 페이지 버퍼블락(PBB<31:0>)에 인가되는데, 이것들의 기능들은 도 9와 관련되어 후술된다.

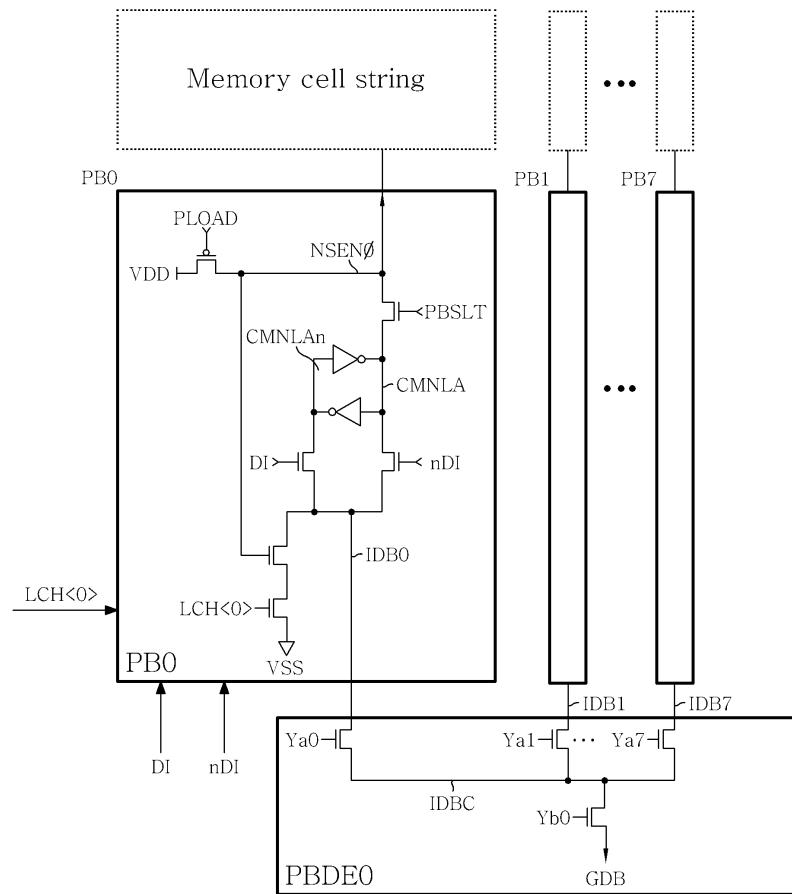

도 9는 도 8에서 도시된 페이지 버퍼들(PB) 및 페이지 버퍼 디코더들(PBDE)을 설명하기 위한 회로도이다. 설명의 편의를 위하여, 도 9는 나란한 배열의(즉, 워드라인 방향으로 병치(並置)된) 페이지 버퍼들(PB<7:0>)이 도시된다. 그러나, 실제상으로는, 상기 페이지 버퍼들은 다른 페이지 버퍼의 상부에 적층된 구조로 이루어진다(즉, 비트라인 방향으로 병치된다).

도 9의 페이지 버퍼 디코더(PBDE0)는 글로벌 데이터 버스(GDB)와 공통 내부 데이터 라인(IDB) 사이에 연결된 제1 트랜지스터, 그리고 공통 내부 데이터 라인과 페이지 버퍼들(<7:0>)의 각자의 내부 라인들(IDB<7:0>) 사이에 연결된 복수개의 제2 트랜지스터들을 포함한다. 도시된 바와 같이, 제1 트랜지스터의 게이트는 y 어드레스 신호(Yb0)를 수신하고, 제

2 트랜지스터들 각자의 게이트들은 y 어드레스 신호들( $Yb<7:0>$ )을 수신한다. 그래서, y 어드레스( $Yb<31:0>$ )는 페이지 버퍼블락들(PBB<31:0>) 중에서 어느 하나를 선택하는데 사용되고, y 어드레스( $Ya<7:0>$ )는 선택된 페이지 버퍼블락(PBB) 내부의 비트라인(BL)을 선택하는데 사용되는 것은 명백하다.

페이지 버퍼(PB0)는 래치 노드(CMNLA)와 반전된 래치 노드(CMNLA<sub>n</sub>)를 가지는 래치 회로(latch circuit)를 포함한다. 페이지 버퍼(PB0)의 제1 및 제2 트랜지스터들은 데이터 입력 선택 신호들(DI 및 nDI)에 의해 각각 제어되고, 이러한 트랜지스터들은 내부 데이터 라인(IDB0)과 반전된 래치 노드(CMNLA<sub>n</sub>) 및 래치 노드(CMNLA) 사이에 각각 연결된다. 또 다른 트랜지스터는 페이지 버퍼선택신호(PBSLT)에 의해 제어되고, 래치 노드(CMNLA)와 센스노드(NSEN0) 사이에 연결된다. 상기 메모리셀 어레이의 메모리 셀 스트링에 연결되는 상기 센스 노드(NSEN0)는, 로드(load) 제어 신호(PLOAD)의 해 제어되는 다른 트랜지스터의 동작에 의해 선택적으로 전원 전압(VDD)에 연결된다. 마지막으로, 2개의 트랜지스터들이 내부 데이터 라인(IDB)과 기준 전압(VSS) 사이에 직렬적으로 연결된다. 이러한 2개의 트랜지스터 중에서 하나는 센스 노드(NSEN0) 상에 나타나는 전압에 의해 제어되고, 다른 하나는 래치신호(LCH<0>)에 의해 제어된다.

요약하면, 프로그래밍 동작에서, 페이지 버퍼(PB0)의 래치 회로는 데이터 입력 선택 신호들(DI 및 nDI)과 내부 데이터 라인(IDB)의 전압에 의해 지시되는 논리값을 저장하고, 그리고 나서 이러한 논리값(즉, 래치 노드(CMNLA)에 나타나는 전압)은 프로그래밍을 위해 메모리 셀 스트링의 비트라인으로 전송된다. 이와 유사한 방식으로, 독출 동작(reading operation)에서, 상기 센스 노드 상에 나타나는 감지된 전압은 일시적으로 래치 회로에 저장되고, 그 다음에 내부 데이터 라인(IDB)을 통해 글로벌 데이터 버스(GDB)로 전송된다. 내부 데이터 라인(IDB)은 공유된 입력 및 출력 라인으로 작용함에 유념해야 한다.

상기한 종래의 불휘발성 메모리 장치는 많은 단점을 지니고 있다. 메모리 장치들이 고용량 메모리에 대한 요구를 만족하기 위해 더욱 집적됨에 따라 다양한 회로들의 레이아웃(layout) 면적이 감소됨으로써, 이러한 종래의 불휘발성 메모리 장치의 단점들은 두드러진다. 이러한 단점들의 전체적인 리스트를 제공하려는 의도없이, 이러한 단점들의 예가 논의된다.

인접하는 내부 데이터 라인들 사이에 기생 용량성 커플링(parasitic capacitive coupling)은 도 10에 도시되는 바와 같은 결과로 될 수 있다. 전술한 바와 같이, 그리고, 도 10에 도시된 바와 같이, 각 페이지 버퍼블락(PBB)의 페이지 버퍼들( $PB<7:0>$ )은 비트라인 방향으로, 즉, 페이지 버퍼 디코더(PBDE)와 메모리 셀 어레이(MCARR) 사이에, 적중된다. 이를테면, 페이지 버퍼 디코더(PBDE)와 메모리 셀 어레이(MCARR) 사이에 배열된다. 또한, 센스 노드 차단 신호(SOBLK)에 의하여 제어되어, 센스 노드( $SON<7:0>$ )들을 비트라인( $BL<7:0>$ )에 각각 선택적으로 커플시키는 다수의 트랜지스터들이 도시된다.

각자의 페이지 버퍼(PB)의 내부 데이터 라인들(IDB) 모두는 페이지 버퍼블락(PBB) 내에 서로 병렬적으로 확장된다. 페이지 버퍼(PB)들의 레이아웃 면적이 감소됨에 따라, 인접하는 내부 데이터 라인(IDB)들의 팅치(P)가 점점 좁아지고, 이에 따라, 용량성 커플링이 내부 데이터 라인들(IDB) 사이에서 증가한다. 인접한 내부 데이터 라인들(IDB) 사이에서 결과적으로 발생되는 커플링 노이즈는 신호의 왜곡과 데이터 에러(error)를 초래한다.

또한, 내부 데이터 라인들(IDB)의 큰 기생성 용량(capacitance)은 각 페이지 버퍼의 래치 회로의 낮은 용량성 래치 노드와의 전하 공유(charge sharing) 조건을 생성할 수 있다. 어떠한 경우에는, 이러한 것은 데이터가 플립(flipped)되는 현상을 유발할 수 있다. 게다가, 내부 데이터 라인들(IDB)의 높은 출력 부하는 페이지 버퍼의 출력 드라이빙 능력의 증가를 필요로 하게 되며, 이는 공간과 전압원(power resources)가 제한됨을 고려할 때, 매우 심각한 문제로 될 수 있다.

또한, 다시 도 8을 참조하면, 언급된 예의 버스 영역은 40개의 y 어드레스 라인들을 포함한다. 이와 같이 상대적으로 많은 수의 라인들은 장치의 버스 영역으로 큰 레이아웃 면적이 수반하여야만 한다.

### 발명이 이루고자 하는 기술적 과제

본 발명의 목적은 종래의 불휘발성 반도체 메모리 장치의 문제점을 개선하기 위한 것으로서, 인접하는 내부 데이터선들 사이의 커플링 노이즈(coupling noise)에 따른 내부 데이터선의 데이터 왜곡 현상을 감소시킬 수 있는 불휘발성 반도체 메모리 장치 및 이에 적용되는 페이지 버퍼를 제공하는 데 있다.

본 발명의 또 다른 목적은 칼럼 어드레스 버스 라인의 수를 감소하여, 소요되는 레이아웃 면적이 감소시키는 불휘발성 반도체 메모리 장치 및 이에 적용되는 페이지 버퍼를 제공하는 데 있다.

### 발명의 구성

본 발명의 일면에 따르면, 프로그램 모드 및 독출 모드에서 실시 가능한 불휘발성 메모리 장치가 제공된다. 상기 메모리 장치는 복수개의 불휘발성 메모리셀들, 복수개의 워드라인들 및 복수개의 비트라인들을 포함하는 메모리셀 어레이를 포함한다. 상기 메모리 장치는 상기 메모리셀 어레이의 비트라인들로부터 독출(read)되는 데이터를 출력하기 위한 내부 데이터 출력 라인과 상기 메모리셀 어레이와 상기 내부 데이터 출력 라인 사이에 전송되는 데이터를 임시적으로 저장하는 페이지 버퍼를 더 포함한다. 상기 페이지 버퍼는 상기 비트라인에 선택적으로 연결되는 센스 노드; 상기 센스 노드에 선택적으로 연결되는 래치 노드를 가지는 래치 회로; 상기 래치 노드의 논리 전압을 설정하는 래치 입력 패스; 및 상기 래치 입력 패스로부터 격리되며, 상기 래치 노드의 상기 논리 전압에 따른 상기 내부 데이터 출력 라인의 논리 전압을 설정하는 래치 출력 패스를 포함한다.

본 발명의 또 다른 일면에 따르면, 복수개의 불휘발성 메모리 셀들을 포함하는 메모리셀 어레이; 상기 메모리셀 어레이의 상기 불휘발성 메모리 셀들로부터 독출(read)되는 데이터 및 상기 메모리셀 어레이의 상기 불휘발성 메모리 셀들에 프로그램되는 데이터를 임시적으로 저장하기 위한 래치 회로를 포함하는 페이지 버퍼; 상기 메모리셀 어레이로부터 독출(read)되어 상기 페이지 버퍼에 임시적으로 저장되는 데이터를 출력하는 내부 데이터 출력 라인; 및 상기 내부 데이터 출력 라인으로부터 격리되는 래치 입력 패스로서, 데이터가 상기 메모리셀 어레이의 상기 불휘발성 메모리 셀들로 프로그램될 때 및 상기 메모리셀 어레이의 상기 불휘발성 메모리 셀들로부터 독출(read)될 때, 상기 래치 회로를 설정하는 상기 래치 입력 패스를 포함하는 불휘발성 메모리 장치가 제공된다.

본 발명의 또 다른 일면에 따르면, 복수개의 불휘발성 메모리 셀들을 포함하는 메모리셀 어레이; 상기 메모리셀 어레이의 불휘발성 메모리 셀들로 프로그램되는 데이터를 입력하는 입력 데이터 버스; 상기 입력 데이터 버스로부터 격리되며, 상기 메모리셀 어레이의 상기 불휘발성 메모리 셀들로부터 독출(read)되는 출력 데이터 버스; 상기 메모리셀 어레이의 상기 불휘발성 메모리 셀들로부터 독출(read)되는 데이터 및 상기 불휘발성 메모리 셀들로 프로그램되는 데이터를 일시적으로 저장하기 위한 래치 회로; 상기 출력 데이터 버스에 연결되는 내부 데이터 출력 라인; 상기 입력 데이터 버스에 연결되는 래치 입력 버스로서, 데이터가 상기 메모리셀 어레이의 상기 불휘발성 메모리 셀들로 프로그램될 때, 상기 래치 회로를 설정하는 상기 래치 입력 패스; 및 상기 래치 회로에 일시적으로 저장된 독출 데이터(read data)를 상기 내부 데이터 출력 라인으로 전송하는 출력 드라이브 회로를 포함하는 불휘발성 메모리 장치가 제공된다.

본 발명의 또 다른 일면에 따르면, 불휘발성 메모리 장치는 복수개의 불휘발성 메모리셀들, 복수개의 워드라인들 및 복수개의 비트라인들을 구비하는 메모리셀 어레이를 포함한다. 상기 메모리 장치는 내부 데이터 출력 라인 및 상기 메모리셀 어레이와 상기 내부 데이터 출력 라인에 연결되는 복수개의 페이지 버퍼들을 더 포함한다. 상기 페이지 버퍼는 복수개의 병치(並置)되는 페이지 버퍼들을 정의하기 위해 순차적으로 배열되며, 상기 페이지 버퍼들의 각각은 상기 메모리셀 어레이로부터 독출(read)되는 데이터를 임시적으로 저장하는 래치 회로를 포함하며, 상기 래치 회로와 상기 내부 데이터 출력 라인 사이에 연결되는 어드레스 게이트를 포함한다. 상기 어드레스 게이트는 상기 내부 데이터 출력 라인으로 상기 각 페이지 버퍼의 래치 회로로부터의 데이터를 선택적으로 출력하기 위하여 어드레스 신호에 응답한다.

본 발명의 또 다른 일면에 따르면, 불휘발성 메모리 장치는 복수개의 불휘발성 메모리 셀들, 복수개의 워드라인들 및 복수개의 비트라인들이 구비된 메모리셀 어레이를 포함하는 상기 불휘발성 메모리 장치가 제공되며, 상기 복수개의 비트라인들은 제1 방향으로 길게 확장된다. 상기 메모리 장치는 상기 메모리셀 어레이로부터 독출(read)되는 데이터를 출력하는 공유된 내부 데이터 출력 라인; 및 상기 메모리셀 어레이, 상기 공유된 내부 데이터 출력 라인 및 상기 복수개의 내부 데이터 입력 라인들 사이에 각각 기능적으로 연결되는 복수개의 페이지 버퍼들을 더 포함한다.

본 발명의 또 다른 일면에 따르면, 불휘발성 메모리 장치는 복수개의 불휘발성 메모리 셀들을 포함하는 메모리셀 어레이, 그리고 로컬 데이터 입력 라인 및 래치 회로를 포함하는 페이지 버퍼를 포함한다. 상기 래치 회로는 상기 메모리셀 어레이의 상기 불휘발성 메모리 셀들로부터의 독출(read)되는 데이터 및 상기 불휘발성 메모리셀에 프로그램되는 데이터를 일시적으로 저장하도록 상기 로컬 데이터 입력 라인에 응답한다. 상기 메모리 장치는 외부 입력신호를 공급하는 글로벌 데이터 입력 라인을 더 포함하며, 상기 외부 입력신호들은 상기 메모리셀 어레이를 프로그램하기 위한 프로그래밍 신호들과 상기 메모리셀 어레이를 독출(read)하기 위한 제어신호들을 포함하며, 게이트 회로로서, 상기 게이트 회로에 공급되는 어드레스 신호에 따라 상기 로컬 데이터 입력 라인으로 상기 외부 입력신호들을 선택적으로 출력하는 상기 게이트 회로를 포함한다.

본 발명의 또 다른 일면에 따르면, 복수개의 불휘발성 메모리 셀들, 복수개의 워드라인들 및 복수개의 비트라인들을 가지는 메모리셀 어레이를 포함하는 불휘발성 메모리 장치가 제공된다. 상기 메모리 장치는 상기 메모리셀 어레이로부터 독출

(read)되는 데이터를 출력하는 내부 데이터 출력 라인; 상기 메모리셀 어레이와 상기 내부 데이터 출력 라인 사이에 기능적으로 연결되는 복수개의 페이지 버퍼들; 및 상기 복수개의 페이지 버퍼들의 적어도 하나의 게이트 회로에 기능적으로 연결되는 복수개의 어드레스 라인들을 더 구비한다.

본 발명의 또 다른 일면에 따르면, 불휘발성 반도체 메모리 장치의 페이지 버퍼가 제공된다. 상기 페이지 버퍼는 래치 노드를 포함하는 래치 회로; 상기 래치 노드의 전압을 제어하는 내부 데이터 입력 라인; 상기 래치 노드로부터 전기적으로 분리되는 내부 데이터 출력 라인; 및 상기 래치 노드의 상기 전압에 따라 상기 내부 출력 라인의 전압을 제어하는 출력 드라이브 회로를 구비한다.

본 발명의 또 다른 일면에 따르면, 전기적으로 프로그램 및 소거될 수 있는 복수개의 메모리 셀들, 복수개의 워드라인들, 그리고 복수개의 비트라인들을 가지는 메모리셀 어레이를 구비하는 불휘발성 반도체 메모리 장치가 제공된다. 상기 메모리 장치는 복수개의 페이지 버퍼들을 포함하는 적어도 하나의 페이지 버퍼블락과 내부 데이터 출력 라인을 더 구비한다. 상기 페이지 버퍼들은 각자 비트라인들에 연결되며, 각각은 복수개의 버퍼선택신호들 중의 적어도 어느 하나에 응답하여 인에이블된다. 상기 페이지 버퍼들 각각은 비트라인 상의 데이터에 대응하여, 자신의 래치 노드에 데이터를 저장한다. 상기 내부 데이터 출력 라인은 상기 복수개의 페이지 버퍼들 사이에 공유되고, 인에이블되는 페이지 버퍼의 래치 노드 상의 데이터에 의하여 드라이빙된다. 상기 내부 데이터 출력 라인은 상기 페이지 버퍼들의 래치 노드들로부터 전기적으로 분리된다.

본 발명과 본 발명의 동작상의 잇점 및 본 발명의 실시에 의하여 달성되는 목적을 충분히 이해하기 위해서는 본 발명의 바람직한 실시예를 예시하는 첨부 도면 및 첨부 도면에 기재된 내용을 참조하여야만 한다. 각 도면을 이해함에 있어서, 동일한 부재는 가능한 한 동일한 참조부호로 도시하고자 함에 유의해야 한다. 또한, 하기의 설명에서, 구체적인 처리흐름과 같은 많은 특정 상세들은 본 발명의 보다 전반적인 이해를 제공하기 위해 기술된다. 그러나, 이들 특정 상세들 없이도, 본 발명의 실시될 수 있다는 것은 당해 기술분야에서 통상의 지식을 가진 자에게는 자명한 사실이다. 그리고, 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 공지 기능 및 구성에 대한 상세한 기술은 생략된다.

이하, 첨부한 도면을 참조하여 본 발명의 바람직하지만 한정되지 않는 실시예를 설명함으로써, 본 발명을 상세히 설명한다.

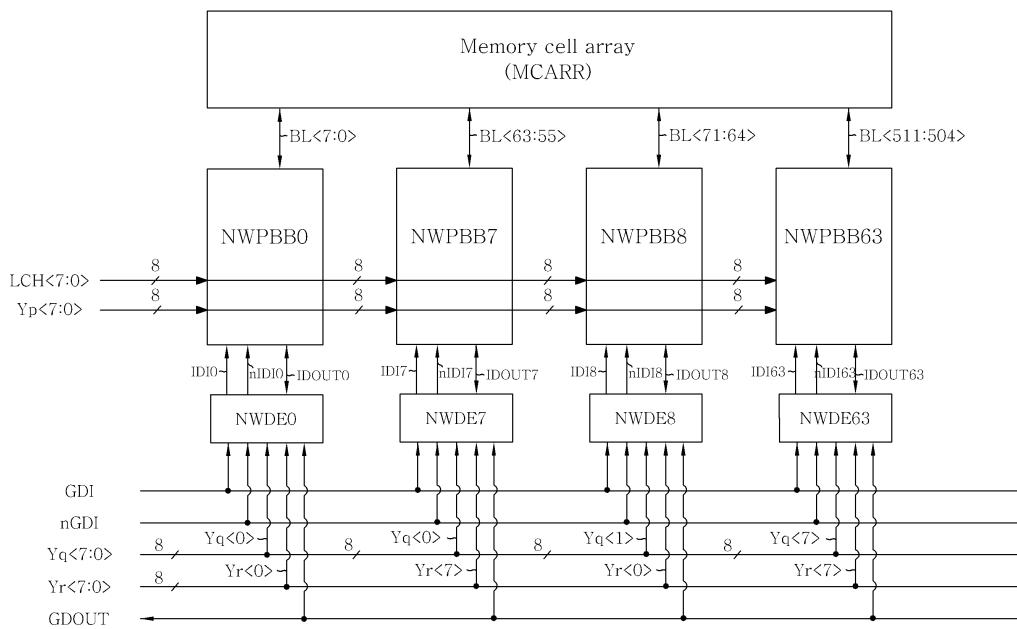

도 11은 본 발명의 일실시예에 따른 불휘발성 반도체 메모리 장치의 개략적인 블락 다이어그램이다.

도 11을 참조하면, 본 실시예의 상기 불휘발성 반도체 메모리 장치는 메모리셀 어레이(MCARR), 페이지 버퍼블락들(NWPBB<63:0>), 제1 및 제2 글로벌 입력 라인들(GDI/nGDI), 글로벌 출력 라인(GDOUT), y 어드레스 라인들(Yp<7:0>, Yq<7:0> 및 Yr<7:0>), 독출래치신호들(LCH<7:0>), 및 페이지 버퍼 디코더들(NWDE<63:0>)을 포함한다.

상기 메모리셀 어레이(MCARR)는 메모리 셀들의 매트릭스 어레이, 워드라인들(WL, 도 11에는 미도시) 및 비트라인(BL<511:0>)들을 포함한다. 본 실시예에서는, 상기 메모리 셀들은 플래시 메모리 셀 트랜지스터들이다.

내부 입력 라인들(IDI<63:0> 및 nIDI<63:0>), 및 내부 출력 라인들(IDOUT<63:0>)은, 상기 페이지 버퍼 디코더들(NWED<63:0>) 및 대응하는 페이지 버퍼블락들(NWPBB<63:0>) 사이에 연결된다.

상기 제1 글로벌 입력 라인(GDI)과 상기 제2 글로벌 입력 라인(nGDI)은 소정의 동작 구간, 예컨대, 독출 모드(read mode), 프로그램 모드(program mode) 및, 소거 모드(erase mode), 동안에 상반된 논리 상태의 입력 데이터를 전송한다.

보다 상세히 후술되는 바와 같이, 상기 페이지 버퍼 디코더들(NWDE<63:0>) 각각은, 상기 내부 입력 라인들(IDI<63:0> 및 nIDI<63:0>)의 데이터들을 출력하기 위하여, 상기 입력 데이터(GDI 및 nGDI)을 상기 y 어드레스 데이터(Yq<7:0>/Yr<7:0>)와 함께 디코딩한다.

또한, 상기 페이지 버퍼 디코더들(NWED<63:0>) 각각은 상기 내부 출력 라인들(IDOUT<63:0>) 상의 데이터에 대응하는 데이터를 상기 글로벌 출력 라인(GDOUT)으로 제공한다.

상기 페이지 버퍼블락들(NWPBB<63:0>)은 상기 래치신호라인(LCH<7:0>)들과 상기 y 어드레스(Yp<7:0>)에 응답한다. 여기서 후술되는 바와 같이, 상기 페이지 버퍼블락들(NWPBB<63:0>)은 내부 입력 라인들(IDI<63:0> 및 nIDI<63:0>) 상

에 대응하는 입력 데이터를 일시적으로 저장하고 나서 비트라인들(BL<511:0>)으로 전송하며, 또한, 비트라인들(BL<511:0>) 상의 데이터에 대응하는 출력 데이터를 일시적으로 저장하고 나서 내부 출력 라인들(IDOUT<63:0>)로 전송하는 기능을 수행한다.

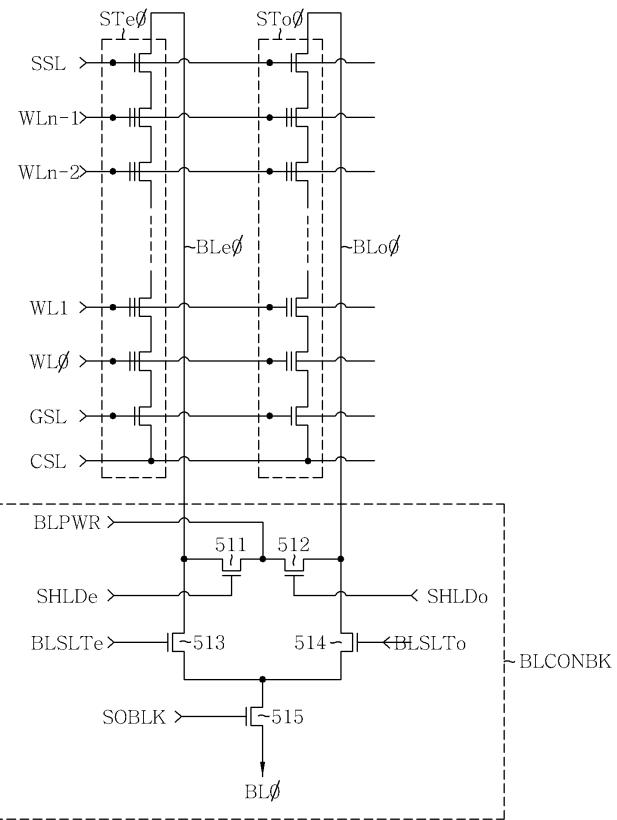

도 12는 본 실시예에 따른 도 11의 상기 메모리셀 어레이(MCARR)의 일부분을 나타내는 도면이다. 특히, 도 12는 도 11의 상기 제1 비트라인(BL0)의 상기 메모리셀 스트링들에 관련된 회로를 나타낸다. 비트라인들(BL<511:1>)은 유사하게 구현된다.

위에서 논의된 바와 같이, 상기 메모리셀 어레이(MCARR)는 일반적으로 메모리셀들(MC)의 매트릭스 어레이, 복수개의 워드라인들(WL<n-1:0>) 및 복수개의 비트라인들(BL<511:0>)을 포함한다. 상기 실시예의 상기 불휘발성 반도체 메모리장치의 상기 메모리셀들(MC)은 낸드(NAND) 타입의 플래시 메모리셀들이다.

도 12는 도 11의 상기 비트라인(BL0)에 맞추어지는 상기 이븐(even) 및 상기 오드(odd) 비트라인들(BLe0 및 BLo0)에 연결되는 상기 제 1 및 제 2 스트링들(STe0 및 STo0)을 나타낸다. 각 스트링(STe0 및 STo0)은 선택 라인들(SSL 및 GSL)에 연결되는 상기 메모리셀들의 양측의 끝단에 위치하는 트랜지스터들을 포함한다. 도시된 바와 같이, 상기 선택 라인들(SSL 및 GSL)은 상기 워드라인들(WL<n-1:0>)에 평행하게 달린다. 또한, 각 스트링(STe0 및 STo0)은 공통 소오스 라인(CSL)에서 끝난다.

상기 이븐 및 오드 비트라인들은 비트라인 제어블락(BLCONBK)에 연결된다. 앞서 논의된 도 11의 설명의 편의와 간편화를 위하여, 상기 비트라인 제어블락(BLCONBK)이 상기 메모리셀 어레이(MCARR)의 일부를 형성하는 것으로 기술되었다. 그러나, 또한 상기 비트라인 제어블락(BLCONBK)은 상기 메모리셀 어레이(MCARR)와 격리되고 구별되는 회로로서 나타날 수도 있다.

독출, 프로그램 및 소거 동작 모드들 각각에서는, 상기 비트라인 제어블락(BLCONBK)은 상기 이븐 비트라인 및 오드 비트라인(BLe0 및 BLo0) 중에서 하나를 선택하고, 상기 선택된 비트라인을 상기 비트라인(BL0)에 연결한다. 이러한 동작은 센스 노드 블락킹 신호(SOBLK)에 의해 제어되는 상기 트랜지스터(515) 및 상기 이븐 비트라인 선택신호(BLSLTe) 및 상기 오드 비트라인 선택신호(BSLSTo)에 의해 각각으로 제어되는 상기 트랜지스터들(513, 514)에 의해 수행된다.

추가적으로, 상기 비트라인 제어블락(BLCONBK)은 상기 독출, 프로그램 모드 및 소거 동작 모드들에서 상기 이븐 비트라인(BLe0) 및 상기 오드 비트라인(BLo0)의 상기 전압을 프리차아지하거나 조절하도록 작용한다. 트랜지스터들(511, 512)이 이러한 목적을 위하여 제공된다. 즉, 트랜지스터(511)은 비트라인 파워전압(BLPWR)을 상기 이븐 비트라인(BLe0)으로 선택적으로 연결하기 위한 이븐 차단 신호(SHLD)e에 응답하고, 상기 트랜지스터(512)는 상기 비트라인 파워전압(BLPWR)을 상기 오드 비트라인(BLo0)에 선택적으로 연결하기 위한 오드 차단신호(SHLD)o에 응답한다.

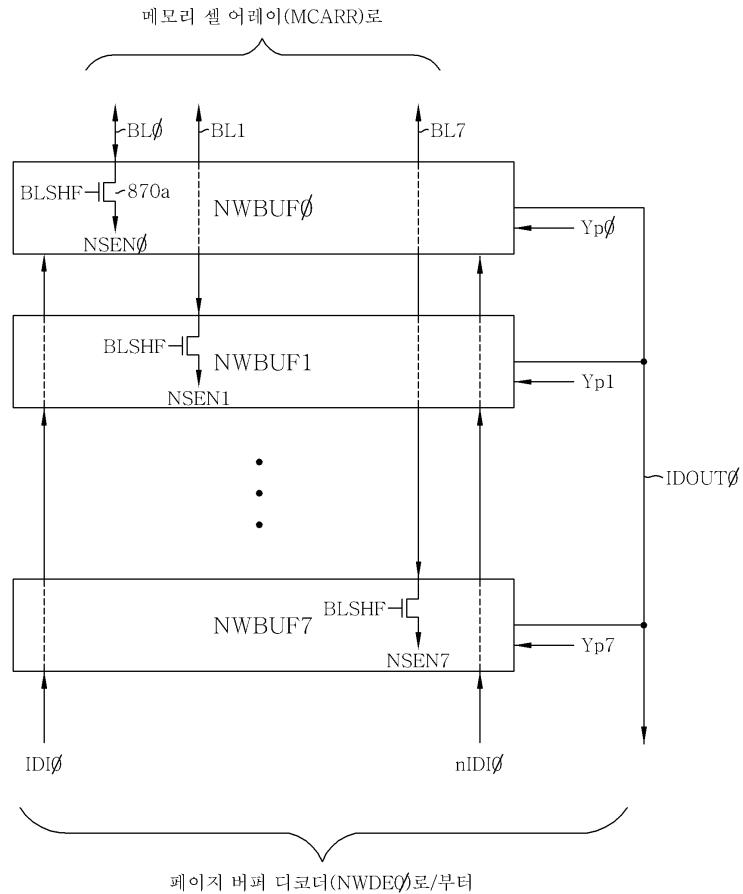

도 13은 도 11에 도시된 상기 페이지 버퍼블락(NWPBBO)의 예를 도시한다. 나머지 페이지 버퍼블락들(NWPBB<63:1>)도 유사한 구성을 가진다.

도 13의 상기 페이지 버퍼블락(NWPBBO)은 복수개의 페이지 버퍼들(NWBUF<7:0>), 내부 출력 라인(IDOUT0), 제1 내부 입력 라인(IDIO) 및 제2 내부 입력 라인(nIDIO)을 포함한다. 상기 페이지 버퍼들(NWBUF<7:0>)은 상기 비트라인들로(BL<7:0>) 전송되는 데이터 및 상기 비트라인들(BL<7:0>)로부터 수신되는 데이터를 각각 저장한다.

상기 내부 출력 라인(IDOUT0)은 상기 페이지 버퍼블락(NWPBBO)에 대한 공통 내부 출력 라인이고, 상기 페이지 버퍼들(NWBUF<7:0>) 중에서 어느 하나에 저장된 상기 데이터에 대응하는 출력 데이터를 전송한다.

상기 제1 내부 입력 라인(IDIO) 및 상기 제2 내부 입력 라인(nIDIO)은 입력 데이터에 기초하여 상기 페이지 버퍼들(NWBUF<7:0>)에서의 데이터 저장을 제어하는 신호들을 공급한다.

필요한 레이아웃 면적을 최소화하기 위해, 상기 페이지 버퍼블락(NWPBBO)에 포함되는 상기 페이지 버퍼들(NWBUF<7:0>)은 적층구조 즉, 상기 페이지 버퍼 디코더(NWDE0)와 상기 메모리셀 어레이(MCARR) 사이에 병치(並置)되는 구조로 배치된다.

상기 페이지 버퍼블록(NWPBB)의 상기 페이지 버퍼들(NWBUF<7:0>) 각각은 상기 내부 입력 라인들(IDIO 및 nIDIO)과 상기 비트라인들(BL<7:0>) 중에서 대응하는 하나 사이에 연결된다. 또한, 상기 페이지 버퍼들(NWBUF<7:0>) 각각은 상기 대응하는 비트라인(BL<7:0>)을 각각의 센스 노드(NSEN<7:0>)에 연결하는 비트라인 차단신호(BLSHF)에 응답하는 트랜지스터(870a)를 구비한다.

또한, 상기 페이지 버퍼들(NWBUF<7:0>) 각각은 각자의 y 어드레스 신호들(Yp<7:0>)을 수신한다. 종래의 메모리 장치와는 달리, 본 실시예에서는, 이러한 어드레스 신호들(Yp<7:0>)은 상기 각각의 페이지 버퍼들(NWBUF<7:0>)에 직접적으로 연결된다(도 11도 참조). 후술되는 바와 같이, 이것은 상기 메모리의 버스영역에 제공되는 라인의 갯수를 축소시키고, 상기 메모리의 상기 y 어드레스 라인들의 전체의 갯수를 축소시키는 이중의 장점을 초래한다. 여기서, 상기 어드레스 신호들(Yp<7:0>)은 버퍼선택신호들로서 언급된다.

도 13에 도시된 바와 같이, 바람직하기로는 상기 내부출력 라인(IDOUT0)은 상기 페이지 버퍼들(NWBUF<7:0>)이 적층된 방향으로 확장된다. 이에 따라, 상기 각각의 페이지 버퍼들(NWBUF<7:0>)로부터 상기 내부출력 라인(IDOUT0)까지의 전송라인의 거리들의 편차(deviation)가 최소화된다. 이것은 상기 페이지 버퍼들(NWBUF<7:0>)로부터 상기 내부출력 라인(IDOUT0)으로 데이터가 로딩될 때 신호의 균일성을 증가시켜서, 상기 불휘발성 메모리의 상기 센싱 마진(sensing margin)을 강화한다.

또한, 본 실시예에서는, 상기 내부출력 라인(IDOUT0)이 상기 페이지 버퍼들(NWBUF<7:0>)에 의해 공유된다. 이러한 구조로부터 기인(起因)하는 한가지 장점은 종래의 메모리(도 10 참조)에서의 상기 내부 데이터 라인들(IDB<7:0>)의 기생적인 커플링(parasitic coupling)과 관련된 문제점들이 회피(回避)될 수 할 수 있다는 것이다.

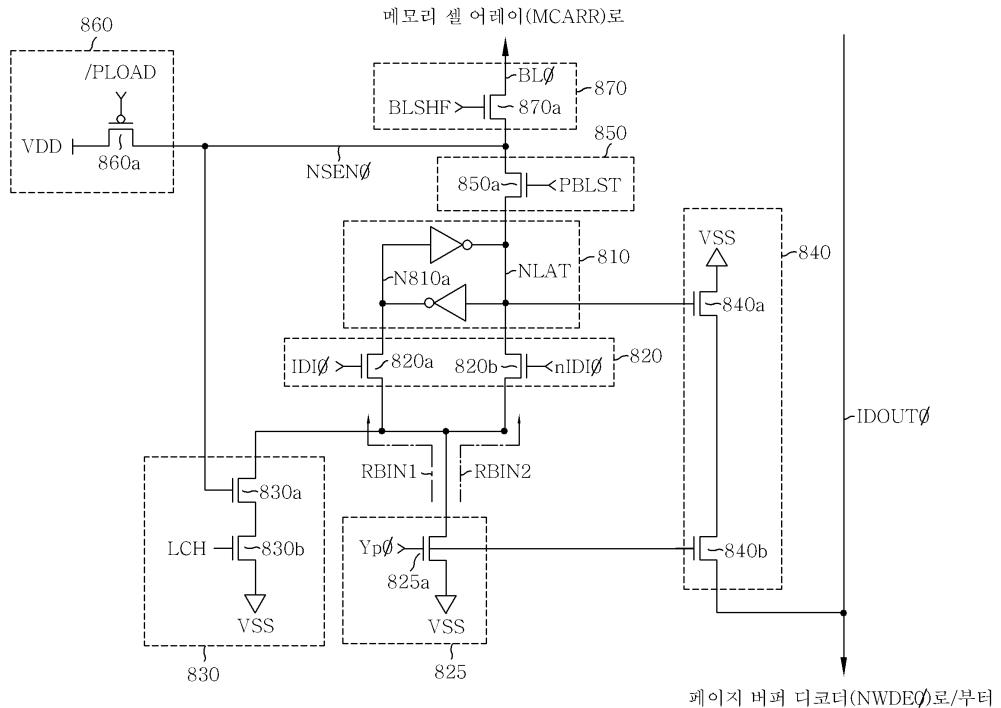

도 14는 도 13의 상기 페이지 버퍼(NWBUFO)의 일예를 도시한다. 나머지 페이지 버퍼들(NWBUF<7:1>)도 유사하게 구성된다.

도 14에 도시되는 바와 같이, 상기 페이지 버퍼(NWBUFO)는 상기 센싱 노드(NSEN0), 래치 유닛(810), 래치 전송 유닛(820), 래치 드라이빙 유닛(825), 센싱응답 유닛(830), 출력 드라이빙 유닛(840), 버퍼선택 유닛(850), 센싱셋팅 유닛(860), 비트라인 차단 유닛(870) 및 상기 내부출력 라인(IDOUT0)을 포함한다. 상기 센싱 노드(NSEN0)는 상기 비트라인(BL0)으로부터 제공된 데이터를 수신하며, 상기 비트라인 차단 유닛(870)을 통하여 상기 비트라인(BL0)에 연결된다.

상기 비트라인 차단 유닛(870)은 상기 비트라인 차단신호(BLSHF)에 응답하여 상기 비트라인(BL0)과 사기 센싱 노드(NSEN0)의 연결을 제어한다. 바람직하게는, 상기 비트라인 차단 유닛(870)은 비트라인 차단 트랜지스터(870a)을 사용하여 구현되며, 상기 비트라인 차단 트랜지스터(870a)는 상기 비트라인 차단 신호(BLSHF)에 응답하여 게이팅되는 낮은 전압의 엔모스(NMOS) 트랜지스터이다.

상기 래치 유닛(810)은 상기 비트라인(BL0)의 데이터에 대응하는 데이터를 저장하는 래치 노드(NLAT)를 포함한다.

상기 래치 드라이빙 유닛(825)은, 소정의 래치 드라이빙 전압을 제공하기 위하여, 상기 버퍼 선택 어드레스(Yp0)에 응답하여 인에이블된다. 본 실시예에서는, 상기 래치 드라이빙 전압은 접지전압(VSS)이고, 상기 래치전송 유닛(820)으로 제공되는 상기 제1 및 제2 내부 입력 라인들(IDIO 및 nIDIO) 상의 데이터에 독립적이다. 본 실시예의 상기 래치 드라이빙 유닛(825)은 래치 드라이빙 트랜지스터(825a)를 포함한다. 바람직하기로는, 상기 래치 드라이빙 트랜지스터(825a)는 상기 버퍼 선택 어드레스(Yp0)에 응답하여 게이팅되며, 상기 접지(GROUND) 전압(VSS)에 연결되는 소오스 단자를 가지는 엔모스(NMOS) 트랜지스터이다.

본 실시예의 상기 래치전송 유닛(820)은 제1 및 제2 래치 전송 트랜지스터(820a 및 820b)를 포함한다. 상기 제1 래치 전송 트랜지스터는(820a)는, 상기 제1 내부 입력 라인(IDIO)에 응답하여, 상기 래치 드라이빙 트랜지스터(825a)로부터 제공되는 상기 래치 드라이빙 전압을 상기 래치 유닛(810)의 노드(N810a)로 제공한다. 바람직하게는, 상기 제1 래치 전송 트랜지스터(820a)는 상기 래치 드라이빙 트랜지스터(825a)에 연결되며, 상기 제1 내부 입력 라인(IDIO) 상의 데이터에 응답하여 게이팅된다. 그러므로, 상기 버퍼 선택 어드레스(Yp0)가 논리 "H" 상태에 있을 때, 논리 "H" 상태의 데이터가 상기 제1 내부 입력 라인(DIO)에 인가되면, 상기 제1 래치 전송 트랜지스터(820a)는 상기 접지전압(VSS)을 상기 래치 유닛(810)의 래치 노드(N810a)로 제공한다.

본 예의 상기 제2 래치 전송 트랜지스터(820b)는 상기 제2 내부 입력 라인(nIDIO)에 응답하여, 상기 래치 드라이빙 트랜지스터(825a)로부터 제공되는 상기 래치 드라이빙 전압을 상기 래치 유닛(810)의 래치 노드(NLAT)로 제공한다. 바람직하

게는, 상기 제2 래치 전송 트랜지스터(820b)는 상기 래치 드라이빙 트랜지스터(825a)와 직렬적으로 연결되며, 상기 제2 내부 입력 라인(nIDIO) 상의 데이터에 응답하여 게이팅된다. 그러므로, 상기 버퍼선택 어드레스(Yp0)가 논리 "H" 상태에 있을 때, 논리 "H" 상태의 데이터가 상기 제2 내부 입력 라인(nIDIO)에 인가되면, 상기 제2 래치 전송 트랜지스터(802b)는 상기 접지전압(VSS)을 상기 래치 유닛(810)의 상기 래치 노드(NLAT)에 제공한다.

즉, 본 실시예에서는, 상기 제1 래치 전송 트랜지스터(820a)가 턴 온(ON)될 때, 논리 "H"의 데이터가 상기 래치 노드(NLAT) 상에 저장된다. 반면에, 상기 제2 래치 전송 트랜지스터(820b)가 턴 온(ON)될 때, 논리 "L"의 데이터가 상기 래치 노드(NLAT) 상에 저장된다.

도 14에서, 참조부호 RBIN1 및 RBIN2은 상기 래치 드라이빙 전압이 상기 래치 유닛(810)으로 전송되는 버퍼입력패스를 나타낸다. 즉, 상기 래치 드라이빙 트랜지스터(825a) 및 상기 제1 래치 전송 트랜지스터(820a)를 통하여 상기 래치 노드(NLAT)에 이르는 전송 패스는 제1 버퍼입력패스(RBIN1)로 나타나며, 상기 래치 드라이빙 트랜지스터(825a) 및 상기 제1 래치 전송 트랜지스터(820b)를 통하여 상기 래치 노드(NLAT)에 이르는 전송 패스는 제2 버퍼입력패스(RBIN2)로 나타난다.

본 예의 상기 센싱응답 유닛(830)은 센싱 응답 전압을 상기 래치전송 유닛(820)으로 전송하도록 센싱 노드(NSEN0)에 의하여 구동되어서, 상기 래치 노드에 저장되는 데이터를 제어한다. 바람직하기로는, 상기 센싱 응답 전압은 접지전압이다. 상기 센싱응답 유닛(830)은 예로서, 센싱 응답 트랜지스터(830a) 및 출력 센싱 트랜지스터(830b)를 포함한다.

바람직하게는, 상기 센싱 응답 트랜지스터(830a)는 상기 센싱 노드(NSEN0) 상의 데이터에 응답하여 게이팅되는 엔모스(NMOS) 트랜지스터이다. 상기 출력 센싱 트랜지스터(830b)는 상기 센싱 응답 트랜지스터(820a)와 직렬적으로 배열되는 엔모스(NMOS) 트랜지스터이며, 상기 접지전압(VSS)에 연결되는 소오스 단자를 가진다. 상기 센싱 응답 트랜지스터(830a)가 턴 온될 때, 상기 출력 센싱 트랜지스터(830b)는 상기 센싱 응답 전압을 상기 래치전송 유닛(820)을 통하여 상기 래치 유닛(810)으로 제공하도록 독출래치신호(LCH)에 응답한다. 또한, 상기 래치 노드(NLAT)는 센싱 응답 전압에 응답하여 상기 센싱 노드(NSEN0)에 대응하는 데이터를 저장한다.

상기 센싱셋팅 유닛(860)은 상기 센싱 노드(NSEN0)를 소정의 셋팅 전압으로 설정한다. 본 예에서는, 상기 셋팅 전압은 전원전압(VDD)이고, 상기 센싱셋팅 유닛(860)은 센싱 셋팅 트랜지스터(860a)를 포함한다. 바람직하게는, 상기 센싱 셋팅 트랜지스터(860a)는 전원전압에 연결되는 소오스 단자를 가지는 피모스(PMOS) 트랜지스터이며, 센싱셋팅신호(/PLOAD)에 응답하여 게이팅된다.

상기 출력 드라이빙 유닛(840)은 상기 버퍼 선택 어드레스(Yp0)에 응답하여 인에이블된다. 상기 출력 드라이빙 유닛(840)은, 인에이블될 때, 상기 래치 노드(NLAT) 상에 저장된 데이터에 응답하여 상기 내부출력 라인(IDOUT0)을 소정의 드라이브 전압으로 드라이브한다. 도 14에 도시된 바와 같이, 상기 내부출력 라인(IDOUT0)은 상기 래치 노드(NLAT) 및 상기 버퍼입력패스들(RBIN1 및 RBIN2)과 격리되며 전기적으로 분리된다.

상기 출력 드라이빙 유닛(840)은, 예를 들면, 제1 출력 드라이빙 트랜지스터(840a) 및 제2 출력 드라이빙 트랜지스터(840b)를 포함한다. 상기 제1 출력 드라이빙 트랜지스터(840a)는 상기 래치 유닛(810)의 상기 래치 노드(NLAT) 상에 저장된 상기 데이터에 의해 게이팅된다. 본 실시예에서는, 상기 래치 유닛(810)의 상기 래치 노드(NLAT) 상에 저장된 데이터가 논리 "H"일 때, 상기 제1 출력 드라이빙 트랜지스터(840a)는 턴 온(ON) 된다. 상기 제2 출력 드라이빙 트랜지스터(840b)는 상기 제1 출력 드라이빙 트랜지스터(840a)와 직렬적으로 연결된다. 상기 제2 출력 드라이빙 트랜지스터(840b)는, 상기 내부출력 라인(IDOUT0)을 상기 드라이브 전압으로 드라이브하도록, 상기 버퍼 선택 어드레스(Yp0)에 응답하여 게이팅된다. 본 예에서는, 상기 드라이브 전압은 상기 제1 출력 드라이빙 트랜지스터(840a)의 상기 소오스 단자에 연결되는 상기 접지전압(VSS)이다. 그래서, 본 실시예에 따르면, 상기 래치 노드(NLAT)에 저장된 데이터가 논리 "H" 상태일 때, 상기 내부출력 라인(IDOUT0)은, 상기 버퍼 선택 어드레스(Yp0)가 상기 논리 "H" 상태로 천이됨에 응답하여, 상기 접지전압(VSS)으로 드라이빙된다.

본 예에서의 상기 버퍼선택 유닛(850)은 상기 래치 노드(NLAT)와의 상기 센싱 노드(NSEN0)의 연결을 제어한다. 본 예에서는, 상기 버퍼선택 유닛(850)은 버퍼 선택 트랜지스터(850a)를 포함하며, 상기 버퍼선택 트랜지스터(850a)는 버퍼선택신호(PBSLT)에 응답하여 게이팅되는 엔모스(NMOS) 트랜지스터이다. 상기 버퍼선택신호(PBSLT)의 상기 전압레벨이 논리 "H" 상태로 변화될 때, 상기 래치 노드(NALT) 상의 데이터는 상기 버퍼선택 트랜지스터(850a)를 통하여 상기 센싱 노드(NSEN0)로 전송되며, 나아가 상기 비트라인(BL0)에 전송된다.

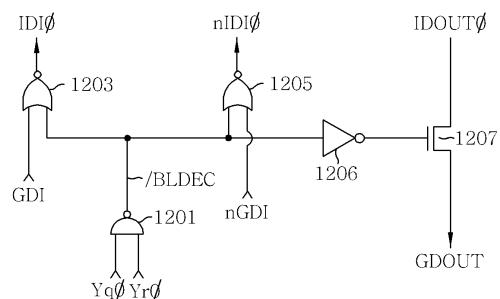

도 15는 도 11에 도시된 상기 페이지 버퍼 디코더(NWDE0)의 일 예를 도시한다. 나머지 페이지 버퍼 디코더들(NWDE<63:1>)도 유사하게 구성될 수 있다.

상기 페이지 버퍼 디코더(NWDE0)는 2가지 주요한 기능을 가진다. 첫째, 상기 페이지 버퍼 디코더(NWDE0)는 상기 내부 출력 라인(IDOUT0) 상의 데이터에 대응하는 출력 데이터를 상기 글로벌 출력 라인(GDOUT)으로 선택적으로 전송한다. 둘째, 상기 페이지 버퍼 디코더(NWDE0)는 상기 제1 글로벌 입력 라인(GDI) 및 상기 제2 글로벌 입력 라인(nGDI) 상의 입력 데이터에 대응하는 데이터를 상기 제1 내부 입력 라인(IDIO) 및 상기 제2 내부 입력 라인(nIDIO)으로 각각 전송한다.

도 15의 예에서의 상기 페이지 버퍼 디코더(NWDE0)는 제1 내지 제3 디코더 논리 게이트들(1201, 1203 및 1205), 인버터(1206) 및 디코더 트랜지스터(1207)를 포함한다.

여기서는, 상기 y 어드레스 신호들(Yq<7:0>)은 메인선택 어드레스들로서 언급되고, 상기 y 어드레스 신호들(Yp<7:0>)은 서브 어드레스들로서 언급된다(도 11을 참조).

상기 제1 디코더 논리 게이트(1201)는 메인선택 어드레스(Yq0)와 서브선택 어드레스(Yr0)의 논리 연산을 수행하며, 상기 논리 연산의 결과를 블락 디코딩 신호(/BLDEC)로 출력한다. 본 예에서는, 상기 제1 디코더 논리 게이트(1201)는 상기 메인선택 어드레스(Yq0)와 상기 서브선택 어드레스(Yr0)의 낸드(NAND) 연산을 수행하며, 상기 낸드(NAND) 연산의 결과를 상기 블락 디코딩 신호(/BLDEC)로서 출력한다. 이 경우에서, 상기 메인선택 어드레스(Yq0)와 상기 서브선택 어드레스(Yr0)가 모두 논리 "H" 상태로 액티브될 때, 상기 블락 디코딩 신호(/BLDEC)는 논리 "L" 상태로 액티브된다.

상기 제2 디코더 논리 게이트(1203)는 상기 블락 디코딩 신호(/BLDEC)에 응답하여 인에이블되며, 상기 제1 글로벌 입력 라인(GDI) 상의 데이터에 따른 상기 논리 연산의 결과를 상기 내부 입력 라인(IDIO)으로 제공한다. 본 예에서는, 상기 제2 디코더 논리 게이트(1203)는 상기 블락 디코딩 신호(/BLDEC)와 상기 제1 글로벌 입력 라인(GDI) 상의 데이터에 노아(NOR) 연산을 수행하는 노아(NOR) 게이트이다. 이 경우에서, 상기 블락 디코딩 신호(/BLDEC)가 논리 "L" 상태일 때(예컨대, 상기 메인선택 어드레스(Yq0)와 상기 서브선택 어드레스(Yr0)가 모두 논리 "H" 상태일 때), 상기 제2 디코더 논리 게이트(1203)는 상기 제1 글로벌 입력 라인(GDI) 상의 데이터를 반전하며, 상기 반전된 결과를 상기 제1 내부 입력 라인(IDIO)으로 제공한다.

상기 제3 디코더 논리 게이트(1205)는 상기 블락 디코딩 신호(/BLDEC)에 응답하여 인에이블되며, 상기 제2 글로벌 입력 라인(nIDIO) 상의 데이터에 따른 논리 연산 결과를 상기 제2 내부 입력 라인(nIDIO)으로 제공한다. 본 예에서는, 상기 제3 디코더 논리 게이트(1205)는 상기 블락 디코딩 신호(/BLDEC)와 상기 제2 글로벌 입력 라인(nGDI) 상의 데이터에 노아(NOR) 연산을 수행하는 노아(NOR) 게이트이다. 이 경우에서, 상기 블락 디코딩 신호가 논리 "L" 상태일 때(상기 메인선택 어드레스(Yq0)와 상기 서브선택 어드레스(Yr0)가 모두 논리 "H" 상태일 때), 상기 제3 디코더 논리 게이트(1205)는 상기 제2 글로벌 입력 라인(nGDI) 상의 데이터를 반전하며, 상기 반전된 데이터를 상기 제2 내부 입력 라인(nIDIO)으로 제공한다.

상기 인버터(1206)는 상기 블락 디코딩 신호(/BLDEC)를 반전하여 상기 디코더 트랜지스터(1207)를 게이팅한다. 본 예에서는, 상기 디코더 트랜지스터(1207)는 상기 블락 디코딩 신호(/BLDEC)가 논리 "L" 상태로 액티브될 때, 상기 내부 출력 라인(IDOUT0) 상의 데이터를 상기 글로벌 출력 라인(GDOUT)으로 제공한다.

본 실시예에서, 상기 불휘발성 메모리는 64개의 페이지 버퍼 디코더들(NWDE<63:0>)을 포함한다. 상기 페이지 버퍼 디코더들(NWDE<63:0>)은 상기 메인선택 어드레스(Yq<7:0>)들과 상기 서브선택 어드레스(Yr<7:0>)들의 조합에 기초하여 개별적으로 선택된다. 상기 메인선택 어드레스(Yq<7:0>)들은 상기 64개의 페이지 버퍼 디코더들(NWDE<63:0>) 가운데에서, 각각이 8개의 버퍼 디코더들을 가지는 8개의 그룹들의 하나를 선택하는데 사용되고, 상기 서브선택 어드레스(Yr<7:0>)들은 상기 선택된 그룹에 포함된 8개의 페이지 버퍼 디코더들 중에서 어느 하나를 선택하는데 사용된다. 또한, 전술한 바와 같이, 상기 버퍼 선택 어드레스들(Yp<7:0>)은 상기 선택된 버퍼 디코더와 관련된 8개의 페이지 버퍼들 중에서 각자의 것들을 선택하는데 사용된다.

이와 같이, 본 실시예의 예에서는, 칼럼 어드레스 버스 라인들의 총 갯수가 24인데, 이는 도 8에 도시된 종래의 메모리 장치의 40개의 칼럼 어드레스 라인들에 비해 매우 유리한다.

또한, 상술한 바와 같이, 내부출력 라인(IDOUT0)는 상기 래치 노드(NLAT) 및 상기 버퍼입력 패스(RBIN1 및 RBIN2)로부터 전기적으로 분리된다. 그래서, 그렇지 않으면 다른 페이지 버퍼들(예를 들면, 'NWBUF<7:1>')에 저장된 데이터 및 상기 내부출력 라인(IDOUT0)에 차아지된 데이터에 의하여 발생될 수 있는 선택된 페이지 버퍼(예를 들면, 'NWBUF0')의 래치 노드(NLAT) 상에 저장된 데이터의 왜곡은 최소화될 수 있다.

상술한 실시예들의 독출, 프로그램 및 소거 동작 모드들의 예들이 기술된다. 하기(下記)의 각 설명에서, 이전에 살펴본 도면들이 참조된다.

독출 동작 모드가 도 16a 및 도 16b를 참조하여 먼저 논의된다.

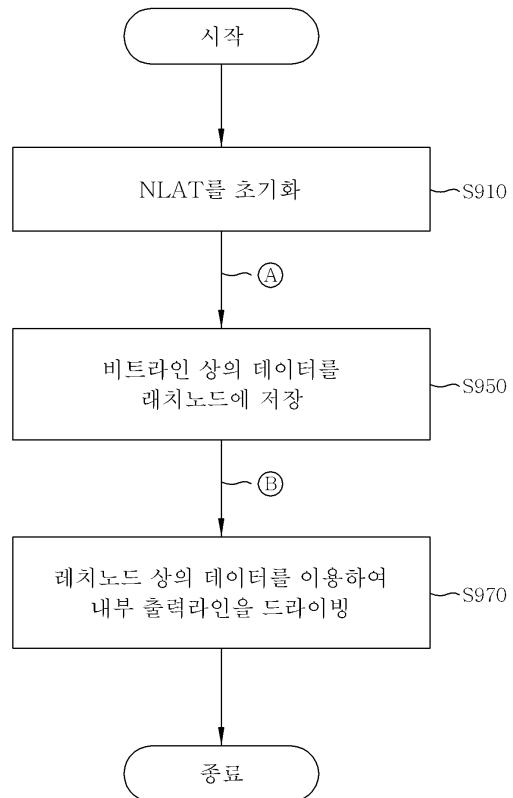

도 16a는 선택되는 메모리 셀(MCsel)에 저장된 데이터를 출력하기 위한 페이지 버퍼(NWBUF)의 구동방법을 설명하기 위한 플로우차트(flowchart)이다.(도 12를 참조)

S910단계에서, 상기 래치 노드(NLAT)는 논리 "H" 상태("제1 논리 상태") 또는 논리 "L" 상태("제2 논리 상태")의 데이터로 초기화된다. 상기 래치 노드(NLAT)의 초기화는 상기 제1 내부 입력 라인(IDIO)과 상기 제2 내부 입력 라인(nIDIO) 중에서 어느 하나에 의하여 수행될 수 있다.

본 실시예의 상기 예의 노말(normal) 독출 동작 상의(operational) 모드에서, 상기 래치 노드(NLAT)는 상기 제2 논리상태의 데이터로 초기화된다. 상기 래치 노드의 상기 제2 논리 상태로의 초기화를 위하여, 상기 버퍼 선택 어드레스(Yp0)는 논리 "H" 펠스가 되며, 상기 제2 내부 입력 라인(nIDIO)도 논리 "H" 펠스가 된다. 이때, 상기 제1 내부 입력 라인(IDIO)은 논리 "L" 상태를 유지한다. 그러면, 상기 래치 노드(NLAT)는 논리 "L" 상태 즉, 상기 제2 논리상태의 데이터로 초기화된다.

반면에, 본 발명의 실시예의 소거 확인 독출 동작 모드에서, 상기 래치 노드(NLAT)는 상기 제1 논리상태의 데이터로 초기화된다. 상기 래치 노드(NLAT)의 제1 논리상태로의 초기화를 위하여, 상기 버퍼선택 어드레스(Yp0)는 논리 "H" 펠스가 되며, 상기 제1 내부 입력 라인(IDIO)도 논리 "H" 상태가 된다. 이때, 상기 제2 내부 입력 라인(nIDIO)은 논리 "L" 상태를 유지한다. 그러면, 상기 래치 노드(NLAT)는 논리 "H" 상태 즉, 상기 제1 논리 상태의 데이터로 초기화된다.

S950단계에서, 상기 선택되는 메모리 셀(MCsel)의 저장되는 데이터에 대응하여, 상기 비트라인(BLO) 상에 디벨로프되는(developed) 데이터가, 상기 래치 노드(NLAT)에 저장된다.

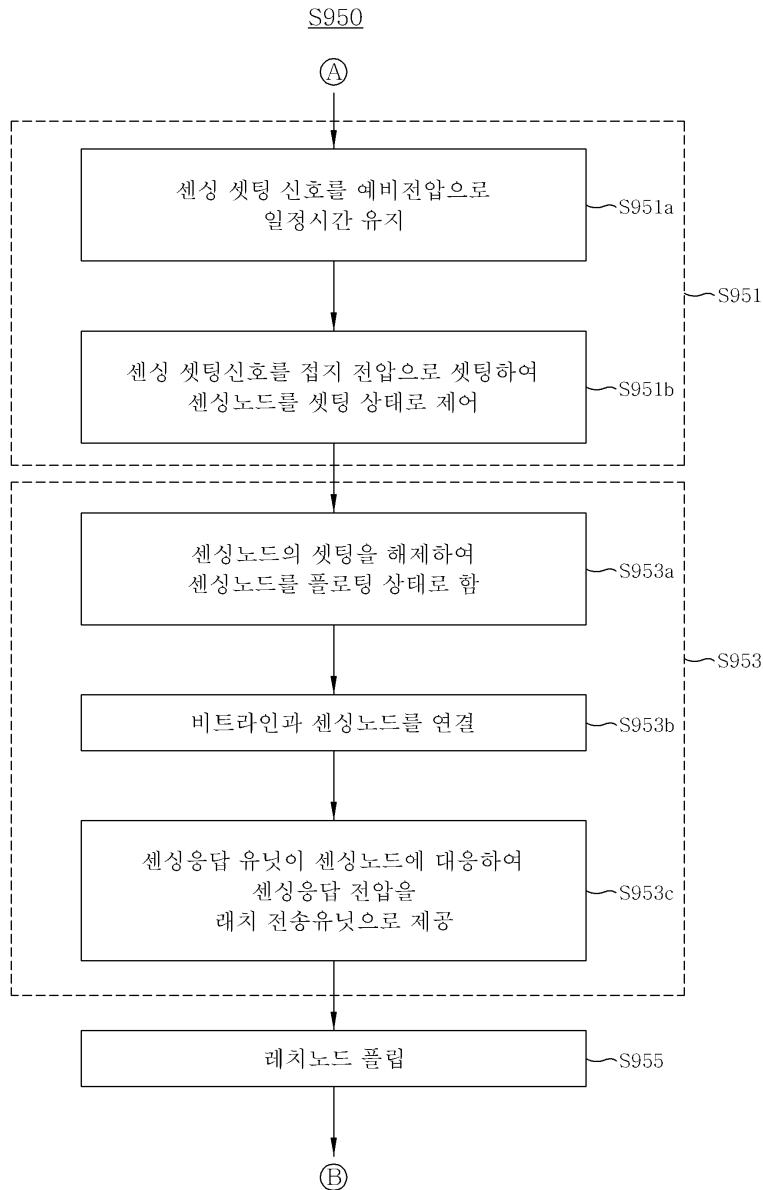

도 16b는 도 16a의 상기 S950단계에서 실행될 수 있는 S951단계, S953단계 및 S955단계를 설명하기 위한 플로우차트이다. 본 예에서는, S951a단계의 실행은 바람직하게 고려되나, 삭제될 수도 있다.

S951단계에서, 상기 센싱 노드(NSENO)는 상기 센싱셋팅 유닛(860)의 센싱 셋팅 트랜지스터(860a)에 의해 상기 전원전압(VDD) 즉, 상기 셋팅전압으로 제어된다. 상기 셋팅전압은, 상기 센싱 응답 전압을 상기 래치전송 유닛(820)으로 제공하도록, 상기 센싱응답 유닛(830)을 제어한다. 또한, 상기 비트라인 차단신호(BLSHF)는 논리 "L" 상태로 변화된다.

본 예에서는, S951단계는 S951a단계 및 S951b단계를 포함한다. S951a에서, 상기 센싱셋팅신호(/PLOAD)의 전압레벨은 전원전압(VDD)의 언더슈팅(undershooting)을 방지하기 위해, 소정의 시간 동안 제1 예비 전압(VPRE1)으로 유지된다. S951b단계에서, 상기 센싱셋팅신호(/PLOAD)는 논리 "L" 상태로 변화된다.

S953단계에서, 상기 센싱응답 유닛(830)은 상기 센싱응답전압을, 상기 비트라인(BLO) 상에 디벨로프된(developed) 데이터에 응답하여 상기 래치전송 유닛(820)으로 제공한다. 본 예에서, S953단계는 S953a단계, S953b단계 및 S953c단계를 포함한다.

S953a단계에서, 상기 센싱셋팅신호(/PLOAD)는 논리 "H" 상태로 된다. 이에따라, 상기 센싱 노드(NSENO)의 상기 셋팅상태는 해제되어, 상기 센싱 노드(NSENO)는 플로팅(floating) 상태로 변화된다. 또한, S953b단계에서, 상기 비트라인 차단트랜지스터(870a)는 턴온되어, 플로팅되는 상기 센싱 노드(NSENO)는 상기 비트라인(BLO)에 연결된다. 그러므로, 상기 센싱 노드(NSENO)는 상기 비트라인(BLO) 상의 디벨로프된 데이터를 수신한다.

결과적으로, 상기 선택되는 메모리 셀(MCsel)이 '오프셀'(OFF cell)인 경우, 상기 센싱 노드(NSENO)의 전압레벨은 대략 상기 전원전압(VDD)으로 유지된다. 반면에, 상기 선택되는 메모리 셀(MCsel)이 '온셀'(ON cell)인 경우, 상기 센싱 노드(NSENO)의 상기 전압레벨은 대략 접지전압(VSS)으로 유지된다.

S953c단계에서, 상기 센싱응답 유닛(830)은 상기 센싱 노드(NSENO)에 따라서 센싱 응답 전압을 상기 래치전송 유닛(820)에 선택적으로 제공한다. 즉, 상기 선택되는 메모리 셀(MCsel)이 '오프셀'(OFF cell)이고 상기 센싱 노드(NSENO)의 전압레벨이 대략 상기 전원전압(VDD)으로 유지될 때, 상기 독출 래치 신호(LCH)가 "H"펄스로 발생되면, 상기 센싱응답 유닛(830)은 상기 센싱응답전압(본 예에서는, 'VSS')을 상기 래치전송 유닛(820)으로 전송한다. 반면에, 상기 선택되는 메모리 셀(MCsel)이 '온셀'(ON cell)이고 상기 센싱 노드(NSENO)의 상기 전압레벨이 대략 상기 접지전압(VSS)으로 유지될 때, 상기 센싱응답전압은 상기 독출 래치 신호(LCH)가 "H"펄스로 발생되더라도 상기 래치전송 유닛(820)으로 제공되지 않는다.

S955단계에서, 상기 래치 노드(NLAT)는 상기 래치전송 유닛(820)에 공급되는 상기 센싱응답전압에 응답하여 플립된다.

S910단계와 관련하여 앞에서 논의된 바와 같이, 노말 독출 동작 모드에서, 상기 래치 노드(NLAT)는 상기 제2 논리상태의 데이터로 초기화된다. 이때, S955단계에서, 상기 제1 내부 입력 라인(IDIO)은 논리 "H" 상태이고, 상기 제2 내부 입력 라인(nIDIO)은 논리 "L" 상태이다. 그러므로, 선택되는 메모리셀(MCsel)이 '오프셀', 즉 프로그램된 셀일 때, 상기 래치 노드(NLAT)는 논리 "L" 상태(제2 논리상태)로부터 논리 "H" 상태(제1 논리상태)로 플립된다. 그러나, 상기 선택되는 메모리 셀(MCsel)이 '온셀'(ON cell), 즉 소거된 셀인 경우, 상기 래치 노드(NLAT)는 상기 논리 "L" 상태(제2 논리상태)를 그대로 유지한다.

반면에, 또한 S910단계와 관련하여 앞에서 기술된 바와 같이, 소거확인 독출동작 모드에서, 상기 래치 노드(NLAT)는 제1 논리상태의 데이터로 초기화된다. 이때, S955단계에서는, 상기 제1 내부 입력 라인(IDIO)은 논리 "L" 상태이고, 상기 제2 내부 입력 라인(nIDIO)은 논리 "H" 상태이다. 그러므로, 상기 선택되는 메모리 셀(MCsel)이 '오프셀', 즉, 소거되지 않은 셀인 경우, 상기 래치 노드(NLAT)는 상기 논리 "H" 상태로부터 논리 "L" 상태로 플립된다. 반면에, 상기 선택되는 메모리 셀이 '온셀'인 경우, 즉 소거된 셀인 경우, 상기 래치 노드(NLAT)는 상기 논리 "H" 상태(제1 논리상태)를 그대로 유지한다.

다시 도 16a를 참조하면, S970단계에서, 상기 출력 드라이빙 유닛(840)은 상기 래치 노드(NLAT) 상에 저장된 데이터에 의해 제어된다. 그러므로, 상기 내부출력 라인(IDIOUT0)은 드라이브 전압, 즉, 상기 접지전압(VSS)으로 선택적으로 드라이빙된다. 즉, 상기 래치 노드(NLAT) 상에 저장된 데이터가 논리 "H"인 경우, 상기 내부출력 라인(IDIOUT0)은 상기 버퍼 선택 어드레스(Yp0)에 응답하여 상기 접지전압(VSS)으로 드라이빙된다. 그러나, 상기 래치 노드(NLAT) 상에 저장되는 데이터가 논리 "L"인 경우에는, 상기 내부출력 라인(IDIOUT0)은, 상기 버퍼선택 어드레스(Yp0)가 논리 "H" 상태로 변화되더라도, 초기 논리 상태인 상기 전원전압(VDD)을 유지한다.

상기 노말 독출 동작 모드의 예는, 도 17의 타이밍 다이어그램을 참조하여 다음에 보다 자세히 기술된다.

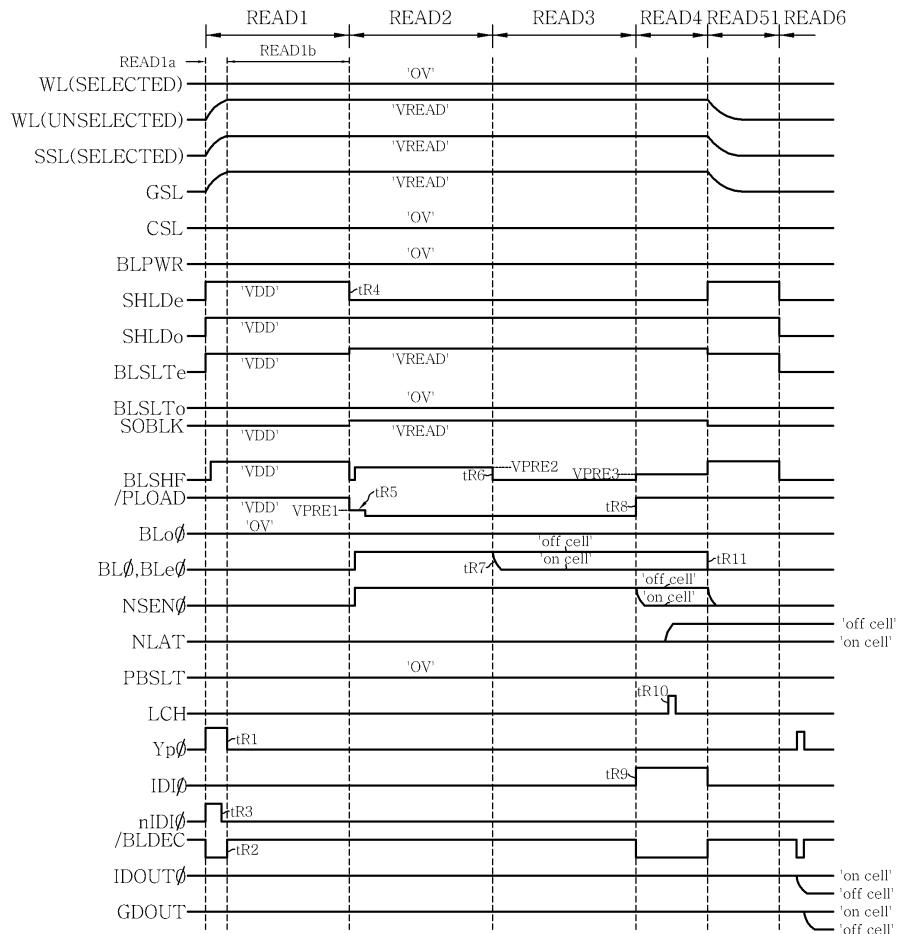

도 17은 도 11 내지 도 15의 상기한 예에서 도시된 상기 불휘발성 메모리 장치의 다양한 신호전압들 및 노드전압들을 나타내는 노말 독출 동작 모드(독출 모드)의 타이밍 다이어그램이다. 다시, 다음의 설명에서, 이전에 살펴본 도면들이 참조된다.

독출 모드에서는, 선택되는 메모리 셀(MCsel)에 기입된 데이터가 인출되고, 그리고 상기 인출된 데이터가 출력된다.

설명의 목적으로, 도 17에 도시되는 상기 독출모드는 6개의 구간들, 즉, 비트라인 디스차아지 및 페이지 버퍼 리셋 구간(이하, "READ1 구간"이라 함), 비트라인 프리차아지 구간(이하, "READ2 구간"이라 함), 비트라인 디벨로프 구간(이하, "READ3 구간"이라 함), 센싱 구간(이하, "READ4 구간"이라 함), 회복 구간(이하, "READ5 구간"이라 함), 데이터 인출 구간(이하, "READ6 구간"이라 함)의 6개의 구간으로 나누어진다.

다시, 설명의 목적으로, 상기 "READ1 구간"은 페이지 버퍼 리셋 구간(이하, 'READ1a 구간'이라 함) 및 비트라인 디스차아지 구간(이하, "READ1b 구간"이라 함)으로 나뉘어진다. 상기 READ1a 구간에서는, 상기 페이지 버퍼의 래치 노드(NLAT)가 논리 "L" 상태 즉, 상기 접지전압(VSS)로 리셋된다. 이후, 상기 READ1b 구간 동안에서는, 상기 이븐 비트라인(BLe0), 오드 비트라인(BLo0) 및 비트라인(BL0)이 상기 접지전압(VSS) 즉, 논리 "L" 상태의 데이터로 디스차아지된다.

상기 READ1a 구간에서의 상기 래치 노드(NLAT)의 리셋은 다음과 같이 일어난다. 상기 READ1a 구간에서, 상기 베퍼션 텍 어드레스(Yp0)는 논리"H" 상태이므로, 상기 래치 드라이빙 트랜지스터(825a)는 "턴온"이다(tR1). 그리고, 상기 메인선택 어드레스(Yq0)와 상기 서브 선택 어드레스(Yr0)가 모두 논리"H"이므로, 상기 블락 디코딩 신호(/BLDEC)는 논리"L"의 상태로 변화된다(tR2). 이때, 상기 제1 글로벌 입력 라인(GDI)은 논리"H"이고, 상기 제2 글로벌 입력 라인(nGDI)은 논리"L"이다. 그러므로, 상기 제1 내부 입력 라인(IDIO)은 논리"L"이고, 상기 제2 내부 입력 라인(nIDIO)은 논리"H"이다(tR3). 따라서, 상기 제1 래치 전송 트랜지스터(820a)는 턴오프(turn off)되며, 상기 제2 래치 전송 트랜지스터(820b)는 턴온(turn on)된다. 따라서, 상기 래치 유닛(810)의 상기 노드(N810a)는 논리"H"로 변화되고, 상기 래치 노드(NLAT)는 논리"L" 상태로 리셋된다.

상기 READ1b 구간에서의 상기 비트라인들(BLe0, BLo0 및 BL0)의 상기 디스차아지가 기술된다. 여기서, 설명의 편의를 위하여, 도 12의 상기 왼쪽 메모리셀 스트링(STe0)에서 최상위의 메모리셀(MCscl)이 선택되는 것으로 가정된다.

상기 'READ1b 구간'에서는, 독출전압(VREAD, 예를 들면, 5V)이 비선택되는 워드라인(WL<n-2:0>)에 인가되고, 접지전압(VSS)이 선택되는 워드라인(WLn-1)에 인가된다. 그리고, 상기 독출전압(VREAD)이 상기 스트링 선택라인(SSL) 및 상기 그라운드 선택라인(GSL)에 모두 인가되며, 상기 접지전압(VSS)이 상기 공통 소오스 라인(CSL)에 인가된다.

그리고, 비트라인 전압라인(BLPWR)은 상기 접지전압(VSS)을 유지하고, 상기 이븐 쉴딩신호(SHLDe), 상기 오드 쉴딩신호(SHLD0), 상기 이븐 비트라인 선택신호(BLSLTe)의 전압레벨들 및 상기 센싱 노드 블락킹 신호(SOBLK)는 상기 전원전압(VDD)으로 변화된다. 따라서, 상기 비트라인들(BLe, BLo 및 BL)은 상기 접지전압(VSS) 즉, 논리 "L" 상태의 데이터로 디스차아지된다.

다음, 상기 READ2 구간에서, 상기 이븐 비트라인(BLe0)과 상기 비트라인(BL0)은 선택되는 메모리셀(MCscl)의 데이터값을 감지하기 위해 소정의 프리차아지 전압(예컨대, 0.8V)으로 프리차아지된다.

그리고, 상기 READ2 구간에서, 제1 전압이 상기 선택되는 워드라인(WLn-1)에 인가되며, 제2 전압이 상기 나머지 비선택되는 워드라인(WL<n-2:0>)에 인가된다. 본 실시예에서는, 상기 제1 전압은 상기 접지전압(VSS)이며, 상기 제2 전압은 상기 독출전압(VREAD)이다. 따라서, 상기 선택되는 메모리셀(MCscl)의 상기 온/오프의 상태는 자신에 저장된 데이터에 의해 따른다. 즉, 선택되는 메모리셀(MCscl)에 저장된 데이터가 논리 "1"인 경우, 상기 선택되는 메모리셀(MCscl)은 "온" 상태이며, 저장된 데이터가 논리 "0"인 경우, 상기 선택되는 메모리셀(MCscl)은 "오프"상태이다.

상기 READ2 구간에서, 상기 이븐 쉴딩신호(SHLDe)는 상기 이븐 비트라인(BLe0)을 상기 비트라인 전압라인(BLPWR)과 연결하는 상기 앤모스 트랜지스터(511)를 "턴오프"시키기 위하여 논리"L"로 된다(tR4). 그러므로, 상기 이븐 비트라인(BLe0) 및 상기 비트라인(BL0)의 디스차아지 상태는 해제된다. 이때, 상기 오드 쉴딩신호(SHLD0)는 상기 전원전압(VDD)로 유지되어, 상기 앤모스 트랜지스터(512)가 "온"상태를 유지한다. 그러므로, 상기 오드 비트라인(BLo0)은 상기 접지전압(VSS)으로 유지되어, 상기 이븐 비트라인들 사이의 차단라인(shielding)으로서 기능을 수행한다.

그리고, 상기 센싱셋팅신호(/PLOAD)의 전압은 상기 전원전압(VDD)에서 소정의 시간 동안에 제1 예비전압(VPRE1)으로 하강(drop)되며, 이후, 접지전압(VSS)으로 하강(drop)한다(tR5). 그러므로, 상기 센싱 트랜지스터(860a)는 턴온되어, 상기 센싱 노드(NSEN0)는 셋팅전압인 상기 전원전압(VDD)로 된다.

본 실시예에 의하면, 상기 센싱셋팅신호(/PLOAD)의 상기 예비전압(VPRE1)은 대략 1.0V로서, 접지전압(VSS)과 전원전압(VDD) 사이의 전압이다. 상기 센싱셋팅신호(/PLOAD)를 미리 결정되는 시간동안 언드슈팅(undershooting)으로부터 초래되는 파워 노이즈(power noise)를 감소시키기 위해 상기 제1 예비전압(VPRE1)으로 유지된다.

이때, 비트라인 차단신호(BLSHF)는 상기 전원전압(VDD)와 상기 접지전압(VSS) 사이의 전압인 제2 예비전압(VPRE2)으로 변화된다. 그러므로, 상기 센싱 노드(NSEN0)과 상기 비트라인(BL0)는 서로 전기적으로 연결된다. 상술한 바와 같이, 상기 비트라인 차단 신호(BLSHF)는 상기 비트라인 차단 트랜지스터(870a)를 상기 제2 예비전압(VPRE2)에서 케이팅한다. 따라서 상기 비트라인들(BLO, BLe0)은 상기 센싱 셋팅 트랜지스터(860a)로부터 제공되는 전류에 기인하여 주어지 레벨로 프리차아지된다. 여기서, 상기 주어진 레벨은, 상기 비트라인 차단트랜지스터(870a)의 상기 문턱전압 만큼, 상기 제2 예비전압(VPRE2)보다 낮다.

또한, 상기 비트라인 차단 트랜지스터(870a)를 통하여 충분한 전류가 흐르도록, 상기 이븐 비트라인 선택신호(BLSLTe) 및 상기 센싱 노드 블락킹신호(SOBLK)의 상기 전압레벨은 상기 독출전압(VREAD)으로 변화된다.

이어서, 상기 READ3 구간에서, 상기 선택되는 메모리 셀(MCsel)에 저장된 데이터를 감지하여, 상기 데이터를 디벨로프하는 과정이 수행된다.

좀더 정확하게는, 상기 READ3 구간에서, 상기 비트라인 차단신호(BLSHF)는, 상기 비트라인 차단 트랜지스터(870a)를 '턴오프'시키기 위하여, 상기 접지전압(VSS)이다(tR6). 따라서, 상기 비트라인(BL0)은 상기 센싱 노드(NSENO)로부터 전기적으로 분리되며, 상기 비트라인(BL0)은 데이터를 디벨로프하도록 진행한다.

상기 선택되는 상기 메모리 셀(MCsel)이 '온셀'(ON cell)인 경우에는, 상기 비트라인(BL0) 상의 데이터는 상기 공통 소오스 라인(CSL)으로 디스차아지된다. 그러므로, 상기 비트라인(BL0)의 전압레벨은 접지전압(VSS)에 근접된다. 반면에, 상기 선택되는 메모리 셀(MCsel)이 '오프셀'(OFF cell)인 경우에는, 상기 비트라인(BL0)의 전압레벨은 실질적으로 변화하지 않는다(누설전류에 의해 유발되는 영향은 제외).

상기 센싱 셋팅 트랜지스터(860a)는 상기 READ3 구간의 대부분에서 '온'(ON) 상태를 유지하지만, 상기 READ3 구간의 종료직전에 턴오프(turn off)된다(tR8). 이 경우, 상기 센싱 노드(NSENO)는 상기 전원전압(VDD)을 유지하다가 플로팅 상태로 된다.

이어서, 상기 READ4 구간에서, 상기 비트라인(BL0) 상에 디벨로프되는 데이터, 즉, 상기 비트라인의 상기 전압레벨에 대응하는 데이터를 상기 페이지 버퍼(NWBUFO)의 래치 노드(NLAT)에 저장되는 과정이 수행된다. 먼저, 상기 'READ3' 구간에서 생성된 상기 센싱 노드(NSENO)의 플로팅 상태가 그대로 유지된다.

여기서, 상기 READ3 구간에서 생성되는 상기 센싱 노드(NSENO)의 플로팅 상태는, 상기 비트라인 차단신호(BLSHF)가 제3 예비전압(VPRE3)으로 변화되어 상기 비트라인 차단 트랜지스터(870a)를 턴온시키는 동안에, 유지된다.

본 실시예에 의하면, 상기 제3 예비전압(VPRE3)은 상기 접지전압(VSS)과 상기 전원전압(VDD) 사이의 전압이며, 센싱 마진에 대응하는 소정의 전압차로 상기 제2 예비전압(VPRE2)보다 낮다. 따라서, 상기 센싱 노드(NSENO)의 전압레벨은 상기 비트라인(BL0) 상에 디벨로프되는 전압레벨에 따라서 결정된다.

이때, 상기 제1 내부 입력 라인(IDIO) 상의 상기 데이터 값은 논리 "H" 상태로 변화되어(tR9), 상기 제1 래치전송 트랜지스터(820a)는 "턴온"(ON)된다.

상기 독출래치신호(LCH)에 응답하여(tR10), 상기 래치 노드(NLAT)는 상기 비트라인(BL0) 상의 상기 전압레벨에 의하여 결정되는 상기 센싱 노드(NSENO) 상의 데이터, 즉, 상기 선택되는 메모리 셀(MCsel)에 저장된 데이터에 대응하는 데이터를 저장한다.

즉, 상기 선택된 메모리 셀(MCsel)이 '온셀'(ON cell)인 경우에는, 상기 비트라인(BL0)과 상기 센싱 노드(NSENO)의 전압레벨은 거의 접지전압(VSS)이다. 그러므로, 상기 독출래치신호(LCH)가 논리 "H" 상태로 인에이블되더라도, 상기 래치 노드(NLAT) 상의 데이터는 논리 "L" 상태를 유지한다.

반면에, 상기 선택된 메모리 셀(MCsel)이 '오프셀'(OFF cell)인 경우에는, 상기 비트라인(BL0)과 상기 센싱 노드(NSENO)의 전압레벨이 누설전류에 의해 상기 프리차아지 전압으로부터 약간 하강(drop)될지 모르지만, 상기 비트라인 차단 트랜지스터(870a)는 상기 제2 및 제3 예비전압(VPRE2 및 VPRE3) 사이의 전압차에 의해 '턴온'(turn on)될 수 없으므로, 상기 전압레벨은 논리 "H" 상태로 유지된다. 그러므로, 상기 독출래치신호(LCH)가 논리 "H" 상태로 인에이블되면, 상기 래치 노드(NLAT) 상의 데이터는 논리 "H" 상태로 플립(flip)된다.

이어서, '상기 READ5 구간'에서, 상기 비트라인(BL0)과 상기 센싱 노드(NSENO)가 리셋되는 과정이 수행된다.

상기 'READ5 구간'에서, 상기 이븐 월딩신호(SHLDe)는 전원전압(VDD)으로 변화되고, 이븐 비트라인 선택신호(BSLSTe) 및 상기 센싱블럭킹신호(SOBLK)은 모두 상기 독출전압(VREAD)에서 상기 전원전압(VDD)으로 변화된다. 그러므로, 상기 비트라인(BL0)과 상기 센싱 노드(NSENO)는 상기 접지전압(VSS)으로 리셋된다(tR11).

그리고, 상기 비선택된 워드라인(WL<n-2:0>), 상기 스트링 선택라인(SSL), 상기 그라운드 선택라인(GSL)은 모두 상기 독출전압(VREAD)으로부터 상기 접지전압(VSS)으로 변화된다.

이어서, 상기 READ6 구간에서, 상기 래치 노드(NLAT)에 대응하는 데이터(상기 'READ4 구간'에서 저장된 데이터)가 상기 내부출력 라인(IDOUT0)을 통하여 상기 글로벌 출력 라인(GDOUT)으로 출력되는 과정이 수행된다.

상기 'READ6 구간'에서는, 상기 버퍼선택 어드레스(Yp0) 및 상기 블락 디코딩 신호(/BLDEC)는 각각의 펠스형태로 활성화된다. 그리고, 상기 래치 노드(NLAT)에 대응하는 데이터가 상기 내부 출력 라인(IDOUT0)을 통하여 상기 글로벌 출력 라인(GDOUT)으로 전송된다.

본 실시예에서, 상기 글로벌 출력 라인(GDOUT)은, 상기 블락 디코딩 신호(/BLDEC)가 활성화되기 이전에, 상기 출력 라인 프리차아지 회로(도시되지 않음)에 의해 상기 전원전압(VDD)로 프리차아지된다.

상기 선택되는 메모리셀(MCsel)이 '온셀'(ON cell)인 경우에는, 상기 래치 노드(NLAT) 상의 데이터는 논리 "L"이고, 그러므로, 상기 글로벌 출력 라인(GDOUT)으로 전송된 데이터는 논리 "H" 상태로 된다. 반면에, 상기 선택되는 메모리셀(MCsel)이 '오프셀'(OFF cell)인 경우에는, 상기 래치 노드(NLAT)의 데이터는 논리 "H"이고, 그러므로, 상기 글로벌 출력 라인(GDOUT)으로 전송된 데이터는 논리 "L" 상태로 디스차아지된다.

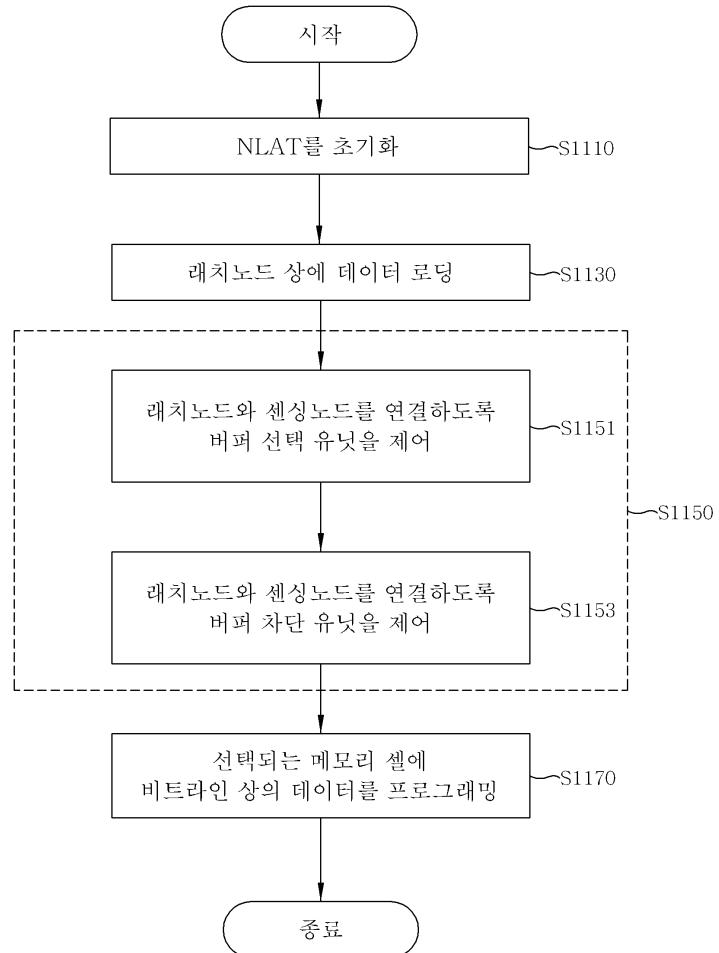

본 발명의 실시예에 따른 프로그램 동작 상의 모드(program mode)가 도 18의 플로우차트를 참조하여 기술된다. 상기 프로그램 모드는 상기 메모리셀 어레이의 상기 선택되는 메모리셀(MCsel)에 입력 데이터를 로딩/loading)하는 과정이 수행된다.

S1110단계에서, 상기 래치 노드(NLAT)가 초기화된다. 상기 래치 노드(NLAT)는, 상기 제1 내부 입력 라인(IDIO)와 상기 제2 내부 입력 라인(nIDIO) 중의 어느 하나에 의하여, 제1 논리상태(즉, 논리 "H"상태) 또는 제2 논리상태(즉, 논리 "L"상태)의 데이터로 초기화된다. 본 실시예에서, 상기 래치 노드(NLAT)는, 상기 제1 내부 입력 라인(IDIO)에 의하여, 제1 논리상태(즉, 논리 "H"상태)인 프로그램 금지(inhibit)상태로 초기화된다.

S1130단계에서, 상기 제1 내부 입력 라인(IDIO)와 상기 제2 내부 입력 라인(nIDIO) 중의 어느 하나에 의하여, 상기 래치전송 유닛(820)이 상기 래치 드라이빙 유닛(825)으로부터 제공되는 접지전압(VSS)인 상기 래치드라이빙전압을 상기 래치 유닛(810)에 제공한다. 그리고, 상기 래치 유닛(810)은 상기 래치 드라이빙 전압을 이용하여, 제1 논리상태(즉, 논리 "H"상태) 또는 제2 논리상태(즉, 논리 "L"상태)의 데이터를 상기 래치 노드(NLAT)에 로딩한다.

상기 S1130단계에서의 데이터 로딩 과정을 자세히 기술하면, 입력 데이터가 논리 "H"인 경우에는, 상기 버퍼선택 어드레스(Yp0)가 "H"펄스로 되며, 상기 제1 내부 입력 라인(IDIO)도 "H" 펄스로 된다. 이때, 상기 제2 내부 입력 라인(nIDIO)은 논리 "L" 상태를 유지한다. 그러면, 상기 래치 노드(NLAT)는, 논리 "H"상태인, 프로그램 금지(inhibit)상태를 유지한다.

반면에, 상기 입력데이터가 논리 "L"인 경우에는, 상기 버퍼선택 어드레스(Yp0)는 논리 "H"펄스로 되며, 상기 제2 내부 입력 라인(nIDIO)도 "H"펄스로 된다. 이때, 상기 제1 내부 입력 라인(IDIO)은 논리 "L"상태를 유지한다. 그러면, 상기 래치 노드(NLAT)도 논리 "H"상태에서 논리 "L" 상태로 변화된다.

결과적으로, 본 실시예에서, 데이터 로딩이 수행될 때, 상기 제1 내부 입력 라인(IDIO)과 상기 제2 내부 입력 라인(nIDIO)은 상반되는 논리 상태들을 가진다. 만약, 상기 버퍼선택 어드레스(Yp0)가 논리 "H"상태일 때, 논리 "H"상태의 데이터가 상기 제1 내부 입력 라인(IDIO)으로 전송되면, 상기 논리 "H"상태의 데이터는 상기 래치 유닛(810)의 상기 래치 노드(NLAT)에 저장된다. 반면에, 논리 "H"상태의 데이터가 상기 제2 내부 입력 라인(nIDIO)으로 전송되면, 논리 "L"상태의 상기 데이터는 상기 래치 유닛(810)의 상기 래치 노드(NLAT)에 저장된다.

S1150단계에서, 상기 래치 노드(NLAT)에 로딩되는 데이터가 상기 비트라인(BLO)로 전송된다. 이러한 과정은 하기의 S1151단계와 S1153단계에서 좀더 상세히 설명된다.

상기 S1151단계에서는, 상기 버퍼선택 유닛(850)은 상기 래치 노드(NLAT)를 상기 센싱 노드(NSEN0) 궁극적으로, 상기 비트라인(BLO)에 연결하도록 제어된다. 즉, 상기 버퍼선택신호(PBSLT)는, 상기 버퍼선택 트랜지스터(850a)를 턴온(turn on)하기 위해, 논리 "H"레벨로 된다. 그러면, 상기 래치 노드(NLAT) 상의 데이터는 상기 센싱 노드(NSEN0)로 전송된다.

상기 S1153단계에서는, 상기 비트라인 차단 유닛(870)은 상기 센싱 노드(NSEN)를 상기 비트라인(BLO)에 연결하도록 제어된다. 좀더 상세히 기술하면, 본 실시예에서, 상기 비트라인 차단신호(BLSHF)는 상기 비트라인 차단 트랜지스터(870a)를 턴온하기 위해 논리 "H"레벨로 된다. 그러면, 상기 센싱 노드(NSEN0)의 데이터가 상기 비트라인(BLO)으로 전송된다.

S1170단계에서, 상기 비트라인(BL0)에 전송되는 데이터에 대응하여, 상기 선택되는 메모리셀(MCsel)은 프로그램된다.

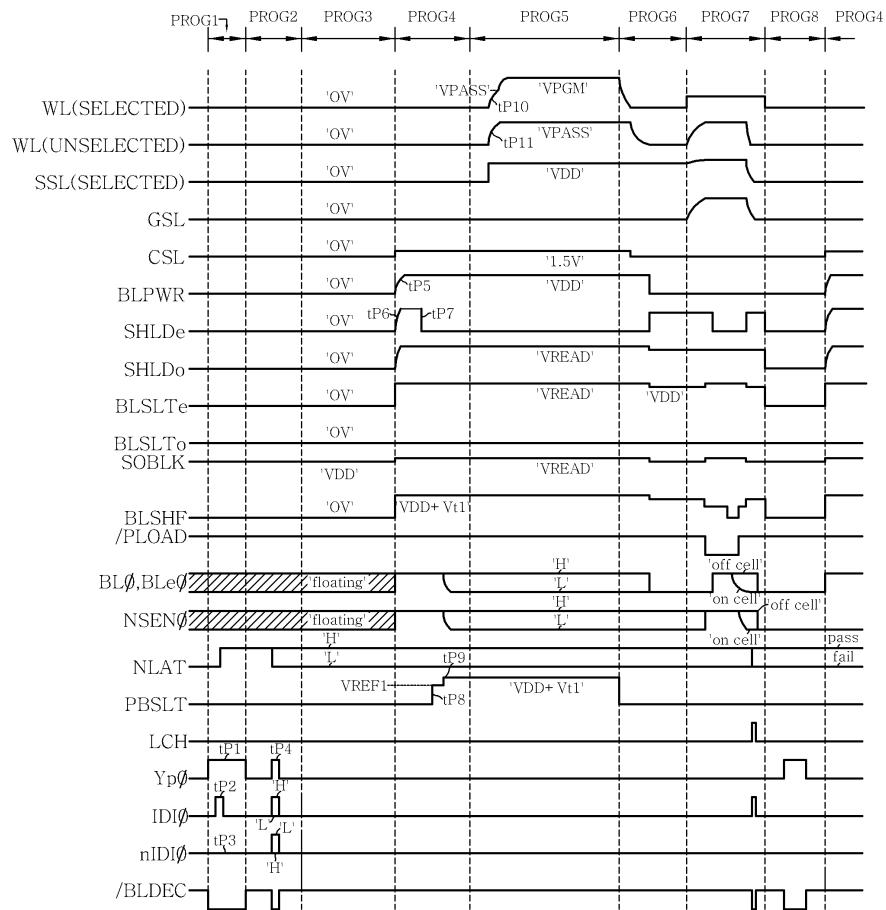

상기 프로그램 모드의 예는 도 19의 타이밍 다이어그램을 참조하여 하기(下記)에서 좀더 상세히 기술된다.

도 19는 도 11 내지 도 15에 도시된 상기 불휘발성 메모리 장치의 다양안 신호전압들과 노드전압을 나타내는 프로그램 모드 타이밍 다이어그램이다. 다시, 다음의 설명에서, 이전에 살펴본 도면들이 참조된다.

설명의 목적으로, 상기 도 19의 타이밍 다이어그램은 8개의 구간, 즉, 페이지 버퍼 셋업 구간(이하, "PROG1 구간"이라 함), 데이터 로딩 구간(이하, "PROG2 구간"이라 함), 고전압 인에이블 구간(이하, "PROG3 구간"이라 함), 비트라인 셋업 구간(이하, "PROG4 구간"이라 함), 프로그램 수행 구간(이하, "PROG5 구간"이라 함), 회복 구간(이하, "PROG6 구간"이라 함), 확인독출 구간(이하, "PROG7 구간"이라 함) 및 Y-스캔 구간(이하, "PROG8 구간"이라 함)으로 나누어진다.

상기 'PROG1 구간'에서는, 외부에서 인가되는 데이터를 로딩하기 이전에, 상기 래치 노드(NLAT)는 프로그램 금지(inhibit)상태로 제어된다. 본 실시예에서, 상기 '프로그램 금지(inhibit)상태'는 외부에서 인가되는 특정 데이터에 대해서는, 셀 프로그래밍(cell programming)의 수행이 요구되지 않는 상태를 말한다. 본 실시예에서는, 외부에서 논리 "H"상태의 데이터가 외부에서 입력되는 경우에는, 셀 프로그래밍(cell programming)이 요구되지 않는다.

본 실시예에서, 상기 'PROG1 구간'에서는, 상기 버퍼선택 어드레스(Yp0)는, 상기 래치드라이빙 트랜지스터(825a)를 턴온하기 위해, 논리 "H"상태이다(tP1). 그리고, 상기 메인선택 어드레스(Yq0)와 상기 서브선택 어드레스(Yr0)가 모두 논리 "H"상태이므로, 상기 블락 디코딩 신호(/BLDEC)는 논리 "L"상태로 액티브(active)된다. 이때, 상기 제1 글로벌 입력 라인(GDI)은 논리 "L"상태를 가지는 액티브 펄스이고, 그리고 상기 제2 글로벌 입력 라인(nGDI)은 논리 "H"상태이다. 그러므로, 상기 제1 내부 입력 라인(IDIO)은 논리 "H"상태를 가지는 액티브 펄스이고(tP2), 상기 제2 내부 입력 라인(nIDIO)은 논리 "L"상태이다. 그러므로, 상기 제1 래치전송 트랜지스터(820a)는 일시적으로 턴온(turn on)되며, 상기 제2 래치전송 트랜지스터(820b)는 '오프(off)"상태로 된다. 이와 같은 방법으로, 상기 래치 노드(NLAT)는 '프로그램 금지상태', 예컨대, 논리 "H"상태로 설정된다.

이어서, 상기 'PROG2 구간'은 외부에서 인가되는 데이터가 상기 페이지 버퍼(NWBUFO)의 상기 래치 노드(NLAT) 상에 로딩되는 과정이 수행된다.

상기 'PROG2 구간'에서는, 상기 제1 내부 입력 라인(IDIO) 또는 제2 내부 입력 라인(nIDIO)에 응답하여, 외부에서 입력되는 데이터에 대응하는 데이터가 상기 래치 노드(NLAT)에 저장된다. 그리고, 상기 래치 노드(NLAT)에 저장되는 데이터는 상기 버퍼입력패스들(RBIN1, RBIN2)을 통하여 제공된다. 상기 제1 내부 입력 라인(IDIO)에 응답하여 상기 래치 노드(NLAT) 상에 저장되는 상기 데이터의 상기 논리상태는, 상기 제2 내부 입력 라인(nIDIO)에 응답하여 상기 래치 노드(NLAT) 상에 저장되는 데이터의 상기 논리상태와 상반된다. 즉, 본 예에서, 상기 제1 내부 입력 라인(IDIO)에 응답하여 상기 래치 노드(NLAT)에 저장되는 데이터는 논리 "H"이며, 상기 제2 내부 입력 라인(nIDIO)에 응답하여 상기 래치 노드(NLAT)에 저장되는 데이터는 논리 "L"이다.

상기 'PROG2 구간'의 시점 'tP4'에서, 상기 버퍼선택 어드레스(Yp0)는 논리 "H"이다. 상기 메인선택 어드레스(Yq0) 및 상기 서브선택 어드레스(Yr0)가 모두 논리 "H"이므로, 상기 블락 디코딩 신호(/BLDEC)는 논리 "L"이다. 이때, 상기 제1 글로벌 입력 라인(GDI) 또는 제2 글로벌 입력 라인(nGDI)은 논리 "H"상태로 변화된다.

즉, 상기 입력 데이터가 논리 "L"이면, 상기 제1 글로벌 입력 라인(GDI)은 논리 "H"상태로 변화된다. 좀더 정확하게는, 상기 제1 내부 입력 라인(IDIO)은 논리 "L"상태로 변화되고, 상기 제2 내부 입력 라인(nIDIO)은 논리 "H"상태로 변화된다. 그러므로, 논리 "L"상태의 데이터가 상기 래치 노드(NLAT) 상에 저장된다.

반면에, 상기 입력되는 데이터가 논리 "H"이면, 상기 제2 글로벌 입력 라인(GDI)은 논리 "L"상태로 변화된다. 좀더 정확하게는, 상기 제2 내부 입력 라인(nIDIO)은 논리 "L"상태로 변화되고, 상기 제1 내부 입력 라인(IDIO)은 논리 "H"상태로 변화된다. 그러므로, 논리 "H"상태의 데이터가 상기 래치 노드(NLAT) 상에 저장된다.

이어서, 상기 'PROG3 구간'이 수행된다. 여기서, 상기 불휘발성 반도체 메모리 장치에 내장되는 고전압 펌프회로들의 그룹이 인에이블된다. 일반적으로, 이러한 회로들은 상기 전원전압(VDD)보다 매우 높은 전압을 발생하기 위한 것이다. 본 실시예의 예에서, 상기 고전압 펌프회로그룹은, 프로그램전압(VPGM, 예를 들면, 20V), 패스전압(VPASS, 예를 들면,

7~9V), 독출전압(VREAD, 예를 들면, 5V) 등을 발생하는 회로들을 포함한다. 그리고, 상기 고전압 펌핑회로 그룹은, 로우 디코더(미도시)에 의하여 이용되어지는 부스팅 전압을 발생하는 회로를 포함할수도 있다. 참고로, 본 실시예의 예에서, 상기 전원전압(VDD)는 대략 2.2V이다.

상기 'PROG4 구간'에서는, 상기 선택되는 메모리셀(MCsSel)과 연결되는 상기 이븐 비트라인(BLe0) 즉, 선택되는 비트라인이 상기 래치 노드(NLAT)에 저장되는 데이터에 대응하는 전압 레벨로 제어된다. 그리고, 상기 선택되는 메모리셀(MCsSel)과 연결되지 않는 오드 비트라인(BLo0) 즉, 비선택되는 비트라인은 프로그램 금지(inhibit)상태로 제어된다.

또한, 상기 'PROG4 구간'에서는, 상기 비트라인 전압라인(BLPWR)의 상기 전압레벨은 상기 전원전압(VDD)으로 상승한다(tP5). 그리고, 상기 이븐 쉴딩신호(SHLDe)와 상기 오드 쉴딩신호(SHLD0)의 상기 전압레벨들은 상기 독출전압(VREAD)로 상승한다(tP6). 그러므로, 전압강하(voltage drop)없이, 상기 이븐 비트라인(BLe0)과 오드 비트라인(BLo0)의 상기 전압레벨들은, 상기 비트라인 전압라인(BLPWR)의 상기 전압인, 전원전압(VDD)으로 변화된다.

그리고, 상기 이븐 비트라인 선택신호(BLSLTe) 및 상기 센싱 노드 블락킹 신호(SOBLK)도 상기 독출전압(VREAD)로 상승된다. 상기 비트라인 차단신호(BLSHF)의 상기 전압레벨은 "VDD+ Vt1"으로로 상승한다. 본 실시예에서, 상기 'Vt1'은 대략 1.5V의 소정의 전압이다.

그리고, 상기 'PROG4 구간'의 시점(tP7)에서, 미리 결정되는 일정시간이 경과후, 상기 이븐 쉴딩신호(SHLDe)의 전압레벨은 다시 상기 접지전압(VSS)으로 감소한다. 그리고, 상기 버퍼선택신호(PBSLT)는 제1 기준전위(VREF1)로 변화된 후에(tP8), 다시 제5 전압으로 변화된다(tP9). 본 실시예의 예에서, 상기 제5 전압은 "VDD+ Vt1"과 동일하며, 상기 제1 기준전위(VREF1)는 대략 1.3V로서, 상기 접지전압(VSS)과 상기 제5 전압 사이의 전압이다.

상기 래치 노드(NLAT) 상에 저장되는 상기 데이터는 상기 선택되는 메모리셀(MCsSel)과 연결되는 상기 이븐 비트라인(BLe0)으로 전송된다. 즉, 상기 래치 노드(NLAT) 상에 저장되는 데이터가 논리 "L"인 경우에, 상기 이븐 비트라인(BLe0)은 "0V"로 된다. 그리고, 상기 래치 노드(NLAT) 상에 저장되는 상기 데이터가 논리 "H"인 경우에, 상기 이븐 비트라인(BLe0)은 상기 전원전압(VDD)을 유지한다.

이어서, 상기 'PROG5 구간'은 상기 이븐 비트라인(BLe0)으로 전송되는 데이터를 상기 선택되는 메모리셀(MCsSel)에 저장하는 과정이 수행된다.

상기 패스전압(VPASS)이 소정의 시간 동안 상기 선택된 워드라인(WLn-1)에 인가된 이후, 제3 전압인 프로그램 전압(VPGM)이 상기 선택된 워드라인(WLn-1)에 인가된다(tP10). 상기 프로그램 전압(VPGM)은, 상기 이븐 비트라인(BLe0) 즉, 상기 비트라인(BLo)의 상기 전압레벨에 대응하는 데이터를, 상기 선택되는 메모리셀(MCsSel)에 프로그램되도록 한다. 그리고, 상기 패스전압(VPASS)이 비선택되는 워드라인들(WL<n-2:0>)에 인가된다(tP11). 그러므로, 상기 비선택되는 메모리셀(MC)들은 프로그래밍 없이 '온'(ON) 상태를 유지한다.

상기 "PROG5 구간"에서, 상기 이븐 비트라인(BLe0)에 전송되는 데이터가 "H"인 경우에는, 프로그램 금지상태가 유지된다. 반면에, 상기 이븐 비트라인(BLe0)에 전송되는 데이터가 논리 "L"인 경우에는, 상기 선택되는 메모리셀(MCsSel)은 FN 터널링에 의하여 프로그램된다. 그러므로, 본 예에서는, 논리 "L" 상태의 데이터가 저장되는 메모리셀(MCsSel)은 '프로그램된 셀'로서 설계될수 있다.

또한, 상기 'PROG5 구간'에서, 상기 스트링 선택라인(SSL)은 상기 전원전압(VDD)으로, 상기 그라운드 선택라인(GSL)은 상기 접지전압(VSS)으로, 그리고 상기 공통 소오스 라인(CSL)은 대략 1.5V의 전압을 가진다.

이어서, 상기 'PROG6 구간'에서, 워드라인들(WL<n-1:0>), 비트라인들(BL0, BLe0, BLo0) 및 상기 센싱 노드(NSEN0)가 상기 접지전압(VSS)으로 디스차아지되는 과정이 수행된다.

즉, 상기 'PROG6 구간'에서, 상기 비트라인 전압라인(BLPWR)은 상기 접지전압(VSS)을 유지한다. 또한, 상기 이븐 쉴딩신호(SHLDe), 상기 오드 쉴딩신호(SHLD0), 상기 이븐 비트라인 선택신호(BLSLTe), 상기 센싱 노드 블락킹신호(SOBLK) 및 상기 비트라인 차단신호(BLSHF)는 상기 전원전압(VDD)으로 변화된다. 그러므로, 상기 워드라인들(WL<n-1:0>), 비트라인들(BL0, BLe0 및 BLo0)과 상기 센싱 노드(NSEN0)는 상기 접지전압(VSS)으로 디스차아지된다.

그리고, 버퍼선택신호(PBSLT)는 상기 접지전압(VSS)으로 변화되도록 상기 비트라인(BL0)와 상기 래치 노드(NLAT)는 전기적으로 분리된다.

상기 'PROG7 구간'은 상기 메모리 셀(MCsel)에 프로그램되는 상기 데이터를 감지하기 위한 과정이 수행된다.

상기 'PROG7 구간'에서 수행되는 동작은 앞에서 기술된 독출모드에서 수행되는 동작과 거의 동일하다. 그러나, 상기 'PROG7 구간'은, 소정의 확인 독출전압이 상기 선택되는 워드라인(WLn-1)에 인가되는 점과, 상기 페이지 버퍼(NWBUFO)의 리셋되는 동작이 생략될 수 있다는 점에서, 상기 독출모드와 다르다. 상기 'PROG7 구간'에서 수행되는 나머지 동작들은 상기 독출 모드의 동작과 유사하므로, 그에 대한 구체적인 기술은, 중복되는 내용을 피하기 위하여 생략된다.

이어서, 상기 'PROG8 구간'은 상기 'PROG7 구간'에서 상기 래치 노드(NLAT) 상에 저장되는 상기 데이터를 이용하여, 상기 선택되는 메모리셀(MCsel)이 올바르게 프로그램되었는지를 확인하는 과정이 수행된다.

즉, 상기 'PROG8 구간'에서는, 상기 래치 노드(NLAT) 상에 저장되는 데이터가 논리 "H"인 경우에서는, 논리 "L" 상태의 데이터가 상기 글로벌 출력 라인(GDOUT)으로 출력되어, 패스(pass) 신호가 발생된다. 그리고, 상기 래치 노드(NLAT) 상의 데이터가 논리 "L"인 경우에서는, 논리 "H" 상태의 데이터가 상기 글로벌 출력 라인(GDOUT)으로 출력되어, 불량(fail) 신호가 발생된다.

상기 불량신호가 상기 'PROG8 구간'에서 발생될 때, 상기 'PROG4 구간'부터 상기 'PROG8 구간'까지의 프로그램 루프(loop)가 반복된다. 결과적으로, 상기 패스신호가 발생될 때, 상기 프로그램 모드가 완료된다.

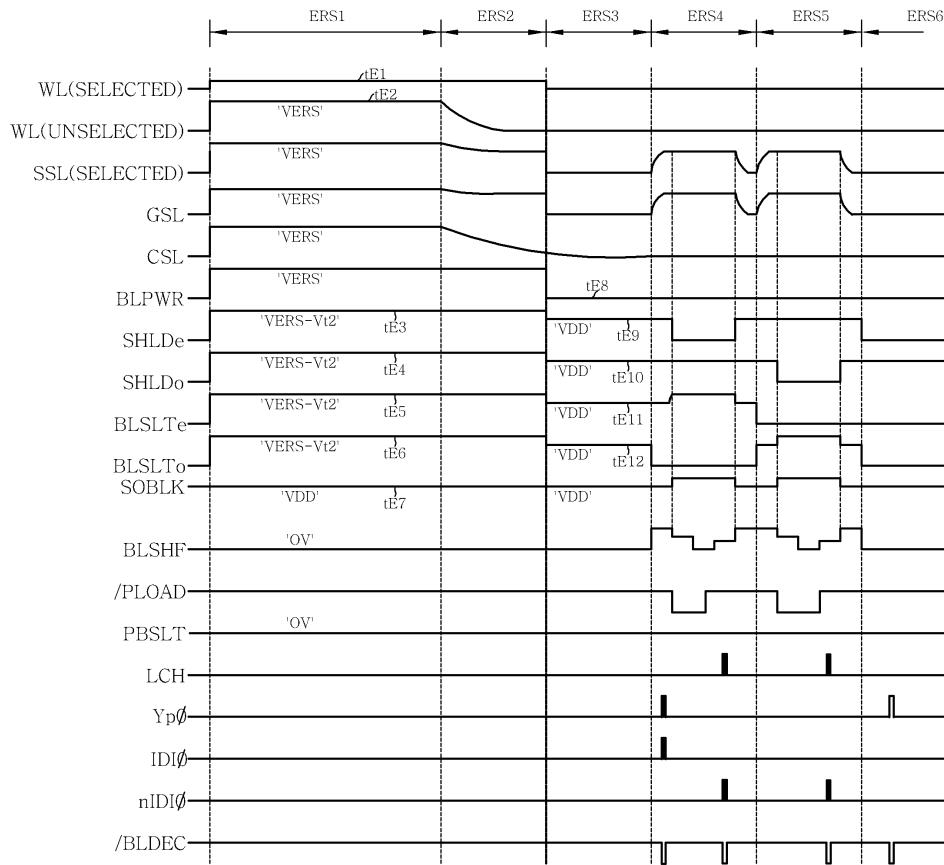

소거 동작 상의 모드(소거 모드)의 예가 도 20의 타이밍 다이어그램을 참조하여 하기에서 기술된다.

도 20은 도 11 내지 도 15의 예에서 도시된 상기 불휘발성 반도체 메모리 장치의 다양한 신호전압들과 노드전압들을 나타내는 소거 모드 타이밍 다이어그램이다. 앞에서와 같이, 다음의 설명에서, 이전에 살펴본 도면들이 참조된다.

설명의 목적으로, 도 20의 상기 소거 모드 타이밍 다이어그램은 6개의 구간들, 즉, 소거수행 구간(이하, "ERS1 구간"이라 함), 제1 회복 구간(이하, "ERS2 구간"이라 함), 제2 회복 구간(이하, "ERS3 구간"이라 함), 제1 확인독출 구간(이하, "ERS4 구간"이라 함), 제2 확인독출 구간(이하, "ERS5 구간"이라 함) 및 Y-스캔 구간(이하, "ERS6 구간"이라 함)으로 나누어진다.

상기 'ERS1 구간'에서는, 소거전압(VERS)이 메모리 셀(MC)들의 벌크(bulk)에 인가되고, 제6 전압은 선택되는 대응하는 메모리 셀들로부터의 데이터를 소거하기 위하여 워드라인들에 인가된다. 본 실시예에서, 상기 소거전압(VERS)은 대략 20V이며, 상기 제6 전압은 약 0.3V이다(tE1). 그리고, 비선택되는 워드라인들은 플로팅상태로 제어된다. 이러한 비선택되는 워드라인들의 전압은 상기 벌크 상의 커플링(coupling)에 의해 거의 상기 소거전압(VERS)이 된다(tE2). 그러므로, 소거 동작은 상기 비선택되는 워드라인들에 연결되는 상기 메모리 셀들에서는 수행되지 않는다.

또한, 'ERS1 구간'에서는, 상기 이븐 쉴딩신호(SHLDe), 상기 오드 쉴딩신호(SHLD0), 상기 이븐 비트라인 선택신호(BLSLTe) 및 상기 오드 비트라인 선택신호(BLSLTo)는 "VERS-Vt2"로 되며(tE3 내지 tE6), 상기 센싱 노드 블락신호(SOBLK)는 전원전압(VDD)을 유지한다(tE7). 이때, 상기 'Vt2'는 고전압 엔모스(NMOS) 트랜지스터들의 문턱전압을 의미한다. 본 실시예에서는, 'Vt2'가 대략 1.3V이다.

이어서, 상기 'ERS2 구간'과 'ERS3 구간'은 상기 선택되는 메모리셀에 저장되는 상기 데이터를 감지하기 위하여, 상기 메모리 셀들(MC)의 벌크(bulk)와 상기 비트라인(BLO)의 전압들이 제어된다.

즉, 상기 'ERS2 구간'에서는, 상기 공통 소오스 라인(CSL)이 디스차아지된다. 좀 더 정확하게는, 상기 'ERS2 구간'은, 상기 메모리 셀(MC)의 벌크(bulk)가 플로팅되고, 공통 소오스 라인(CSL)에 차아지되는 "VERS-Vt"의 전압이 상기 접지전압(VSS)로 디스차아지되는 구간이다.

그리고, 상기 'ERS3 구간'에서는, 벌크(bulk)와 비트라인들(BL0, BLe0, BLo0)이 디스차아지된다. 즉, 상기 비트라인 전압라인(BLPWR)은 상기 접지전압(VSS)으로 변화되고(tE8), 상기 이븐 쉴딩신호(SHLDe), 상기 오드 쉴딩신호(SHLD0), 상기 이븐 비트라인 선택신호(BLSLTe) 및 상기 오드 비트라인 선택신호(BLSLTo)는 전원전압(VDD)으로 변화된다(tE9 내지 tE12). 그러므로, 상기 비트라인들(BL0, BLe0, BLo0)은 접지전압(VSS)로 디스차아지된다.

이어서, 상기 'ERS4 구간'과 'ERS5 구간'에서는, 상기 메모리 셀(MC)의 어느 미(未)소거되는 데이터를 감지할 수 있도록 상기 래치 노드(NLAT)가 셋팅되는 과정이 수행된다. 그리고, 상기 메모리셀의 상기 데이터가 상기 래치 노드(NLAT) 상에 감지되어 저장된다.

즉, 상기 'ERS4 구간'에서는, 상기 래치 노드(NLAT)가 논리 "H"로 셋팅된 후에, 상기 'ERS1 구간'에서 미(未)소거된 상기 이븐 비트라인(BLe0)에 연결되는 메모리셀(MC)의 데이터를 감지한다. 상기 'ERS4 구간'에서의 동작은 상기 노말 독출모드에서 수행되는 동작과 거의 유사하다. 그러나, 상기 독출모드와 관련지어 전술한 바와 같이, 상기 ERS4 구간과 상기 노말 독출모드는 상기 래치 노드(NLAT) 상에 리셋되는 값의 측면에서 다른다. 즉, 상기 노말 독출모드에서의 상기 래치 노드(NLAT)는 논리 "L"상태로 리셋되는 반면에, 상기 'ERS4 구간'에서 수행되는 동작은 상기 래치 노드(NLAT)를 논리 "H"상태로 리셋한다.

그리고, 상기 'ERS4 구간'에서 수행되는 상기 동작은, 상기 독출되는 데이터의 셀성이 'ERS4 구간'에서의 상기 제2 내부 입력 라인(nIDIO)의 활성화에 의하여 수행되는 점에서, 상기 노말 독출 모드와 다르다. 여기서, 상기 'ERS4 구간'에서 수행되는 나머지 동작들은 상기 독출모드에서 수행되는 동작들과 거의 유사하므로, 그에 대한 구체적인 기술은 중복을 피하기 위하여 생략된다.

상기 'ERS5 구간'은 상기 'ERS1 구간'에서 미(未)소거된 상기 오드 비트라인(BLo0)에 연결되는 메모리셀(MC)의 데이터를 감지하는 구간이다. 상기 'ERS5 구간'에서 수행되는 상기 동작은, 상기 래치 노드(NLAT)를 셋팅하는 동작이 수행되지 않는다는 점에서, 상기 'ERS4 구간'의 동작과 차이점이 있다. 상기 'ERS5 구간'에서 수행되는 나머지 동작들은 상기 'ERS4 구간'의 동작들과 거의 동일하므로, 그에 대한 구체적인 기술은 중복을 피하기 위하여 생략된다.

이어서, 상기 'ERS6 구간'은 상기 'ERS4 구간'과 상기 'ERS5 구간'에서 감지되는 상기 데이터를 이용하여 메모리셀(MC)들의 상기 소거동작이 올바르게 수행되었는지를 확인하는 과정이 수행된다.

상기 'ERS6 구간'에서 상기 래치 노드(NLAT)가 논리 "H"인 경우, 논리 "L"상태의 데이터가 상기 글로벌 출력 라인(GDOUT)에 출력되어, 패스신호가 발생된다. 반면에, 상기 래치 노드(NLAT)가 논리 "L"인 경우, 논리 "H"상태의 데이터가 상기 글로벌 출력 라인(GDOUT)에 출력되어, 불량신호가 발생된다.

그러므로, 상기 패스신호가 발생될 때, 상기 소거모드가 완료된다.

상기 'ERS6 구간'에서, 상기 메모리 셀(MC)이, 상기 'ERS4 구간'과 상기 'ERS5 구간'에서, 모두 '온셀'(ON cell)로 감지될 때, 상기 래치 노드(NLAT)는 논리 "H"상태를 유지한다.

만약, 이븐 비트라인(BLe0)이 '오프셀'(비소거된 셀)에 연결된 경우에는, 상기 'ERS4 구간'에서 래치 노드(NLAT)는 상기 접지전압(VSS)으로 디스차아지된다. 그러므로, 상기 'ERS5 구간'에서, 상기 오드 비트라인(BLo0)에 연결되는 메모리셀(MC)이 '온셀'로서 감지되더라도, 래치 노드(NLAT) 상의 데이터는 논리 "L"이다.

마찬가지로, 오드 비트라인(BLo0)이 '오프셀'에 연결되는 경우는, 상기 이븐 비트라인(BLe0)에 연결되는 상기 메모리 셀(MC)이 '온셀'일지라도, 상기 'ERS5 구간'에서, 상기 래치 노드(NLAT)의 데이터는 논리 "L"로 된다.

그러므로, 상기 패스신호는, 상기 이븐 비트라인(BLe0) 및 상기 오드 비트라인(BLo0)이 모두 '온셀'에 연결되어 있는것으로 감지되는 경우에만, 발생된다.

## 발명의 효과

상기와 같은 본 발명의 불휘발성 반도체 메모리 장치와 이에 적용되는 페이지 버퍼에서, 상기 내부출력 라인(IDOUT0)는 상기 래치노드(NLAT) 및 상기 버퍼입력패스(RBIN1, RBIN2)와 전기적으로 분리된다. 그러므로, 상기 내부출력 라인(IDOUT0)에 차아지되는 다른 페이지 버퍼(NWBUF<7:1>)의 데이터에 의하여 선택되는 상기 페이지 버퍼(NWBUFO)의 래치 노드(NLAT)에 저장되는 데이터가 왜곡되는 현상은, 원천적으로 차단될 수 있다.

본 발명의 불휘발성 반도체 메모리 장치에서는, 상기 비트라인 차단 트랜지스터(870a)가 상기 페이지 버퍼(NWBUF0)에 포함되도록 구현된다. 그러므로, 본 발명의 불휘발성 반도체 메모리 장치에서는, 각 페이지 버퍼들의 센싱 노드(NSENO)간의 기생 캐패시터가 발생할 여지는 현저히 감소되므로, 센싱 노드(NSENO)간의 커플링 노이즈가 매우 작게 된다. 또한, 각 페이지 버퍼의 센싱 노드의 길이가 거의 동일하므로, 센싱 노드간의 센싱 마진(margin)의 균일성은 현저히 개선된다.

한편, 본 발명의 불휘발성 반도체 메모리 장치에서는, 512개의 비트라인들 및 페이지 버퍼들을 디코딩하여 데이터의 입출력을 제어하는 데, 소요되는 칼럼 어드레스의 버스 라인의 수는 총 24개이다. 종래기술과 비교할 때, 본 발명의 불휘발성 반도체 메모리 장치에서 소요되는 칼럼 어드레스를 위한 버스 라인의 수는 현저히 감소되는 효과가 발생한다. 따라서, 칼럼 어드레스의 버스 라인을 위한 레이아웃 면적도 현저히 감소된다.

또한, 본 발명의 불휘발성 반도체 메모리 장치에서, 내부출력 라인(IDOUT0)은 상기 페이지 버퍼들(NWBUF<7:0>)에 의하여 공유된다. 그러므로, 종래기술에서의 각 페이지 버퍼들의 내부출력 라인들(IDB<7:0>)간의 라인 대 라인 캐패시터에 의한 커플링 노이즈 문제는 제거될 수 있다.

본 발명의 불휘발성 반도체 메모리 장치에 의하면, 상기 내부출력 라인(DOUT0)이 페이지 버퍼들(NWBUF<7:0>)의 적층 방향으로 신장된다. 그러므로, 본 발명의 불휘발성 반도체 메모리 장치에서는, 상기 내부출력 라인(IDOUT0)에서 각 페이지 버퍼들(NWBUF<7:0>)까지의 거리의 차이는 거의 소멸된다. 따라서, 본 발명의 불휘발성 반도체 메모리 장치에 의하면, 각 페이지 버퍼들(NWBUF<7:0>)간의 데이터 로딩/loading)의 균일성(uniformity)의 현저히 개선되어, 센싱 마진(margin)의 균일성은 현저히 좋아진다.

본 발명의 바람직한 실시예가 설명의 목적을 위해 도시되었으나, 본 기술분야의 통상의 지식을 가진자는 본 발명의 사상과 범위 내에서 다양한 변형, 추가 및 대체가 가능하다는 점을 이해할 것이다. 본 명세서에서는, 단지 일례로서, 낸드(NAND) 타입의 불휘발성 반도체 메모리 장치가 도시되고 기술되었으나, 본 발명의 기술적 사상은 불휘발성 반도체 메모리 장치의 다른 형태 예컨대, 앤드(AND) 타입의 반도체 메모리 장치에 적용될 수 있음은 당업자에게는 자명하다. 따라서, 본 발명의 기술적 보호범위는 수반하는 청구범위의 기술적 사상에 의해 정의되어져야 한다. 한편, "연결되는" 및 이와 유사한 문구는 구성요소들 사이에 직접의 연결을 규정하는 것으로 해석되지 않는다.

## 도면의 간단한 설명

본 발명의 상세한 설명에서 사용되는 도면을 보다 충분히 이해하기 위하여, 각 도면의 간단한 설명이 제공된다.

도 1a 내지 도 1c는 플래시 메모리 셀의 개략적인 단면도, 플래시 메모리 셀의 등가회로도 및 플래시 메모리 셀의 문턱전압 특징을 각각 나타내는 도면이다.

도 2는 플래시 메모리 셀들의 문턱전압 분포를 나타내는 도면이다.

도 3a 및 도 3b는 각각 낸드(NAND) 플래시 메모리 셀 블락의 개략적인 도면과 낸드 플래시 메모리 셀 블락의 소거, 프로그램 및 독출전압을 나타내는 테이블이다.

도 4는 도 3에 도시된 낸드(NAND) 플래시 메모리 셀 블락의 프로그래밍 동작을 설명하기 위한 도면이다.

도 5는 도 3에 도시된 낸드(NAND) 플래시 메모리 셀 블락의 독출동작을 설명하기 위한 도면이다.

도 6은 도 3에 도시된 낸드 플래시 메모리 셀 블락의 소거동작을 설명하기 위한 도면이다.

도 7은 메모리 블락과 페이지 버퍼블락의 개략적인 도면이다.

도 8은 종래의 불휘발성 메모리 장치의 개략적인 도면이다.

도 9는 도 8의 불휘발성 메모리 장치에 포함된 페이지 버퍼와 페이지 버퍼 디코더의 개략적인 도면이다.

도 10은 도 8의 불휘발성 메모리 장치에 포함된 페이지 버퍼블락의 페이지 버퍼들의 레이아웃을 나타내는 도면이다.

도 11은 본 발명의 일실시예에 따른 불휘발성 반도체 메모리 장치의 블락도이다.

도 12는 도 11의 불휘발성 메모리에 포함된 메모리 어레이의 일예를 개략적으로 나타내는 도면이다.

도 13은 도 11의 불휘발성 메모리에 포함된 페이지 버퍼블락의 일예를 나타내는 도면이다.

도 14는 도 13의 페이지 버퍼블락에 포함된 페이지 버퍼의 일예를 개략적으로 나타내는 도면이다.

도 15는 도 11의 불휘발성 메모리에 포함된 페이지 버퍼 디코더의 일예를 개략적으로 나타내는 도면이다.

도 16a 및 도 16b는 본 발명의 실시예에 따른 불휘발성 메모리의 독출모드를 설명하기 위한 플로우 차트이다.

도 17은 본 발명의 실시예에 따른 불휘발성 메모리의 독출모드를 설명하기 위한 타이밍도이다.

도 18은 본 발명의 실시예에 따른 불휘발성 메모리의 프로그래밍 모드를 설명하기 위한 플로우 차트이다.

도 19는 본 발명의 실시예에 따른 불휘발성 메모리의 프로그래밍 모드를 설명하기 위한 타이밍도이다.

도 20은 본 발명의 실시예에 따른 불휘발성 메모리의 소거모드를 설명하기 위한 타이밍도이다.

\* 도면의 주요부분에 대한 부호의 설명 \*

Yp : 버퍼선택 어드레스 Yq : 메인선택 어드레스

Yr : 서브선택 어드레스

MCARR : 메모리셀 어레이 BLCONBK: 비트라인 제어블락

PBB, NWPBB :페이지 버퍼블락

NWDE: 페이지 버퍼 디코더 NWBUF: 페이지 버퍼

IDOUT0: 내부출력 라인 GDOU0: 글로벌 출력 라인

IDIO: 제1 내부 입력 라인 nIDIO: 제2 내부 입력 라인

GDI: 제1 글로벌 입력 라인 nGDI: 제2 글로벌 입력 라인

BL, BLO: 비트라인 WL: 워드라인

BL0: 이븐 비트라인 BLo0: 오드 비트라인

SHLDe: 이븐 쉴딩신호 SHLDo: 오드 쉴딩신호

BLSLTe: 이븐 비트라인 선택신호 BLSLTo: 오드 비트라인 선택신호

SOBLK: 센싱 노드 블락킹신호

VPGM: 프로그램 전압 VPASS: 패스전압

VREAD: 독출전압 VERS: 소거전압

VDD: 전원전압 VSS: 접지전압

NLAT:래치 노드 NSEN0:센싱 노드

810:래치 유닛 820:래치전송 유닛

825:래치 드라이빙 유닛 830:센싱응답 유닛

840:출력 드라이빙 유닛 850:버퍼선택 유닛

860:센싱셋팅 유닛 870:비트라인 차단 유닛

PBSLT:버퍼선택신호 BLSHF:비트라인 차단신호

LCH:독출래치신호 /PLOAD:센싱셋팅신호

/BLDEC:블락 디코딩 신호 RBIN1, RBIN2:버퍼입력패스

도면

도면1a

도면1b

도면1c

도면2

도면3a

도면3b

|            | Erase  | Program                   | Read              |

|------------|--------|---------------------------|-------------------|

| Sel. W/L   | 0      | Vpgm                      | 0                 |

| Unsel. W/L | Float  | Vpass                     | V <sub>READ</sub> |

| SSL        | Float  | V <sub>CC</sub>           | V <sub>READ</sub> |

| GSL        | Float  | 0                         | V <sub>READ</sub> |

| CSL        | Float  | 1.5                       | 0                 |

| "0" B/L    | Float  | 0(program)                | 1.2               |

| "1" B/L    | Float  | V <sub>CC</sub> (inhibit) | <0.8              |

| Bulk       | Verase | 0                         | 0                 |

Cell Vth

-1 ~ -3V

"ON"

1 ~ 3V

"OFF"

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

## 도면13

## NWPBBO

## 도면14

NWBUFØ

### 도면 15

## NWDEØ

도면16a

## 도면16b

## 도면17

## 도면18

## 도면19

## 도면20