(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4636461号

(P4636461)

(45) 発行日 平成23年2月23日(2011.2.23)

(24) 登録日 平成22年12月3日(2010.12.3)

(51) Int.Cl.

HO3K 17/22 (2006.01)

F 1

HO3K 17/22

E

請求項の数 12 (全 36 頁)

(21) 出願番号 特願2009-5214 (P2009-5214)

(22) 出願日 平成21年1月13日 (2009.1.13)

(65) 公開番号 特開2010-166184 (P2010-166184A)

(43) 公開日 平成22年7月29日 (2010.7.29)

審査請求日 平成22年6月9日 (2010.6.9)

早期審査対象出願

(73) 特許権者 000002325

セイコーインスツル株式会社

千葉県千葉市美浜区中瀬1丁目8番地

(74) 代理人 100154863

弁理士 久原 健太郎

(74) 代理人 100142837

弁理士 内野 則彰

(74) 代理人 100123685

弁理士 木村 信行

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100108578

弁理士 高橋 詔男

最終頁に続く

(54) 【発明の名称】電源電圧監視回路、および該電源電圧監視回路を備える電子回路

## (57) 【特許請求の範囲】

## 【請求項 1】

電子回路に供給される電源電圧を監視する電源電圧監視回路であって、

前記電源電圧の増加に対して飽和特性を示す信号電圧を出力する信号出力回路と、

前記電源電圧そのものと、予め設定された設定電圧を前記信号電圧に加算した加算電圧

とを比較し、当該電源電圧が前記加算電圧を超えた場合に、前記信号電圧が正常であるこ

とを示す信号を出力する信号電圧監視回路と、

を備えることを特徴とする電源電圧監視回路。

## 【請求項 2】

前記信号電圧監視回路が、

前記電子回路に供給される前記電源電圧の配線が一方の入力端子に接続され、前記信号

出力回路から出力される前記信号電圧の配線が他方の入力端子に接続されたコンパレータ

から構成され、

前記コンパレータが、

前記他方の入力端子に、前記信号電圧に予め設定された前記設定電圧を加算して前記加

算電圧を生成する回路を有し、前記電源電圧と前記加算電圧とを比較し、当該電源電圧が

前記加算電圧を超えた場合に、前記信号電圧が正常であることを示す信号を出力する

ことを特徴とする請求項 1 に記載の電源電圧監視回路。

## 【請求項 3】

前記設定電圧が、

10

20

前記信号出力回路が動作可能となる前記電源電圧と、この動作可能となる前記電源電圧が供給された際に前記信号出力回路が出力する前記信号電圧との差分電圧であることを特徴とする請求項 1 または請求項 2 に記載の電源電圧監視回路。

【請求項 4】

コンデンサの一端と抵抗の一端とが接続され、前記コンデンサの他端が前記電源電圧の配線に接続され、前記抵抗の他端が接地された直列回路と、

前記コンデンサの一端と前記抵抗の一端との接続点の電圧である検出電圧が入力され、前記検出電圧と予め設定された閾値電圧とを比較し、前記電源電圧が前記電子回路を動作可能であるか否かを示す動作可能信号を出力する電圧監視部と、

前記動作可能信号がリセット端子に入力され、前記信号電圧が正常であることを示す信号がセット端子に入力され、出力端子から前記信号が正常な検出状態であることを示す検出信号を出力するラッピング部と

をさらに有することを特徴とする請求項 1 から請求項 3 のいずれか 1 項に記載の電源電圧監視回路。

【請求項 5】

前記信号出力回路は、

電源から電流源回路を通して電流の供給を受けるインピーダンス回路を有し、前記インピーダンス回路により前記信号電圧を生成して出力し、

前記信号電圧監視回路は、

前記電圧差が前記設定電圧を超えた場合に、前記電源電圧が前記電子回路の最低動作電源電圧以上になったことを示す信号を出力する、

ことを特徴とする請求項 1 から請求項 4 のいずれか 1 項に記載の電源電圧監視回路。

【請求項 6】

前記インピーダンス回路は、

前記電源電圧と比較される基準電圧として、さらには温度依存性を示す電圧として前記信号電圧を生成して出力すること、

を特徴とする請求項 5 に記載の電源電圧監視回路。

【請求項 7】

前記信号出力回路は、

前記電源の投入時において、前記電源電圧が所定の電圧に遷移するまでの間は、前記電源電圧の増加に従い増加する前記信号電圧を出力すると共に、前記電源電圧が前記所定の電圧を超えて増加する場合に、飽和特性を持って単調増加する電圧を前記信号電圧として出力し、

前記信号電圧監視回路は、

前記信号出力回路から出力される前記信号電圧と前記電源電圧とを比較し、前記電圧差が前記設定電圧を超えた場合に、前記電源電圧が前記電子回路の最低動作電源電圧を超えたことを示す信号を出力すること、

を特徴とする請求項 1 から請求項 6 のいずれか 1 項に記載の電源電圧監視回路。

【請求項 8】

前記信号電圧監視回路は、

前記設定電圧である予め定められるオフセット電位を、一方の入力端子に入力される信号の電圧に加えるオフセット機能を有し、

前記一方の入力端子に前記信号電圧を入力し、他方の入力端子に前記電源電圧を入力し、前記電源電圧の電圧値が前記オフセット電位が加えられた前記信号電圧の電圧値を超えた場合に、前記電源電圧が前記電子回路の最低動作電源電圧以上になったことを示す信号を出力する比較回路を

備えることを特徴とする請求項 1 から請求項 7 のいずれか 1 項に記載の電源電圧監視回路。

【請求項 9】

前記信号出力回路は、

10

20

30

40

50

前記電流源回路と前記インピーダンス回路とが直列に接続されて構成され、前記電流源回路と前記インピーダンス回路との回路接続点から前記信号電圧が出力されること

を特徴とする請求項5から請求項8のいずれか1項に記載の電源電圧監視回路。

【請求項10】

前記インピーダンス回路は、

前記電流源回路から出力される電流を入力とし、

検出された物理量に応じた電圧信号を、前記信号電圧として出力するセンサであることを特徴とする請求項9に記載の電源電圧監視回路。

【請求項11】

10

前記センサは、温度を検出する温度センサであること

を特徴とする請求項10に記載の電源電圧監視回路。

【請求項12】

請求項1から請求項11のいずれか1項に記載の電源電圧監視回路を備えることを特徴とする電子回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子回路における最低動作電源電圧の低電圧化を図り、電子回路における低電圧動作化を可能にする、電源電圧監視回路、および該電源電圧監視回路を備える電子回路に関する。

20

【背景技術】

【0002】

電子回路では、その回路に適した動作可能電源電圧範囲が定められている。その動作可能電源電圧範囲においては、その回路の動作が保証され、その回路から出力される信号の信頼度を確保できる。

【0003】

30

電子回路の電源投入時においては、その電源電圧が動作可能電源電圧になるまで過渡的に立ち上ることがから、上記の動作可能電源電圧に到達するまでの状態遷移が生じることになる。このため、電子回路には、出力される信号の信頼度を確保するために、出力される信号を制御して確定させる処置が施されている（例えば、特許文献1参照）。

【0004】

このような処置として、電源電圧監視回路を設けて、入力される電源電圧を監視して、低電源電圧状態を検出する処置がとられる場合がある。例えば、特許文献1の図1に示された電源電圧監視回路では、電子回路20に給電される電源電圧を監視し、電源電圧が所定の設定値以上になると、電子回路20に対して動作許可信号を提供する。これにより、電子回路20が誤動作することを防止することが可能となる。

【先行技術文献】

【特許文献】

【0005】

40

【特許文献1】特開平08-279739号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1の電源電圧監視回路では、前述のようにブリーダ抵抗により電源電圧を検出する電源電圧検出回路を用いている。すなわち、回路内で本来的に最低動作電源電圧が保証されるべき回路とは、別の回路により最低動作電源電圧以上になったことを検出するよう構成されている。このことは、電子回路において電源電圧を効率的に利用できないという意味において非効率である。

【0007】

50

すなわち、電源電圧の最低動作電源電圧の保証が必要である本来の回路において、電源電圧が最低動作電源電圧を超えると、直ちにその情報を外部の回路に発信できる構成が望ましい。このようすることで、最低動作電源電圧の低電圧化を図ることができるので、電子回路、例えば、I C 等の最低動作電源電圧仕様を低電圧化することが可能になる。

【0008】

本発明は、上記問題を解決すべくなされたもので、本発明の目的は、電子回路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができる、電源電圧監視回路、および該電源電圧監視回路を備える電子回路を提供することにある。

【課題を解決するための手段】

【0009】

本発明は、上記問題を解決するためになされたもので、本発明の電源電圧監視回路は、電子回路に供給される電源電圧を監視する電源電圧監視回路であって、前記電源電圧の増加に対して飽和特性を示す信号電圧を出力する信号出力回路と、前記電源電圧と前記信号電圧とを比較し、前記電源電圧と前記信号電圧との間に所定の電圧差が発生した場合に、前記信号電圧が正常であることを示す信号を出力する信号電圧監視回路と、を備えることを特徴とする。

【0010】

また、本発明の電源電圧監視回路は、電源から電流源回路を通して電流の供給を受けるインピーダンス回路を有し、前記インピーダンス回路により前記信号電圧を生成して出力する信号出力回路と、前記信号出力回路から出力される信号電圧と前記電源電圧とを比較し、前記電源電圧と前記信号電圧との間に所定の電圧差が発生した場合に、前記電源電圧が前記電子回路の最低動作電源電圧以上になったことを示す信号を出力する信号電圧監視回路と、を備えることを特徴とする。

【0011】

また、本発明の電源電圧監視回路は、前記インピーダンス回路により、前記電源電圧と比較される基準電圧として、さらには温度依存性を示す電圧として前記信号電圧を生成して出力すること、を特徴とする。

【0012】

また、本発明の電源電圧監視回路は、前記信号出力回路は、電源の投入時において電源電圧が所定の電圧に遷移するまでの間は、前記電源電圧の増加に従い増加する信号電圧を出力すると共に、前記電源電圧が前記所定の電圧を超えて増加する場合に、飽和特性を持って単調増加する電圧を信号電圧として出力し、前記信号電圧監視回路は、前記信号出力回路から出力される信号電圧と前記電源電圧とを比較し、前記電源電圧と前記信号電圧との間に所定の電圧差が発生した場合に、前記電源電圧が前記電子回路の最低動作電源電圧を超えたことを示す信号を出力すること、を特徴とする。

【0013】

また、本発明の電源電圧監視回路は、前記信号電圧監視回路は、予め定められる電位差によって示されるオフセット電位を一方の入力に設定し、入力される2つの信号の電位差が該オフセット電位を満たす場合に前記電源電圧が最低動作電源電圧を超えたことを示す信号を出力するオフセット機能付の比較回路を備えることを特徴とする。

【0014】

また、本発明の電源電圧監視回路は、前記信号出力回路は、電流源回路とインピーダンス回路とが直列に接続されて構成され、前記電流源回路とインピーダンス回路との回路接続点から前記信号電圧が出力されることを特徴とする。

【0015】

また、本発明の電源電圧監視回路は、前記インピーダンス回路は、前記電流源回路から出力される電流を入力とし、検出された物理量に応じた電圧信号を出力するセンサであることを特徴とする。

【0016】

また、本発明の電源電圧監視回路は、前記センサは、温度を検出する温度センサである

10

20

30

40

50

ことを特徴とする。

【0017】

また、本発明の電子回路は、上記のいずれかに記載の電源電圧監視回路を備えることを特徴とする。

【発明の効果】

【0018】

本発明の電源電圧監視回路によれば、信号出力回路は、温度センサ等の電源電圧に対して飽和特性を示す信号電圧を出力し、信号電圧監視回路は、信号出力回路から出力される信号電圧と電源電圧とを比較し、電源電圧と信号電圧との間に所定の電圧差が発生した場合に、信号出力回路から出力される信号電圧が正常であることを示す信号を出力する。

10

これにより、電子回路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができる。このため、例えば、I C 等の最低動作電源電圧仕様を低電圧化することが可能になる。

【図面の簡単な説明】

【0019】

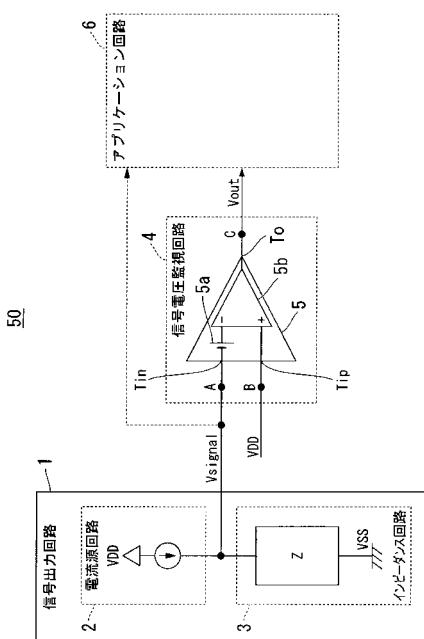

【図1】本発明の第1実施形態による電源電圧監視回路を示す概略構成図である。

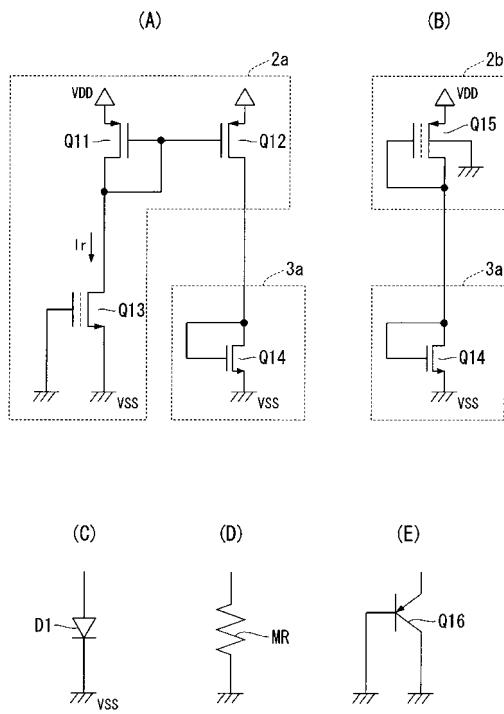

【図2】信号出力回路の構成を示す図である。

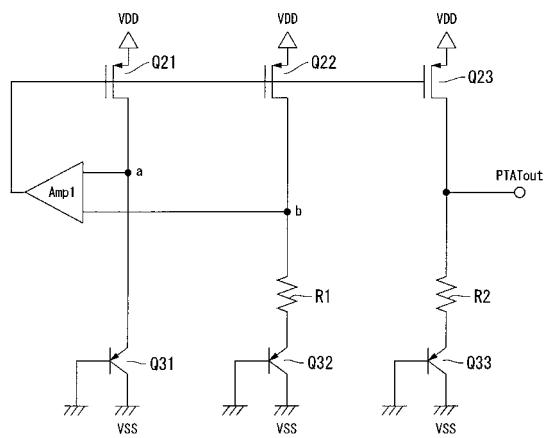

【図3】バンドギャップレファレンス回路の例を示す図である。

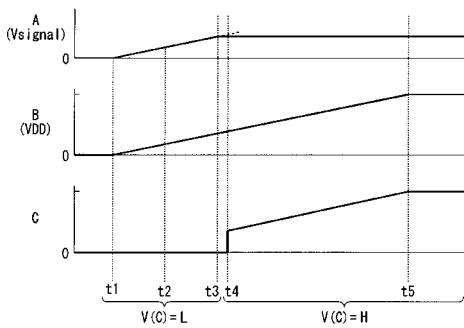

【図4】第1実施形態における電源電圧監視回路の動作を示すタイミングチャートである。

20

【図5】アプリケーション回路の第1の例を示す図である。

【図6】アプリケーション回路の第2の例を示す図である。

【図7】本発明の第2実施形態による検出回路を示す概略構成図である。

【図8】第2実施形態における検出回路の動作を示すタイミングチャートである。

【図9】第3実施形態による検出回路を示す概略構成図である。

【図10】第3実施形態における検出回路の動作を示すタイミングチャートである。

【図11】第4実施形態による検出回路を示す概略構成図である。

【図12】第4実施形態における検出回路の動作を示すタイミングチャートである。

【図13】第5実施形態による検出回路を示す概略構成図である。

【図14】第5実施形態による低電源電圧検出回路を示す概略構成図である。

30

【図15】第5実施形態による低電源電圧検出回路の動作を示す図である。

【図16】第5実施形態における検出回路の動作を示すタイミングチャートである。

【図17】第6実施形態による低電源電圧検出回路を示す概略構成図である。

【図18】第6実施形態による低電源電圧検出回路の動作を示す図である。

【図19】第7実施形態による検出回路を示す概略構成図である。

【図20】第7実施形態における検出回路の動作を示すタイミングチャートである。

【図21】第8実施形態による検出回路を示す概略構成図である。

【図22】第8実施形態における検出回路の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0020】

40

以下、本発明の実施形態について図面を参照して説明する。

【0021】

(第1実施形態)

図1は、本発明の第1の実施形態による電源電圧監視回路を示す概略構成図である。

電源電圧監視回路50は、信号出力回路1と、信号電圧監視回路4とで構成される。また、電源電圧監視回路50の出力信号は、後続するアプリケーション回路6に出力される。また、信号出力回路1の出力信号もアプリケーション回路6において使用される場合もある。

【0022】

電源電圧監視回路50における信号出力回路1は、一定電流を供給する電流源回路2と

50

、該電流源回路 2 からの電流を入力とするインピーダンス回路 3 とが直列に接続されて構成される。また、電流源回路 2 とインピーダンス回路 3 の回路接続点から信号電圧  $V_{sig}$  が出力される。

【 0 0 2 3 】

このインピーダンス回路 3 は、例えば、順方向にバイアスされ温度センサとして使用されるダイオード等で構成される。そして、電源の投入時において電源電圧  $V_{DD}$  が所定の電圧に遷移するまでの間、すなわち電源電圧が低くインピーダンス回路 3 に供給される電流が少ない場合は、インピーダンス回路 3 は高インピーダンス状態を示し、信号電圧  $V_{sig}$  の電圧は電源電圧  $V_{DD}$  になる。すなわち、電源電圧  $V_{DD}$  が低い状態では、インピーダンス回路 3 から出力される信号電圧  $V_{sig}$  は、電源電圧  $V_{DD}$  の増加と共に直線的に増加する（図 4 の信号電圧  $V_{sig}$  と電源電圧  $V_{DD}$  を参照）。

【 0 0 2 4 】

そして、電源電圧  $V_{DD}$  が増加し所定の電圧を超えた場合は、電流源回路 2 を通してインピーダンス回路 3 に流れる電流が増大するが、インピーダンス回路 3 に一定値以上の電流が流れると、インピーダンス回路 3 の両端の電圧は飽和特性を示し、一定の電圧（閾値電圧）となる。さらに、電源電圧が増加し、インピーダンス回路 3 に供給される電流が増加すると、インピーダンス回路 3 の両端の電圧は、前述の一定値から飽和特性を持って緩やかに単調増加する電圧となる。なお、インピーダンス回路 3 が温度センサ用のダイオード等で構成される場合には、前述の一定の電圧（閾値電圧）は温度依存性を示す電圧となる。このインピーダンス回路の詳細については、後述する。

【 0 0 2 5 】

上述のインピーダンス回路 3 から出力される信号電圧  $V_{sig}$  は、信号電圧監視回路 4 において電源電圧  $V_{DD}$  と比較される際の基準電圧となる信号であり、前述のように、インピーダンス回路 3 が温度センサ用のダイオード等で構成される場合には、温度依存性を示す信号となる。

【 0 0 2 6 】

電源電圧監視回路 5 0 における信号電圧監視回路 4 は、2つの入力端子（ $T_{in}$ 、 $T_{in}$ ）と出力端子  $T_o$  を有する。信号電圧監視回路 4 は、入力される 2 つの信号の電位を比較し、その電位差が所定の値以上であるか否かを検出し、検出結果をローレベルまたはハイレベルの 2 値化された論理信号によって出力する。

【 0 0 2 7 】

信号電圧監視回路 4 の一形態としてオフセットコンパレータ 5 を示す。オフセットコンパレータ 5 は、バイアス電圧源 5 a 及びコンパレータ 5 b を備える。バイアス電圧源 5 a は、所定のバイアス電位  $V_b$  を発生させて、入力端子  $T_{in}$  の入力信号に対して電圧オフセットを設定する。コンパレータ 5 b は、入力される 2 つの信号の電位差を検出する。

【 0 0 2 8 】

オフセットコンパレータ 5 では、入力端子  $T_{in}$  がバイアス電圧源 5 a を介してコンパレータ 5 b の反転入力端に接続され、入力端子  $T_{in}$  がコンパレータ 5 b の非反転入力端に接続され、コンパレータ 5 b の出力端が出力端子  $T_o$  に接続される。

【 0 0 2 9 】

入力端子  $T_{in}$  に入力される信号は、バイアス電圧源 5 a によりバイアス電位  $V_b$  分だけ高い電位に変換され、コンパレータ 5 b に入力される。このような構成をとることにより、オフセットコンパレータ 5 は、入力端子  $T_{in}$  に入力された信号が、入力端子  $T_{in}$  に入力された信号の電圧より、所定の電圧（バイアス電位  $V_b$ ）分だけ高くなつた閾値電圧により比較される。

【 0 0 3 0 】

入力端子  $T_{in}$  に入力される信号  $V_{DD}$  の電位が、入力端子  $T_{in}$  に入力される信号  $V_{sig}$  の電位にバイアス電位  $V_b$  を加算した電圧より低い状態から高い状態に遷移すると出力信号  $V_{out}$  が反転する。その出力信号  $V_{out}$  は、入力端子  $T_{in}$  に入力される信号  $V_{DD}$  の電位が、入力端子  $T_{in}$  に入力される信号  $V_{sig}$  の電位にバイアス電位  $V_b$

10

20

30

40

50

を加算した電圧より低い状態では、ローレベルを示す。また、出力信号  $V_{out}$  は、入力端子  $T_{ip}$  に入力される信号  $V_{DD}$  の電位が、入力端子  $T_{in}$  に入力される信号  $V_{sig}$  の電位にバイアス電位  $V_b$  を加算した電圧より高い状態では、ハイレベルを示す。

#### 【0031】

信号電圧監視回路 4 の出力電圧  $V_{out}$  は、後続するアプリケーション回路 6 に向けて出力される。アプリケーション回路 6 では、信号電圧監視回路 4 の出力電圧  $V_{out}$  を入力し、該出力電圧  $V_{out}$  がハイレベルに遷移したことを検出し、電源電圧が最低動作電源電圧を超えたことを検知する。また、信号出力回路 1 の信号出力  $V_{sig}$  も、例えば、温度センサの信号としてアプリケーション回路 6 に出力され、アプリケーション回路 6 において利用されることがある。

10

#### 【0032】

また、図 2 は、信号出力回路の構成例を示す図である。図 2 (A) に示す例は、電流源回路 2a を、参照電流  $I_r$  を生成するデプレッション型の PMOS トランジスタ Q13 と、カレントミラー回路を構成する PMOS トランジスタ Q11, Q12 とで構成している。また、インピーダンス回路 3a を、ゲートとドレインとを基準電位  $V_{SS}$  に共通接続した NMOS トランジスタ Q14 で構成し、NMOS トランジスタ Q14 をダイオード ( 温度検出用センサ ) として用いる例を示している。

#### 【0033】

また、図 2 (B) は、バックバイアスをかけたデプレッション型の PMOS ランジスタ Q15 により電流源回路 2b を構成し、インピーダンス回路 3a を図 2 (A) と同様に、ゲートとドレインとを基準電位  $V_{SS}$  に共通接続した NMOS トランジスタ Q14 で構成した例を示している。

20

#### 【0034】

なお、インピーダンス回路 12a は、図 2 (A), (B) に示す NMOS トランジスタ Q14 に限定されず、電流源回路からの電流を入力とし、検出された物理量に応じた電圧信号を出力するセンサであればよい。例えば、図 2 (C) に示す温度検出用のダイオード D をインピーダンス回路として使用することができる。また、図 2 (D) に示す MR 素子 ( 磁気抵抗素子 ) をインピーダンス回路として使用することができる。さらに、図 2 (E) に示す、コレクタとベースを共通接地したバー・ポラトランジスタ素子 Q15 を温度センサとして使用することができる。

30

#### 【0035】

また、図 3 に示すような、バンドギャップレファレンス回路であってもよい。図 3 に示すバンドギャップレファレンス回路では、ゲートが共通接続される 3 つの PMOS トランジスタ Q21, Q22, Q23 を有している。

また、PMOS トランジスタ Q21 のドレインにエミッタが接続されると共に、コレクタとベースが基準電位  $V_{SS}$  に共通接続されるバイポーラ型の PNP トランジスタ Q31 と、PMOS トランジスタ Q22 のドレインに抵抗  $R_1$  を介してエミッタが接続されると共に、コレクタとベースが基準電位  $V_{SS}$  に共通接続されるバイポーラトランジスタ Q32 を有している。

#### 【0036】

さらに、PMOS トランジスタ Q23 のドレインに抵抗  $R_2$  を介してエミッタが接続されると共に、コレクタとベースが基準電位  $V_{SS}$  に共通接続されるバイポーラ型の PNP トランジスタ Q33 を有している。ここで、トランジスタ Q31, Q32 はエミッタ面積が 1 対  $n$  ( $n > 1$ ) の関係を有している。

40

#### 【0037】

また、トランジスタ Q31 のエミッタ側 ( 回路点 a ) と、抵抗  $R_1$  の回路点 b とが演算增幅器  $AMP_1$  の入力端子にイマジナリーショート点として入力され、算增幅器  $AMP_1$  の出力端子は、PMOS トランジスタ Q21, Q22, Q23 のゲートに接続されている。これにより、前述の回路点 a と回路点 b の電位が等しくなるように PMOS トランジスタ Q21 と Q22 に流れる電流が制御される。また、抵抗  $R_1$  と  $R_2$  は同じ温度係数を持

50

つ抵抗が選択され、例えば、抵抗 R 1 と抵抗 R 2 の抵抗値が等しくなるように選定する。

【0038】

この構成において、PMOSトランジスタQ23が電流源回路となり、抵抗R2とトランジスタQ33がインピーダンス回路となるPTAT回路が構成され、出力電圧PTAT<sub>out</sub>(PMOSトランジスタQ23のドレインの電圧)は、

【0039】

$$PTAT_{out} = (V_t / R_1) \ln(N), \dots$$

ここで、「 $V_t = KT/q$ 、K:ボルツマン定数、T:絶対温度、q:電子の電荷量」で表され、出力電圧PTAT<sub>out</sub>は絶対温度Tに比例する電圧として出力される。

【0040】

このように、図3に示すバンドギャップレファレンス回路は、電流源回路(PMOSトランジスタQ23)と、インピーダンス回路(抵抗R2とバイポーラトランジスタQ33)を有しており、図1に示す信号出力回路1とすることができます。また、例えば、先行文献(特開2001-147725)において示されるバンドギャップレファレンス回路も、同様に、図1に示す信号出力回路1として用いることができる。

【0041】

上述したように、信号出力回路1は電流源回路とインピーダンス回路とで構成されるが、このインピーダンス回路は、電源の投入時において電源電圧VDDが所定の電圧に遷移するまでの間は、電源電圧の増加に従い直線的に増加すると共に、電源電圧が所定の電圧範囲を超えた場合に一定値の電圧、または該一定値から緩やかに単調増加する電圧を信号電圧として出力するインピーダンス回路であればよい。すなわち、インピーダンス回路は、図2に示した、トランジスタ、ダイオード、MRセンサ等、図3に示したバンドギャップレファレンス回路に限らず、例えば、ツエナーダイオード(電源に抵抗を介して接続されるツエナーダイオード)等であってもよい。

【0042】

図4は、第1実施形態における電源電圧監視回路の動作を示すタイミングチャートである。図4に示すタイミングチャートは、図1に示す信号電圧監視回路4のA点に入力される信号電圧V<sub>sig</sub>、B点に入力される電源電圧VDD、およびC点から出力される出力信号V<sub>out</sub>の遷移状態を示している。

【0043】

図に示される初期状態では、電源は未投入の状態であり、それぞれの回路において電荷の充電などもなく、各信号とも無信号の状態を示している。

時刻t1において、信号出力回路1および信号電圧監視回路4に電源が投入される。その後、電源電圧VDDが徐々に上昇する。同じ電源から電力が供給される信号出力回路1の出力である信号電圧V<sub>sig</sub>は、電源電圧VDDが低い状態では、電流源回路2の働きにより出力電圧は電源電圧VDDになる。すなわち、信号電圧V<sub>sig</sub>は、電源電圧VDDの上昇に応じて同様の変化特性を示して徐々に上昇する。

【0044】

信号電圧監視回路4では、入力される信号の判定に一方の信号にオフセット電位を印加して比較することにより、入力される信号の電位差が小さな場合でもオフセットされた電位によって比較判定された結果が出力されることから出力信号がハイレベルとローレベルを交互に出力してばたつくような不安定な状態となることはない。このため信号V<sub>out</sub>は、ローレベルを示す。すなわち、時刻t1から時刻t2までの間は、信号電圧V<sub>sig</sub>および電源電圧VDDは徐々に直線的に増加するが、信号電圧V<sub>sig</sub>と電源電圧VDDの電位差が、オフセットコンパレータ5に付与されたオフセット電位よりも小さいため、信号V<sub>out</sub>は、ローレベルを示す。

【0045】

電源投入後の最低動作電源電圧が供給されるまでの過渡状態においては、信号電圧監視回路4から出力される信号V<sub>out</sub>がローレベルに維持されるため、アプリケーション回路6では、例えば、信号V<sub>out</sub>がローレベルの場合に、例えば、自身を非活性状態に置

10

20

30

40

50

き、不要な信号を出力しないようにできる。

【0046】

時刻  $t_2$  では、電源電圧  $V_{DD}$  が上昇し、それぞれの回路が動作可能な状態に遷移する。信号電圧監視回路 4 では、入力される信号電圧  $V_{sig}$  と電源電圧  $V_{DD}$  の電位差が小さな状態にあるが、一方の入力信号にはオフセット電位が印加されることにより、信号  $V_{out}$  は、ローレベルに確定している。アプリケーション回路 6 では、信号  $V_{out}$  がローレベルに確定することにより、例えば、自身を非活性状態に置き、不要な信号を出力しないようにできる。

【0047】

時刻  $t_3$  では、信号  $V(A)$  によって示される信号出力回路 1 から出力される信号電圧  $V_{sig}$  が所定の電圧に到達すると、インピーダンス回路 3 の飽和電圧特性により、一定の電圧が出力されるようになる。電源が出力する電源電圧  $V_{DD}$  の電位は、継続的に上昇する。また、信号電圧  $V_{sig}$  と電源電圧  $V_{DD}$  の電位差は、オフセットコンパレータ 5 に付与されたオフセット電位よりも小さいため信号  $V_{out}$  は、ローレベルに維持されている。

10

【0048】

時刻  $t_4$  では、信号出力回路 1 から出力される信号電圧  $V_{sig}$  と電源電圧  $V_{DD}$  とに、所定の電位差、すなわち信号電圧監視回路 4 におけるオフセット電位の電圧以上の電位差が生じたことが、信号電圧監視回路 4 によって検出される。その検出によって、例えば、電源によって印加される電源電圧  $V_{DD}$  が信号出力回路 1 およびアプリケーション回路 6 に動作可能な電源電圧が供給される状態に遷移したことが示される。

20

【0049】

これにより、信号電圧監視回路 4 は、信号  $V_{out}$  に出力していた出力信号のローレベル状態を解除し、ハイレベルに遷移させる。このハイレベルの電位は、電源電圧  $V_{DD}$  の電位上昇にともなって上昇する。

【0050】

時刻  $t_5$  では、電源電圧  $V_{DD}$  が所定の動作可能電源電圧に達して上昇が止まり、電源電圧  $V_{DD}$  が一定値を示すようになる。また、信号  $V_{out}$  の上昇も止まり一定値を示す状態に遷移する。

【0051】

30

以上に示したように電源が投入されることにより各信号の状態が遷移する。電源が出力する電源電圧  $V_{DD}$  が所定の動作可能電源電圧に達するまで、信号  $V_{out}$  に不要な検出信号が出力されることなく、ローレベルを確保できる。

【0052】

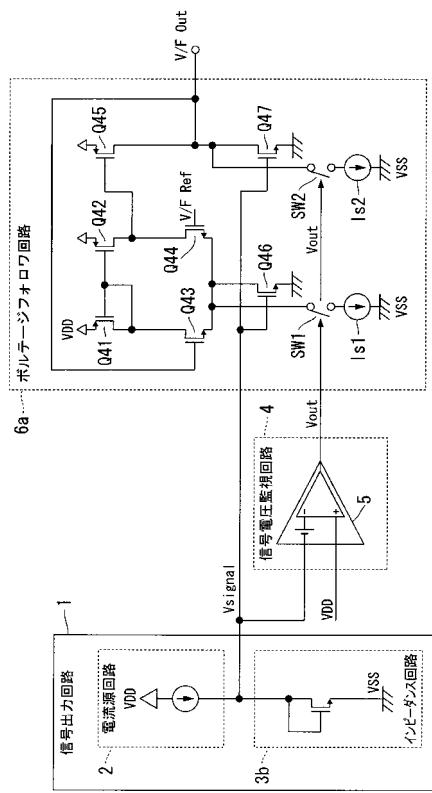

また、図 5 は、図 1 に示すアプリケーション回路の第 1 の例を示す図であり、後段に接続されるアプリケーション回路の例として、ボルテージフォロワ回路 6 a を例に挙げたものである。

【0053】

図 5 に示す例は、信号出力回路 1 内のインピーダンス回路を、N MOS トランジスタをダイオードとして使用し、温度センサとしてインピーダンス回路 3 b を構成した例である。また、ボルテージフォロワ回路 6 a において、信号出力回路 1 から出力される信号電圧  $V_{sig}$  と、信号電圧監視回路 4 からの出力信号  $V_{out}$  の両方を利用する例である。

40

【0054】

このボルテージフォロワ回路 6 a は、カレントミラー負荷型作動入力段と、電流負荷型のソース接地利得段とで構成されるボルテージフォロワ回路であり、N MOS トランジスタ Q 4 4 のゲートに入力される入力信号  $V_{F/F \cdot REF}$  の電圧が、出力信号  $V_{F/F \cdot Out}$  の電圧として出力される。

【0055】

このボルテージフォロワ回路 6 a において、カレントミラー負荷型作動入力段は、PMOS トランジスタ Q 4 1, Q 4 2 で構成されるカレントミラー回路と、作動信号がゲート

50

に入力されるN M O SトランジスタQ 4 3, Q 4 4と、バイアス電流源となるN M O SトランジスタQ 4 6, Q 4 7とで構成されている。また、N M O SトランジスタQ 4 3のゲートは、P M O SトランジスタQ 4 5のドレインに接続され、ボルテージフォロワ回路が構成されている。ソース接地利得段は、P M O SトランジスタQ 4 5とN M O SトランジスタQ 4 7とで構成されている。

#### 【0056】

上記構成において、N M O SトランジスタQ 4 6, Q 4 7のゲートには、信号出力回路1から出力される信号電圧V s i gが入力される。すなわち、ボルテージフォロワ回路6 aにおけるバイアス電流は、信号電圧V s i gをゲートに受けるN M O SトランジスタQ 4 6, Q 4 7により、生成されるものとしている。

10

#### 【0057】

この構成により、電源電圧V D Dが上昇し、信号出力回路1からの出力信号V s i gの電圧レベルが、N M O SトランジスタQ 4 6, Q 4 7のゲート・ソース間の閾値を越えると、ボルテージフォロワ回路6 a内のN M O SトランジスタQ 4 6, Q 4 7によりバイアス電流が生成され、ボルテージフォロワ回路6 aとしての動作を開始することができる。このように、信号出力回路1からの信号V s i gにより、ボルテージフォロワ回路6 aを直接に活性化させることができ、ボルテージフォロワ回路6 aにおける最低動作電源電圧の低電圧化を図ることができる。

#### 【0058】

また、この図5に示すボルテージフォロワ回路6 aにおいては、電源V D Dが低下すると、信号電圧V s i gも低下するので、バイアス電流が低下することになり、ボルテージフォロワ回路6 aの動作ポイントが大きく想定から外れてしまうことが考えられる。このような場合、信号V o u tによってS W 1, S W 2をON / OFF制御することにより、電流源I s 1, I s 2によりバイアス電流の低下を補うようなことが可能となる。なお、信号V o u tは、信号電圧監視回路4内のオフセットコンパレータ5の出力信号である。

20

#### 【0059】

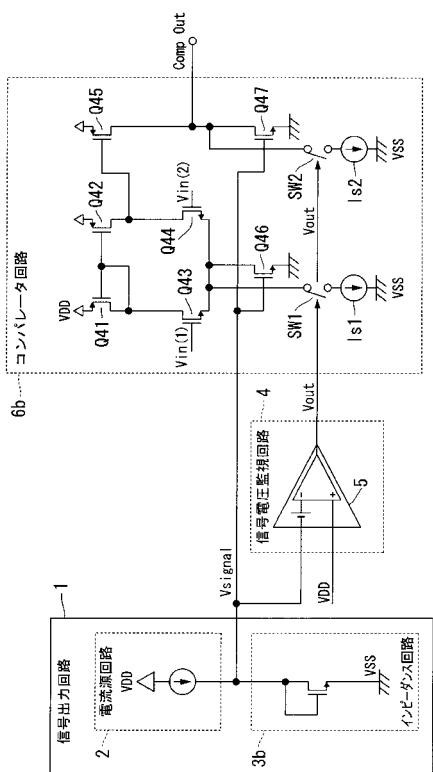

また、図6は、図1に示すアプリケーション回路の第2の例を示す図であり、後段に接続されるアプリケーション回路の例として、コンパレータ回路6 bを例に挙げたものである。

#### 【0060】

30

図6に示す例は、信号出力回路1内のインピーダンス回路を、N M O Sトランジスタをダイオードとして使用し、温度センサとしてインピーダンス回路3 bを構成した例である。また、コンパレータ回路6 bにおいて、信号出力回路1から出力される信号電圧V s i gと、信号電圧監視回路4からの出力信号V o u tの両方を利用する例である。

#### 【0061】

このコンパレータ回路6 bは、図5に示すボルテージフォロワ回路6 aと同様な回路構成のものであり、同一の構成部分には同一の符号を付し、重複する説明は省略する。このコンパレータ回路6 bでは、N M O SトランジスタQ 4 3, Q 4 4のそれぞれのゲートに入力される信号V i n (1)の電圧と、V i n (2)と電圧とが比較され、比較結果が出力信号C o m p · O u tとして出力される。

40

#### 【0062】

この構成により、電源電圧V D Dが上昇し、信号出力回路1から出力される信号電圧V s i gの電圧レベルが、N M O SトランジスタQ 4 6, Q 4 7のゲート・ソース間の閾値を越えると、コンパレータ回路6 b内のN M O SトランジスタQ 4 6, Q 4 7によりバイアス電流が生成され、コンパレータ回路6 bとしての動作を開始することができる。このように、信号出力回路1から出力される信号電圧V s i gにより、コンパレータ回路6 bを直接に活性化させることができ、コンパレータ回路6 bにおける最低動作電源電圧の低電圧化を図ることができる。

#### 【0063】

また、この図6に示すコンパレータ回路6 bにおいては、電源電圧V D Dが低下すると

50

、信号電圧  $V_{sig}$  も低下するので、バイアス電流が低下することになり、コンパレータ回路 6 b の動作ポイントが大きく想定から外れてしまうことが考えられる。このような場合、 $V_{out}$  によって SW1, SW2 を ON / OFF 制御することにより、電流源  $I_{s1}$ ,  $I_{s2}$  によりバイアス電流の低下を補うようなことが可能となる。なお、信号  $V_{out}$  は、信号電圧監視回路 4 内のオフセットコンパレータ 5 の出力信号である。

【 0 0 6 4 】

以上、本発明の第 1 実施形態について説明したが、図 1 に示す電源電圧監視回路 50 において、前述の信号出力回路は信号出力回路 1 が相当し、前述の信号電圧監視回路は信号電圧監視回路 4 が相当する。また、前述のオフセット機能付の比較回路はオフセットコンパレータ 5 が相当し、前述の電流源回路は電流源回路 2 が相当し、インピーダンス回路はインピーダンス回路 3 が相当する。 10

【 0 0 6 5 】

そして、図 1 に示す電源電圧監視回路 50 においては、温度センサ等の印加される電圧に対して飽和特性を示す信号電圧  $V_{sig}$  を出力する信号出力回路 1 と、電源電圧  $V_{DD}$  と信号電圧  $V_{sig}$  とを比較し、電源電圧  $V_{DD}$  と信号電圧  $V_{sig}$  との間に所定の電圧差が発生した場合に、信号電圧  $V_{sig}$  が正常であることを示す信号  $V_{out}$  を出力する信号電圧監視回路 4 と、を有して構成される。

これにより、電子回路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができる。また、電源電圧  $V_{DD}$  が所定の電圧になることを持つことなく、例え、定格動作電圧よりもかなり低い電圧であっても、この電源電圧において回路動作を許可することができる。 20

【 0 0 6 6 】

また、本発明の電源電圧監視回路 50 においては、電源から電流源回路 2 を通して電流の供給を受けるインピーダンス回路 3 を有し、このインピーダンス回路 3 により、信号電圧  $V_{sig}$  を生成して出力する信号出力回路 1 と、信号出力回路 1 から出力される信号電圧  $V_{sig}$  と電源電圧  $V_{DD}$  とを比較し、電源電圧  $V_{DD}$  と信号電圧  $V_{sig}$  との間に所定の電圧差が発生した場合に、電源電圧  $V_{DD}$  が電子回路の最低動作電源電圧以上になったことを示す信号  $V_{out}$  を出力する信号電圧監視回路 4 と、有して構成される。

これにより、電子回路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができるようになる。 30

【 0 0 6 7 】

また、本発明の電源電圧監視回路 50 においては、インピーダンス回路 3 により、電源電圧  $V_{DD}$  と比較される基準電圧として、さらには温度依存性を示す電圧として信号電圧  $V_{sig}$  を生成して出力する。

これにより、例え、温度検出用のダイオード等の温度センサの検出信号を信号電圧  $V_{sig}$  とし、この信号電圧  $V_{sig}$  を電源電圧  $V_{DD}$  と比較して、信号電圧  $V_{sig}$  が正常であること示す信号  $V_{out}$  を出力することができる。

【 0 0 6 8 】

また、本発明の電源電圧監視回路 50 においては、信号出力回路 1 は、電源の投入時に電源電圧  $V_{DD}$  が所定の電圧になるまでは、電源電圧  $V_{DD}$  の増加に従い増加する電圧を信号電圧  $V_{sig}$  として出力すると共に、電源電圧  $V_{DD}$  が所定の電圧を超えて増加する場合に、飽和特性を持って単調増加する電圧を信号電圧  $V_{sig}$  として出力する。信号電圧監視回路 4 は、信号出力回路 1 から出力される信号電圧  $V_{sig}$  と電源電圧  $V_{DD}$  とを比較し、電源電圧  $V_{DD}$  と信号電圧  $V_{sig}$  との間に所定の電圧差が発生した場合に、電源電圧  $V_{DD}$  が電子回路における最低動作電源電圧以上になったことを示す信号  $V_{out}$  を出力する。 40

これにより、電子化路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができるようになる。

【 0 0 6 9 】

また、本発明の電源電圧監視回路においては、信号電圧監視回路 4 は、オフセット電位

が一方の入力に設定される比較器（オフセットコンパレータ5）を有し、この比較器（オフセットコンパレータ5）により信号出力回路1から出力される信号電圧 $V_{sig}$ と電源電圧 $V_{DD}$ とを比較し、信号出力回路1から出力される信号電圧 $V_{sig}$ と電源電圧 $V_{DD}$ の電位差がオフセット電位を満たす場合に電源電圧 $V_{DD}$ が最低動作電源電圧を超えたことを示す信号 $V_{out}$ を出力する。

これにより、信号出力回路からの信号とオフセット電位とを基に、電子回路における最低動作電源電圧を容易に検出することができる。

#### 【0070】

また、本発明の電源電圧監視回路50においては、信号出力回路1は、電流源回路2とインピーダンス回路3とが直列に接続されて構成され、電流源回路2とインピーダンス回路3との回路接続点から信号電圧が出力される。10

これにより、例えば、インピーダンス回路として順方向にバイアスされたダイオード等を使用して信号出力回路1を容易に構成することができる。また、インピーダンス回路を温度センサ等で構成することができる。

#### 【0071】

また、本発明の電源電圧監視回路50においては、インピーダンス回路3は、電流源回路2から出力される電流を入力とし、検出された物理量に応じた電圧信号を出力するセンサである。

これにより、センサからの出力信号を検出対象として、センサが安定して動作できる電源電圧のレベルを検出することができる。このため、センサが安定して動作できる電圧を電子回路の最低動作電源電圧とすることことができ、電子回路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができるようになる。20

#### 【0072】

また、本発明の電源電圧監視回路50においては、インピーダンス回路3は、電流源回路2から出力される電流を入力とし、検出された温度に応じた電圧信号を出力する温度センサである。

これにより、温度センサからの出力信号を検出対象として、この温度センサが安定して動作できる電源電圧のレベルを検出することができる。このため、温度センサが安定して動作できる電圧を電子回路の最低動作電源電圧とることができ、電子回路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができるようになる。30

#### 【0073】

また、本発明の電子回路は、本発明の電源電圧監視回路を備えるので、これにより、電子回路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができるようになる。

#### 【0074】

##### （第2実施形態）

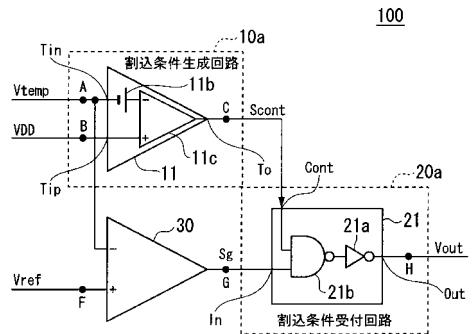

図7は、第2実施形態による検出回路を示す概略構成図である。この第2の実施の形態では、図1に示す第1の実施の形態の電源電圧監視回路の応用例であり、温度センサ等の信号を検出する検出回路の例を示したものである。

#### 【0075】

この図7に示す第2の実施の形態では、図1に示す信号出力回路1中のインピーダンス回路を、例えば、図2に示すようにダイオード等の温度センサとして構成し、この温度センサから信号される信号を $V_{temp}$ としたものである。すなわち、図1に示す信号出力回路1から出力される信号電圧 $V_{sig}$ を、温度センサの出力信号 $V_{temp}$ としたものである。また、図1に示す信号電圧監視回路4を、図7に示す割込条件生成回路10aとして使用した例を示したものである。40

#### 【0076】

なお、後述する第3実施形態から第8実施の形態において説明される検出回路、および第9実施形態のセンサ装置も、図1に示す本発明の電源電圧監視回路の応用例として示されるものである。また、図1の信号電圧監視回路4を構成するオフセットコンパレータ550

が、第4実施形態から第7の実施形態における割込条件生成回路中のオフセットコンパレータ11に相当するものである。

#### 【0077】

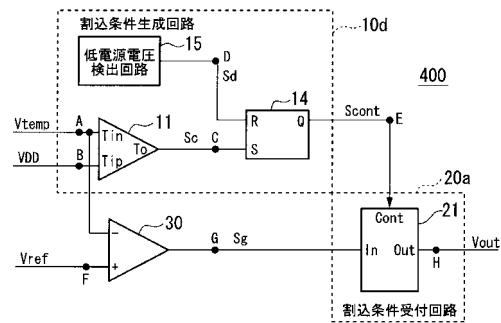

図7に示す検出回路100は、割込条件生成回路10a、割込条件受付回路20a及びコンパレータ30を備える。

検出回路100における割込条件生成回路10aは、2つの入力端子(Tip、Tin)と出力端子Toを有する。割込条件生成回路10aは、入力される2つの信号の電位を比較し、その電位差が所定の値以上であるか否かを検出し、検出結果を2値化された論理信号によって出力する。

#### 【0078】

割込条件生成回路10aの一形態としてオフセットコンパレータ11を示す。オフセットコンパレータ11は、バイアス電圧源11b及びコンパレータ11cを備える。バイアス電圧源11bは、所定のバイアス電位Vbを発生させて、入力される信号に発生させた電位分の電圧オフセットを設定する。コンパレータ11cは、入力される2つの信号の電位差を検出する。

オフセットコンパレータ11では、入力端子Tinがバイアス電圧源11bを介してコンパレータ11cの反転入力端に接続され、入力端子Tipがコンパレータ11cの非反転入力端に接続され、コンパレータ11cの出力端が出力端子Toに接続される。

入力端子Tinに入力される信号は、バイアス電圧源11bによりバイアス電位Vb分だけ高い電位に変換され、コンパレータ11cに入力される。

このような構成をとることにより、オフセットコンパレータ11は、入力端子Tipに入力された信号の電圧が、入力端子Tinに入力された信号の電圧より、所定の電圧(バイアス電位Vb)分だけ高くなつた閾値電圧により比較される。入力端子Tipに入力される信号の電位が、入力端子Tinに入力される信号の電位にバイアス電位Vbを加算した電圧より低い状態から高い状態に遷移すると出力信号が反転する。その出力信号は、前者の状態(バイアス電位Vbを加算した電圧より低い状態)では、ローレベルを示す。

割込条件生成回路10aからは、オフセットコンパレータ11の出力と同じ信号が出力される。

#### 【0079】

割込条件受付回路20aは、信号入力端子Inと制御入力端子Contと出力端子Outを有する。

割込条件受付回路20aの一形態として出力設定回路21を示す。出力設定回路21は、インバータ(反転回路)21a及びNAND(反転論理積)ゲート21bを備える。出力設定回路21では、信号入力端子InがNANDゲート21bの一方の入力端に接続され、制御入力端子ContがNANDゲート21bの他方の入力端に接続され、NANDゲート21bの出力端がインバータ21aを介して出力端子Outに接続される。このような構成をとることにより、制御入力端子Contに入力される制御信号Scontがローレベルの場合には、出力信号Voutがローレベルに設定され、制御信号Scontがローレベルの場合には、入力される信号Sgと同じ論理を示す信号が出力信号Voutに出力される。すなわち、割込条件受付回路20aは、制御信号として入力される割込信号による割込みが解除されるまで、入力される信号Sgの出力を許可せずローレベルを示す所定の電圧を出力信号Voutとして出力する。また、割込条件受付回路20aは、割込信号による割込みが解除されると、入力される信号Sgの出力を許可して出力信号Voutとして出力する。

コンパレータ30は、入力される2つの信号の電位差を検出し、検出した電位差に基づいて判定した結果を2値化した論理信号で出力する。

#### 【0080】

次に、センサ回路を構成する検出回路100の接続例を示す。検出回路100には、検出回路100を作動させる電源電圧VDDと、図示されないセンサ回路からの入力信号Vtempと、図示されない基準電源RFから出力される基準電圧Vrefとが入力される

10

20

30

40

50

。図示されないセンサ回路及び基準電源 R F は、電源に接続される電源端子に定電流源が接続され、その定電流源の負荷となるインピーダンス素子を介して接地電圧 V S S に接続される。それぞれの出力は、定電流源とインピーダンス素子との接続点から出力される。よって、電源電圧 V D D が低い状態では、これらの出力電圧は電流源の働きにより電源電圧になる。

割込条件生成回路 10 a における入力端子 T i p には、電源が接続され電源電圧 V D D が入力される。また、入力端子 T i n には、図示されないセンサ回路の出力端が接続される。

コンパレータ 30 における非反転入力端子には、基準電圧 V r e f を出力する図示されない基準電源 R F が接続され、反転入力端子には、図示されないセンサ回路の出力端が接続される。

割込条件受付回路 20 a における入力端子 I n にはコンパレータ 30 の出力端が接続され、制御入力端子 C o n t には割込条件生成回路 10 a の出力端子 T o が接続され、出力端子 T o が検出回路 100 の出力端子に接続される。

#### 【 0 0 8 1 】

このような構成による検出回路 100 では、割込条件生成回路 10 a から出力される制御信号 S c o n t は、電源電圧 V D D が入力信号 V t e m p の電圧にバイアス電位 V b 加算した電位より低い場合にはローレベルを示す。また、割込条件生成回路 10 a から出力される制御信号 S c o n t は、電源電圧 V D D が入力信号 V t e m p の電圧にバイアス電位 V b 加算した電位より高い場合にはハイレベルを示す。

コンパレータ 30 の出力信号 S g は、入力信号 V t e m p の電圧が基準電圧 V r e f より低い場合にはハイレベルを示す。また、入力信号 V t e m p の電圧が基準電圧 V r e f より高い場合にはローレベルを示す。

割込条件受付回路 20 a の出力信号 V o u t には、制御信号 S c o n t がローレベルの場合には、固定的にローレベルが出力され、制御信号 S c o n t がハイレベルの場合には、入力信号 V t e m p に応じて変化するコンパレータ 30 からの出力信号 S g が出力される。

#### 【 0 0 8 2 】

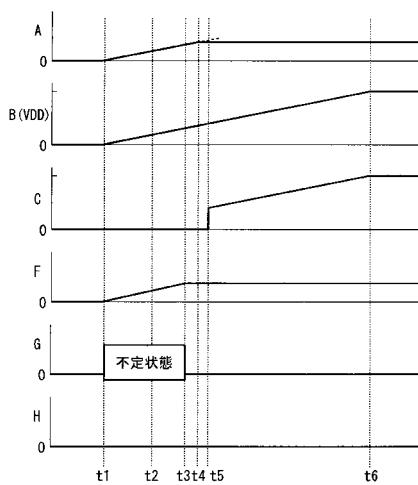

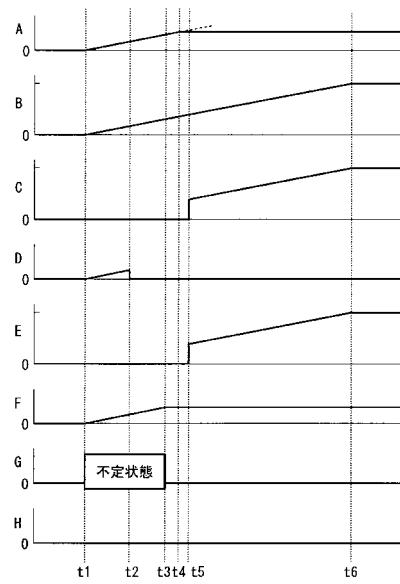

図 8 は、第 2 実施形態における検出回路 100 の動作を示すタイミングチャートの例である。図 7 のブロック図に示された点 A ~ H にしたがって、それらの点における各信号の遷移について説明する。

点 A の波形は、センサ回路から入力され、検出回路 100 が検出処理をする入力信号 V t e m p の電圧遷移を示す。点 B の波形は、検出回路 100 に供給される電源電圧 V D D の電圧遷移を示す。この電源電圧 V D D は、検出回路 100 並びに図 7 に図示されていない基準電源 R F 及びセンサ回路に供給されている電源電圧を示す。点 C の波形は、割込条件生成回路 10 a におけるオフセットコンパレータ 11 によって判定され、割込条件生成回路 10 a から出力された制御信号 S c o n t の電圧遷移を示す。この信号に基づいて、割込条件受付回路 20 a が制御される。点 F の波形は、基準電源 R F から出力される基準電圧 V r e f の電圧遷移を示す。点 G の波形は、コンパレータ 30 による判定結果である出力信号 S g の電圧遷移を示す。この信号は、割込条件受付回路 20 a への入力信号になる。点 H の波形は、割込条件受付回路 20 a の出力信号 V o u t の電圧遷移を示す。このタイミングチャートに示される範囲では、センサ回路によって検出すべき事象は生じていない状態を示し、出力信号 V o u t は、常時ローレベルを示す。

#### 【 0 0 8 3 】

図に示される初期状態では、電源は未投入の状態であり、それぞれの回路において電荷の充電などもなく、各信号とも無信号の状態を示している。

時刻 t 1 において、検出回路 100 並びに検出回路 100 に接続されているセンサ回路及び基準電源 R F に対し、電源が投入される。

その後、電源電圧 V D D が徐々に上昇する。同じ電源から電力が供給されるセンサ回路及び基準電源 R F の出力である入力信号 V t e m p 及び基準電圧 V r e f は、電源電圧 V

10

20

30

40

50

$V_{DD}$  が低い状態では、電流源の働きによりこれらの出力電圧は電源電圧  $V_{DD}$  になる。入力信号  $V_{temp}$  及び基準電圧  $V_{ref}$  は、電源電圧  $V_{DD}$  の上昇に応じて同様の変化特性を示して徐々に上昇する。

割込条件生成回路 10a では、入力される信号の判定に一方の信号にオフセット電位を印加して比較することにより、入力される信号の電位差が小さな場合でもオフセットされた電位によって比較判定された結果が出力されることから出力信号がハイレベルとローレベルを交互に出力してばたつくような不安定な状態となることはない。このため制御信号  $S_{cont}$  は、ローレベルを示す。

#### 【0084】

検出回路 100 では、電源投入後の動作可能電源電圧が供給されるまでの過度状態においては、コンパレータ 30 の出力信号  $S_g$  に不要な検出信号が出力されることがある。つまり、コンパレータ 30 が備える入力信号判定回路が正常に動作するために必要な電源電圧に到達していないために、出力信号  $S_g$  は、信号の状態を特定できない不定状態となる。

一方、割込条件受付回路 20a は、電源電圧が所定の電圧に達するまで入力信号の出力を許可せず所定の電圧を出力信号  $V_{out}$  として出力する。出力信号  $V_{out}$  として出力される所定の電圧は、センサ回路において非検出状態（解除状態）を示す電圧が設定され、制御信号  $S_{cont}$  に応じて制御される。制御信号  $S_{cont}$  には、ローレベルが出力されていることにより、出力信号  $V_{out}$  がローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【0085】

時刻  $t_2$  では、電源電圧  $V_{DD}$  が上昇し、それぞれの回路が動作可能な状態に遷移する。

割込条件生成回路 10a では、入力信号  $V_{temp}$  は電源電圧  $V_{DD}$  の上昇にしたがって上昇するため、その電位差が小さな状態にある。一方の信号にはオフセット電位が印加されていることにより、出力される制御信号  $S_{cont}$  は、ローレベルに確定している。センサ回路及び基準電源 RF の出力である入力信号  $V_{temp}$  及び基準電圧  $V_{ref}$  も電源電圧  $V_{DD}$  の上昇にしたがって徐々に上昇するため、その電位差が小さな状態にある。電位差が小さい 2 つの信号を比較して得られる出力信号  $S_g$  は、信号の状態を特定できない不定状態が継続する。割込条件受付回路 20a では、制御信号  $S_{cont}$  がローレベルに確定していることにより、出力信号  $V_{out}$  がローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【0086】

時刻  $t_3$  では、基準電源 RF から入力される基準電圧  $V_{ref}$  が所定の電圧に到達すると定電圧制御され、一定の電圧が入力されるようになる。電源電圧  $V_{DD}$  及びセンサ回路からの入力信号  $V_{temp}$  の電位は、継続的に上昇する。

基準電圧  $V_{ref}$  が所定の電圧を示すようになり、基準電圧  $V_{ref}$  は入力信号  $V_{temp}$  より低い電位を示すことから、出力信号  $S_g$  は、状態が定まらない不定状態から正しい判定結果が出力される状態に遷移する。また、制御信号  $S_{cont}$  による制御が継続されることにより、出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【0087】

時刻  $t_4$  では、センサ回路からの入力信号  $V_{temp}$  は、所定の検出状態を示す定常動作状態に遷移する。これにより、センサ回路が検出する状態によって入力信号  $V_{temp}$  は変化することになり、これまで継続していた電源電圧  $V_{DD}$  の上昇にともなう上昇は停止する。そして、センサ回路が備える定電流回路が供給する電流とセンサ回路のインピーダンスによって定まる入力信号  $V_{temp}$  の電圧値より、電源電圧  $V_{DD}$  の方が高くなつたことにより、センサ回路からの入力信号  $V_{temp}$  による変化が検出できるようになる。

時刻  $t_5$  では、センサ回路からの入力信号  $V_{temp}$  と電源電圧  $V_{DD}$  とに、所定の電

10

20

30

40

50

位差、すなわち割込条件生成回路 10 a におけるオフセット電位の電圧以上の電位差が生じることを、割込条件生成回路 10 a によって検出される。その検出によって、電源電圧 VDD がセンサ回路に動作可能な電源電圧が供給される状態に遷移したことが示される。割込条件生成回路 10 a では、制御信号 Scont の割込み状態（ローレベル）を解除することにより、制御信号 Scont の電圧が電源電圧 VDD の電位上昇にともなって上昇する。

時刻  $t_6$  では、電源電圧 VDD が所定の動作可能電源電圧に達して上昇が止まり、電源電圧 VDD が一定値を示すようになる。また、制御信号 Scont の電圧上昇も止まり一定値を示す状態に遷移する。

以上に示したように電源が投入されたことにより各信号の状態が遷移する。電源電圧 VDD が所定の動作可能電源電圧に達するまで、出力信号 Vout はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【0088】

##### （第3実施形態）

図を参照し、形態の異なる検出回路の実施形態について示す。

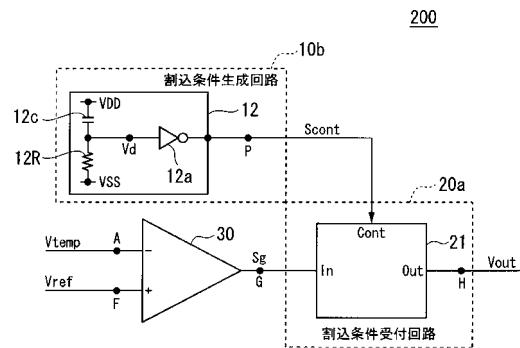

図 9 は、第3実施形態による検出回路を示す概略構成図である。図 9 に示す例では、図 7 に示す第2の実施の形態における割込条件生成回路 10 a（図 1 に示す信号電圧監視回路 4 と同じ構成の回路）に代えて、POC（Power On Clear）回路 12 を使用する例を示したものである。これは、後述する実施の形態の説明において、図 9 に示す POC 回路 12 と、図 7 に示す割込条件生成回路 10 a とを併用して使用する場合があるため、ここで POC 回路 12 を使用する検出回路の例について説明しておくものである。

#### 【0089】

図 9 に示す検出回路 200 は、割込条件生成回路 10 b、割込条件受付回路 20 a 及びコンパレータ 30 を備える。図 7 と同じ構成には同じ符号を付し、異なる構成について説明する。

検出回路 200 における割込条件生成回路 10 b は、電源投入時に所定時間の間、初期状態を保持する信号を出力する。割込条件生成回路 10 b は、POC（Power On Clear）回路 12 からなる。POC 回路 12 は、いわゆる電源投入初期化回路である。

POC 回路 12 は、直列に接続されたコンデンサ 12C と抵抗 12R は、電源（電源電圧 VDD）にコンデンサ 12C の一端が接続され、基準となる電源（接地電圧 VSS）に抵抗 12R の一端が接続される。コンデンサ 12C と抵抗 12R の接続点は、インバータ（NOT回路）12a の入力端に接続され、インバータ 12a が割込条件生成回路 10 b の制御信号 Scont を出力する。

この割込条件生成回路 10 b の出力は、割込条件受付回路 20 a の制御入力端子 cont に接続される。

#### 【0090】

このような構成による検出回路 200 では、割込条件生成回路 10 b から出力される制御信号 Scont は、電源の投入後、所定の時間経過するまでローレベルを示し、所定の時間経過するとハイレベルを示す。

コンパレータ 30 の出力信号 Sg は、入力信号 Vtemp の電圧が基準電圧 Vref より低い場合にはハイレベルを示す。また、コンパレータ 30 の出力信号 Sg は、入力信号 Vtemp の電圧が基準電圧 Vref より高い場合にはローレベルを示す。

割込条件受付回路 20 a の出力信号 Vout は、制御信号 Scont がローレベルの場合には固定的にローレベルが出力され、制御信号 Scont がハイレベルの場合には入力信号 Vtemp に応じて変化するコンパレータ 30 の出力信号 Sg が出力される。

#### 【0091】

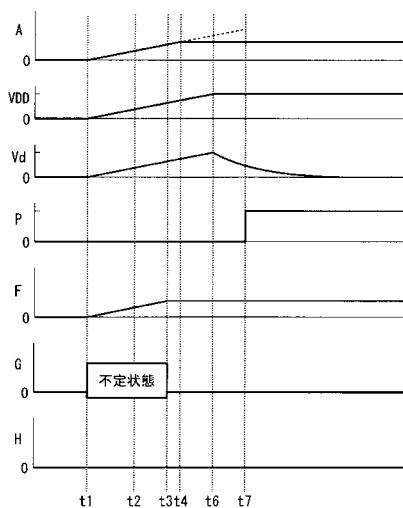

図 10 は、第3実施形態における検出回路の動作を示すタイミングチャートである。

図 9 のブロック図に示された点 A ~ H、点 P 及び点 Vd にしたがって、それらの点における各信号の遷移について説明する。図 8 と同じ信号、時刻には同じ符号を付し、異なる信号、時刻を中心に説明する。図 8 に示した検出回路 100 は、検出回路 200 と読み替

10

20

30

40

50

える。

点の波形  $V_{DD}$  は、 $POC$  回路 12 の電源電圧  $V_{DD}$  の電圧遷移を示す。点  $V_d$  の波形は、 $POC$  回路 12 における  $CR$  回路の接合点  $V_d$  の電圧遷移を示す。点  $P$  の波形は、割込条件生成回路 10b における  $POC$  回路 12 よりて判定され、出力された制御信号  $S_{cont}$  の電圧遷移を示す。この信号に基づいて、割込条件受付回路 20a が制御される。

#### 【0092】

図に示される初期状態では、電源は未投入の状態であり、それぞれの回路において電荷の充電などもなく、各信号とも無信号の状態を示している。

時刻  $t_1$  において、検出回路 200 並びに検出回路 200 に接続されているセンサ回路及び基準電源  $RF$  に対し、電源が投入される。その後、電源電圧  $V_{DD}$  が徐々に上昇する。センサ回路及び基準電源  $RF$  の出力である入力信号  $V_{temp}$  及び基準電圧  $V_{ref}$  は、電源電圧  $V_{DD}$  が低い状態では、電流源の働きによりこれらの出力電圧は電源電圧になる。入力信号  $V_{temp}$  及び基準電圧  $V_{ref}$  は、電源電圧  $V_{DD}$  の上昇に応じて同様の変化特性を示して徐々に上昇する。

割込条件生成回路 10b における  $POC$  回路 12 では、電源電圧  $V_{DD}$  を検出する。

コンデンサ 12C と抵抗 12R からなる時定数回路により、電源電圧  $V_{DD}$  を入力としたステップ応答として同定される一次遅れの過度特性により点  $V_d$  の電位が遷移する。電源投入に追従して点  $V_d$  の電位が上昇するが、インバータ 12a がまだ活性化されないことから制御信号  $S_{cont}$  はローレベルを示す。

#### 【0093】

検出回路 200 では、電源投入後の動作可能電源電圧が供給されるまでの過度状態にあり、コンパレータ 30 の出力信号  $S_g$  は、信号の状態を特定できない不定状態となる。

一方、割込条件受付回路 20a は、電源電圧  $V_{DD}$  が所定の電圧に達するまで入力信号の出力を許可せず所定の電圧を出力信号  $V_{out}$  として出力する。出力信号  $V_{out}$  として出力される所定の電圧は、センサ回路において非検出状態（解除状態）を示す電圧が設定され、制御信号  $S_{cont}$  に応じて制御される。制御信号  $S_{cont}$  には、ローレベルが出力されていることにより、出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【0094】

時刻  $t_2$  では、電源電圧  $V_{DD}$  が上昇し、それぞれの回路が動作可能な状態に遷移する。

割込条件生成回路 10b における  $POC$  回路 12 では、点  $V_d$  の電位がインバータ 12a における閾値電位より高い状態を示す。インバータ 12a の電源電圧が過度的に上昇するにつれインバータ 12a の閾値電位も電源電圧の上昇に応じて上昇する。これにより、制御信号  $S_{cont}$  は、ローレベルに確定している。センサ回路及び基準電源  $RF$  の出力である入力信号  $V_{temp}$  及び基準電圧  $V_{ref}$  も電源電圧  $V_{DD}$  の上昇にしたがって徐々に上昇するため、その電位差が小さな状態にある。電位差が小さい 2 つの信号を比較して得られる出力信号  $S_g$  は、信号の状態を特定できない不定状態が継続する。割込条件受付回路 20a では、制御信号  $S_{cont}$  がローレベルに確定することにより、出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【0095】

時刻  $t_3$  では、基準電源  $RF$  から入力される基準電圧  $V_{ref}$  が所定の電圧に到達すると定電圧制御され、一定の電圧が入力されるようになる。電源電圧  $V_{DD}$  及びセンサ回路からの入力信号  $V_{temp}$  の電位は、継続的に上昇する。

基準電圧  $V_{ref}$  が所定の電圧を示すようになり、基準電圧  $V_{ref}$  は入力信号  $V_{temp}$  より低い電位を示すことから、出力信号  $S_g$  は、状態が定まらない不定状態から正しい判定結果が出力される状態に遷移する。また、制御信号  $S_{cont}$  による制御が継続されることにより、出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

10

20

30

40

50

## 【0096】

時刻  $t_4$  では、センサ回路からの入力信号  $V_{temp}$  は、所定の検出状態を示す定常動作状態に遷移する。これにより、センサ回路が検出する状態によって入力信号  $V_{temp}$  は変化することになり、これまで継続していた電源電圧  $V_{DD}$  の上昇とともに上昇は停止する。そして、センサ回路が備える定電流回路が供給する電流とセンサ回路のインピーダンスとによって定まる入力信号  $V_{temp}$  の電圧値より、電源電圧  $V_{DD}$  の方が高くなつことにより、センサ回路からの入力信号  $V_{temp}$  による変化が検出できるようになる。

時刻  $t_6$  では、電源電圧  $V_{DD}$  が所定の動作可能電源電圧に達して上昇が止まり、電源電圧  $V_{DD}$  が一定値を示すようになる。また、制御信号  $S_{cont}$  の電位の上昇も止まり一定値を示す状態に遷移する。 10

割込条件生成回路 10b における POC 回路 12 では、電源電圧  $V_{DD}$  が定電圧制御に遷移したことから、点  $V_d$  の電位上昇が止まり降下に転じる。

時刻  $t_7$  では、割込条件生成回路 10b における POC 回路 12 では、点  $V_d$  の電位がインバータ 12a の閾値電圧以下に低下したことにより制御信号  $S_{cont}$  がハイレベルに遷移する。割込条件生成回路 10b は、制御信号  $S_{cont}$  に出力していた制御信号の割込み状態（ローレベル）を解除する。これにより、検出回路 200 は、検出信号の出力が行える通常状態に遷移する。

以上に示したように電源が投入されたことにより各信号の状態が遷移する。電源電圧  $V_{DD}$  が所定の動作可能電源電圧に達するまで、出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。 20

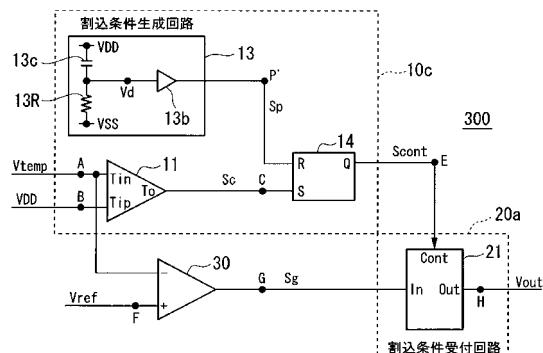

## 【0097】

## (第4実施形態)

図を参照し、形態の異なる検出回路の実施形態について示す。

図 11 は、第4実施形態による検出回路を示す概略構成図である。

検出回路 300 は、割込条件生成回路 10c、割込条件受付回路 20a 及びコンパレータ 30 を備える。図 7 及び図 9 と同じ構成には同じ符号を付し、異なる構成について説明する。

検出回路 300 において割込条件生成回路 10c は、オフセットコンパレータ 11、POC 回路 13 及び RS フリップフロップ 14 を備える。 30

POC 回路 13 は、いわゆる電源投入初期化回路である。

POC 回路 13 は、直列に接続されたコンデンサ 13c と抵抗 13r は、電源の正極（電源電圧  $V_{DD}$ ）にコンデンサ 13c の一端が接続され、電源の負極（接地電圧  $V_{SS}$ ）に抵抗 13r の一端が接続される。コンデンサ 13c と抵抗 13r の接続点は、バッファ 13b の入力端に接続される。バッファ 13b は、入力される電圧（点  $V_d$  の電圧）がバッファ 13b の閾値電圧（反転電圧）以上になると、出力する信号  $S_{p'}$  が電源電圧  $V_{DD}$  によって示されるハイレベルになり、閾値電圧（反転電圧）以下になると、信号  $S_{p'}$  が基準電圧  $V_{SS}$  によって示されるローレベルになる。バッファ 13b から出力される信号は、POC 回路 13 の出力信号となる。  $V_d$  がバッファ 13b の反転電圧以上になると、信号  $S_{p'}$  が電源電圧  $V_{DD}$  になり、反転電圧以下になると、信号  $S_{p'}$  が基準電圧  $V_{SS}$  になる。バッファ 13b の閾値電圧は、電源電圧  $V_{DD}$  の半分の電圧になる。 40

オフセットコンパレータ 11 は、信号  $S_c$  を出力する。信号  $S_c$  は、実施形態における制御信号  $S_{cont}$  に相当する。

RS フリップフロップ 14 は、RS 型フリップフロップを示す。

## 【0098】

オフセットコンパレータ 11 の出力端が RS フリップフロップ 14 のセット入力端（S）に接続され、POC 回路 13 の出力端が RS フリップフロップ 14 のリセット入力端（R）に接続され、RS フリップフロップ 14 の出力端が割込条件生成回路 10c の制御信号  $S_{cont}$  を出力する。RS フリップフロップ 14 は、セット入力端（S）及びリセット入力端（R）にハイレベルが入力された場合は、それぞれ出力信号をハイレベル（セッ 50

ト) 及びローレベル(リセット)に設定し、ともにハイレベルが入力されるとリセット要求を優先させてローレベル(リセット)を設定する。

#### 【0099】

このような構成による検出回路300では、割込条件生成回路10cから出力される制御信号S<sub>cont</sub>は、電源電圧V<sub>DD</sub>が入力信号V<sub>temp</sub>の電圧にバイアス電位V<sub>b</sub>加算した電位より低い場合にはローレベルを示す。また、制御信号S<sub>cont</sub>は、電源電圧V<sub>DD</sub>が入力信号V<sub>temp</sub>の電圧にバイアス電位V<sub>b</sub>加算した電位より高い場合にはハイレベルを示す。

割込条件生成回路10cから出力される制御信号S<sub>cont</sub>は、電源の投入後、所定の時間経過するまでハイレベルを示し、所定の時間経過するとローレベルを示す。

10

#### 【0100】

コンパレータ30の出力信号S<sub>g</sub>は、入力信号V<sub>temp</sub>の電圧が基準電圧V<sub>ref</sub>より低い場合にはハイレベルを示す。また、入力信号V<sub>temp</sub>の電圧が基準電圧V<sub>ref</sub>より高い場合にはローレベルを示す。

割込条件受付回路20aの出力信号V<sub>out</sub>は、制御信号S<sub>cont</sub>がローレベルの場合には固定的にローレベルが出力され、制御信号S<sub>cont</sub>がハイレベルの場合には入力信号V<sub>temp</sub>に応じて変化するコンパレータ30の出力信号S<sub>g</sub>が出力される。

#### 【0101】

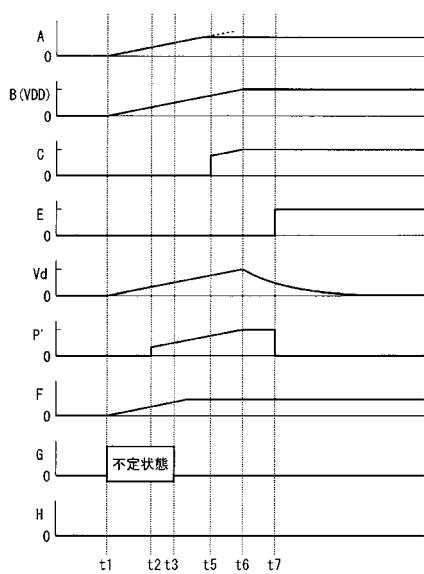

図12は、第4実施形態における検出回路の動作を示すタイミングチャートである。

図11のブロック図に示された点A～H及び点P'にしたがって、それらの点における各信号の遷移について説明する。図8及び図10と同じ信号、時刻には同じ符号を付し、異なる信号、時刻を中心に説明する。図8に示した検出回路100及び図10に示した検出回路200は、検出回路300と読み替える。

20

点Cの波形は、割込条件生成回路10cにおけるオフセットコンパレータ11から出力される信号S<sub>c</sub>の電圧遷移を示す。点Eの波形は、割込条件生成回路10cにおけるRSフリップフロップ14から出力される制御信号S<sub>cont</sub>を示す。点P'の波形は、割込条件生成回路10cにおけるPOC回路13から出力される信号S<sub>p'</sub>の電圧遷移を示す。

#### 【0102】

図に示される初期状態では、電源は未投入の状態であり、それぞれの回路において電荷の充電などもなく、各信号とも無信号の状態を示している。

30

時刻t1において、検出回路300並びに検出回路300に接続されているセンサ回路及び基準電源RFに対し、電源が投入される。その後、電源電圧V<sub>DD</sub>が徐々に上昇する。センサ回路及び基準電源RFの出力である入力信号V<sub>temp</sub>及び基準電圧V<sub>ref</sub>は、電源電圧V<sub>DD</sub>が低い状態では、電流源の働きによりこれらの出力電圧は電源電圧になる。入力信号V<sub>temp</sub>及び基準電圧V<sub>ref</sub>は、電源電圧V<sub>DD</sub>の上昇に応じて同様の変化特性を示して徐々に上昇する。

検出回路300では、電源投入後の動作可能電源電圧が供給されるまでの過度状態にあり、コンパレータ30の出力信号S<sub>g</sub>は、信号の状態を特定できない不定状態となる。

#### 【0103】

割込条件生成回路10cにおけるオフセットコンパレータ11では、入力される信号の判定に一方の信号にオフセット電位を印加して比較することにより、入力される信号の電位差が小さな場合でもオフセットされた電位によって比較判定された結果が出力されることから不安定となることはない。このため信号S<sub>c</sub>は、ローレベルを示す。

POC回路13では、電源電圧V<sub>DD</sub>を検出する。電源投入に追従して点V<sub>d</sub>の電位が上昇するが、バッファ13bがまだ活性化されないことから信号S<sub>p'</sub>はローレベルを示す。RSフリップフロップ14は、セット(S)端子にローレベル、リセット(R)端子にローレベルが入力されるが、まだ活性化されないことから制御信号S<sub>cont</sub>は初期状態が保持されたローレベルが出力される。

#### 【0104】

40

50

一方、割込条件受付回路 20a は、電源電圧が所定の電圧に達するまで入力信号の出力を許可せず所定の電圧を出力信号  $V_{out}$  として出力する。出力信号  $V_{out}$  として出力される所定の電圧は、センサ回路において非検出状態（解除状態）を示す電圧が設定され、制御信号  $S_{cont}$  に応じて制御される。制御信号  $S_{cont}$  には、ローレベルが出力されていることにより、出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【0105】

時刻  $t_2$  では、電源電圧  $V_{DD}$  が上昇し、それぞれの回路が動作可能な状態に遷移する。

割込条件生成回路 10c におけるオフセットコンパレータ 11 では、入力信号  $V_{temp}$  と電源電圧  $V_{DD}$  の電位差が小さな状態にあるが、一方の信号にはオフセット電位が印加されていることにより、信号  $S_c$  は、ローレベルに確定している。POC 回路 13 では、点  $V_d$  における信号の電圧がバッファ 13b における閾値電位より高い状態を示す。バッファ 13b の電源電圧  $V_{DD}$  が過度的に上昇するにつれバッファ 13b の閾値電位も電源電圧  $V_{DD}$  の上昇に応じて上昇する。これにより、信号  $S_p'$  は、ハイレベルを出力する。RS フリップフロップ 14 は、セット (S) 端子にローレベル、リセット (R) 端子にハイレベルが入力され、出力 (Q) 端子には制御信号  $S_{cont}$  としてローレベルが出力される。

センサ回路及び基準電源 RF の出力である入力信号  $V_{temp}$  及び基準電圧  $V_{ref}$  も電源電圧  $V_{DD}$  の上昇にしたがって徐々に上昇するため、その電位差が小さな状態にある。電位差が小さい 2 つの信号を比較して得られる出力信号  $S_g$  は、信号の状態を特定できない不定状態が継続する。

割込条件受付回路 20a では、制御信号  $S_{cont}$  がローレベルに確定することにより、出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【0106】

時刻  $t_3$  では、によって示される基準電源 RF からの入力が所定の電圧に到達すると定電圧制御され、一定の電圧が入力されるようになる。電源電圧  $V_{DD}$  及びセンサ回路からの入力信号  $V_{temp}$  の電位は、継続的に上昇する。

基準電圧  $V_{ref}$  が所定の電圧を示すようになり、基準電圧  $V_{ref}$  は入力信号  $V_{temp}$  より低い電位を示すことから、出力信号  $S_g$  は、状態が定まらない不定状態から正しい判定結果が出力される状態に遷移する。また、制御信号  $S_{cont}$  による制御が継続されることにより、出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【0107】

時刻  $t_4$  では、センサ回路からの入力信号  $V_{temp}$  は、所定の検出状態を示す定常動作状態に遷移する。これにより、センサ回路が検出する状態によって入力信号  $V_{temp}$  は変化することになり、これまで継続していた電源電圧  $V_{DD}$  の上昇にともなう上昇は停止する。そして、センサ回路が備える定電流回路が供給する電流とセンサ回路のインピーダンスによって定まる入力信号  $V_{temp}$  の電圧値より、電源電圧  $V_{DD}$  の方が高くなつたことにより、センサ回路からの入力信号  $V_{temp}$  による変化が検出できるようになる。

#### 【0108】

時刻  $t_5$  では、センサ回路からの入力信号  $V_{temp}$  と電源電圧  $V_{DD}$  とに、所定の電位差、すなわち割込条件生成回路 10c におけるオフセット電位の電圧以上の電位差が生じることを、割込条件生成回路 10c におけるオフセットコンパレータ 11 が検出する。その検出によって、電源電圧  $V_{DD}$  がセンサ回路に動作可能な電源電圧が供給される状態に遷移したことが示される。

オフセットコンパレータ 11 は、信号  $S_c$  にハイレベルを出力し、その電位は電源電圧  $V_{DD}$  の電位上昇にともなって上昇する。

10

20

30

40

50

R S フリップフロップ 1 4 は、セット ( S ) 端子にハイレベル、リセット ( R ) 端子にハイレベルが入力され、出力 ( Q ) 端子にローレベルを出力する。

また、制御信号 S c o n t による制御が継続されることにより、出力信号 V o u t はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【 0 1 0 9 】

時刻 t 6 では、電源電圧 V D D が所定の動作可能電源電圧に達して上昇が止まり、電源電圧 V D D が一定値を示すようになる。また、信号 S c のほか、他の信号の上昇も止まり一定値を示す状態に遷移する。割込条件生成回路 1 0 b における P O C 回路 1 3 による点 V d では、点 V d における信号の電位が低下する。点 V d における信号は、電源電圧 V D D の半分の電圧を閾値電圧としてバッファ 1 3 b によって判定され、信号 S p ' にハイレベルが出力される。

10

割込条件生成回路 1 0 c における R S フリップフロップ 1 4 は、入力信号には状態の変更がなくセット ( S ) 端子にハイレベル、リセット ( R ) 端子にハイレベルが入力され、出力 ( Q ) 端子にローレベルの出力を継続する。割込条件生成回路 1 0 c は、制御信号 S c o n t の割込み状態 ( ローレベル ) を継続させる。また、制御信号 S c o n t による制御が継続されることにより、出力信号 V o u t はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【 0 1 1 0 】

時刻 t 7 では、割込条件生成回路 1 0 b における P O C 回路 1 3 による点 V d では、点 V d における信号の電位がバッファ 1 3 b の閾値電圧 ( 電源電圧 V D D の半分の電圧 ) 以下に低下したことにより信号 S p ' がローレベルに遷移する。

20

R S フリップフロップ 1 4 は、セット ( S ) 端子にハイレベル、リセット ( R ) 端子にローレベルが入力され、出力 ( Q ) 端子にはハイレベルが出力され、制御信号 S c o n t として出力される。

#### 【 0 1 1 1 】

割込条件生成回路 1 0 c は、制御信号 S c o n t を割込み解除状態 ( ハイレベル ) に設定する。これにより、検出回路 3 0 0 は、検出信号の出力が行える通常状態に遷移し、割込条件受付回路 2 0 a の入力である出力信号 S g が出力されるように切り換えられる。出力信号 S g は、ローレベルであることから、出力信号 V o u t はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

30

#### 【 0 1 1 2 】

以上に示したように電源が投入されたことにより各信号の状態が遷移する。電源電圧 V D D が所定の動作可能電源電圧に達するまで、出力信号 V o u t はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【 0 1 1 3 】

##### ( 第 5 実施形態 )

図を参照し、形態の異なる検出回路の実施形態について示す。

図 1 3 は、第 5 実施形態による検出回路を示す概略構成図である。

検出回路 4 0 0 は、割込条件生成回路 1 0 d 、割込条件受付回路 2 0 a 及びコンパレータ 3 0 を備える。図 7 及び図 1 1 と同じ構成には同じ符号を付し、異なる構成について説明する。

40

#### 【 0 1 1 4 】

検出回路 4 0 0 において割込条件生成回路 1 0 d は、オフセットコンパレータ 1 1 、 R S フリップフロップ 1 4 及び低電源電圧検出回路 1 5 を備える。

低電源電圧検出回路 1 5 は、電源電圧の低下検出を行う。

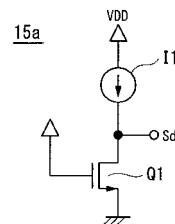

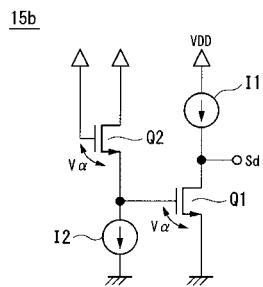

図 1 4 は、低電源電圧検出回路 1 5 の一例を示す概略構成図である。

図 1 4 に示した低電源電圧検出回路 1 5 は、トランジスタ Q 1 と定電流源 I 1 を備える。

トランジスタ Q 1 は、N チャネル電界効果型トランジスタ ( N M O S F E T ) を示す。

トランジスタ Q 1 は、ゲートが電源の正極 ( 電源電圧 V D D ) に接続され、ソースが電源

50

の負極（接地電圧  $V_{SS}$ ）に接続され、ドレインが片端が電源の正極に接続された定電流源  $I_1$  に接続される。すなわち、トランジスタ  $Q_1$  は、定電流源  $I_1$  を負荷としたソース接地型增幅回路を構成する。

#### 【0115】

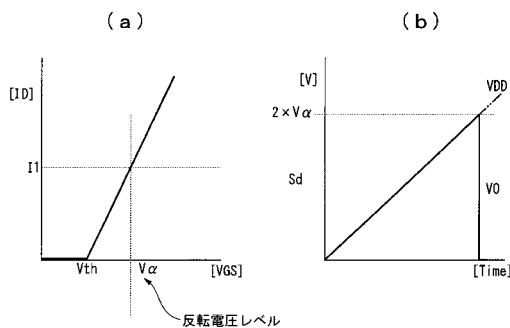

図15は、図14に示した低電源電圧検出回路15の動作を示す図である。

図15(a)は、横軸にトランジスタ  $Q_1$  におけるゲート・ソース間電圧 ( $V_{GS}$ ) を示し、縦軸にドレイン電流 ( $I_D$ ) を示し、トランジスタ  $Q_1$  の增幅特性を示すグラフである。グラフの横軸における切片になる  $V_{th}$  は、トランジスタ  $Q_1$  のゲート・ソース間電圧  $V_{GS}$  が所定の電圧  $V$  以下の状態では、トランジスタ  $Q_1$  は飽和状態にならずに、定電流源  $I_1$  に設定された定電流  $i_1$  を流すことができない。また、ゲート・ソース間電圧  $V_{GS}$  が所定の電圧  $V$  を越えた状態では、トランジスタ  $Q_1$  は飽和状態になる。

10

#### 【0116】

図15(b)は、この回路構成によって示される特性により、徐々に上昇する電源電圧  $V_{DD}$  を印加したときの信号  $S_d$  の変化を示すタイミングチャートである。

電源電圧  $V_{DD}$  が、電圧  $V$  に到達するまで信号  $S_d$  の電圧は、電圧  $V_{DD}$  の変化にしたがって遷移する。電源電圧  $V_{DD}$  が、電圧  $V$  に到達すると信号  $S_d$  は、ローレベルを示す状態に遷移する。

#### 【0117】

図13に戻り、割込条件生成回路10dの接続を示す。

20

オフセットコンパレータ11の出力端がRSフリップフロップ14のセット入力端 (S) に接続され、低電源電圧検出回路15の出力端がRSフリップフロップ14のリセット入力端 (R) に接続され、RSフリップフロップ14の出力端が割込条件生成回路10dの出力信号を出力する。

#### 【0118】

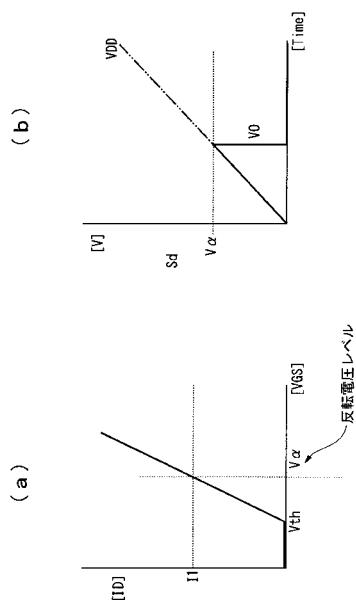

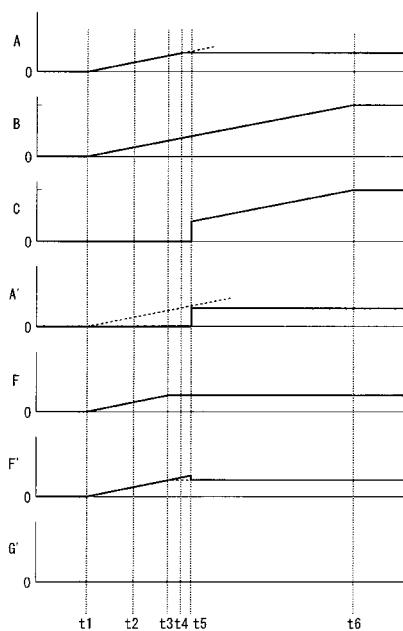

図16は、第5実施形態における検出回路の動作を示すタイミングチャートである。

図13のブロック図に示された点A～Hにしたがって、それらの点における各信号の遷移について説明する。図8、図10及び図14と同じ信号、時刻には同じ符号を付し、異なる信号、時刻を中心に説明する。図8に示した検出回路100、図10に示した検出回路200及び図14に示した検出回路300は、検出回路400と読み替える。

30

点の波形Dは、低電源電圧検出回路15から出力される信号  $S_d$  を示す。

#### 【0119】

図に示される初期状態では、電源は未投入の状態であり、それぞれの回路において電荷の充電などもなく、各信号とも無信号の状態を示している。

時刻  $t_1$  において、検出回路400並びに検出回路400に接続されているセンサ回路及び基準電源RFに対し、電源が投入される。その後、電源電圧  $V_{DD}$  が徐々に上昇する。センサ回路及び基準電源RFの出力である入力信号  $V_{temp}$  及び基準電圧  $V_{ref}$  は、電源電圧  $V_{DD}$  が低い状態では、電流源の働きによりこれらの出力電圧は電源電圧になる。入力信号  $V_{temp}$  及び基準電圧  $V_{ref}$  は、電源電圧  $V_{DD}$  の上昇に応じて同様の変化特性を示して徐々に上昇する。

40

検出回路400では、電源投入後の動作可能電源電圧が供給されるまでの過度状態にあり、コンパレータ30の出力信号  $S_g$  は、信号の状態を特定できない不定状態となる。

#### 【0120】

割込条件生成回路10dにおけるオフセットコンパレータ11では、入力される信号の判定に一方の信号にオフセット電位を印加して比較することにより、入力される信号の電位差が小さな場合でもオフセットされた電位によって比較判定された結果が出力されることから不安定となることはない。このため信号  $S_c$  は、ローレベルを示す。

低電源電圧検出回路15では、電源電圧が回路を構成する半導体素子（例えば、トランジスタ  $Q_1$  及び  $Q_2$ ）における閾値電位よりも低い状態にあり、信号  $S_d$  は電源電圧の上昇と共に上昇する。RSフリップフロップ14は、セット (S) 端子にローレベル、リセ

50

ット (R) 端子にローレベルが入力されるが、まだ活性化されないことから制御信号 S<sub>cont</sub> は初期状態が保持されたローレベルが出力される。

【0121】

一方、割込条件受付回路 20a は、電源電圧が所定の電圧に達するまで入力信号の出力を許可せず所定の電圧を出力信号 V<sub>out</sub> として出力する。出力信号 V<sub>out</sub> として出力される所定の電圧は、センサ回路において非検出状態（解除状態）を示す電圧が設定され、制御信号 S<sub>cont</sub> に応じて制御される。制御信号 S<sub>cont</sub> には、制御信号 S<sub>cont</sub> としてローレベルが出力されていることにより、出力信号 V<sub>out</sub> はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

【0122】

時刻 t<sub>2</sub> では、電源電圧 V<sub>DD</sub> が上昇し、それぞれの回路が動作可能な状態に遷移する。

割込条件生成回路 10d におけるオフセットコンパレータ 11 では、入力信号 V<sub>temp</sub> と電源電圧 V<sub>DD</sub> の電位差が小さな状態にあるが、一方の信号にはオフセット電位が印加されていることにより、信号 S<sub>c</sub> は、ローレベルに確定している。低電源電圧検出回路 15 では、電源電圧が回路を構成する半導体素子（例えば、トランジスタ Q<sub>1</sub> 及び Q<sub>2</sub>）における閾値電位よりも高い状態になり、信号 S<sub>d</sub> は電源電圧が所定の閾値電圧を超えたことから、ローレベルを出力する。RS フリップフロップ 14 は、セット (S) 端子にローレベル、リセット (R) 端子にローレベルが入力され、制御信号 S<sub>cont</sub> には、回路が活性化され入力信号の状態にしたがってローレベルが出力される。

センサ回路及び基準電源 RF の出力である入力信号 V<sub>temp</sub> 及び基準電圧 V<sub>ref</sub> も電源電圧 V<sub>DD</sub> の上昇にしたがって徐々に上昇するため、その電位差が小さな状態にある。電位差が小さい 2 つの信号を比較して得られる出力信号 S<sub>g</sub> は、信号の状態を特定できない不定状態が継続する。

割込条件受付回路 20a では、制御信号 S<sub>cont</sub> がローレベルに確定することにより、出力信号 V<sub>out</sub> はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

【0123】

時刻 t<sub>3</sub> では、によって示される基準電源 RF からの入力が所定の電圧に到達すると定電圧制御され、一定の電圧が入力されるようになる。電源電圧 V<sub>DD</sub> 及びセンサ回路からの入力信号 V<sub>temp</sub> の電位は、継続的に上昇する。

【0124】

基準電圧 V<sub>ref</sub> が所定の電圧を示すようになり、基準電圧 V<sub>ref</sub> は入力信号 V<sub>temp</sub> より低い電位を示すことから、出力信号 S<sub>g</sub> の出力は、状態が定まらない不定状態から正しい判定結果が出力される状態に遷移する。また、制御信号 S<sub>cont</sub> による制御が継続されることにより、出力信号 V<sub>out</sub> はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

【0125】

時刻 t<sub>4</sub> では、センサ回路からの入力信号 V<sub>temp</sub> は、所定の検出状態を示す定常動作状態に遷移する。これにより、センサ回路が検出する状態によって入力信号 V<sub>temp</sub> は変化することになり、これまで継続していた電源電圧 V<sub>DD</sub> の上昇にともなう上昇は停止する。そして、センサ回路が備える定電流回路が供給する電流とセンサ回路のインピーダンスによって定まる入力信号 V<sub>temp</sub> の電圧値より、電源電圧 V<sub>DD</sub> の方が高くなつたことにより、センサ回路からの入力信号 V<sub>temp</sub> による変化が検出できるようになる。

【0126】

時刻 t<sub>5</sub> では、センサ回路からの入力信号 V<sub>temp</sub> と電源電圧 V<sub>DD</sub> とに、所定の電位差、すなわち割込条件生成回路 10d におけるオフセット電位の電圧以上の電位差が生じることを、割込条件生成回路 10d におけるオフセットコンパレータ 11 が検出する。その検出によって、電源電圧 V<sub>DD</sub> がセンサ回路に動作可能な電源電圧が供給される状態

10

20

30

40

50

に遷移したことが示される。

オフセットコンパレータ11は、信号S<sub>c</sub>にハイレベルを出力し、電源電圧V<sub>DD</sub>の電位上昇にともなって上昇する。

R S フリップフロップ14は、セット(S)端子にハイレベル、リセット(R)端子にローレベルが入力され、出力を反転させハイレベルを出力する。

割込条件生成回路10dは、制御信号S<sub>cont</sub>の割込み状態(ローレベル)を解除する。これにより、検出回路400は、検出信号の出力が行える通常状態に遷移する。

#### 【0127】

時刻t6では、電源電圧V<sub>DD</sub>が所定の動作可能電源電圧に達して上昇が止まり、電源電圧V<sub>DD</sub>が一定値を示すようになる。また、信号S<sub>c</sub>並びに他信号も電源電圧の上昇にともなう電圧の上昇も止まり一定値を示す状態に遷移する。

#### 【0128】

以上に示したように電源が投入されたことにより各信号の状態が遷移する。電源電圧V<sub>DD</sub>が所定の動作可能電源電圧に達するまで、出力信号V<sub>out</sub>はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【0129】

##### (第6実施形態)

図を参照し、形態の異なる低電源電圧検出回路の実施形態について示す。

図17は、第6実施形態による低電源電圧検出回路を示す概略構成図である。

図17に示した低電源電圧検出回路15bは、トランジスタQ1、Q2と定電流源I1、I2を備える。

トランジスタQ1とQ2は、Nチャネル電界効果型トランジスタ(NMOSFET)を示す。トランジスタQ2は、ゲートとドレインが電源の正極(電源電圧V<sub>DD</sub>)に接続され、ソースが片端が電源の負極(設置電圧V<sub>SS</sub>)に接続された定電流源I2に接続される。

トランジスタQ1は、ゲートがトランジスタQ2のソースに接続され、ソースが接地電圧V<sub>SS</sub>に接続され、ドレインが片端が電源の正極に接続された定電流源I1に接続される。すなわち、トランジスタQ1とQ2は、多段接続された増幅回路を形成し、定電流源I1を負荷としたソース接地型増幅回路を出力段とした構成になる。

#### 【0130】

図18は、第6実施形態による低電源電圧検出回路の動作を示す図である。

図18(a)は、横軸にトランジスタQ1(Q2)におけるゲート・ソース間電圧(V<sub>GS</sub>)を示し、縦軸にドレイン電流(I<sub>D</sub>)を示し、トランジスタQ1(Q2)の増幅特性を示すグラフである。グラフ横軸の切片になるV<sub>th</sub>は、トランジスタQ1(Q2)のゲート・ソース間電圧V<sub>GS</sub>の閾値電圧を示す。このグラフに示されるように、トランジスタQ1(Q2)のゲート・ソース間電圧V<sub>GS</sub>が所定の電圧V<sub>th</sub>以下の状態では、設定された定電流I1を流すことができないトランジスタQ1(Q2)はオフ(遮断)状態になる。また、ゲート・ソース間電圧V<sub>GS</sub>が所定の電圧V<sub>th</sub>を越えた状態では、トランジスタQ1(Q2)はオン(導通)状態になる。なお、トランジスタQ1とQ2は、特性が異なるものを選定しても良い。

#### 【0131】

図18(b)は、この回路構成によって示される特性により、徐々に上昇する電源電圧V<sub>DD</sub>を印加したときの信号S<sub>d</sub>の変化を示すタイミングチャートである。

電源電圧V<sub>DD</sub>が、電圧(2×V<sub>th</sub>)に到達するまで信号S<sub>d</sub>の電圧は、電源電圧V<sub>DD</sub>の変化にしたがって遷移する。電源電圧V<sub>DD</sub>が、電圧(2×V<sub>th</sub>)に到達すると信号S<sub>d</sub>は、ローレベルを示す状態に遷移する。

トランジスタQ1とQ2を多段に接続された構成にしたことで、低電源検出電圧の閾値電圧をトランジスタ1段の場合の倍の電圧にすることができる。

#### 【0132】

##### (第7実施形態)

10

20

30

40

50

図を参照し、形態の異なる検出回路の実施形態について示す。

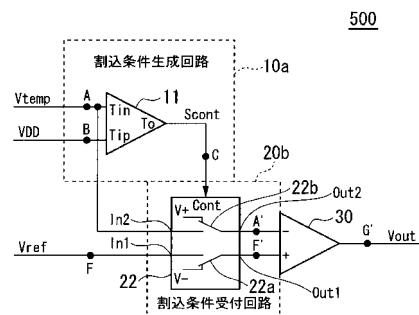

図19は、第7実施形態による検出回路を示す概略構成図である。

検出回路500は、割込条件生成回路10a、割込条件受付回路20b及びコンパレータ30を備える。図7と同じ構成には同じ符号を付し、異なる構成について説明する。

検出回路500における割込条件受付回路20bは、選択回路22を備える。

選択回路22は、入力される制御信号に連動するスイッチ22a及び22bを備える。

スイッチ22a及びスイッチ22bは、入力端(  $I_{n1}$  、  $I_{n2}$  )に対応して設けられる出力端(  $Out_1$  、  $Out_2$  )との間にそれぞれ接続され、制御信号入力端子  $Cont$  に制御信号  $Scout$  として入力される割込み信号に応じて、所定の電圧を出力するか入力端に入力された入力信号を出力するかを選択し切り換える。スイッチ22a及びスイッチ22bから出力される所定の電圧は、スイッチ22bから出力される電圧(  $V_+$  )よりスイッチ22aから出力される電圧(  $V_-$  )のほうが低く設定される。すなわち、割込条件受付回路20bは、制御信号として入力される割込信号による割込みが解除されるまで入力信号の出力を許可せず、スイッチ22a及びスイッチ22bを介して出力する所定の電圧を出力信号として出力する。また、割込条件受付回路20aは、割込信号による割込みが解除されると入力信号の出力を許可して出力信号として出力する。

次に、検出回路500の接続を示す。

検出回路500には、検出回路500を作動させる電源と、図示されないセンサ回路からの入力信号  $V_{temp}$  と、図示されない基準電源  $RF$  から出力される基準電圧  $V_{ref}$  20 とが入力される。

割込条件生成回路10aにおける入力端子  $Tip$  には、電源の正極に接続され電圧  $VD$   $D$  が印加される。また、入力端子  $Tin$  には、図示されないセンサ回路の出力端が接続される。

割込条件受付回路20bにおける入力端子  $In1$  には基準電圧  $V_{ref}$  を出力する図示されない基準電源  $RF$  が接続され、入力端子  $In2$  には図示されないセンサ回路の出力端が接続され、制御入力端子  $Cont$  には割込条件生成回路10aの出力端が接続される。

コンパレータ30における非反転入力端子には、割込条件受付回路20bにおける出力端子  $Out_1$  が接続され、反転入力端子には、割込条件受付回路20bにおける出力端子  $Out_2$  が接続される。

### 【0133】

30

図20は、第7実施形態における検出回路の動作を示すタイミングチャートである。

図19のブロック図に示された点A～G'にしたがって、それらの点における各信号の遷移について説明する。図8と同じ信号、時刻には同じ符号を付し、異なる信号、時刻を中心説明する。図8に示した検出回路100は、検出回路500と読み替える。

点の波形  $A'$  は、割込条件受付回路20bにおける点  $A'$  に出力する信号  $Sa'$  の電圧遷移を示す。信号  $Sa'$  には、センサ回路から入力された入力信号  $V_{temp}$  と同じ信号、又は、予め定められた所定の電圧のいずれかが出力される。

点の波形  $F'$  は、割込条件受付回路20bにおける点  $F'$  に出力する信号  $Sf'$  の電圧遷移を示す。信号  $Sf'$  には、検出回路500に供給される基準電源  $RF$  から出力される基準電圧  $V_{ref}$  、又は、予め定められた所定の電圧のいずれかが出力される。

点の波形  $G'$  は、コンパレータ30によって判定され、検出回路500の出力信号  $V_{out}$  になる。このタイミングチャートに示される範囲では、センサ回路によって検出すべき事象は生じていない状態を示し、出力信号  $V_{out}$  は、常時ローレベルを示す。

### 【0134】

40

図に示される初期状態では、電源は未投入の状態であり、それぞれの回路において電荷の充電などもなく、各信号とも無信号の状態を示している。

時刻  $t_1$ において、検出回路500並びに検出回路500に接続されているセンサ回路及び基準電源  $RF$  に対し、電源が投入される。その後、電源電圧  $VD$   $D$  が徐々に上昇する。センサ回路及び基準電源  $RF$  の出力である入力信号  $V_{temp}$  及び基準電圧  $V_{ref}$  は、電源電圧  $VD$   $D$  が低い状態では、電流源の働きによりこれらの出力電圧は電源電圧  $VD$  50

D になる。入力信号  $V_{temp}$  及び基準電圧  $V_{ref}$  は、電源電圧  $V_{DD}$  の上昇に応じて同様の変化特性を示して徐々に上昇する。

割込条件生成回路 10a では、入力される信号の判定に一方の信号にオフセット電位を印加して比較する。これにより、割込条件生成回路 10a では、入力される信号の電位差が小さな場合でもオフセットされた電位によって比較判定された結果が出力されることから不安定となることはない。このため制御信号  $S_{cont}$  は、ローレベルを示す。

#### 【0135】

一方、割込条件受付回路 20b の信号が入力されるコンパレータ 30 では、電源電圧  $V_{DD}$  が所定の電圧に達するまで出力信号  $V_{out}$  を非検出状態（解除状態）を示すように確定させる処理が施される。解除状態を示すように確定させる処理は、制御信号  $S_{cont}$  によって制御される。制御信号  $S_{cont}$  がローレベルであることにより、割込条件受付回路 20b は、出力端（ $Out_1$ 、 $Out_2$ ）から信号  $S_f'$  と信号  $S_a'$  によって示される所定の電圧を出力する。割込条件受付回路 20b は、信号  $S_f'$  には接地電位  $V_S$  近傍の電圧（ $V_-$ ）を、信号  $S_a'$  には電源電圧  $V_{DD}$  に応じて上昇する電圧（ $V_+$ ）を出力する。

これにより、コンパレータ 30 の出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

時刻  $t_2$  では、電源電圧  $V_{DD}$  が上昇し、それぞれの回路が動作可能な状態に遷移する。

割込条件生成回路 10a では、入力信号  $V_{temp}$  と電源電圧  $V_{DD}$  の電位差が小さな状態にあるが、一方の信号にはオフセット電位が印加されていることにより、制御信号  $S_{cont}$  は、ローレベルに確定している。センサ回路及び基準電源 RF の出力である入力信号  $V_{temp}$  及び基準電圧  $V_{ref}$  も電源電圧  $V_{DD}$  が上昇するのにしたがって徐々に上昇する。

制御信号  $S_{cont}$  がローレベルであることにより、割込条件受付回路 20b 並びにコンパレータ 30 では、時刻  $t_1$  からの状態が継続する。これにより、コンパレータ 30 の出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【0136】

時刻  $t_3$  では、基準電圧  $V_{ref}$  によって示される基準電源 RF からの入力が所定の電圧に到達すると定電圧制御され、一定の電圧が入力されるようになる。電源電圧  $V_{DD}$  及びセンサ回路からの入力信号  $V_{temp}$  の電位は、継続的に上昇する。

基準電圧  $V_{ref}$  が所定の電圧を示すようになり、基準電圧  $V_{ref}$  は入力信号  $V_{temp}$  より低い電位を示すようになる。

前述の時刻  $t_2$  からの状態と同様に割込条件生成回路 10a では、入力信号  $V_{temp}$  と電源電圧  $V_{DD}$  の電位差が小さな状態にあるが、一方の信号にはオフセット電位が印加されていることにより、制御信号  $S_{cont}$  は、ローレベルに確定している。センサ回路の出力、すなわち入力信号  $V_{temp}$  は電源電圧  $V_{DD}$  が上昇するのにしたがって徐々に上昇する。

制御信号  $S_{cont}$  がローレベルであることにより、割込条件受付回路 20b 並びにコンパレータ 30 では、時刻  $t_1$  からの状態が継続する。これにより、コンパレータ 30 の出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【0137】

時刻  $t_4$  では、センサ回路からの入力信号  $V_{temp}$  は、所定の検出状態を示す定常動作状態に遷移する。これにより、センサ回路が検出する状態によって入力信号  $V_{temp}$  は変化することになり、これまで継続していた電源電圧  $V_{DD}$  の上昇にともなう上昇は停止する。そして、センサ回路が備える定電流回路が供給する電流とセンサ回路のインピーダンスによって定まる入力信号  $V_{temp}$  の電圧値より、電源電圧  $V_{DD}$  の方が高くなつたことにより、センサ回路からの入力信号  $V_{temp}$  による変化が検出できるようになる

10

20

30

40

50

。

## 【0138】

時刻  $t_5$  では、センサ回路からの入力信号  $V_{temp}$  と電源電圧  $V_{DD}$  とに、所定の電位差、すなわち割込条件生成回路 10b におけるオフセット電位の電圧（バイアス電圧  $V_b$ ）以上の電位差が生じることを、割込条件生成回路 10b によって検出される。その検出によって、電源電圧  $V_{DD}$  がセンサ回路に動作可能な電源電圧が供給される状態に遷移したことが示される。割込条件生成回路 10b では、制御信号  $S_{cont}$  が割込み解除状態（ハイレベル）に設定され、制御信号  $S_{cont}$  の電圧は電源電圧  $V_{DD}$  の電位上昇とともにあって上昇する。

制御信号  $S_{cont}$  が割込み解除状態（ハイレベル）に設定されたことにより、割込条件受付回路 20b は、入力端に入力された入力信号を出力するように切り換える。割込条件受付回路 20b は、信号  $S_a'$  には入力された入力信号  $V_{temp}$  を出力し、信号  $S_f'$  には入力された基準電圧  $V_{ref}$  を出力する。

## 【0139】

時刻  $t_6$  では、電源電圧  $V_{DD}$  が所定の動作可能電源電圧に達して上昇が止まり、一定値を示すようになる。また、制御信号  $S_{cont}$  の電圧上昇も止まり一定値を示す状態に遷移する。

## 【0140】

以上に示したように電源が投入されたことにより各信号の状態が遷移する。電源電圧  $V_{DD}$  が所定の動作可能電源電圧に達するまで、出力信号  $V_{out}$  に不要な検出信号が出力されることなく、出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

## 【0141】

## (第8実施形態)

図を参照し、形態の異なる検出回路の実施形態について示す。

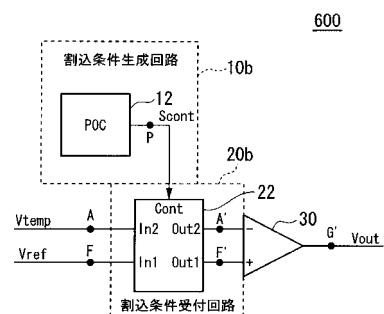

図 21 は、第8実施形態による検出回路を示す概略構成図である。

検出回路 600 は、割込条件生成回路 10b、割込条件受付回路 20b 及びコンパレータ 30 を備える。図 7、図 9 及び図 19 と同じ構成には同じ符号を付している。

## 【0142】

次に、検出回路 600 の接続を示す。

検出回路 600 には、検出回路 600 を作動させる電源と、図示されないセンサ回路からの入力信号  $V_{temp}$  と、図示されない基準電源  $R_F$  から出力される基準電圧  $V_{ref}$  とが入力される。

割込条件受付回路 20b における入力端子  $I_{n1}$  には、基準電圧  $V_{ref}$  を出力する図示されない電源の正極（電源電圧  $V_{DD}$ ）が接続され、入力端子  $I_{n2}$  には、図示されないセンサ回路の出力端が接続され、制御入力端子  $C_{ont}$  には、割込条件生成回路 10b の出力端が接続される。

コンパレータ 30 における非反転入力端子には、割込条件受付回路 20b における出力端子  $OUT_1$  が接続され、反転入力端子には、割込条件受付回路 20b における出力端子  $OUT_1$  が接続される。

## 【0143】

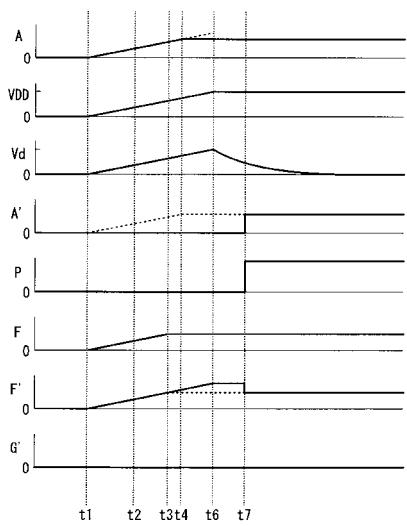

図 22 は、第8実施形態における検出回路の動作を示すタイミングチャートである。

図 21 のブロック図に示された点 A ~ G' 及び点 P にしたがって、それらの点における各信号の遷移について説明する。図 8、図 10 及び図 20 と同じ信号、時刻には同じ符号を付し、異なる信号、時刻を中心に説明する。図 7 に示した検出回路 100、図 9 に示した検出回路 200 及び図 19 に示した検出回路 500 は、検出回路 600 と読み替える。

## 【0144】

図に示される初期状態では、電源は未投入の状態であり、それぞれの回路において電荷の充電などもなく、各信号とも無信号の状態を示している。

時刻  $t_1$  において、検出回路 600 並びに検出回路 600 に接続されているセンサ回路

10

20

30

40

50

及び基準電源 R F に対し、電源が投入される。その後、電源電圧 V D D が徐々に上昇する。センサ回路及び基準電源 R F の出力である入力信号 V t e m p 及び基準電圧 V r e f は、電源電圧 V D D が低い状態では、電流源の働きによりこれらの出力電圧は電源電圧 V D D になる。入力信号 V t e m p 及び基準電圧 V r e f は、電源電圧 V D D の上昇に応じて同様の変化特性を示して徐々に上昇する。

割込条件生成回路 10 b における P O C 回路 12 では、電源電圧 V D D を検出する。

コンデンサ 12 C と抵抗 12 R からなる時定数回路により、電源電圧 V D D を入力としたステップ応答として同定される一次遅れの過度特性により点 V d の電位が遷移する。電源投入に追従して電源電圧 V D D が上昇するが、インバータ 12 a がまだ活性化されないことから制御信号 S c o n t はローレベルを示す。

10

#### 【 0 1 4 5 】

一方、割込条件受付回路 20 b の信号が入力されるコンパレータ 30 では、電源電圧 V D D が所定の電圧に達するまで出力信号 V o u t を非検出状態（解除状態）を示すように確定させる処理が施される。解除状態を示すように確定させる処理は、制御信号 S c o n t によって制御される。制御信号 S c o n t がローレベルであることにより、割込条件受付回路 20 b は、出力端（Out 1、Out 2）から信号 S f ' と信号 S a ' によって示される所定の電圧を出力する。信号 S f ' には接地電位 V S S 近傍の電圧（V -）を、信号 S a ' には電源電圧 V D D に応じて上昇する電圧（V +）を出力する。

これにより、コンパレータ 30 の出力信号 V o u t には、ローレベルが出力され、不要な検出状態を示す信号が出力されずに解除状態を示す信号を出力する。

20

#### 【 0 1 4 6 】

時刻 t 2 では、電源電圧 V D D が上昇し、それぞれの回路が動作可能な状態に遷移する。

割込条件生成回路 10 b における P O C 回路 12 では、点 V d の電圧がインバータ 12 a における閾値電位より高い状態を示す。インバータ 12 a の電源電圧 V D D が過度的に上昇するにつれインバータ 12 a の閾値電位も電源電圧 V D D の上昇に応じて上昇する。これにより、制御信号 S c o n t は、ローレベルに確定している。センサ回路及び基準電源 R F の出力である入力信号 V t e m p 及び基準電圧 V r e f も電源電圧 V D D が上昇するのにしたがって徐々に上昇する。

制御信号 S c o n t がローレベルであることにより、割込条件受付回路 20 b 並びにコンパレータ 30 では、時刻 t 1 からの状態が継続する。これにより、コンパレータ 30 の出力信号 V o u t はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

30

#### 【 0 1 4 7 】

時刻 t 3 では、基準電源 R F から入力される基準電圧 V r e f が所定の電圧に到達すると定電圧制御され、一定の電圧が入力されるようになる。電源電圧 V D D 及びセンサ回路からの入力信号 V t e m p の電位は、継続的に上昇する。

基準電圧 V r e f が所定の電圧を示すようになり、基準電圧 V r e f は入力信号 V t e m p より低い電位を示すようになる。

前述の時刻 t 2 からの状態と同様に割込条件生成回路 10 b における状態の変化はなく、制御信号 S c o n t にはローレベルが出力されている。センサ回路の出力、すなわち入力信号 V t e m p は電源電圧 V D D が上昇するのにしたがって徐々に上昇する。

40

制御信号 S c o n t がローレベルであることにより、割込条件受付回路 20 b 並びにコンパレータ 30 では、時刻 t 1 からの状態が継続する。これにより、コンパレータ 30 の出力信号 V o u t はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

#### 【 0 1 4 8 】

時刻 t 4 では、センサ回路からの入力信号 V t e m p は、所定の検出状態を示す定常動作状態に遷移する。これにより、センサ回路が検出する状態によって入力信号 V t e m p は変化することになり、これまで継続していた電源電圧 V D D の上昇にともなう上昇は停

50

止する。

【0149】

時刻  $t_6$  では、電源電圧  $V_{DD}$  が所定の動作可能電源電圧に達して上昇が止まり、一定値を示すようになる。また、制御信号  $S_{cont}$  の上昇も止まり一定値を示す状態に遷移する。割込条件生成回路 10b における POC 回路 12 では、点  $V_d$  の電位上昇が止まり下降に転じる。

【0150】

時刻  $t_7$  では、割込条件生成回路 10b における POC 回路 12 による点  $V_d$  の電位がインバータ 12a の閾値電圧以下に低下したことにより制御信号  $S_{cont}$  がハイレベルに遷移する。割込条件生成回路 10b は、制御信号  $S_{cont}$  に出力していた制御信号の割込み状態（ローレベル）を解除し、割込み解除状態を示すハイレベルを出力する。

割込条件受付回路 20b からの信号が入力されるコンパレータ 30 では、割込条件受付回路 20b に入力された信号が、割込条件受付回路 20b を経由して入力される。電源電圧  $V_{DD}$  が所定の電圧に達するまで出力信号  $V_{out}$  を解除状態を示すように確定させる処理が施される。解除状態を示すように確定させる処理は、制御信号  $S_{cont}$  として入力される制御信号  $S_{cont}$  によって制御される。

制御信号  $S_{cont}$  がハイレベルであることにより、割込条件受付回路 20b は、出力端 ( $Out_1$ 、 $Out_2$ ) から信号  $S_f'$  と信号  $S_a'$  を出力し、その信号は基準電圧  $V_{ref}$  と入力信号  $V_{temp}$  による信号になる。

これにより、検出回路 600 は、検出信号の出力が行える通常状態に遷移する。

【0151】

以上に示したように電源が投入されたことにより各信号の状態が遷移する。電源電圧  $V_{DD}$  が所定の動作可能電源電圧に達するまで、出力信号  $V_{out}$  はローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

【0152】

（実施形態 9）

実施形態 1 から実施形態 7 に示した検出回路（検出回路 100 から検出回路 600）は、センサ 900 と組み合わせることにより、所望のセンサ装置を構成することができる。

センサ 900 として適応できる各種センサの例として、温度センサ、MR センサ、BG R センサなどを上げることができる。

センサ 900 は、電源の正極（電源電圧  $V_{DD}$ ）に接続された定電流回路と、定電流回路の負荷になるインピーダンス回路とを組み合わせて構成することができる。インピーダンス回路は、それぞれのセンサの目的により、検出した現象の大きさに応じてインピーダンスが変化する素子を選定する。

これにより、電源投入後の動作において、電源投入によって出力信号に誤った検出信号を送出することなく信頼性の高いセンサ装置を構成することが可能となる。

【0153】

従来の検出回路及びセンサ装置では、自ら動作可能状態を外部に伝えられる構成を有していないものが一般的である。そのような検出回路及びセンサ装置が、有していた電源電圧監視回路では、電源電圧  $V_{DD}$  を効率的に使用できず、最低動作電圧を低くすることを阻害するものであった。本発明を適応することにより、上記の課題も解決することができる。

【0154】

以上、本発明の実施の形態について説明したが、本発明の電源電圧監視回路、この電源電圧監視回路の応用例である検出回路、センサ装置、および電子回路は、上述の図示例にのみ限定されるものではなく、本発明の要旨を逸脱しない範囲内において種々変更を加え得ることは勿論である。

【符号の説明】

【0155】

1 信号出力回路

10

20

30

40

50

- 2 電流源回路

3 , 3 a , 3 b インピーダンス回路

4 信号電圧監視回路

5 オフセットコンパレータ

5 a バイアス電圧源

5 b コンパレータ

6 アプリケーション回路

6 a ボルテージフォロワ回路、

6 b コンパレータ回路

5 0 電源電圧監視回路

100 検出回路

10 a 割込条件生成回路

11 オフセットコンパレータ

11 b バイアス電圧源

11 c コンパレータ

20 a 割込条件受付回路

21 出力設定回路

21 a インバータ

21 b N A N D ゲート

30 コンパレータ

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

100

【図 8】

【図 9】

【図 10】

【図 11】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図17】

【図18】

### 【図20】

【 図 1 9 】

【 図 2 1 】

【図22】

---

フロントページの続き

(72)発明者 杉浦 正一

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

(72)発明者 五十嵐 敦史

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

審査官 栗栖 正和

(56)参考文献 特開平06-213941(JP, A)

特開2001-127594(JP, A)

特開平02-108323(JP, A)

特開平04-181810(JP, A)

特開2007-081533(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03K 17/00 - 17/70