(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-265552

(P2007-265552A)

(43) 公開日 平成19年10月11日(2007.10.11)

(51) Int.C1.

G 11 C 11/4091 (2006.01)

F 1

G 11 C 11/34 353 F

テーマコード(参考)

5MO24

審査請求 未請求 請求項の数 19 O L (全 26 頁)

(21) 出願番号

特願2006-90423 (P2006-90423)

(22) 出願日

平成18年3月29日 (2006.3.29)

(71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

(74) 代理人 100115691

弁理士 藤田 篤史

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【要約】

【課題】半導体記憶装置におけるプリチャージ時の消費電流を低減させる。

【解決手段】プリチャージ電位制御回路106は、プリチャージ時に、グローバルデータ線対GDL、/GDLの共通の電位が所定の第1の検知電位より高い場合は、グローバルデータ線対GDL、/GDLに第1の検知電位以下の印加用低電圧を印加し、グローバルデータ線対GDL、/GDLの共通の電位が所定の第2の検知電位より低い場合は、グローバルデータ線対GDL、/GDLに第2の検知電位以上の印加用高電圧を印加し、上記グローバルデータ線対GDL、/GDLの電位が第1の検知電位以下かつ第2の検知電位以上の場合は、電圧を印加しない。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

メモリセルと、上記メモリセルに接続されたビット線対と、列選択信号の値に応じてオンオフするスイッチング素子を介して上記ビット線に接続されたデータ線対と、上記データ線対の共通の初期電位を制御するプリチャージ回路とを備えた半導体記憶装置であって、

プリチャージ時に、上記データ線対の共通の電位が所定の第1の検知電位より高い場合は、上記データ線対に上記第1の検知電位以下の印加用低電圧を印加し、上記データ線対の電位が所定の第2の検知電位より低い場合は、上記データ線対に上記第2の検知電位以上の印加用高電圧を印加し、上記データ線対の電位が上記第1の検知電位以下でかつ上記第2の検知電位以上の場合は、電圧を印加しないプリチャージ電位制御回路を備えたことを特徴とする半導体記憶装置。

**【請求項 2】**

請求項1の半導体記憶装置であって、

上記プリチャージ電位制御回路は、

上記印加用低電圧を発生する印加用低電圧源と上記印加用高電圧を発生する印加用高電圧源との間の電圧を分圧し、上記第1の検知電位および上記第2の検知電位を出力する検知電位出力回路を備えたことを特徴とする半導体記憶装置。

**【請求項 3】**

請求項2の半導体記憶装置であって、

上記検知電位出力回路は、

ドレインとゲートが上記印加用高電圧源に接続された印加用高電圧源接続Nチャネル型MOSトランジスタを備え、

上記印加用高電圧源接続Nチャネル型MOSトランジスタのソースと上記印加用低電圧源との間の電圧を分圧し、上記第1の検知電位および上記第2の検知電位として出力するように構成されていることを特徴とする半導体記憶装置。

**【請求項 4】**

請求項3の半導体記憶装置であって、

上記スイッチング素子は、上記印加用高電圧源接続Nチャネル型MOSトランジスタと同じサイズのNチャネル型MOSトランジスタで構成されていることを特徴とする半導体記憶装置。

**【請求項 5】**

請求項2の半導体記憶装置であって、

上記検知電位出力回路は、

ソースが上記印加用高電圧源に接続され、ドレインとゲートが接続された印加用高電圧源接続Pチャネル型MOSトランジスタを備え、

上記印加用高電圧源接続Pチャネル型MOSトランジスタのドレインおよびゲートと上記印加用低電圧源との間の電圧を分圧し、上記第1の検知電位および上記第2の検知電位として出力するように構成されていることを特徴とする半導体記憶装置。

**【請求項 6】**

請求項2の半導体記憶装置であって、

上記検知電位出力回路は、

抵抗値を調整する機能を有する抵抗素子によって、上記印加用低電圧源と上記印加用高電圧源との電位差を分圧するように構成されていることを特徴とする半導体記憶装置。

**【請求項 7】**

請求項1の半導体記憶装置であって、

上記プリチャージ電位制御回路は、

上記印加用低電圧源に接続されたソースと上記データ線対に接続されたドレインとを有するNチャネル型MOSトランジスタと、

上記印加用高電圧源に接続されたソースと上記データ線対に接続されたドレインとを有

10

20

30

40

50

する P チャネル型 M O S トランジスタと、

上記 N チャネル型 M O S トランジスタのゲートに、上記データ線対の電位が上記第 1 の検知電位より高いときには上記 N チャネル型 M O S トランジスタを導通させる電圧を出力し、上記データ線対の電位が上記第 1 の検知電位より低いときには上記 N チャネル型 M O S トランジスタを非導通にさせる電圧を出力する N チャネル型 M O S トランジスタ制御回路と、

上記 P チャネル型 M O S トランジスタのゲートに、上記データ線対の電位が上記第 2 の検知電位より低いときには上記 P チャネル型 M O S トランジスタを導通させる電圧を出力し、上記データ線対の電位が上記第 2 の検知電位より高いときには上記 P チャネル型 M O S トランジスタを非導通にさせる電圧を出力する P チャネル型 M O S トランジスタ制御回路と、

を備えたことを特徴とする半導体記憶装置。

【請求項 8】

請求項 1 の半導体記憶装置であって、

上記プリチャージ電位制御回路は、

上記データ線対の電位と上記第 1 の検知電位とが入力され、上記データ線対の電位と上記第 1 の検知電位との大小関係に応じた電圧を出力する第 1 の差動増幅回路と、

上記データ線対の電位と上記第 2 の検知電位とが入力され、上記データ線対の電位と上記第 2 の検知電位との大小関係に応じた電圧を出力する第 2 の差動増幅回路と、

を備え、

上記第 1 の差動増幅回路の出力に応じて、上記データ線対に上記印加用低電圧を印加するかどうかが制御され、

上記第 2 の差動増幅回路の出力に応じて、上記データ線対に上記印加用高電圧を印加するかどうかが制御されるように構成されていることを特徴とする半導体記憶装置。

【請求項 9】

請求項 1 の半導体記憶装置であって、

さらに、上記ビット線対の信号を増幅させるセンスアンプ回路を備え、

上記センスアンプ回路の高い方の駆動用電圧は、上記印加用高電圧と共に電源から供給されることを特徴とする半導体記憶装置。

【請求項 10】

請求項 1 の半導体記憶装置であって、

さらに、上記ビット線対の信号を増幅させるセンスアンプ回路を備え、

上記センスアンプ回路の低い方の駆動用電圧は、上記印加用低電圧と共に電源から供給されることを特徴とする半導体記憶装置。

【請求項 11】

請求項 1 の半導体記憶装置であって、

さらに、上記ビット線対の信号を増幅させるセンスアンプ回路とを備え、

上記スイッチング素子は、上記センスアンプ回路の高い方の駆動用電圧と同じ電圧で導通する N チャネル型 M O S トランジスタで構成されていることを特徴とする半導体記憶装置。

【請求項 12】

請求項 1 の半導体記憶装置であって、

さらに、上記データ線対の信号を増幅するリードアンプ回路を備え、

上記リードアンプ回路は、

上記増幅動作時に、ソースが低い方のリードアンプ駆動用電圧源に接続され、ドレインが上記データ線対のうちの第 1 のデータ線に接続され、ゲートが上記第 1 のデータ線と対となる第 2 のデータ線に接続された状態となる第 1 の N チャネル型 M O S トランジスタと、

上記増幅動作時に、ソースが低い方のリードアンプ駆動用電圧源に接続され、ドレインが上記第 2 のデータ線に接続され、ゲートが上記第 1 のデータ線に接続された状態となる

10

20

30

40

50

第 2 の N チャネル型 M O S トランジスタと、

上記増幅動作時に、ソースが高い方のリードアンプ駆動用電圧源に接続され、ドレインが上記第 1 のデータ線に接続され、ゲートが上記第 2 のデータ線に接続された状態となる第 1 の P チャネル型 M O S トランジスタと、

上記増幅動作時に、ソースが高い方のリードアンプ駆動用電圧源に接続され、ドレインが上記第 2 のデータ線に接続され、ゲートが上記第 1 のデータ線に接続された状態となる第 2 の P チャネル型 M O S トランジスタと、

を備えたことを特徴とする半導体記憶装置。

【請求項 1 3】

請求項 1 の半導体記憶装置であって、

上記プリチャージ回路は、上記データ線対の電位が上記第 1 の検知電位より高い第 3 の検知電位より高い場合に、上記第 3 の検知電位以下の場合よりも、上記プリチャージ回路から上記データ線対に大きな電流を流し得るように構成されたことを特徴とする半導体記憶装置。

【請求項 1 4】

請求項 1 の半導体記憶装置であって、

上記プリチャージ回路は、上記データ線対の電位が上記第 2 の検知電位より低い第 4 の検知電位よりも低い場合に、上記第 4 の検知電位以上の場合よりも、上記プリチャージ回路から上記データ線対に大きな電流を流し得るように構成されたことを特徴とする半導体記憶装置。

【請求項 1 5】

請求項 1 の半導体記憶装置であって、

上記プリチャージ回路は、上記データ線対の電位が上記第 1 の検知電位より高い第 3 の検知電位よりも高い場合に、上記第 3 の検知電位以下の場合よりも、上記プリチャージ回路から上記データ線対に大きな電流を流し、上記データ線対の電位が上記第 2 の検知電位より低い第 4 の検知電位よりも低い場合に、上記第 4 の検知電位以上の場合よりも、上記プリチャージ回路から上記データ線対に大きな電流を流し得るように構成されたことを特徴とする半導体記憶装置。

【請求項 1 6】

請求項 1 5 の半導体記憶装置であって、

上記プリチャージ電位制御回路は、

上記印加用低電圧を発生する印加用低電圧源と上記印加用高電圧を発生する印加用高電圧源との間の電圧を分圧し、上記第 1 の検知電位、上記第 2 の検知電位、上記第 3 の検知電位、および上記第 4 の検知電位として出力する検知電位出力回路を備えたことを特徴とする半導体記憶装置。

【請求項 1 7】

請求項 1 5 の半導体記憶装置であって、

上記プリチャージ電位制御回路は、

上記印加用低電圧源に接続されたソースと上記データ線対に接続されたドレインとを有する第 1 の N チャネル型 M O S トランジスタおよび第 2 の N チャネル型 M O S トランジスタと、

上記印加用高電圧源に接続されたソースと上記データ線対に接続されたドレインとを有する第 1 の P チャネル型 M O S トランジスタおよび第 2 の P チャネル型 M O S トランジスタと、

上記第 1 の N チャネル型 M O S トランジスタのゲートに、上記データ線対の電位が上記第 3 の検知電位より高いときには上記第 1 の N チャネル型 M O S トランジスタを導通させる電圧を出力し、上記データ線対の電位が上記第 3 の検知電位より低いときには上記第 1 の N チャネル型 M O S トランジスタを非導通にさせる電圧を出力する第 1 の N チャネル型 M O S トランジスタ制御回路と、

上記第 2 の N チャネル型 M O S トランジスタのゲートに、上記データ線対の電位が上記

10

20

30

40

50

第1の検知電位より高いときには上記第2のNチャネル型MOSトランジスタを導通させる電圧を出力し、上記データ線対の電位が上記第1の検知電位より低いときには上記第2のNチャネル型MOSトランジスタを非導通にさせる電圧を出力する第2のNチャネル型MOSトランジスタ制御回路と、

上記第1のPチャネル型MOSトランジスタのゲートに、上記データ線対の電位が上記第2の検知電位より低いときには上記第1のPチャネル型MOSトランジスタを導通させる電圧を出力し、上記データ線対の電位が上記第2の検知電位より高いときには上記第1のPチャネル型MOSトランジスタを非導通にさせる電圧を出力する第1のPチャネル型MOSトランジスタ制御回路と、

上記第2のPチャネル型MOSトランジスタのゲートに、上記データ線対の電位が上記第4の検知電位より低いときには上記第2のPチャネル型MOSトランジスタを導通させる電圧を出力し、上記データ線対の電位が上記第4の検知電位より高いときには上記第2のPチャネル型MOSトランジスタを非導通にさせる電圧を出力する第2のPチャネル型MOSトランジスタ制御回路と、

を備えたことを特徴とする半導体記憶装置。

#### 【請求項18】

請求項17の半導体記憶装置であって、

上記第1のNチャネル型MOSトランジスタのサイズは、上記第2のNチャネル型MOSトランジスタのサイズより大きく、かつ上記第2のPチャネル型MOSトランジスタのサイズは、上記第1のPチャネル型MOSトランジスタのサイズより大きいことを特徴とする半導体記憶装置。

#### 【請求項19】

請求項15の半導体記憶装置であって、

上記プリチャージ電位制御回路は、

上記データ線対の電位と上記第3の検知電位とが入力され、上記データ線対の電位と上記第3の検知電位との大小関係に応じた電圧を出力する第1の差動増幅回路と、

上記データ線対の電位と上記第1の検知電位とが入力され、上記データ線対の電位と上記第1の検知電位との大小関係に応じた電圧を出力する第2の差動増幅回路と、

上記データ線対の電位と上記第2の検知電位とが入力され、上記データ線対の電位と上記第2の検知電位との大小関係に応じた電圧を出力する第3の差動増幅回路と、

上記データ線対の電位と上記第4の検知電位とが入力され、上記データ線対の電位と上記第4の検知電位との大小関係に応じた電圧を出力する第4の差動増幅回路と、

を備え、

上記第1の差動増幅回路の出力に応じて、上記データ線対に上記印加用低電圧を印加するかどうかが制御され、

上記第3の差動増幅回路の出力に応じて、上記データ線対に上記印加用低電圧を印加するかどうかが制御され、

上記第2の差動増幅回路および上記第4の差動増幅回路の出力に応じて、上記プリチャージ回路に流れる電流が変化するように構成されたことを特徴とする半導体記憶装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、ダイナミックランダムアクセスメモリ(DRAM)などの半導体記憶装置に関するものである。

#### 【背景技術】

#### 【0002】

従来の半導体記憶装置として、例えば特許文献1に示されるような回路を備えたものが知られている。特許文献1に示される回路では、グローバルデータライン40A、40Bが、メモリコアに接続されたローカルデータラインに、トランスファゲートで構成されるスイッチ部620を介して接続される。そして、グローバルデータライン40A、40B

10

20

30

40

50

は、プリチャージ時、外部印加電源電圧  $V_{DD}$  の半分の電位  $V_{DD}/2$  等のプリチャージ用電源に接続される。

【特許文献 1】特開 2003-151276 号公報 (段落 0020 ~ 0036、図 4A)

【非特許文献 1】伊藤清男著「超 LSI メモリ」培風館、1994年11月5日、p. 85 - 96

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0003】

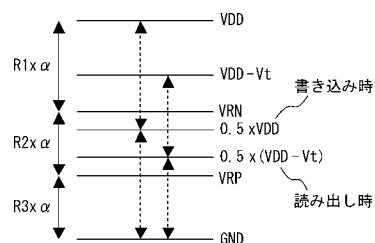

しかしながら、上記従来の構成においては、読み出し時のローカルデータラインの H レベルの電位と書き込み時のグローバルデータライン 40A、40B の H レベルの電位とを等しくした場合、以下に説明するような問題が生じる。

##### 【0004】

ここで、読み出し時のローカルデータラインの H レベルの電位と書き込み時のグローバルデータライン 40A、40B の H レベルの電位を電圧  $V_{DD}$ 、それぞれの L レベルの電位を電圧  $GND (0V)$  とする。

##### 【0005】

読み出し動作時、グローバルデータライン 40A、40B の L 側の電位は電圧  $GND$  となるが、H 側の電位は、電圧  $V_{DD}$  よりスイッチ部 620 を構成するトランジスタの閾値電圧  $V_t$  分低い電位、すなわち  $V_{DD} - V_t$  までしか上昇しない。したがって、この時のグローバルデータライン 40A、40B の電位を平均した電位は、 $0.5 \times (V_{DD} - V_t)$  である。

##### 【0006】

一方、書き込み動作時、グローバルデータライン 40A、40B の H 側、L 側の電位は、それぞれ電圧  $V_{DD}$ 、電圧  $GND$  となる。したがって、この時のグローバルデータライン 40A、40B の電位を平均した電位は、 $0.5 \times V_{DD}$  である。

##### 【0007】

上記のような場合、読み出し動作時のグローバルデータライン 40A、40B の電位を平均した電位と書き込み動作時のグローバルデータライン 40A、40B の電位を平均した電位とが異なっている。したがって、プリチャージ時に常に一定の電圧が所定の電圧源から印加されるようになっている従来の構成では、読み出し動作後のプリチャージ時と書き込み動作後のプリチャージ時との少なくとも一方で電流が流れ、電力が消費されてしまうという問題がある。つまり、プリチャージ用電源の電位が、読み出し動作時のグローバルデータライン 40A、40B の電位の平均、すなわち  $0.5 \times (V_{DD} - V_t)$  にされた場合、書き込み動作後のプリチャージの開始時には、グローバルデータライン 40A、40B の平均電位は  $0.5 \times V_{DD}$  なので、電位差が生じて電流が流れてしまう。逆に、プリチャージ用電源の電位が、書き込み動作時のグローバルデータライン 40A、40B の電位の平均、すなわち  $0.5 \times V_{DD}$  となるように設定された場合、読み出し動作後のプリチャージの開始時には、グローバルデータライン 40A、40B の電位は  $0.5 \times (V_{DD} - V_t)$  なので、電位差が生じて電流が流れてしまう。プリチャージ回路は半導体記憶装置に例えば 1000 個程度搭載されるため、プリチャージ時に上記のように電流が流れることによって半導体装置全体で消費される電力は大きくなる。

##### 【0008】

本発明は、上記の点に鑑み、半導体記憶装置のプリチャージ時の消費電流を低減させることを目的とする。

#### 【課題を解決するための手段】

##### 【0009】

上記の課題を解決するため、請求項 1 の発明は、メモリセルと、上記メモリセルに接続されたビット線対と、列選択信号の値に応じてオンオフするスイッチング素子を介して上記ビット線に接続されたデータ線対と、上記データ線対の共通の初期電位を制御するプリチャージ回路とを備えた半導体記憶装置であって

10

20

30

40

50

プリチャージ時に、上記データ線対の共通の電位が所定の第1の検知電位より高い場合は、上記データ線対に上記第1の検知電位以下の印加用低電圧を印加し、上記データ線対の電位が所定の第2の検知電位より低い場合は、上記データ線対に上記第2の検知電位以上の印加用高電圧を印加し、上記データ線対の電位が上記第1の検知電位以下でかつ上記第2の検知電位以上の場合は、電圧を印加しないプリチャージ電位制御回路を備えたことを特徴とする。

#### 【0010】

これにより、プリチャージ時にデータ線対が第1の検知電位以下でかつ第2の検知電位以上の電位に保たれる。また、データ線対の電位が第1の検知電位以下でかつ第2の検知電位以上になっている時、プリチャージ電位制御回路はデータ線対に電圧を印加しないので、プリチャージ電位制御回路とデータ線対との間に電流が流れることがない。

#### 【0011】

請求項2の発明は、

請求項1の半導体記憶装置であって、

上記プリチャージ電位制御回路は、

上記印加用低電圧を発生する印加用低電圧源と上記印加用高電圧を発生する印加用高電圧源との間の電圧を分圧し、上記第1の検知電位および上記第2の検知電位を出力する検知電位出力回路を備えたことを特徴とする。

#### 【0012】

これにより、比較的小さい回路面積でプリチャージ電位制御回路を構成することが容易になる。

#### 【0013】

請求項3の発明は、

請求項2の半導体記憶装置であって、

上記検知電位出力回路は、

ドレインとゲートが上記印加用高電圧源に接続された印加用高電圧源接続Nチャネル型MOSトランジスタを備え、

上記印加用高電圧源接続Nチャネル型MOSトランジスタのソースと上記印加用低電圧源との間の電圧を分圧し、上記第1の検知電位および上記第2の検知電位として出力するように構成されていることを特徴とする。

#### 【0014】

これにより、印加用高電圧源接続Nチャネル型MOSトランジスタのソースの電位の印可用高電圧に対する依存性が、読み出し動作時のデータ線対の平均電位の印可用高電圧に対する依存性に近いので、単に抵抗分圧によって第2の検知電位が生成される場合に比べ、広い印加用高電圧の範囲でプリチャージ電位制御回路を動作させることができる。

#### 【0015】

請求項4の発明は、

請求項3の半導体記憶装置であって、

上記スイッチング素子は、上記印加用高電圧源接続Nチャネル型MOSトランジスタと同じサイズのNチャネル型MOSトランジスタで構成されていることを特徴とする。

#### 【0016】

これにより、製造工程のばらつきによる影響が少なく、動作の安定したプリチャージ制御回路を構成することが容易になる。

#### 【0017】

請求項5の発明は、

請求項2の半導体記憶装置であって、

上記検知電位出力回路は、

ソースが上記印加用高電圧源に接続され、ドレインとゲートが接続された印加用高電圧源接続Pチャネル型MOSトランジスタを備え、

10

20

30

40

50

上記印加用高電圧源接続Pチャネル型MOSトランジスタのドレインおよびゲートと上記印加用低電圧源との間の電圧を分圧し、上記第1の検知電位および上記第2の検知電位として出力するように構成されていることを特徴とする。

【0018】

これにより、印加用高電圧源接続Pチャネル型MOSトランジスタのドレインおよびゲートの電位の印可用高電圧に対する依存性が、読み出し動作時のデータ線対の平均電位の印可用高電圧に対する依存性に近いので、単に抵抗分圧によって第2の検知電位が生成される場合に比べ、広い印加用高電圧の範囲でプリチャージ電位制御回路を動作させることができる。

【0019】

請求項6の発明は、

請求項2の半導体記憶装置であって、

上記検知電位出力回路は、

抵抗値を調整する機能を有する抵抗素子によって、上記印加用低電圧源と上記印加用高電圧源との電位差を分圧するように構成されていることを特徴とする。

【0020】

これにより、ウェハに回路パターンが作り込まれる時にはらつきが生じる場合でも、その後に抵抗値を調整することによって、プリチャージ電位制御回路を所望の第1の検知電位および第2の検知電位で動作させることができる。

【0021】

請求項7の発明は、

請求項1の半導体記憶装置であって、

上記プリチャージ電位制御回路は、

上記印加用低電圧源に接続されたソースと上記データ線対に接続されたドレインとを有するNチャネル型MOSトランジスタと、

上記印加用高電圧源に接続されたソースと上記データ線対に接続されたドレインとを有するPチャネル型MOSトランジスタと、

上記Nチャネル型MOSトランジスタのゲートに、上記データ線対の電位が上記第1の検知電位より高いときには上記Nチャネル型MOSトランジスタを導通させる電圧を出力し、上記データ線対の電位が上記第1の検知電位より低いときには上記Nチャネル型MOSトランジスタを非導通にさせる電圧を出力するNチャネル型MOSトランジスタ制御回路と、

上記Pチャネル型MOSトランジスタのゲートに、上記データ線対の電位が上記第2の検知電位より低いときには上記Pチャネル型MOSトランジスタを導通させる電圧を出力し、上記データ線対の電位が上記第2の検知電位より高いときには上記Pチャネル型MOSトランジスタを非導通にさせる電圧を出力するPチャネル型MOSトランジスタ制御回路と、

を備えたことを特徴とする。

【0022】

請求項8の発明は、

請求項1の半導体記憶装置であって、

上記プリチャージ電位制御回路は、

上記データ線対の電位と上記第1の検知電位とが入力され、上記データ線対の電位と上記第1の検知電位との大小関係に応じた電圧を出力する第1の差動增幅回路と、

上記データ線対の電位と上記第2の検知電位とが入力され、上記データ線対の電位と上記第2の検知電位との大小関係に応じた電圧を出力する第2の差動增幅回路と、

を備え、

上記第1の差動增幅回路の出力に応じて、上記データ線対に上記印加用低電圧を印加するかどうかが制御され、

上記第2の差動增幅回路の出力に応じて、上記データ線対に上記印加用高電圧を印加す

るかどうかが制御されるように構成されていることを特徴とする。

【0023】

これらにより、比較的小さい回路面積でプリチャージ電位制御回路を構成することが容易になる。

【0024】

請求項9の発明は、

請求項1の半導体記憶装置であって、

さらに、上記ビット線対の信号を増幅させるセンスアンプ回路を備え、

上記センスアンプ回路の高い方の駆動用電圧は、上記印加用高電圧と共に電源から供給されることを特徴とする。

10

【0025】

請求項10の発明は、

請求項1の半導体記憶装置であって、

さらに、上記ビット線対の信号を増幅させるセンスアンプ回路を備え、

上記センスアンプ回路の低い方の駆動用電圧は、上記印加用低電圧と共に電源から供給されることを特徴とする。

【0026】

これらにより、センスアンプ回路の駆動電圧とプリチャージ回路の印加用電圧とが一致し、センスアンプによる増幅動作によってビット線対に生じる電位が、印加用電圧に依存するので、広い印加用電圧の範囲で消費電力を低減できる。

20

【0027】

請求項11の発明は、

請求項1の半導体記憶装置であって、

さらに、上記ビット線対の信号を増幅させるセンスアンプ回路とを備え、

上記スイッチング素子は、上記センスアンプ回路の高い方の駆動用電圧と同じ電圧で導通するNチャネル型MOSトランジスタで構成されていることを特徴とする。

【0028】

これにより、センスアンプ回路とスイッチング素子とが電源を共有でき、個々に電源を設ける必要がないので、比較的小さい回路面積でセンスアンプ回路やスイッチング素子を構成することが容易になる。

30

【0029】

請求項12の発明は、

請求項1の半導体記憶装置であって、

さらに、上記データ線対の信号を増幅するリードアンプ回路を備え、

上記リードアンプ回路は、

上記増幅動作時に、ソースが低い方のリードアンプ駆動用電圧源に接続され、ドレインが上記データ線対のうちの第1のデータ線に接続され、ゲートが上記第1のデータ線と対となる第2のデータ線に接続された状態となる第1のNチャネル型MOSトランジスタと、

上記増幅動作時に、ソースが低い方のリードアンプ駆動用電圧源に接続され、ドレインが上記第2のデータ線に接続され、ゲートが上記第1のデータ線に接続された状態となる第2のNチャネル型MOSトランジスタと、

上記増幅動作時に、ソースが高い方のリードアンプ駆動用電圧源に接続され、ドレインが上記第1のデータ線に接続され、ゲートが上記第2のデータ線に接続された状態となる第1のPチャネル型MOSトランジスタと、

上記増幅動作時に、ソースが高い方のリードアンプ駆動用電圧源に接続され、ドレインが上記第2のデータ線に接続され、ゲートが上記第1のデータ線に接続された状態となる第2のPチャネル型MOSトランジスタと、

を備えたことを特徴とする。

【0030】

40

50

これにより、少ないトランジスタでリードアンプ回路を構成することができる。また、プリチャージ回路およびプリチャージ電位制御回路によって、データ線対が第1の検知電位以下でかつ第2の検知電位以上の電位にプリチャージされることによって、リードアンプ回路の感度は高くなる。

【0031】

請求項13の発明は、

請求項1の半導体記憶装置であって、

上記プリチャージ回路は、上記データ線対の電位が上記第1の検知電位より高い第3の検知電位より高い場合に、上記第3の検知電位以下の場合よりも、上記プリチャージ回路から上記データ線対に大きな電流を流し得るように構成されたことを特徴とする。

10

【0032】

請求項14の発明は、

請求項1の半導体記憶装置であって、

上記プリチャージ回路は、上記データ線対の電位が上記第2の検知電位より低い第4の検知電位よりも低い場合に、上記第4の検知電位以上の場合よりも、上記プリチャージ回路から上記データ線対に大きな電流を流し得るように構成されたことを特徴とする。

20

【0033】

請求項15の発明は、

請求項1の半導体記憶装置であって、

上記プリチャージ回路は、上記データ線対の電位が上記第1の検知電位より高い第3の検知電位よりも高い場合に、上記第3の検知電位以下の場合よりも、上記プリチャージ回路から上記データ線対に大きな電流を流し、上記データ線対の電位が上記第2の検知電位より低い第4の検知電位よりも低い場合に、上記第4の検知電位以上の場合よりも、上記プリチャージ回路から上記データ線対に大きな電流を流し得るように構成されたことを特徴とする。

20

【0034】

これにより、データ線対の電位が第1の検知電位よりも高く、かつ第3の検知電位以下の場合、第3の検知電位よりも高い場合よりも小さな電流が流れ、データ線対の電位はゆっくり降下する。同様に、データ線対の電位が第2の検知電位よりも低く、かつ第4の検知電位以上の場合、第4の検知電位以下の場合よりも小さな電流が流れ、データ線対の電位はゆっくり上昇する。

30

【0035】

請求項16の発明は、

請求項15の半導体記憶装置であって、

上記プリチャージ電位制御回路は、

上記印加用低電圧を発生する印加用低電圧源と上記印加用高電圧を発生する印加用高電圧源との間の電圧を分圧し、上記第1の検知電位、上記第2の検知電位、上記第3の検知電位、および上記第4の検知電位として出力する検知電位出力回路を備えたことを特徴とする。

40

【0036】

これにより、4つの検知電位を出力するために検知電位出力回路が共有されるので、比較的小さい回路面積でプリチャージ電位制御回路を構成することが容易になる。

【0037】

請求項17の発明は、

請求項15の半導体記憶装置であって、

上記プリチャージ電位制御回路は、

上記印加用低電圧源に接続されたソースと上記データ線対に接続されたドレインとを有する第1のNチャネル型MOSトランジスタおよび第2のNチャネル型MOSトランジスタと、

上記印加用高電圧源に接続されたソースと上記データ線対に接続されたドレインとを有

50

する第1のPチャネル型MOSトランジスタおよび第2のPチャネル型MOSトランジスタと、

上記第1のNチャネル型MOSトランジスタのゲートに、上記データ線対の電位が上記第3の検知電位より高いときには上記第1のNチャネル型MOSトランジスタを導通させる電圧を出力し、上記データ線対の電位が上記第3の検知電位より低いときには上記第1のNチャネル型MOSトランジスタを非導通にさせる電圧を出力する第1のNチャネル型MOSトランジスタ制御回路と、

上記第2のNチャネル型MOSトランジスタのゲートに、上記データ線対の電位が上記第1の検知電位より高いときには上記第2のNチャネル型MOSトランジスタを導通させる電圧を出力し、上記データ線対の電位が上記第1の検知電位より低いときには上記第2のNチャネル型MOSトランジスタを非導通にさせる電圧を出力する第2のNチャネル型MOSトランジスタ制御回路と、

上記第1のPチャネル型MOSトランジスタのゲートに、上記データ線対の電位が上記第2の検知電位より低いときには上記第1のPチャネル型MOSトランジスタを導通させる電圧を出力し、上記データ線対の電位が上記第2の検知電位より高いときには上記第1のPチャネル型MOSトランジスタを非導通にさせる電圧を出力する第1のPチャネル型MOSトランジスタ制御回路と、

上記第2のPチャネル型MOSトランジスタのゲートに、上記データ線対の電位が上記第4の検知電位より低いときには上記第2のPチャネル型MOSトランジスタを導通させる電圧を出力し、上記データ線対の電位が上記第4の検知電位より高いときには上記第2のPチャネル型MOSトランジスタを非導通にさせる電圧を出力する第2のPチャネル型MOSトランジスタ制御回路と、

を備えたことを特徴とする。

### 【0038】

請求項18の発明は、

請求項17の半導体記憶装置であって、

上記第1のNチャネル型MOSトランジスタのサイズは、上記第2のNチャネル型MOSトランジスタのサイズより大きく、かつ上記第2のPチャネル型MOSトランジスタのサイズは、上記第1のPチャネル型MOSトランジスタのサイズより大きいことを特徴とする。

### 【0039】

請求項19の発明は、

請求項15の半導体記憶装置であって、

上記プリチャージ電位制御回路は、

上記データ線対の電位と上記第3の検知電位とが入力され、上記データ線対の電位と上記第3の検知電位との大小関係に応じた電圧を出力する第1の差動増幅回路と、

上記データ線対の電位と上記第1の検知電位とが入力され、上記データ線対の電位と上記第1の検知電位との大小関係に応じた電圧を出力する第2の差動増幅回路と、

上記データ線対の電位と上記第2の検知電位とが入力され、上記データ線対の電位と上記第2の検知電位との大小関係に応じた電圧を出力する第3の差動増幅回路と、

上記データ線対の電位と上記第4の検知電位とが入力され、上記データ線対の電位と上記第4の検知電位との大小関係に応じた電圧を出力する第4の差動増幅回路と、

を備え、

上記第1の差動増幅回路の出力に応じて、上記データ線対に上記印加用低電圧を印加するかどうかが制御され、

上記第3の差動増幅回路の出力に応じて、上記データ線対に上記印加用低電圧を印加するかどうかが制御され、

上記第2の差動増幅回路および上記第4の差動増幅回路の出力に応じて、上記プリチャージ回路に流れる電流が変化するように構成されたことを特徴とする。

### 【0040】

10

20

30

40

50

これらにより、比較的小さい回路面積でプリチャージ電位制御回路を構成することが容易になる。

【発明の効果】

【0041】

半導体記憶装置のプリチャージ時の消費電流が低減する。

【発明を実施するための最良の形態】

【0042】

以下、本発明の実施形態について、図面を参照して説明する。なお、以下の各実施形態において、他の実施形態と同様の機能を有する構成要素については同一の符号を付して説明を省略する。

【0043】

《発明の実施形態1》

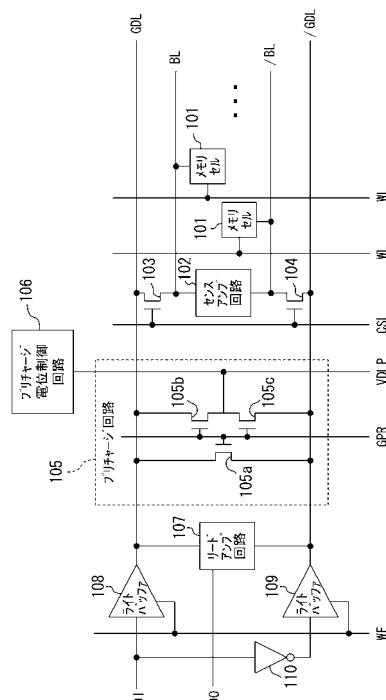

図1は、本発明の実施形態1に係る半導体記憶装置の構成を示す回路図である。

【0044】

同図に示すように、半導体記憶装置は、メモリセル101、センスアンプ回路102、Nチャネル型MOSトランジスタ103、104（スイッチング素子）、プリチャージ回路105、プリチャージ電位制御回路106、リードアンプ回路107、ライトバッファ108、109およびインバータ110を備えている。

【0045】

メモリセル101には、ビット線BLおよびビット線/B<sub>L</sub>のいずれか一方とワード線WLとが接続されている。メモリセル101は、接続されているワード線WLが活性化されると、接続されているビット線BLまたはビット線/B<sub>L</sub>との間でデータの入出力をを行うようになっている。

【0046】

センスアンプ回路102は、ビット線対BL、/BLの間の電位差を増幅するようになっている。ここで、センスアンプ回路102の高い方の駆動用電圧は電圧VDDであり、低い方の駆動用電圧は電圧GND(0V)となっている。

【0047】

Nチャネル型MOSトランジスタ103は、グローバルデータ線GDL（データ線）とビット線BLとの間に接続され、ゲートには列選択信号CSLが入力されるようになっている。

【0048】

Nチャネル型MOSトランジスタ104は、グローバルデータ線/GDL（データ線）とビット線/B<sub>L</sub>との間に接続され、ゲートには列選択信号CSLが入力されるようになっている。

【0049】

ここで、列選択信号CSLのHレベルは電圧VDD、Lレベルは電圧GNDとなっている。

【0050】

なお、Nチャネル型MOSトランジスタ103、104は、センスアンプ回路102の高い方の駆動用電圧と同じ電圧VDDで導通するようになっている。

【0051】

プリチャージ回路105は、Nチャネル型MOSトランジスタ105a～105cを備えている。Nチャネル型MOSトランジスタ105a～105cのゲートには、グローバルデータ線プリチャージ信号GPRが入力され、プリチャージ時には、Nチャネル型MOSトランジスタ105a～105cが導通状態になるようになっている。

【0052】

プリチャージ電位制御回路106は、グローバルデータ線GDL、/GDLの電位が所定の第1の検知電位より高い場合は、グローバルデータ線GDL、/GDLに電圧GNDを印加し、グローバルデータ線GDL、/GDLの電位が所定の第2の検知電位より低い

10

20

30

40

50

場合は、グローバルデータ線 GDL、/GDL に電圧 VDD を印加し、グローバルデータ線 GDL、/GDL の電位が第 1 の検知電位 VRN 以下でかつ第 2 の検知電位 VRP 以上の場合は、電圧を印加しないようになっている。このプリチャージ電位制御回路 106 の詳細な構成については後述する。

#### 【0053】

リードアンプ回路 107 は、グローバルデータ線対 GDL、/GDL 間の電位差を增幅し、出力データ DO を出力するようになっている。このリードアンプ回路 107 の詳細な構成についても後述する。

#### 【0054】

ライトバッファ 108、109 は、ライトイネーブル信号 WE によって活性状態と非活性状態のいずれかに制御されるようになっている。ライトバッファ 108 は、活性状態では、入力される入力データ DI をそのままグローバルデータ線 GDL に出力し、非活性状態では、入力される入力データ DI をグローバルデータ線 GDL に出力しないようになっている。ライトバッファ 109 には、インバータ 110 から出力される入力データ DI の反転データ /DI が入力されるようになっている。ライトバッファ 109 は、活性状態では、入力される反転データ /DI をそのままグローバルデータ線 /GDL に出力し、非活性状態では、入力される反転データ /DI をグローバルデータ線 /GDL に出力しないようになっている。

#### 【0055】

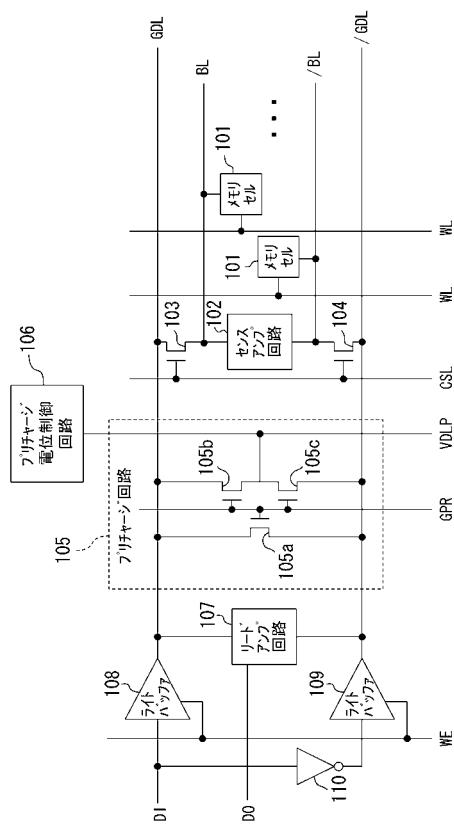

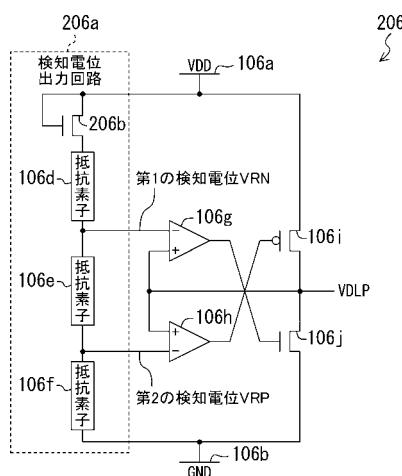

次に、プリチャージ電位制御回路 106 の詳細な構成について説明する。

#### 【0056】

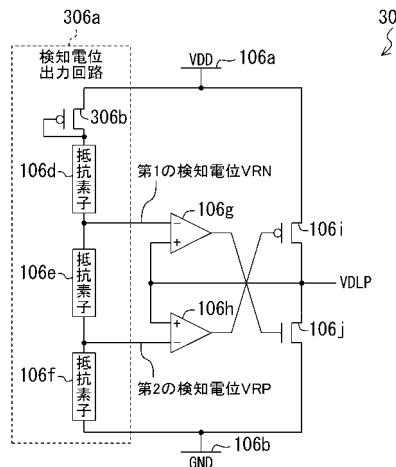

図 2 に示すように、プリチャージ電位制御回路 106 は、印加用高電圧源 106a、印加用低電圧源 106b、検知電位出力回路 106c、差動增幅回路 106g、106h、P チャネル型 MOS トランジスタ 106i、および N チャネル型 MOS トランジスタ 106j を備えている。

#### 【0057】

印加用高電圧源 106a は、電圧 VDD を発生するようになっている。なお、印加用高電圧源 106a は、センスアンプ回路 102 に、電圧 VDD を高い方の駆動用電圧として供給するようになっている。

#### 【0058】

印加用低電圧源 106b は、電圧 GND を発生するようになっている。なお、印加用高電圧源 106a は、センスアンプ回路 102 に、電圧 GND を低い方の駆動用電圧として供給するようになっている。

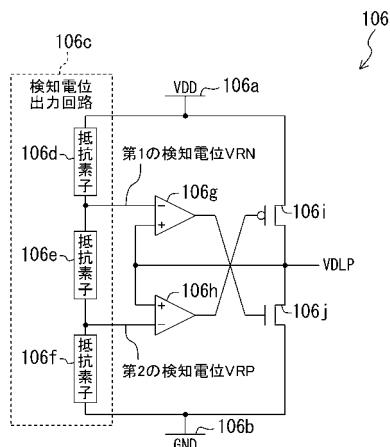

#### 【0059】

検知電位出力回路 106c は、抵抗素子 106d ~ 106f を備え、印加用高電圧源 106a と印加用低電圧源 106b との間の電圧を分圧し、第 1 の検知電位 VRN、および第 2 の検知電位 VRP を出力するようになっている。例えば、図 3 に示すように、VRN として  $0.5 \times VDD$  より所定分高い電圧、VRP として  $0.5 \times (VDD - V_t)$  より所定分低い電圧を出力するようになっている。 $0.5 \times VDD$  は、書き込み動作時のグローバルデータ線 GDL、/GDL の平均電位、 $0.5 \times (VDD - V_t)$  は、読み出し動作時のグローバルデータ線 GDL、/GDL の平均電位である。書き込み動作と読み出し動作の詳細については後述する。ここで、抵抗素子 106d ~ 106f の抵抗値をそれぞれ R1、R2、R3 とすると、検知電位と抵抗素子の抵抗値の関係は、第 1 の検知電位 VRN =  $VDD \times (R2 + R3) / (R1 + R2 + R3)$ 、第 2 の検知電位 VRP =  $VDD \times R3 / (R1 + R2 + R3)$  で表される。この関係に従って、第 1 の検知電位 VRN が  $0.5 \times VDD$  より大きい値に、第 2 の検知電位 VRP が  $0.5 \times (VDD - V_t)$  より小さい値になるように、抵抗素子 106d ~ 106f の抵抗値 R1、R2、R3 が設定される。

#### 【0060】

差動增幅回路 106g は、グローバルデータ線 GDL、/GDL の電位が第 1 の検知電

10

20

30

40

50

位VRNより高いときには、Nチャネル型MOSトランジスタ106jのゲートに、Nチャネル型MOSトランジスタ106jを導通させる高い電圧を出力するようになっている。逆に、グローバルデータ線GDL、/GDLの電位が第1の検知電位VRN以下のときには、Nチャネル型MOSトランジスタ106jのゲートに、Nチャネル型MOSトランジスタ106jを非導通にさせる低い電圧を出力するようになっている。

【0061】

差動増幅回路106hは、グローバルデータ線GDL、/GDLの電位が第2の検知電位VRPより低いときには、Pチャネル型MOSトランジスタ106iのゲートに、Pチャネル型MOSトランジスタ106iを導通させる低い電圧を出力するようになっている。逆に、グローバルデータ線GDL、/GDLの電位が第2の検知電位VRP以上のときには、Pチャネル型MOSトランジスタ106iのゲートに、Pチャネル型MOSトランジスタ106iを非導通にさせる高い電圧を出力するようになっている。

10

【0062】

上記構成により、グローバルデータ線GDL、/GDLの電位は、第1の検知電位VRN以下でかつ第2の検知電位VRP以上の範囲に維持される。

【0063】

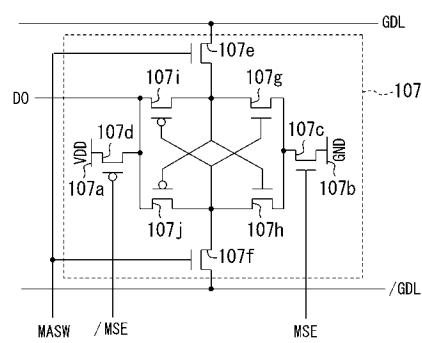

次に、リードアンプ回路107(メインアンプ回路)の詳細な構成について説明する。

【0064】

図4に示すように、リードアンプ回路107は、リードアンプ駆動用電圧源107a、107b、Nチャネル型MOSトランジスタ107c、107e～107h、Pチャネル型MOSトランジスタ107d、107i、107jを備えたクロスカップル型のアンプである。

20

【0065】

リードアンプ駆動用電圧源107aは、電圧VDDを発生するようになっている。

【0066】

リードアンプ駆動用電圧源107bは、電圧GNDを発生するようになっている。

【0067】

Nチャネル型MOSトランジスタ107c、およびPチャネル型MOSトランジスタ107dは、リードアンプ回路107を活性化させるためにメインアンプ起動信号MSE、/MSEによって、導通状態にされるようになっている。

30

【0068】

Nチャネル型MOSトランジスタ107e、107fは、グローバルデータ線対GDL、/GDL間の電圧が増幅される際、メインアンプスイッチへの入力信号MASWによって、導通状態にされるようになっている。

【0069】

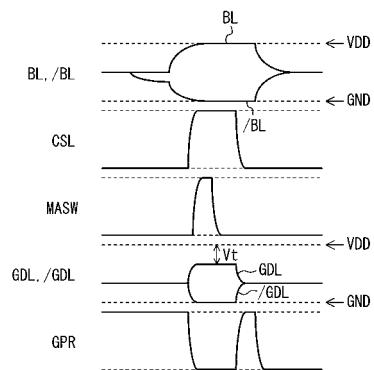

次に、上記のように構成された半導体記憶装置の読み出し動作について、図5のタイミングチャートを参照して説明する。

【0070】

図5は、本発明の実施形態1に係る半導体記憶装置の読み出し動作時の各信号の電圧レベルの例を示すタイミングチャートである。

40

【0071】

まず、あるメモリセル101に接続されたワード線WLが活性化すると、メモリセル101に記憶されたデータがビット線BLまたはビット線/BLに出力される。そして、活性状態にされたセンスアンプ回路102によって、ビット線BLとビット線/BLとの間の電圧が増幅される。その結果、図5に示すように、増幅後のビット線BL、/BLの電位は、例えば、それぞれ電圧VDD、電圧GNDとなる。

【0072】

一方、センスアンプ回路102によるビット線BLおよびビット線/BLの電圧の増幅が開始される時、グローバルデータ線プリチャージ信号GPRはHレベルとなっている。そのため、グローバルデータ線GDL、/GDLはプリチャージ回路105によってプリ

50

チャージされた状態になっている。すなわち、プリチャージ回路 105 の N チャネル型 MOS トランジスタ 105a ~ 105c が導通状態であり、グローバルデータ線 GDL、/ GDL の電位は、後に詳述するようにプリチャージ電位制御回路 106 によって制御されて互いに等しい所定の範囲の電位となっている。

【0073】

センスアンプ回路 102 によって、ビット線 BL およびビット線 / BL の電位がそれぞれ電圧 VDD、電圧 GND まで増幅された後、列選択信号 CSL が H レベルにされる。これにより、N チャネル型 MOS トランジスタ 103、104 が導通状態になり、グローバルデータ線 GDL とビット線 BL とが接続され、グローバルデータ線 / GDL とビット線 / BL とが接続される。また、列選択信号 CSL が H レベルになると同時に、グローバルデータ線プリチャージ信号 GPR が L レベルにされる。そして、グローバルデータ線対 GDL、/ GDL に、ビット線対 BL、/ BL のデータが転送される。すると、例えば、図 5 に示すように、グローバルデータ線 / GDL の電位は電圧 GND となるが、グローバルデータ線 GDL の電位は、電圧 VDD より N チャネル型 MOS トランジスタ 103 の閾値電圧  $V_t$  分低い電位、すなわち  $VDD - V_t$  までしか上昇しない。

10

【0074】

その後、メインアンプスイッチへの入力信号 MASW が H レベルになり、リードアンプ回路 107 の N チャネル型 MOS トランジスタ 107e、107f は導通状態となる。これにより、グローバルデータ線対 GDL、/ GDL の信号が、リードアンプ回路 107 の増幅動作を行う部分に入力される。その後、メインアンプ起動信号 MSE、/ MSE がそれぞれ H レベル、L レベルにされ、リードアンプ回路 107 は、活性化された状態になり、メモリセル 101 のデータに基づくグローバルデータ線対 GDL、/ GDL の信号を増幅して、出力データ DO を出力する。

20

【0075】

出力データ DO が output された後、次の読み出しに備えるため、メインアンプスイッチへの入力信号 MASW が L レベルにされ、メインアンプ起動信号 MSE、/ MSE がそれぞれ L レベル、H レベルにされることにより、リードアンプ回路 107 は非活性化される。また、列選択信号 CSL が L レベルにされ、ビット線対 BL、/ BL のデータがグローバルデータ線対 GDL、/ GDL に転送されない状態になる。その後、グローバルデータ線プリチャージ信号 GPR が H レベルにされる。これにより、プリチャージ回路 105 の N チャネル型 MOS トランジスタ 105a ~ 105c が導通状態となり、グローバルデータ線 GDL、/ GDL の電位は、互いに等しい所定の電位となり、プリチャージ電位制御回路 106 によって制御される。

30

【0076】

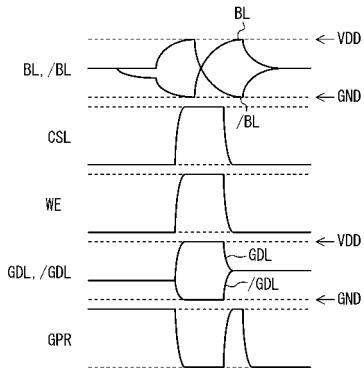

次に、本発明の実施形態 1 に係る半導体記憶装置の書き込み動作について、図 6 のタイミングチャートを参照して説明する。

【0077】

図 6 は、本発明の実施形態 1 に係る半導体記憶装置の書き込み動作時の各信号の電圧レベルの例を示すタイミングチャートである。

40

【0078】

まず、あるメモリセル 101 に接続されたワード線 WL が活性化すると、メモリセル 101 に記憶されたデータがビット線 BL またはビット線 / BL に出力される。そして、活性状態にされたセンスアンプ回路 102 によって、ビット線 BL とビット線 / BL との間の電圧が増幅される。その結果、図 6 に示すように、例えば、増幅後のビット線 BL、/ BL の電位は、それぞれ電圧 VDD、電圧 GND となる。

【0079】

一方、センスアンプ回路 102 によるビット線 BL およびビット線 / BL の電圧の増幅が開始される時、グローバルデータ線プリチャージ信号 GPR は H レベルとなっている。そのため、グローバルデータ線 GDL、/ GDL はプリチャージ回路 105 によってプリチャージされた状態になっている。すなわち、プリチャージ回路 105 の N チャネル型 M

50

OSトランジスタ105a～105cが導通状態であり、グローバルデータ線GDL、/GDLの電位は、後に詳述するようにプリチャージ電位制御回路106によって制御されて互いに等しい所定の範囲の電位となっている。

#### 【0080】

センスアンプ回路102によって、ビット線BLおよびビット線/BLの電位がそれぞれ電圧VDD、電圧GNDまで増幅された後、列選択信号CSLがHレベルにされる。これにより、Nチャネル型MOSトランジスタ103、104が導通状態になり、グローバルデータ線GDLとビット線BLとが接続され、グローバルデータ線/GDLとビット線/BLとが接続される。一方、列選択信号CSLがHレベルになるのと同時に、グローバルデータ線プリチャージ信号GPRがLレベルにされる。また、列選択信号CSLがHレベルになると同時に、ライトイネーブル信号WEがHレベルとなり、ライトバッファ108、109が活性状態となる。これにより、グローバルデータ線GDL、/GDLは入力データDIに基づいた電位となる。図6に示すように、例えば、グローバルデータ線GDL、/GDLの電位は、それぞれ電圧VDD、電圧GNDとなる。そして、ビット線BL、/BLの電位は、電圧VDD-Vt、電圧GNDとなる。そして、メモリセル101のデータが、入力データDIに応じたデータに書き換えられる。

#### 【0081】

データが書き込まれると、次の読み出しに備えるため、ライトイネーブル信号WEがLレベルとなり、ライトバッファ108、109が非活性状態となる。また、列選択信号CSLがLレベルにされ、グローバルデータ線対GDL、/GDLに、ビット線対BL、/BLのデータが転送されない状態になる。その後、グローバルデータ線プリチャージ信号GPRがHレベルにされる。これにより、プリチャージ回路105のNチャネル型MOSトランジスタ105a～105cが導通状態となり、グローバルデータ線GDL、/GDLの電位は、互いに等しい所定の電位となり、プリチャージ電位制御回路106によって制御される。

#### 【0082】

次に、上記のように構成されたプリチャージ電位制御回路106がプリチャージ時にグローバルデータ線GDL、/GDLの電位を制御する動作について説明する。

#### 【0083】

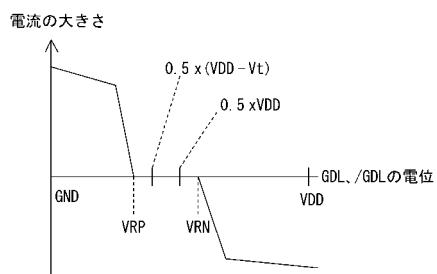

図7は、上記のように構成された半導体記憶装置において、プリチャージ電位制御回路106からプリチャージ回路105に流れる電流の大きさとグローバルデータ線GDL、/GDLの電位との関係を示すグラフである。

#### 【0084】

プリチャージ電位制御回路106では、グローバルデータ線GDL、/GDLの電位が第1の検知電位VRN以下でかつ、第2の検知電位VRP以上の時、Pチャネル型MOSトランジスタ106i、およびNチャネル型MOSトランジスタ106jが両方非導通になり、グローバルデータ線GDL、/GDLにはプリチャージ電位制御回路106から電圧が印加されず、電流が流れない。したがって、電流グローバルデータ線GDL、/GDLの電位が、読み出し動作時のグローバルデータ線GDL、/GDLの電位の平均 $0.5 \times (VDD - Vt)$ である場合であっても、書き込み動作時のグローバルデータ線GDL、/GDLの電位の平均 $0.5 \times VDD$ である場合であっても、プリチャージ時に電流が流れない。つまり、読み出し動作後のプリチャージ時と書き込み動作後のプリチャージ時のいずれの場合にも電流が流れず、電力が消費されない。

#### 【0085】

また、読み出し動作時や書き込み動作時に、グローバルデータ線GDL、/GDLの電位が電圧GND以上で第2の検知電位VRPより低くなっている場合には、Pチャネル型MOSトランジスタ106iが導通し、プリチャージ電位制御回路106からプリチャージ回路105に電流が流れ、グローバルデータ線GDL、/GDLの電位が上がる。逆に、グローバルデータ線GDL、/GDLの電位が第1の検知電位VRNより高く電圧VD以下の場合、Nチャネル型MOSトランジスタ106jが導通し、プリチャージ回路106

10

20

30

40

50

05からプリチャージ電位制御回路106に電流が流れ、グローバルデータ線GDL、/GDLの電位が下がる。これらの動作により、グローバルデータ線GDL、/GDLの電位は、第1の検知電位VRN以下でかつ、第2の検知電位VRP以上の範囲の電位、すなわち $0.5 \times VDD$ に近い電位に保たれる。このように、グローバルデータ線GDL、/GDLの電位が $0.5 \times VDD$ に近いプリチャージ電位に保たれることにより、リードアンプ回路107が適切に動作する。さらに、グローバルデータ線GDL、/GDLに製造上の不具合やばらつき等によってリーク電位が生じる場合でも、電流供給能力の許す限り、グローバルデータ線GDL、/GDLの電位を第1の検知電位VRN以下でかつ、第2の検知電位VRP以上の範囲、すなわち $0.5 \times VDD$ に近い電位に維持することができる、リードアンプ回路107を適切に動作させることができる。

10

## 【0086】

なお、上記の説明では、第1の検知電位VRNは、 $0.5 \times VDD$ より所定分高い電圧、第2の検知電位VRPは $0.5 \times (VDD - Vt)$ より所定分低い電圧に設定されている例を示したが、これに限らない。検知電位は、例えば、リードアンプ回路107の適正動作可能範囲、許容消費電力、またはローバルデータ線GDL、/GDLの電位を変動させる要因等に応じて設定されればよい。

## 【0087】

## 《発明の実施形態2》

本発明の実施形態2の半導体記憶装置は、プリチャージ電位制御回路106に代えて、図8に示すようなプリチャージ電位制御回路206を備えている。

20

## 【0088】

本実施形態のプリチャージ電位制御回路206は、検知電位出力回路206aが、検知電位出力回路106cの構成に加えて印加用高電圧源接続Nチャネル型MOSトランジスタ206bを備えている点で、プリチャージ電位制御回路106と異なっている。

## 【0089】

印加用高電圧源接続Nチャネル型MOSトランジスタ206bは、ドレインとゲートが印加用高電圧源106aに接続され、ソースが抵抗素子106dに接続されている。印加用高電圧源接続Nチャネル型MOSトランジスタ206bは、Nチャネル型MOSトランジスタ103および/または、Nチャネル型MOSトランジスタ104と同じサイズのNチャネル型MOSトランジスタで構成されていてもよい。

30

## 【0090】

本実施形態の半導体記憶装置は、検知電位出力回路206aを除いては、実施形態1の半導体装置と同様の動作を行う。検知電位出力回路206aは、印加用高電圧源接続Nチャネル型MOSトランジスタ206bのソースと上記印加用低電圧源106bとの間の電圧を分圧し、第1の検知電位VRNおよび第2の検知電位VRPとして出力する。

## 【0091】

上記構成により、実施形態1の効果に加え、さらに供給電源VDDのレベルが変わった場合でもプリチャージ時のグローバルデータ線GDL、/GDLは、不必要的電流を流さないように、プリチャージ前のグローバルデータ線GDL、/GDLの平均電位の供給電源VDDに依存した電位、すなわち書き込み時は $0.5 \times VDD$ 、読み出し時は $0.5 \times (VDD - Vt)$ となることから、実施例1に比べ、より広い供給電源VDDの範囲で電流の消費を抑えることが可能となる。またトランジスタの面積は一般的に抵抗素子106dの面積よりも小さいことから、面積も削減可能となる。

40

## 《発明の実施形態3》

本発明の実施形態3の半導体記憶装置は、プリチャージ電位制御回路106に代えて、図9に示すようなプリチャージ電位制御回路306を備えている。

## 【0092】

本実施形態のプリチャージ電位制御回路306は、検知電位出力回路306aが、検知電位出力回路106cの構成に加えて印加用高電圧源接続Pチャネル型MOSトランジスタ306bを備えている点で、プリチャージ電位制御回路106と異なっている。

50

## 【0093】

印加用高電圧源接続 P チャネル型 MOS トランジスタ 306b は、ソースが印加用高電圧源 106a に接続され、ドレインとゲートが抵抗素子 106d に接続されている。

## 【0094】

本実施形態の半導体記憶装置は、検知電位出力回路 306a を除いては、実施形態 1 の半導体装置と同様の動作を行う。検知電位出力回路 306a は、印加用高電圧源接続 P チャネル型 MOS トランジスタ 306b のドレインおよびゲートと印加用低電圧源 106b との間の電圧を分圧し、第 1 の検知電位 VRN および第 2 の検知電位 VRP として出力する。

## 【0095】

上記構成により、実施形態 2 のように印加用高電圧源接続 N チャネル型 MOS トランジスタ 206b のゲートが印加用高電圧源 106a に直接接続される場合よりも、ゲート酸化膜が破壊されにくくなる。また、印加用高電圧源接続 P チャネル型 MOS トランジスタ 306b のドレインおよびゲートの電位の印加用高電圧源 106a の供給電圧に対する依存性が、読み出し動作時のグローバルデータ線 GDL、/GDL の平均電位の印加用高電圧源 106a の供給電圧に対する依存性に近いので、実施例 1 に比べ、より広い供給電圧の範囲で電流の消費を抑えることが可能となる。

## 【0096】

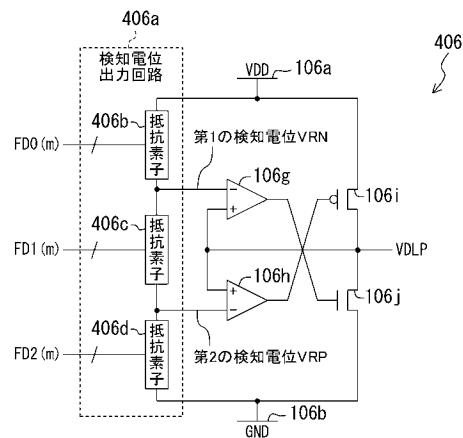

## 《発明の実施形態 4》

本発明の実施形態 4 の半導体記憶装置は、プリチャージ電位制御回路 106 に代えて、

図 10 に示すようなプリチャージ電位制御回路 406 を備えている。

## 【0097】

本実施形態のプリチャージ電位制御回路 406 は、検知電位出力回路 406a が、検知電位出力回路 106c の抵抗素子 106d ~ 106f に代えて、抵抗値を調整する機能を有する抵抗素子 406b ~ 406d を備えている点で、プリチャージ電位制御回路 106 と異なっている。抵抗値を調整する方法としては、ウェハに回路パターンが作り込まれた後にレーザートリミングやアンチヒューズによって抵抗値を調整する方法がある。

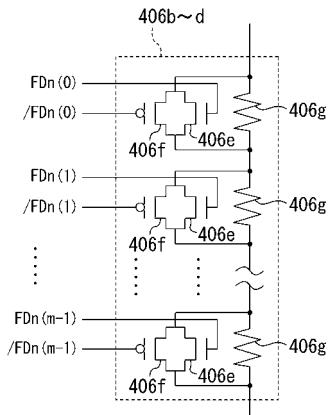

## 【0098】

図 11 は、レーザートリミングやアンチヒューズによって抵抗値が調整される各抵抗素子 406b ~ d の構成例を示す回路図である。

## 【0099】

図 11 に示されるように、各抵抗素子 406b ~ d は、N チャネル型 MOS トランジスタ 406e、P チャネル型 MOS トランジスタ 406f、および抵抗素子 406g から構成される回路を複数備えている。

## 【0100】

N チャネル型 MOS トランジスタ 406e と P チャネル型 MOS トランジスタ 406f のゲートには、ヒューズデータ  $F D_n(k)$ 、および  $/F D_n(k)$  がそれぞれ入力されるようになっている。ここで、n は抵抗素子 406b ~ 406d のうちのいずれの抵抗素子であるかを指定する記号であり、m は抵抗素子 406b ~ 406d のそれぞれに含まれる抵抗素子 406g の数を示す記号である。また、括弧内の k は、複数ある 406g のうちのいずれの 406g であるかを指定する記号である。ヒューズデータ  $F D_n(k)$ 、および  $/F D_n(k)$  の各電位は、ウェハに回路パターンが作り込まれた後に、レーザートリミングやアンチヒューズによって設定されるようになっている。

## 【0101】

上記のプリチャージ電位制御回路 406 を用いた場合、レーザートリミングやアンチヒューズによってヒューズデータ  $F D_n(k)$ 、および  $/F D_n(k)$  の各電位を調整することができる。したがって、ウェハに回路パターンが作り込まれた後に、抵抗素子 406b ~ 406d の抵抗値を調整することによって、検知電位出力回路 406a に適当な第 1 の検知電位 VRN と第 2 の検知電位 VRP とを出力させ、リードアンプ回路 107 を適切に動作させることができる。

## 【0102】

## 《発明の実施形態5》

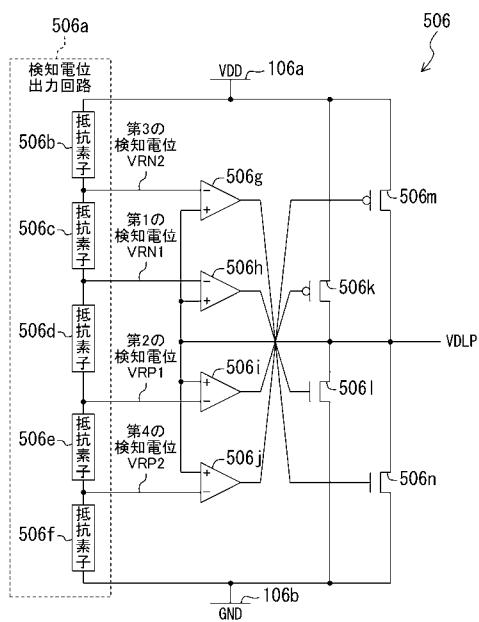

本発明の実施形態5の半導体記憶装置は、プリチャージ電位制御回路106に代えて、図12に示すようなプリチャージ電位制御回路506を備えている。

## 【0103】

本実施形態のプリチャージ電位制御回路506は、印加用高電圧源106a、印加用低電圧源106b、検知電位出力回路506a、差動增幅回路506g～506j、Pチャネル型MOSトランジスタ506k、506m、およびNチャネル型MOSトランジスタ506l、506nを備えている。

## 【0104】

検知電位出力回路506aは、抵抗素子506b～506fを備え、印加用高電圧源106aと印加用低電圧源106bとの間の電圧を分圧し、第1の検知電位VRN1、第2の検知電位VRP1、第3の検知電位VRN2、および第4の検知電位VRP2を出力するようになっている。例えば、VRN1として $0.5 \times VDD$ より所定分低い電圧、VRP1として $0.5 \times (VDD - V_t)$ より所定分高い電圧、VRN2としてVRN1より所定分高い電圧、VRP2としてVRP1より所定分低い電圧を出力するようになっている。

## 【0105】

差動增幅回路506gは、グローバルデータ線GDL、/GDLの電位が第3の検知電位VRN2よりも高い場合には、Nチャネル型MOSトランジスタ506nのゲートに、Nチャネル型MOSトランジスタ506nを導通させる高い電圧を出力するようになっている。逆に、グローバルデータ線GDL、/GDLの電位が第3の検知電位VRN2以下のときには、Nチャネル型MOSトランジスタ506nのゲートに、Nチャネル型MOSトランジスタ506nを非導通にさせる低い電圧を出力するようになっている。

## 【0106】

差動增幅回路506hは、グローバルデータ線GDL、/GDLの電位が第1の検知電位VRN1よりも高い場合には、Nチャネル型MOSトランジスタ506lのゲートに、Nチャネル型MOSトランジスタ506lを導通させる高い電圧を出力するようになっている。逆に、グローバルデータ線GDL、/GDLの電位が第1の検知電位VRN1以下のときには、Nチャネル型MOSトランジスタ506lのゲートに、Nチャネル型MOSトランジスタ506lを非導通にさせる低い電圧を出力するようになっている。

## 【0107】

差動增幅回路506iは、グローバルデータ線GDL、/GDLの電位が第2の検知電位VRP1以上の場合には、Pチャネル型MOSトランジスタ506kのゲートに、Pチャネル型MOSトランジスタ506kを非導通にさせる高い電圧を出力するようになっている。逆に、グローバルデータ線GDL、/GDLの電位が第2の検知電位VRP1より低いときには、Pチャネル型MOSトランジスタ506kのゲートに、Pチャネル型MOSトランジスタ506kを導通させる低い電圧を出力するようになっている。

## 【0108】

差動增幅回路506jは、グローバルデータ線GDL、/GDLの電位が第4の検知電位VRP2以上の場合には、Pチャネル型MOSトランジスタ506mのゲートに、Pチャネル型MOSトランジスタ506mを非導通にさせる高い電圧を出力するようになっている。逆に、グローバルデータ線GDL、/GDLの電位が第4の検知電位VRP2より低いときには、Pチャネル型MOSトランジスタ506mのゲートに、Pチャネル型MOSトランジスタ506mを導通させる低い電圧を出力するようになっている。

## 【0109】

また、Pチャネル型MOSトランジスタ506mのサイズはPチャネル型MOSトランジスタ506kのサイズより大きく、Nチャネル型MOSトランジスタ506nのサイズはNチャネル型MOSトランジスタ506lのサイズより大きくなるように構成される。

## 【0110】

10

20

30

40

50

本実施形態の半導体記憶装置は、プリチャージ電位制御回路 506 を除いては、実施形態 1 の半導体装置と同様の動作を行う。

【0111】

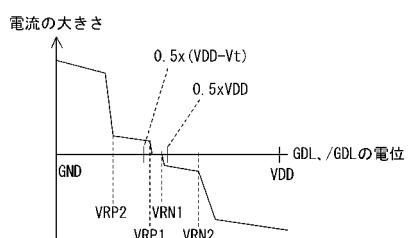

次に、上記のように構成されたプリチャージ電位制御回路 506 がプリチャージ時にグローバルデータ線 GDL、/GDL の電位を制御する動作について、図 13 を参照して説明する。

【0112】

図 13 は、本実施形態の半導体記憶装置において、プリチャージ電位制御回路 506 からプリチャージ回路 105 に流れる電流の大きさとグローバルデータ線 GDL、/GDL の電位との関係を示すグラフである。

10

【0113】

プリチャージ電位制御回路 506 では、グローバルデータ線 GDL、/GDL の電位が第 3 の検知電位 VRN2 より高い時、N チャネル型 MOS トランジスタ 5061、506n が両方導通し、プリチャージ回路 105 からプリチャージ電位制御回路 506 に電流が流れ、グローバルデータ線 GDL、/GDL の電位が下がる。

【0114】

グローバルデータ線 GDL、/GDL の電位が第 3 の検知電位 VRN2 以下でかつ、第 1 の検知電位 VRN1 より高い時、N チャネル型 MOS トランジスタ 5061 だけが導通し、プリチャージ回路 105 からプリチャージ電位制御回路 506 に電流が流れ、グローバルデータ線 GDL、/GDL の電位が下がる。この時、N チャネル型 MOS トランジスタ 5061 だけが導通しているので、N チャネル型 MOS トランジスタ 5061、506n が両方導通している場合より、流れる電流は小さく、単位時間あたりの電力消費量は少ない。

20

【0115】

グローバルデータ線 GDL、/GDL の電位が第 4 の検知電位 VRP2 より低い時、P チャネル型 MOS トランジスタ 506k、506m が両方導通し、プリチャージ電位制御回路 106 からプリチャージ回路 105 に電流が流れ、グローバルデータ線 GDL、/GDL の電位が上がる。

【0116】

グローバルデータ線 GDL、/GDL の電位が第 4 の検知電位 VRP2 以上でかつ、第 2 の検知電位 VRP1 より低い時、P チャネル型 MOS トランジスタ 506k だけが導通し、プリチャージ電位制御回路 106 からプリチャージ回路 105 に電流が流れ、グローバルデータ線 GDL、/GDL の電位が上がる。この時、P チャネル型 MOS トランジスタ 506k だけが導通しているので、P チャネル型 MOS トランジスタ 506k、506m が両方導通している場合より、流れる電流は小さく、単位時間あたりの電力消費量も少ない。

30

【0117】

グローバルデータ線 GDL、/GDL の電位が第 1 の検知電位 VRN1 以下でかつ、第 2 の検知電位 VRP1 以上の時、P チャネル型 MOS トランジスタ 506k、506m、および N チャネル型 MOS トランジスタ 5061、506n がすべて非導通になり、グローバルデータ線 GDL、/GDL にはプリチャージ電位制御回路 506 から電圧が印加されず、電流が流れない。

40

【0118】

上記のような動作により、プリチャージ開始から十分な時間が経過すると、電流グローバルデータ線 GDL、/GDL の電位は、第 1 の検知電位 VRN1 以下でかつ、第 2 の検知電位 VRP1 以上の電位に保たれる。このように、グローバルデータ線 GDL、/GDL の電位が第 1 の検知電位 VRN1 以下でかつ、第 2 の検知電位 VRP1 以上の電位、すなわち  $0.5 \times VDD$  に近い電位に保たれるので、リードアンプ回路 107 が適切に動作する。さらに、グローバルデータ線 GDL、/GDL に製造上の不具合やばらつき等によってリーク電位が生じる場合でも、電流供給能力の許す限り、グローバルデータ線 GDL

50

、 / G D L の電位を第 1 の検知電位 V R N 1 以下でかつ、第 2 の検知電位 V R P 1 以上の範囲、すなわち  $0.5 \times V_{DD}$  に近い電位に維持することができるので、リードアンプ回路 107 を適切に動作させることができる。

【 0 1 1 9 】

また、電流グローバルデータ線 G D L 、 / G D L の電位が、読み出し動作後、読み出し動作時のグローバルデータ線 G D L 、 / G D L の電位の平均  $0.5 \times (V_{DD} - V_t)$  となっている場合、電流グローバルデータ線 G D L 、 / G D L の電位が第 2 の検知電位 V R P 1 になるまでは電流が流れるが、第 2 の検知電位 V R P 1 になった後は電流は流れない。一方、電流グローバルデータ線 G D L 、 / G D L の電位が、書き込み動作後、書き込み動作時のグローバルデータ線 G D L 、 / G D L の電位の平均  $0.5 \times V_{DD}$  となっている場合、電流グローバルデータ線 G D L 、 / G D L の電位が第 1 の検知電位 V R N 1 になるまでは電流が流れるが、第 1 の検知電位 V R N 1 になった後は電流は流れない。このように、電流グローバルデータ線 G D L 、 / G D L が所定の範囲の電位になれば電圧が印加されなくなって電流が流れなくなるので、所定の一点の電位となるまで電流が流れる従来の構成に比べ、各プリチャージ時に流れる電流量の平均は小さくなり、消費電力が低減される。

【 0 1 2 0 】

また、グローバルデータ線 G D L 、 / G D L の電位が第 3 の検知電位 V R N 2 より高い時、第 3 の検知電位 V R N 2 以下でかつ第 1 の検知電位 V R N 1 より高い時よりも、大きな電流が流れ、グローバルデータ線 G D L 、 / G D L の電位はより高速に降下する。同様に、グローバルデータ線 G D L 、 / G D L の電位が第 4 の検知電位 V R P 2 より低い時は、第 4 の検知電位 V R P 2 以上でかつ第 2 の検知電位 V R P 1 より低い時よりも、大きな電流が流れ、グローバルデータ線 G D L 、 / G D L の電位はより高速に上昇する。

【 0 1 2 1 】

また、プリチャージ時間を変化させることによって、リードアンプ 107 の動作の安定性や消費電力を調整することができる。例えば、グローバルデータ線 G D L 、 / G D L の電位がプリチャージ終了時に必ず第 1 の検知電位 V R N 1 以下で第 2 の検知電位 V R P 1 以上の範囲になるようにプリチャージ時間を長くすることによって、リードアンプ回路 107 により安定した動作をさせることができる。逆に、グローバルデータ線 G D L 、 / G D L の電位を第 3 の検知電位 V R N 2 以下で第 4 の検知電位 V R P 2 以上の範囲に維持しておけば十分な場合、プリチャージ時間をある程度短くすることによって消費電力を低減することができる。つまり、プリチャージ時間が、第 1 の検知電位 V R N 1 以下で第 2 の検知電位 V R P 1 以上の電位までグローバルデータ線 G D L 、 / G D L の電位が遷移するために必要な時間よりも短い時間であった場合、プリチャージ終了時にグローバルデータ線 G D L 、 / G D L の電位が第 1 の検知電位 V R N 1 以下で第 2 の検知電位 V R P 1 以上の範囲になるとは限らないが、電流が流れる時間が短くなり、消費電力が低減する。

【 産業上の利用可能性 】

【 0 1 2 2 】

本発明に係る半導体記憶装置は、プリチャージ時の消費電流が低減するという効果を有し、例えば、ダイナミックランダムアクセスメモリ ( D R A M ) などの半導体記憶装置等として有用である。

【 図面の簡単な説明 】

【 0 1 2 3 】

【 図 1 】本発明の実施形態 1 に係る半導体記憶装置の構成を示す回路図である。

【 図 2 】本発明の実施形態 1 に係るプリチャージ電位制御回路 106 の構成を示す回路図である。

【 図 3 】本発明の実施形態 1 に係る半導体記憶装置の第 1 の検知電位 V R N 、および第 2 の検知電位 V R P がどのように設定されるかを示す説明図である。

【 図 4 】本発明の実施形態 1 に係るリードアンプ回路 107 の構成を示す回路図である。

【 図 5 】本発明の実施形態 1 に係る半導体記憶装置の読み出し動作時の各信号の電圧レベ

10

20

30

30

40

50

ルの例を示すタイミングチャートである。

【図6】本発明の実施形態1に係る半導体記憶装置の書き込み動作時の各信号の電圧レベルの例を示すタイミングチャートである。

【図7】本発明の実施形態1に係る半導体記憶装置において、プリチャージ電位制御回路106からプリチャージ回路105に流れる電流の大きさとグローバルデータ線GDL、/GDLの電位との関係を示すグラフである。

【図8】本発明の実施形態2に係るプリチャージ電位制御回路206の構成を示す回路図である。

【図9】本発明の実施形態3に係るプリチャージ電位制御回路306の構成を示す回路図である。

【図10】本発明の実施形態4に係るプリチャージ電位制御回路406の構成を示す回路図である。

【図11】本発明の実施形態4に係るレーザートリミングやアンチヒューズによって抵抗値が調整される各抵抗素子406b～dの構成例を示す回路図である。

【図12】本発明の実施形態5に係るプリチャージ電位制御回路506の構成を示す回路図である。

【図13】本発明の実施形態5に係る半導体記憶装置において、プリチャージ電位制御回路506からプリチャージ回路105に流れる電流の大きさとグローバルデータ線GDL、/GDLの電位との関係を示すグラフである。

【符号の説明】

【0124】

|                |                          |

|----------------|--------------------------|

| 101            | メモリセル                    |

| 102            | センスアンプ回路                 |

| 103・104        | Nチャネル型MOSトランジスタ          |

| 105            | プリチャージ回路                 |

| 105a～105c      | Nチャネル型MOSトランジスタ          |

| 106            | プリチャージ電位制御回路             |

| 106a           | 印加用高電圧源                  |

| 106b           | 印加用低電圧源                  |

| 106c           | 検知電位出力回路                 |

| 106d～106f      | 抵抗素子                     |

| 106g・106h      | 差動増幅回路                   |

| 106i           | Pチャネル型MOSトランジスタ          |

| 106j           | Nチャネル型MOSトランジスタ          |

| 107            | リードアンプ回路                 |

| 107a・107b      | リードアンプ駆動用電圧源             |

| 107c・107e～107h | Nチャネル型MOSトランジスタ          |

| 107d・107i・107j | Pチャネル型MOSトランジスタ          |

| 108・109        | ライトバッファ                  |

| 110            | インバータ                    |

| 206            | プリチャージ電位制御回路             |

| 206a           | 検知電位出力回路                 |

| 206b           | 印加用高電圧源接続Nチャネル型MOSトランジスタ |

| 306            | プリチャージ電位制御回路             |

| 306a           | 検知電位出力回路                 |

| 306b           | 印加用高電圧源接続Pチャネル型MOSトランジスタ |

| 406            | プリチャージ電位制御回路             |

| 406a           | 検知電位出力回路                 |

| 406b～406d      | 抵抗素子                     |

| 406e           | Nチャネル型MOSトランジスタ          |

10

20

30

40

50

4 0 6 f P チャネル型 M O S トランジスタ

4 0 6 g 抵抗素子

5 0 6 プリチャージ電位制御回路

5 0 6 a 検知電位出力回路

5 0 6 b ~ 5 0 6 f 抵抗素子

5 0 6 g ~ 5 0 6 j 差動増幅回路

5 0 6 k ~ 5 0 6 m P チャネル型 M O S トランジスタ

5 0 6 l ~ 5 0 6 n N チャネル型 M O S トランジスタ

【図 1】

【図 2】

【図 3】

【図4】

【図5】

【図8】

【図6】

【図7】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 折笠 憲一

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 5M024 AA04 BB15 BB29 BB37 DD13 FF02 FF23 PP01 PP02 PP03

PP07 PP09 PP10