(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294842

(P2005-294842A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

H01L 25/065

H01L 21/301

H01L 21/60

H01L 25/07

H01L 25/18

F 1

H01L 25/08

H01L 21/60

H01L 21/78

H01L 21/78

Z

301N

B

A

テーマコード(参考)

5 F 0 4 4

審査請求 未請求 請求項の数 34 O L (全 19 頁)

(21) 出願番号 特願2005-103706 (P2005-103706)

(22) 出願日 平成17年3月31日 (2005.3.31)

(31) 優先権主張番号 2004-022666

(32) 優先日 平成16年4月1日 (2004.4.1)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeongtong-gu, Suwon-si

Gyeonggi-do, Republic

of Korea

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100108453

弁理士 村山 靖彦

最終頁に続く

(54) 【発明の名称】段差型ダイを有する半導体パッケージとその製造方法

(57) 【要約】 (修正有)

【課題】 段差型ダイを有する半導体パッケージを提供する。

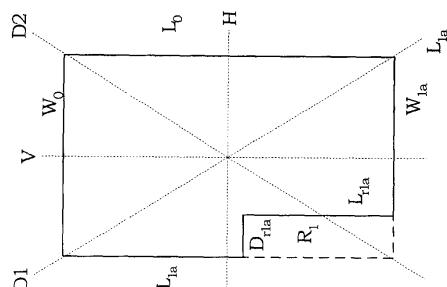

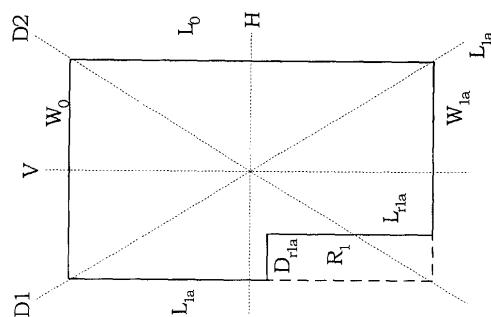

【解決手段】 半導体ダイは、最大幅 $W_0$ 、最大長さ $L_0$ 及び第1凹部 $R_1$ を有し、 $W_0$ において第1凹部深さ $D_{r1a}$ 減少されて第1短軸幅 $W_{1a}$ が形成され、 $L_0$ において第1凹部長さ $L_{r1a}$ 減少されて第1短軸長さ $L_{1a}$ が形成される。

【選択図】 図5 A

## 【特許請求の範囲】

## 【請求項 1】

変形された矩形の外周を有する半導体ダイにおいて、

最大幅  $W_0$  と、

最大長さ  $L_0$  と、

第 1 凹部

とを有し、

前記  $W_0$  において第 1 凹部深さ  $D_{r1a}$  減少されて第 1 短軸幅  $W_{1a}$  が形成され、前記  $L_0$  において第 1 凹部長さ  $L_{r1a}$  減少されて第 1 短軸長さ  $L_{1a}$  が形成されることを特徴とする半導体ダイ。

10

## 【請求項 2】

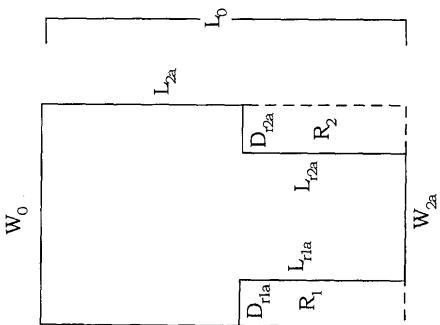

第 2 凹部をさらに有し、

前記  $W_0$  において第 2 凹部深さ  $D_{r2a}$  減少されて第 2 幅  $W_{2a}$  が形成され、前記  $L_0$  において第 2 凹部長さ  $L_{r2a}$  減少されて第 2 長さ  $L_{2a}$  が形成されることを特徴とする請求項 1 に記載の半導体ダイ。

## 【請求項 3】

偶数個  $N$  の凹部をさらに有し、

前記  $W_0$  において  $N$  番目凹部深さ  $D_{rNa}$  に減少されて第  $N$  幅  $W_{Na}$  が形成され、前記  $L_0$  が  $N$  番目凹部長さ  $L_{rNa}$  に減少されて第  $N$  長さ  $L_{Na}$  が形成されることを特徴とする請求項 2 に記載の半導体ダイ。

20

## 【請求項 4】

前記  $N$  個の凹部は、中心縦軸を基準にして対称に配列することを特徴とする請求項 3 に記載の半導体ダイ。

## 【請求項 5】

前記  $N$  個の凹部は、中心水平軸を基準にして対称に配列することを特徴とする請求項 3 に記載の半導体ダイ。

## 【請求項 6】

前記  $N$  個の凹部は、中心縦軸を基準にして対称に配列することを特徴とする請求項 5 に記載の半導体ダイ。

30

## 【請求項 7】

前記  $N$  個の凹部は、第 1 対角線軸を基準にして対称に配列することを特徴とする請求項 3 に記載の半導体ダイ。

## 【請求項 8】

前記凹部は、前記半導体ダイの角を取り囲むことを特徴とする請求項 1 に記載の半導体ダイ。

## 【請求項 9】

前記凹部は、前記半導体ダイの第 1 面に沿って中間地点に形成することを特徴とする請求項 1 に記載の半導体ダイ。

## 【請求項 10】

前記第 1 凹部及び第 2 凹部は、互いに噛み合って前記半導体ダイの一方の角を取り囲むことを特徴とする請求項 2 に記載の半導体ダイ。

40

## 【請求項 11】

前記第 1 凹部及び第 2 凹部は、前記半導体ダイの周辺領域により互いに離隔されることを特徴とする請求項 2 に記載の半導体ダイ。

## 【請求項 12】

前記第 1 凹部は、前記半導体ダイの第 1 角を取り囲み、

前記第 2 凹部は、前記半導体ダイの第 1 角と異なる第 2 角を取り囲むことを特徴とする請求項 2 に記載の半導体ダイ。

## 【請求項 13】

前記第 1 角及び第 2 角は、対角線に向かい合っていることを特徴とする請求項 12 に記

50

載の半導体ダイ。

【請求項 1 4】

前記第1角及び第2角は、前記半導体ダイの一方面の両先端に位置することを特徴とする請求項12に記載の半導体ダイ。

【請求項 1 5】

外周に凹部が形成された複数のダイを半導体ウエハに形成する段階と、

前記ウエハにおいて個別ダイを分離する段階と

を有することを特徴とする半導体素子製造方法。

【請求項 1 6】

前記分離段階は、前記ダイの外周面をレーザスクライピングしてウエハで脆弱な部分を形成する段階と、

前記脆弱な部分に沿って隣接するダイから個別ダイを分離する段階と、

を有することを特徴とする請求項15に記載の半導体素子製造方法。

【請求項 1 7】

前記分離段階は、前記ダイの外周面の外側において前記凹部に近接するするウエハの上部を除去して前記ウエハの活性面に開放口を形成する段階と、

前記活性面の反対面においてウエハの下部を除去して上下部がウエハの元来の厚さと少なくとも同じくする段階と、

ダイ間の切断線に沿って前記ウエハの残り部分を除去する段階と、

を有することを特徴とする請求項15に記載の半導体素子製造方法。

【請求項 1 8】

半導体ウエハに複数のダイを形成する段階は、隣接する少なくとも二つのダイの凹部が相互補完的でかつダイの外周面に沿って一定間隔に離隔されるようにダイを配列する段階を含むことを特徴とする請求項15に記載の半導体素子製造方法。

【請求項 1 9】

半導体ウエハに複数のダイを形成する段階は、隣接する少なくとも二つのダイの凹部が完全に相互補完的でなくダイの外周面の隣接部分に沿って互いに異なる地点から互いに異なる間隔に離隔されるようにダイを配列する段階を含むことを特徴とする請求項15に記載の半導体素子製造方法。

【請求項 2 0】

半導体ウエハに複数のダイを形成する段階は、凹部と境界をなすダイの外周面の一部にはボンドパッドが形成されないように複数のボンドパッドを、ダイの外周面に隣接して配置させる段階を含むことを特徴とする請求項15に記載の半導体素子製造方法。

【請求項 2 1】

前記複数のボンドパッドは、ダイの外周面の一直線に沿って配列することを特徴とする請求項20に記載の半導体素子製造方法。

【請求項 2 2】

接触部を有する基板と、

外周面に凹部を有する第1半導体ダイと、

を備える半導体素子パッケージにおいて、

前記接触部が凹部を介して露出するように前記基板に第1半導体ダイを実装することを特徴とする半導体素子パッケージ。

【請求項 2 3】

前記基板は下部半導体ダイであって、前記接触部は少なくとも一つのボンドパッドを備えて、

複数のボンドパッドは、前記第1半導体ダイの活性面に形成することを特徴とする請求項22に記載の半導体素子パッケージ。

【請求項 2 4】

前記第1半導体ダイの活性面に形成されるボンドパッドは、延長領域のみに位置することを特徴とする請求項23に記載の半導体素子パッケージ。

10

20

30

40

50

**【請求項 25】**

接触面を有する基板と、

外周面に凹部が形成された第1半導体ダイと、

を備える半導体素子パッケージにおいて、

前記接触部が凹部を介して露出するように前記基板に第1半導体ダイが実装されることを特徴とする請求項22に記載の半導体素子パッケージ。

**【請求項 26】**

基板を用意する段階と、

前記基板に複数の第1ボンドパッドを有する第1半導体ダイを実装する段階と、

外周面に第1凹部が形成された第2半導体ダイを形成する段階と、

前記複数の第1ボンドパッドが前記第1凹部を介して露出するように前記第1半導体ダイ上に前記第2半導体ダイを実装する段階と、

を有することを特徴とする半導体素子パッケージ製造方法。

**【請求項 27】**

変形された矩形の外周面に第2凹部が変形されている第3半導体素子を形成する段階と、

前記第2半導体素子の活性面に形成されている複数の第2ボンドパッドが、前記第2凹部を介して露出するように前記第2半導体ダイ上に前記第3半導体ダイを実装する段階と、

をさらに有することを特徴とする半導体素子パッケージ製造方法。

**【請求項 28】**

前記第1ボンドパッドと第2ボンドパッド及び基板を電気的に接続する段階をさらに有することを特徴とする請求項27に記載の半導体素子パッケージ製造方法。

**【請求項 29】**

前記第3半導体ダイの活性面に形成されている複数の第3ボンドパッドと基板とを電気的に接続する段階をさらに有することを特徴とする請求項28に記載の半導体素子パッケージ製造方法。

**【請求項 30】**

前記第1半導体ダイ、第2半導体ダイ及び第3半導体ダイは、実質的に同じ構造を有し、前記第2半導体ダイは、前記第1半導体ダイ及び第3半導体ダイを基準にして約180°回転されることを特徴とする請求項29に記載の半導体素子パッケージ製造方法。

**【請求項 31】**

前記第1半導体ダイ、第2半導体ダイ及び第3半導体ダイは、実質的に同じ構造を有し、前記第2半導体ダイは、前記第1半導体ダイ及び第3半導体ダイを基準にして約90°回転されることを特徴とする請求項29に記載の半導体素子パッケージ製造方法。

**【請求項 32】**

少なくとも二つの半導体ダイを備える半導体素子パッケージにおいて、

外周面に凹部が形成されており、基板に実装される第1半導体ダイと、

前記凹部内に位置するように前記第1半導体ダイと水平に実装され第2半導体ダイと、

を備えることを特徴とする半導体素子パッケージ。

**【請求項 33】**

前記第2半導体ダイは、実質的に前記凹部内に位置することを特徴とする請求項32に記載の半導体素子。

**【請求項 34】**

前記第2半導体ダイは、前記凹部内に完全に位置することを特徴とする請求項32に記載の半導体素子。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体集積回路チップと、それを用いたパッケージング組立に関し、さらに

10

20

30

40

50

詳細には変形された矩形の外周面を有する集積回路チップまたはダイ及びそれを一つ以上用いて具現された関連チップまたはマルチチップパッケージに関する。

#### 【背景技術】

##### 【0002】

一般に、半導体パッケージの製造工程には、半導体ウエハ加工、パッケージ組立及びテスト等の三つに大別することができる。ウエハ加工工程は、熱処理、イオン注入、蒸着、平坦化、フォトリソグラフィ及びエッチングなどのようなベア半導体ウエハや基板の中または表面に複数の集積回路素子を作る上必要なあらゆる工程を含む。

##### 【0003】

当該工程が完了すると、パラメータ及び/または機能テストを行った後ウエハダイシング工程に移行する。この工程の間、半導体ウエハの背面が練磨され厚さが減少し、切断線に沿って個別集積回路チップに分離される。このため、ウエハダイシング工程のことを、例えば、ウエハソーリングまたはウエハスクリーピング工程ともいう。

##### 【0004】

一旦ウエハから個別集積回路チップが分離されると、それぞれの個別集積回路チップをリードフレームの等の基板に取り付けるといったパッケージ組立工程を行うが、基板は、集積回路チップ、回路基板、またはソケットと連結するための外部連結構造を含む。直接回路チップ、基板の一部、及びチップと基板との間の電気的連結部を封止する封止部を形成し、パッケージの抵抗性を増加させることによって、外部による機械的損傷や汚染から保護する。パッケージは、一つ以上の集積回路チップを有するが、マルチチップパッケージの場合、実質的に同じチップを含むか或いは多様な機能や大きさを有するチップを含むことができる。例えば、マルチチップパッケージは、一つのパッケージ内にマイクロプロセッサー集積回路チップとそれと連結されているメモリチップの両方を含んで構成される。

##### 【0005】

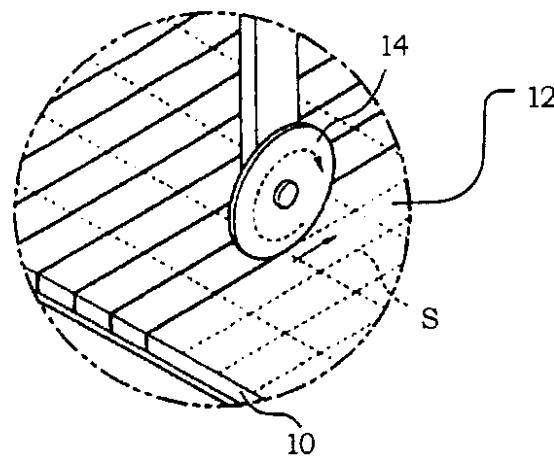

現在、半導体チップの大部分は、図1に示すように、矩形を有するが、これは、従来のウエハダイシング方法に由来する。従来の一般的なウエハダイシング装置は、ダイシングブレード(dicing blade)14を用いてウエハ10上に形成された複数の半導体チップ12間の切断線Sに沿って移動する。ダイシングブレード14の切断長さが集積回路チップ12の表面長さと略同じであることから、従来のダイシング装置では、単純で一定した矩形にしか切断できず、例えば、三角や平行四辺形の形態がなかった。

##### 【0006】

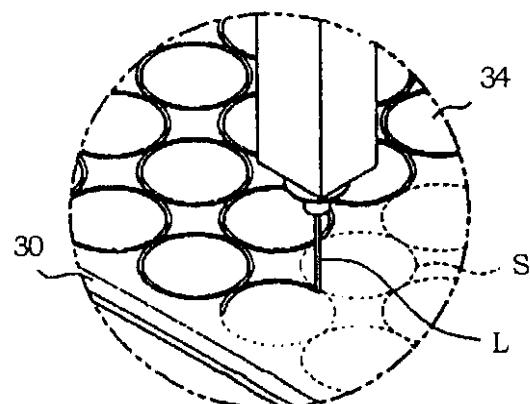

また、従来のダイシングブレード使用による収率及び/または信頼性を減少させる原因となるチッピング(chipping)といった問題点を解決するために、レーザスクリーピングを用いたダイシング方法が米国特許出願第10/805、212号に開示されている。さらに、東京精密株式会社のレーザスクリーピング装置であるマホウダイシング装置(Mahoh dicing machine)は、従来のソーリングによるウエハ表面の損傷を減す非接触方法を用いて半導体ウエハをダイシングする。半導体ウエハ表面にレーザダイのレーザビームを照射して多様な形態の集積回路チップを切断する。これにより、従来のソーリング方法における研磨材によるウエハの一部を除去する際発生するチッピング等の損傷を減らすことができる。

##### 【0007】

集積回路チップの矩形は、具現される半導体パッケージの形態も限定しているためパッケージもやはり矩形が圧倒的に多い。このために、複数のパッケージが回路基板と同じ基板に実装されるとき、パッケージの実装密度が減少するとともに集積回路チップの実装に必要な基板の大きさが増大する。

##### 【0008】

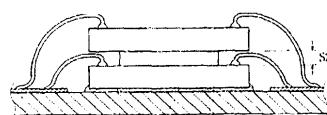

また、集積回路チップの矩形は、マルチチップパッケージの小型・薄型形状にすることが困難である。例えば、二つの集積回路チップが積層されると、上部チップの大きさが下部チップのボンドパッドを覆う程度であれば、集積回路チップ間にスペーサが介在され下部チップのボンドパッドに接近可能な空間を作らなければならない。しかし、図3Aに示

10

20

30

40

50

すように、スペーサの介在により積層チップの厚さがS<sub>2</sub>にまで増大してしまう。

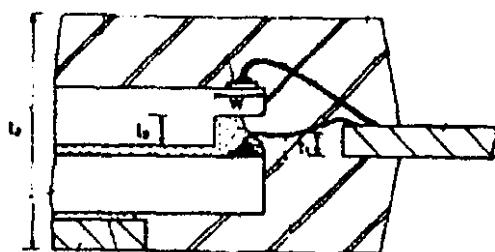

【0009】

上下部チップ間の干渉を解決するための方法の一つとして、図3Bに示すように、上部チップの下部面端部を除去して下部チップのボンドパッドにワイヤボンディングできる大きさの五目型開放部を形成する方法がある。しかし、この方法は、上部チップの一部が薄形化されてしまうことから、ワイヤボンディングの際弱くなつた箇所が折れたりクラックが発生したりする恐れがある。

【0010】

下部チップのボンドパッドを覆う方法の一つとして、下部チップを基準にして上部チップを回転させて対角方向に実装し、下部チップにワイヤボンディング領域を露出する方法がある。この方法は、チップの一部が機械的損傷の危険に晒されないものの下部チップのボンドパッドに接近性を向上させるために、大きさ及び方向の異なるチップを用いなければならないという制限があり、さらにオフセット配列のために装置及び/または制御装置を使用しなければならない問題点があった。

【発明の開示】

【発明が解決しようとする課題】

【0011】

本発明の目的は、一つ以上の凹部を有しながら外周面が矩形以外の多様な形態の集積回路チップを提供し、それに具現されるチップ及びマルチチップパッケージを提供することにある。

【課題を解決するための手段】

【0012】

上記目的を達成するために、本発明は、最大幅W<sub>0</sub>と最大長さL<sub>0</sub>を含む変形された矩形の外周を有する半導体ダイを提供する。一面に沿って角まで凹部が形成されており、元来の幅から第1凹部深さD<sub>r1a</sub>に減少されて第1部方幅W<sub>1a</sub>を形成し、元来の長さL<sub>0</sub>から第1凹部長さL<sub>r1a</sub>に減少されて第1部方長さL<sub>1a</sub>が形成される。本発明による集積回路チップにおいて凹部の数、大きさ及び位置によって部分端部と大きさが形成される。また、凹部は、矩形の基本構造に対して非対称に配列されたり、垂直(中心縦軸)、水平(中心水平軸)、または対角線軸を基準として対称に配列され得る。

【0013】

本発明に係る上記のような外周面を有する集積回路チップの製造方法は、凹部を有する複数個のダイを半導体ウエハに形成した後そのウエハから個別ダイを分離する段階を含む。個別ダイに分離する段階は、ダイの外周面をレーザスクライビングしてウエハに脆弱な部分を形成した後、その脆弱部分に沿って隣接したダイから個別ダイを分離する段階を含む。さらに他の実施例において、個別ダイに分離する段階は、ダイの外周面端で凹部近方に位置するウエハの上部を取り除いてウエハの活性面に開口部を形成する段階と、活性面の反対の背面を一部除去して上下部の厚さがウエハの元来の厚さと少なくとも同じくする段階、及びダイ間の切断線に沿ってウエハの残り部分を除去する段階を含む。

【0014】

本発明に係る凹部を有するダイは、半導体ウエハに多様な構造で配列され得る。例えば、少なくとも二つのダイの凹部が相互補完的であるか、または外周面に沿って実質的に一定距離を置いて配置され得る。或いは少なくとも二つのダイの凹部が相互補完的でないことも、またダイの外周面の隣接部分に沿って互いに異なる地点から実質的に互に異なる距離へと離隔され得る。

【0015】

集積回路チップに形成された変形された外周面形態だけではなく、ボンドパッドの構造も変形できるので、実施例に示す通り、凹部と近い外周面にボンドパッドを形成させないこともできる。また、ボンドパッドは、外周面に沿って実質的に垂直一列に配列され得る。

【0016】

10

20

30

40

50

本発明は、前述した凹部を有する集積回路チップを備えるマルチチップパッケージを提供する。すなわち、パッケージは、接触部を備える基板と、外周面に凹部が形成された第1半導体ダイとを備えて、接触部が凹部を介して露出するように第1半導体ダイが基板に実装される。他の実施形態によるパッケージにおいて、下部半導体ダイは、基板として役割を果たし、少なくとも一つのボンドパッドを持つ接触部及び第1半導体ダイの活性面に形成された複数のボンドパッドを備える。さらに他の実施形態によるパッケージにおいて、接触面を有する基板、及び外周面に凹部が形成された第1半導体ダイを備えて、接触部が凹部を介して露出するように第1半導体ダイが基板に実装される。

### 【0017】

本発明は、また前述したパッケージを製造する方法を提供する。すなわち、基板を準備する段階と、基板に複数の第1ボンドパッドを備えた第1半導体ダイを実装する段階と、外周面に第1凹部が形成された第2半導体ダイを形成する段階と、複数の第1ボンドパッドが第1凹部を介して露出するように第1半導体ダイ上に第2半導体ダイを実装する段階とを含む。パッケージ製造方法は、外周面に第2凹部が形成された第3半導体素子を形成する段階と、第2半導体素子の活性面に形成された複数の第2ボンドパッドが第2凹部を介して露出するように第2半導体ダイ上に第3半導体ダイを実装する段階をさらに含むことができる。パッケージ製造方法は、第1ボンドパッド及び第2ボンドパッドと基板とを電気的に接続する段階及び/または第3半導体ダイの活性面に形成された複数の第3ボンドパッドと基板とを電気的に接続する段階をさらに含むことができる。

### 【0018】

本発明の実施形態に係るパッケージ製造方法は、第1半導体ダイ、第2半導体ダイ及び第3半導体ダイを実質的に同じ構造で用意する段階と、第2半導体ダイを第1半導体ダイ及び第3半導体ダイに対して約180°回転させるダイ組立段階とを含む。パッケージ製造方法は、実質的に同じ構造の第1半導体ダイ、第2半導体ダイ及び第3半導体ダイを用意する段階と、第2半導体ダイを第1半導体ダイ及び第3半導体ダイに対して約90°回転させるダイ組立段階とを含む。

### 【0019】

本発明の実施形態に係るパッケージ構造において、外周面に凹部を有し基板に実装される第1半導体ダイと、第1半導体ダイに対して水平に実装される第2半導体ダイとを備えて、第2半導体ダイは、凹部内に位置する。本発明の実施形態に係る集積回路チップ構造において、第2半導体ダイは、凹部内に実質的に位置するかまたは凹部内に完全に位置することを特徴とする。

### 【発明の効果】

### 【0020】

本発明は、多様な外周面とボンドパッド構造を有する集積回路チップを用いることによって表面領域を低減できるとともに基板又は回路基板に対する実装密度を向上させることができる。

### 【発明を実施するための最良の形態】

### 【0021】

以下、本発明の実施形態について添付図面を参照しながらさらに詳細に説明する。

### 【0022】

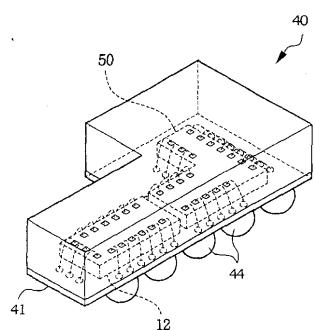

図4は、本発明の実施形態におけるマルチチップパッケージ40を示す図で、従来の矩形の第1集積回路チップ12と本発明において変形された外側部を有する第2集積回路チップ50とが基板41に実装される構造を有する。基板41は、集積回路チップと回路基板及びソケットとその他フィックスチャーとを繋ぐためにソルダボール44のような外部接続構造を有する。

### 【0023】

図5に示すように、本発明における集積回路チップは、端部に一つ以上の凹部R1...Rnが形成され従来の集積回路チップとは相違する。凹部は外周面と平行に形成された端部RD1、RL1を有する。少なくとも一つの凹部は少なくとも一つの端部に形成され

10

20

30

40

50

、隣接した凹部同士に交差して L 字に具現され得る。集積回路チップ、凹部の配置及び方向は、対角線軸 D 1 、 D 2 と平行線軸 V 、 H を基準にしてなっており、一つ以上の軸を基準にして対称に配置される。

【 0 0 2 4 】

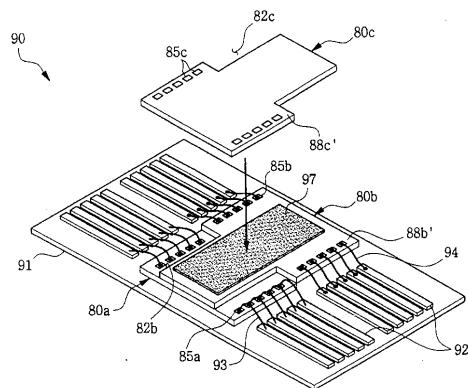

図 6 及び図 7 に示すように、マルチチップ積層パッケージ 9 0 は、チップ実装領域周囲で複数のリードまたは伝導性パターンが形成される基板 9 1 を備える。複数の集積回路チップ 8 0 a 、 8 0 b 、 8 0 c は、基板のチップ実装領域に順次に積層される。各々の集積回路チップには一端の両側に一对の凹部 8 2 a 、 8 2 b 、 8 2 c が形成されている。集積回路チップの他端の両側は元来の幅を維持しながら複数のボンドパッド 8 8 a 、 8 8 b 、 8 8 c が形成されており、集積回路チップとリード 9 2 は、ボンディングワイヤ 9 3 、 9 4 、 9 5 と連結する。集積回路チップ 8 0 a 、 8 0 b 、 8 0 c は、接着層 9 7 を用いて基板に取り付けられるが、このとき、上部に取り付けられる集積回路チップ 8 0 b 、 8 0 c を下部チップに対して 180° 回転させて実装することができる。このような方法で、上部チップの凹部及び下部チップの周辺領域が連続して配列されると、集積回路チップの厚さよりも大きい開口部が形成され、ボンディングワイヤ 9 3 を下部チップのボンドパッド 8 5 a に取り付けることができる。

【 0 0 2 5 】

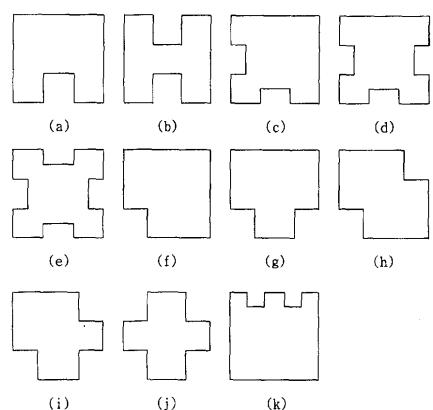

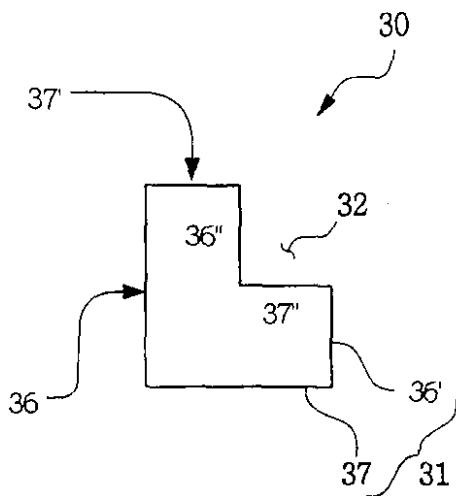

図 8 に示すように、互いに直交する側面 3 6 、 3 7 を有する集積回路チップ 3 0 に一つの凹部 3 2 を形成すると、凹部端部 3 6 ' 、 3 7 ' の長さに減少された少なくとも二つの外周面 3 6 ' 、 3 7 ' が生まれる。凹部の大きさ及び配置に応じて集積回路チップ 3 0 の形態が変わるが、凹部が角を取り囲む場合、集積回路チップ 3 0 は L 字に具現され、図 8 に、図示していないが、凹部が集積回路チップの一面に形成される場合、 C 字に具現される。

【 0 0 2 6 】

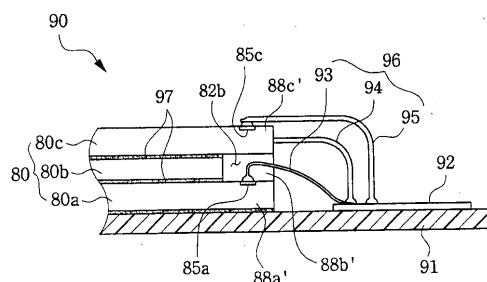

一つ以上の凹部が形成される場合、図 9 ( a ) ~ ( k ) に示すように、集積回路チップに多様な外周面が具現されている。図 5 に示すように、凹部の大きさ及び配置に応じて集積回路チップの外周面は、一つ以上の対角線軸及び/または平行線軸を基準にして対称をなす。例えば、( a ) の外周面は、軸 ( V ) を基準にして対称状で、( b ) の外周面は、二本の軸 ( V 、 H ) を基準にして対称状で、( e ) の外周面は、四本の軸 ( D 1 、 D 2 、 V 、 H ) を基準にして対称をなす。

【 0 0 2 7 】

図 10 に示すように、段差を有する複数の集積回路チップ 3 0 が半導体ウエハに反復パターンで配列される。すなわち、集積回路チップは、同一方向に配列された後、切断線 2 6 a 、 2 6 b 、 2 6 c に沿ってスクライビング、特にレーザースクライビングにより分離される。切断された部位 3 1 は除去され集積回路チップ 3 0 に凹部が形成されることになる。切断された部位 3 1 は、個別半導体素子に含まれず、一般にこの部分はスクラップと呼ばれる。

【 0 0 2 8 】

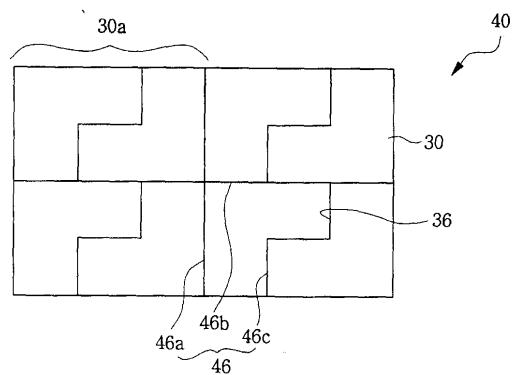

図 11 に示すように、凹部を有する集積回路チップが二以上集まって矩形の一つのユニット 3 0 a をなす。このような配置は、半導体ウエハ表面に反復的に行われることができ、切断線 8 0 a 、 8 0 b 、 8 0 c に沿って個別集積回路チップに分離するとスクラップを減少させることができることから素子当たり必要とする製造費用をも低減できる。

【 0 0 2 9 】

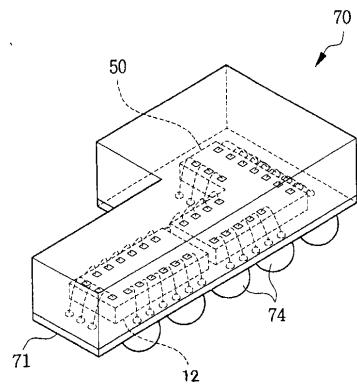

図 12 は、本発明の実施形態におけるマルチチップパッケージ 7 0 を示す図で、従来の矩形第 1 集積回路チップ 1 2 と本発明の外周面を有する第 2 集積回路チップ 5 0 とが基板 7 1 に水平に実装される構造である。基板 7 1 は、集積回路チップと回路基板及びソケットとフィクスチャーを繋ぐためにソルダボール 7 4 のような外部連結構造を含む。

【 0 0 3 0 】

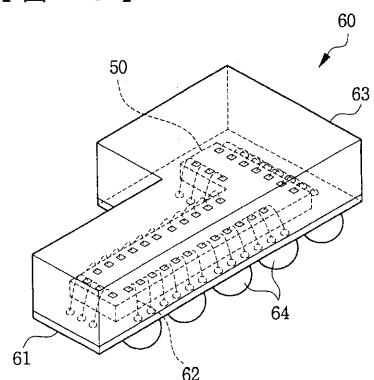

図 13 は、本発明の実施形態におけるシングルチップパッケージ 6 0 を示す図で、変形された外周面を有する一つの集積回路チップ 5 0 を備える構造である。集積回路チップ 5

10

20

30

40

50

0は、基板61に実装され、基板61は、集積回路チップと回路基板及びソケットとフィクスチャーを繋ぐソルダボール64のような外部接続構造を有する。図12及び図13に示すように、具現された半導体素子パッケージもやはりチップの構造に対応する外周面を有するので外周面が矩形ではない。

#### 【0031】

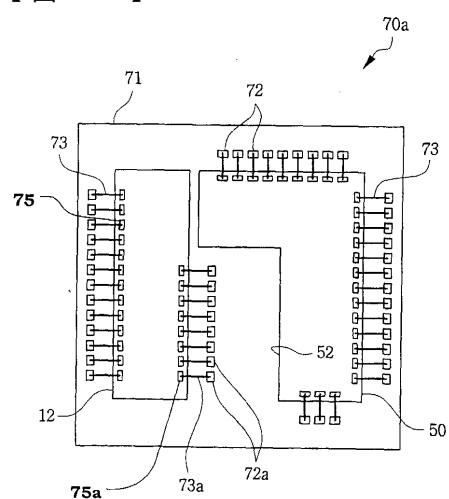

図14に示すように、本発明は、集積回路チップに凹部を形成して外周面を変形させるだけではなく、隣接した集積回路チップの配置及び連結手段を考慮してボンドパッドの配列を変えることができる。図14に示すように、マルチチップパッケージ70は、矩形集積回路チップ12と変形集積回路チップ50とが水平に実装される構造を有する。しかし、集積回路チップ12、50及び基板71のボンドパッド72、72a、75、75aが端部及び/または縦軸に沿って一律的に配列されるのではなく、従来と異なって若干非対称的に配列されている。特に、集積回路チップ50には凹部の端部52に沿ってボンドパッドが形成されておらず、矩形集積回路チップ12には集積回路チップ50の凹部で作られた空間に基板71の外側と隣接していない端部の一部に内部ボンドパッド75aが形成されている。集積回路チップのボンドパッド及び基板のボンドパッドは、ボンディングワイヤ73、73aと連結される。

#### 【0032】

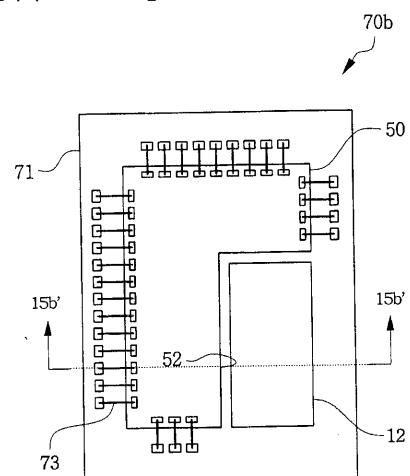

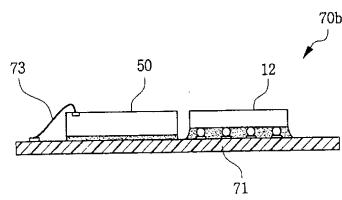

図15A及び図15Bに示すように、本発明のさらに他の実施形態におけるマルチチップパッケージ70bで、凹部の端部52に沿って集積回路チップのボンドパッドが形成されない構造を有する。

#### 【0033】

図15Bは、図15Aの15b'、15b'線に沿って切断された断面図で、集積回路チップ12が、基板にフリップチップボンディングされ集積回路チップの活性面に形成されているボンドパッド及び基板のボンドパッドが半田ボールや半田バンプのような伝導性構造により直接連結された構造を有する。従って、ボンディングワイヤ73を用いる必要がない。

#### 【0034】

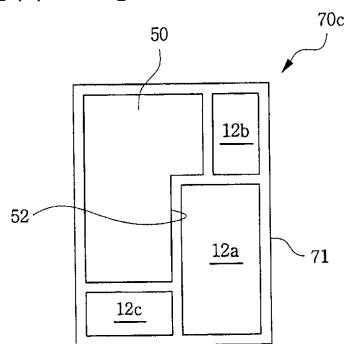

図16は、本発明のさらに他の実施形態に関し、マルチチップパッケージ炉及び集積回路チップ12a、12b、12c、50が基板71にフリップチップボンディングされている構造を示す。これにより、ボンディングワイヤが不要となり、基板に対する集積回路チップの実装密度が向上し、かつ取り付けが簡単に行える。また、形態の異なる集積回路チップを基板表面に完全な形態で配置できるため、実装密度を高めることができる。

#### 【0035】

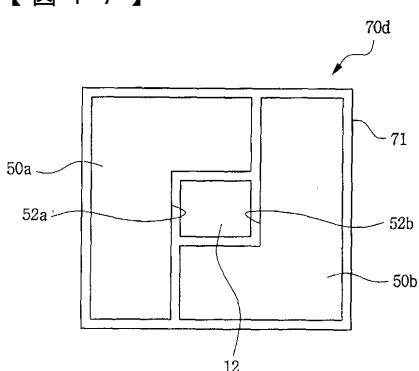

図17は、本発明のさらに他の実施形態に関し、マルチチップパッケージ炉及び集積回路チップ12、50a、50bの凹部の端部52a、52b間で形成された内部空間に集積回路チップ12が配置されている構造を示す。各々の集積回路チップは、基板にフリップチップボンディングされるのでワイヤボンディングが不要で、これにより基板に対する集積回路チップの実装密度が向上し、かつ取り付けが簡単に行える。

#### 【0036】

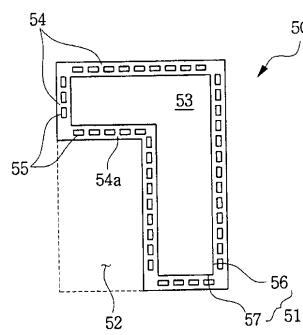

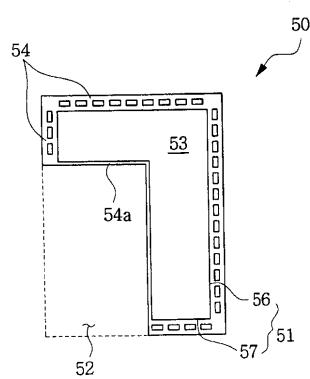

図18に示すように、本発明の実施形態における集積回路チップ50は、チップ最端部57、56、角部51、及びボンドパッド54、54aが一定に配列された凹部端部54aを含む構造である。図19は、集積回路チップ50のさらに他の実施形態を示すもので、ボンドパッドがチップ端部のみに形成されており凹部端部54aには形成されていない。例えば、図17のマルチチップ構造のように、凹部間に形成された空間により他の集積回路チップを配置させることができ、そうした構造に有用である。

#### 【0037】

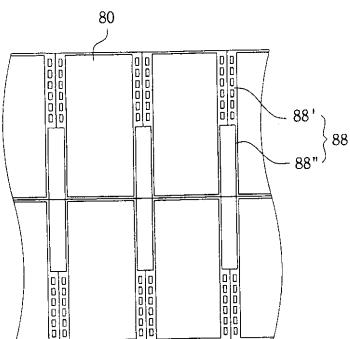

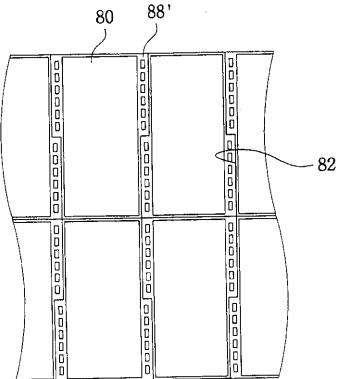

図20A及び図20Bは、ボンドパッドが形成された周辺領域88'、と凹部領域88'、とを含む外周面88を有する集積回路チップ80が複数配置された構造を示している。図20Bに示すように、基板上での集積回路チップの方向を変えることにより開放領域やスクラップを減少させながら実装密度を高めることができる。しかし、集積回路チップで

具現され得ない半導体ウエハ部分はそのまま置いたほうが良い。つまり、当該部分は、新しい製造過程や生産ラインまたは新しい装置を用いる際パラメータ及び機能テストを行うテストプラグ構造を作るのに必要だからである。このようなテスト構造により、キャパシタ、レジスタ、トランジスタ及び配置構造等が分析できることから、重要な機能的構成の品質や効果的な大きさを理解することができる。

【0038】

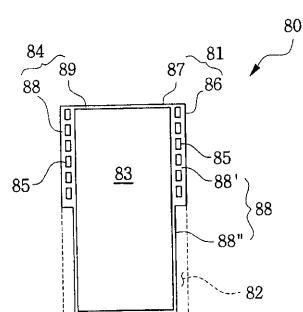

図21は、図20A及び図20Bの集積回路チップから分離段階を経て得られた個別集積回路チップ80を示す図である。図20A及び図20Bに示すように、集積回路チップ80の第1段の両側に二つの凹部領域82が形成されており、第2段の両側に表面86を有する周辺領域88が形成されている。周辺領域88及び凹部領域82は、素子が適切に機能するための必要なメモリ、論理及び/または入出力回路を含む内部機能領域、すなわちセル領域83を取り囲む形状である。チップの周辺領域は、隅部84、81となる左右側上端領域89、87を含む。

【0039】

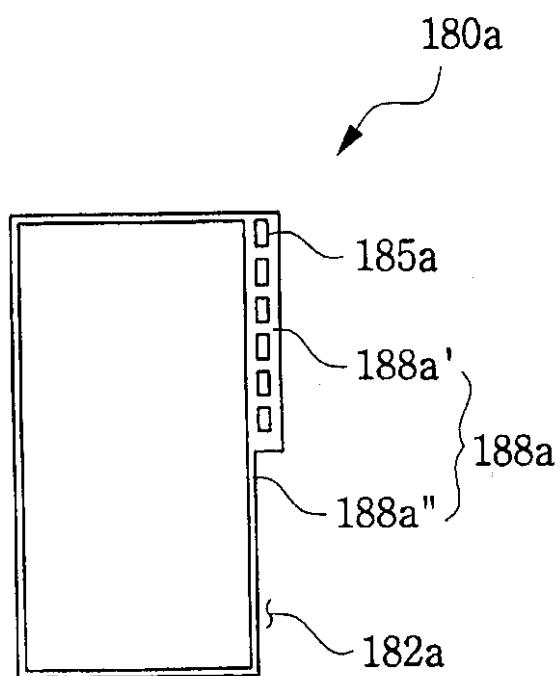

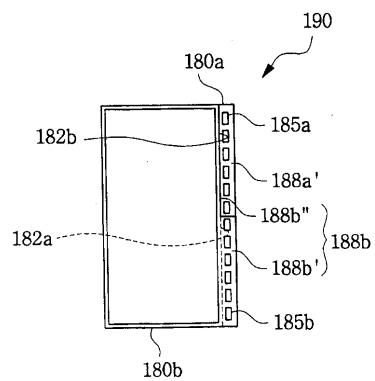

図22に示すように、本発明のさらに他の実施形態の集積回路チップ180aによると、ボンドパッド185aが形成された周辺領域188a'及び周辺領域と一緒にチップの一側面188aを形成する凹部領域188a''を含む一つの凹部182aを有する。図23に示すように、本発明の実施形態によるマルチチップパッケージ190は、図22の第1集積回路チップ180a上に第2集積回路チップ180bが積層されている構造を有する。第2集積回路チップ180bは第1集積回路チップと反対方向の周辺領域188b'及び凹部端部188b''を含む。すなわち、第1チップ180a上に第2チップ180bが積層されるとき、またはその反対の場合、上部チップの凹部領域が下部チップのボンドパッド185bを露出させることによって、チップと基板との連結の際一列に形成されたボンドパッド185a、185bを提供する。

【0040】

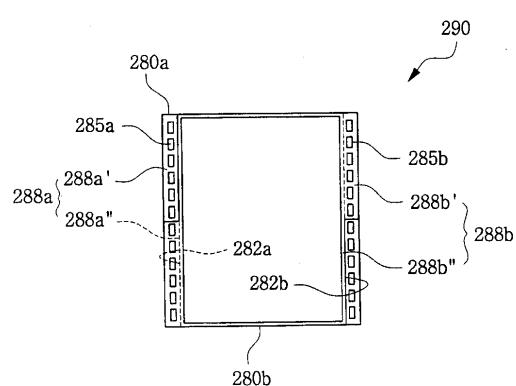

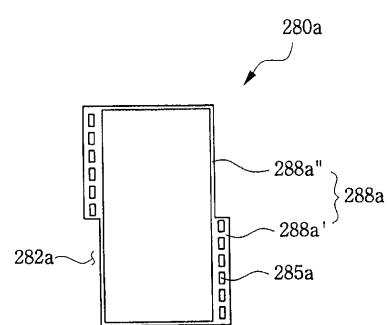

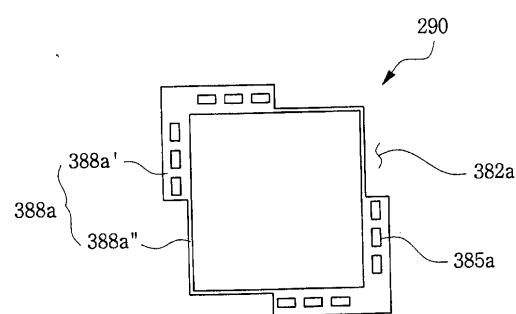

図24に示すように、本発明のさらに他の実施形態における集積回路チップ280aは、チップ両側に形成された二つの凹部282a、288aを有し、一方の凹部288aは、ボンドパッドが形成された周辺領域288a'及び周辺領域299a''を含む。図25に示すように、本発明の実施形態におけるマルチチップパッケージ290は、図24の第1集積回路チップ280a上に第2集積回路チップ280bが積層された構造を有する。第2集積回路チップ280bは、第1集積回路チップ280aと反対方向の周辺領域288b'及び凹部領域288b''を含む。すなわち、第1チップ280a上に第2チップ280bが積層される時、またはその反対の場合、上部チップの凹部領域が下部チップのボンドパッド286bを露出させる。これにより、チップと基板との連結際両列に形成されたボンドパッド285a、285bを提供する。

【0041】

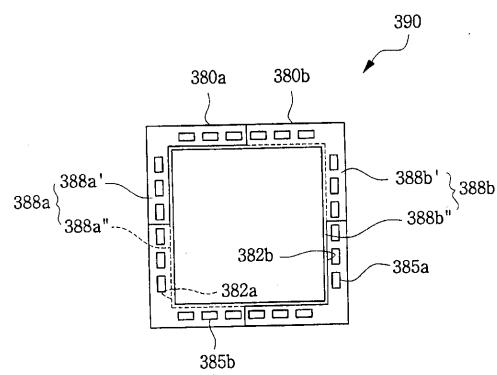

図26に示すように、本発明のさらに他の実施形態における集積回路チップ290は、チップ対角線角に形成された一対の凹部382a、388aを有し、一方の凹部388aは、ボンドパッドが形成された周辺領域388a'及び周辺領域388a''を含む。図27に示すように、本発明の実施形態によるマルチチップパッケージ390は、図26の第1集積回路チップ290上に第2集積回路チップ290を90°回転させて積層した構造を有する。図27に示すように、第2チップは、第1チップと反対方向の周辺領域388b'及び凹部領域388b''を含む。これにより、第1チップ上に第2チップが積層される場合またはその反対の場合、上部チップの凹部領域が下部チップのボンドパッド385bを露出することによって、チップと基板との連結際端部に沿って形成されるボンドパッド385a、385bを提供する。

【0042】

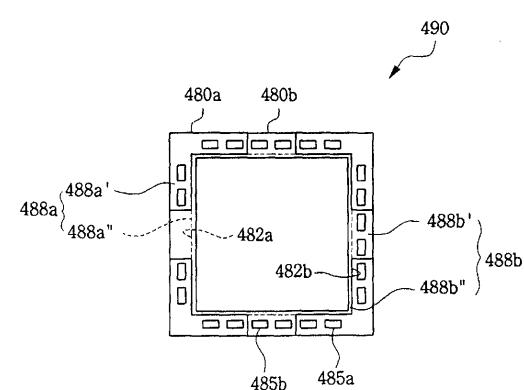

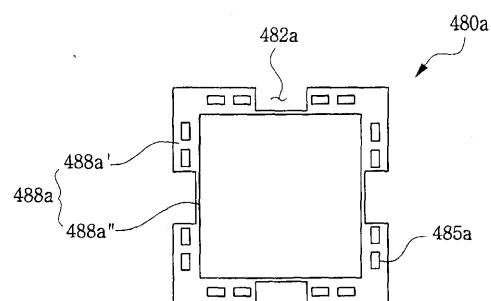

図28に示すように、本発明のもう一つの実施形態における集積回路チップ480aは、チップ端部の中間に形成された凹部482aを有し、一つの凹部488a'は、ボンドパッド485aが形成された周辺領域488a'及び隣接周辺領域間に形成された凹部領

10

20

30

40

50

域 4 8 8 a ' ' とを含む。図 2 9 に示すように、本発明の実施形態によるマルチチップパッケージ 4 9 0 は、図 2 8 の第 1 集積回路チップ 4 8 0 a と、上記第 1 集積回路チップ 4 8 0 a と相互補完的形態の凹部 4 8 8 a を含む第 2 集積回路チップ 4 8 0 b が積層される構造を有する。すなわち、第 1 チップ上に第 2 チップが積層されると、上部チップの凹部領域が下部チップのボンドパッド 4 8 5 b を露出することになる。これにより、チップと基板との連結際端部に沿って形成されたボンドパッド 4 8 5 a 、 4 8 5 b を提供する。

#### 【 0 0 4 3 】

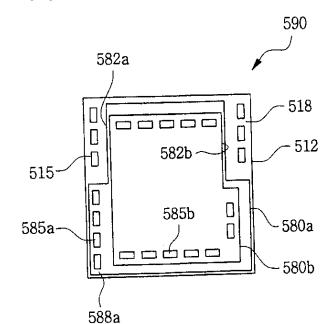

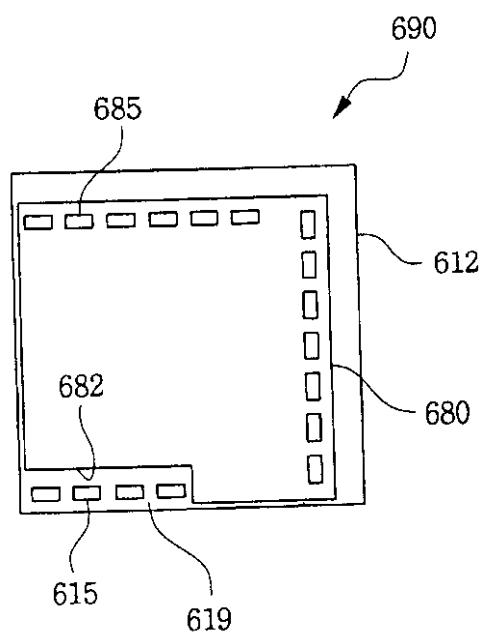

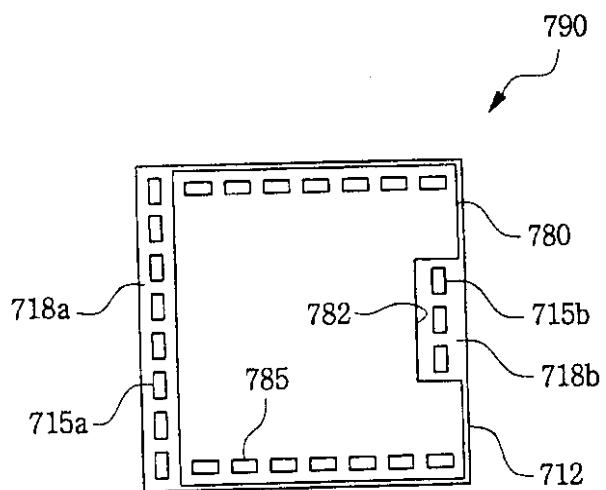

図 3 0 乃至図 3 2 に示すように、大きさと形態の異なる多様な外周面を有する集積回路チップを用いてチップスタック構造 5 9 0 、 6 9 0 、 7 9 0 を具現することにより、下部チップのボンドパッドを、上部チップの大きさと位置に応じて露出することができ、かつ上部チップの凹部に対応して配置することができる。よって、下部チップのボンドパッドがスペーサを追加したり背面をエッチングしたりするなどの追加工程を加えず露出することができる。

#### 【 0 0 4 4 】

本発明の実施形態による集積回路チップは、論理及び/またはメモリ回路が形成されたセル領域、及び入出力回路及び/または入出力パッドが形成された一つ以上の周辺領域を含む構造を有する。集積回路チップのセル領域及び/または周辺領域に隣接した凹部が形成される。本発明の実施形態による集積回路チップ及びチップスタック構造は、ワイヤボンディング及び/またはフリップチップボンディングのような連結方法を用いて一つ以上の基板に連結できる。そして、エポキシモルディング化合物のような樹脂密封材で密封し、集積回路チップ、ワイヤボンディング及びインナーリードの汚染、副食または機械的損傷から保護することができる。

#### 【 0 0 4 5 】

本明細書に開示された連結方法である、ワイヤボンディング、フリップチップボンディング及び/または T A B 方法だけでなく、多様な方法が使用可能であり、基板として、リードフレーム、印刷回路基板、フレキシブル回路基板またはセラミック基板以外にも多様な基板が使用可能である。

#### 【 0 0 4 6 】

以上、本発明の実施例によって多様な外周面とボンドパッド構造を有する集積回路チップは、基板及び/またはパッケージと一緒に用いることができる。また、多様な要素等と適合できるので捨てられる表面領域が低減し、基板または第 2 回路基板に対する実装密度を向上させることができる。マルチチップパッケージに対する素子水準、またはパッケージが実装されるマザーボードやモジュールボードのような上位水準において実装密度を向上させることができる。さらに、基板水準においてパッケージの実装密度を向上させることによって基板の大きさを小さくすることができる。

#### 【 0 0 4 7 】

なお、本明細書と図面に開示された本発明の実施形態は理解を助けるための特定例を提示したに過ぎず、本発明の範囲を限定するものではない。ここに開示された実施形態の他にも本発明の技術的思想に基づき他の変形例が実施可能であることは本発明が属する技術分野における通常の知識を有する者に自明である

#### 【 図面の簡単な説明 】

#### 【 0 0 4 8 】

【 図 1 】従来技術のウエハダイシング方法を示す斜視図である。

【 図 2 】レーザウエハダイシング方法を示す図である。

【 図 3 A 】従来技術の積層チップパッケージの実施形態を示す図である。

【 図 3 B 】従来技術の積層チップパッケージの実施形態を示す図である。

【 図 4 】本発明の実施形態を示す図である。

【 図 5 A 】代表的な大きさと軸を有する本発明の実施形態を示す図である。

【 図 5 B 】代表的な大きさと軸を有する本発明の実施形態を示す図である。

【 図 6 】本発明の実施形態におけるマルチチップパッケージの組立を示す図である。

10

20

30

40

50

【図 7】図 6 のマルチチップパッケージの部分断面図である。

【図 8】本発明の集積回路チップを示す平面図である。

【図 9】本発明の集積回路チップの具現可能な多様な外周面形態 ( a ) ~ ( k ) を示す図である。

【図 10】半導体ウエハ上に図 8 の複数の集積回路チップが配置されている配置方向を示す図である。

【図 11】半導体ウエハ上に図 8 の複数の集積回路チップが配置されている配置方向を示す図である。

【図 12】本発明の実施形態を示す斜視図である。

【図 13】本発明の実施形態を示す斜視図である。

【図 14】本発明の実施形態におけるマルチチップパッケージを示す平面図である。

【図 15 A】本発明の実施形態におけるマルチチップパッケージを示す平面図である。

【図 15 B】本発明の実施形態におけるマルチチップパッケージを示す断面図である。

【図 16】本発明のさらに他の実施形態におけるマルチチップパッケージを示す平面図である。

【図 17】本発明のさらに他の実施形態におけるマルチチップパッケージを示す平面図である。

【図 18】本発明のさらに他の実施形態における集積回路チップを示す平面図である。

【図 19】本発明のさらに他の実施形態における集積回路チップを示す平面図である。

【図 20 A】本発明の半導体ウエハに形成される集積回路チップの配列を示す平面図である。

【図 20 B】本発明の半導体ウエハに形成される集積回路チップの配列を示す平面図である。

【図 21】本発明の半導体ウエハに形成される集積回路チップの配列を示す平面図である。

【図 22】本発明の実施形態における集積回路チップを示す平面図である。

【図 23】本発明の実施形態におけるチップ積層の集積回路チップの配列を示す平面図である。

【図 24】本発明の実施形態における集積回路チップを示す平面図である。

【図 25】本発明の実施形態におけるチップ積層の集積回路チップの配列を示す平面図である。

【図 26】本発明の実施形態における集積回路チップを示す平面図である。

【図 27】本発明の実施形態における集積回路チップから具現されるマルチチップ積層パッケージを示す平面図である。

【図 28】本発明の実施形態における集積回路チップを示す平面図である。

【図 29】本発明の実施形態における集積回路チップから具現されたマルチチップ積層パッケージを示す平面図である。

【図 30】本発明の実施形態におけるマルチチップ積層パッケージを示す平面図である。

【図 31】本発明の実施形態におけるマルチチップ積層パッケージを示す平面図である。

【図 32】本発明の実施形態におけるマルチチップ積層パッケージを示す平面図である。

【符号の説明】

【0 0 4 9】

4 0 マルチチップパッケージ

4 1 基板

8 2 a , 8 2 b , 8 2 c 凹部

1 8 2 a 凹部

2 8 2 a , 2 8 8 a 凹部

3 8 2 a , 3 8 8 a 凹部

4 8 2 a , 4 8 8 a 凹部

10

20

30

40

【図1】

【図2】

【図3 A】

【図3 B】

【図5 A】

【図4】

【図5 B】

【図6】

( 7 )

【 図 9 】

【 図 1 0 】

【 図 8 】

### 【 図 1 1 】

【 図 1 2 】

【図13】

【図14】

【図15A】

【図16】

【図15B】

【図17】

【図 18】

【図 20 A】

【図 19】

【図 20 B】

【図 21】

【図 22】

【図23】

【図25】

【図24】

【図26】

【図27】

【図29】

【図28】

【図30】

【図3-1】

【図3-2】

## フロントページの続き

(74)代理人 100110364

弁理士 実広 信哉

(72)発明者 姜 仁九

大韓民国忠清南道天安市佛堂洞（番地なし） ドンギルハイヴィルアパート203棟601號

(72)発明者 金 震鎬

大韓民国忠清南道天安市雙龍2洞（番地なし） 龍岩マウル東亞碧山アパート101棟903號

(72)発明者 鄭 泰敬

大韓民国京畿道水原市長安區亭子1洞（番地なし） 大林チンヒュンアパート821棟1803號

(72)発明者 高 錫

大韓民国忠清南道天安市新芳洞（番地なし） 星志サマルアパート201棟403號

(72)発明者 李 容在

大韓民国京畿道城南市盆唐區九美洞221番地 ムジグマウル506棟704號

F ターム(参考) 5F044 AA01 AA02 EE02