(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6475635号

(P6475635)

(45) 発行日 平成31年2月27日(2019.2.27)

(24) 登録日 平成31年2月8日(2019.2.8)

(51) Int.Cl.

F 1

|                    |                  |      |       |      |

|--------------------|------------------|------|-------|------|

| <b>H01L 29/78</b>  | <b>(2006.01)</b> | H01L | 29/78 | 652J |

| <b>H01L 29/744</b> | <b>(2006.01)</b> | H01L | 29/74 | C    |

| <b>H01L 29/12</b>  | <b>(2006.01)</b> | H01L | 29/78 | 652T |

| <b>H01L 29/739</b> | <b>(2006.01)</b> | H01L | 29/78 | 652G |

|                    |                  | H01L | 29/78 | 652E |

請求項の数 25 (全 17 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2015-550412 (P2015-550412)  |

| (86) (22) 出願日 | 平成25年12月4日 (2013.12.4)        |

| (65) 公表番号     | 特表2016-506081 (P2016-506081A) |

| (43) 公表日      | 平成28年2月25日 (2016.2.25)        |

| (86) 國際出願番号   | PCT/US2013/073093             |

| (87) 國際公開番号   | W02014/105372                 |

| (87) 國際公開日    | 平成26年7月3日 (2014.7.3)          |

| 審査請求日         | 平成28年12月5日 (2016.12.5)        |

| (31) 優先権主張番号  | 13/730,133                    |

| (32) 優先日      | 平成24年12月28日 (2012.12.28)      |

| (33) 優先権主張國   | 米国(US)                        |

|           |                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------|

| (73) 特許権者 | 592054856<br>クリー インコーポレイテッド<br>CREE INC.<br>アメリカ合衆国 ノースカロライナ州 2<br>7703 ダラム シリコン ドライブ<br>4600 |

| (74) 代理人  | 110000578<br>名古屋国際特許業務法人                                                                      |

| (72) 発明者  | チャン チンチュン<br>アメリカ合衆国 ノースカロライナ州 2<br>7519 ケリー ヒッコリーウッド<br>ブルバード 108                            |

最終頁に続く

(54) 【発明の名称】ゲート酸化膜層において電界を低下させた半導体デバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲートと、ソースと、ドレインとを備えるトランジスタデバイスであって、前記ゲートはゲート酸化膜に少なくとも部分的に接触しており、前記ゲート酸化膜上における電界を低下させるために、複数のドープ領域が、前記トランジスタデバイスのウェル領域間に延びる接合型電界効果 (J F E T ) 領域内に存在し、前記複数のドープ領域は、前記 J F E T 領域内において前記ウェル領域間に配置されるとともに、前記 J F E T 領域の上面の完全に下方に、かつ、完全に該 J F E T 領域内に、かつ、完全に前記ウェル領域間にあり、前記複数のドープ領域のドープ領域が前記ウェル領域より下方には延びていない、トランジスタデバイス。

## 【請求項 2】

前記トランジスタデバイスの本体が炭化ケイ素を含む、請求項 1 に記載のトランジスタデバイス。

## 【請求項 3】

前記複数のドープ領域のうち少なくとも 1 つのドープ領域が前記 J F E T 領域のほぼ中央に設けられる、請求項 1 に記載のトランジスタデバイス。

## 【請求項 4】

前記複数のドープ領域のうち少なくとも 1 つのドープ領域が前記ソースに接続され、これにより前記トランジスタデバイスの前記ドレインを有する側からの電界を効果的に遮蔽する、請求項 1 に記載のトランジスタデバイス。

**【請求項 5】**

前記複数のドープ領域のうち少なくとも1つのドープ領域は、深さが約0.1ミクロン(μm)と約0.3ミクロン(μm)の間である、請求項1に記載のトランジスタデバイス。

**【請求項 6】**

前記複数のドープ領域のうち少なくとも1つのドープ領域は、幅が約0.5ミクロン(μm)と約1.0ミクロン(μm)の間である、請求項1に記載のトランジスタデバイス。

**【請求項 7】**

前記JFET領域の幅が、約2.0ミクロン(μm)と約3.6ミクロン(μm)の間である、請求項1に記載のトランジスタデバイス。 10

**【請求項 8】**

前記複数のドープ領域のうち少なくとも1つのドープ領域がP領域である、請求項1に記載のトランジスタデバイス。

**【請求項 9】**

ゲート酸化膜と少なくとも部分的に接触しているゲートと、ソースと、ドレインとを有するトランジスタデバイスであって、

第1導電型のウェル領域と、

前記ウェル領域の上にある第2導電型の領域と、

前記ウェル領域に隣接する接合型電界効果(JFET)領域と、 20

前記第2導電型の領域の一部及び前記JFET領域にわたって延びる埋め込みチャネル層であって、前記ゲート酸化膜により少なくとも部分的に覆われており、該ゲート酸化膜上において前記トランジスタデバイスが低下した電界を有する、埋め込みチャネル層と、

前記ウェル領域の下方にあるドリフト層と、

前記JFET領域内において前記第2導電型の領域に近接する第1導電型の領域と、

前記JFET領域内に存在する前記第1導電型である第1の領域及び第2の領域であって、前記ウェル領域が前記トランジスタデバイス内に第1の深さまで注入され、前記第1の領域及び前記第2の領域のうち少なくとも1つが、前記JFET領域内において、前記ウェル領域の前記第1の深さの半分と前記第1の深さの間である第2の深さで注入され、かつ、前記JFET領域の上面の完全に下方にある、第1の領域及び第2の領域と 30

を備えるトランジスタデバイス。

**【請求項 10】**

前記JFET領域において導入された前記第1導電型の前記第1の領域及び前記第2の領域は、前記ゲート酸化膜において電界を低下させる、請求項9に記載のトランジスタデバイス。

**【請求項 11】**

前記トランジスタデバイスはMOSFETである、請求項9に記載のトランジスタデバイス。

**【請求項 12】**

前記トランジスタデバイスは絶縁ゲートバイポーラトランジスタである、請求項9に記載のトランジスタデバイス。 40

**【請求項 13】**

前記トランジスタデバイスは金属酸化物半導体制御サイリストである、請求項9に記載のトランジスタデバイス。

**【請求項 14】**

前記第1導電型はP+型であり、前記第2導電型はN+型である、請求項9に記載のトランジスタデバイス。

**【請求項 15】**

前記トランジスタデバイスの本体は炭化ケイ素を含む、請求項9に記載のトランジスタデバイス。 50

**【請求項 16】**

前記 J F E T 領域において導入された前記第 1 導電型の前記第 1 の領域及び前記第 2 の領域の一方は P + 領域であり、かつ、前記 J F E T 領域のほぼ中央に導入される、請求項 9 に記載のトランジスタデバイス。

**【請求項 17】**

前記 J F E T 領域に導入された前記第 1 導電型の前記第 1 の領域及び前記第 2 の領域の一方は P + 領域であり、かつ、前記ソースに接続されており、これにより、前記トランジスタデバイスの前記ドレインを有する側からの電界を効果的に遮蔽する、請求項 9 に記載のトランジスタデバイス。

**【請求項 18】**

前記 J F E T 領域内に導入された前記第 1 導電型の前記第 1 の領域及び前記第 2 の領域の一方は P + 領域であり、かつ、深さが前記ウェル領域よりも浅い、請求項 9 に記載のトランジスタデバイス。

**【請求項 19】**

前記 J F E T 領域内に導入された前記第 1 導電型の前記第 1 の領域及び前記第 2 の領域の一方は P + 領域であり、かつ、深さが約 0.1 ミクロン ( μm ) と約 0.3 ミクロン ( μm ) の間である、請求項 9 に記載のトランジスタデバイス。

**【請求項 20】**

前記 J F E T 領域内に導入された前記第 1 導電型の前記第 1 の領域及び前記第 2 の領域の一方は P + 領域であり、かつ、幅が約 0.5 ミクロン ( μm ) と約 1.0 ミクロン ( μm ) の間である、請求項 9 に記載のトランジスタデバイス。

**【請求項 21】**

前記 J F E T 領域の幅は約 2.0 ミクロン ( μm ) と約 3.6 ミクロン ( μm ) の間である、請求項 9 に記載のトランジスタデバイス。

**【請求項 22】**

前記 J F E T 領域内に存在する第 2 のドープ領域をさらに備え、前記第 2 のドープ領域が完全に前記 J F E T 領域内に、かつ、完全に前記ウェル領域の間にある、請求項 1 に記載のトランジスタデバイス。

**【請求項 23】**

第 1 の電流端子がソースであり、第 2 の電流端子がドレインである、請求項 9 に記載のトランジスタデバイス。

**【請求項 24】**

前記複数のドープ領域が前記 J F E T 領域の上面から離間している、請求項 1 に記載のトランジスタデバイス。

**【請求項 25】**

前記第 1 の領域及び前記第 2 の領域のうち少なくとも一方が前記 J F E T 領域の上面から離間している、請求項 9 に記載のトランジスタデバイス。

**【発明の詳細な説明】****【発明の詳細な説明】****【0001】****【開示の分野】**

本開示は、トランジスタ構造、特に、ゲート酸化膜において電界が低下した、金属酸化物半導体電界効果トランジスタ ( M O S F E T ) 等のトランジスタ構造、及び、このようなトランジスタ構造の製造方法に関する。

**【背景技術】**

金属酸化物半導体電界効果トランジスタ ( M O S F E T ) は周知のものである。特に、パワー M O S F E T は市販化されており、電力システムにおいて広く用いられることが期待されている。炭化ケイ素 ( S i C ) 上のパワー M O S F E T 等の従来の M O S F E T 構造の場合、起こりうる課題の 1 つとして、デバイスの接合型電界効果 ( J F E T ) 領域の中央にあるゲート酸化膜において高電界が存在することが挙げられる。J F E T 領域は一

般に、N型ドーパントを含有し得るN型ドリフト層の活性部分であり、2つのP型ウェルの間に位置する。JFET領域は、ゲート電圧を印加することによってP型ウェルの表面に達するチャネル領域に接触している領域を指し得る。JFET領域は、N+ソース領域、チャネル領域、N型ドリフト領域、基板、及びドレイン電極と共に電子の導電路を構成する。ドレインに高バイアス（動作上の最大値に近い）が印加され、ゲートは接地電位附近に保たれている動作状態下では、JFET領域の直上にあるゲート酸化膜内で高電界が発生してしまう。界面物質やゲート酸化膜に欠陥があると、ドレインが正バイアスが高い状況下に置かれる長時間の阻止動作中に、ゲート酸化膜が破壊される結果となり得る。また、従来のMOSFETは、ドレインが正バイアスが高い状況下に置かれる長時間の阻止動作中に生じ得るホットキャリア注入の悪影響を受ける可能性もある。

10

#### [概要]

本開示は、ゲート酸化膜界面において電界を低下させ、これにより、ドレインが正バイアスが高い状況下に置かれる長時間の阻止動作中のデバイス信頼性が、ゲート酸化膜の電界が低くなることに起因して向上とともに、ドレインが正バイアスが高い状況下に置かれる長時間の阻止動作中にホットキャリアがゲート酸化膜内に注入される可能性が低減するトランジスタデバイスに関する。ある好適な実施形態において、トランジスタデバイスはMOSFETデバイスであり、より好適には炭化ケイ素（SiC）MOSFETデバイスである。しかしながら、より一般的には、トランジスタデバイスは、トランジスタを有する任意の種類のデバイス（例えばパワーMOSFET、二重注入電界効果型トランジスタ（DIMOSFET）、絶縁ゲートバイポーラトランジスタ（IGBT）等）であってもよい。

20

#### 【0002】

一実施形態において、ゲート酸化膜において電界を低下させたトランジスタデバイスが開示される。トランジスタデバイスは、ゲートと、ソースと、ドレインとを備え、ゲートは少なくとも部分的にゲート酸化膜層の上にある。トランジスタデバイスは、ゲート酸化膜上における電界を低下させるために、トランジスタデバイスのJFET領域内にP+領域を有する。トランジスタデバイスは、ゲート酸化膜界面において電界を低下させることができ、ドレインが正バイアスが高い状況下に置かれる長時間の阻止動作中に発生し得る信頼性の問題や故障を、大幅に低減又は解消できる。

30

別の実施形態では、トランジスタデバイスは、ゲートと、ソースと、ドレインとを有し、第1導電型の第1エピタキシャル層と、第1エピタキシャル層の上にある第2導電型の第2エピタキシャル層と、トランジスタデバイスの第1面に隣接する埋め込みチャネル層とを備える。埋め込みチャネル層は第2エピタキシャル層の一部にわたって延びており、ゲート酸化膜により少なくとも部分的に覆われる。トランジスタデバイスはまた、第1エピタキシャル層から下方に向かってトランジスタデバイスの本体内へある深さまで延びている第1導電型のウェル領域と、ウェル領域に隣接するJFET領域と、ウェル領域の下方にあるドリフト層とを備える。

#### 【0004】

トランジスタデバイスのJFET領域内には、第1導電型の独立した領域が導入されており、これは一実施形態ではP+領域であってもよい。一実施形態において、P+領域はJFET領域のほぼ中央に導入され、ソースに接続されており、これによりトランジスタデバイスのドレイン側からの電界を効果的に遮蔽する。また、JFET領域内に導入されたP+領域はP+ウェル領域より浅くてもよく、これにより電流の広がり抵抗も低減される。

40

#### 【0005】

別の実施形態において、ゲート酸化膜において電界を低下させたMOSFETが開示される。MOSFETは、ゲートと、ソースと、ドレインとを有し、ゲートはゲート酸化膜層に少なくとも部分的に接触している。MOSFETは、P+型エピタキシャル層と、P+型エピタキシャル層の上にあるN+型領域とを備える。MOSFETはまた、MOSF

50

E T の第1面に隣接する埋め込みチャネル層を備え、埋め込みチャネル層はN +型領域の一部にわたって延びる。またMOSFETは、P +型エピタキシャル層から下方に向かってMOSFETの本体内へある深さまで延びるP +型ウェルと、P +ウェルに隣接するJFET領域とを備える。MOSFETはまた、ゲート酸化膜上における電界を低下させるために、JFET領域内にP +領域を備える。

#### 【0006】

ゲート酸化膜において電界を低下させたデバイスの製造方法も開示される。一実施形態において、トランジスタデバイスの製造方法が開示される。本方法は、ソース及びゲートを設ける工程を含み、ゲートはゲート酸化膜層に少なくとも部分的に接触する。本方法はまた、ゲート酸化膜上における電界を低下させるために、P +型ウェル領域に隣接するJFET領域内にP +領域を設けることも開示する。10

#### 【0007】

別の実施形態において、基板上にドリフト層を設ける工程と、ドリフト層上にウェル領域を注入する工程とを含む、トランジスタの製造方法が開示される。本方法はまた、第1エピタキシャル層を、第1エピタキシャル層がウェル領域の少なくとも一部を覆うように設ける工程と、第1エピタキシャル層上に第2エピタキシャル層を設ける工程と、第2エピタキシャル層の一部の上方に埋め込みチャネル層を設ける工程とを含む。ソース及びゲートは、ゲートがゲート酸化膜層に少なくとも部分的に接触するように設けられる。本方法はまた、ウェル領域に隣接するJFET領域内に、P +領域を導入する。

#### 【0008】

さらに別の実施形態において、MOSFETの製造方法が開示される。本方法は、ドリフト層上にP +型エピタキシャル層を設ける工程と、P +型エピタキシャル層上にN +型領域を設ける工程とを含む。MOSFETの第1面に隣接する埋め込みチャネル層が、N +型領域の一部にわたって延びるように設けられる。P +型ウェルが、P +型エピタキシャル層から下方に向かってMOSFETの本体内へある深さまで延びるように形成される。ソース及びゲートは、ゲートがゲート酸化膜層に少なくとも部分的に接触するように設けられる。本方法はまた、ゲート酸化膜上における電界を低下させるために、P +型ウェル領域に隣接するJFET領域内に、P +領域を設ける工程を含む。20

#### 【0009】

当業者であれば、添付の図面に関連する好適な実施形態に関する以下の詳細な説明を考察すると、本開示の範囲が理解でき、また、その更なる態様が実現できるであろう。30

本明細書に組み込まれるとともに本明細書の一部を構成する各添付図面は、本開示のいくつかの態様を例示したものであり、その説明とともに、本開示の原理を明らかにする役割を果たす。

#### 【図面の簡単な説明】

#### 【0010】

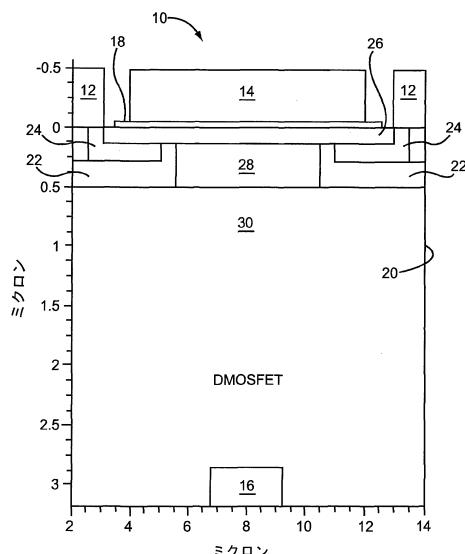

【図1】埋め込みチャネルを有する二重注入電界効果型トランジスタ(DIMOSFET)である。

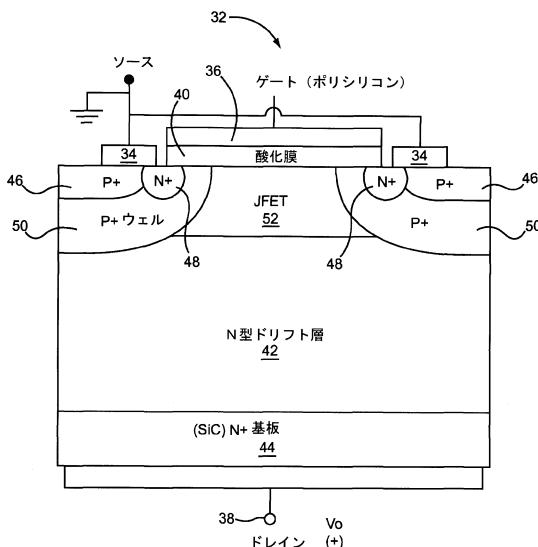

【図2】ゲート酸化膜界面において電界が低下していない、標準的なMOSFETセルの別の実施形態である。40

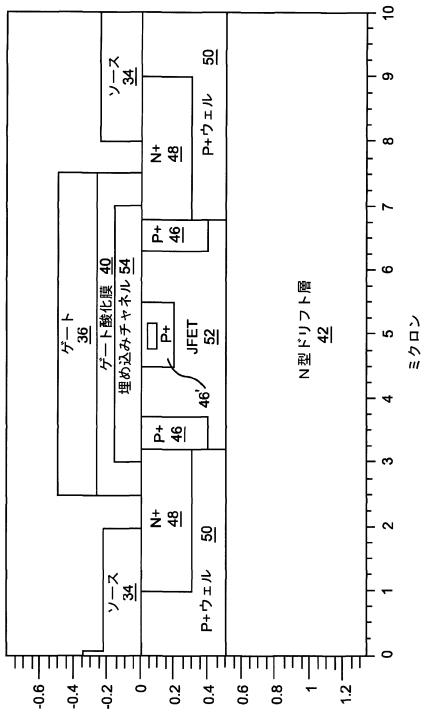

【図3A】一実施形態による、トランジスタデバイスのJFET領域に導入されたP +領域を含む新たな構造を有するトランジスタデバイスを示す。

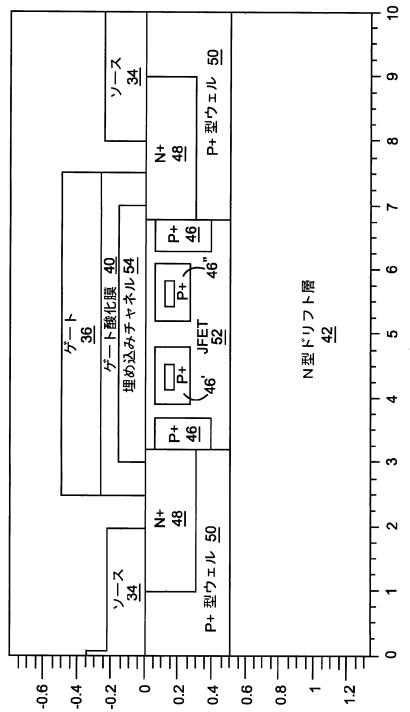

【図3B】一実施形態による、トランジスタデバイスのJFET領域内に導入された複数のP +領域を含む新たな構造を有する代替のトランジスタデバイスを示す。

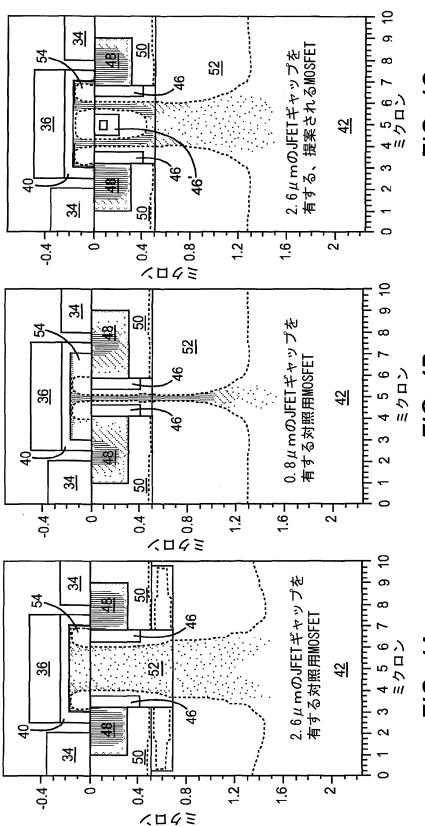

【図4】図4Aは、2 . 6ミクロン(μm)という標準的なJFETギャップを有する従来のMOSFETの順方向電流伝導分布を示す。図4Bは、0 . 8ミクロン(μm)という狭められたJFETギャップを有する従来のMOSFETの順方向電流伝導分布を示す。図4Cは、一実施形態によるトランジスタデバイスのJFET領域内に導入されたP +領域を有し、かつ2 . 6ミクロン(μm)という標準的なJFETギャップを有するMOSFETの順方向電流伝導分布を示す。50

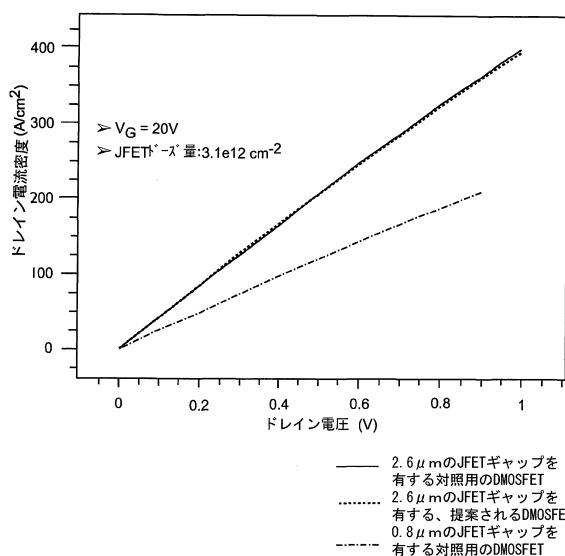

【図5】図4A～4Cに示される種々のMOSFETの順方向IV曲線のグラフであり、トランジスタデバイスのJFET領域内に導入されたP+領域を有する提案されたトランジスタ構造が、標準的なJFETギャップを有する従来のMOSFETと同じオン抵抗を示すことを例証している。

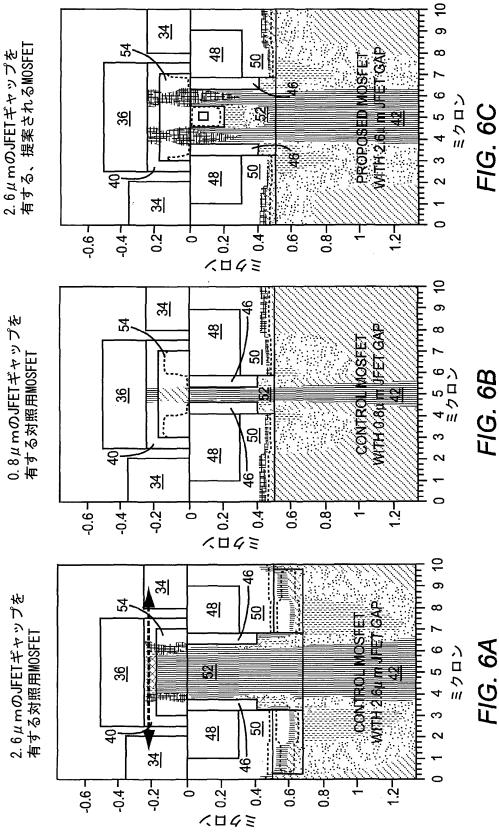

【図6】図6Aは、2.6ミクロン(μm)という標準的なJFETギャップを有する従来のMOSFETの、960ボルトの阻止電圧における電界分布を示した図である。図6Bは、0.8ミクロン(μm)という狭められたJFETギャップを有する従来のMOSFETの、960ボルトの阻止電圧における電界分布を示した図である。図6Cは、一実施形態によるトランジスタデバイスのJFET領域内に導入されたP+領域を有し、かつ2.6ミクロン(μm)という標準的なJFETギャップを有するMOSFETの、960ボルトの阻止電圧における電界分布を示した図である。10

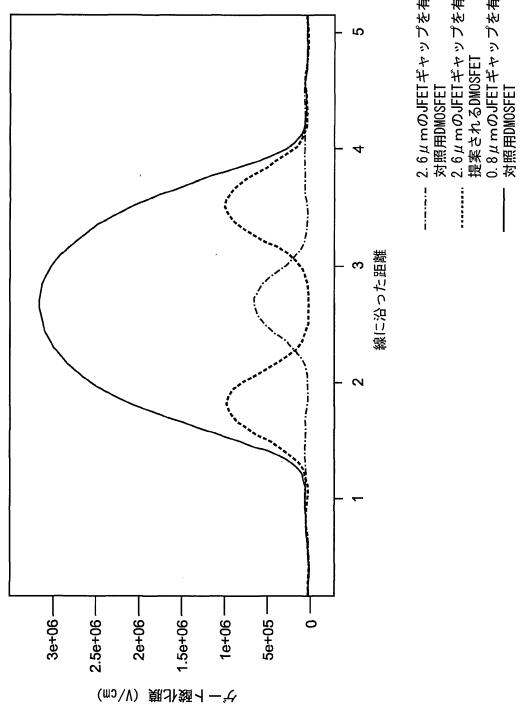

【図7】図7は、図4A～4Cに示される種々のMOSFETについての、ゲート酸化膜の中央でのゲート酸化膜の上面における電界分布の図であり、トランジスタデバイスのJFET領域内に導入されたP+領域を有するトランジスタ構造によって、オン抵抗を犠牲にすることなく電界の大幅な低下が達成されていることを示している。

#### 【発明を実施するための形態】

##### 【0011】

###### [詳細な説明]

以下に説明する各実施形態は、当業者が実施形態を実施することを可能にするために必要な情報を示すとともに、各実施形態を実行する最良の形態を示している。当業者であれば、以下の説明を添付の図面に照らして考察すると、本開示の概念を理解し、本明細書では特に論じていないこれらの概念の応用を認識するであろう。これらの概念及び応用が本開示及び添付の特許請求の範囲の範疇にあることは理解されるべきである。20

##### 【0012】

本明細書では、様々な要素を説明するために「第1」、「第2」等の語を使用するが、これらの要素はこれらの用語によって限定されるべきではないことは理解されるであろう。これらの語は、要素を互いに区別するためだけに使用されている。例えば、本開示の範囲から逸脱することなく、第1の要素を第2の要素と称することができるし、同様に第2の要素を第1の要素と称することもできる。本明細書で使用する場合、「及び／又は」という語は、関連する記載項目の1つ以上の任意のもの、またそのすべての組み合わせを含む。30

##### 【0013】

層、領域、又は基板といった要素が、別の要素の「上に(on)」ある、もしくは「上へと(onto)」延びていると述べられている場合、一方の要素が他方の要素の上に直接ある、もしくは上へと直接延びていることも可能であるし、又は介在する要素が存在していてもよいことは理解されよう。一方、ある要素が別の要素の「上に直接(directly on)」ある、もしくは「上へと直接(directly onto)」延びていると述べられている場合は、介在する要素は存在しない。同様に、層、領域、又は基板といった要素が、別の要素の「上方に(over)」ある、もしくは「上方を(over)」延びていると述べられている場合、一方の要素が他方の要素の上方に直接ある、もしくは上方へと直接延びていることも可能であるし、又は介在する要素が存在していてもよいことは理解されよう。一方、ある要素が別の要素の「上方に直接(directly over)」ある、もしくは「上方を直接(directly over)」延びていると述べられている場合は、介在する要素は存在しない。また、ある要素が別の要素に「接続されている」又は「結合されている」と述べられている場合、一方の要素が他方の要素に直接接続又は結合されていることも可能であるし、又は介在する要素が存在してもよいことは理解されよう。一方、ある要素が別の要素に「直接接続されている」又は「直接結合されている」と述べられている場合には、介在する要素が存在しない。40

##### 【0014】

本明細書では、「下方に」、「上方に」、「上部の」、「下部の」、「水平方向の」、50

又は「垂直方向の」といった相対的な用語が、図面に示されているように、ある要素、層、又は領域の別の要素、層又は領域に対する位置関係を説明するために使用され得る。これらの語及び上述した語は、各図に示されているデバイスの向きに加えて、異なる向きも含むことを意図していることは理解されよう。

#### 【0015】

本明細書で使用する用語は、特定の実施形態を説明するためのものにすぎず、本開示を限定するためのものではない。本明細書で使用するように、単数形の冠詞「1つの（a / a n）」及び「その（t h e）」は、文脈でそうではないことを明確に示していない限り、複数形も含むことが意図される。さらに、「備える」「備えている」「含む」、及び／又は「含んでいる」という語は、本明細書で使用する場合、説明される特徴、整数、工程、動作、要素、及び／又は構成部品の存在を明示するが、1つ以上の他の特徴、整数、工程、動作、要素、構成部品、及び／又はこれらの集まりの存在又は追加を排除するものではないことは理解されよう。

#### 【0016】

特に定義がなされていない限り、本明細書で使用する全ての語（技術用語及び科学用語を含む）は、本開示が属する技術分野の当業者が通常理解している意味と同じ意味を有する。さらに、本明細書で使用する語は、本明細書の文脈及び従来技術におけるこれらの語の意味と整合性のある意味を有すると解釈すべきであり、本明細書で明確に定義しない限り、理想的又は過度に形式的な意味で解釈されるものではないと理解されよう。

#### 【0017】

ゲート酸化膜界面において電界を低下させ、これによりデバイスの信頼性の向上をもたらすMOSFET構造が必要とされている。この問題に対処する手法の1つとして、JFETギャップを狭めることが挙げられる。しかしながら、従来のMOSFETデバイス上でJFETギャップを（順電圧降下を犠牲にせずに）狭めることは、高電界をかけている状況下でのデバイス信頼性を向上させることはできるが、故障をなくすことはできないということを、本発明の発明者は認識してきた。

#### 【0018】

本開示は、ゲート酸化膜界面において電界を低下させて、ドレインが正バイアスが高い状況下に置かれる長時間の阻止動作下での故障又は信頼性の問題を大幅に低減する、もしくは解消するために、新規な構造を有するトランジスタデバイスに関する。ある好適な実施形態において、トランジスタデバイスはMOSFETデバイスであり、より好適には炭化ケイ素（SiC）MOSFETデバイスである。しかしながら、より一般的には、トランジスタデバイスは、トランジスタを有する任意の種類のデバイス（例えばパワーMOSFET、二重分化電界効果トランジスタ（double differentiated field effect transistor: DMOSFET）、トレンチゲート型金属酸化物半導体電界効果トランジスタ（UMOSFET）、絶縁ゲートバイポーラトランジスタ（IGBT）等）であってもよい。

#### 【0019】

一実施形態において、ゲート酸化膜において電界を低下させたトランジスタデバイスが開示される。トランジスタデバイスは、ゲートと、ソースと、ドレインとを備え、ゲートは少なくとも部分的にゲート酸化膜層の上にある。トランジスタデバイスは、ゲート酸化膜上における電界を低下させるために、トランジスタデバイスのJFET領域内に少なくとも1つのP+領域を有する。トランジスタデバイス内で発生し得る材料欠陥が存在するために、ゲート酸化膜内の高電界が、その欠陥箇所又はその周囲で強められることがある。この電界を低下させることにより、特にドレインが高い正バイアスの状況下に置かれる長時間の阻止動作中に、欠陥がトランジスタデバイスの信頼性に対してもたらす影響を大幅に減少させることができる。炭化ケイ素MOSFETでは、信頼性を保証するために、定格電圧でのゲートの電界を1MV/cm未満に低下させることができることが望ましい場合がある。

#### 【0020】

別の実施形態において、トランジスタデバイスは、ゲートと、ソースと、ドレインとを

10

20

30

40

50

有し、第1導電型の第1エピタキシャル層と、第1エピタキシャル層の上にある第2導電型の第2エピタキシャル層と、トランジスタデバイスの第1面に隣接する埋め込みチャネル層とを備える。埋め込みチャネル層は、第2エピタキシャル層の一部にわたって延びており、ゲート酸化膜層により少なくとも部分的に覆われる。トランジスタデバイスはまた、第1エピタキシャル層から下方に向かってトランジスタデバイスの本体内へある深さまで延びる第1導電型のウェル領域と、ウェル領域に隣接するJFET領域と、ウェル領域の下方にあるドリフト層とを含む。

#### 【0021】

当該デバイスのJFET領域内には、第1導電型の独立した領域が導入されており、これは一実施形態ではP+領域であってもよい。一実施形態において、P+領域はJFET領域のほぼ中央に導入され、ソースに接続されており、これによりデバイスのドレイン側からの電界を効果的に遮蔽する。JFET領域内に導入されたP+領域はP+ウェル領域より浅くてもよく、これにより電流の広がり抵抗も低減される。10

#### 【0022】

本開示の様々な実施形態を具体的に説明する前に、発明者によって行われた、本明細書で開示されたトランジスタデバイスをより深く理解することを可能にする調査研究について考察する。

#### 【0023】

図1は、ゲート酸化膜界面において電界を低下させないMOSFETデバイス10を示す。図1において、MOSFETデバイス10は、従来のDMOSFETである。従来のDMOSFET10は、半導体本体20上に位置するソース12、ゲート14、及びドレイン16を備え、ゲート14がゲート領域を絶縁する酸化膜層18の上にある状態である。DMOSFET10はP+型ウェル22を備える。P+型ウェル22は、半導体本体20内において約0.5ミクロン(μm)の深さまで注入されており、適切なレベル、一実施形態では例えば約 $5 \times 10^{18} \text{ cm}^{-3}$ と $5 \times 10^{20} \text{ cm}^{-3}$ の間のレベルにドープされるが、他のドーパントレベルを用いることもできる。N+ソース領域24は、適切なレベル、一実施形態では例えば約 $5 \times 10^{19} \text{ cm}^{-3}$ にドープされるが、他のドーパントレベルを用いることもできる。N+ソース領域24はP+型ウェル22に隣接しており、P+型ウェル22と埋め込みチャネル26との間に位置する。埋め込みチャネル26は、ソース領域24、P+型ウェル22、及び、半導体本体20の、活性領域の間にある部分、つまりJFET領域28にわたって延びている。2030

#### 【0024】

JFET領域28は一般的に、N型ドーパントを含有し得るN型ドリフト層の活性部分であり、P+型ウェル22等、2つのp型ウェルの間に位置している。JFET領域は一般的に、ゲート電圧を印加することによって各P型ウェルの表面に達するチャネル領域に接触している領域を指し得る。JFET領域28は、N+ソース領域24、チャネル領域26、N型ドリフト領域30、基板、及びドレイン電極16とともに電子の導電路を構成する。JFET領域28は、エピタキシャル成長によって設けられてもよく、イオン注入によって設けられてもよい。特定の実施形態においては、JFET領域28は約0.5ミクロン(μm)から約1.5ミクロン(μm)の範囲の厚さを有していてもよい。DMOSFET10の埋め込みチャネル26、JFET領域28、及び支持ドリフト領域30は、適切なレベルまでドープされていてもよい。一実施形態において、埋め込みチャネル26は約 $1 \times 10^{16} \text{ cm}^{-3}$ と $1 \times 10^{17} \text{ cm}^{-3}$ の間のレベルに、JFET領域28は約 $2 \times 10^{16} \text{ cm}^{-3}$ と $5 \times 10^{16} \text{ cm}^{-3}$ の間のレベルに、支持ドリフト領域30は約 $2 \times 10^{14} \text{ cm}^{-3}$ と $5 \times 10^{16} \text{ cm}^{-3}$ の間のレベルにそれぞれドープされていてもよいが、他のドーパントレベルを用いることもできる。40

#### 【0025】

典型的なDMOSFETにおいて、その製造プロセスは、層成長中のドーピングではなくイオン注入を用いることによって、チャネル表面を制御する。イオン注入はDMOSFETでは正確に行うことが難しく、得られるデバイスはチャネル移動度が制限される。50

た、図1に示される従来のDMOSFET10は、デバイスのJFET領域28の中央にあるゲート酸化膜に高電界を有する可能性がある。

#### 【0026】

この高電界が界面物質やゲート酸化膜内の欠陥と組み合わされると、ドレインが正バイアスが高い状況下に置かれる長時間の阻止動作状態で、ゲート酸化膜が破壊される結果となり得る。また、図1に示される従来のDMOSFET10は、ドレインが正バイアスが高い状況下に置かれている長時間の阻止動作中に生じ得るホットキャリア注入による悪影響を受ける可能性もある。

#### 【0027】

図2は、ゲート酸化膜界面において電界を低下させない、標準的なDMOSFETセルの別の実施形態を示す。図2において、DMOSFET32は、DMOSFETの本体上に位置するソース34、ゲートコンタクト36、及びドレイン38を備え、ゲートコンタクト36がゲート領域を絶縁する酸化膜層40の上にある状態である。DMOSFET32はN型支持ドリフト層42及びN+基板44を備えていてもよく、一実施形態では、N+基板44は炭化ケイ素基板であってもよい。DMOSFET32はまた、少なくとも1つのP+領域46と、少なくとも1つのN+領域48とを備えていてもよい。DMOSFETはまた、少なくとも1つのP+領域46を有するDMOSFET32の本体内へと注入された、少なくとも1つのP+型ウェル領域50も備えていてもよい。少なくとも1つのN+ソース領域48は適切なレベル（一実施形態では例えば約 $5 \times 10^{19} \text{ cm}^{-3}$ ）にドープされていてもよく、少なくとも1つのP+領域46に隣接している。JFET領域52は酸化膜層40の下にあり、適切なレベル、一実施形態では例えば約 $2 \times 10^{16} \text{ cm}^{-3}$ と $5 \times 10^{16} \text{ cm}^{-3}$ の間のレベルにドープされる。DMOSFET32の支持ドリフト領域52も適切なレベル（一実施形態では例えば約 $2 \times 10^{14} \text{ cm}^{-3}$ と $5 \times 10^{16} \text{ cm}^{-3}$ の間のレベル）にドープされていてもよく、基板44（任意の材料で形成され得るが、一実施形態ではN+炭化ケイ素基板であってもよい）によって、ドレイン38に至るまで支持される。

#### 【0028】

典型的な従来技術のDMOSFETにおいて、その製造プロセスは、層成長中のドーピングではなくイオン注入を用いることによって、チャネル表面を制御する。イオン注入はDMOSFETでは正確に行なうことが難しく、得られるデバイスはチャネル移動度が制限される。また、図2に示されているDMOSFET32は、デバイスのJFET領域52の中央にあるゲート酸化膜において、高電界を有する可能性がある。この高電界が界面物質やゲート酸化膜内の欠陥と組み合わされると、ドレインが正バイアスが高い状況下に置かれている長時間の阻止動作状態で、ゲート酸化膜が破壊される結果となり得る。また、図2に示されるDMOSFET32は、ドレインが正バイアスが高い状況下に置かれる長時間の阻止動作中に生じ得るホットキャリア注入による悪影響を受ける可能性もある。

#### 【0029】

図1及び図2に示した従来技術のMOSFETデバイスは、ゲート酸化膜界面における電界を低下させるとともに、逆バイアスがかかった動作中での偶発的な電圧を阻止する能力を持ちながら、オン状態での電流の流れの最大値を増大させるトランジスタの設計へと変更する共通の要求を示している。例示のために、図1～3に示されるデバイスの基板とドリフト層はそれぞれ炭化ケイ素（SiC）で形成されていることが想定されているが、他の半導体材料を用いてもよい。

#### 【0030】

ゲート酸化膜界面における高電界に対処する手法の1つとして、JFETギャップを狭めることが挙げられる。しかしながら、従来のMOSFETデバイス上でJFETギャップを（順電圧降下を犠牲にせずに）狭めることは、ドレインが正バイアスが高い状況下に置かれる長時間の阻止動作中でのデバイスの信頼性を向上させることはできるが、故障をなくすことはできないということを、本発明の発明者は認識してきた。

#### 【0031】

10

20

30

40

50

ゲート酸化膜界面において電界を低下させて、ドレインが正バイアスが高い状況下に置かれる長時間の阻止動作中における故障をなくすために、新規のトランジスタ構造が提案される。J F E T領域内に、少なくとも1つの独立したP+領域が導入される。一実施形態において、この少なくとも1つのP+領域は、J F E T領域のほぼ中央に導入され、ソースに接続されており、これによりデバイスのドレイン側からの電界を効果的に遮蔽する。また、J F E T領域内に導入された少なくとも1つのP+領域はP+ウェル領域より浅くてもよく、これによって電流の広がり抵抗も低減される。

#### 【0032】

次に、図3Aを参照すると、提案された新規な構造が示されている。図3Aは、少なくとも1つのP+領域をJ F E T領域に導入したために、ゲート酸化膜界面において電界が低下しているデバイスを示す。図3Aには正方形又は矩形として描かれているが、J F E T領域に導入された少なくとも1つのP+領域は任意の形状とすることができます。また、J F E T領域に導入されたP+領域（又は複数のP+領域）は、J F E T領域の表面と同一面上にあってもよいし、J F E T領域の上面よりも下方にあってもよい。

#### 【0033】

図3Aにおいて、本デバイスはDMOSFETであるが、ソース、ゲート、ゲート酸化膜層、P+ウェル、及びJ F E T領域を有する、MOSFET、UMOSFET、IGBT等を含むがこれらに限定されない任意の種類のデバイスであってもよい。図1に示される従来のDMOSFETのように、この新たな構造はソース34及びゲートコンタクト36を備え、ゲートコンタクト36がゲート領域を絶縁する酸化膜層40の上にある。本デバイスはP+型ウェル50を備える。P+型ウェル50は、デバイス内において約0.5ミクロン(μm)の深さまで注入されており、適切なレベル、一実施形態では例えば約 $5 \times 10^{18} \text{ cm}^{-3}$ と $5 \times 10^{20} \text{ cm}^{-3}$ の間のレベルにドープされているが、他のドーパントレベルを用いることもできる。N+ソース領域48は適切なレベル（一実施形態では例えば約 $5 \times 10^{19} \text{ cm}^{-3}$ であるが、他のドーパントレベルを用いることもできる）にドープされており、P+ウェル50に隣接しており、P+型ウェル50と埋め込みチャネル54との間に位置する。埋め込みチャネル54はデバイスの活性領域の間にある部分、つまりJ F E T領域52にわたって延びていてもよい。

#### 【0034】

J F E T領域52のようなJ F E T領域は一般的に、N型ドーパントを含有し得るN型ドリフト層の活性部分であり、2つのP型ウェルの間、もしくはP+型ウェル50等のP+型ウェルの内部に位置している。J F E T領域は一般的に、ゲート電圧を印加することによってP型ウェルの表面に達するチャネル領域に接触している領域を指し得る。J F E T領域52は、N+ソース領域48、チャネル領域54、N型ドリフト領域42、基板、及びドレイン（図3Aには示さず）と共に電子の導電路を構成する。J F E T領域52は、エピタキシャル成長によって設けられてもよく、イオン注入によって設けられてもよい。特定の実施形態において、J F E T領域52は約0.5ミクロン(μm)から約1.5ミクロン(μm)の範囲の厚さを有していてもよい。

#### 【0035】

本デバイスの埋め込みチャネル54、J F E T領域52、及び支持ドリフト領域42は、適切なレベルまでドープされていてもよい。一実施形態において、埋め込みチャネル54は約 $1 \times 10^{16} \text{ cm}^{-3}$ と $1 \times 10^{17} \text{ cm}^{-3}$ の間のレベルに、J F E T領域52は約 $1 \times 10^{16} \text{ cm}^{-3}$ と $5 \times 10^{17} \text{ cm}^{-3}$ の間のレベルに、支持ドリフト領域42は約 $1 \times 10^{14} \text{ cm}^{-3}$ と $5 \times 10^{16} \text{ cm}^{-3}$ の間のレベルにそれぞれドープされていてもよいが、他のドーパントレベルを用いることもできる。

#### 【0036】

新たに提案されたデバイスでは、図3Aに示されているように、J F E T領域52内に、少なくとも1つの独立したP+領域46'、例えば独立したP+領域46'が導入される。図3Aでは正方形又は矩形として描かれているが、J F E T領域52に導入された少なくとも1つの独立したP+領域46'は任意の形状とすることができます。また、J F E

10

20

30

40

50

T領域52に導入された少なくとも1つの独立したP+領域46'は、JFET領域52の表面と同一面上にあってもよく、あるいはJFET領域52の上面よりも下方にあってもよい。一実施形態において、独立したP+領域46'は、アルミニウムを約 $1 \times 10^{18} \text{ cm}^{-3}$ 以上のドープで注入することによって形成されてもよい。一実施形態において、独立したP+領域46'はJFET領域52のほぼ中央に導入され、ソース34に接続されており、これによりデバイスのドレイン側からの電界を効果的に遮蔽する。JFET領域52内に導入された独立したP+領域46'はP+型ウェル領域50よりも浅くてもよく、これによって電流の広がり抵抗も低減される。

#### 【0037】

一実施形態において、独立したP+領域46'はデバイス内に向かって深さが約0.2ミクロン(μm)であるが、他の深さを用いてもよい。また、一実施形態において、JFET領域52内に導入された独立したP+領域46'は、幅が0.5ミクロン(μm)と1.0ミクロン(μm)の間であってもよいが、他の幅を使用してもよい。図3に示されるように、独立したP+領域46'は、シミュレーションの目的のみに使用されるオーミック接触(独立したP+領域46'内に四角で示されている)を有していてもよい。実際の際は、独立したP+領域46'はソース34に短絡される。

#### 【0038】

図3Bは、JFET領域52内に導入された複数のP+領域46', 46"を備える、新規な構造を有する代替のトランジスタデバイスを示す。図3Bには、JFET領域52内に導入されたP+領域(46', 46")が2つあるが、任意の数のP+領域46', 46"をJFET領域52内に導入してもよい。種々の実施形態において、P+領域46', 46"は、様々な形状を有することができ、JFET領域52の上面の下方に異なる注入プロファイルを有することも可能である。図3Bの実施形態では、P+領域46', 46"はJFET領域52の上面の下方にある。特に、一実施形態において、P+領域46'又はP+領域46"がソース34に短絡されている限り、1つ以上のP+領域46', 46"をJFET領域52の上面に向かって不純物濃度が低くなる(retrograde)ように構成することによって、MOS界面に対するイオン注入損傷を低減することが可能である。

#### 【0039】

図4A～4Cは、種々のデバイスの順方向電流伝導分布を示したものである。図4Aは、約2.6ミクロン(μm)という典型的なJFETギャップを有する、対照用の従来のMOSFETの順方向電流伝導分布を示す。図4Bは、約0.8ミクロン(μm)という狭められたJFETギャップを有する、対照用のMOSFETの順方向電流伝導分布を示す。図4Bから分かるように、狭められたJFETギャップを有するMOSFETによって、対照用の従来のMOSFETと比較して、広がり抵抗が大幅に増大する。これは、狭められたJFETギャップを有するMOSFETは、狭いJFET領域において伝導の妨げになる部分を発生させてしまうことを意味する。図4Cは、JFETギャップ内に導入されたP+領域と、約2.6ミクロン(μm)という標準的なJFETギャップとを有する提案された構造のMOSFETの順方向電流伝導分布を示す。図4Cから分かるように、JFETギャップ内に導入されたP+領域を備える提案された構造を有するMOSFETは、狭められたJFETギャップを有するMOSFETに伴う広がり抵抗の上昇がなく、標準的なJFETギャップを有する従来のMOSFETにより近いものとなっている。

#### 【0040】

さらに、図5から分かるように、JFETギャップ内に導入されたP+領域を有する提案されたデバイスはまた、標準的なJFETギャップを有する従来のMOSFETと同じオン抵抗を示している。図5は、図4A～4Cに示すデバイスの各々についてドレイン電圧対ドレイン電流密度を測定した際の順方向IV特性を示したものである。図5から分かるように、狭められたJFETギャップを有するMOSFETは、標準的なJFETギャップを有する従来のMOSFETと比べてオン抵抗が低く、一方、JFETギャップ内に導入されたP+領域を有する提案されたデバイスはまた、標準的なJFETギャップを有

する従来のMOSFETと同等のオン抵抗を示す。

#### 【0041】

図6A～6Cは、対照用のG2-1200V DMOSFETと比較した、図4A～4Cに示すデバイスの等電界線(electrical field contour)を示す。このシミュレーションでは960ボルトのドレイン電圧を使用した。図6A～6Cから分かるように、JFETギャップ内に導入されたP+領域を有する提案されたデバイスは、標準的なJFETギャップを有する従来のDMOSFETと比べて、ゲート酸化膜界面において電界が低下している(図6C)。

#### 【0042】

このことは、ゲート酸化膜の上面及びゲート酸化膜の中央での電界分布を示した図7でも見受けられる。図7から分かるように、JFETギャップ内に導入されたP+領域を有する提案された構造において、オン抵抗を全く犠牲にせずに電界の大幅な低下が達成されている。

#### 【0043】

図3の提案された構造は、種々の標準的な技術のいずれかに従って製造されてもよい。同様に、JFET領域52内に導入されたP+領域46'は、本開示の一実施形態において種々の標準的な技術のいずれかに従って形成されてもよい。そのプロセスを通じて、例示的な材料、ドーピング型、ドーピングレベル、構造の寸法、及び選択された代替物が概説されている。これらの態様は単に例証のためのものであり、本明細書で開示された概念及び後に続く特許請求の範囲は、これらの態様に限定されない。

#### 【0044】

本明細書で説明されている改良されたトランジスタ構造の製造方法は、従来技術のDMOSFETに効果的に使用されてきた技術を向上させるものである。しかしながら、従来使われてきた方法は、トランジスタデバイスがそのJFET領域内に導入されたP+領域を備えるという事実を説明するために改変されている。上述したように、本発明に係るMOSFETは、任意選択的に、公知の手段により形成された炭化ケイ素基板を備えていてもよい。再び図2及び図3を参照すると、4H-SiCからなるドリフト領域層42を、基板44上にエピタキシャル成長させる。本方法は、第1導電型、好適にはP+型のドープされたウェル領域50を少なくとも1つ形成することを含む。ウェル領域50は任意の一般的な技術によって形成可能であるが、好ましくはドーパントをデバイス内に、デバイスの上部から下方に向かって1ミクロン( $\mu m$ )よりも深い深さまで注入することによって形成される。この第1層50上には、第2導電型(例えば一実施形態ではN+型)の第2層48が形成される。この時点で、トランジスタデバイスの本体は、上部から底部への電流導通を制御するための、好ましくは炭化ケイ素からなる半導体層を備える。

#### 【0045】

先に構造要素46, 48, 50, 52をイオン注入によって形成し、次に上面に層54をエピタキシーによって成長させる。埋め込みチャネル層54をエピタキシーによって形成し、埋め込みチャネル層54は、P+型ウェル50とN+ソース領域48の上方にある領域において、選択的にエッチングされる。これは、これらの層とのコンタクトを形成するためである。その後、チャネル54を二酸化ケイ素等のゲート絶縁層(ゲート酸化膜40)で覆い、その上にゲートコンタクト36が形成される。次に、任意の既知の方法に従って、JFET領域内に第1導電型の領域を導入する。一実施形態ではこの第1導電型の領域はP+領域である。この種のトランジスタと同様に、ソースコンタクト34及びドレンコンタクト38を設けることによってトランジスタデバイスが完成する。

#### 【0046】

本明細書で説明されている方法を用いて、ゲート酸化膜界面において電界を低下させるためにJFET領域内に導入されたP+領域を備える他のトランジスタを製造することも可能である。したがって、本発明は種々のMOSFETに限定されるものではなく、絶縁ゲートバイポーラトランジスタや金属酸化物半導体制御サイリスタに等しく適用可能である。これらのデバイスのすべてにおいて、製造に用いられる半導体材料は炭化ケイ素が好

10

20

30

40

50

適であるが、本発明はこのようなものに限定されない。

【0047】

当業者であれば、本開示の好適な実施形態の改良や改変を認識するであろう。このような改良や改変はすべて、本明細書にて開示された概念及び以下に続く特許請求の範囲内であるとみなされる。

【0048】

本明細書で開示された構造を製造するのに用いられ得る方法の例には、以下に記す方法が含まれるが、これに限定されない：トランジスタデバイスの製造方法であって、ゲートがゲート酸化膜層に少なくとも部分的に接触するように、ソース及びゲートを設ける工程と、ゲート酸化膜上における電界を低下させるために、P+型ウェル領域に隣接する接合型電界効果（JFET）領域内に少なくとも1つのP+領域を設ける工程とを含み、JFET領域内に導入された少なくとも1つのP+領域がゲート酸化膜において電界を低下させる、トランジスタデバイスの製造方法。また、一実施形態において、トランジスタデバイスの本体は炭化ケイ素を含んでいてもよい。一実施形態において、本方法は上記で開示した方法のいずれを含んでいてもよく、少なくとも1つのP+領域はJFET領域のほぼ中央に設けられる。さらに別の実施形態において、本方法は上記で開示した方法のいずれかを含んでいてもよく、さらに、少なくとも1つのP+領域をソースに接続することを含んでいてもよい。一実施形態において、少なくとも1つのP+領域の深さは約0.1ミクロン（μm）と約0.3ミクロン（μm）の間の深さであり、少なくとも1つのP+領域の幅は約0.5ミクロン（μm）と約1.0ミクロン（μm）の間の幅である。この開示された方法は、約2.0ミクロン（μm）と約3.6ミクロン（μm）の間のJFET領域の幅を与えてよい。10

【0049】

上述の方法に加えて、トランジスタデバイスの製造方法は、基板上にドリフト層を設ける工程と、ドリフト層上にウェル領域を注入する工程と、第1エピタキシャル層を、該第1エピタキシャル層がウェル領域の少なくとも一部を覆うように設ける工程と、第1エピタキシャル層上に第2エピタキシャル層を設ける工程と、第2エピタキシャル層の一部の上方に埋め込みチャネル層を設ける工程と、ゲートがゲート酸化膜に少なくとも部分的に接触するように、ソース及びゲートを設ける工程と、ウェル領域に隣接する接合型電界効果（JFET）領域内に、少なくとも1つのP+領域を設ける工程とを含んでいてもよい。20

【0050】

別の実施形態において、JFET領域内に導入された少なくとも1つのP+領域は、ゲート酸化膜において電界を低下させる。別の実施形態において、トランジスタデバイスの本体は炭化ケイ素を含んでいてもよい。一実施形態において、少なくとも1つのP+領域は、JFET領域のほぼ中央に設けられる。別の実施形態において、本方法は上記で開示した任意の方法を含んでいてもよく、さらに本方法では、少なくとも1つのP+領域をソースに接続することを含む。さらに別の実施形態において、本方法は上記で開示した方法の任意の方法を含んでいてもよく、P+領域は深さがウェル領域よりも浅い。一実施形態において、少なくとも1つのP+領域は深さが約0.1ミクロン（μm）と約0.3ミクロン（μm）の間である。別の実施形態において、少なくとも1つのP+領域は幅が約0.5ミクロン（μm）と約1.0ミクロン（μm）の間である。さらに別の実施形態において、JFET領域の幅は約2.0ミクロン（μm）と約3.6ミクロン（μm）の間である。30

【0051】

上述の方法に加えて、MOSFETの製造方法は、ドリフト層上にP+型エピタキシャル層を設ける工程と、P+型エピタキシャル層上にN+型領域を設ける工程と、MOSFETの第1面に隣接する埋め込みチャネル層を、N+型領域の一部にわたって延びるように設ける工程と、P+型エピタキシャル層から下方に向かってMOSFETの本体内へある深さまで延びるP+型ウェルを形成する工程と、ゲートがゲート酸化膜に少なくとも部40

分的に接触するようにソース及びゲートを設ける工程と、ゲート酸化膜において電界を低下させるために、P+型ウェル領域に隣接する接合型電界効果（J F E T）領域内にP+領域を設ける工程とを含んでいてもよい。一実施形態において、J F E T領域内に導入された少なくとも1つのP+領域は、ゲート酸化膜において電界を低下させる。別の実施形態において、M O S F E Tの本体は炭化ケイ素を含んでいてもよい。さらに別の実施形態において、少なくとも1つのP+領域は、J F E T領域のほぼ中央に設けられる。M O S F E Tの製造方法は、少なくとも1つのP+領域をソースに接続することを含む。一実施形態において、少なくとも1つのP+領域は、深さがP+ウェル領域よりも浅い。別の実施形態において、少なくとも1つのP+領域は深さが約0.1ミクロン(μm)と約0.3ミクロン(μm)の間である。さらに別の実施形態において、少なくとも1つのP+領域は幅が約0.5ミクロン(μm)と約1.0ミクロン(μm)の間である。別の実施形態において、J F E T領域の幅は約2.0ミクロン(μm)と約3.6ミクロン(μm)の間である。

10

【図1】

FIG. 1

(従来技術)

【図2】

FIG. 2

【図3A】

【図3B】

FIG. 3A

FIG. 3B

【図4】

FIG. 4C

FIG. 4B

FIG. 4A

【図5】

FIG. 5

【図6】

【図7】

FIG. 7

---

フロントページの続き

(51)Int.Cl.

F I

H 01 L 29/78 655 A

(72)発明者 ハル ブレット

アメリカ合衆国 ノースカロライナ州 27614 ローリー ケイツブリッジ レーン 210

1

審査官 綿引 隆

(56)参考文献 特開2011-060930(JP, A)

特開2004-022693(JP, A)

特開2004-193578(JP, A)

特開平03-142972(JP, A)

特開2011-258635(JP, A)

特開平07-078978(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 331

H 01 L 21 / 336

H 01 L 29 / 739

H 01 L 29 / 744

H 01 L 29 / 78