(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6319882号

(P6319882)

(45) 発行日 平成30年5月9日(2018.5.9)

(24) 登録日 平成30年4月13日(2018.4.13)

(51) Int.Cl.

H02M 3/155 (2006.01)

F 1

H02M 3/155

H

請求項の数 5 (全 15 頁)

(21) 出願番号 特願2014-29427 (P2014-29427)

(22) 出願日 平成26年2月19日 (2014.2.19)

(65) 公開番号 特開2014-166135 (P2014-166135A)

(43) 公開日 平成26年9月8日 (2014.9.8)

審査請求日 平成29年2月17日 (2017.2.17)

(31) 優先権主張番号 13/774,340

(32) 優先日 平成25年2月22日 (2013.2.22)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

エヌエックスピー ユーエスエイ インコ

ーポレイテッド

N X P U S A, I n c.

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100142907

弁理士 本田 淳

(72) 発明者 イヴァン カルロス リベイロ ナシメント

ブラジル国 13087-200 サンパ

ウロ カンピナス ルア ジョアン チャ

ッティ 102 カーサ 9

最終頁に続く

(54) 【発明の名称】ハイブリッド・スイッチ・モード電源(SMP S)のための遷移制御

## (57) 【特許請求の範囲】

## 【請求項 1】

ハイブリッド・スイッチ・モード電源(SMP S)であって、該ハイブリッド・スイッチ・モード電源が線形モードにおいて動作するときに可変デューティサイクルに比例する出力電圧を生成するように構成されている線形回路であって、第1の入力ノードで受け取った基準電圧と、第2の入力ノードで受け取った前記出力電圧との間の比較に基づいて出力ノードに誤差電圧を供給するように構成されている誤差増幅器を含む前記線形回路と、

前記線形回路に結合されているヒステリシス回路であって、該ヒステリシス回路は、該ハイブリッド・スイッチ・モード電源がヒステリシスマードにおいて動作するときに前記可変デューティサイクルが2つの所定の値のうちの1つをとるようにするように構成されている、前記ヒステリシス回路と、

前記線形回路および前記ヒステリシス回路に結合されている遷移制御回路であって、該遷移制御回路は、第1のスイッチ、第2のスイッチ、および第3のスイッチに結合され、該遷移制御回路は、保持信号を前記第1のスイッチ、前記第2のスイッチ、および前記第3のスイッチに印加することによって、該ハイブリッド・スイッチ・モード電源が前記ヒステリシスマードから前記線形モードに遷移するのに応答して、前記線形回路の少なくとも一部分をバイパスするように構成され、前記線形回路のバイパスされる少なくとも一部分は、前記誤差増幅器の第1の入力ノードから出力ノードまでをバイパスする経路を含み、前記第1のスイッチおよび第2のスイッチは、前記経路に配置され、前記保持信号は、

10

20

前記第1のスイッチおよび第2のスイッチをそれぞれ閉鎖するように構成され、前記保持信号は、第3のスイッチを開鎖して前記誤差増幅器の出力ノードを、選択された電圧レベルにさせるようにさらに構成される、前記遷移制御回路とを備える、ハイブリッド・スイッチ・モード電源。

#### 【請求項2】

前記ヒステリシス回路は、前記出力電圧が低閾値を下回って降下するのに応答して、前記可変デューティサイクルが所定の高い値をとるようにするように構成されている、請求項1に記載のハイブリッド・スイッチ・モード電源。10

#### 【請求項3】

前記ヒステリシス回路は、前記出力電圧が高閾値を上回って上昇するのに応答して、前記可変デューティサイクルが所定の低い値をとるように構成されている、請求項1に記載のハイブリッド・スイッチ・モード電源。10

#### 【請求項4】

前記遷移制御回路は、前記出力電圧に関して過電圧または不足電圧状態を特定するように構成されている、請求項1に記載のハイブリッド・スイッチ・モード電源。

#### 【請求項5】

ハイブリッド・スイッチ・モード電源(SMPS)を動作させる方法であって、線形動作モードにある間に、デューティサイクルに比例する出力電圧を生成すること、前記デューティサイクルが、不足電圧の発生に応答して第1の所定値を、または過電圧の発生に応答して第2の所定値をとるようにするためにヒステリシス動作モードに入ること、20

前記ヒステリシス動作モードから前記線形動作モードに前記ハイブリッド・スイッチ・モード電源を戻す際に、選択された期間において保持信号を生成することによって前記ヒステリシス動作モードおよび前記線形動作モードの間の遷移を停止することであって、前記保持信号は、第1のスイッチおよび第2のスイッチをそれぞれ閉鎖することによって前記ハイブリッド・スイッチ・モード電源内の誤差増幅器の入力ノードから出力ノードまでをバイパスし、前記保持信号は、第3のスイッチを閉鎖することによってデジタル的に選択された電圧を前記誤差増幅器の出力ノードに印加させる、前記遷移を停止すること、

前記選択された期間において後続の不足電圧または過電圧の発生が起こることに応答して、前記デジタル的に選択された電圧を段階的に増大又は低減すること、を備える、方法30

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、概して電子デバイスに関し、より具体的には、ハイブリッド・スイッチ・モード電源(hybrid Switched-Mode Power Supply: SMPS)における遷移制御のためのシステムおよび方法に関する。

##### 【背景技術】

##### 【0002】

「電源」は、電気または電子デバイスにエネルギーを供給する回路である。現代の電子機器に使用される電源は、電池、直流(DC)電源、交流(AC)電源などを含む。現代の電源の一例が、スイッチモード電源(SMPS)である。おおまかに言えば、SMPSは、多くの場合SMPSの入力電圧とは異なるレベルにおいて調整された出力電圧を負荷に供給するのに使用される。40

##### 【0003】

一般的に、SMPSは、トランジスタのゲートに電圧をスイッチング方式で、所与のデューティサイクル(すなわち、オン時間とオフ時間との比)で印加するように構成されている回路を含み、それによって、SMPSのデューティサイクルが出力電圧を調整する。動作時、トランジスタはその時間のほとんどを、その2つの最低散逸状態(two lowest d

50

issipation states)（「完全オン」および「完全オフ」）の間のスイッチングに費やすため、消費エネルギーがより少ない。それにもかかわらず、特定のタイプの集積回路（たとえば、マイクロプロセッサ、マイクロコントローラなど）の特性である負荷変動が、依然としてS M P S の出力電圧を望ましくない様式で変化させる可能性がある。従って、S M P S がより迅速に突然の負荷変化に追いつくことを可能にする試みにおいて、線形モードおよびヒステリシスモードにおいて動作することが可能であるハイブリッドS M P S が開発されている。

#### 【0004】

ハイブリッドS M P S において、出力電圧が高閾値と低閾値との間であるとき、負荷変化はS M P S のデューティサイクルを線形的に増大または低減することによって対処される。このとき、出力電圧が高閾値または低閾値のいずれかに達する場合、S M P S はヒステリシスモードにおいて動作する。具体的には、ヒステリシスモードにおいて、出力電圧が高閾値に達すると、デューティサイクルは最低規定値（たとえば、0%）に変更される。逆に、出力電圧が低閾値に達すると、S M P S はその最高規定デューティサイクル（たとえば、100%）を適用する。このように、ハイブリッドS M P S は、負荷変動後にその線形動作範囲内の適切な値にその出力電圧を戻してステアリングすることが可能であり得る。

10

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

20

本発明者らは、ハイブリッドS M P S におけるヒステリシスモードから線形モードへの遷移が良好に操作されない場合があることを発見した。たとえば、S M P S がヒステリシスモードにおいて動作した後に線形モードに戻るとき、出力電圧は依然として過渡状態にある場合があり、その直後に高閾値または低閾値に達する場合があり、従って、負荷に損傷を与えるか、または他の様態でシステムの動作を準最適なものにする場合がある、線形モードとヒステリシスモードとの間の永続的な振動（ヒステリシス振動と称される）が促進される。

#### 【課題を解決するための手段】

#### 【0006】

30

本願発明の一側面は、ハイブリッド・スイッチ・モード電源（S M P S）であって、該ハイブリッド・スイッチ・モード電源が線形モードにおいて動作するときに可変デューティサイクルに比例する出力電圧を生成するように構成されている線形回路と、前記線形回路に結合されているヒステリシス回路であって、該ヒステリシス回路は、該ハイブリッド・スイッチ・モード電源がヒステリシスモードにおいて動作するときに前記デューティサイクルが2つの所定の値のうちの1つをとるようにするように構成されている、前記ヒステリシス回路と、前記線形回路および前記ヒステリシス回路に結合されている遷移制御回路であって、該遷移制御回路は、該ハイブリッド・スイッチ・モード電源が前記ヒステリシスモードから前記線形モードに遷移するのに応答して、前記線形回路の少なくとも一部分をバイパスするように構成されている。

#### 【0007】

40

本願発明の一側面は、ハイブリッド・スイッチ・モード電源（S M P S）を動作させる方法であって、線形動作モードにある間に、デューティサイクルに比例する出力電圧を生成すること、前記デューティサイクルが、不足電圧の発生に応答して第1の所定値を、または過電圧の発生に応答して第2の所定値をとるようにするためにヒステリシス動作モードに入ること、少なくとも部分的に、前記デューティサイクルを、選択された期間の間に後続の不足電圧または過電圧の発生が起こる可能性を低減するように制御することによって、前記線形動作モードに戻ることを備える。

#### 【0008】

本願発明の一側面は、電子チップであって、ハイブリッド・スイッチ・モード電源（S M P S）の線形回路およびヒステリシス回路に結合されている遷移制御回路を備え、該遷

50

移回路は、前記ハイブリッド・スイッチ・モード電源のヒステリシス動作モードから線形動作モードへの遷移を容易にするように構成されている。

**【図面の簡単な説明】**

**【0009】**

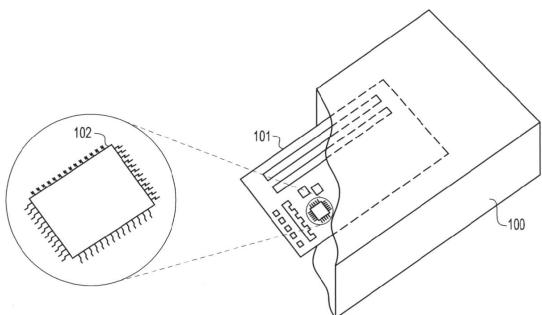

【図1】特定の実施形態に応じた、1つ以上の電子チップを有するデバイスのプリント回路基板（P C B）の一例の図。

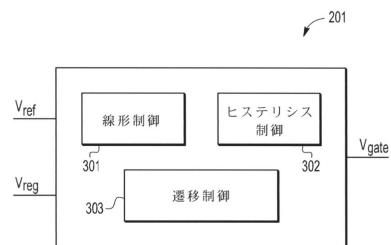

【図2】特定の実施形態に応じた、ハイブリッド・スイッチ・モード電源（S M P S）の一例の回路図。

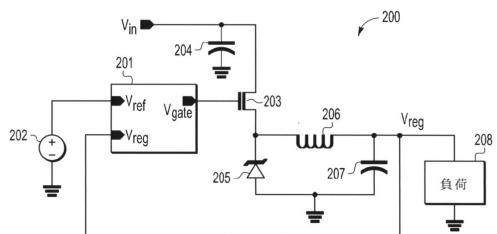

【図3】特定の実施形態に応じた、制御回路の一例のブロック図。

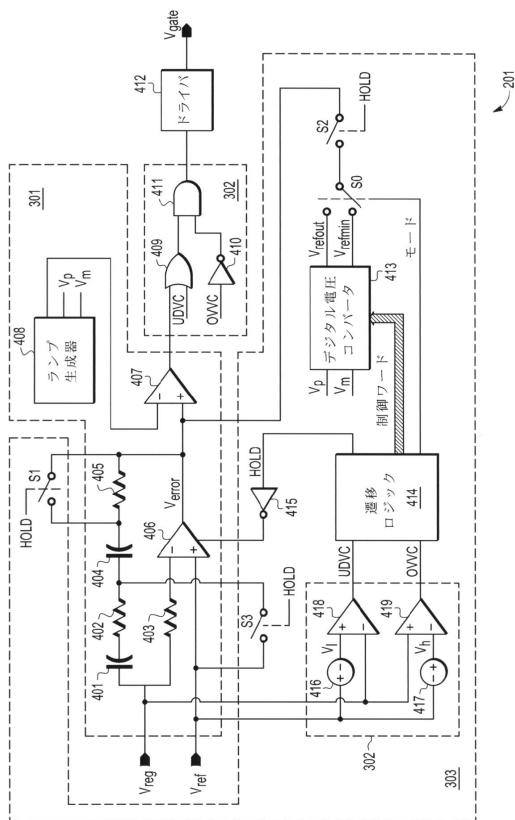

【図4】特定の実施形態に応じた、制御回路の一例の回路図。

10

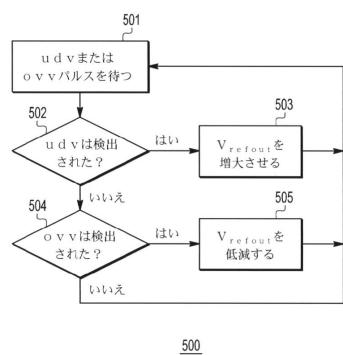

【図5】特定の実施形態に応じた、遷移制御回路の動作を示すフローチャート。

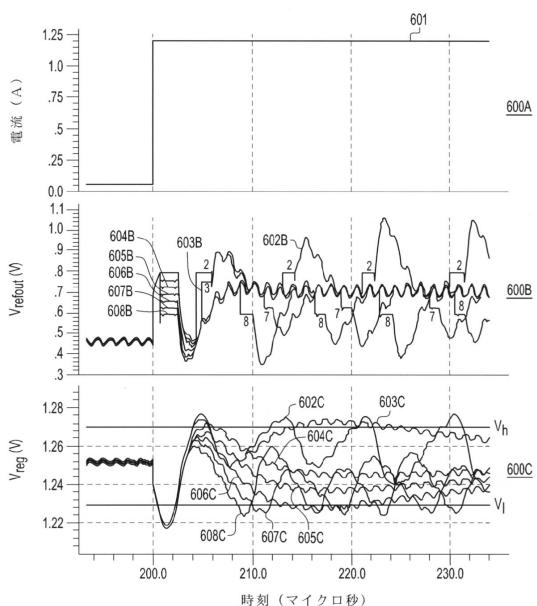

【図6】特定の実施形態に応じた、遷移制御回路の電圧選択動作を示すグラフ。

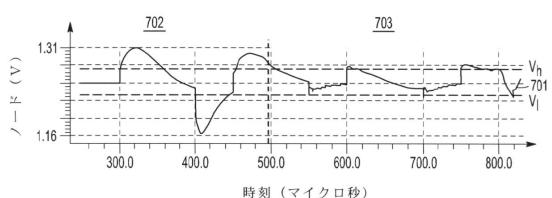

【図7】特定の実施形態に応じた、ハイブリッドS M P Sの動作を比較したグラフ。

**【発明を実施するための形態】**

**【0010】**

本発明（複数の場合もあり）は例として示されており、添付の図面によって限定されない。図面において、同様の参照符号は類似の要素を示す。図面内の要素は簡潔かつ明瞭にするために示されており、必ずしも原寸に比例して描かれてはいない。

**【0011】**

本明細書において、ハイブリッド・スイッチ・モード電源（S M P S）における遷移制御のためのシステムおよび方法が開示される。「ハイブリッド」という用語は、S M P Sが、異なる時点においてヒステリシスモードまたは線形モードのいずれかにおいて動作することが可能であることを指す。特定の実施形態において、これらのシステムおよび方法は、負荷変動、入力電圧変動、温度変化などの後に、ハイブリッドS M P Sがヒステリシスモードから線形モードに戻って遷移することを容易にすることができる。ハイブリッドS M P Sをヒステリシスモードにおいて動作するようにする、最初の過電圧（overvoltage）または不足電圧（undervoltage）の発生が検出されると、下記に記載の特定のシステムおよび方法は、選択された監視期間の間に後続の過電圧または不足電圧の発生の可能性を低減するように動作することができる。たとえば、遷移制御回路が、ヒステリシスモードと線形モードとの間のハイブリッドS M P Sの遷移中のハイブリッドS M P Sの線形回路の動作の態様を、過電圧または不足電圧状態を最小限に抑えるかまたは低減するように制御することができる。

20

**【0012】**

多くの実施態様において、本明細書に開示のシステムおよび方法は、たとえば、サーバ、デスクトップ、ラップトップ、スイッチ、ルータなどのようなコンピュータ・システムまたは情報技術（I T）製品、携帯電話機、タブレット、テレビセット、カメラ、音響システムなどの遠隔通信ハードウェア、消費者装置または消費財、撮像、診断、もしくは治療用機器などの科学機器、産業ロボット、医療用または実験用電子機器、自動車、バス、トラック、列車、船舶、航空機などの運搬用車両、軍装備品などを含む、広範な電子デバイス内に組み込まれてもよい。より一般的には、これらのシステムおよび方法は、1つ以上の電子部品または構成要素を有する任意のデバイスまたはシステム内に組み込まれてもよい。

30

**【0013】**

図1を参照すると、電子デバイス100のブロック図が描かれている。特定の実施形態において、電子デバイス100は、上記の電子デバイスのいずれか、または任意の他の電子デバイスであってもよい。図示されているように、電子デバイス100は、1つ以上のプリント回路基板（P C B）101を含み、当該P C B 101のうちの少なくとも1つは、1つ以上のチップ102を含む。いくつかの実施態様において、チップ102内の1つ以上の集積回路（I C）は、ハイブリッドS M P Sならびに／またはハイブリッドS M P Sにおける遷移制御のためのシステムおよび方法を実装してもよい。

40

50

## 【0014】

I C (複数の場合もあり)の例は、たとえば、システム・オン・チップ (S o C)、特定用途向け集積回路 (A S I C)、デジタル信号プロセッサ (D S P)、フィールドプログラマブル・ゲート・アレイ (F P G A)、プロセッサ、マイクロプロセッサ、コントローラ、マイクロコントローラ (M C U)、グラフィックス・プロセッシング・ユニット (G P U)などを含んでもよい。付加的にまたは代替的に、I C (複数の場合もあり)は、たとえば、ランダム・アクセス・メモリ (R A M)、静态RAM (S R A M)、磁気抵抗R A M (M R A M)、不揮発性R A M (「フラッシュ」メモリなどのようなN V R A M)、および / または同期D R A M (S D R A M)のようなダイナミックR A M (D R A M)、ダブル・データ・レートR A M、消去可能プログラマブルR O M (E P R O M)、電気的消去可能プログラマブルR O M (E E P R O M)などのメモリ回路またはデバイスを含んでもよい。付加的にまたは代替的に、I C (複数の場合もあり)は、たとえば、アナログ - デジタル変換器 (A D C)、デジタル - アナログ変換器 (D A C)、位相ロックループ (P L L)、発振器、フィルタ、増幅器などのような、1つ以上の混合信号またはアナログ回路を含んでもよい。付加的にまたは代替的に、I C (複数の場合もあり)は、1つ以上の微小電気機械システム (M E M S)、ナノ電気機械システム (N E M S)などを含んでもよい。

## 【0015】

従って、チップ102内のI Cはいくつかの異なる部分、エリア、または領域を含んでもよい。これらのさまざまな部分は、1つ以上の処理コア、キャッシュメモリ、内部バス (複数の場合もあり)、タイミングユニット、コントローラ、アナログセクション、機械的要素などを含んでもよい。従って、さまざまな実施形態において、I C (複数の場合もあり)は、2つ以上の供給電圧 (たとえば、2つ、3つ、4つなど)を受け取るように構成される回路を含んでもよい。いくつかの実施態様において、供給電圧は、ほぼ10V ± 10%、5V ± 10%、1.2V ± 10%程度などであってもよい。

## 【0016】

一般的に言って、チップ102は、たとえば、ボール・グリッド・アレイ (B G A)パッケージングなどの任意の適切なパッケージング技術を使用してP C B 1 0 1上に取り付けられるように構成された電子構成要素パッケージを含んでもよい。いくつかの実施態様において、P C B 1 0 1は、電子デバイス100内に機械的に取り付けられるか、またはそれに固定されてもよい。いくつかの実施態様において、P C B 1 0 1は、さまざまな形態をとってもよく、かつ / または、チップ102に加えて複数の他の要素もしくは構成要素を含んでもよいことに留意されたい。また、いくつかの実施形態において、P C B 1 0 1は使用されなくてもよいことに留意されたい。

## 【0017】

図1の例は電子チップ102をモノリシック形態で示しているが、代替的な実施形態において、本明細書に記載のシステムおよび方法は別個の構成要素によって実装されてもよいことは理解されたい。たとえば、いくつかの場合において、1つ以上の別個のキャパシタ、インダクタ、トランジスタなどがチップ102の外部に位置してもよい。その上、これらの外部構成要素のうちの1つ以上は、チップ102内に作製された集積回路に動作可能に結合されてもよい。

## 【0018】

図2は、いくつかの実施形態に応じた、ハイブリッドS M P S 2 0 0の一例の回路図である。図示のように、電圧源202が基準電圧 $V_{r e f}$ を制御回路201に提供する。いくつかの場合において、たとえば、電圧源202は、バンドギャップ基準電圧回路などであってもよい。制御回路201は、電圧 $V_{g a t e}$ をトランジスタ203のゲートに印加し、当該トランジスタは、P型金属酸化膜半導体 (P M O S)トランジスタなどであってもよい。しかしながら、他の例において、N型M O S (N M O S)が使用されてもよい。トランジスタ203のソースは結合キャパシタ204と並列に入力電圧 $V_{i n}$ に結合されている。ダイオード205およびインダクタまたはコイル206がトランジスタ203の

10

20

30

40

50

ドレインに結合されている。このように、この構成において、ダイオード 205、インダクタ 206、およびキャパシタ 207 は、ほぼ一定の調整電圧  $V_{reg}$  を電気負荷 208 に供給するように構成されているネットワークを形成する。出力電圧  $V_{reg}$  は制御回路 201 の対応するピンにフィードバックされる。

#### 【0019】

ここで、図 2 のハイブリッド S MPS 200 は、非同期降圧（ステップダウン）DC-DC コンバータを実装するために使用されているが、これは例示のみを目的としたものであることに留意されたい。他の実施形態において、昇圧（ステップアップ）コンバータ、昇降圧コンバータ、シングルエンド一次インダクタ変換器（SEPIC）コンバータなどを含むが、これらには限定されない他のタイプの DC-DC コンバータがハイブリッド S MPS 200 を使用して実装されてもよい。10

#### 【0020】

いくつかの実施形態において、負荷 208 は、プロセッサ、プロセッサコア、マイクロコントローラ、メモリデバイスなどを含んでもよい。たとえば、さまざまな実施形態において、負荷 208 は、x86、RISC（登録商標）、PowerPC（登録商標）、ARM（登録商標）などのようなさまざまなインストラクション・セット・アーキテクチャ（ISA）のいずれかを実装する汎用または組み込みプロセッサ（複数の場合もあり）であってもよい。付加的にまたは代替的に、負荷 208 は、たとえば、GPU、SoC、ASIC、DSP、FPGA、MCU などのような特定用途向け処理装置であってもよい。付加的にまたは代替的に、負荷 208 は、たとえば、RAM、SRAM、MRAM、NVRAM、FLASH、DRAM、SDRAM、DDR SDRAM、EPROM、EEPROM などのようなメモリ回路を含んでもよい。しかしながら、より一般的に、負荷 208 は、集積または個別デバイスまたはシステムであってもよい。20

#### 【0021】

動作時、制御回路 201 は、トランジスタ 203 のゲートに  $V_{gate}$  をスイッチング方式で、調整可能なデューティサイクルで印加し、当該デューティサイクルはこのとき、 $V_{reg}$  の値を調整するように選択されてもよい。ここで、「デューティサイクル」という用語は、検討中の合計時間の関数としての、 $V_{gate}$  がアクティブである（たとえば、論理ハイにある）時間の割合を指す。その上、ハイブリッド S MPS 200 は、線形モードおよびヒステリシスモードにおいて動作するように構成されてもよい。30

#### 【0022】

線形モードにおいて動作するとき、制御回路 201 は  $V_{reg}$  の値を（ $V_{reg}$  ピンを通じて）監視し、たとえば負荷変化の影響を弱め、それゆえ、所望の  $V_{reg}$  値を維持するために  $V_{gate}$  のデューティサイクルを調整する。たとえば、特定の時点において負荷 208 が以前よりも引きこむ電流が少なくなり始めた場合、 $V_{reg}$  は上昇する傾向にある。従って、制御回路 201 は、 $V_{reg}$  をその所望の値に維持する試みにおいて  $V_{gate}$  のデューティサイクルを低減してもよい。その後、負荷 208 が引きこむ電流が以前よりも多くなり始めた場合、 $V_{reg}$  は下降する傾向にあり、制御回路 201 は  $V_{reg}$  を維持するために再び  $V_{gate}$  のデューティサイクルを増大させる。40

#### 【0023】

しかしながら、大きい、かつ／または突然の負荷変化の存在下で、ハイブリッド S MPS 200 はヒステリシスモードにおいて動作してもよい。ヒステリシスモードにおいて、 $V_{reg}$  が高閾値 ( $V_h$ ) を上回って上昇すると、制御回路 201 は  $V_{gate}$  のデューティサイクルをその最低規定値（たとえば、0%）に変更する。逆に、 $V_{reg}$  が低閾値 ( $V_l$ ) を下回って下降すると、制御回路 201 は  $V_{gate}$  のデューティサイクルをその最高規定値（たとえば、100%）に変更する。このように、制御回路 201 は、負荷変動後にハイブリッド S MPS 200 の線形動作範囲内の適切な値に  $V_{reg}$  を戻してステアリングすることが可能であり得る。

#### 【0024】

ここで、負荷変化または変動と称するが、 $V_{reg}$  が変化する傾向になり得る他の理由50

があつてもよいことに留意されたい。たとえば、供給電圧  $V_{in}$ 、気温などの変化も、本明細書に記載のものと同様に制御回路 201 によって修正可能である  $V_{reg}$  の変化を引き起こす場合がある。

#### 【0025】

図 3 は、特定の実施形態に応じた、制御回路 201 の一例のブロック図である。通常、制御回路 201 は、線形制御ブロックまたは回路 301 と、ヒステリシス制御ブロックまたは回路 302 と、遷移制御ブロックまたは回路 303 とを含む。入力端子  $V_{ref}$  および  $V_{reg}$ 、ならびに出力端子  $V_{gate}$  は図 2 に示すものと同じである。線形制御ブロック 301 およびヒステリシス制御ブロック 302 は、それぞれハイブリッド SMPSS の線形動作モードおよびヒステリシス動作モードを実施することができる。

10

#### 【0026】

遷移制御ブロック 303 は、(たとえば、その直後に高閾値または低閾値のいずれかに達することによって)出力電圧が遷移後に過渡状態のままである可能性を低減するよう、ハイブリッド SMPSS のヒステリシスモードから線形モードに戻る遷移を容易にするように動作する。このように、遷移制御ブロック 303 はヒステリシス振動を回避するように動作する。下記により詳細に説明するように、遷移制御ブロック 303 は、ヒステリシスモードの間に線形制御ブロック 301 の動作を変更することができる。

#### 【0027】

図 4 は、特定の実施形態に応じた、制御回路 201 の一例の回路図である。図 3 におけるように、制御回路 201 はここでも線形制御回路 301、ヒステリシス制御回路 302、および遷移制御回路 303 に分割される。線形回路 301 は誤差増幅器 406 を含み、当該増幅器は、その非反転入力において  $V_{ref}$  を受信し、その反転入力において(抵抗器 403 を通じて)  $V_{reg}$  を受信する。誤差増幅器の出力  $V_{error}$  は、抵抗器 405、キャパシタ 404、抵抗器 402、キャパシタ 401、および抵抗器 403 を含むフィードバックネットワークを介して増幅器 406 にフィードバックされる。また、 $V_{error}$  は比較器 407 の非反転入力に提供され、当該比較器は、その反転入力において、ランプ生成器 408 によってパラメータ  $V_p$  (最大ランプ電圧) および  $V_m$  (最小ランプ電圧) に基づいて生成されるランプ信号を受信する。

20

#### 【0028】

動作時、線形制御回路 301 は基本的に、 $V_{reg}$  を  $V_{ref}$  と比較する。誤差増幅器 406 によって判定されるものとして、 $V_{reg}$  が  $V_{ref}$  よりも小さい場合、比較器 407 によって生成される信号のデューティサイクルが増大する。逆に、 $V_{reg}$  が  $V_{ref}$  よりも大きい場合、比較器 407 によって生成される信号のデューティサイクルが低減する。しかしながら、過電圧または不足電圧状態が発生する場合、すなわち、 $V_{reg}$  がそれぞれ高閾値電圧よりも大きくなるか、または低閾値電圧よりも小さくなる場合、ハイブリッド SMPSS はヒステリシスモードにおいて動作し始める。

30

#### 【0029】

ヒステリシスモードへの遷移を容易にするために、線形制御回路 301 内の比較器 407 の出力がヒステリシス回路 302 に供給される。特に、OR ゲート 409 が、比較器 407 の出力と、不足電圧状態(「udvc」)が存在すること( $udvc = '1'$ )または存在しないこと( $udvc = '0'$ )を示す信号とを受信する。過電圧状態(「odvc」)が存在すること( $ovvc = '1'$ )または存在しないこと( $ovvc = '0'$ )を示す信号がインバータ 401 に入力される。 $udvc$  および  $ovvc$  の生成の説明は下記により詳細に提供される。OR ゲート 409 およびインバータ 410 の出力は AND ゲート 411 に入力として提供される。AND ゲート 411 の出力はドライバ回路 412 に提供され、当該ドライバ回路は  $V_{gate}$  を生成する。

40

#### 【0030】

ヒステリシスモードにおける動作は以下のように説明され得る。不足電圧状態が検出される(すなわち、 $V_{reg}$  が低閾値電圧  $V_1$  よりも小さい)と、OR ゲート 409 およびインバータ 410 の出力は両方とも論理ハイにあり、AND ゲート 411 の出力も論理ハ

50

イにあり、それゆえ、ドライバ412は、 $V_{gat e}$ が100%のデューティサイクル（または何らかの他の所定の高い値）を有するようにする一定の「1」信号を受信する。他方、過電圧状態が検出される（すなわち、 $V_{reg}$ が高閾値電圧 $V_h$ よりも大きい）と、インバータ410の出力は論理ローにあり、ANDゲート411の出力も論理ローにあり、それゆえ、ドライバ412は、 $V_{gat e}$ が0%のデューティサイクル（または何らかの他の所定の低い値）を有するようにする一定の「0」信号を受信する。

#### 【0031】

ヒステリシスモードがトリガされると、遷移制御回路303は、線形モードに戻る遷移を容易にし、ヒステリシス振動を回避するように動作する。具体的には、事前に選択されている電圧（たとえば、約20mV）が要素416によって基準電圧 $V_{ref}$ から減算されて、その結果、低閾値電圧 $V_l$ がもたらされ、当該電圧は比較器418の非反転入力に結合される。別の事前に選択されている電圧が要素417によって基準電圧 $V_{ref}$ に加算されて、その結果、高閾値電圧 $V_h$ がもたらされ、当該電圧は比較器419の反転入力に結合される。 $V_{reg}$ が比較器418の反転入力、および、比較器419の非反転入力に結合される。

10

#### 【0032】

それゆえ、比較器418は不足電圧検出器として機能し（すなわち、 $V_{reg}$ が $V_l$ よりも小さいとき、 $udvc$ は論理ハイにある）、比較器419は過電圧検出器として機能する（すなわち、 $V_{reg}$ が $V_h$ よりも大きいとき、 $ovvc$ は論理ハイにある）。これらの $udvc$ および $ovvc$ 信号はその後、前述のように遷移ロジック414に、および、ヒステリシス回路302にも供給される。

20

#### 【0033】

$udvc$ または $ovvc$ 信号が検出され、電源がヒステリシスモードにおいて動作しているとき、遷移ロジック414は、増幅器406への入力をショートカットして、事前に選択されている電圧値 $V_{refout}$ が増幅器406の出力に印加されることを可能にするために、「保持(hold)」信号( $hold = 1$ )をインバータ415を通じて線形制御回路401の誤差増幅器406に、および、スイッチS1～S3に印加し、それによつて、誤差増幅器406を効率的にバイパスしてその出力 $V_{error}$ を強制的に既知の値にする。

#### 【0034】

30

$V_{refout}$ を選択するために、遷移ロジック414は「制御ワード(control word)」信号をデジタル電圧コンバータ413に発行する。制御ワードは、たとえば、5ビットワードなどであってもよい（ただし、任意の他の適切なビット数が使用されてもよい）。デジタル電圧コンバータ413は、制御ワードならびに $V_p$ および $V_m$ 値（ブロック408によって生成されるランプの最大値および最小値）を受け取って $V_{refout}$ を生成し、 $V_{refout}$ はその後、スイッチS2を通じて増幅器406の出力に印加される。制御ワードおよび $V_{refout}$ の値は、たとえば、図5において説明するように選択されてもよい。 $udvc$ または $ovvc$ 信号がもはや検出されなくなると、このことは、電源が再び線形モードにおいて動作していることを示している。従って、遷移ロジック414は保持信号の発行を停止する。

40

#### 【0035】

いくつかの実施態様において、遷移ロジック414はまた、電源を連続または不連続電流モードにおいて動作するように制御してもよい。手短に図2に戻って、インダクタ206を通る電流が、その最小値が0Vを上回るような波形を有するとき、インダクタ206は連続電流モードにおいて動作している。逆に、インダクタ206を通る電流が、ダイオード205が存在しなければ0Vを下回る最小値を有する波形を有するとき、インダクタ206は不連続電流モードにおいて動作していると考えられる。図4に戻って参照すると、連続電流モードにおいて、S0は $V_{refout}$ をS2に結合し、一方で不連続電流モードにおいてS0は $V_{refmin}$ をS2に結合する。たとえば、 $V_{refmin}$ は、結果として低電流で動作するのにより適している固定デューティサイクル（たとえば、10

50

%)をもたらすように選択されてもよい。

#### 【0036】

さまざまな実施形態において、図3および図4に示すモジュールまたはブロックは、処理回路、論理機能、および/またはデータ構造を表してもよい。これらのモジュールは別個のブロックとして図示されているが、他の実施形態において、これらのモジュールによって実行される動作のうちの少なくともいくつかは組み合わされてより少ないブロックになつてもよい。逆に、図3および図4のうちの任意の所与のものが、その動作が2つ以上の論理ブロックの間で分割されるように実装されてもよい。特定の構成によって図示しているが、他の実施形態において、これらのさまざまなモジュールまたはブロックは、他の適切な方法で再構成されてもよい。

10

#### 【0037】

図5は、特定の実施形態に応じた、遷移制御回路303の動作を示すフローチャートである。ブロック501において、遷移制御回路303は、不足電圧または過電圧状態を示す不足電圧または過電圧パルスまたは信号を待ってもよく、当該信号は、電源がヒステリシスモードにおいて動作していることを示す。ブロック502において、不足電圧状態が検出された場合、制御はブロック503に移動し、遷移制御回路303はデジタル電圧コンバータ413に $V_{refout}$ の値を増大させるデジタル制御ワードを生成する。ブロック504において、過電圧状態が検出された場合、制御はブロック505に移動し、遷移制御回路303はデジタル電圧コンバータ413に $V_{refout}$ の値を低減させる別のデジタル制御ワードを生成する。そうでない場合、制御はブロック501に戻る。いくつかの実施形態において、各値が等間隔に区切られた0%~100%の所与のデューティサイクルに対応するいくつかの所定の制御ワード値(たとえば、32の値)が使用されてもよく、従って、後述するように $V_{refout}$ がそれらの値のいずれかをとることが可能になる。

20

#### 【0038】

いくつかの実施形態において、図5の方法は、「監視期間」とも称される、事前に選択されている期間の間アクティブであつてもよい。いくつかの場合において、監視期間は、最初の過電圧または不足電圧状態が検出されるとき、すなわち、電源が線形モードからヒステリシスモードにスイッチングするときに開始してもよい。その後、監視期間は選択された時間、たとえば、20μsにわたって継続してもよく、監視期間の間の後続のパルスによって延長されてもよい。監視期間の間、不足電圧または過電圧状態が反復することによって、遷移制御回路303はその制御ワードを、 $V_{refout}$ をそれに応じて変更するように増分的に変更してもよい。

30

#### 【0039】

たとえば、第1の過電圧状態が検出されると(ブロック504)、第1の制御ワードが発行されてもよい(ブロック505)。同じ監視期間の間に、第2の過電圧が再び検出された場合、第1の制御ワードよりも低い値を有する第2の制御ワードが発行されてもよく、以下同様である。しかしながら、別の過電圧状態が検出されても、そのことが監視期間が満了した後でしかない場合、直前の監視期間において使用されたものと同じ制御ワードが使用されてもよい。逆に、第1の不足電圧状態が検出されると(ブロック502)、第1の制御ワードが発行されてもよい(ブロック503)。同じ監視期間の間に、第2の不足電圧が再び検出された場合、第1の制御ワードよりも高い値を有する第2の制御ワードが発行されてもよく、以下同様である。その後、また別の不足電圧状態が検出されても、そのことが監視期間が満了した後でしかない場合、直前の監視期間において使用されたものと同じ制御ワードが使用されてもよい。

40

#### 【0040】

別の例として、以下の動作を考える。第1の不足電圧状態が検出されると(ブロック502)、(たとえば、5ビットワードにおける)「16」の値を有する第1の制御ワードが発行されてもよい(ブロック503)。その後、監視期間が満了する前に第2の不足電圧状態(ブロック502)が検出された場合、「17」の値を有する、すなわち、( $V_r$

50

$v_{refout}$  (17) が  $v_{refout}$  (16) よりも大きいと想定して) 先行する値よりも増分的に高い第2の制御ワードが発行されてもよい(ブロック503)。逆に、第1の不足電圧状態の後で、まだ監視期間が満了する前に過電圧状態(ブロック504)が検出された場合、「15」の値を有する(すなわち、第1の値よりも増分的に小さい)制御ワードが発行されてもよい(ブロック505)。

#### 【0041】

いくつかの実施態様において、監視期間が満了した後に、最後に記憶された値が使用されてもよい。代替的に、後続の監視期間の間に、それぞれ最初不足電圧状態が検出されるか、または過電圧状態が検出されるかに応じて、最後に記憶された値がインクリメントまたはデクリメントされてもよい。

10

#### 【0042】

図5の方法は、SMP(S)におけるヒステリシス制御モードと線形制御モードとの間の円滑な遷移を可能にすることができる。ヒステリシス期間の終わりに100%または0%のデューティサイクルからステップするのではなく、事前に選択されている監視期間の間に後続の過電圧または不足電圧状況の発生を防止または少なくとも低減するより微妙な遷移が実行されることができる。

#### 【0043】

本明細書、特に図5に関連して説明されたさまざまな動作は、処理回路または他のハードウェア構成要素によって実施されてもよいことを理解されたい。所与の方法の各動作が実行される順序は変更されてもよく、本明細書に示すシステムのさまざまな要素は追加、並べ替え、組み合わせ、省略、改変などされてもよい。本明細書に記載の発明(複数の場合もあり)は、すべてのこのような改変および変更を包含することが意図されており、従って、上記の記載は限定的な意味ではなく例示的な意味において評価されるべきである。

20

#### 【0044】

図6は、いくつかの実施形態に応じた、遷移制御回路303の電圧選択動作を示すグラフを示す。特に、グラフ600Aは、負荷によって引きこまれている電流を曲線601として示す。この場合において、曲線601は  $t = 200 \mu s$  において約0.06Aから1.2Aに急激に増大しており、従って、不足電圧状態が生じてヒステリシス動作がトリガされる。

#### 【0045】

30

グラフ600Bは、種々のシナリオにおいて遷移制御回路303によって増幅器406の出力ノードにおいて印加される  $v_{refout}$  の種々の値を示す。特に、曲線602Bは  $v_{refout}$  を約0.8Vとして示し、曲線603Bは  $v_{refout}$  を約0.76Vとして示し、曲線604Bは  $v_{refout}$  を約0.73Vとして示し、曲線605Bは  $v_{refout}$  を約0.7Vとして示し、以下  $v_{refout}$  を約0.6Vとして示す曲線607Bまで同様である。一方、グラフ600Cは、それらの同じシナリオにおける調整出力電圧  $v_{reg}$  の結果を示す。具体的には、曲線602Cは曲線602Bの  $v_{refout}$  に対応する  $v_{reg}$  を示し、曲線603Cは曲線603Bの  $v_{refout}$  に対応する  $v_{reg}$  を示し、以下同様である。 $v_h$ (約1.27V)および  $v_l$ (約1.23V)を表す水平線も示されている。

40

#### 【0046】

ここで、制御ワードによって選択された  $v_{refout}$  が高すぎる(たとえば、曲線602B)場合、 $v_{reg}$  は、この例では  $20 \mu s$  に設定されている監視期間内に後続の過電圧状態で跳ね戻る(たとえば、602C)ことに留意されたい。逆に、制御ワードによって選択された  $v_{refout}$  が低すぎる(たとえば、曲線608B)場合、 $v_{reg}$  は、監視期間内に後続の不足電圧状態で跳ね戻る(たとえば、608C)。他の値の  $v_{refout}$ (たとえば、曲線604B~606B)はヒステリシスモードから線形モードへの円滑な復帰をもたらす(たとえば、曲線604~606C)。言い換えれば、いくつかの場合において、監視期間内に  $v_{reg}$  振動を防止する  $v_{refout}$  値を生成する制御ワードの範囲があり得、それらのうちの1つ以上が図5の方法を使用して発見され得る。

50

**【 0 0 4 7 】**

図7は、特定の実施形態に応じた、ハイブリッドSMPsの動作を比較したグラフを示す。特に、曲線701は $V_h$ および $V_1$ に対する $V_{reg}$ を経時的に示す。この例において、ヒステリシス制御回路302および遷移制御回路303は、時刻 $t = 500 \mu s$ の前はオフにされており、その後オンにされている。そのため、 $t = 500 \mu s$ の前に過電圧または不足電圧状態が発生するたびに、 $V_{reg} 701$ ははるかに大きい過電圧および不足電圧ピークを有し、遷移制御回路303がオンにされた後(703)よりも線形のみのモード(702)に回復するのにより多くの時間がかかることが分かる。従って、特定の場合において、遷移制御回路303は、ヒステリシスマードから線形モードへの遷移を円滑にし、従ってヒステリシス振動を低減または取り除くことができるだけでなく、SMPsが線形モードにおいて動作する時間全体を増大させることによって、回復プロセスを加速させることもできる。

10

**【 0 0 4 8 】**

実例となる非限定的な実施形態において、ハイブリッドSMPsは、SMPsが線形モードにおいて動作するときに可変デューティサイクルに比例する出力電圧を生成するように構成されている線形回路と、線形回路に結合されているヒステリシス回路であって、当該ヒステリシス回路は、SMPsがヒステリシスマードにおいて動作するときにデューティサイクルが2つの所定の値のうちの1つをとるように構成されている、ヒステリシス回路とを含んでもよい。ハイブリッドSMPsは、線形回路およびヒステリシス回路に結合されている遷移制御回路をも含んでもよく、当該遷移制御回路は、ハイブリッドSMPsがヒステリシスマードから線形モードに遷移するのに応答して、線形回路の少なくとも一部分をバイパスするように構成されている。

20

**【 0 0 4 9 】**

たとえば、ヒステリシス回路は、出力電圧が低閾値を下回って降下するのに応答して、デューティサイクルが所定の高い値をとるように構成されてもよい。その上、ヒステリシス回路は、出力電圧が高閾値を上回って上昇するのに応答して、デューティサイクルが所定の低い値をとるように構成されてもよい。

**【 0 0 5 0 】**

特定の実施態様において、線形回路は、基準電圧と出力電圧との間の差を示すように構成されている誤差増幅器を含んでもよく、遷移制御回路は、誤差増幅器の出力ノードにおいて印加される電圧を制御するように構成されている。また、遷移制御回路は、出力電圧に関して過電圧または不足電圧状態を特定するように構成されてもよい。従って、第1の過電圧または不足電圧状態が特定されたのに応答して、遷移制御回路は、デジタル電圧コンバータによって誤差増幅器の出力ノードに印加されるべき第1の電圧レベルに変換可能な第1の制御ワードを生成するように構成されてもよい。

30

**【 0 0 5 1 】**

その後、第1の過電圧または不足電圧状態後で、監視期間が満了する前に第2の過電圧または不足電圧状態が特定されたのに応答して、遷移制御回路は、第1の制御ワードと異なり、デジタル電圧コンバータによって誤差増幅器の出力ノードに印加されるべき第2の電圧レベルに変換可能な第2の制御ワードを生成するように構成されてもよい。付加的にまたは代替的に、第1の過電圧または不足電圧状態後で、監視期間が満了した後に第2の過電圧または不足電圧状態が特定されたのに応答して、遷移制御回路は、デジタル電圧コンバータによって誤差増幅器の出力ノードに印加されるべき第1の電圧レベルに変換可能な第1の制御ワードを生成するように構成されてもよい。

40

**【 0 0 5 2 】**

特定の場合において、ハイブリッドSMPsが不連続電流モードにおいて動作していると判定されたのに応答して、遷移制御回路は、デジタル電圧コンバータによって生成される固定電圧値が、誤差増幅器の出力ノードに印加されるように構成されてもよい。

**【 0 0 5 3 】**

50

別の実例となる非限定的な実施形態において、ハイブリッド・スイッチ・モード電源（S M P S）を動作させる方法は、線形動作モードにある間に、デューティサイクルに比例する出力電圧を生成すること、デューティサイクルが、不足電圧の発生に応答して第1の所定値を、または過電圧の発生に応答して第2の所定値をとるようにするためにヒステリシス動作モードに入ること、少なくとも部分的に、デューティサイクルを、選択された期間の間に後続の不足電圧または過電圧の発生が起こる可能性を低減するように制御することによって、線形動作モードに戻ることを含んでもよい。いくつかの実施形態において、出力電圧を制御することは、ハイブリッドS M P S内の増幅器の入力をショートカットすること、選択された電圧を増幅器の出力に印加することを含んでもよい。

## 【0054】

10

方法は、不足電圧または過電圧の発生に応答して、増幅器の出力に印加されるべき第1の電圧レベルに変換可能な第1の制御ワードを生成することをも含んでもよい。その後、選択された期間が満了する前に後続の過電圧の発生が起きたのに応答して、方法は、第1の制御ワードと異なり、増幅器の出力に印加されるべき第2の電圧レベルに変換可能な第2の制御ワードを生成することをさらに含んでもよく、第2の電圧レベルは第1の電圧レベルよりも低い。

## 【0055】

20

いくつかの実施形態において、選択された期間が満了した後に後続の過電圧の発生が起きたのに応答して、方法は、第1の制御ワードを維持することを含んでもよい。不足電圧または過電圧の発生に応答して、方法は、増幅器の出力に印加されるべき第1の電圧レベルに変換可能な第1の制御ワードを生成することを含んでもよい。

## 【0056】

他の場合において、選択された期間が満了する前に後続の不足電圧の発生が起きたのに応答して、方法は、第1の制御ワードと異なり、増幅器の出力に印加されるべき第2の電圧レベルに変換可能な第2の制御ワードを生成することを含んでもよく、第2の電圧レベルは第1の電圧レベルよりも高い。方法は、選択された期間が満了した後に後続の不足電圧の発生が起きたのに応答して、第1の制御ワードを維持することを含んでもよい。

## 【0057】

30

また別の実例となる非限定的な実施態様において、電子チップは、ハイブリッド・スイッチ・モード電源（S M P S）の線形回路およびヒステリシス回路に結合されている遷移制御回路を含んでもよく、遷移回路は、ハイブリッドS M P Sのヒステリシス動作モードから線形動作モードへの遷移を容易にするように構成されてもよい。

## 【0058】

40

たとえば、線形回路は、ハイブリッドS M P Sが線形モードにおいて動作するときに可変デューティサイクルに比例する出力電圧を生成するように構成されてもよく、ヒステリシス回路は、ハイブリッドS M P Sがヒステリシスマードにおいて動作するときにデューティサイクルが2つの所定の値のうちの1つをとるようにするように構成されてもよく、遷移回路は、所与の監視期間の間の後続の不足電圧または過電圧の発生の数を低減するように構成されてもよい。その上、遷移制御回路は、デジタル的に選択された電圧を増幅器の出力に印加することによって、線形回路内の増幅器をバイパスするように構成されてもよい。

## 【0059】

本明細書において、具体的な実施形態を参照して本発明（複数の場合もあり）を説明したが、添付の特許請求の範囲に明記されているような本発明（複数の場合もあり）の範囲から逸脱することなくさまざまな改変および変更を為すことができる。従って、本明細書および図面は限定的な意味ではなく例示とみなされるべきであり、すべてのこのような改変が本発明（複数の場合もあり）の範囲内に含まれることが意図されている。本明細書において具体的な実施形態に関して記載されているいかなる利益、利点、または問題に対する解決策も、任意のまたはすべての請求項の重要な、必要とされる、または基本的な特徴または要素として解釈されるようには意図されていない。

50

## 【0060】

別途記載されない限り、「第1の」および「第2の」のような用語は、そのような用語が説明する要素間で適宜区別するように使用される。従って、これらの用語は必ずしも、このような要素の時間的なまたは他の優先順位付けを示すようには意図されていない。「結合されている」または「動作可能に結合されている」という用語は、接続されているとして定義されるが、必ずしも直接ではなく、必ずしも機械的ではない。「備える」、「有する」、「含む」、ならびに「包含する」といった用語は制約のない連結動詞である。結果として、1つ以上の要素を「備える」、「有する」、「含む」または「包含する」システム、デバイス、または装置は、それらの1つ以上の要素を保持するが、それらの1つ以上の要素のみを保持するようには限定されない。同様に、1つ以上の動作を「備える」、「有する」、「含む」または「包含する」方法またはプロセスは、それらの1つ以上の動作を保持するが、それらの1つ以上の動作のみを保持するようには限定されない。10

## 【符号の説明】

## 【0061】

301...線形回路、302...ヒステリシス回路、303...遷移制御回路。

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 エデヴァルド ペレイラ シルヴィア ジュニア

ブラジル国 13076-112 サンパウロ カンピナス ルア ドウトール マーリオ ナチ

ヴィダデ 908 アパルタメント 132

審査官 栗栖 正和

(56)参考文献 米国特許出願公開第2013/0043849(US, A1)

特開平03-040719(JP, A)

米国特許出願公開第2006/0273772(US, A1)

特開2003-111395(JP, A)

特開2013-021790(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/155