(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-248279

(P2004-248279A)

(43) 公開日 平成16年9月2日(2004.9.2)

(51) Int.CI.<sup>7</sup>H04L 29/06

// H04L 7/00

F 1

H04L 13/00 305Z

H04L 7/00 A

テーマコード(参考)

5K034

5K047

審査請求 未請求 請求項の数 9 O L (全 23 頁)

(21) 出願番号 特願2004-32633 (P2004-32633)

(22) 出願日 平成16年2月9日 (2004.2.9)

(31) 優先権主張番号 03090038.5

(32) 優先日 平成15年2月12日 (2003.2.12)

(33) 優先権主張国 欧州特許庁 (EP)

(71) 出願人 501263810

トムソン ライセンシング ソシエテ ア

ノニム

Thomson Licensing S.

. A.

フランス国、エフー92100 プロー

ニュ ビヤンクール、ケ アルフォンス

ル ガロ、46番地

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

(74) 代理人 100107766

弁理士 伊東 忠重

最終頁に続く

(54) 【発明の名称】異なるタイプのインターフェースからの入力信号、又は異なるタイプのインターフェースへの出力信号を共通フォーマットの中央演算処理でプリプロセスするための方法及び装置

## (57) 【要約】 (修正有)

【課題】異なるタイプのインターフェースからの入力信号又は異なるタイプのインターフェースへの出力信号に対する、共通のシステムクロックのプリプロセスを容易にする。

【解決手段】音声処理技術では、異なるサンプルクロックの周波数、及び/又は異なるデータフレーム又は異なるデータワードのフォーマットに関連する異なるタイプのインターフェースが存在する。異なるタイプのインターフェースからの入力信号は、その後の共通フォーマットの中央演算処理のためにプリプロセスされる。このプリプロセスは、共通のシステムクロックに対する同期、異なるタイプのインターフェースに符合する異なるチャネルプロトコルに従うチャネルデコードに対する同期、及び該PCMビットストリームから、これよりサンプルワードが中央演算処理に供給される中間的な記憶装置に記憶されるサンプルワードを形成するように同期を利用する。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

共通のシステムクロック (sys\_ck) を使用して、共通フォーマットの中央演算処理のために、異なるタイプのインターフェース (IEC958, I2S, AC-Link, ADAT) からの入力信号 (SADI) をプリプロセスするための方法であって、前記異なるインターフェースタイプは、異なるサンプルクロック周波数、及び / 又は異なるデータフレーム又はデータワードのフォーマットに関連しており、

前記異なるタイプのインターフェースからの入力信号 (SADI) から、システムクロックに同期した入力信号を発生し (GPI)、

前記異なるタイプのインターフェースに関連する前記異なるチャネルプロトコル (IEC958, I2S, AC-Link, ADAT) に従い、前記システムクロックに同期した入力信号をチャネルデコードし (11)、一様なワードフォーマットを有する対応するPCMビットストリームのフォーマット信号を供給し、

前記PCMビットストリームのフォーマット信号から、たとえば FIFO のような、これよりサンプルワードが前記中央演算処理に供給される中間的な記憶装置 (14) に記憶されるサンプルワードを形成するように、前記PCMビットストリームのフォーマット信号をさらに処理する (13)、

ことを特徴とする方法。

## 【請求項 2】

共通のシステムクロック (sys\_ck) を使用して、共通フォーマットの中央演算処理において、異なるタイプのインターフェース (IEC958, I2S, AC-Link, ADAT) への出力信号 (SADO) をプリプロセスするための方法であって、前記異なるインターフェースタイプは、異なるサンプルクロック周波数、及び / 又は異なるデータフレーム又はデータワードのフォーマットに関連しており、

システムクロックに同期したPCMビットストリームのフォーマット信号をサンプルワードから形成することで、前記中央演算処理から出力され (SB)、たとえば FIFO のような中間的な記憶装置 (14) に記憶される前記サンプルワードをさらに処理し (13)、PCMビットストリームのフォーマット信号は、一様なワードフォーマットを有し、かつ前記異なるタイプのインターフェース (IEC958, I2S, AC-Link, ADAT) に関連しており、

前記異なるタイプのインターフェースに関連する前記異なるチャネルプロトコル (IEC958, I2S, AC-Link, ADAT) に従い、一様なワードフォーマットを有する前記システムクロックに同期したPCMビットストリームのフォーマット信号をチャネルエンコードして、対応するシステムクロックに同期した出力信号を供給し (12)、

前記システムクロックに同期した出力信号から、もはやシステムクロックに同期しないが前記タイプのインターフェースに従うインターフェースタイプに適合した出力信号 (SAD0) を発生する (GPO)、

ことを特徴とする方法。

## 【請求項 3】

共通のシステムクロック (sys\_ck) を使用して、共通フォーマットの中央演算処理のために、異なるタイプのインターフェース (IEC958, I2S, AC-Link, ADAT) からの入力信号 (SADI) をプリプロセスするための装置であって、前記異なるインターフェースタイプは、異なるサンプルクロック周波数、及び / 又は異なるデータフレーム又はデータワードのフォーマットに関連しており、

前記異なるタイプのインターフェースからの入力信号 (SADI) から、システムクロックに同期した入力信号を発生するための手段 (GPI) と、

前記異なるタイプのインターフェースに関連する前記異なるチャネルプロトコル (IEC958, I2S, AC-Link, ADAT) に従い、前記システムクロックに同期した入力信号をチャネルデコードして、一様なワードフォーマットを有する対応するPCMビットストリームのフォーマット信号を供給するための手段 (11) と、

10

20

30

40

50

前記PCMビットストリームのフォーマット信号から、たとえば FIFOのような、これよりサンプルワードが前記中央演算処理に供給される中間的な記憶装置(14)に記憶されるサンプルワードを形成するように、前記PCMビットストリームのフォーマット信号をさらに処理するための手段(13)と、

を備えることを特徴とする装置。

**【請求項4】**

共通のシステムクロック(s y s \_ c l k)を使用して、共通フォーマットの中央演算処理において、異なるタイプのインターフェース(I E C 9 5 8, I 2 S, A C - L i n k, A D A T)への出力信号(S A D O)をプリプロセスするための装置であって、前記異なるインターフェースタイプは、異なるサンプルクロック周波数、及び/又は異なるデータフレーム又はデータワードのフォーマットに関連しており、

10

システムクロックに同期したPCMビットストリームのフォーマット信号をサンプルワードから形成することで、前記中央演算処理から出力され(S B)、たとえば FIFOのような中間的な記憶装置(14)に記憶される前記サンプルワードをさらに処理するための手段と(13)、PCMビットストリームのフォーマット信号は、一様なワードフォーマットを有し、かつ前記異なるタイプのインターフェース(I E C 9 5 8, I 2 S, A C - L i n k, A D A T)に関連しており、

前記異なるタイプのインターフェースに関連する前記異なるチャネルプロトコル(I E C 9 5 8, I 2 S, A C - L i n k, A D A T)に従い、一様なワードフォーマットを有する前記システムクロックに同期したPCMビットストリームのフォーマット信号をチャネルエンコードして、対応するシステムクロックに同期した出力信号を供給するための手段と(12)、

20

前記システムクロックに同期した出力信号から、もはやシステムクロックに同期しないが前記タイプのインターフェースに従うインターフェースタイプに適合した出力信号(S A D O)を発生するための手段(G P O)と、

を備えることを特徴とする装置。

**【請求項5】**

前記インターフェースのタイプは、I E C 9 5 8、I 2 S、A C - L i n k及びA D A Tのうちの少なくとも2つを含む、

請求項1乃至4のいずれか記載の方法又は装置。

30

**【請求項6】**

チャネルの置き換えを検出して回避するために、システムクロックに同期した処理で、幾つかの個々のサンプルがそれらのチャネルタイプで記録又はチェックされ、前記チャネルの置き換えは、たとえばサンプルを挿入又は消去した場合に生じ、前記記録は、たとえば、前記システムクロックに同期した処理で特に使用されないサブコードのビットを使用して実行される、

請求項1乃至5のいずれか記載の方法又は装置。

**【請求項7】**

前記中間的な記憶装置(14)に関するDMAブロック転送のために、それぞれのDMAデータブロックの最初のワードについてLFの記録が実行され、該LF記録は、DMAバッファ出力を準備するときにプロセッサの処理数を低減するために評価される、

40

請求項1乃至6のいずれか記載の方法又は装置。

**【請求項8】**

前記サンプルワードの更なる処理を実行するストリームユニットの正確に時間設定されたスタートアップを容易にするために、内部発生されたタイムスタンプが中央演算処理により前記ストリームユニットに供給される、

請求項1乃至7のいずれか記載の方法又は装置。

**【請求項9】**

個別のクロック、及びデータ又は前記システムクロックに対する同期信号を有するインターフェース信号の同期のために、同期されるクロック(b c k)の同じエッジでクロックさ

50

れる 2 つの連続する D フリップフロップが使用される、

請求項 1 乃至 8 のいずれか記載の方法又は装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、共通のシステムクロックを利用して、異なるタイプのインターフェースからの入力信号、又は異なるタイプのインターフェースへの出力信号を共通フォーマットの中央演算処理でプリプロセスするための方法及び装置に関する。

【背景技術】

【0002】

デジタル I/O 向けの IEC 958 及び ADAT、或いは主に A/D / D/A コンバータへの接続向けの AC-LINK 及び I2S のような、様々な A/V システム向けデジタルオーディオ入力 / 出力インターフェースが一般に使用されている。今日では、一般的なインターフェースアプリケーションは、単一のインターフェースタイプを超える機能を要求することもある。

【0003】

かかるインターフェースの公知のビルディングブロックは、単一のインターフェースを通常実現する。たとえば、受信機は、雑音のないデータビットと、シリアルデータビットストリームから一連のサンプルワードを形成する後段の直列 - 並列変換向けのビットクロックとを出力するプロトコルのデコーダから構成されている。その後、このサンプルワードは、たとえば、ダイレクトメモリアクセス (DMA) 及び / 又は、割込み又はポーリングデータ転送、並びに必要であれば、オーディオデータをバッファリングするための FIFO を利用して、処理システムのメモリに書き込まれる。

【0004】

送信機は、対応して逆方向のデータ処理を実現する類似の構成要素から構成される。一般的なシステムは、プロセッサのクロックとオーディオのサンプリング周波数の比により、データ転送向けの DMA を利用する。基本的な DMA 転送動作は、処理速度が問題とされない場合にはソフトウェアで実行することができる。以下では、DMA の使用に対して時々言及するが、本発明では、それぞれのケースで、DMA 入力及び出力を割込み又はポーリング機構により置き換えることができる。

【0005】

(IEC 958 受信機のような) 単一プロトコル向けの専用インターフェースは、専用の直列 - 並列コンバータ、すなわち、MSB first 又は LSB first を実現し、ビット数等はインターフェースの仕様に従うコンバータを一般に利用する (又は、送信機の場合には、並列 - 直列コンバータを利用する)。

【発明の開示】

【課題を解決するための手段】

【0006】

共通すなわち中央のプロセッサと相互作用のために異なるタイプのオーディオインターフェースを結合するとき、複数の異なる動作条件が考慮されなければならない。基本的に、かかるインターフェースは、随伴する同期及びクロック信号をほとんど用いることなく或いは全く用いることなしに、オーディオデータのシリアル転送を利用する。さらに、オーディオインターフェースは、プロセッサ又はバスのシステムクロックに関連していない特別なオーディオに関連したクロックを使用している。したがって、1 つ以上の同時に使用されているオーディオインターフェースを組み込むことは、アクティブなインターフェースあたり最多で 1 つの追加の異なるクロックまで、幾つかの独立なオーディオクロックが出現することになる。

【0007】

全ての先に説明されたインターフェースは、最大 24 ビットの PCM データワードを転送するものであり、これにより、幾つかの順次に転送される PCM データワードは、完全な

10

20

30

40

50

オーディオサンプルを形成する（I E C 9 5 8、I 2 S T Y P E 2、ステレオ；A D A T type 8；A C - L i n k type 2 t o 6：マルチチャネル）。あるタイプのインターフェースについて、追加のサイド情報は、たとえば、S P D F：V U C；A D A T：U s e r B i t s；A C - L i n k：T a g，C m d，S t a t u sのようなオーディオ情報ビットとマージされる。シリアルP C Mデータの転送は、L S B（最下位ビット）f i r s t又はM S B（最上位ビット）f i r s tのいずれかとなることができる。

#### 【 0 0 0 8 】

本発明により解決されるべき課題は、異なるタイプのインターフェースからの入力信号又は異なるタイプのインターフェースへの出力信号に対して、共通のシステムクロックのプリプロセスを容易にすることである。ここで、異なるインターフェースのタイプは、異なるサンプルクロック周波数、及び／又は異なるデータフレームのフォーマット又は異なるデータワードのフォーマットに関連している。また、本発明により解決されるべき課題は、共通のシステムクロックの動作領域をできるだけ広くすることである。この問題は、請求項1及び請求項2に開示される方法により解決される。本方法を利用する装置は、請求項3及び請求項4に開示されている。

#### 【 0 0 0 9 】

以下の説明において、用語「オーディオサンプル」又は「サンプル」は、K個の番号（又はワード）からなる完全なKチャネルのサンプルを示している。1つの番号はチャネルの1つにそれぞれ対応しており、Kはオーディオチャネルの数である。これらの番号は、「サンプルワード」又は「ワード」と示される。

#### 【 0 0 1 0 】

本発明のオーディオインターフェースのアーキテクチャは、パラメータ付きユニバーサルオーディオI Cセル又はユニットの実現に関連している。このユニットは、システムI C設計、P C B設計及びソフトウェア設計についてできるだけ高い柔軟性を保持するやり方で、中央演算処理システムにおいて、同時かつ様々な形態で、先に説明されたタイプのインターフェースの少なくとも全てから到来するデータ、又は先に説明されたタイプのインターフェースの少なくとも全てに供給されるデータを処理することができる。

#### 【 0 0 1 1 】

本発明は、全体的なセル又はユニットのアーキテクチャ、及び特定の詳細な解決策に関連している。

#### 【 0 0 1 2 】

D S P（デジタルシグナルプロセッサ）は、D S Pデータワードからなる入力及び出力を様々な特殊なシリアルデータフォーマットにすることができる、一般的に機器構成可能なシリアルインターフェースS I O（シリアル入出力）を含んでいることがある。先に説明された单一プロトコル向け専用インターフェースの代替として、先に説明されたマルチタイプインターフェースのうちの1つを実現するために、かかるユニバーサルS I Oを特定のプロトコルのデコーダ又はエンコーダと結合することができる。完全なユニットは、ビットクロック又はそれぞれのチャネルクロックで時間を計測することができる。プロセッサクロックを利用して、プロセッサによるパラレルサンプルワードへのアクセスが好適に提供される。

#### 【 0 0 1 3 】

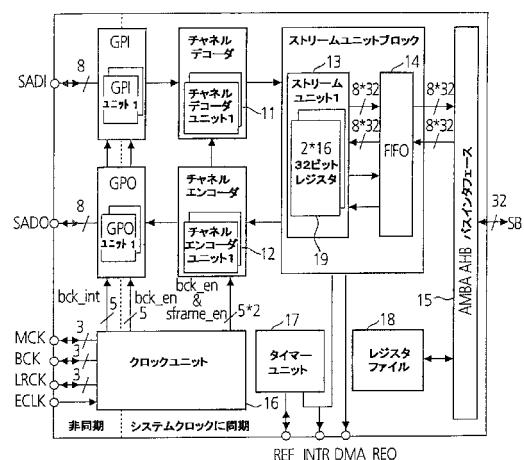

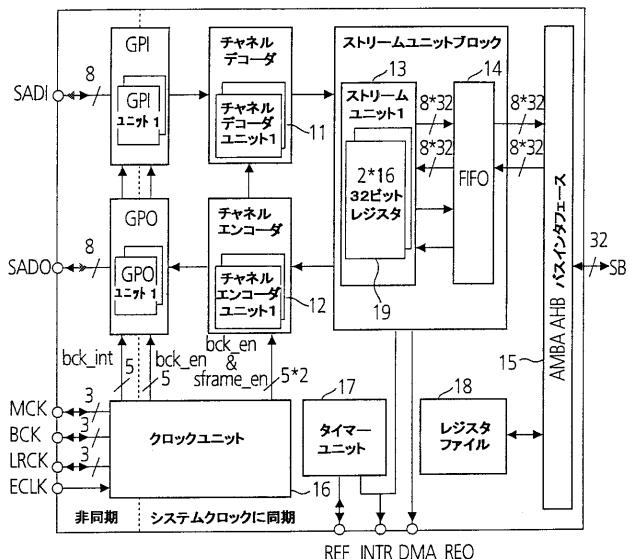

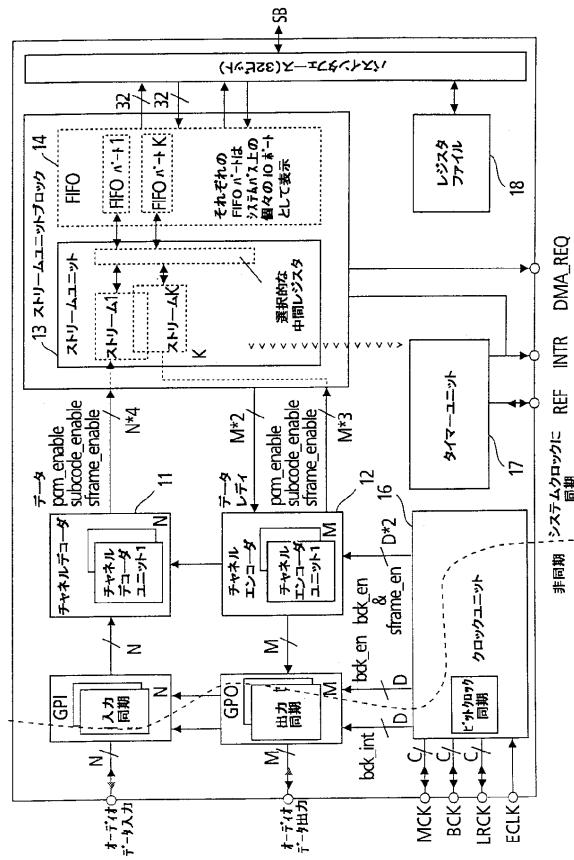

図1は、本発明によるデジタルオーディオインターフェースユニットの例示的なアーキテクチャを示している。シリアルオーディオデータ入力S A D I信号及びシリアルオーディオデータ出力S A D O信号が左側に示されており、システムプロセッサ（R I S C、D S P又はμ P、図示せず）に接続しているシステムバスS Bが右側に示されている。全てのオーディオクロックに関連する信号は、できるだけ早く（入力）又はできるだけ遅く（出力）システムクロックに同期される。このシステムクロックは、バスクロックに等しい場合がある。有利なことに、これにより、システムクロックの処理領域、すなわちシステムクロックでのみ時間を計測されるロジックの部分をできるだけ広くすることができる。

10

20

30

40

50

## 【0014】

汎用の入力ブロックGPI（同期ステージと、SADI信号を双方向かつ汎用的に使用するための制御ロジックとを含む）を介して、N個のオーディオデータ入力は、1つずつ、チャネルプロトコルのデコード（すなわち、IEC958、I2S、AC-Link、ADAT等のプロトコル）に対応するNチャネルデコーダユニット11に供給され、入力ビット当たりのデータビットのタイプ（たとえば、PCM、サブコード又はignore）を判定する。結果的に得られたN組の一般的PCMビットストリームフォーマット信号は、インターフェースのタイプに依存しないストリームユニット13に供給され、このユニット13は、N入力のうちの単一の入力又は複数の入力から、できる限り中間的なレジスタでの記憶装置を利用して、到来するシリアルデータビット（PCM及びサブコード）をサンプルワードとして FIFO14に出力する。FIFO14は、バスインターフェース15を介して、その出力信号をバスSBに渡すことができる。

10

## 【0015】

同様に、バスSBからのデータは、バスインターフェース15、FIFO14、ストリームユニット13、Mチャネルエンコーダユニット12及び汎用出力ブロックGPO（シリアルオーディオデータ出力のための同期ステージ、及びSADO信号を双方向かつ汎用的に使用するための制御ロジックを含む）を介して、M個のシリアルオーディオデータ出力信号SADOを供給する出力に渡す。これにより、MはNと異なる。

20

## 【0016】

チャネルエンコーダユニット12は、一般的PCMビットストリームを異なるインターフェースフォーマットにエンコードする。すなわち、このユニット12は、1つ以上のIEC958、AC'97、I2S及びADATエンコーダを含んでいる。

20

## 【0017】

ストリームユニット13は、直列・並列変換を実行する。このユニット13は、あるストリームに属する異なる入力信号から全ての到来するPCMビットを収集し、レジスタファイル19に記録する。この記録の内容は、その結果 FIFO14に転送することができる。FIFO14から到来するデータについて逆も可能である。たとえば、最大16チャネルからそれぞれ構成される8つの同時のオーディオストリームを処理するために、8つの異なるストリームユニットが存在する。レジスタファイル18は、オーディオセルについて全ての制御及び状態レジスタを含んでいる。クロックユニット16は、同期された内部ビットクロック及びイネーブル信号を発生する。タイマユニット17は、現在のシステムの時間のためのカウンタ、ローダブルタイマー、及び外部の基準信号でシステムの時間をサンプルするためのレジスタを含んでいる。

30

## 【0018】

入力データSADI及び出力データSADOは、対応するビットクロックBCK、マスタークロックMCK、及び信号LRCCKを伴う。この信号LRCCKは、たとえば、I2S及びAC'97といった、個別のクロック、データ及び同期信号を有するインターフェースタイプ向けの完全なオーディオサンプルの最初のPCMワードのうちの最初のビットを特定する。このクロック信号又は同期信号は、クロックユニット16により選択され、システムクロックに同期される。

40

## 【0019】

プロトコルのコンバータは、直列・並列変換と同様に、共通のビットクロック／チャネルクロックによりクロックされる。

## 【0020】

原理的に、本発明の方法は、共通のシステムクロックを使用して、共通のフォーマットの中央演算処理向けに異なるタイプのインターフェースからの入力信号をプリプロセス（pre-processing）するために適するものである。この異なるインターフェースのタイプは、異なるサンプルクロック周波数、及び／又は異なるデータフレームのフォーマット又は異なるデータワードのフォーマットに関連している。本方法は、以下のステップを含んでいる。

50

**【 0 0 2 1 】**

異なるタイプのインターフェースからの入力信号から、システムクロックに同期した入力信号を生成するステップ。

**【 0 0 2 2 】**

該異なるタイプのインターフェースに適合する異なるチャネルプロトコルに従い、該システムクロックに同期した入力信号をチャネルデコードし(*channel decoding*)、これにより、一様なワードフォーマットを有する対応するPCMビットストリームのフォーマット信号を供給するステップ。

**【 0 0 2 3 】**

該PCMビットストリームのフォーマット信号から、たとえばFIFOのような、これよりサンプルワードが中央演算処理に供給される中間的な記憶装置に記憶されるサンプルワードを形成するように、該PCMビットストリームのフォーマット信号をさらに処理するステップ。 10

**【 0 0 2 4 】**

或いは、本発明の方法は、共通のシステムクロックを使用して、共通フォーマットの中央演算処理において異なるタイプのインターフェースへの出力信号をプリプロセスするために適するものである。この異なるインターフェースのタイプは、異なるサンプルクロック周波数、及び／又は異なるデータフレームのフォーマット又は異なるデータワードのフォーマットに関連している。本方法は、以下のステップを含んでいる。 20

**【 0 0 2 5 】**

サンプルワードから、システムクロックに同期したPCMビットストリームのフォーマット信号を形成することにより、該中央演算処理から出力され、たとえばFIFOのような中間的な記憶装置に記憶されるサンプルワードをさらに処理するステップ。このPCMビットストリームのフォーマット信号は、一様なワードフォーマットを有しており、異なるタイプのインターフェースに適合する。 20

**【 0 0 2 6 】**

該異なるタイプのインターフェースに適合する異なるチャネルプロトコルに従い、一様なワードフォーマットを有する該システムクロックに同期したPCMビットストリームのフォーマット信号をチャネルエンコードし(*channel encoding*)、これにより、対応するシステムクロックに同期した出力信号を供給するステップ。 30

**【 0 0 2 7 】**

該システムクロックに同期した出力信号から、もはやシステムクロックに同期していないが、かかるインターフェースのタイプに従うインターフェースのタイプに適合した出力信号を発生するステップ。

**【 0 0 2 8 】**

原理的に、本発明の装置は、共通のシステムクロックを使用して、共通フォーマットの中央演算処理向けに異なるタイプのインターフェースからの入力信号をプリプロセスするために適するものである。かかる異なるインターフェースのタイプは、異なるサンプルクロック周波数、及び／又は異なるデータフレームのフォーマット又は異なるデータワードのフォーマットに関連している。本装置は、以下の構成要素を含んでいる。 40

**【 0 0 2 9 】**

異なるタイプのインターフェースからの入力信号から、システムクロックに同期した入力信号を発生するための手段。

**【 0 0 3 0 】**

該異なるタイプのインターフェースに適合する異なるチャネルプロトコルに従い、該システムクロックに同期した入力信号をチャネルデコードし、これにより、一様なワードフォーマットを有する対応するPCMビットストリームのフォーマット信号を供給するための手段。

**【 0 0 3 1 】**

該PCMビットストリームのフォーマット信号から、たとえば、FIFOのような、こ 50

れよりサンプルワードが中央演算処理に供給される中間的な記憶装置に記憶されているサンプルワードを形成するように、該PCMビットストリームのフォーマット信号をさらに処理するための手段。

#### 【0032】

或いは、本発明の装置は、共通のシステムクロックを使用して、共通のフォーマットの中央演算処理において異なるタイプのインターフェースへの出力信号をプリプロセスするために適するものである。該異なるインターフェースのタイプは、異なるサンプルクロック周波数、及び／又は異なるデータフレームのフォーマット又は異なるデータワードのフォーマットに関連している。本装置は、以下の構成要素を含んでいる。

#### 【0033】

サンプルワードから、システムクロックに同期したPCMビットストリームのフォーマット信号を形成することにより、該中央演算処理から出力され、たとえば FIFO のような中間的な記憶装置に記憶されるサンプルワードをさらに処理するための手段。このPCMビットストリームのフォーマット信号は、一様なワードフォーマットを有しており、該異なるタイプのインターフェースに適合している。

#### 【0034】

該異なるタイプのインターフェースに適合する異なるチャネルプロトコルに従い、該システムクロックに同期したPCMビットストリームフォーマットをチャネルエンコードし、これにより、対応するシステムクロックに同期した出力信号を供給するための手段。

#### 【0035】

該システムクロックに同期した出力信号から、もはやシステムクロックに同期しないが該タイプのインターフェースに従うインターフェースのタイプに適合した出力信号を発生するための手段。

#### 【0036】

本発明の有効な追加の実施の形態は、それぞれ従属的な請求項に開示されている。本発明の典型的な実施の形態は、添付図面を参照して説明される。

#### 【発明を実施するための最良の形態】

#### 【0037】

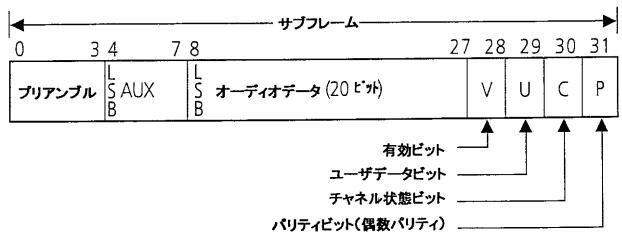

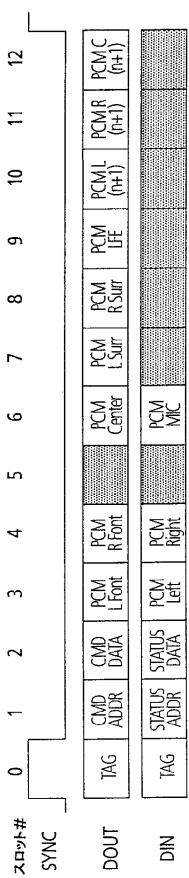

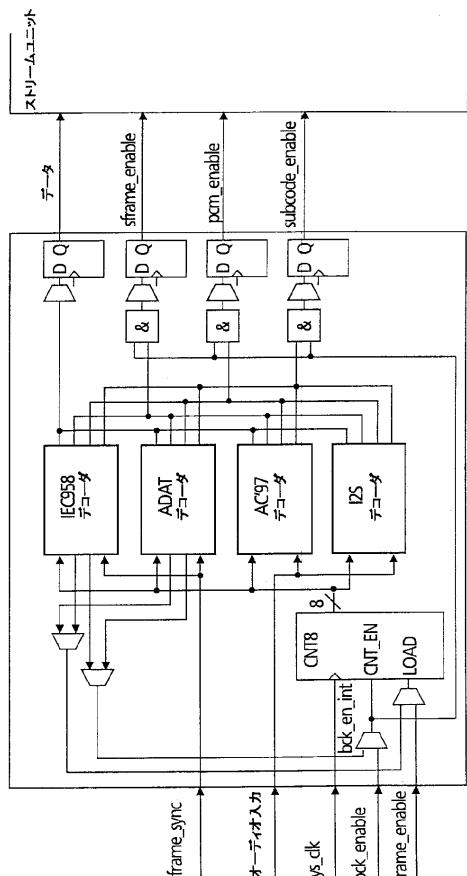

図2～図5は、IEC958サブフレームのフォーマットフレーム、ACフォーマットフレーム、ADATフォーマットフレーム及びI2Sフォーマットフレームをそれぞれ示している。これらの図から、フォーマットが非常に異なっていることが明らかである。

#### 【0038】

現在の最新技術による実現とは対照的に、図7に示されるチャネルデコーダのプロックは、要求されるプロトコルの全て又はほぼ全てをデコードする。この要求されるプロトコルは、固定された入力ピンに関連される。好都合なことに、プロトコルのデコーダ機能の全て又はほぼ全てを1つのユニットに実現することは、全ての個々のプロトコルのデコーダの追加される複雑さと同じ複雑さではない。これは、ロジックの一部（すなわち、IEC958, ADAT, AC'97及びI2Sボックス外のロジック）は、図7に示されるように共有することができるからである。IEC958及びADATデコーダにおけるクロックデータ分離器又はプリアンブル検出器のような特定の機能は、共有されていない。

#### 【0039】

他方で、マルチプロトコルのエンコーダ／デコーダ（コンバータ）に関連するI/O信号の数を、対応する簡単な单一プロトコルのエンコーダ／デコーダ（コンバータ）の更に多い数と比較したとき、同じ数のI/Oピン及び該ピンを接続するためのある種のマルチプレクサロジックにより、複数の单一プロトコルのエンコーダ／デコーダの解決策について更に低い複雑さとすることができますが、一般に、低いトランスペアレンシー及びフレキシビリティという犠牲を払うことになる。

#### 【0040】

ストリームユニット13は、多数の単方向のストリームの形式でデータ転送を実行する。それぞれのストリームに対して、1組のコンフィグレーションレジスタが割り当てられ

10

20

30

40

50

ており、どの入力信号を FIFO14（したがって、その後の処理システム）に転送すべきか、及び利用可能なPCMサンプルのタイムスロット（すなわち、第一、第二等、1つの信号入力についてのサンプルワード）のうちのどのタイムスロットで FIFO14に転送すべきかが判定される。それぞれのストリームは、処理システムにより独立にアクセスすることができるそれ自身の FIFO（領域）を所有しており、結果として、ストリーム当たりの別個のDMAユニット（図示せず）は、適切なDMAデータ転送のために必要とされる（ストリームは、互いに独立に動作する）。入力ストリームは、複数の信号入力について構成される場合（「チャネルアグレゲーション」、たとえば、 $3 \times 2$  チャネルストリームを形成する3つのIEC958インターフェース）、全ての信号は、同じインターフェースタイプに一致しなければならず、同じサンプリング周波数を有さなければならず、及び同位相でなければならない。ストリーム出力の処理及び特徴は、類似している。10

#### 【0041】

ストリームユニットについて、幾つかの設計オプションが存在する。独立な FIFOを使用することに対して、ソフトウェアにより適切なサイズに作られた分離されたストリーム FIFOに分割される単一の FIFO-RAMを使用し、FIFOからチャネルエンコーダ／デコーダにビットを直接転送するか、或いはチャネルエンコーダ／デコーダから FIFOにビットを直接転送することである。すなわち、任意の中間的なレジスタを必要とすることなしに、全ビットを連続して処理すること（全体のデータレートを制限する場合がある）、或いは、FIFO14とチャネルデコーダ11及びチャネルエンコーダ12の間に配置される中間的な（シフト）レジスタを使用することである。20

#### 【0042】

先に説明されたように、1つ又は複数のストリームユニットだけでなく、全てのチャネルエンコーダ／デコーダは、信号I/Oピンに接近した同期のため、共通のシステムクロックでクロックされる。最新技術の処理では、幾つかの入力及び出力ストリームが同時に転送される典型的なオーディオシナリオでは、SIOタイプ（シリアル入出力）の実現は、幾つかの異なる（ビット／チャネル）クロックを一般に使用して、関連するSIOユニットを実行する。したがって、SIOユニットを一体化することによる全体の最適化が不可能であるが、本発明では、使用される単一の（system\_）クロックのためにストリームユニット13にとって全体的な最適化が可能である。これにより、（ビット毎に、又は1回の読み出し／修正／書き込み用のレジスタを使用して）FIFOからシリアルオーディオビットストリームを直接読み出すか、あるいはFIFOにシリアルオーディオビットストリームを直接書込むことで、多数の組のオーディオデータバスのレジスタなしに、1つ又は複数の完全なストリームユニットを実現することが可能である。別の容易に実現可能となる機能は、チャネルアグレゲーションであり、すなわち、幾つかの同じタイプのI/O信号を共通のストリームにマージすることである。それぞれの論理ストリームは、該ストリームについてどのI/O信号が使用されているかを選択し、これにより、I/O信号のマルチブレクサは、ストリームユニットに配置される。30

#### 【0043】

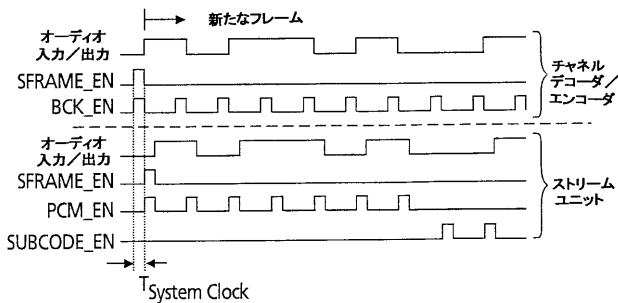

図12の上半部分では、チャネルエンコーダ11及びチャネルデコーダ12における幾つかのタイミングは、図12の下半部分のストリームユニット13における幾つかの信号のタイミングと共に示されている。40

#### 【0044】

先に説明されたように、システムクロック sys\_ck でチャネルエンコーダ／デコーダをクロックすることにより、マルチブレクサにより選択された幾つかの可能なオーディオビットクロックのうちの任意の1つによる、図11に部分的に示されている同期装置ユニットの主要部分に対するクロックを回避する。最後の同期ステージTFF1, TFF2及びRFF0は、対応するオーディオビットクロックにより直接クロックされる。したがって、チップの入力バス付近の同期は、2つ以上のフリップフロップが同じゲート制御された立ち上がり／立ち下りエッジ（gated edge）でクロックされるのを回避する。この同期装置は、図1及び図6のクロックユニットブロック16にそれぞれ含まれ50

ている。

【0045】

S I O タイプのものでさえ公知の実現は、複数のサンプルに関して動作しないだけでなく、現在のプロセッサ向けの単一サンプルのワードと典型的に同じプロセッサのマシンワードに関して動作しないという事実による問題点を有している。

【0046】

好都合なことに、検出されていないチャネルの置き換え (permutation)、及びタイムスタンプを使用したタイミングの良い出力は、図1又は図6のそれぞれに従う構成で実現することが容易である。これは、ストリームユニットがワードに代えてオーディオサンプルを処理するためである。

10

【0047】

幾つかの実施の形態が以下に説明される。

【0048】

図1及び図6では、チャネルデコーダ／エンコーダ11, 12とストリームユニット13の間のインターフェース信号は、対応する情報信号 `s frame_enable` (サンプルフレームイネーブル) を含んでおり、この情報信号は、1つのシステムクロック (`sys_clock`) のサイクルパルスであり、このパルスは、新たなサンプルの開始を示しており、ストリームユニット13のチャネルエンコーダ又はチャネルデコーダにより発生される。信号 `pcm_enable` 及び信号 `subcode_enable` のそれぞれの1サイクルのパルスは、関連するデータラインに有効な各PCMのサブコードビットを伝送又は要求する `sys_clock` サイクルを示している。

20

【0049】

[基本的なオーディオPCM及びストリームフォーマット]

Pチャネルオーディオ信号 (P = 1, 2, 3, サポートされるストリーム当たりの最大チャネル数) を転送するオーディオストリームは、サンプルのシーケンシャルな形式で転送され、それぞれのサンプル (たとえば、ステレオ又は6チャネルサンプル) は、チャネル当たり1つのP個のデータワード (たとえば、32ビットのデータワード) から構成されることが想定されている。そのとき、考慮されるオーディオインターフェースにより転送される入力ワードのオーディオコンテンツのサイズは、最大24ビットを超えない、すなわち最大24ビットを超える必要がない。したがって、たとえば、通常のRISCプロセッサ又はある種のDSP、或いはダブルワード $2 \times 16$ ビットとしてのオーディオワードを記憶する16ビットDSP向けのような、選択されたプロセッサ／メモリシステムのため、ワード当たりより多くのビットが利用可能である場合、又はたとえば、24ビットDSPの場合において24ビットのうちの全てのビットが要求されない場合、追加のワードビットを使用して、他のサイド情報を転送することができる。

30

【0050】

本発明の処理システムにデータを入力する場合、かかるサイド情報を取ることが要求される場合があるが、この処理は、追加の費用なしで、移動、スケーリング、整数から浮動小数点への変換、浮動小数点から整数への変換のような必要な他の動作とともに容易に実行することができる。

40

【0051】

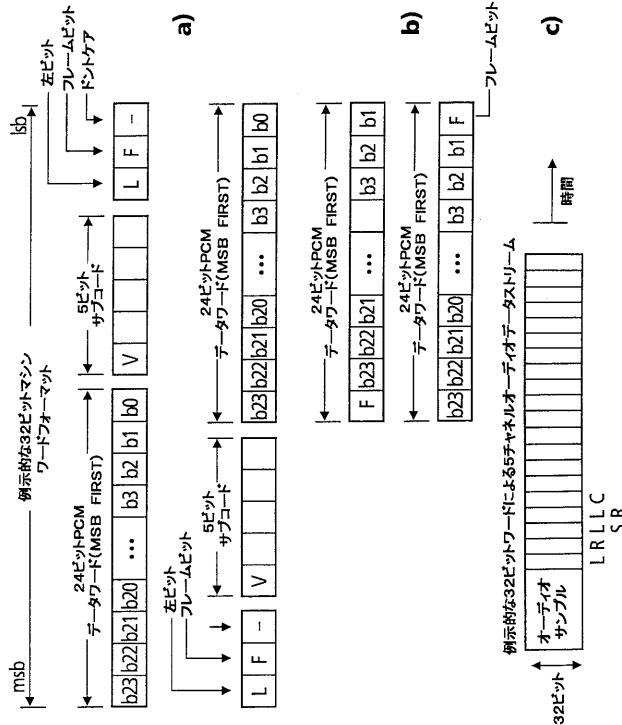

図8a及び図8bは、たとえば、FIFO14又はシステムメモリで処理されるような、32ビット及び24ビットのマシンワード (図8c) 向けの、可能なサンプルフォーマットを示している。サイド情報のビットの簡単な変換／除去或いは挿入のために、(より長い)ワードにおいて左揃え又は右揃えのいずれかにされるPCMビットを表すフォーマットが使用される。したがって、これらの変形例のみが示されている。PCMビット、Fビット及びLビットに関して、全てのオーディオサンプルは、使用されるチャネルエンコーダ／デコーダとは無関係に同じ表現を有しており、2つの代替的なフォーマットのうちの1つのみがGPI/GPO又はステージについて選択され、したがって、ハードウェア又はソフトウェアに対して固有なサンプルを表している。

50

## 【0052】

理解 / 表現を容易にするために、本実施の形態に関する以下の説明は、32ビットのフォーマットに限定される。全ての機能性、又はあるケースでは機能性のうちのサブセットは、より長いマシンワード又はより短いマシンワードで容易に実現することができる。

## 【0053】

## [サブコード]

個々のサンプルワードに挿入される第一のタイプのかかる追加の情報は、サブコード情報とすることができます、SODIF(VUCP)、ADAT(C1..C4)、AC97(Tags)のような幾つかのインターフェースは、サブコード情報を定義している。SPDIFのケースでは、サブコードビットは、それぞれのサンプルと既に直接関連付けされて、転送される。図8aは、例示的な32ビットのワードフォーマットであり、24ビットをデータに使用し、ワード当たり最大5ビットをサブコードに使用し、3ビットを更なる情報に使用する。サブコードの総量及び内容は、インターフェースのタイプに依存する。本発明によれば、オリジナルのサブコードの総量は保持されるが、サブコードのビットに使用されるビット位置は固定及びユニークに選択することができる。唯一の例外は、有効ビット(V)であり、それぞれのサンプルの有効性を示している。この情報項目は、信号入力の場合に、ストリームユニット13により特別な方法で解釈及び処理することができる。

a) 入力ワードは、Vビットを含んでおり、受信されたときに送出され、これにより、有効な情報のソフトウェア処理が可能となる。

b) 又は、全てのサンプルワードが無効である場合に、Pチャネルサンプルは廃棄される(FIFO/メモリへの書き込みを禁止する)。

c) 又は、無効なワードがミュートされる。

d) 又は、サンプルワードは、CDプレーヤのような既存の装置で公知の形式で周囲の有効なワードから補間される。

## 【0054】

サブコードの転送のための好適な方法は、IEC958入力のケースにおいて関連するサンプルワードと共に、4つのVUCPサブコードビットを転送すること、(4つのサブコードビットを有するフォーマットについて)Pチャネルサンプルのうちの第一のワードにおける全てのADATサブコードビットを転送すること、I2Sのケースにおける隣接する非PCMの位置(non-pcm location)にサブコードのビットを埋め、単一のI2Sインターフェースを介してDSPのような装置との結合されたオーディオとサブコードのデータ交換を可能にし、及び/又は(データスロットに関係する)AClinkのタグビットで有効ビットを埋める。

## 【0055】

## [チャネルの置き換えの回避]

オーディオ入力及び出力に関する1つの問題は、チャネルの置き換えに関する可能性である。これは、幾つかの典型的なマシンワード(典型的にはオーディオチャネル当たり1つ)が殆どのオーディオハードウェアの構成において单一のPチャネルサンプルを転送することが必要とされる事実による。したがって、プロセッサシステム(プロセッサ、DMAユニット、シリアルI/Oユニット、FIFO)は、個々のマシンワードに対応するのみであって、より大きなエンティティに対応するものではない。したがって、1つのデータワードがオーディオデータストリームから誤って挿入又は消去された場合、「マシン」ワードのシーケンスを読んでいる装置又はステージ(サブルーチン、スレッド、プロセッサ、オーディオインターフェースハードウェア等)は、どのワードがどのオーディオチャネルのうちの1つに関連されているかに関する情報のトラックを解放する可能性がある。

## 【0056】

図6に説明されるようなシステムでは、システムプロセッサ、DMA、或いは割り込みベース又はボーリングベースのオーディオストリームの入力/出力を含んでおり、かかる

10

20

30

40

50

チャネルの置き換えの原因は、誤った F I F O アクセス、入力及び出力のインタイムのサービスを不可能にする一時的なプロセッサの計算負荷、或いは一時的に増加される割り込み遅延である場合がある。

#### 【 0 0 5 7 】

したがって、適切なチャネルでストリーム入力及び出力を開始することは、入力／出力がその後に正しいことを保証しない。全ての先の影響がシステムエラーとして考慮された場合、及び正常の（デバックされた）状況下にあるように見えない場合であっても、正しいチャネルタイプの出力がチェックされる実用が存在する。図 6 に説明される例示的なオーディオインタフェースでは、説明される問題は、F I F O 又は D M A コントローラにおいて生じる可能性がある。しかし、ストリームユニット 1 3 は、チャネルエンコーダ／デコーダにより転送される s f r a m e \_ e n a b l e 信号のためサンプルの境界を認識しており、したがって、このチェックを実行することができる。10

#### 【 0 0 5 8 】

本発明の特徴は、チャネルの置き換えの検出及び補正を可能にすることであり、最終的なデータストリームの消費者によって識別することができるよう、個々のサンプルをそれらのタイプで記録することである。安全かつ実現が容易な測定は、（特に使用されていない）ビットのうちの 1 つにより、オーディオサンプルのサンプルワードのうちの 1 つ、特に“ L ” ビット、すなわちサンプルの最初のワードを“ 1 ” に記録すなわち設定し、サンプルの全ての他のワードについて、このビットを“ 0 ” に設定することである。したがって、左揃え／右揃えのエラーは、1 サンプル毎に検出可能となる。20

#### 【 0 0 5 9 】

一方で、オーディオデータ転送の一端にはプロセッサソフトウェアがあるので、このビット挿入、すなわちそれぞれのサンプルに対するこのチェックは、プロセッサにとって負荷が比較的高くなる。他方で、聴取者がチャネルの置き換えを検出するためにある程度の時間を必要とすることを考慮して、それぞれ L 番目のサンプル（ L は、たとえば 0 . 1 秒を下回る検出時間となるに十分に小さい数）のうちの最初のワードのみを記録／チェックすることは十分なことである。したがって、4 8 キロヘルツ当たり 1 1 5 2 / 1 0 2 4 サンプルのレンジにおける典型的なオーディオコーデックのフレーム、又は D M A ブロックサイズは、「 F ビット（フレームビット）」のマークのための距離として使用することができる。30

#### 【 0 0 6 0 】

D M A ブロックサイズの距離を使用することで（それぞれの D M A ブロックの最初のサンプルのうちの最初のワードは F = “ 1 ” で記録される）、オーディオインタフェースハードウェアは、（処理システムのメモリにおける） D M A ブロックの最初のサンプルと同じである、 F ビットの組を有するサンプルが出力／入力されるポイントをタイミングよく正確に判定することができる。この特徴は、オーディオインタフェースのハードウェアによるタイムスタンプ及びブロックエラー（以下を参照）のような追加のサイド情報の測定、及び該サイド情報を D M A ブロックと協力して転送／処理すること（完了）を容易にする。

#### 【 0 0 6 1 】

オーディオ入力処理のケースでは、 F ビットは、ストリームユニットハードウェアにより、 F L E N オーディオサンプルのそれぞれのシーケンスの最初のワードについて設定される。ストリームユニットのはじめのスタートアップ又はリストートは、 F I F O 1 4 に書き込まれた最初のサンプルの最初のワードが F = “ 1 ” で記録されるようなやり方で常に行われる。 D M A （或いは割込み又はポーリング）データ入力は、関連する目的地のメモリ位置へのそれぞれ単一の（ D M A ）ブロックの転送後に発見される最初のワードが、常に、 F ビットの組を有する当該ワードであるように、同じブロック長 F L E N \* P を使用するためにセットアップされる。これは、（ D M A ）ブロック完了処理の間にチェックされる。かかる（ D M A ）ブロックの最初のワードが設定されていない場合、データ入力はミスアラインメントされており、このストリームユニット（及び関連する D M A ）につ4050

いての入力処理のリスタートが必要とされる。

#### 【0062】

出力処理の場合では、出力のために使用される(DMA)ブロックのサイズは、ストリームユニット13と同様に、FLEN\*Pワードの値に再び初期化される。出力のためにソフトウェアにより準備されるそれぞれのDMAブロックについて、最初のFビットのみが設定され、他の全てのビットがリセットされる。ストリームユニット13の開始に応じて、関連する FIFO14(すなわち、当該ストリームに拘束されるその一部)は、空きメモリ状態にされなければならない。したがって、開始後にストリームユニット13により読み出される最初のワードは、Fビットの組を有するワードであり、その時、Fビットのリセットを有するFLEN\*(P+P)番目のワードでは、Fビットが再び設定される等となる。10

#### 【0063】

ストリームユニットのハードウェアは、Fビットの組の出現をチェックする。Fビットが誤入された場合、すなわち、FビットがPチャネルサンプルの最初として出力されないワードについて設定されている場合、Fビットの組を有するサンプルが前のサンプルから厳密にFLENサンプル離れていない場合、或いはFビットがFLENサンプルの間にゼロである場合、ストリームユニットは停止され、エラー状態にスイッチされる。この状態は、出力処理をリスタートすることができるよう、ソフトウェアにより検出される(状態変化による割込み又はポーリング)。20

#### 【0064】

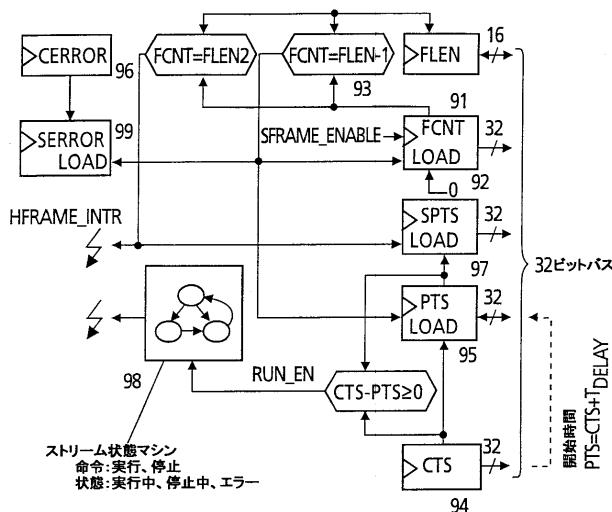

図9には、ストリームユニット13で必要とされるハードウェアが示されている。フレームカウンタFCNT92及びフレーム長(すなわち(DMA)ブロックサンプルカウント)レジスタFLEN91は、オーディオ入力の間に、Fビットの組を挿入して、オーディオ出力の間にFビットの適切な出現をチェックすることが要求される。図9のサンプル実現について、FCNTは、それぞれ(Pチャネル)のサンプル(より詳細には、適切なチャネルユニットからのそれぞれのsfra me\_enableパルス)についてインクリメントされ、0からFLEN-1までカウントする。その後、FCNTは、“0”に再びリセットされる。最終的に、FLEN-1に達することは、次のサンプルの最初のワードがFビットの組で記録されることを示す。30

#### 【0065】

Fビットを使用することの代替は、サンプル間にブロックベースで挿入されるSYNCワード(並びに、最終的にはブロック長、及び選択的にはチェックサム及び他のサイド情報)の挿入/チェックである。これは、ワード当たり1ビットを必要としないという利点を有する。代わりに、全てのビットは、オーディオデータ向けに使用することができるが、このメカニズムは、オーディオデータワードが同期ワードであるとして誤って解釈されるという可能性のため(このsyncコードが禁止されたデータワードである場合を除いて)、完全に問題がないわけではない。検出がチェックサムにより更に確実に行われたとしても、スタートアップは、SYNCワードの繰り返される出現の後にのみ実行される。別の代替は、(ワード当たりの追加ビット、すなわち追加のポインタにより) FIFO14においてブロックの最初のワードを記録し、それぞれのブロック転送の後、このポインタ対実際のDMA(又は割込み)ポインタをチェックすることである。この実施の形態は、DMAの連鎖を排除するものである。40

#### 【0066】

更なる代替は、専用DMAユニット(図示せず)を使用することであり、FIFOが使用される場合にFIFOのワード記録と共に、できる限りオーディオセル/インタフェースに組み込まれる。この場合、ストリームハードウェア及びDMAハードウェアは、DMAブロックの転送とストリームユニットのFCNT/FLENブロックが同相であるように動作するか、DMAユニットがワードの概念を採用するように動作する。それにもかかわらず、この代替は、汎用のDMAユニットに代わって、専用DMAユニットを必要とするという不都合を有する。50

【0067】

[F L ビットフィールド、ドントケア定義]

【表1】

| L | F | 記述            |

|---|---|---------------|

| 0 | 0 | 符号拡張          |

| 0 | 1 | 新たなソフトウェアフレーム |

| 1 | 0 | 左チャネル         |

| 1 | 1 | 符号拡張          |

10

オーディオインターフェースセルによる出力のためにDMAバッファを準備するとき、プロセッサ動作の回数を低減するために、Fビットが拡張されてFL2ビットフィールドとなる。表1及び図8aを参照されたい。表によれば、LF = 01bは、DMAブロックの最初のサンプル(F = 1)のうちの最初のワード(L = 0)を示しており、LF = 10bは、サンプルの最初でないワードを示している。他の2つのコードLF = 00b及びLF = 11bは、「特定的ではないサンプル」を定義している。

【0068】

20

オーディオデータの入力に応答して、ストリームユニット13は、コードLF = 01b及びLF = 10bのみを挿入し、したがって、各サンプルは、L又はFのいずれかで正しく記録され、個々のサンプルのアラインメントと同様にDMAブロックをチェックすることができる。オーディオデータの出力の間、ソフトウェアは、はじめに、LF = 00b又はLF = 11bコードを有する符号拡張かつ右揃え24ビットPCMのビット数(32ビット以内)、又は下位8ビットが最初は0である左揃え24ビットPCMのビット数のいずれかを有するDMA出力バッファを準備する。ストリームユニット13は、コードLF = 00b及びLF = 11bを「特定的でないサンプル情報」として解釈し、該サンプルを次のワードとして出力する。それぞれのDMAバッファの真の最初のワードは、DMAブロック出力を開始する前に、LF = 10bコード、すなわちストリームユニットによるFビットのチェックを導くコードでソフトウェアにより記録される。チェック結果が「真でない」場合、ストリームユニットは停止し、ソフトウェアにより出力処理を再開することができる。上記説明を参照されたい。

30

【0069】

オーディオ入力処理により得られるLFビットフィールドは、DMAブロック長及びチャネル数が等しい場合にオーディオ出力処理について当てはまるように、再使用することができる。

【0070】

40

[タイムスタンプ、ブロックエラー、SPTS]

先に説明したストリームユニット13の拡張は、それぞれ独立な入力又は出力ストリーム当たりの1つの拡張、すなわちカウンタ92FCNT、レジスタ91FLEN、及びFビットメカニズムであり、DMAバッファ(図示せず)の真の最初のワードに関連するレジスタ95における正確なPTSタイムスタンプを取り込むこと、及びDMAブロックにおける正確なサンプルのためのエラー情報を収集する累積的なエラーレジスタSERROR99を取り込むことを容易にする。これは、比較結果93FCNT = FLEN - 1及び当該取込みを可能にするためのsfraframe\_enableを使用して行われる。

【0071】

図9におけるカウンタ94CTS(現在の時間)は、それぞれのシステムクロックをカウントし、最大値0xFFFFFFFに達したときに“0”に巻き直しするマシンワード幅(32ビット)のアップカウンタを表している。カウンタCTSの出力は、オーデ

50

イオインターフェースセルのための時間基準として使用することができる。ステージ 95 PTS (プレゼンテーション・タイム・スタンプ) は、以下に基づいて CTS 値を取込むことである。

(FCNT = FLEN - 1) AND sframe\_enable

チャネルエラー記憶装置 96 CERROR は、SErrorレジスタ 99 によりサンプリングされたときクリアされ、その後、(たとえば、(FCNT = FLEN - 1) AND sframe\_enable で) 再びサンプルされるまで、入力又は出力信号に関連する全てのエラー情報を収集する。したがって、SError は、まさに終了された DMA ブロック / 終了されようとしている DMA ブロックの全てのサンプルに関連するチャネルのエラー情報を正確に含んでいる。オーディオ入力の間、アクティブ状態にある SERR 10 OR は、完全な入力ブロックがエラーについて更に検査されるべきであるか、又はミュート或いは無視されるべきかのいずれかであることを示し、後者の 2 つの機能は、ブロックベースで都合よくエラーを処理することができる。

#### 【0072】

オーディオ入力の間、はじめに、ストリームユニット 13 は、(FCNT = FLEN - 1) のブロックエンド、サンプル PTS 及び情報アイテム SERROR を発見し、次のサンプルを  $F = 1$  で記録することができる。次いで、 FIFO 14 から最後のブロックサンプルを読み出した後、DMA ユニットは、そのブロック完了信号 (割込み) を発生する。したがって、PTS 及び SERROR レジスタの値は、DMA 完了の割り込みの間に、ソフトウェアにより都合よく読み出すことができ、まさに終了された DMA ブロック又は次の DMA ブロックに付属させることができる (後者は、両者の値がブロックエンドでサンプリングされるため、PTS にとって都合がよい)。 20

#### 【0073】

明らかに、これは、「使用される FIFO サイズ < FLEN \* P」及び「割込み遅延 < DMA フレーム周期」であることを要求しており、さもなければ、サンプリングされた PTS / SERROR 値と DMA ブロック値との間の関係が失われる可能性がある。「使用される FIFO サイズ」は、実際に記憶されるサンプルワード数を示す。「DMA フレーム周期」は、時間間隔 FLEN / Fs を示し、Fs はサンプリング周波数である。 30

#### 【0074】

簡単な代替では、「割込み遅延 < FLEN / Fs」を使用することができる。

#### 【0075】

オーディオ出力について、DMA 完了状態は、サンプリングが FIFO 遅延のために発生する前に生じる場合がある。したがって、DMA 完了状態の間に PTS と SERROR とを読み出すことは適切ではない。代わりに、たとえば、割り込みにより、又は PTS を読出す代わりに、及び SPTS レジスタ 97 (その時間でのサンプル PTS) を読出すことにより、DMA ブロックの中央 (すなわち、FCNT = FLEN / 2)、及びサンプルの両方の値を読むことは、「使用される FIFO サイズ < 0.5 \* FLEN \* P」及び「割り込み遅延 < 0.5 \* FLEN \* 1 / Fs」である限り使用することができる。ここで、Fs はサンプリング周波数である。たとえば、sys\_clock 発振器について最も悪いケースである 100 ppm の精度、及びサンプリング周波数 44100 Hz での 1152 サンプルの DMA フレームサイズによれば、DMA フレーム周期は 26.1 ms となり、その結果、約 5.2 μs という最も悪いケースのタイムスタンプ精度となり、この精度は、基準クロック発振器が 100 ppm の精度を有する場合にも達成可能である。 40

#### 【0076】

##### [タイムド・スタートアップ]

図 9 と共に説明される更なる機能は、正確に時間設定されたストリームユニット 13 の起動である。ストリームユニットは、空きメモリ状態の FIFO 14、及び停止されたストリームユニットシーケンサ (図示せず) で開始される。PTS レジスタ 95 は、(CTS に関連する) 適切な開始時間、及びストリーム状態マシン 98 に発生される RUN 命令でロードされる。CTS が開始時間に進んだ後、すなわち、条件 mod (CTS - PTS 50

) 0 が真である場合、ランイネーブル信号 R U N \_ E N がストリーム状態マシン 9 8 に発生される。

### 【 0 0 7 7 】

#### [ 共通の I / O タイミング ]

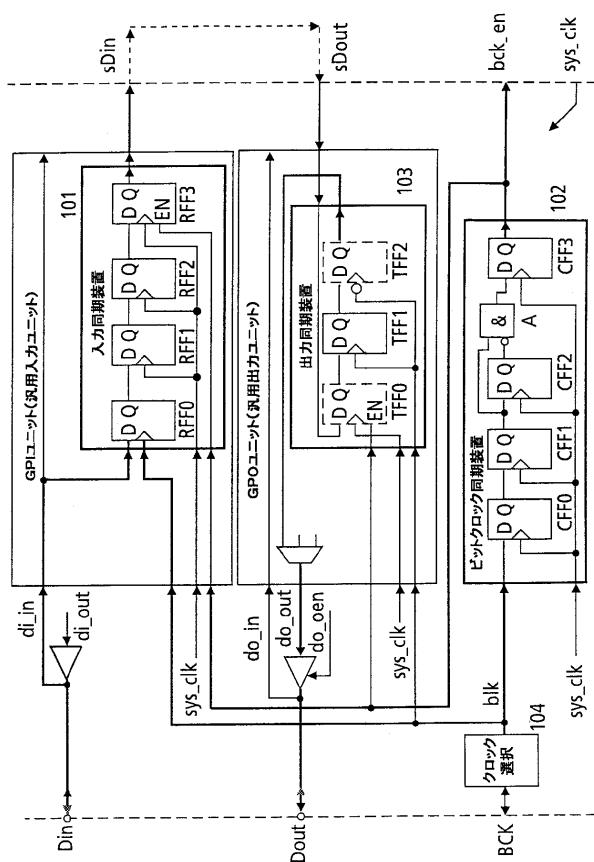

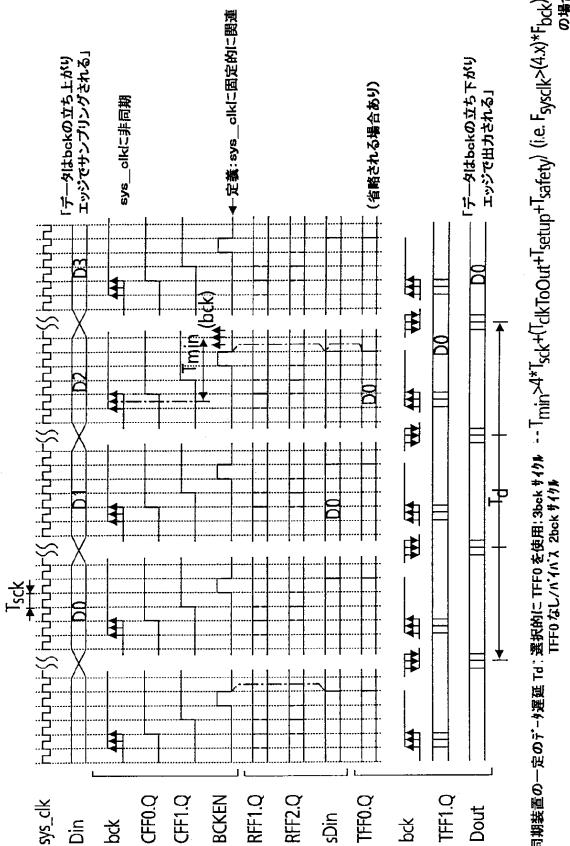

入力信号及び出力信号は、「ビットクロック ( b c k ) 領域」から更に高いシステムクロック ( s y s \_ c l k ) 領域に同期することができ、それによって、ビットクロック領域の入力から出力まで “ i n p u t - t o - o u t p u t ” の遅延は、簡単な複数の「ビットクロック」周期により表現することができ、「システムクロック」周波数とは完全に独立である。先に説明したような I 2 S ( 図 5 参照、 B I T \_ C L K に同期する D A T A / L R C K ) 又は A C L i n k ( A C 9 7 ) インタフェースのような、別々のクロック、並びにデータ及び / 又は同期信号を有するシリアルオーディオデータインタフェースに関連する信号は、インターフェースのビットクロック又はチャネルクロックに代わり、共通の ( 更に高い ) システムクロック ( 図 1 0 、 s y s \_ c l k ) のみを使用するロジックにより処理される場合 ( 図 1 0 における B C K = b c k 、図 5 における B I T \_ C L K ) 、オーディオインターフェースの 1 つ以上のクロックが固定位相を有さず、かつシステムクロックの整数倍の正確な周波数を有さない限り、追加のクロック同期ステージが必要とされる。このクロック同期は、図 1 0 に示されるような R F F 1 / R F F 2 及び / 又は C F F 0 / C F F 1 のそれぞれのような 2 つの D フリップフロップの構成を使用することで達成することができる。これらの D フリップフロップは、システムクロック s y s \_ c l k でクロックされる。同期されるべき 1 つ以上の入力信号 ( R F F 0 の出力 Q での信号及び / 又はクロック b c k ) は、第一のフリップフロップ C F F 0 及び R F F 1 のそれぞれの D 入力に供給される。このように、「同期された」入力信号は、第二のフリップフロップ C F F 1 及び R F F 2 の Q 出力で利用可能である。かかる 2 つのフリップフロップ回路は、「準安定」という公知の影響のため、第一のフリップフロップのエラーの確率を十分に低い量に低減する。ホールドウィンドウに関する第一のフリップフロップの入力のセットアップの妨害により、技術に依存した確率に関係する所与の期間の間、フリップフロップの未定義の出力状態がもたらされる。フリップフロップのかかる準安定状態は、不安定である。しかし、2 つのフリップフロップ回路により、それぞれのフリップフロップは、好都合なことに、約 1 クロック周期内でその 2 つの安定状態のうちの 1 つに強制的に再び設定される。

### 【 0 0 7 8 】

より詳細には、図 1 0 における基準クロック b c k について一般に使用される同期装置の形態は、( C F F 0 及び C F F 1 のような ) かかる準安定抑圧回路、及び ( たとえば、フリップフロップ C F F 2 、 A N D ゲート A 及びフリップフロップ C F F 3 による立ち上がりエッジについて具体化される ) その後のエッジ検出器からなる構成を使用し、単一のシステムクロックサイクルを示すイネーブル信号 b c k \_ e n を取得する ( たとえば、オリジナルのクロック b c k のそれぞれの立ち上がりエッジ当たり 1 つのイネーブルサイクル ) 。この場合、類似の入力回路 ( 「入力同期装置」 1 0 1 ) の出力は、後続する同期ロジック ( 同期装置 1 0 1 における R F F 3 ) により読むことができる。入力同期装置 1 0 1 及びビットクロック同期装置 1 0 2 の ( システムクロック数で測定される ) 遅延を殆ど同一に維持することは、たとえば、約 1 周期のシステムクロック s y s \_ c l k のウィンドウ内で信号 b c k の立ち上がりエッジ付近で入力信号 ( R F F 0 . Q ) をサンプリングするとして説明することができる入力側 ( b c k 、 R F F 0 . Q ) のシステム動作となる。したがって、クロック b c k に同期し、かつシステムクロック s y s \_ c l k に非同期である入力信号 ( R F F 0 . Q ) は、システムクロック s y s \_ c l k が、同期されるクロック b c k よりも幾分高い限り、たとえば、クロック b c k の立ち上がりエッジ付近で正しく読む込むことができる。フリップフロップ R F F 0 は、適切に定義された ( 小さな ) セットアップを達成するために、ビットクロック b c k で入力信号 D i n をサンプリングし、システムクロック s y s \_ c l k のサイクルタイムにより決定される ( より大きな ) ウィンドウのみを達成する代わりに、入力データ D i n の範囲 ( たとえば、 b c k の立ち

上がりの傾斜付近)をホールドする。

【0079】

図11のタイミングチャートは、図10の入力同期回路内で生じる各種信号をその時間的な関係において示している。サンプルウィンドウ、すなわち入力信号のサンプリングを行うことができる期間は、入力信号Dinに関して示されている。

【0080】

図10に関連して、代わりに、クロックbckの立ち下がりエッジ又は両方のエッジに関してサンプリングする等価回路を使用することができる。

【0081】

図10の回路では、同期(sys\_c1k)領域からインタフェースの形式特定の領域へのデータの出力は、システムクロックsys\_c1kでクロックされ、信号bck\_enでイネーブルされるTFF0のようなフリップフロップの出力信号を使用することにより、出力同期装置103において達成することができる。(sys\_c1k周波数)/(bck周波数)の整数比が、たとえば、次のbckの立ち上がりエッジの前で十分に大きい限り、(フリップフロップのクロックから出力までの“clock-to-output”遅延を加えて)bck\_enサイクルの終了で、したがって、たとえば、bck\_enパルスが生成されるクロックbckの立ち上がりエッジの後に出力データが現れる。bckエッジに関して適切に定義された時間での出力ポイントを取得するために、TFF0の出力は、たとえば、bckの立ち上がりエッジでフリップフロップTFF1によりリサンプリングされ、これにより、その出力Qは、オーディオインタフェース向けに使用される標準的なI/O機能に準拠するために、bck\_enの立ち下がりエッジでフリップフロップTFF2によりリサンプルされる。入力は、ビットクロックの立ち上がりエッジでサンプリングされ、出力は、ビットクロックの立ち下がりエッジで変化する。また、図11のタイミングチャートは、図10の出力同期回路内で発生する対応する信号をそれらの時間的な関係で示している。

【0082】

代わりに、クロックbckの立ち下がりエッジ又は両サイドのエッジに関してサンプリングする等価な出力同期回路を使用することもできる。

【0083】

フリップフロップTFF0及びTFF2は、ある種の範囲で選択的である。

【0084】

また、TFF0は、同期装置の外部に配置することができ、これにより、(図10における信号sDoutについても当てはまるように)sys\_c1kの同期ロジック領域のそれぞれの出力信号は、同じ特性、すなわち、sys\_c1kでクロックされ、bck\_enでイネーブルされるフリップフロップから生じる特性を有していかなければならない。

【0085】

TFF2は、オーディオインタフェース向けに使用される先の標準的なI/O特性が要求される場合にのみ必要とされる。TFF2が必要とされない場合、入力サンプリング及び出力変化は、クロックbckの同じタイプのエッジ、たとえば立ち上がりエッジにより影響を受ける。

【0086】

クロック選択ユニット104は、同期処理のために使用される、外部のビットクロックBCK又は内部のビットクロックbckのいずれかを選択する。内部クロック源が使用される場合、この同じクロックをBCKに出力することができ、又は出力しないこともできる。また、クロック選択ユニットは、通過する信号を反転する。

【0087】

入力/出力/クロック同期装置の組は、以下の構成からなる。

ビットクロックbckの同じタイプの「サンプル」エッジ(たとえば、立ち上がりエッジ)でクロックされる入力ステージRFF0及び出力ステージTFF1。反対のタイプの「出力」エッジでクロックされる第二の選択的な出力ステージTFF2。ビットクロックb

10

20

30

40

50

$c_k$  ( $CFF0$ ,  $CFF1$ ) 及びデータ入力  $Din$  ( $RFF1$ ,  $RFF2$ ) のための準安定「抑圧」回路、すなわち、少なくとも 1 つのフリップフロップが、 $SYSclk$  でクロックされ、かつ  $bck\_en$  でイネーブルされる  $sys\_clk$  領域で動作し ( $RFF3$  及び  $FFF0$ )、以下の特性を有している (フリップフロップ  $FFF0$  を用いることなしに、正確な値は図 10 における好適な実施の形態で適用される)。

#### 【0088】

a)  $bck$  に対する  $Din$  のセットアップ及びホールド間隔は、 $sys\_clk$  特性とは独立に、 $RFF0$  により決定される。b)  $bck$  の「出力エッジ」(たとえば、立下りエッジ) から  $Dout$  までの伝播遅延は、(使用された場合には)  $FFF2$  又は(さもなければ)  $FFF1$  のクロックからデータ出力までの遅延により特徴付けられ、 $sys\_clk$  パラメータにより特徴付けられるものではない。c) 比 ( $sys\_clk$  周波数) / ( $bck$  周波数) が  $3 \dots 4$ 、よりも大きい限り、 $Din$  と  $Dout$  の間の 2 つの  $bck$  サイクルのうちの有効な「同期装置の一定の遅延」(図 11 参照、 $T_d$ ) が適用される。

#### 【0089】

この遅延は、 $sDout$  と  $sDin$  が直接連動している場合(一点破線)であって、 $FFF0$  フリップフロップが省略される場合に適用される。( $FFF0$  のような)ループに挿入されるそれぞれの追加のフリップフロップは、別の  $bck$  サイクルをこの遅延に加える。すなわち、システムクロックは、ビットクロックよりも有意に高くなればならないが、同期領域のためのロジックは、周波数の比とは独立に設計することができる。

#### 【0090】

準安定抑圧回路及びエッジ検出器の変形例が可能である。同じ信号の異なるクロックエッジに関してクロックすること、及び / 又は  $CFF1$  と  $CFF2$  のフリップフロップを 1 つのフリップフロップに結合することで、同じ準安定なエラーの確率を達成するために、最大の可能な  $sys\_clk$  周波数を低下する代償として、要求される ( $sys\_clk$  周波数) / ( $bck$  周波数) の比を減少することができる。図 10 における例示的な実現は、その周波数の比を約“2”に低下するが、同じシステムクロックが使用された場合、準安定を決定するために利用可能な時間が要素“2”を超える分だけ短縮される。

#### 【0091】

オーディオインターフェースのうちの幾つか (I2S インタフェースでは  $LCK =$  左右指示、AC97 インタフェースでは  $SYNC$ 、或いは通常のシリアル DSP インタフェース向けのワードストローブ) においてのみ必要とされ、存在する同期信号は、原則として、同期信号のエッジを有する、それぞれシリアル転送されるオーディオ ( $m$  チャネル) サンプルのうちの最初のサンプル(又はある他のビット  $n$ )を示すものであって、 $Din$  及び  $Dout$  信号のように扱うことができる。同期信号を入力同期装置(図 10、101)に入力すること、かかる同期信号を出力同期装置(図 10、103)に出力することができる。これは、これらの同期信号は、データ信号と同じタイミング又は類似のタイミングを典型的に有しているためである(入力が  $BCK$  の一方のエッジでサンプリングされ、出力が  $BCK$  の反対のエッジでサンプリングされる)。クロック同期装置は、ビットクロックのみに必要とされ、このビットクロックに同期される転送された全ての他の信号は、入力及び出力同期装置のセルにより処理される。

#### 【0092】

結果的に、データ入力信号に対する同期信号は、データ出力信号に対する同期信号と同様に、同期ロジックのために異なる遅延を受けないが、出力サイドに対する入力サイドは(データ出力に対する同期入力のように)、図 11 に  $Dout$  に対する  $Din$  のケースについて示されるように、遅延  $T_d$  を受ける。

#### 【0093】

本発明のストリームユニット及び同期装置の効果は、以下に示される。チャネル ( $F$  ビット) の置き換えを回避することができる。 $F$  リビット関係、ドントケア出力同期信号、(PTS) ブロックのタイムスタンプが使用される、タイムド・スタートアップが実行可

10

20

30

40

50

能である、ブロックエラー処理をストリームユニットに組み込むことができる。

【0094】

より低い構成の複雑さ。これは、典型的な要求されるストリームユニットの数がプロトコルユニット／シフタユニットの数よりも少ないことによる。

【0095】

単一のソフトウェアによる実現が可能。これは、単一のストリームユニットでの実現及びオーディオデータと共にサイド情報を処理することによる。

【0096】

一定のビットクロック遅延を有する同期装置に関して、一方で、同期されるビットクロックよりも有意に高いシステムクロックが要求され、したがって、すべての同期ケース向10けに適用することができない。しかし、このシステムクロックは、オーディオアプリケーション向けに適用することができる。これは、典型的なオーディオビットクロック周波数は、実際のI C技術向けに、及びある程度に現在のF P G A技術向けに適用できるシステムクロックよりも有意に低いためである。この一定のビットクロック遅延は、全ての比s

y s \_ c l k / b i t \_ b l k > Nについて達成することができる。ここで、Nは選択された同期ロジックに依存する。

【図面の簡単な説明】

【0097】

【図1】本発明のデジタルオーディオインタフェースユニットに関する簡略化されたブロ20ック図である。

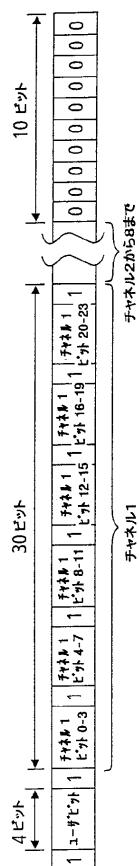

【図2】I E C 9 5 8サブフレームフォーマットを示す図である。

【図3】A C ' 9 7フォーマットフレームを示す図である。

【図4】A D A T フォーマットフレームを示す図である。

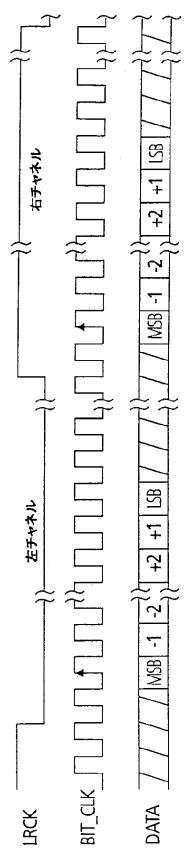

【図5】I 2 S フォーマットフレームを示す図である。

【図6】図1のブロック図のさらに詳細な図である。

【図7】チャネルデコーダのブロック図である。

【図8】F I F O又はシステムメモリ(図示せず)における記憶のためのフォーマット例である。

【図9】ストリームユニットで使用されるカウンタ回路を示すブロック図である。

【図10】G P I /シンクロナイザユニットのブロック図である。

【図11】同期タイミングを説明するタイミングチャートである。

【図12】チャネルエンコーダ／デコーダ及びストリームユニットのタイミングを説明するタイミングチャートである。

【符号の説明】

【0098】

- 1 1 : チャネルエンコーダユニット

- 1 2 : チャネルデコーダユニット

- 1 3 : ストリームユニット

- 1 4 : F I F O

- 1 5 : バスインタフェース

- 1 6 : クロックユニット

- 1 7 : タイマーユニット

- 1 8 , 1 9 : レジスタファイル

- 1 0 1 : 入力同期回路

- 1 0 2 : ビットクロック同期装置

- 1 0 3 : 出力同期回路

- 1 0 4 : クロック選択ユニット

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【 四 5 】

【 四 6 】

【 図 7 】

〔 四 8 〕

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(72)発明者 ウルリヒ シュライバー

ドイツ連邦共和国 30827 ガルブゼン ライファイゼンシュトラーセ 7

(72)発明者 マルクス シュナイダー

ドイツ連邦共和国 30159 ハノーヴァー ケストナーシュトラーセ 20

(72)発明者 ウルリヒ グリース

ドイツ連邦共和国 30419 ハノーヴァー フリーデンナオアー・シュトラーセ 20ベー

F ターム(参考) 5K034 AA05 CC05 DD01 HH61 PP01

5K047 AA11 DD01 GG43 LL06 MM26 MM38