# ITALIAN PATENT OFFICE

Document No.

102008901686936A1

**Publication Date**

20100615

**Applicant**

STMICROELECTRONICS DESIGN AND APPLICATION S.R.O.

Title

"REGOLATORE LINEARE DI TIPO LOW-DROPOUT CON EFFICIENZA MIGLIORATA E PROCEDIMENTO CORRISPONDENTE"

**DESCRIZIONE** dell'invenzione industriale dal titolo:

"Regolatore lineare di tipo low-dropout con efficienza migliorata e procedimento corrispondente"

di: STMicroelectronics Design and Application s.r.o., nazionalità ceca, Pobrezni 620/3 - 186 00 Praha 8 - Repubblica Ceca

Inventore designato: Karel NAPRAVNIK

Depositata il: 15 dicembre 2008

\*\*\*\*

#### TESTO DELLA DESCRIZIONE

## Campo dell'invenzione

La presente descrizione si riferisce ai regolatori lineari di tipo low-dropout (LDO). Gli LDO sono utilizzati in un'ampia gamma di applicazioni nel settore dell'elettronica al fine di applicare ad un carico un segnale regolato in funzione di un segnale di riferimento.

#### Descrizione della tecnica relativa

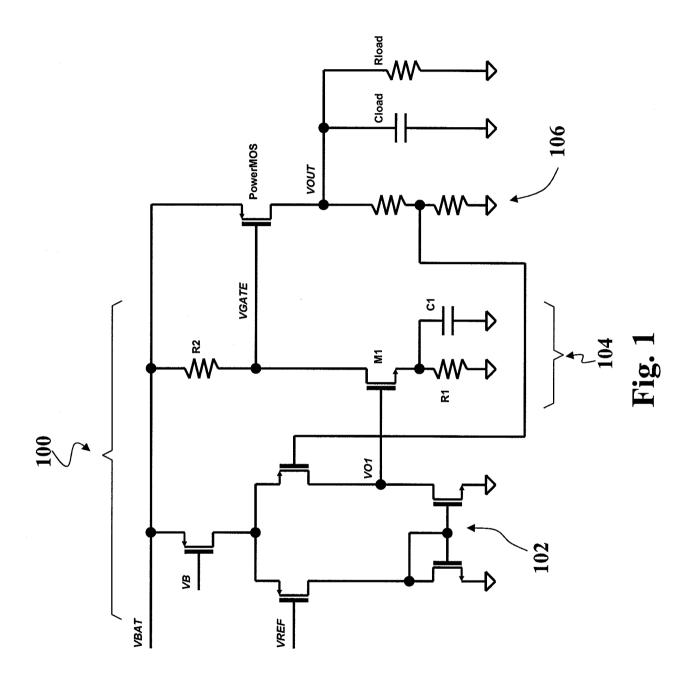

schema della figura 1 è un esempio configurazione circuitale di un regolatore lineare di tipo low-dropout di tipo convenzionale. L'LDO della figura 1 è sostanzialmente costituito da una disposizione a cascata di un amplificatore di errore 100 (a sua volta comprendente un amplificatore differenziale 102 che riceve un segnale di riferimento VREF seguito da uno stadio di guadagno 104) e di uno stadio di uscita 106. Lo stadio di uscita 106 comprendente un MOS di potenza che riceve dallo stadio di quadagno 104 una tensione VGATE sul suo gate ed applica una tensione di uscita VOUT ad un carico comprendente una componente resistiva Rload ed una componente capacitiva Cload.

Nella forma di attuazione illustrata nella figura 1, lo stadio di guadagno 104 che costituisce lo stadio di uscita dell'amplificatore di errore 100 comprende un MOSFET M1. Il drain del MOSFET M1 è collegato alla tensione di alimentazione VBAT tramite un resistore R2 e fornisce il segnale VGATE al MOS di potenza dello stadio di uscita 106. Il source del MOSFET M1 è collegato a massa tramite una rete RC comprendente un collegamento in parallelo di un resistore R1 e di un condensatore C1.

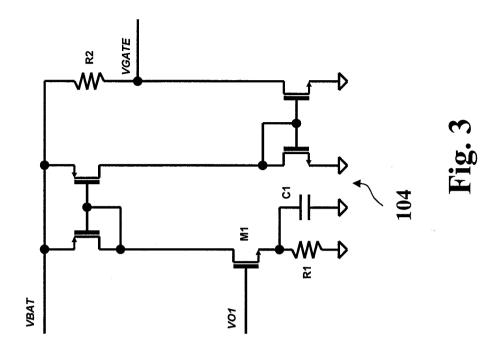

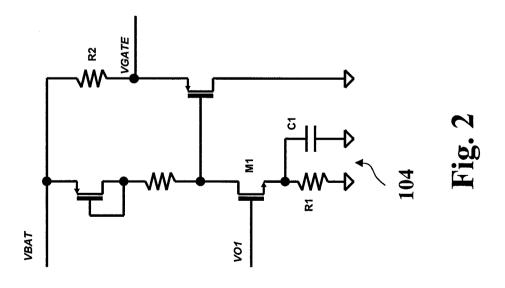

Le figure 2 e 3 illustrano altre forme di attuazione convenzionali dello stesso stadio 104.

Quale che sia la specifica forma di attuazione considerata, questi stadi pilotano un MOS di potenza non-lineare (ossia il transistore M1 di passaggio del LDO) tramite un elemento lineare (cioè il resistore R2).

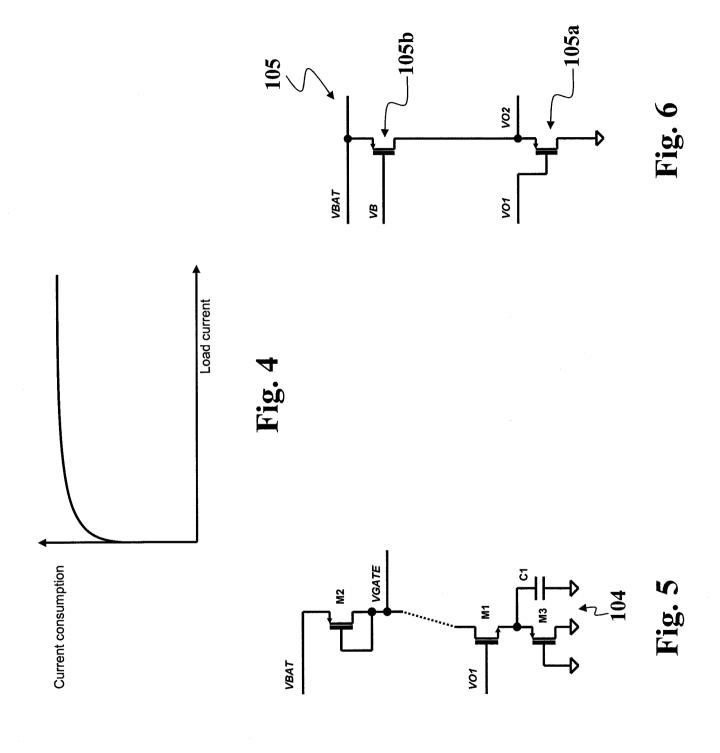

Come risultato, l'assorbimento di corrente non è proporzionale in modo lineare alla corrente di uscita dell'LDO. Un tipico profilo dell'andamento dell'assorbimento di corrente rispetto alla corrente nel carico di un LDO è illustrato nella figura 4.

Questo profilo di assorbimento determina una minore efficienza in presenza di carichi medi. Tuttavia, la stabilità dell'LDO è sostanzialmente non influenzata dalle variazioni della corrente nel carico.

L'inventore ha notato che le varie forme di attuazione dello stadio di guadagno 104 illustrate nelle figure 1 a 3 possono essere modificate per ottenere un profilo di assorbimento di corrente lineare sostituendo il resistore R2 tramite un transistore collegato come un diodo.

Questo diodo costituisce un elemento non-lineare in grado di compensare la non-linearità del MOS di potenza di uscita in quanto si crea uno specchio di corrente lineare.

Adottando questa soluzione, l'assorbimento di corrente è reso esattamente proporzionale in modo lineare alla corrente del carico.

L'inventore ha tuttavia notato che l'impedenza di uscita del transistore/diodo costituente l'elemento di compensazione non-lineare aumenta per correnti più basse (per cui il secondo polo del guadagno ad anello aperto dell'LDO è spostato verso le frequenze più basse) mentre lo zero positivo nel guadagno ad anello aperto dell'LDO creato dalla rete RC associata al source di M1 (cioè R1 e C1) rimane a frequenza costante.

Di conseguenza, il margine di fase alle frequenze medie viene ridotto e la stabilità dell'LDO è influenzata in modo negativo dalle variazioni di corrente nel carico.

### Scopo e sintesi dell'invenzione

Lo scopo dell'invenzione è dunque di fornire una struttura di LDO avente una maggiore efficienza in quanto l'assorbimento di corrente reso linearmente proporzionale alla corrente nel carico evitando tuttavia che la stabilità sia influenzata in senso negativo.

Secondo la presente invenzione, tale scopo è ottenuto tramite una soluzione avente le caratteristiche esposte nelle rivendicazioni che seguono. L'invenzione riguarda anche un corrispondente procedimento.

Le rivendicazioni formano parte integrante dell'insegnamento relativo all'invenzione qui fornito.

In una forma di attuazione, si ottiene un nuovo regolatore di tipo low-dropout (LDO) con elevata efficienza in cui l'efficienza è migliorata applicando una forte dipendenza lineare dell'assorbimento di corrente rispetto alla corrente nel carico.

Una forma di attuazione fornisce una soluzione al problema di stabilità nell'ambito di una struttura che si presta ad un'attuazione efficace.

## Breve descrizione delle viste annesse

L'invenzione sarà ora descritta, a titolo di esempio non limitativo, con riferimento alle viste annesse, in cui:

- le figure 1 a 4 sono già state descritte in precedenza,

- la figura 5 è rappresentativa di una possibile forma di attuazione della soluzione qui descritta,

- la figura 6 fornisce ulteriori dettagli sulla forma di attuazione della figura 5, e

- le figure 7 e 8 sono schemi circuitali particolareggiati di forme di attuazione.

# Descrizione particolareggiata di forme di attuazione

Nella seguente descrizione, sono illustrati vari dettagli specifici finalizzati ad un'approfondita comprensione delle forme di attuazione. Le forme di attuazione possono essere realizzate senza uno o più dei dettagli specifici, o con altri metodi, componenti, materiali, etc. In altri casi, strutture, materiali od operazioni noti non sono mostrati o descritti in dettaglio per evitare di rendere oscuri vari aspetti delle forme di attuazione.

Il riferimento ad "una forma di attuazione" nell'ambito di questa descrizione sta ad indicare che una particolare configurazione, struttura o caratteristica descritta in relazione alla forma di attuazione è compresa in almeno una forma di attuazione. Quindi, frasi come "in una forma di attuazione", eventualmente presenti in diversi luoghi di questa descrizione, non sono necessariamente

riferite alla stessa forma di attuazione. Inoltre, particolari conformazioni, strutture, o caratteristiche, possono essere combinati in ogni modo adeguato in una o più forme di attuazione.

I riferimenti qui utilizzati sono soltanto per comodità e non definiscono dunque l'ambito di tutela o la portata delle forme di attuazione.

La forma di attuazione qui descritta è una modifica proposta rispetto alla generale configurazione di un LDO così come illustrato nella figura 1. Di conseguenza, la descrizione particolareggiata della forma di attuazione qui descritta non ripeterà quegli elementi che sono comuni con la struttura della figura 1.

Si apprezzerà peraltro che, in tutte le viste qui annesse, componenti/elementi identici o equivalenti fra loro sono indicati con gli stessi riferimenti.

Si apprezzerà altresì che la forma di attuazione qui descritta è applicabile a qualunque struttura di LDO comprendente un amplificatore di errore comprendente una disposizione a cascata di un amplificatore differenziale e di uno stadio di uscita di guadagno, in modo indipendente dai dettagli strutturali di questi amplificatori o stadi. Il fatto di riferirsi ai dettagli realizzativi della struttura di LDO della figura 1 ha pertanto soltanto scopi esemplificativi e non limitativi.

La forma di attuazione illustrata nella figura 5 comporta il fatto di sostituire al resistore R2 nello stadio 104 della figura 1 (o al resistore R2 nello stadio 104 di una qualsiasi delle figure 2 e 3) un transistore (ad esempio un MOSFET) M2 collegato come un diodo. Così come indicato nella parte introduttiva di questa descrizione, tale diodo costituisce un elemento non-lineare suscettibile

di compensare la non-linearità del MOS di potenza di uscita in quanto si crea uno specchio di corrente lineare. Adottando questa soluzione, l'assorbimento di corrente è reso esattamente proporzionale in modo lineare alla corrente del carico.

Così come indicato, questo passo di per sé fa sì che il secondo polo nel guadagno ad anello aperto dell'LDO sia spostato verso frequenze più basse, influenzando così in modo negativo la stabilità dell'LDO.

La forma di attuazione della figura 5 compensa lo spostamento di tale secondo polo (e la corrispondente riduzione del margine di fase) sostituendo anche il resistore R1 sul source del MOSFET M1 tramite con un transistore (ad esempio, un MOSFET) M3 collegato come diodo. La frequenza dello zero positivo creato dalla rete RC in corrispondenza del source del MOSFET M1 diminuisce così all'ammontare della corrente nel carico, ottenendo l'effetto di compensazione desiderato. L'assorbimento di corrente è reso proporzionale in modo lineare alla corrente nel carico senza tuttavia influenzare in modo negativo il margine di fase, conservando così la stabilità dell'LDO.

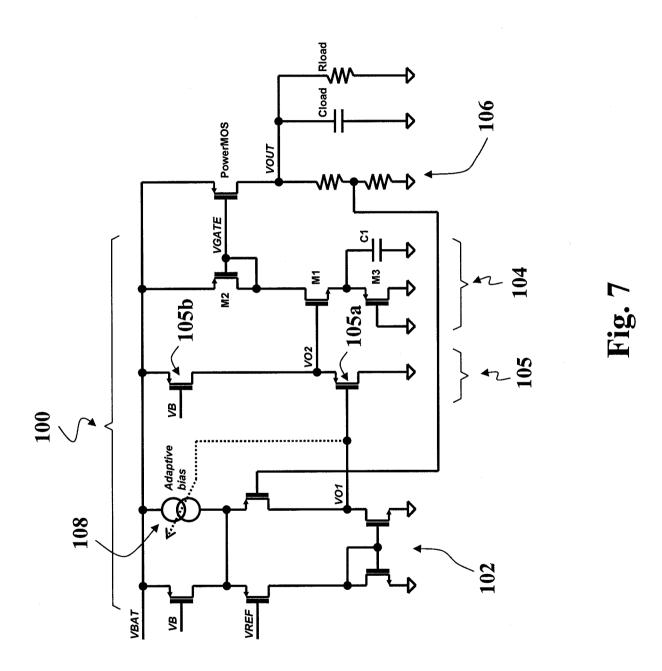

Nella forma di attuazione della figura 5 (se l'amplificatore differenziale 102 non è dimensionato così da fornire una tensione di uscita sufficiente), una tensione di ingresso più elevata per tenere in conto la tensione di soglia del transistore M3 può essere fornita tramite un traslatore di livello (level shifter) 105 disposto fra l'amplificatore differenziale 102 e lo stadio 104.

La figura 6 illustra una possibile forma di attuazione di tale traslatore di livello 105, che comprende una coppia di MOSFET 105a, 105b collegati con le loro linee source-

drain in parallelo fra la tensione di alimentazione VBAT e la massa. Il MOSFET "basso" 105a riceve la tensione VO1 dall'uscita dell'amplificatore differenziale 102 e fornisce una tensione "traslata in su" VO2 allo stadio 104. La corrente di polarizzazione per il traslatore di livello 105 (che può essere regolato tramite un segnale VB sul gate del MOSFET "alto" 105a) non risulta essere critica, un valore di  $0,5\mu A$  essendo accettabile per la maggiore parte delle applicazioni.

Lo schema completo dell'LDO della figura 1 modificato così da incorporare le forme di attuazione descritte è illustrato nella figura 7.

In una forma di attuazione così come esemplificata, l'LDO può utilizzare un bias adattativo 108 nell'amplificatore differenziale 102 così da ridurre la corrente di quiescenza in presenza di correnti di uscita basse e migliorare in modo conseguente l'efficienza per basse correnti di carico.

In talune condizioni di uso, la corrente di uscita può essere troppo bassa, facendo sì che il guadagno ad anello aperto dell'LDO diventi molto alto. In tali circostanze la stabilità può diventare critica.

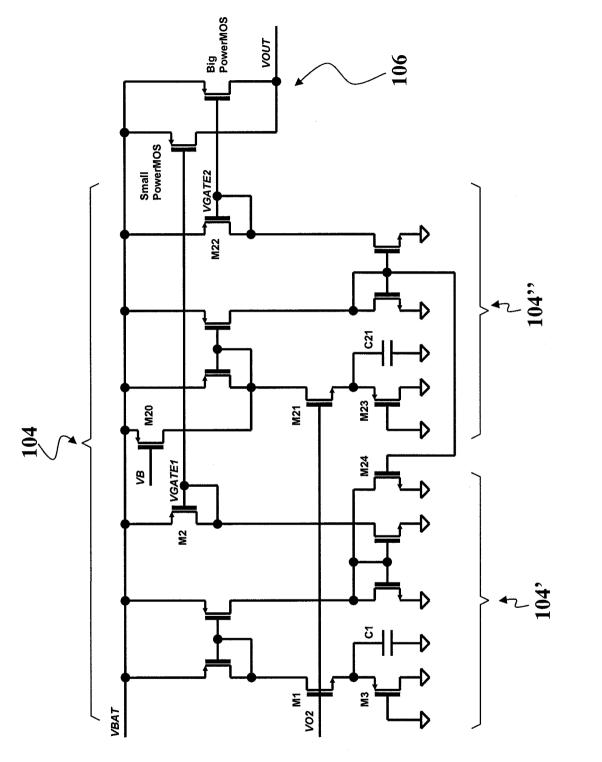

Questa situazione può essere presa in conto facendo sì che lo stadio di uscita 102 sia "suddiviso" in una sezione di bassa potenza (SmallPowerMOS) ed una sezione di alta potenza (BigPowerMOS). Lo stadio 104 è modificato in modo corrispondente così da comprendere due unità di pilotaggio 104' e 104'' come dettagliato nella figura 8. Ancora una volta, componenti/elementi identici o equivalenti a componenti già descritti sono indicati con gli stessi riferimenti.

Per correnti di uscita basse, sono attive l'unità di pilotaggio 104' ed il MOS di bassa potenza. La corrente attraverso il MOSFET M21 (che gioca il ruolo di M1) è meno della corrente proveniente da M20, per cui l'unità di pilotaggio 104'' ed il MOS di alta potenza non sono attivi.

Se la corrente di uscita cresce al di sopra di una certa soglia, allora l'unità di pilotaggio 104" comincia ad operare mentre l'unità di pilotaggio 104" viene disattivata dal MOSFET M24. Questo comportamento fa sì che il MOS di alta potenza non piloti mai una bassa corrente (eccetto nel caso di corrente zero) e non mette mai in pericolo la stabilità.

La figura 8 fa vedere che in ciascuna delle due unità di pilotaggio 104', 104'':

- è presente un transistore M1; M21 pilotato dall'amplificatore differenziale 102 così da produrre un rispettivo segnale di pilotaggio VGATE1, VGATE2 per l'una e per l'altra tra la sezione di bassa potenza SmallPowerMOS e la sezione di alta potenza BigPowerMOS dello stadio di uscita 106 del regolatore,

- il transistore M2; M21 in questione è interposto con la sua linea source-drain fra un primo carico resistivo M3, M23 compreso in una rete RC M3, C1; M23, C21 per creare uno zero nel guadagno ad anello aperto del regolatore, ed un secondo carico resistivo M2; M22 per produrre il rispettivo segnale di pilotaggio VGATE1, VGATE2 per l'una e l'altra fra la sezione di bassa potenza SmallPowerMOS e la sezione di alta potenza BigPowerMOS dello stadio di uscita 106 del regolatore,

- tanto il primo carico resistivo M3; M23 quanto il secondo carico resistivo M2; M22 sono elementi di compensazione non-lineari (ad esempio transistori collegati

come diodi) per assicurare - così come meglio illustrato in dettaglio in precedenza - che l'assorbimento di corrente sia reso proporzionale in modo lineare alla corrente nel carico del regolatore senza influenzare in modo negativo la stabilità del regolatore.

Le forme di attuazione qui descritte dimostrano una migliorata efficienza, in particolare per correnti di carico medie e basse. Questo risultato è ottenuto applicando una forte dipendenza lineare in corrente rispetto alla corrente nel carico.

Anche se la presente descrizione fa riferimento a titolo di esempio a circuiti a transistori ad effetto di campo (Field Effect Transistor o FET, in particolare del tipo MOSFET), le forme di attuazione qui descritte si prestano ad essere attuate anche con tecnologia bipolare.

Le denominazioni "source", "gate" e "drain", qui utilizzate e relative appunto alla tecnologia FET, sono quindi da intendersi come tali da applicarsi a tutti gli effetti (rivendicazioni comprese) anche alle denominazioni "emettitore", "base" e "collettore", che indicano gli elementi omologhi di un transistore bipolare. Ad esempio, il termine "linea source-drain" è qui da intendersi come comprensivo del concetto "linea emettitore-collettore").

Fermo restando il principio dell'invenzione, i particolari e le forme di attuazione potranno variare, anche in modo significativo, rispetto a quanto qui descritto a puro titolo di esempio, senza per questo uscire dall'ambito dell'invenzione, così come definito dalle rivendicazioni annesse.

#### RIVENDICAZIONI

- regolatore lineare di tipo low-dropout Un comprendente un amplificatore di errore (100) comprendente un amplificatore differenziale (102) ed uno stadio di quadaqno (104) disposti in cascata, detto stadio quadagno (104) comprendendo almeno un transistore pilotato (VO1) da detto amplificatore differenziale (102) per produrre almeno un segnale di pilotaggio (VGATE) per uno stadio di uscita (106) del regolatore, in cui detto almeno un transistore (M1) è interposto con la sua linea source-drain fra:

- almeno un primo carico resistivo (M3) compreso in una rete RC (M3, C1) che crea uno zero nel guadagno ad anello aperto del regolatore, e

- almeno un secondo carico resistivo (M2) per produrre detto almeno un segnale di pilotaggio (VGATE) per detto stadio di uscita (106) del regolatore, in cui detto almeno un secondo carico resistivo (M2) è un elemento di compensazione non-lineare per rendere l'assorbimento di corrente proporzionale in modo lineare alla corrente del carico del regolatore,

in cui anche detto almeno un primo carico resistivo (M3) è un elemento non-lineare per far sì che la frequenza di detto zero creato da detta rete RC (M3, C1) diminuisca all'aumentare della corrente del carico del regolatore, per cui l'assorbimento di corrente è reso proporzionale in modo lineare alla corrente nel carico del regolatore senza influenzare negativamente la stabilità del regolatore.

- 2. Regolatore secondo la rivendicazione 1, in cui almeno uno fra detti carichi resistivi non-lineari (M2, M3) è realizzato come un diodo.

- 3. Regolatore secondo la rivendicazione 2, in cui almeno uno di detti carichi resistivi non-lineari (M2, M3) è realizzato come un transistore, quale un MOSFET collegato come un diodo.

- 4. Regolatore secondo una qualsiasi delle precedenti rivendicazioni, comprendente un traslatore di livello (105) interposto fra detto amplificatore differenziale (102) e detto stadio di guadagno (104) per aumentare il livello (VO2) del pilotaggio (VO1) di detto almeno un transistore (M1) da parte di detto amplificatore differenziale (102).

- 5. Regolatore secondo una qualsiasi delle precedenti rivendicazioni, in cui detto amplificatore differenziale (102) comprende un bias adattativo (108) per ridurre la corrente di quiescenza in presenza di basse correnti di uscita del regolatore.

- **6.** Regolatore secondo una qualsiasi delle precedenti rivendicazioni, in cui:

- detto stadio di uscita (106) comprende una sezione di bassa potenza (SmallPowerMOS) ed una sezione di alta potenza (BigPowerMOS),

- detto stadio di guadagno (104) comprende due unità di pilotaggio (104', 104'') attivabili selettivamente per pilotare rispettivamente detta sezione di bassa potenza (SmallPowerMOS) e detta sezione di alta potenza (BigPowerMOS) di detto stadio di uscita (106),

in cui, in ciascuna di dette due unità di pilotaggio (104', 104''):

- è presente un transistore (M1; M21) pilotato da detto amplificatore differenziale (102) per produrre un rispettivo segnale di pilotaggio (VGATE1, VGATE2) per l'una e per l'altra tra la sezione di bassa potenza (SmallPowerMOS) e la sezione di alta potenza (BigPowerMOS) di detto stadio di uscita (106) del regolatore,

- detto transistore (M2; M21) è interposto con la sua linea source-drain fra un primo carico resistivo (M3, M23) compreso in una rete RC (M3, C1; M23, C21) per creare uno zero nel guadagno ad anello aperto del regolatore, ed un secondo carico resistivo (M2; M22) per produrre il rispettivo segnale di pilotaggio (VGATE1, VGATE2) per l'una e l'altra fra la sezione di bassa potenza (SmallPowerMOS) e la sezione di alta potenza (BigPowerMOS) dello stadio di uscita (106) del regolatore,

- tanto detto primo carico resistivo (M3; M23) quanto detto secondo carico resistivo (M2; M22) sono elementi di compensazione non-lineari per cui l'assorbimento di corrente è reso proporzionale in modo lineare alla corrente nel carico del regolatore senza influenzare negativamente la stabilità del regolatore.

- 7. Procedimento di funzionamento di un regolatore lineare di tipo low-dropout comprendente un amplificatore di errore (100) comprendente un amplificatore differenziale (102) ed uno stadio di guadagno (104) disposti in cascata, comprendente il pilotare (VO1) almeno un transistore (M1) in detto stadio di guadagno (104) tramite detto amplificatore differenziale (102) per produrre almeno un segnale di pilotaggio (VGATE) per uno stadio di uscita

- (106) del regolatore, in cui detto almeno un transistore (M1) è interposto con la sua linea source-drain fra:

- almeno un primo carico resistivo (M3) compreso in una rete RC (M3, C1) che crea uno zero nel guadagno ad anello aperto del regolatore, e

- almeno un secondo carico resistivo (M2) per produrre detto almeno un segnale di pilotaggio (VGATE) per detto stadio di uscita (106) del regolatore, in cui detto almeno un secondo (M2) carico resistivo è un elemento di compensazione non-lineare per rendere l'assorbimento di corrente proporzionale in modo lineare alla corrente del carico del regolatore,

- il procedimento comprendendo rendere anche detto almeno un primo carico resistivo (M3) un elemento non-lineare per far sì che la frequenza di detto zero creato da detta rete RC (M3, C1) diminuisca all'aumentare della corrente del carico del regolatore, per cui l'assorbimento di corrente è reso proporzionale in modo lineare alla corrente nel carico del regolatore senza influenzare negativamente la stabilità del regolatore.

#### CLAIMS

- 1. A low-dropout linear regulator including an error amplifier (100) including a cascaded arrangement of a differential amplifier (102) and a gain stage (104), said gain stage (104) including at least one transistor (M1) driven (VO1) by said differential amplifier (102) to produce at least one drive signal (VGATE) for an output stage (106) of the regulator, wherein said at least one transistor (M1) is interposed over its source-drain line between:

- at least one first (M3) resistive load included in a RC network (M3, C1) creating a zero in the open loop gain of the regulator, and

- at least one second resistive load (M2) to produce at least one drive signal (VGATE) for an output stage (106) of the regulator, wherein said at least one second (M2) resistive load is a non-linear compensation element to render current consumption linearly proportional to the load current to the regulator,

wherein also said at least one first resistive load (M3) is a non-linear element causing the frequency of said zero created by said RC network (M3, C1) to decrease as the load current of the regulator decreases, whereby current consumption is made linearly proportional to the load current to the regulator without adversely affecting regulator stability.

2. The regulator of Claim 1, wherein at least one of said non-linear resistive loads (M2, M3) is realized as a diode.

- 3. The regulator of Claim 2, wherein at least one of said non-linear resistive loads (M2, M3) is realized as a transistor, such as a MOSFET, connected as a diode.

- 4. The regulator of any of the previous claims, including a level shifter (105) interposed between said differential amplifer (102) and said gain stage (104) to increase the level (VO2) of the drive (VO1) of said at least one transistor (M1) by said differential amplifier (102).

- 5. The regulator of any of the previous claims, wherein said differential amplifier (102) includes an adaptive bias (108) to decrease the quiescent current at low output currents of the regulator.

- 6. The regulator of any of the previous claims, wherein:

- said output stage (106) includes a small power section (SmallPowerMOS) and a large power section (BigPowerMOS),

- said gain stage (104) includes two drivers (104', 104'') selectively activatable to drive said small power section (SmallPowerMOS) and said large power section (BigPowerMOS), respectively, of said output stage (106),

wherein, in each of said two drivers (104', 104''):

- a transistor (M1; M21) is provided driven (VO2) by said differential amplifier (102) to produce a respective drive signal (VGATE1, VGATE2) for either of said small power section (SmallPowerMOS) and said large power section (BigPowerMOS) of said output stage (106) of the regulator,

- said transistor (M1; M21) is interposed over its source-drain line between a first (M3; M23) resistive load included in a RC network (M3, C1; M23, C21) creating a zero in the open loop gain of the regulator, and a second resistive load (M2; M22) to produce said respective drive signal (VGATE1, VGATE2) for either of said small power section (SmallPowerMOS) and said large power section (BigPowerMOS) of said output stage (106) of the regulator,

- both said first resistive load (M3; M23) and said second (M2; M22) resistive load are a non-linear compensation elements whereby current consumption is made linearly proportional to the load current to the regulator without adversely affecting regulator stability.

- 7. A method of operating a low-dropout linear regulator including an error amplifier (100) including a cascaded arrangement of a differential amplifier (102) and a gain stage (104), including driving (V01) at least one transistor (M1) in said gain stage (104) by means of said differential amplifier (102) to produce at least one drive signal (VGATE) for an output stage (106) of the regulator, wherein said at least one transistor (M1) is interposed over its source-drain line between:

- at least one first (M3) resistive load included in a RC network (M3, C1) creating a zero in the open loop gain of the regulator, and

- at least one second resistive load (M2) to produce at least one drive signal (VGATE) for an output stage (106) of the regulator, wherein said at least one second (M2) resistive load is a non-linear compensation element to render current consumption linearly proportional to the load current to the regulator,

the method including making also said at least one first resistive load (M3) a non-linear element causing and cause the frequency of said zero created by said RC network (M3, C1) to decrease as the load current of the regulator decreases, whereby current consumption is made linearly proportional to the load current to the regulator without adversely affecting regulator stability.

Fig. 8