(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2013-0139882

(43) 공개일자 2013년12월23일

(51) 국제특허분류(Int. Cl.)

*H01G 11/32* (2013.01) *H01G 11/74* (2013.01)

(21) 출원번호 10-2013-7007383

(22) 출원일자(국제) 2011년08월10일

심사청구일자 **없음**

(85) 번역문제출일자 2013년03월22일

(86) 국제출원번호 PCT/US2011/047173

(87) 국제공개번호 WO 2012/027102

국제공개일자 2012년03월01일

(30) 우선권주장

12/860,995 2010년08월23일 미국(US)

(71) 출원인

**코닝 인코포레이티드**

미국 뉴욕 (우편번호 14831) 코닝 원 리버프론트

플라자

(72) 별명자

**가드카레, 키쇼르 피**

미국, 뉴욕 14870, 페인티드 포스트, 웨스턴 레인

120

**쥬스, 웰리페 미구엘**

미국, 뉴욕 14870, 페인티드 포스트, 인디안 파이

프 7

(뒷면에 계속)

(74) 대리인

**청운특허법인**

전체 청구항 수 : 총 23 항

(54) 발명의 명칭 **복층형 울트라캐패시터 전류 컬렉터 제조방법**

### (57) 요 약

다층 전류 컬렉터 제조방법은 제1포뮬레이션으로부터 전류 컬렉터 기판(103)의 각각의 주면에 걸쳐 제1층(104)을 형성하는 단계, 제2포뮬레이션으로부터 각각의 제1층(104)에 걸쳐 제2층(105)을 형성하는 단계를 포함하며, 상기 제1포뮬레이션 및 제2포뮬레이션 중 어느 하나는 흑연 포뮬레이션이고, 상기 제1포뮬레이션 및 제2포뮬레이션 중 또 다른 하나는 카본블랙 포뮬레이션이다.

**대 표 도** - 도1

(72) 발명자

립, 제임스 로버트

미국, 뉴욕 14850, 이타카, 유닛 133-비, 워렌 로

드 700

레디, 캄줄라 피

미국, 뉴욕 14830, 코닝, 테레사 드라이브 11810

## 특허청구의 범위

### 청구항 1

제1포뮬레이션으로부터 전류 컬렉터 기판의 각각의 주면에 걸쳐 제1층을 형성하는 단계; 및 제2포뮬레이션으로부터 각각의 제1층에 걸쳐 제2층을 형성하는 단계를 포함하며, 상기 제1포뮬레이션 및 제2포뮬레이션 중 어느 하나는 흑연 포뮬레이션이고, 상기 제1포뮬레이션 및 제2포뮬레이션 중 또 다른 하나는 카본블랙 포뮬레이션인 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

### 청구항 2

청구항 1에 있어서,

적어도 하나의 제1층은 전류 컬렉터 기판의 주면과 직접 접촉하는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

### 청구항 3

청구항 1에 있어서,

적어도 하나의 제1층은 전류 컬렉터 기판의 주면과 직접 접촉하고 각각의 제2층은 제1층과 직접 접촉하는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

### 청구항 4

청구항 1에 있어서,

각각의 제1층에 걸쳐 제2층을 형성하기 전에 각각의 제1층을 건조하는 단계를 더 포함하는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

### 청구항 5

청구항 1에 있어서,

전류 컬렉터 기판의 또 다른 주면 상에 제1층 및 제2층을 형성하기 전에 전류 컬렉터 기판의 어느 한 주면 상의 제1층 및 제2층을 건조시키는 단계를 더 포함하는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

### 청구항 6

청구항 1에 있어서,

상기 제1층은 흑연층인 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

### 청구항 7

청구항 1에 있어서,

카본블랙층은  $0.005\mu\text{m}$  내지  $0.1\mu\text{m}$  범위의 평균 입자 직경 및  $1\mu\text{m}$  내지  $100\mu\text{m}$  범위의 평균 덩어리 직경을 갖는 적어도 하나의 카본블랙 물질로 이루어진 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

### 청구항 8

청구항 1에 있어서, 상기 형성 단계 동안, 카본블랙 포뮬레이션은 30 cps 이하의 점성을 갖는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

### 청구항 9

청구항 1에 있어서,

흑연층은  $0.1\mu\text{m}$  내지  $100\mu\text{m}$  범위의 평균 입자 직경을 갖는 적어도 하나의 흑연 물질을 포함하는 것을 특징으로

하는 다층 전류 컬렉터를 제조하기 위한 방법.

#### 청구항 10

청구항 1에 있어서,

상기 형성 단계동안 흑연 포뮬레이션은 300 cps 이하의 점성을 갖는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

#### 청구항 11

청구항 1에 있어서,

제1포뮬레이션 및 제2포뮬레이션 중 적어도 어느 하나는 적어도 하나의 전도성 강화제를 더 포함하는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

#### 청구항 12

청구항 1에 있어서,

적어도 하나의 추가 층을 형성하는 단계를 더 포함하는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

#### 청구항 13

청구항 1에 있어서,

적어도 하나의 추가 층을 형성하는 단계를 더 포함하며, 상기 적어도 하나의 추가 층은 적어도 하나의 전도성 강화제를 포함하는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

#### 청구항 14

청구항 1에 있어서,

전류 컬렉터 기판의 적어도 한 주면과 직접 접촉하는 적어도 하나의 추가 층을 형성하는 단계를 더 포함하는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

#### 청구항 15

청구항 1에 있어서,

전류 컬렉터 기판의 적어도 한 주면과 직접 접촉하는 적어도 하나의 추가 층을 형성하는 단계를 더 포함하며, 상기 적어도 하나의 추가 층은 물을 포함하는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

#### 청구항 16

청구항 1에 있어서,

상기 제1층 및 제2층은 거의 동시에 형성되는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

#### 청구항 17

청구항 1에 있어서,

상기 제1층 및 제2층은 슬롯-다이를 이용하여 거의 동시에 형성되는 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

#### 청구항 18

청구항 1에 있어서, 제1 및 제2층에서의 총 고체에 대한 흑연의 비율은 약 2 내지 50 vol.%인 것을 특징으로 하는 다층 전류 컬렉터를 제조하기 위한 방법.

#### 청구항 19

제1포뮬레이션으로부터 전류 컬렉터 기판의 각각의 주면에 걸쳐 제1층을 형성하는 단계;

제2포뮬레이션으로부터 각각의 제1층에 걸쳐 제2층을 형성하는 단계; 및

각각의 제2층에 걸쳐 적어도 하나의 활성 카본층을 형성하는 단계를 포함하며,

상기 제1포뮬레이션 및 제2포뮬레이션 중 어느 하나는 흑연 포뮬레이션이고, 상기 제1포뮬레이션 및 제2포뮬레이션 중 또 다른 하나는 카본블랙 포뮬레이션인 것을 특징으로 하는 울트라캐페시터 전극을 제조하기 위한 방법.

### 청구항 20

청구항 19에 있어서,

상기 제1층은 흑연층인 것을 특징으로 하는 울트라캐페시터 전극을 제조하기 위한 방법.

### 청구항 21

청구항 19에 있어서,

상기 제1층 및 제2층은 슬롯-다이를 이용하여 거의 동시에 형성되는 것을 특징으로 하는 울트라캐페시터 전극을 제조하기 위한 방법.

### 청구항 22

청구항 19에 있어서,

전류 컬렉터 기판의 또 다른 주면 상에 제1층 및 제2층을 형성하기 전에 전류 컬렉터 기판의 어느 한 주면 상의 제1층 및 제2층을 전조시키는 단계를 더 포함하는 것을 특징으로 하는 울트라캐페시터 전극을 제조하기 위한 방법.

### 청구항 23

전류 컬렉터 기판, 및

상기 전류 컬렉터 기판의 각각의 주면에 걸쳐 형성된 복합층을 포함하며,

상기 복합층은 흑연 및 카본블랙을 포함하고, 상기 복합층에서의 총 고체에 대한 흑연의 비율은 약 2 내지 50 vol%인 것을 특징으로 하는 다층 전류 컬렉터.

## 명세서

### 기술 분야

[0001] 본 출원은 35 U.S.C. § 120 하에 2010년 8월 23일 출원된 미국출원 제12/860,995호의 우선권의 이점을 청구하며, 그와 관련된 내용들은 전체적으로 참조에 의해 여기에 반영된다.

[0002] 본 발명은 전류 컬렉터 제조방법, 특히 울트라캐페시터 전극 제조방법에 관한 것이다. 특히, 본 발명은 제1포뮬레이션(first formulation)으로부터 전류 컬렉터 기판의 각각의 주면에 걸쳐 제1층을 형성하는 단계, 및 제2포뮬레이션으로부터 각각의 제1층에 걸쳐 제2층을 형성하는 단계를 포함하는 다층의 복합 전류 컬렉터 제조방법에 관한 것이다. 여러 실시예에 있어서, 제1포뮬레이션 및 제2포뮬레이션 중 어느 하나는 흑연 포뮬레이션이고, 상기 제1포뮬레이션 및 제2포뮬레이션 중 또 다른 하나는 카본블랙 포뮬레이션이다. 더욱이, 본 발명은 여기에 기술된 다층 전류 컬렉터 형성 방법을 포함하는 울트라캐페시터 전극 제조방법에 관한 것이다.

### 배경기술

[0003] 다층의 복합 전류 컬렉터는 예전대 배터리와 비견될 정도로 단위 체적당 그리고 단위 중량당 높은 신뢰성을 갖는 전하-저장 및 전하-전달 처리를 갖는 전기화학 소자인 전기화학 이중층 캐페시터(EDLC)라고도 부르는 울트라캐페시터를 위한 전극에 이용된다. 또한, 울트라캐페시터는 유해한 또는 독성의 재료를 포함하지 않아 사용하기에 용이하기 때문에 바람직하며, 또 큰 온도 범위에 채용될 수 있고, 500,000 사이클 이상의 검증된 사이클

수명을 갖는다. 울트라캐패시터는 휴대용 전자기기 및 전기자동차의 정전시 고장에 대한 안전 상태 유지와 같은 광범위한 응용에 이용된다.

[0004] 울트라캐패시터에 있어서, 전자는 외부 회로를 통해 각각의 2개의 전극에 그리고 그 전극으로부터 전기를 유도하고, 반면 그 전극들간 이온이 흐른다. 울트라캐패시터 소자의 많은 내인성 및 외인성 요소들은 활성물질과 전류 컬렉터간 인터페이스에 전극 저항을 포함하는 전체적으로 균등한 직렬 저항에 기여한다. 그러한 전극 계면 저항의 감소는 균등한 직렬 저항을 감소시키고 울트라캐패시터 소자에 대한 전력 밀도를 증가시킨다. 그러나, 그러한 전류 컬렉터 인터페이스에 중간 코팅을 포함하는 요소들간 불화합성은 다층 전류 컬렉터 및 울트라캐패시터 전극을 제조하는데 어려움을 초래한다.

## 발명의 내용

### 해결하려는 과제

[0005] 따라서, 원하는 미세구조, 두께 및 구성을 갖는 다층 전류 컬렉터를 제조하기 위한 방법의 필요성을 갖게 한다. 또한, 전극 계면 저항을 감소시켜 울트라캐패시터의 성능을 향상시키는 다층 전류 컬렉터 및 울트라캐패시터 전극을 제조하기 위한 방법의 필요성을 갖게 한다. 또한, 비용의 효율적인 방식, 예컨대 재료 비용 및/또는 제조 시간을 감소시키는 방식으로 다층 전류 컬렉터 및 울트라캐패시터 전극을 제조하기 위한 방법의 필요성을 갖게 한다.

### 과제의 해결 수단

[0006] 여기에 기술된 상세한 설명 및 여러 예시의 실시예들에 따르면, 본 발명은 다층 복합 전류 컬렉터 제조방법 및 울트라캐패시터 전극 제조방법에 관한 것이다.

[0007] 여러 예시의 실시예들에 있어서, 본 발명은 제1포뮬레이션으로부터 전류 컬렉터 기판의 각각의 주면에 걸쳐 제1층을 형성하는 단계, 및 제2포뮬레이션으로부터 각각의 제1층에 걸쳐 제2층을 형성하는 단계를 포함하는 다층의 복합 전류 컬렉터 제조방법에 관한 것이다. 다른 실시예들에 있어서, 제1포뮬레이션 및 제2포뮬레이션 중 어느 하나는 흑연 포뮬레이션이고, 상기 제1포뮬레이션 및 제2포뮬레이션 중 또 다른 하나는 카본블랙 포뮬레이션이다.

[0008] 또한, 본 발명은 전류 컬렉터 기판 및 이 전류 컬렉터 기판의 각각의 주면에 걸쳐 형성된 복합층을 포함하는 다층 전류 컬렉터에 관한 것이다. 상기 복합층은 흑연 및 카본블랙 모두를 포함하며, 상기 복합층에서의 총 고체에 대한 흑연의 비율은 약 2 내지 50 vol.%이다.

[0009] 본 발명의 또 다른 실시예들은 여기에 기술된 다층 전류 컬렉터 제조방법을 포함하는 울트라캐패시터 전극 제조 방법에 관한 것이다.

### 도면의 간단한 설명

[0010] 수반되는 도면들이 본 발명을 더 잘 이해할 수 있게 하기 위해 제공되며, 본 명세서에 통합되어 본 명세서의 일부를 구성한다. 도면들은 청구된 바와 같은 발명으로 한정하지 않으며, 오히려 발명의 원리의 설명을 돋기 위한 설명과 함께 발명의 예시의 실시예들을 설명하기 위해 제공된다.

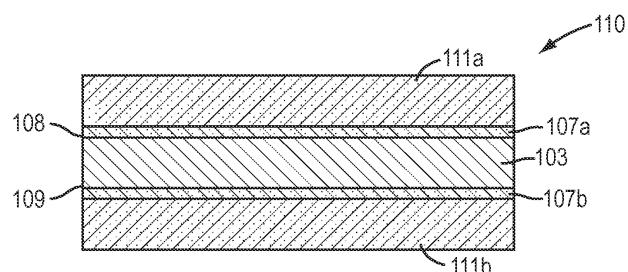

도 1은 본 발명의 적어도 하나의 실시예에 따른 이중 슬롯 다이(double slot die)를 이용하여 전류 컬렉터 기판 상에 제1 및 제2층을 형성을 나타내는 개략도이다.

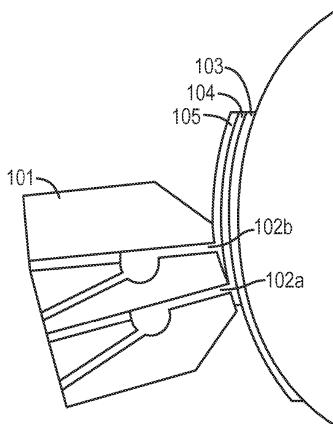

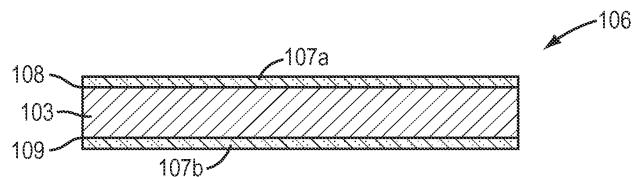

도 2는 본 발명의 적어도 하나의 실시예에 따라 이루어진 다층 전류 컬렉터의 횡단면도이다.

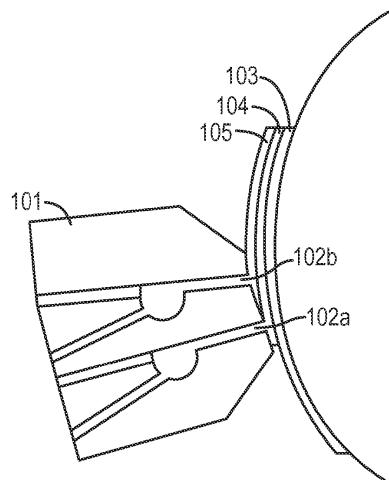

도 3은 본 발명의 적어도 하나의 실시예에 따라 이루어진 울트라캐패시터의 일부의 횡단면도이다.

### 발명을 실시하기 위한 구체적인 내용

[0011] 상기한 일반적인 설명 및 이하의 상세한 설명은 단지 예시일 뿐 청구항 발명으로 제한하려는 것이 아니라는 것

을 이해해야 한다. 다른 실시예들은 여기에 기술된 실시예들의 구성 및 실시 고려사항으로부터 당업자들에 자명할 것이다. 그러한 구성 및 예들은 청구항들에 의해 나타낸 발명의 실제 범위 및 목적을 갖는 단지 예로서 고려하기 위한 것이다.

- [0012] 여기에 사용된 "그(the)", "하나(a)", 또는 "한(an)"은 "적어도 하나"를 의미하며, 명확하게 반대로 나타내지 않는 한 "오직 하나"로 한정하지 않는다. 따라서, 예컨대, "그 카본블랙 물질" 또는 "하나의 카본블랙 물질"의 사용은 적어도 하나의 카본블랙 물질을 의미하려는 것이다.

- [0013] 본 발명은, 여러 실시예에 있어서, 제1포뮬레이션으로부터 전류 컬렉터 기판의 각각의 주면에 걸쳐 제1층을 형성하는 단계, 및 제2포뮬레이션으로부터 각각의 제1층에 걸쳐 제2층을 형성하는 단계를 포함하는 다층 전류 컬렉터 제조방법에 관한 것이다.

- [0014] 여기서 사용한 바와 같이, 용어 "전류 컬렉터 기판" 및 그 변형들은 2개의 주요 대향하는 표면들 또는 측면들 (예컨대, 제1 및 제2표면)을 갖춘 기판을 의미하려는 것이다. 상기 기판은, 여러 실시예에 있어서, 예컨대 알루미늄, 티타늄, 니켈, 동, 주석, 텅스텐, 몰리브덴, 강철, 스테인레스 강철, 합금과 같은 금속, 및 도금(금 또는 백금)에 의한 금속들의 조합과 같은 금속의 조합물을 포함한다. 적어도 하나의 실시예에 있어서, 전류 컬렉터 기판은 알루미늄 시트로 이루어질 것이다.

- [0015] 또한 상기 기판은, 여러 실시예들에 있어서, 한정하진 않지만 유리, 폴리머, 또는 ITO와 같은 코팅 또는 전도성 표면을 갖는 다른 유기 요소 또는 화합물과 같은 절연재, 주석-도핑 인듐 산화물 전도성 폴리머, 및 그래핀 시트 또는 시트들이나 그 조합물을 포함한다.

- [0016] 여러 실시예에 있어서, 전류 컬렉터 기판의 두께는 5 내지 100  $\mu$ , 예컨대 15 내지 40  $\mu$ , 또는 25  $\mu$ 와 같은 20 내지 30  $\mu$ 의 범위가 될 것이다.

- [0017] 여기에 사용된 바와 같이, 용어 "층"은 표면에 걸친 포뮬레이션 또는 재료의 두께를 의미하려는 것이다.

- [0018] 여기에 기술된 바와 같이, 상기 제1층은 전류 컬렉터 기판과 제2층 사이에 배치된다. 여러 실시예에 있어서, 제1층 및 제2층 중 어느 하나는 흑연층이고, 상기 제1층 및 제2층 중 또 다른 하나는 카본블랙층이다.

- [0019] 여기에 사용된 바와 같이, 상기 용어 "포뮬레이션"은 전류 컬렉터 기판 상에 또는 그 기판에 걸쳐 층을 형성할 수 있는 점성이 있는 조성물을 의미하려는 것이다. 여기에 개시된 제1포뮬레이션은 제1층을 형성하고, 여기에 개시된 제2포뮬레이션은 제2층을 형성한다. 여러 실시예에 있어서, 제1포뮬레이션 및 제2포뮬레이션 중 어느 하나는 흑연 포뮬레이션이고, 상기 제1포뮬레이션 및 제2포뮬레이션 중 또 다른 하나는 카본블랙 포뮬레이션이다.

- [0020] 여기에 사용된 바와 같이, 용어 "흑연층"은 적어도 하나의 흑연 물질을 포함하는 층을 의미하려는 것이다. 상기 흑연층에 유용한 흑연 물질은 천연 및 합성 흑연을 포함한다. 예시의 흑연 물질로 한정하지 않고, 또 분말 형태로도 한정하진 않지만, 예로서 뉴저지, 애즈버리의 애즈버리 카본사에 의해 판매되는 그레이드 4827, TC307, UF440, 및 3442와; 사우스 캐롤라이나, 럭지빌의 쇼와 덴코 카본사에 의해 판매되는 UFG5를 포함한다. 또한, 흑연 물질은 뉴저지, 애즈버리의 애즈버리 카본사에 의한 상표명 GRAPHOKOTE<sup>®</sup> 572 및 AQUAKAST<sup>®</sup>와; 독일, 카우저스라우테른의 Fuchs Lubritech GMBH에 의한 상표명 LUBRODAL<sup>®</sup> EC 1204B 및 HYDROGRAF<sup>®</sup> A M2로 판매되는 잉크 또는 분산재로 제공될 수 있다.

- [0021] 여러 실시예에 있어서, 여기에 기술된 흑연 물질은 0.1  $\mu$  내지 10  $\mu$ 와 같은 0.1  $\mu$  내지 100  $\mu$  범위의 평균 입자 직경을 가질 것이다.

- [0022] 여러 실시예에 있어서, 상기 흑연 물질은 한정하진 않지만, 탈이온수에서의 흑연 물질의 분산재 또는 부유액과 같은 흑연 물질을 포함하는 흑연 포뮬레이션으로부터 형성된다. 예컨대, 상기 흑연 포뮬레이션은 탈이온수로 희석된 흑연 잉크를 포함하는 분산재의 형태가 될 것이다. 또 다른 예시의 실시예에 있어서, 상기 흑연 포뮬레이션은 부유액의 형태가 되며, 여기서 흑연은 용액에 혼합되고, 그 흑연은 부유액이 사용되는 기간 동안 정착된다. 당업자의 능력 내에서 예컨대 흑연층에서의 고체의 원하는 퍼센테이지 및 선택된 흑연 물질에 기초하여 적절한 희석 및/또는 정착 시간과 같은 파라미터를 결정한다.

- [0023] 여러 실시예에 있어서, 상기 흑연 포뮬레이션은 1 내지 20 wt.%의 흑연 물질 또는 고체, 예컨대 13 wt.%와 같은 5 내지 15 wt.%의 흑연 물질 또는 고체를 포함한다.

- [0024] 여러 실시예에 있어서, 흑연층의 형성 동안, 흑연 포뮬레이션은 300 cps 이하의 점성, 예컨대 150 cps 이하, 80

cps 이하, 60 cps 이하, 또는 40 cps 이하의 점성을 가질 수 있다.

[0025] 여러 실시예에 있어서, 상기 흑연 포뮬레이션은 적어도 하나의 바인더(binder)를 더 포함한다. 여기에 사용된 바와 같이, 바인더는 한정하진 않지만 폴리테트라플루오로에틸렌(PTFE; polytetrafluoroethylene), 폴리비닐리덴 플루오르(PVDF; polyvinylidene fluoride), 폴리비닐피롤리돈(PVP; polyvinylpyrrolidone), 폴리비닐 아세테이트(PVA; polyvinyl acetate), 폴리에틸렌 옥사이드(PEO; polyethylene oxide), 폴리프로필렌, 폴리에틸렌, 폴리우레тан, 폴리아크릴레이트, 및 다른 유기(여전히 화학적으로 그리고 전기화학적으로 불활성) 바인더를 포함한다. 적어도 하나의 실시예에 있어서, 상기 바인더는 PVP 및 폴리아크릴레이트의 조합물이 될 것이다.

[0026] 여러 실시예에 있어서, 상기 바인더는 0 내지 50 wt.%의 흑연 포뮬레이션, 예컨대 0.1 내지 49 wt.%, 및 5 wt.%와 같은 1 내지 40 wt.%의 흑연 포뮬레이션을 포함할 것이다.

[0027] 여러 실시예에 있어서, 상기 흑연 포뮬레이션은 예컨대 금속 나노튜브, 로드, 및 와이어; 카본 나노튜브, 로드, 및 와이어; 그래핀 입자; 전도성 나노입자; 및 전도성 폴리머와 같은 적어도 하나의 추가 전도성 강화제를 더 포함한다.

[0028] 여러 실시예에 있어서, 상기 추가의 전도성 강화제는 0.01 내지 50 wt.%의 흑연 포뮬레이션, 예컨대 0.1 내지 49 wt.%, 및 10 wt.%와 같은 5 내지 20 wt.%의 흑연 포뮬레이션을 포함할 것이다.

[0029] 일단 기판 상에 형성되면, 그 흑연층의 두께는 여러 실시예에서 0.1  $\mu$  내지 2  $\mu$  또는 0.1  $\mu$  내지 5  $\mu$ 과 같은 0.01  $\mu$  내지 10  $\mu$ 의 범위가 될 것이다. 여러 실시예에 있어서, 흑연층은 기판 상에서의 두께가 균등하고, 다른 것들은 두께가 균등하지 않을 것이다.

[0030] 여기에 사용된 바와 같이, 상기 용어 "카본블랙층"은 적어도 하나의 카본블랙 물질을 포함하는 층을 의미하려는 것이다. 그러한 카본블랙층에 유용한 카본블랙 물질은 한정하진 않지만, 예컨대 매사추세츠, 보스톤의 카봇 코포레이션에 의한 상표명 BLACK PEARLS<sup>®</sup>, VULCAN<sup>®</sup> XC 72, 및 독일, 에센의 에보닉에 의한 상표명 PRINTEX<sup>®</sup>로 판매되는 분말 형태와, 스위스, 볼디오의 텁칼사에 의한 상표명 ENSACO<sup>®</sup> 250G, 250P, 260G, 및 350G로 판매되는 과립 형태의 것을 포함한다. 카본블랙 물질은 또한 예컨대 캔터키, 씬시아나의 솔루션 디스펄션스에 의한 상표명 AJACK<sup>®</sup> BLACK 99 및 7983으로 판매되는 분산제 또는 잉크로 제공될 수 있다.

[0031] 여러 실시예에 있어서, 여기에 기술된 카본블랙층에 유용한 카본블랙 물질은 0.01  $\mu\text{m}$  내지 0.05  $\mu\text{m}$ 과 같은 0.005  $\mu\text{m}$  내지 0.1  $\mu\text{m}$  범위의 평균 입자 직경을 가지며, 5  $\mu\text{m}$  내지 30  $\mu\text{m}$ 과 같은 1  $\mu\text{m}$  내지 100  $\mu\text{m}$  범위의 평균 둑어리 직경을 갖는다.

[0032] 여러 실시예에 있어서, 상기 카본블랙층은 한정하진 않지만 탈이온수에서의 카본블랙 물질의 부유액 또는 분산제와 같은 카본블랙 물질을 포함하는 카본블랙 포뮬레이션으로부터 형성된다. 예컨대, 상기 카본블랙 포뮬레이션은 탈이온수로 희석된 카본블랙 잉크를 포함하며, 상기 카본블랙은 부유액이 사용되는 기간 동안 정착된다. 또 다른 예시의 실시예에 있어서, 상기 카본블랙 포뮬레이션은 탈이온수로 희석된 카본블랙 잉크를 포함하는 분산제의 형태가 된다. 당업자의 능력 내에서 예컨대 카본블랙층에서의 고체의 원하는 퍼센테이지 및 선택된 카본블랙 물질에 기초하여 적절한 희석 및/또는 정착 시간과 같은 파라미터를 결정한다.

[0033] 여러 실시예에 있어서, 상기 카본블랙 포뮬레이션은 1 내지 20 wt.%의 카본블랙 물질 또는 고체, 예컨대 12 wt.%와 같은 5 내지 15 wt.%의 카본블랙 물질 또는 고체를 포함한다.

[0034] 여러 실시예에 있어서, 카본블랙층의 형성 동안, 카본블랙 포뮬레이션은 30 cps 이하의 점성, 예컨대 20 cps 이하, 10 cps 이하, 6 cps 이하의 점성을 가질 수 있다.

[0035] 여러 실시예에 있어서, 카본블랙 포뮬레이션은 여기에 기술된 적어도 하나의 바인더를 포함한다. 적어도 하나의 실시예에 있어서, 상기 바인더는 PVP 및 폴리아크릴레이트의 조합물이 될 것이다. 여러 실시예에 있어서, 상기 바인더는 0.01 내지 50 wt.%의 카본블랙 포뮬레이션, 예컨대 0.1 내지 49 wt.%, 1 내지 40 wt.%, 또는 15 wt.%와 같은 5 내지 25 wt.%의 흑연 포뮬레이션을 포함할 것이다.

[0036] 여러 실시예에 있어서, 상기 카본블랙 포뮬레이션은 예컨대 금속 나노튜브, 로드, 및 와이어; 카본 나노튜브, 로드, 및 와이어; 그래핀 입자; 전도성 나노입자; 및 전도성 폴리머와 같은 적어도 하나의 추가 전도성 강화제를 더 포함한다.

[0037] 여러 실시예에 있어서, 상기 추가의 전도성 강화제는 0.01 내지 50 wt.%의 카본블랙 포뮬레이션, 예컨대 0.1 내

지 49 wt.%, 또는 10 wt.%와 같은 5 내지 20 wt.%의 흑연 포뮬레이션을 포함할 것이다.

[0038] 일단 기판 상에 형성되면, 그 카본블랙층의 두께는 0.01 내지 10  $\mu$ , 예컨대 1 내지 2  $\mu$  또는 1 내지 5  $\mu$ 의 범위가 될 것이다. 여러 실시예에 있어서, 카본블랙층은 기판 상에서의 두께가 균등하고, 다른 것들은 두께가 균등하지 않을 것이다.

[0039] 적어도 하나의 실시예에 있어서, 제1층은 흑연층이고, 제2층은 카본블랙층이다.

[0040] 여기에 기술된 방법에 따르면, 상기 제1층 및 제2층은 한정하진 않지만, 슬롯 다이 코팅, 슬라이드 비드, 및 커튼 코팅과 같은 기술들을 이용하여 형성된다. 여러 실시예에 있어서, 상기 제1 및 제2층은 동일한 또는 다른 기술들을 이용하여 형성될 수 있다. 적어도 하나의 실시예에 있어서, 상기 제1 및 제2층은 각각 슬롯 다이 코팅 기술을 이용하여 형성될 수 있다.

[0041] 여러 실시예에 있어서, 상기 제1 및 제2층은 동시에 또는 분리적으로 형성, 예컨대 제1층이 형성된 후 제2층이 형성되거나, 또는 거의 동시에 형성될 수 있다.

[0042] 적어도 하나의 실시예에 있어서, 제1 및 제2층은 슬롯 다이, 예컨대 이중 슬롯 다이를 이용하여 거의 동시에 형성될 수 있다. 그와 같은 실시예에 있어서, 각각의 층에 대응하는 포뮬레이션은 슬롯에서 합쳐진 후 전류 컬렉터 기판 상에 함께 제공된다. 선택적으로, 2개의 포뮬레이션은 전류 컬렉터 기판에 적용될 때 공통 비드로 분리적으로 슬롯 다이로부터 빠져나올 수 있다. 다른 실시예에 있어서는 제1 및 제2층의 형성 동안 그 포뮬레이션들의 혼합이 있을 수 있다.

[0043] 원하는 특성의 층(들)을 달성하기 위해, 통상의 기술자의 능력 범위 내에서 예컨대 적절한 코팅 속도, 층 포뮬레이션(들)의 유동률, 심 두께(shim thickness), 건조 조건들, 및 코팅 다이 립(1ip)과 코팅 표면의 갭 거리와 같은 상기 기판에 제1 및 제2층을 형성하기 위한 파라미터들을 선택할 수 있다.

[0044] 상기 제1 및 제2층에서의 총 고체에 대한 흑연의 비율(vol.%)은 2 내지 50 vol.%의 범위가 될 수 있다. 그 총 고체는 흑연 및 카본블랙 뿐만 아니라 소정 임의의 첨가물을 포함할 수 있다. 한 실시예에 있어서, 총 고체에 대한 흑연의 비율은 10 내지 30 vol.%의 범위가 될 수 있다.

[0045] 전류 컬렉터 기판에 걸쳐 복합층을 형성하기 위한 다층 형성 기술이 여기에 기술되어 있으며, 상기 복합층은 흑연 및 카본블랙 모두를 포함한다.

[0046] 출원인은 상기 복합층의 전체적인 구성이 기존의 형성 기술들을 이용하여 달성하기 어렵다는 것을 알고 있다. 특히, 흑연 및 카본블랙 모두를 포함하는 단일의 포뮬레이션을 이용하여 2-50 vol.%, 예컨대 10-30 vol.% 흑연을 포함하는 복합층 구성을 형성하는 것은 분산재의 안정성, 처리 및 제조가능성을 포함한 다수의 특성들에 대한 제약에 직면하고 있다. 각각의 포뮬레이션에 흑연과 카본블랙 성분들을 통합함으로써, 단일 포뮬레이션에서의 2개의 성분들의 호환성에 대한 도전에 직면하고 있다.

[0047] 도 1은 본 발명의 적어도 하나의 실시예에 따른 이중 슬롯 다이를 이용한 전류 컬렉터 기판 상에 제1 및 제2층을 형성하는 것을 나타낸 개략도이다. 코팅 다이(101)는 2개의 슬롯(102a, 102b)을 갖춘다. 제1포뮬레이션은 제1슬롯(102a)에서 다이를 빠져나가며 전류 컬렉터 기판(103) 상에 제1층(104)을 형성한다. 한편, 제2포뮬레이션은 제2슬롯(102b)에서 다이를 거의 동시에 빠져나가며 제1층(104) 상에 제2층(105)을 형성한다.

[0048] 여러 예시의 실시예들에 있어서, 제1층은 전류 컬렉터 기판과 직접 접촉하여 형성될 것이다. 다른 예시의 실시예들에 있어서, 제2층은 상기 제1층과 직접 접촉하여 형성될 것이다. 단지 예시의 형태로, 일 실시예에서 상기 제1층은 전류 컬렉터 기판과 직접 접촉하는 흑연층이 되고, 상기 제2층은 상기 흑연층과 직접 접촉하는 카본블랙층이 될 것이다.

[0049] 여러 실시예에 있어서, 상기 방법은 기판 상에 적어도 하나의 추가 층을 형성하는 단계를 포함한다. 상기 추가 층은 상기 제1층과 제2층간, 또는 제2층에 걸쳐 상기 제1층 전에 형성될 것이다. 단지 예시의 형태로, 일 실시예에서 상기 추가 층은 전류 컬렉터 기판과 직접 접촉하여 형성될 것이다.

[0050] 상기 추가 층은 전도성 강화제와 같은 추가 물질을 포함하거나, 또는 거의 모든 탈이온수를 포함할 것이다. 전도성 강화제는 금속 나노튜브, 로드, 및 와이어; 카본 나노튜브, 로드, 및 와이어; 그래핀 입자; 전도성 나노입자; 및 전도성 폴리머를 포함할 것이다. 적어도 하나의 실시예에 있어서, 상기 추가 층은 탈이온수이고 전류 컬렉터 기판과 직접 접촉하여 형성될 것이다.

[0051] 여러 실시예에 있어서, 상기 추가 층은 0.01 내지 50 wt.%의 전도성 강화제, 예컨대 0.1 내지 49 wt.%, 또는 13

wt.%와 같은 5 내지 20 wt.%의 전도성 강화제로부터 형성될 것이다.

[0052] 여러 실시예에 있어서, 추가 층이 여기에 기술한 방법들을 이용하여 형성되고, 제1층 및 제2층 중 어느 하나 또는 그 모두로서 거의 동시에 형성되거나, 또는 상기 제1층 및 제2층 중 어느 하나 또는 그 모두가 순차 형성될 수 있다. 단지 예시의 형태로, 일 실시예에 있어서 상기 추가 층은 제1층 및 제2층, 예컨대 트리플 슬롯 다이와 같은 슬롯 다이로 거의 동시에 형성될 것이다.

[0053] 여러 실시예에 있어서, 상기 방법은 전류 컬렉터 기판의 어느 한 주면 또는 그 모든 주면 상의 상기 제1층 및/ 또는 제2층을 건조시키는 단계를 포함한다. 단지 예시의 방식으로, 일 실시예에 있어서 제1층들은 전류 컬렉터 기판의 각 주면 상에 형성되고 이후 상기 제1층들은 걸쳐 각각의 제2층들을 형성하기 전에 건조될 수 있다. 여러 다른 실시예들에 있어서, 이후 각각의 제2층이 건조될 것이다. 또 다른 실시예에 있어서, 제1층 및 제2층은 전류 컬렉터 기판의 제1표면 상에 형성되고 이후 그 기판의 제2표면 상에 제1층 및 제2층을 형성하기 전에 건조될 수 있다.

[0054] 여기에 사용된 바와 같이, 상기 건조는 슬벤트 또는 액체 매질의 제거에 의해 습식 코팅을 고형화시키는 공정이다. 상기 건조는 한정하진 않지만 인-라인식 오븐(in-line oven), 적외선(IR), 또는 마이크로파와 같은 방법을 이용하여 행해진다. 상기 제1층, 제2층, 또는 그 조합물은 동일하거나 다른 방법들을 이용하여 건조될 것이다.

[0055] 단지 예시의 방식으로, 일 실시예에 있어서, 상기 제1 및 제2층들은 인-라인식 오븐을 이용하여 건조될 것이다. 적절한 건조 방법(들) 및 파라메터들을 선택하는 것은 통상의 기술자의 능력 범위 내에 있다.

[0056] 도 2는 본 발명의 적어도 하나의 실시예에 따라 이루어진 다층 전류 컬렉터의 횡단면도이다. 그러한 다층 전류 컬렉터(106)는 기판(103)의 제1표면(108) 상에 건조된 흑연 및 카본블랙 복합층(107a)을 갖추고 기판(103)의 제2표면(109) 상에 건조된 흑연 및 카본블랙 복합층(107b)을 갖춘다.

[0057] 더욱이, 개시된 본 발명은 전류 컬렉터 기판의 주면들 모두에 흑연층 및 카본블랙층 및/또는 복합층을 포함하는 다층 전류 컬렉터에 관한 것이다.

[0058] 여기에 사용된 바와 같이, "복합층"은 카본블랙층 및 흑연층이 결합되거나 혼합되는 영역을 의미하려는 것이다. 상기 복합층은 상기 흑연층과 카본블랙층 사이에 배치될 것이다.

[0059] 여러 실시예에 있어서, 상기 흑연층은 전류 컬렉터 기판의 어느 한 주면 또는 그 모든 주면 상의 그러한 결합된 층(즉, 흑연, 카본블랙 및 복합층) 전체 두께의 0 내지 99%, 예컨대 10-90%, 20-80%, 30-70%, 또는 40-60%를 포함할 것이다.

[0060] 여러 실시예에 있어서, 상기 카본블랙층은 전류 컬렉터 기판의 어느 한 주면 또는 그 모든 주면 상의 그러한 결합된 층의 전체 두께의 0 내지 99%, 예컨대 10-90%, 20-80%, 30-70%, 또는 40-60%를 포함할 것이다.

[0061] 여러 실시예에 있어서, 흑연과 카본블랙층의 혼합은 거의 없으며, 복합층이 제공되지 않을 수 있다. 다른 실시예들에서는, 복합층이 전류 컬렉터 기판의 어느 한 주면 또는 그 모든 주면 상의 그러한 결합된 층의 전체 두께의 100%까지, 예컨대 10-90%, 20-80%, 30-70%, 또는 40-60%까지 포함되도록 복합층을 형성하기 위해 상기 흑연층 및 카본블랙층의 어느 정도의 혼합이 있을 수 있다.

[0062] 복합층이 제공될 때, 흑연층 및 카본블랙층이 유지되는 정도가 개별적으로 서로 다를 것이다. 여러 실시예에 있어서, 흑연층의 일부가 유지되는 반면 흑연층이 제거되어 복합층에서 거의 완전히 없어질 수 있다. 마찬가지로, 여러 실시예에 있어서, 카본블랙층의 일부가 유지되는 반면 카본블랙층이 제거되어 복합층에서 거의 완전히 없어질 수 있다. 여러 실시예에 있어서, 상기 흑연층은 10 내지 40%를 포함하고, 카본블랙층은 10 내지 40%를 포함하며, 복합층은 총 두께의 20 내지 80%를 포함할 수 있다.

[0063] 더욱이, 본 발명은 울트라캐페시터를 제조하기 위한 방법에 관한 것이며, 상기 방법은 제1포뮬레이션으로부터 전류 컬렉터 기판의 각각의 주면에 걸쳐 제1층을 형성하는 단계, 제2포뮬레이션으로부터 각각의 제1층에 걸쳐 제2층을 형성하는 단계, 및 각각의 제2층에 걸쳐 적어도 하나의 활성 카본층을 형성하는 단계를 포함한다. 실시예들에 있어서, 상기 제1포뮬레이션 및 제2포뮬레이션 중 어느 하나는 흑연 포뮬레이션이고, 상기 제1포뮬레이션 및 제2포뮬레이션 중 또 다른 하나는 카본블랙 포뮬레이션이다.

[0064] 상기의 개시에 따르면, 제1층 및 제2층이 한정하진 않지만 슬롯 다이 코팅, 슬라이드 비드, 및 커튼 코닝과 같은 기술들을 이용하여 형성될 것이다. 여러 실시예에 있어서, 상기 제1층 및 제2층은 동일한 또는 다른 기술들

을 이용하여 형성될 수 있다. 적어도 하나의 실시예에 있어서, 상기 제1층 및 제2층은 슬롯 다이 코팅 기술을 이용하여 형성될 수 있다. 여러 실시예에 있어서, 상기 제1 및 제2층은 동시에 또는 분리적으로 형성, 즉 제1 층이 형성된 후 제2층이 형성되거나, 또는 거의 동시에 형성될 수 있다.

[0065] 적어도 하나의 실시예에 있어서, 제1 및 제2층은 슬롯 다이, 예컨대 이중 슬롯 다이를 이용하여 거의 동시에 형성될 수 있다. 그와 같은 실시예에 있어서, 상기 2개의 층들은 슬롯에서 합쳐진 후 전류 컬렉터 기판 상에 함께 제공된다. 선택적으로, 2개의 층들은 전류 컬렉터 기판에 적용될 때 공통 비드로 분리적으로 슬롯 다이로부터 빠져나올 수 있다.

[0066] 원하는 특성의 층(들)을 달성하기 위해, 통상의 기술자의 능력 범위 내에서 예컨대 적절한 코팅 속도, 층 포뮬레이션(들)의 유동률, 심 두께(shim thickness), 건조 조건들, 및 코팅 다이 립과 코팅 표면의 캡 거리와 같은 상기 기판에 제1 및 제2층을 형성하기 위한 파라미터들을 선택할 수 있다.

[0067] 여러 예시의 실시예들에 있어서, 제1층은 전류 컬렉터 기판과 직접 접촉하여 형성될 것이다. 다른 예시의 실시예들에 있어서, 제2층은 상기 제1층과 직접 접촉하여 형성될 것이다. 단지 예시의 방식으로, 일 실시예에서 상기 제1층은 전류 컬렉터 기판과 직접 접촉하는 흑연층이 되고, 상기 제2층은 상기 제1층과 직접 접촉하는 카본블랙층이 될 것이다.

[0068] 또한, 상술한 바와 같이, 상기 방법은 기판 상에 적어도 하나의 추가 층을 형성하는 단계를 포함한다. 상기 추가 층은 상기 제1층과 제2층간, 또는 제2층에 걸쳐 상기 제1층 앞에 형성될 것이다. 단지 예시의 방식으로, 일 실시예에서 상기 추가 층은 전류 컬렉터 기판과 직접 접촉하여 형성될 것이다.

[0069] 여러 실시예에 있어서, 추가 층이 여기에 기술한 방법들을 이용하여 형성되고, 제1층 및 제2층 중 어느 하나 또는 그 모두로서 거의 동시에 형성되거나, 또는 상기 제1층 및 제2층 중 어느 하나 또는 그 모두가 순차 형성될 수 있다. 단지 예시의 방식으로, 일 실시예에 있어서 상기 추가 층은 제1층 및 제2층, 예컨대 트리플 슬롯 다이와 같은 슬롯 다이로 거의 동시에 형성될 것이다.

[0070] 상술한 바와 같이, 상기 건조는 한정하진 않지만 인-라인식 오븐(in-line oven), 적외선(IR), 또는 마이크로파와 같은 방법을 이용하여 행해진다. 상기 제1층 및 제2층은 동일하거나 다른 방법들을 이용하여 건조될 것이다. 단지 예시의 방식으로, 일 실시예에 있어서, 상기 제1 및 제2층들은 인-라인식 오븐을 이용하여 건조될 것이다. 적절한 건조 방법(들) 및 파라미터들을 선택하는 것은 통상의 기술자의 능력 범위 내에 있다. 또한 상술한 바와 같이, 전류 컬렉터 기판의 각각의 주면 상의 제1층 및 제2층이 분리적으로, 함께, 또는 합동으로 건조될 수 있다.

[0071] 적어도 하나의 활성 카본층이 전류 컬렉터의 각 측면 상에 제2층에 걸쳐 형성된다. 여기에 사용된 바와 같이, 상기 용어 "활성 카본층"은 적어도 하나의 활성 카본 물질을 포함하는 활성 카본 포뮬레이션의 층을 의미하려는 것이다. 그러한 활성 카본 포뮬레이션에 유용한 활성 카본 물질은 한정하진 않지만, 아주 작은 구멍이 많은 다공성을 만들고 이에 따라 높은 비표면적(high specific surface area)을 갖도록 처리되는 카본을 포함한다.

예컨대, 활성 카본은 300 내지 2500  $\text{m}^2/\text{g}$ 의 범위를 갖는 높은 BET 비표면적에 특징이 있다. 여기에 기술된 활성 카본 포뮬레이션에 유용한 활성 카본 물질은 한정하진 않지만, 일본, 오사카의 쿠라레이 케미칼사(Kuraray Chemical Company Ltd), 캘리포니아, 콤프톤의 카본 액티베이티드 코포레이션(Carbon Activated Corporation), 및 뉴저지, 패터슨의 제너럴 카본 코포레이션(General Carbon Corporation)에 의해 판매되는 카본을 포함한다. 전체 내용이 여기에 참조로 반영되는 공통 소유권이 있는 미국출원 제12/335,044호 및 제61/297,469호에 다른 적절한 활성 카본 물질이 개시되어 있다.

[0072] 여러 실시예에 있어서, 상기 활성 카본은 0.1 내지 100 wt.%의 활성 카본 포뮬레이션, 예컨대 1 내지 99 wt.%, 또는 85 wt.%와 같은 10 내지 90 wt.%의 활성 카본 포뮬레이션을 포함한다.

[0073] 여러 실시예에 있어서, 상기 활성 카본 포뮬레이션은 여기에 기술한 바와 같이 적어도 하나의 바인더(binder)를 더 포함한다. 여기에 사용된 바와 같이, 바인더는 한정하진 않지만 폴리테트라플루오로에틸렌(PTFE; polytetrafluoroethylene), 폴리비닐리덴 폴루오르(PVDF; polyvinylidene fluoride), 폴리비닐피롤리돈(PVP; polyvinylpyrrolidone), 폴리비닐 아세테이트(PVA; polyvinyl acetate), 폴리에틸렌 옥사이드(PEO; polyethylene oxide), 폴리프로필렌, 폴리에틸렌, 폴리우레탄, 폴리아크릴레이트, 및 다른 유기(여전히 화학적으로 그리고 전기화학적으로 불활성) 바인더를 포함한다. 적어도 하나의 실시예에 있어서, 상기 바인더는 PTFE가 될 것이다. 여러 실시예에 있어서, 상기 바인더는 0.01 내지 50 wt.%의 활성 카본 포뮬레이션, 예컨대 0.1

내지 49 wt.%, 또는 10 wt.%와 같은 1 내지 40 wt.%의 활성 카본 포뮬레이션을 포함할 것이다.

[0074] 여러 실시예에 있어서, 상기 활성 카본 포뮬레이션은 예컨대 카본블랙; 금속 나노튜브, 로드, 및 와이어; 카본나노튜브, 로드, 및 와이어; 그래핀 입자; 흑연(천연 또는 합성); 전도성 나노입자; 및 전도성 폴리머와 같은 적어도 하나의 추가 전도성 강화제를 더 포함한다. 적어도 하나의 실시예에 있어서, 상기 전도성 강화제는 카본블랙을 포함한다. 상기 전도성 강화제는 0.01 내지 50 wt.%의 활성 카본 포뮬레이션, 예컨대 0.1 내지 49 wt.%, 또는 5 wt.%와 같은 1 내지 45 wt.%의 활성 카본 포뮬레이션을 포함할 것이다.

[0075] 일단 기판 상에 제공되면, 그 활성 카본층의 두께는 100nm 내지 5mm, 예컨대 0.25 $\mu$ m 내지 200 $\mu$ m 또는 500nm 내지 150 $\mu$ m의 범위가 될 것이다. 여러 실시예에 있어서, 활성 카본층은 기판 상에서의 두께가 균등하고, 다른 것들은 두께가 균등하지 않을 것이다.

[0076] 예컨대, 적층 방법, 그라비어 방법(gravure method), 슬롯 다이 또는 사출 방법, 테이프-캐스팅 방법, 공통 률러 방법, 프레싱, 또는 그들 조합을 포함하는 활성 카본층을 형성하기 위한 적절한 방법들을 선택하는 것은 통상의 기술자의 능력 범위 내에 있다.

[0077] 도 3은 본 발명의 적어도 하나의 실시예에 따라 이루어진 울트라캐페시터 전극의 일부를 나타낸 획단면도이다.

상기 울트라캐페시터 전극(110)은 기판(103)의 제1표면(108) 상에 제1 및 제2층(107a)에 걸친 활성 카본층(111a) 및 기판(103)의 제2표면(109) 상에 제1 및 제2층(107b)에 걸친 활성 카본층(111b)을 갖춘다.

[0078] 여러 비한정 예시의 실시예들에 있어서, 개시의 방법들은 카본블랙 및 흑연 물질을 포함하는 하나의 포뮬레이션 보다 더 안정한 흑연 및 카본블랙층을 형성하기 위한 2개의 포뮬레이션을 이용한다. 따라서, 그러한 개시의 방법들은 여러 배치(batch) 또는 런(run)에 걸쳐 일정한 특성들을 갖는 제품을 신뢰성 있게 만들 수 있다. 또한 여기에 기술된 방법들은 여러 층들에 사용된 포뮬레이션의 구성을 변경함으로써 흑연 및 카본블랙층의 미세 구조, 두께, 및 조성을 변경할 수 있게 한다.

[0079] 여러 실시예에 있어서, 그러한 개시의 방법들은 현재 기술분야에서 공지된 방법들에 의해 얻어진 제품과 비교하여, 활성 카본층과 전류 컬렉터 기판간 계면 저항을 유지하거나 감소시키는 다층 전류 컬렉터 및/또는 울트라캐페시터 전극을 제조할 수 있다. 다른 실시예들에 있어서, 상기 방법들은 현재 기술분야에서 공지된 방법에 의해 얻어진 제품과 비교하여, 동일하거나 또는 더 열적으로 강한 다층 전류 컬렉터 및/또는 울트라캐페시터 전극을 제조할 수 있다.

[0080] 여러 실시예에 있어서, 상기 개시의 방법들은 현재 기술분야에서 공지된 방법보다 빠른 속도로 다층 전류 컬렉터 및/또는 울트라 캐페시터 전극을 제조할 수 있다.

[0081] 달리 나타내지 않는 한, 본 명세서 및 청구항들에 사용된 모든 숫자는 그렇게 나타내었다 해도 모든 경우 용어 "약"으로 변경되는 것으로 이해해야 한다. 본 명세서 및 청구항들에 사용된 정확한 수치들은 본 발명의 추가 실시예들을 형성한다는 것을 이해해야 한다. 그러한 예에서 개시된 수치들의 정확성을 보장하기 위한 노력들이 이루어진다. 그러나, 소정의 측정된 수치는 본질적으로 각각의 측정 기술에서 발견된 표준편차를 야기하는 소정의 오류를 포함할 수 있다.

## 예

[0083] 이하의 예들은 청구된 바와 같은 발명들로 한정하려는 것은 아니다.

## 비교예

[0085] 1 밀리리터 두께의 알루미늄 포일(세정 또는 처리되지 않은)이 전류 컬렉터 기판으로서 선택된다. 전도성 카본 중간 코팅 잉크가 헨케(Henkel)의 코팅 잉크 DAG EB 012를 1:1 비율의 탈이온수와 5분동안 핸드 믹싱하여 딥 코팅(dip coating) 적용을 위해 준비되고 2시간 내에 사용한다. 다음에, 기판이 전도성 카본 중간 코팅 잉크로 딥 코팅되도록 기판의 양측면이 동시에 코팅된다. 전도성 중간 코팅의 두께는 1 내지 3  $\mu$  범위를 목표로 한다. 다음에, 그러한 코팅된 기판은 적어도 10분 동안 컨베션 오븐(convective oven)에서 105°C로 베이크(bake)된다.

[0086] 다음에, 그렇게 제조된 전류 컬렉터는 활성 카본 시트의 양측면에 200°C 및 250 pli(pounds per linear inch)로 적층된다. 상기 활성 카본 시트는 일본 오사카의 쿠라레이 케미칼사의 Kuraray YP50F의 활성 카본을 매사추세츠, 보스톤의 카봇 코포레이션에 의한 BLACK PERALS<sup>®</sup> 2000의 카본블랙과 85:5의 비율로 혼합함으로써 준비된다. 다음에, 텔라웨어, 월밍턴의 DuPont에 의한 Teflon<sup>®</sup> PTFE613A가 85:5:10 비율의 활성 카본:카본블랙:PTFE

를 만들기 위해 추가된다. 이소프로필 알콜이 그 혼합물에 추가되어 혼합된 후 반건조된다. 다음에, 그 재료가 약 9 내지 10 밀리리터 두께의 프리-폼(pre-form)으로 프레스된다. 상기 프리-폼은 체계적인 캘린더링(calendering)에 의해 3 내지 5 밀리리터의 카본 시트로 치밀화된다.

[0087] 결과의 형성된 전극의 평면 영역에 걸친 비저항은 13/16인치 직경의 디스크를 펀칭(punching)하여 평면 영역에 걸친 비저항(수신한 바와 같은)을 측정함으로써 얻어진다. 각 실린더 상부를 커버하는 실버 포일 콘택트를 갖는 2개의 세라믹 실린더(직경=1인치) 사이의 그러한 샘플 상에 1001b 로드(load)를 인가하기 위해 Instron 4202가 사용된다. 키슬리 멀티미터(Keithley multimeter) 2700을 이용하여 DC 4선 저항 측정이 이루어지고, 이후 비저항에 대한 저항치가 계산된다.

[0088] 다음에, 상기 샘플이 적어도 16시간 동안 150°C에서 가열되고, 식힌 후, 다시 평면 영역에 걸친 비저항을 측정한다.

[0089] 그러한 전극 샘플은 16시간 동안 150°C 노출 후  $0.10 \text{ ohm-cm}^2$ (수신한 바와 같은)와  $0.11 \text{ ohm-cm}^2$ 의 측정된 평면 영역에 걸친 비저항을 나타냈다. 따라서, 전도성 카본 중간 코팅은 양호한 특성 및 열적 안정성을 나타냈다.

#### 발명예

[0091] 제1층 포뮬레이션(흑연 포뮬레이션)은 뉴저지, 애즈버리의 애즈버리 카본사의 GK572를 이용하여 준비한다. 50:50의 GK572:탈이온수 희석은 약 5분 동안 혼합하여 준비한다. 그 혼합물은 인정한 분산재를 유지했다.

[0092] 제2층 포뮬레이션(카본블랙 포뮬레이션)은 헨켈(Henkel)의 DAG EB 012를 이용하여 준비한다. 60:40의 DAG:탈이온수 희석은 약 5분 동안 혼합한 후 그 혼합물을 3일 동안 가라앉혀 준비한다. 가라앉힌지 3일째에 그 부유액을 채취한다.

[0093] 1밀리미터 두께 알루미늄 포일(세정 또는 처리하지 않은)이 전류 컬렉터 기판으로 선택되어 제1 및 제2층 포뮬레이션을 이용하여 슬롯 다이 코팅된다. 우선, 그 기판의 한측면이 다층 슬롯 다이를 이용하여 22 ft/min 선속도로 코팅된다. 3밀리미터의 두꺼운 심(shim)을 이용한 제1포뮬레이션 유동률은 1.3 ml/min이었다. 5밀리미터의 두꺼운 심을 이용한 제2포뮬레이션 유동률은 4.8 ml/min이었다. 다음에, 그 코팅된 기판은 239°F에서 인-라인식 오븐을 통해 건조했다.

[0094] 다음에, 상기 기판의 또 다른 표면은 상기 동일한 조건 하에 다층 슬롯-다이로 코팅되고, 239°F에서 인-라인 건조했다.

[0095] 다음에, 제조된 전류 컬렉터는 상기 비교예에서 기술한 바와 같이 활성 카본 시트의 양측면에 적층된다.

[0096] 상술한 방법을 이용하여, 그러한 결과의 형성된 전극 샘플은 16시간 동안 150°C 노출 후  $0.11 \text{ ohm-cm}^2$ (수신한 바와 같은)와  $0.11 \text{ ohm-cm}^2$ 의 측정된 평면 영역에 걸친 비저항을 나타냈다.

[0097] 이러한 데이터는 비교예 1의 제품과 같은 유사한 전도성 중간 코팅 특성을 암시한다. 그러나, 상기 발명예의 방법은 좀더 콘트롤된 다용도의 방법이다. 예컨대, 상기한 비교예의 잉크는 단지 약 2시간의 작업 수명을 갖는 반면, 상기한 발명예의 2개의 포뮬레이션은 안정적이다.

도면

도면1

도면2

도면3