(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4454837号

(P4454837)

(45) 発行日 平成22年4月21日(2010.4.21)

(24) 登録日 平成22年2月12日(2010.2.12)

(51) Int.Cl.

F 1

H04N 5/907 (2006.01)

H04N 5/907

B

G11B 20/10 (2006.01)

G11B 20/10

311

H04N 5/765 (2006.01)

H04N 5/782

K

請求項の数 1 (全 9 頁)

(21) 出願番号

特願2000-374233 (P2000-374233)

(22) 出願日

平成12年12月8日 (2000.12.8)

(65) 公開番号

特開2002-176611 (P2002-176611A)

(43) 公開日

平成14年6月21日 (2002.6.21)

審査請求日

平成19年12月4日 (2007.12.4)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100096965

弁理士 内尾 裕一

(72) 発明者 清水 哲也

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 小田 浩

(56) 参考文献 特開2001-238117 (JP, A)

最終頁に続く

(54) 【発明の名称】 画像処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

所定の記録フォーマットに対応した所定の画素数よりも多い第1の画素数の画像信号を出力する撮像手段と、

前記撮像手段から出力された前記第1の画素数の画像信号を前記所定の画素数の画像信号に変換する変換手段と、

前記所定の画素数に対応した記憶容量を持ち、前記変換手段から出力される前記所定の画素数の画像信号を記憶する第1のメモリと、

前記第1の画素数に対応した記憶容量を持ち、前記撮像手段より出力された前記第1の画素数の画像信号を記憶する第2のメモリと、

前記第2のメモリのアドレスを発生し、前記撮像手段より出力された前記第1の画素数の画像信号を前記第2のメモリに書き込むと共に前記第2のメモリより前記第1の画素数の画像信号を読み出すメモリインターフェイスと、

前記第1のメモリに記憶されている前記所定の画素数の画像信号を、前記所定の記録フォーマットに従って動画像データとして記録媒体に記録する記録手段と、

前記第2のメモリから読み出された前記第1の画素数の画像信号を静止画像データとして出力する静止画処理手段とを備え、

前記変換手段、前記第1のメモリ、前記メモリインターフェイス及び前記静止画処理手段を同一の集積回路上に配置し、前記撮像手段、前記記録手段及び前記第2のメモリを前記集積回路とは独立した回路として構成したことを特徴とする画像処理装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は画像処理装置関し、特に、メモリを用いて異なる画素数の画像信号を処理する装置に関する。

**【0002】****【従来の技術】**

従来、ビデオカメラにより撮影された画像信号をデジタル信号として磁気テープに記録するビデオカメラ一体型デジタルVTRが知られている。また、近年では、メモリカードスロットを備え、動画像データについては従来通り磁気テープに記録し、メモリカードに対して静止画像を記録可能なデジタルVTRも開発されている。

10

**【0003】****【発明が解決しようとする課題】**

一方、近年の半導体技術の向上により、CCDの画素数が飛躍的に増加しており、前記のデジタルVTRにおいても従来のものより多画素のCCDを用いて静止画像を撮影、記録することが考えられる。

**【0004】**

しかし、従来のデジタルでは、動画像データと静止画像データとが同一の画素数の信号であることを前提として設計されている。そのため、このようにCCDの画素数が増加し、その結果、静止画像データの画素数が増加した場合に、容易に対応することができない。

20

**【0005】**

また、近年では、回路特性の安定化や消費電力の削減のため、メモリを含めた動画像処理回路、静止画像処理回路などの各回路を同一の集積回路上に配置するのが一般的である。

**【0006】**

しかし、画像信号の画素数が増加した場合、特に静止画処理については画像データの画素数に対応した記憶容量のメモリが必要となるが、静止画処理用のメモリまでもが同一の集積回路上に配置されている場合、メモリ回路のみを増設、あるいはより大容量のものに交換することができない。そのため、画像信号の画素数が増加する度に新たに集積回路を設計しなおす必要があり、大変な労力、コストがかかっていた。

**【0007】**

30

本発明は、前述の如き問題を解決することを目的とする。

**【0008】**

本発明の他の目的は、画像信号の画素数が変更した場合であっても容易に動画像、静止画像データの処理を可能とする処にある。

**【0009】**

本発明の更に他の目的は、画像信号の画素数が変更された場合であっても集積回路の設計を変更することなく容易に静止画像データの処理を可能とする処にある。

**【0010】****【課題を解決するための手段】**

本発明は、所定の記録フォーマットに対応した所定の画素数よりも多い第1の画素数の画像信号を出力する撮像手段と、前記撮像手段から出力された前記第1の画素数の画像信号を前記所定の画素数の画像信号に変換する変換手段と、前記所定の画素数に対応した記憶容量を持ち、前記変換手段から出力される前記所定の画素数の画像信号を記憶する第1のメモリと、前記第1の画素数に対応した記憶容量を持ち、前記撮像手段より出力された前記第1の画素数の画像信号を記憶する第2のメモリと、前記第2のメモリのアドレスを発生し、前記撮像手段より出力された前記第1の画素数の画像信号を前記第2のメモリに書き込むと共に前記第2のメモリより前記第1の画素数の画像信号を読み出すメモリインターフェイスと、前記第1のメモリに記憶されている前記所定の画素数の画像信号を、前記所定の記録フォーマットに従って動画像データとして記録媒体に記録する記録手段と、前記第2のメモリから読み出された前記第1の画素数の画像信号を静止画像データとして

40

50

出力する静止画処理手段とを備え、前記変換手段、前記第1のメモリ、前記メモリインターフェイス及び前記静止画処理手段を同一の集積回路上に配置し、前記撮像手段、前記記録手段及び前記第2のメモリを前記集積回路とは独立した回路として構成した。

【0011】

【発明の実施の形態】

以下、本発明の実施形態について説明する。

【0012】

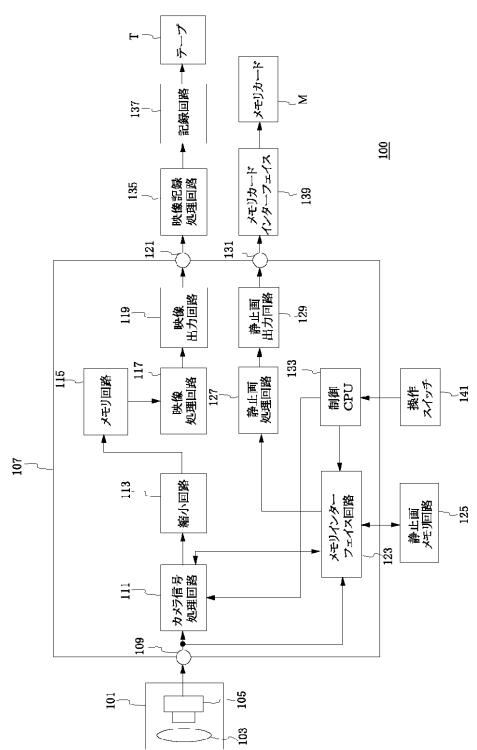

図1は本発明が適用されるカメラ一体型デジタルVTR100の構成を示すブロック図である。本形態のデジタルVTRは、メモリカードを装着するカードスロットを備え、動画データを磁気テープに記録する動画モードと、静止画像データをメモリカードに記録する静止画モードとを持つ。まず、動画モード時の動作について説明する。

10

【0013】

図1において、101は撮像回路であり、レンズ、絞り等を含む光学系103と、CCDとその駆動回路やA/D変換器等を含む撮像素子105からなる。図1の装置では、撮像素子として、一般的な補色フィルタを配した単版のCCDを用いており、CCDの画素数は約200万画素、1フレームの有効画素数が水平1600画素×垂直1200画素のUXGAサイズの画像データを出力するものである。本形態では、CCDの色フィルタはシアン(Cy)、イエロー(Y)、グリーン(G)、マゼンタ(Mg)で構成され、図2に示す配列となっている。

【0014】

20

CCDから画像データを読み出す際、動画モードにおいては、隣接する2ラインの画素を加算して読み出すのが一般的である。撮像回路101は、不図示の制御回路によりその読み出し動作が制御され、操作スイッチ143により動画記録モードに設定されると、以下のように画像信号を読み出す。

【0015】

例えば、図2の配列の場合、1フレームの画像データのうち、第1フィールドの画像信号はNライン+(N+1)ライン、(N+2)ライン+(N+3)ラインの順に読み出し、第2フィールドの画像信号は(N+1)ライン+(N+2)ライン、(N+3)ライン+(N+4)ラインの順に読み出す。

【0016】

30

撮像回路101から出力されたデジタル画像信号は入力端子109を介してカメラ信号処理回路111に出力される。カメラ信号処理回路111は、入力端子109を介して出力された画像データに対してクランプ処理、ホワイトバランス処理の後色分離処理を行う。更に、輪郭補正処理、補正処理の後、マトリクス回路により輝度信号Yと色差信号Cr,Cb信号に変換し、動画モードにおいては、変換された画像信号を縮小回路113に出力する。

【0017】

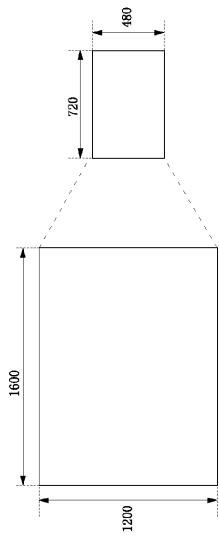

縮小回路113は、カメラ信号処理回路111から出力された画像信号に対して、LPFにより垂直・水平方向の2次元に帯域制限をかける。そして、この帯域制限された画像信号をITU-R601に準拠したサンプリング構造でサブサンプルすることで、カメラ信号処理回路111から出力される画像信号の1フレームの画素数をテープTに記録する上で規定されたフォーマットに従う所定の画素数、例えば本形態では、図3に示すように水平720画素×垂直480画素となるように変換し、そのサイズを縮小する。

40

【0018】

縮小回路113により処理された画像信号はメモリ回路115に書き込まれる。メモリ回路115は1フレーム分の前記所定の画素数、例えば720×480画素の画像信号をベースバンドのまま、即ち圧縮・符号化処理していない状態で記憶可能な容量を持つ。

【0019】

メモリ回路115に記憶された画像信号は、その出力するべきタイミングに同期して映像処理回路117により読み出される。映像処理回路117はメモリ回路115から読み出

50

した画像信号に対し、電子ズーム処理やワイプ、フェード等の周知の合成処理や特殊効果処理を施し、映像出力回路 119 に出力する。映像出力回路 119 は映像処理回路 117 からの画像信号に対して水平、垂直同期信号を付加し、基準規格の I T U - R 601 / R 656 に準拠したデジタル映像信号に変換して出力端子 121 を介して映像記録処理回路 135 に出力する。

【0020】

映像記録処理回路 135 は出力端子 121 を介して出力されたデジタル画像信号に対して周知のブロック符号化処理を施してその情報量を圧縮する。そして、圧縮符号化された画像データに対して、同期、I D データの付加、あるいはエラー訂正符号化等の処理を施し、記録データ列を生成して記録回路 137 に出力する。記録回路 137 は映像記録処理回路 135 から出力された記録データ列に対してデジタル変調等の処理を施すと共に、回転ヘッドによりテープ T 上に多数のトラックを形成して記録する。

10

【0021】

次に、静止画モードについて説明する。静止画モードとは、操作スイッチ 143 の静止画記録用シャッタボタンが操作されたことに応じて撮像回路 101 から出力される画像信号のうちの 1 フレームを抽出し、静止画像データとしてメモリカード M に記録するモードである。

【0022】

操作スイッチ 143 の静止画記録スイッチが操作されると、撮像回路 101 は静止画記録スイッチの操作タイミングに応じた 1 フレームの画像信号を非加算読み出しにて C C D より読み出し、入力端子 109 に出力する。

20

【0023】

即ち、撮像回路 101 は静止画記録スイッチが操作されていない状態では前述のように加算読み出しにより画像信号を読み出し、不図示のモニタに出力している。従って、ユーザは静止画像の記録待機状態ではこのモニタにより通常の動画像データを確認することができる。そこで、ユーザが静止画記録スイッチを操作すると、撮像回路 101 はその操作タイミングに応じた 1 フレームの画像信号のみ非加算読み出しにて C C D より読み出す。

【0024】

例えば、図 2 に示すフィルタ配列の場合、非加算読み出し時においては、第 1 フィールドの画像信号は N ライン、( N + 2 ) ラインの順に読み出し、第 2 フィールドの画像信号は ( N + 1 ) ライン、( N + 3 ) ラインの順に、隣接ラインの画素が加算されない状態で読み出される。

30

【0025】

このように入力端子 109 より入力された 1 フレームの画像信号は一旦メモリインターフェイス回路 123 に出力され、静止画メモリ回路 141 に記憶される。

【0026】

メモリインターフェイス回路 123 は操作スイッチ 143 の指示を受けた制御 C P U 133 により制御され、静止画メモリ回路 141 に対して画像データの書き込み、読み出しを行う回路である。静止画メモリ回路 141 は撮像回路 101 の C C D の有効画素数に対応する画素数の 1 フレームの画像データを縮小することなく記憶可能な容量を持つものである。

40

【0027】

また、本形態では、静止画メモリ回路 125 として、汎用の S D R A M (Synchronous Dynamic RAM) を使用している。従って、メモリインターフェイス回路 123 は静止画メモリ回路 125 として使用される汎用 S D R A M の規格に準拠してカメラ信号処理回路 111 からの画像データをパケット化し、コマンドを付加して静止画メモリ回路 125 にアクセスする。更に、メモリインターフェイス回路 123 にて発生する汎用 D R A M アドレスに関しては、メモリの拡張性を考慮し、十分な本数を確保している。また、本形態では、例えば、静止画メモリ回路 125 として、記憶容量が 64 M ビット程度以上の汎用の S D R A M を用いることができる。

50

## 【0028】

静止画メモリ回路125に書き込まれた1フレームの画像データは、メモリインターフェイス回路123により順次（ノンインターレース）走査にて読み出され、カメラ信号処理回路111に出力される。

## 【0029】

カメラ信号処理回路111は動画モードと同様、メモリインターフェイス回路123より出力される画像信号に対し、クランプ処理、ホワイトバランス処理の後色分離処理を行い、更に、輪郭補正処理、補正処理の後、マトリクス回路により輝度信号Yと色差信号Cr, Cb信号に変換する。カメラ信号処理回路111により処理された1フレームの画像信号は再びメモリインターフェイス回路123に出力され、静止画メモリ回路125に記憶される。

10

## 【0030】

輝度信号と色差信号に変換されて静止画メモリ141に書き込まれた1フレームの画像信号は、メモリインターフェイス回路123により、静止画処理回路127による処理に適した順序で読み出され、静止画処理回路127に出力される。

## 【0031】

静止画処理回路127はメモリインターフェイス回路123から出力される画像信号をJPEG規格に従って符号化し、静止画像データとして静止画出力回路129に出力する。静止画出力回路129はメモリカードインターフェイス139にて扱うファイルフォーマットに従う形態に変換し、出力端子131を介してメモリカードインターフェイス139に出力する。メモリカードインターフェイス139はメモリカードM上の書き込みアドレスを指定し、出力端子131から出力された1フレームの符号化された静止画像データを一つのファイルとしてメモリカードMに記録する。メモリカードMはVTR100に設けられたメモリカードスロットを介してVTR100本体に着脱可能に構成される。

20

## 【0032】

ここで、図1において、カメラ信号処理回路111、縮小回路113、メモリ回路115、映像処理回路117、映像出力回路119、メモリインターフェイス回路123、静止画処理回路127、静止画出力回路及び、制御CPU133は同一の集積回路107上に構成されている。そして、静止画メモリ回路125はこれら集積回路107とは別の回路として構成される。

30

## 【0033】

即ち、本形態では、動画処理と静止画処理に係る回路の大部分は同一の集積回路上に置くことで回路特性の均一化、消費電力の抑制を図っている。そして、動画処理と静止画素処理に係る回路のうち、静止画メモリ回路125については集積退路とは別の回路構成とすることで、撮像回路101にて用いるCCDの画素数がより多くなった場合にも、容易に対応できるようにした。

## 【0034】

即ち、撮像回路101にて用いるCCDの画素数がより多くなった場合、縮小回路113による縮小処理を撮像回路101からの画像信号のサイズに応じて変更し、静止画メモリ125を撮像回路101からの画像信号のサイズに応じた容量を持つ、例えば、128Mビットの汎用SDRAMや64Mビットの汎用SDRAMを複数設けることで容易に対応可能となる。

40

## 【0035】

また、動画像処理用のメモリ115については、動画像処理にて扱う画像信号の画素数が、テープTに対する記録フォーマットにて規定された所定の画素数、即ち720画素×480画素と決まっているため、CCDの画素数が変更してもそれに応じてメモリ回路115の容量を変更する必要がない。

## 【0036】

このように画像信号の画素数が増加することを考慮し、前述のように、メモリインターフェイス回路123にて発生するアドレスを予め十分確保しておくことが望ましい。

50

## 【0037】

また、静止画メモリ回路125の記憶容量については、連写機能を考慮して複数フレーム分の容量を持つメモリを使用することも可能である。

## 【0038】

図1の装置では、動画処理用のメモリ回路115を集積回路107上に配置したが、この動画処理用のメモリ回路も静止画メモリ回路125と同様、汎用のSDRAMを使い、別の回路として構成することも可能である。

## 【0039】

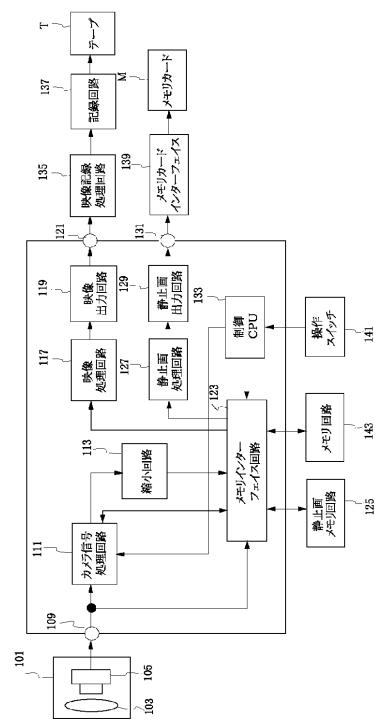

図4はこのように動画処理用のメモリ回路も汎用のSDRAMを用いた場合のカメラ一体型VTR100の構成を示す図である。図4において、図1と同様の構成については同一番号を付し、その詳細な説明は省略する。

10

## 【0040】

図4において、動画モードにおいては、縮小回路113により縮小された画像信号がメモリインターフェイス回路123に出力される。メモリインターフェイス回路123は制御CPU133からの制御信号に応じて書き込みアドレスを発生し、縮小回路113から出力された画像信号をメモリ回路143に書き込む。そして、メモリインターフェイス回路123はメモリ回路143に記憶された画像信号を所定の出力タイミングに同期して読み出し、映像処理回路117に出力する。

## 【0041】

また、静止画モード時の動作は図1の装置と同様である。

20

## 【0042】

本形態では、メモリ回路143も汎用のSDRAMとすることで、更に使い勝手が向上する。

## 【0043】

即ち、撮像回路101にて用いられるCCDの画素数が36万画素程度の場合、メモリ回路143を32Mビット程度の汎用SDRAMとし、メモリ回路143の記憶領域を動画処理用領域と静止画処理用領域とに分けて使用することで、特に静止画メモリ回路125を設けることなく動画像データの処理と静止画像データの処理を実現することが可能となる。

## 【0044】

30

一方、CCDの画素数が増えた場合には、メモリ回路143に加え、新たに静止画メモリ回路125を追加することで、動画像データよりも画素数の多い静止画像データの処理を行うことが可能となる。

## 【0045】

このように、動画像処理用のメモリ回路143と静止画メモリ回路125のメモリインターフェイスを共通の汎用のSDRAM用インターフェイスとして、回路の大幅な設計変更することなく画素数が36万画素程度の画像信号から、100万画素を超えるような多画素の画像信号まで処理可能となる。

## 【0046】

なお、前述の実施形態では、静止画メモリ回路125として汎用のSDRAMを使っていたが、勿論これ以外のメモリを使用することも可能である。

40

## 【0047】

## 【発明の効果】

以上述べたように、本発明によれば、画像信号の画素数が変更した場合であっても容易に動画像、静止画像データの処理が可能となる。また、撮像された画像信号の画素数が変更された場合であっても集積回路の設計を変更することなく容易に静止画像データの処理を行うことが可能となる。

## 【図面の簡単な説明】

【図1】本発明が適用されるカメラ一体型VTRの構成を示す図である。

【図2】図1の装置にて用いる撮像素子のフィルタ構成を示す図である。

50

【図3】図1の装置による縮小処理を示す図である。

【図4】本発明が適用されるカメラ一体型VTRの他の構成を示す図である。

【図1】

【図2】

|        |    |    |    |    |

|--------|----|----|----|----|

| Nライン   | Cy | Ye | Cy | Ye |

| N+1ライン | Mg | G  | Mg | G  |

| N+2ライン | Cy | Ye | Cy | Ye |

| N+3ライン | G  | Mg | G  | Mg |

【図3】

【 図 4 】

---

フロントページの続き

(58)調査した分野(Int.Cl. , DB名)

H04N 5/907

G11B 20/10

H04N 5/765