US 20130082783A1

### (19) United States

## (12) Patent Application Publication Shimizu et al.

# (10) **Pub. No.: US 2013/0082783 A1** (43) **Pub. Date: Apr. 4, 2013**

### (54) SEMICONDUCTOR DEVICE

(71) Applicant: RENESAS ELECTRONICS CORPORATION, Kawasaki-shi (JP)

(72) Inventors: **Toshihiko Shimizu**, Tokorozawa (JP);

Yoshikumi Matsunaga, Niiza (JP); Yuri

Kusakari, Kawasaki (JP)

(73) Assignee: **RENESAS ELECTRONICS**

CORPORATION, Kawasaki-shi (JP)

(21) Appl. No.: 13/686,130

(22) Filed: Nov. 27, 2012

### Related U.S. Application Data

(60) Continuation of application No. 13/064,897, filed on Apr. 25, 2011, now Pat. No. 8,339,204, which is a continuation of application No. 12/453,159, filed on Apr. 30, 2009, now Pat. No. 7,952,434, which is a continuation of application No. 12/068,825, filed on Feb. 12, 2008, now abandoned, which is a division of application No. 11/505,472, filed on Aug. 17, 2006, now Pat. No. 7,348,856, which is a division of application No. 10/890,281, filed on Jul. 14, 2004, now Pat. No. 7,116,175.

### (30) Foreign Application Priority Data

### **Publication Classification**

(51) **Int. Cl.**

*H03F 3/195* (2006.01) *H03F 3/68* (2006.01)

(52) U.S. Cl.

### (57) ABSTRACT

Power amplifier circuits which constitute an RF power module used for a digital device capable of handling high frequency signals in two frequency bands are disposed over the same IC chip. The power amplifier circuits are disposed around the IC chip, and a secondary circuit is disposed between the power amplifier circuits. Thus, the power amplifier circuits are provided within the same IC chip to enable a size reduction. Further, the distance between the power amplifier circuits are provided within the same IC chip. It is therefore possible to suppress the coupling between the power amplifier circuits and restrain crosstalk between the power amplifier circuits.

FIG. 1

Vdd1 Ly (m3((m) **₩** 2AM3 1-1, Qa2(Qa)  $\mathbb{Z}$  $\mathbb{R}$ 2AM2  $\mathbb{R}$ 2AM1 Z. . . . .

FIG. 3

FIG. 4

FIG. 5

FIG. 6

# FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 16

FIG. 17

### SEMICONDUCTOR DEVICE

## CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application is a Continuation of U.S. application Ser. No. 13/064,897 filed Apr. 25, 2011, which is a Continuation of U.S. application Ser. No. 12/453,159 filed Apr. 30, 2009, which is a Continuation of U.S. application Ser. No. 12/068,825 filed Feb. 12, 2008, which is a Divisional application of U.S. application Ser. No. 11/505,472 filed Aug. 17, 2006 which is a Divisional of U.S. application Ser. No. 10/890,281 filed Jul. 14, 2004. Priority is claimed based on U.S. application Ser. No. 13/064,897 filed Apr. 25, 2011, which claims the priority of U.S. application Ser. No. 12/453, 159 filed Apr. 30, 2009, which claims the priority of U.S. application Ser. No. 12/068,825 filed Feb. 12, 2008, which claims the priority of U.S. application Ser. No. 11/505,472 filed Aug. 17, 2006 which claims the priority of U.S. application Ser. No. 10/890,281 filed Jul. 14, 2004, which claims the priority of Japanese Patent Application No. 2003-290136 filed on Aug. 8, 2003, all of which is incorporated by reference.

### FIELD OF THE INVENTION

[0002] The present invention relates to a semiconductor device and method, and, more particularly, to a device, system, and method for an RF (Radio Frequency) power module.

### BACKGROUND OF THE INVENTION

[0003] An RF power module is a signal amplifying electronic component used in a communication device such as, for example, a cellular phone, or the like. The RF power module is assembled by packaging semiconductor chips, each having signal amplifying transistors, chip parts, and the like, over a module board. The respective semiconductor chips and the module board are electrically connected to one another through bonding wires. Also, the chip parts can be electrically connected to the module board by connecting their terminals to pads of the module board by soldering.

[0004] Such a configuration with a bias circuit and a bias switch circuit employed in high frequency power amplifiers for a dual band system constructed of HBTs (Heterojunction Bipolar Transistors), has been disclosed in Japanese Patent Laid-Open No. 2000-332551.

[0005] Further, such a configuration that, in high frequency parts or components for a dual band system, includes a plurality of GND lines provided between output microstrip lines to prevent interference between two outputs has been disclosed in, for example, Japanese Patent Laid-Open No. 2001-141756.

[0006] Furthermore, a technique for providing ground pads between output pads of both a semiconductor chip and a wiring board to prevent interference between two outputs in a power module for a dual band, and for wire-bonding, has been disclosed in, for example, Japanese Patent Laid-Open No. 2001-345400.

### SUMMARY OF THE INVENTION

[0007] The miniaturization of the RF power module has been provided herein. An important problem exists in how to miniaturize the RF power module without causing degradation of characteristics like reliability, performance, etc.

[0008] The present invention may provide a technique for decreasing the size of a semiconductor device.

[0009] The present invention may provide a semiconductor device wherein all of a plurality of stages of amplifier circuits of high frequency power amplifier circuits may be respectively formed of horizontal type field effect transistors and may be provided over the same semiconductor chip having a silicon semiconductor substrate.

[0010] Since all of a plurality of stages of amplifier circuits of high frequency power amplifier circuits may be respectively formed of horizontal type field effect transistors and may be provided over the same semiconductor chip having a silicon semiconductor substrate, a semiconductor device may be reduced in size.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0011] Understanding of the present invention will be facilitated by consideration of the following detailed description of the preferred embodiments of the present invention taken in conjunction with the accompanying drawings, in which like numerals refer to like parts, and wherein:

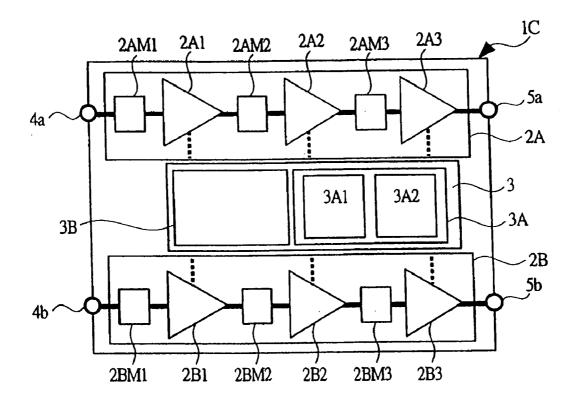

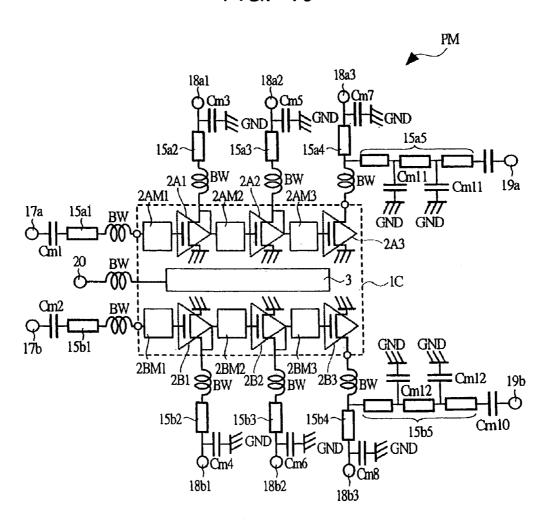

[0012] FIG. 1 is a circuit block diagram showing a semiconductor device according to an exemplary embodiment of the present invention;

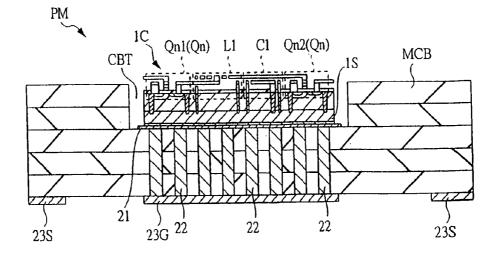

[0013] FIG. 2 is a fragmentary circuit diagram illustrating the semiconductor device shown in FIG. 1;

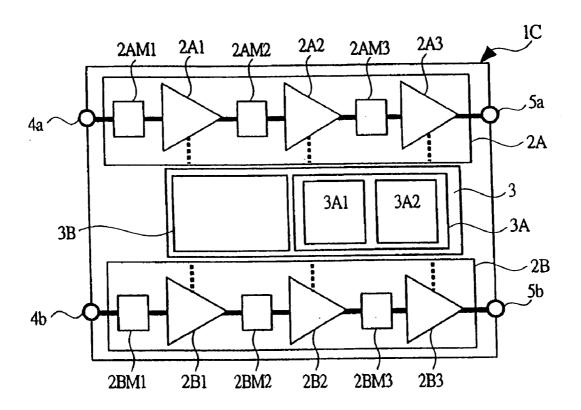

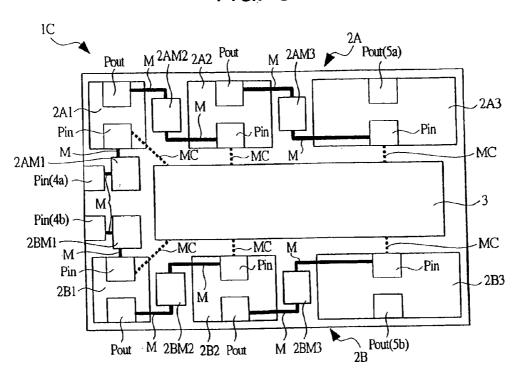

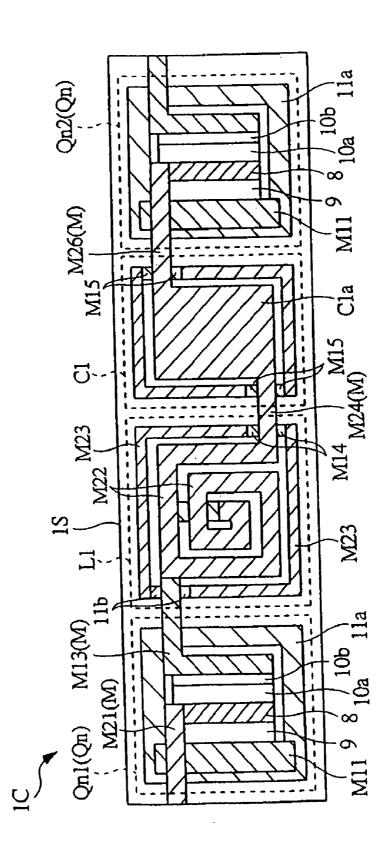

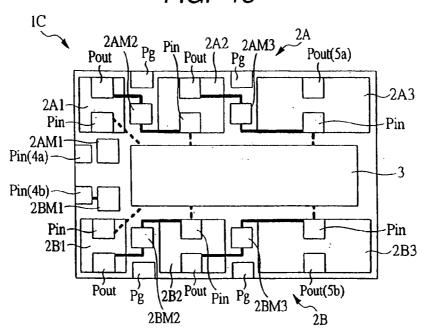

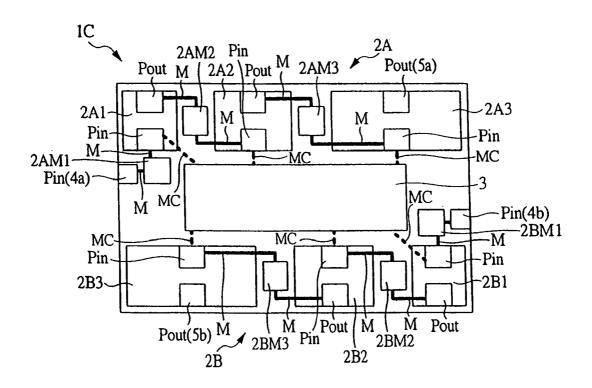

[0014] FIG. 3 is an overall plan view of a semiconductor chip, showing a circuit layout example of the semiconductor device shown in FIG. 1;

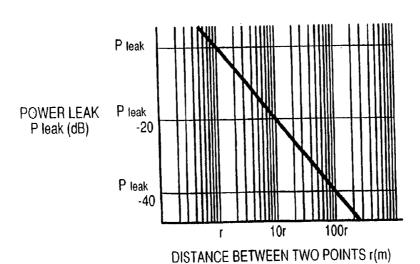

[0015] FIG. 4 is a graph diagram depicting the relationship between a distance and a power leak;

[0016] FIG. 5 is a fragmentary plan view showing the semiconductor chip of the semiconductor device shown in FIG. 1;

[0017] FIG. 6 is a fragmentary cross-sectional view illustrating the semiconductor chip shown in FIG. 5;

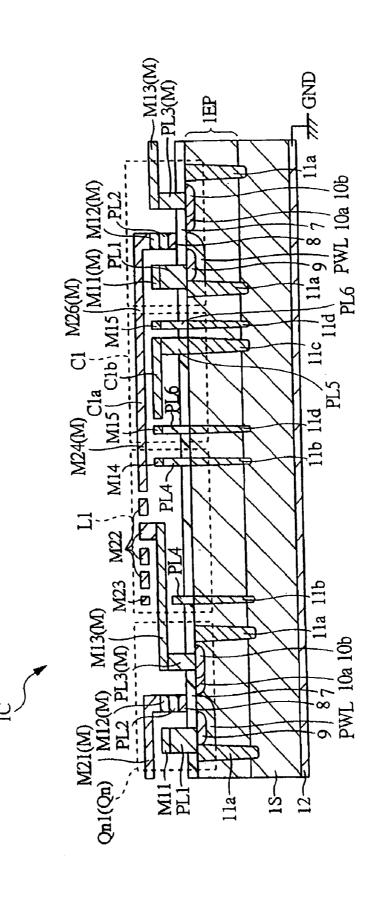

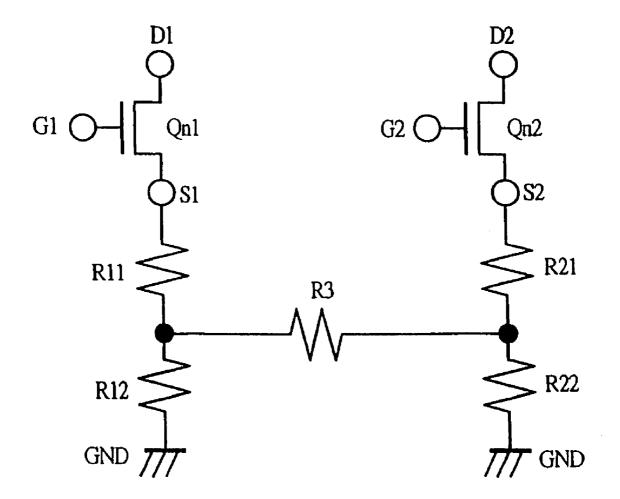

[0018] FIG. 7 is a circuit diagram showing an equivalent circuit of an amplifying stage of the semiconductor chip shown in FIG. 5;

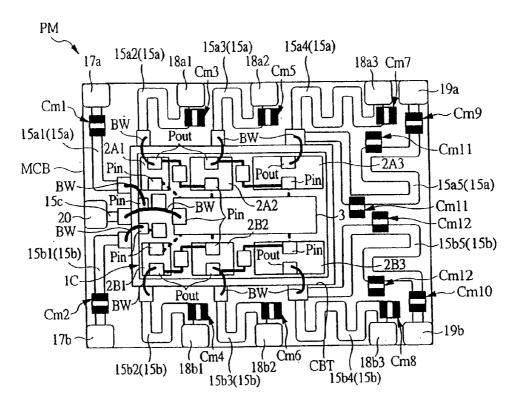

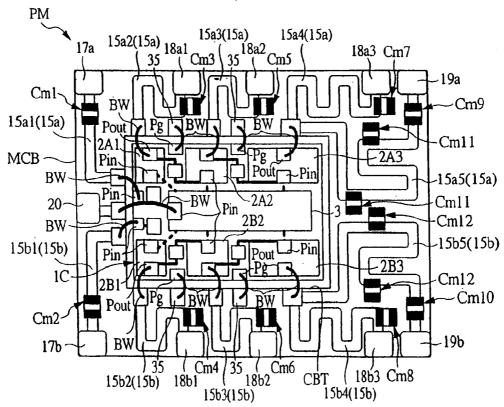

[0019] FIG. 8 is an overall plan view illustrating one example of an RF power module in which the semiconductor chip shown in FIG. 5 is mounted on a module board;

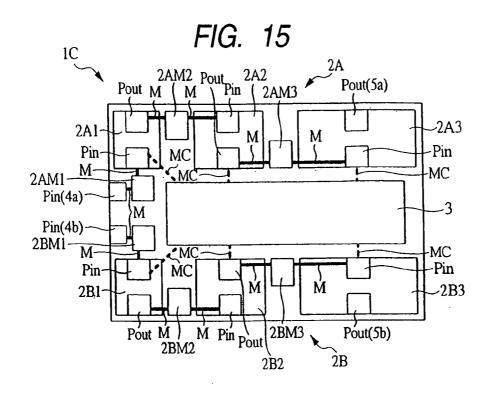

[0020] FIG. 9 is a cross-sectional view showing the RF power module shown in FIG. 8;

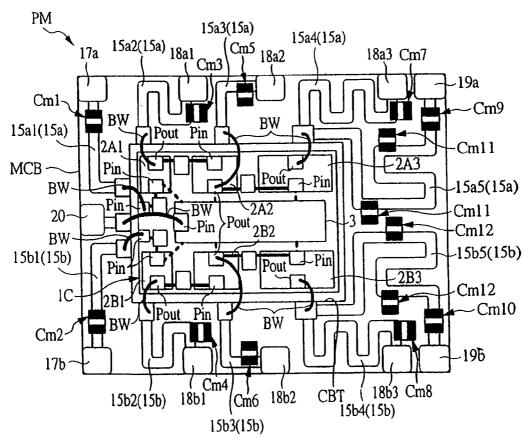

[0021] FIG. 10 is a circuit diagram illustrating an equivalent circuit of the RF power module shown in FIG. 8;

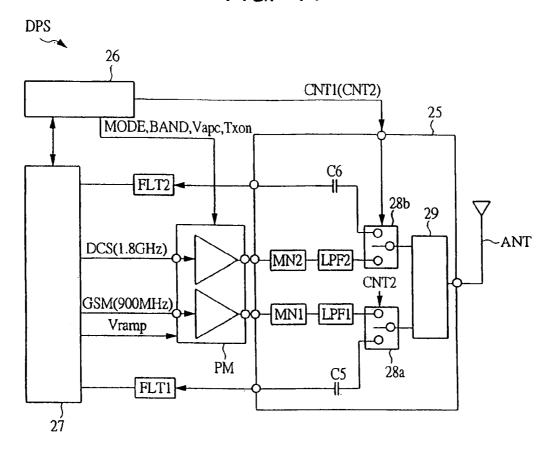

[0022] FIG. 11 is an explanatory view showing one example of a digital cellular phone system using the RF power module shown in FIG. 8;

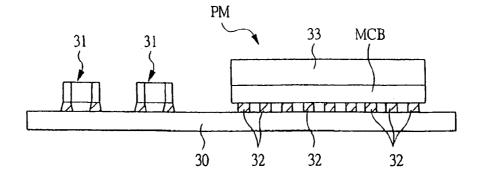

[0023] FIG. 12 is a fragmentary side view illustrating a packaged example of the RF power module of the digital cellular phone system shown in FIG. 11;

[0024] FIG. 13 is an overall plan view of a semiconductor chip, showing a circuit layout example of a semiconductor device according to another exemplary embodiment of the present invention:

[0025] FIG. 14 is an overall plan view illustrating one example of an RF power module in which the semiconductor chip shown in FIG. 13 is mounted on a module board;

[0026] FIG. 15 is an overall plan view of a semiconductor chip, showing a circuit layout example of a semiconductor device according to a further exemplary embodiment of the present invention;

[0027] FIG. 16 is an overall plan view illustrating one example of an RF power module in which the semiconductor chip shown in FIG. 15 is mounted on a module board; and [0028] FIG. 17 is an overall plan view of a semiconductor chip, showing a circuit layout example of a semiconductor device according to yet another exemplary embodiment of the present invention.

#### DETAILED DESCRIPTION

[0029] It is to be understood that the figures and descriptions of the present invention have been simplified to illustrate elements that are relevant for a clear understanding of the present invention, while eliminating, for the purpose of clarity, many other elements found in typical semiconductor devices, systems and methods. Those of ordinary skill in the art may recognize that other elements and/or steps are desirable and/or required in implementing the present invention. However, because such elements and steps are well known in the art, and because they do not facilitate a better understanding of the present invention, a discussion of such elements and steps is not provided herein. The disclosure herein is directed to all such variations and modifications to such elements and methods known to those skilled in the art.

[0030] Prior to the detailed description of embodiments of the present invention, the meaning of certain terms employed in embodiments discussed hereinbelow is explained as follows:

[0031] 1. GSM (Global System for Mobile Communication) may indicate one wireless communication system or standard used in a digital cellular phone. GSM may include three frequency bands of a radio wave, such as a 900 MHz band called "GSM900" or simply "GSM", a 1800 MHz band called "GSM1800" or "DCS1800" (Digital Cellular System) or PCN, and 1900 MHz band called "GSM1900", "DCS1900", or "PCS" (Personal Communication Services). Incidentally, GSM1900 may be principally used in North America. In addition, GSM850, corresponding to an 850 MHz band, might also be used in North America.

[0032] 2. A GMSK (Gaussian filtered Minimum Shift Keying) modulation system or scheme may be a system used in communications of audible or voice signals, i.e., a system that phase-shifts the phase of a carrier according to transmit data. An EDGE modulation system or scheme may be a system used in data communications, i.e., a system in which an amplitude shift may be further added to a phase shift of GMSK modulation.

[0033] 3. A MOSFET (Metal Oxide Semiconductor Field Effect Transistor), corresponding to a field effect transistor, may be abbreviated as "MOS", and an n channel type MOS may be abbreviated as "nMOS".

[0034] In an exemplary embodiment of the present invention, a semiconductor device may be applied to an RF (Radio Frequency) power module used in a digital cellular phone for transmitting information by using, for example, a network of a GMS system.

[0035] As shown in FIG. 1, a circuit block diagram of an IC (integrated circuit) chip (or semiconductor chip) 1C for amplifier circuits, which may constitute an RF power module according to the present embodiment, is illustrated. A circuit block of an IC chip (semiconductor chip) 1C for amplifier circuits, which may be used in the RF power module capable of using two frequency bands (dual band system) of, for example, GSM900 and DCS1800, and using two communication systems of the GMSK modulation system and the EDGE (Enhanced Data GSM Environment) modulation system at their frequency bands, is illustrated in FIG. 1.

[0036] The IC chip 1C may include a power amplifier circuit 2A for GSM900, a power amplifier circuit 2B for DCS1800, and a peripheral circuit 3 which may effect control, compensation and the like on amplifying operations of the those power amplifier circuits 2A and 2B. The power amplifier circuits 2A and 2B respectively may have three amplifying stages 2A1 through 2A3 and 2B1 through 2B3 and three matching circuits 2AM1 through 2AM3 and 2BM1 through 2BM3. That is, input terminals 4a and 4b of the IC chip 1C may be electrically connected to their corresponding inputs of the amplifying stages 2A1 and 2B1, each corresponding to a first stage via the input matching circuits 2AM1 and 2BM1. The outputs of the amplifying stages 2A1 and 2B1, each corresponding to the first stage, may be electrically connected to their corresponding inputs of the amplifying stages 2A2 and 2B2, each corresponding to a second stage via the inter-stage matching circuits 2AM2 and 2BM2. The outputs of the amplifying stages 2A2 and 2B2 may be electrically connected to their corresponding inputs of the final-stage amplifying stages 2A3 and 2B3 via the inter-stage matching circuits 2AM3 and 2BM3. The outputs of the final-stage amplifying stages 2A3 and 2B3 may be electrically connected to their corresponding output terminals 5a and 5b. Thus, in the present exemplary embodiment, all the amplifying stages 2A1 through 2A3 and 2B1 through 2B3 of the power amplifier circuits 2A and 2B may be provided in one IC chip 1C. In general, three amplifying stages may be respectively provided in discrete IC chips, or the amplifying stages corresponding to the first and second stages may be provided in one IC chip and the final-stage amplifying stage may be provided in an IC chip different from the IC chip provided with the first-stage and second-stage amplifying stages, because, for example, the power of the final-stage amplifying stage may be high and generated heat may increase upon its operation, and thus signal interference with other amplifying stages may also increase. Therefore, miniaturization of the RF power module may be impaired. On the other hand, since all the amplifying stages 2A1 through 2A3 and 2B1 through 2B3 of the power amplifying states 2A and 2B may be provided in one IC chip 1C in the present exemplary embodiment, the adjacent intervals among the respective amplifying stages 2A1 through 2A3 and 2B1 through 2B3 may be greatly shortened. It may therefore be possible to realize substantial miniaturization of the RF power module with the IC chip 1C built therein.

[0037] The peripheral circuit 3 may include a control circuit 3A, and a bias circuit 3B, which may apply a bias voltage to each of the amplifying stages 2A1 through 2A3 and 2B1 through 2B3, etc. The control circuit 3A may be a circuit which may generate a desired voltage to be applied to each of the power amplifier circuits 2A and 2B and may include a power supply control circuit 3A1 and a bias voltage generating circuit 3A2. The power supply control circuit 3A1 may be a circuit which generates a first power supply voltage applied to each of drain terminals of output power MOSs of the amplifying stages 2A1 through 2A3 and 2B1 through 2B3. Also, the bias voltage generating circuit 3A2 may be a circuit which may generate a first control voltage for controlling the bias circuit 3B. The present exemplary embodiment may be configured in such a manner that when the power supply control circuit 3A1 generates the first power supply voltage, based on an output level designation signal supplied from a baseband circuit provided outside the IC chip 1C, the bias voltage generating circuit 3A2 may generate the first control voltage, based on the first power supply voltage generated by the power supply control circuit 3A1. The baseband circuit may be a circuit which generates the output level designation signal. The output level designation signal may be a signal for designating or specifying output levels of the power amplifier circuits 2A and 2B and may be generated based on the distance between a cellular phone and a base station, i.e., an output level corresponding to the intensity of a radio wave. In the present exemplary embodiment, elements constitutive of such a peripheral circuit 3 may also be provided in one IC chip 1C. Thus, interface units (interface unit between IC chip 1C and module board (wiring board) and interface units, respectively, necessary for IC chip 1C and module board) may be greatly cut down, and the IC chip 1C and the module board may be reduced in area. It may therefore be possible to realize substantial miniaturization of the RF power module.

[0038] As seen in FIG. 2, an example illustrative of circuit configurations of the power amplifier circuit 2A and the bias circuit 3B is shown. Incidentally, since the power amplifier circuits 2A and 2B and their bias circuit 3B may be identical in circuit configuration, the power amplifier circuit 2A and an example of the circuit configuration for the power amplifier circuit 2A may be shown as representative of the present embodiment.

[0039] The power amplifier circuit 2A according to the present embodiment 1 may have a circuit configuration wherein three nMOSQn (Qn1, Qn2 and Qn3) may be sequentially connected in tandem as the three-stage amplifying stages 2A1 through 2A3. The output level of the power amplifier circuit 2A may be controlled by the bias circuit 3B and the first power supply voltage Vdd1 supplied from the power supply circuit 3A1. In the present embodiment, the first power supply voltage Vdd1 may be supplied to the respective drain electrodes of the three nMOSQn1, Qn2 and Qn3.

[0040] Each of the matching circuits 2AM1 through 2AM3 may have an inductor (passive element) and a capacitor (passive element). The inductor may be formed of a wiring and may have the function of impedance-matching between the input of the amplifying stage 2A1 (nMOSQn1), corresponding to the first stage, and each of the respective interstages. The capacitor may be connected between the inductor and each of the inputs of the nMOSQn of the respective stages and may additionally have the functions of the impedance matching, and that of shutting off dc voltages of the first power supply voltage Vdd1 and a gate bias voltage.

[0041] The bias circuit 3B may have a plurality of voltage division circuits. Each of the voltage division circuits may include a pair of resistors R1 and R2. Each pair of resistors R1 and R2 may be connected in series between an input terminal 4c of the bias circuit 3B and a reference potential (e.g., ground potential: 0V). Wiring portions that connect among the respective pairs of resistors R1 and R2 and the inputs (gate electrodes) of the nMOSQn1 through Qn3 of the respective stages may be electrically connected to one another, respectively. When the first control voltage or output level control voltage is inputted to the input terminal 4c of the bias circuit 3B, the voltage may be divided by each pair of resistors R1 and R2 to thereby generate a desired gate bias voltage, which in turn may be inputted to each of the gate electrodes of the respective nMOSQn1 through Qn3.

[0042] As seen in FIG. 3, an example of a circuit layout of the IC chip 1C for the amplifier circuits, which is shown in FIG. 1, is shown. Additionally, FIG. 4 shows a graph diagram illustrating the relationship between a distance and a power leak, respectively.

[0043] In the present exemplary embodiment as is shown in FIG. 3, the power amplifier circuits 2A and 2B may be disposed around a main surface (device forming surface) of the IC chip 1C, and the peripheral circuit 3 may be disposed between the respective power amplifier circuits 2A and 2B. Since the final-stage amplifying stages 2A3 and 2B3 of the power amplifier circuits 2A and 2B may be high in power, an increase in heat generated upon their operation may cause an increase in signal interference with other amplifying stages. Problems with interference between signals may be large because the phases of respective higher harmonics may be inverse, such as in the case where high frequency signals to be treated may be 900 MHz and 1800 MHz, respectively. As described above, the final-stage amplifying stages 2A3 and 2B3 may be disposed in the vicinity of opposed sides of the IC chip 1C, such that the distance therebetween may become long. Since the amount of propagation of a signal between two points may be inversely proportional substantially to the square of the distance, as shown in FIG. 4, the power amplifier circuits 2A and 2B may be disposed away from each other as described above, whereby crosstalk (radiation or interference) between the power amplifier circuit in operation and the power amplifier circuit in non-operation, for example, may be suppressed. Further, the occurrence of an unnecessary output from the power amplifier circuit being in non-operation may be suppressed. Even if the power amplifier circuits 2A and 2B, which may be different in a system, are provided in the same IC chip 1C, the crossband isolation characteristic between the power amplifier circuits 2A and 2B may be improved. It may thus be possible to enhance reliability and stability of the operation of the RF power module.

[0044] Signs Pin in FIG. 3 may indicate input bonding pads and signs Pout may indicate output bonding pads, respectively. The bonding pads Pin of the respective amplifying stages 2A1 through 2A3 and amplifying stages 2B1 through 2B3 may be placed over the central side of the IC chip 1C, whereas the bonding pads Pout of the respective amplifying stages 2A1 through 2A3 and the amplifying stages 2B1 through 2B3 may be disposed on the sides of the IC chip 1C. Signs M may indicate input, output and amplifying interstage wirings, respectively. The amplifying interstage wirings M may connect between the bonding pads Pin and Pout in bent states. Further, signs Mc may indicate wirings which connect the amplifying stages 2A1 through 2B3 and the peripheral circuit 3.

[0045] As seen in FIG. 5, a fragmentary plan view of the IC chip 1C is shown. Additionally, FIG. 6 shows a fragmentary cross-sectional view of a spot cut along the horizontal direction of the CI chip 1C shown in FIG. 5. Incidentally, although FIG. 5 is a plan view, the same hatching may be applied to ones lying in the same layer.

[0046] A semiconductor substrate (hereinafter also "substrate") 1S, constituting the IC chip 1C, may include, for example, a p+ type silicon (Si) monocrystal and may be configured as a low resistance substrate whose resistivity ranges from, for example, approximately 1 to 10 m $\Omega$ ·cm. An epitaxial layer 1EP comprising, for example, a p- type silicon monocrystal may be formed over the substrate 1S. The resistivity of the epitaxial layer 1EP may be higher than that of the

substrate 1S. Over a main surface of the epitaxial layer 1EP, nMOSQn for the amplifying stages 2A1 through 2A3 and 2B1 through 2B3, and inductors L1, capacitors C1 each having a high Q (Quality factor) value and strip lines for the matching circuits 2AM1 though 2AM3 and 2BM1 through 2BM3, may be formed. Although the nMOSQn1 and Qn2 of the two amplifying stages are illustrated in the present embodiment, the amplifying stages 2A1 through 2A3 and 2B1 through 2B3 of all of the first through three stages may be formed over the same substrate 1S as described above. The nMOSQn shown here indicate unit MOSs. In practice, a plurality of the unit MOSs may be connected in parallel to form the respective one of the amplifying stages 2A1 through 2A3 and 2B1 through 2B3.

[0047] First, the nMOSQn may be formed of a horizontal type MOS like, for example, an LDMOS (Laterally Diffuses MOS), or the like. A type well PWL may be formed in the epitaxial layer 1EP, corresponding to a region for forming each nMOSQn. The p type well PWL may be formed by ion-implanting an impurity, such as boron (B), into the epitaxial layer 1EP. A gate insulating film 7 for each nMOSQn may be formed over the p type well PWL of the epitaxial layer 1EP. The gate insulating film 7 may be formed of, for example, silicon oxide (SiO<sub>2</sub>), or the like, and may further be formed by, for example, a thermal oxidation method, or the like. A gate electrode (input) 8 for each nMOSQn may be formed over the gate insulating film 7. The gate electrode 8 may include a laminated conductor film of, for example, polycrystalline silicon, and a metal silicide layer (e.g., titanium silicide layer or cobalt silicide layer) formed thereon. A channel for each nMOSQn may be formed above the p type well PWL located below the gate electrode 8.

[0048] An n<sup>+</sup> type semiconductor region 9 may be formed within a region for the p type well PWL, which may be located in the vicinity of one end of each gate electrode 8. The n+ type semiconductor region 9 may be a region which functions as the source of the nMOSQn and may be formed by ion-implanting an impurity, such as phosphorous (P), into the p type well PWL. An n<sup>-</sup> type semiconductor region 10a may be formed in the epitaxial layer 1EP in the vicinity of the other end of the gate electrode 8. Then, an n<sup>+</sup> type semiconductor region 10b may be formed at a spot spaced by the n<sup>-</sup> type semiconductor region 10a from the other end of the gate electrode 8, being electrically connected to the n<sup>-</sup> type semiconductor region 10a (LDD (Lightly Doped Drain) structure). The n<sup>-</sup> type semiconductor region 10a and the n<sup>+</sup> type semiconductor region 10b may be regions which function as the drains (outputs) of the nMOSQn and may be formed by ion-implanting an impurity, such as phosphorous (P), into the corresponding p type well PWL.

[0049] In the present exemplary embodiment, p<sup>++</sup> type semiconductor regions 11a may be formed in the epitaxial layer 1EP for the region for forming each nMOSQn so as to make contact with the n<sup>+</sup> type semiconductor regions 9 and 10. The p<sup>++</sup> type semiconductor regions 11a may be provided by introducing, for example, boron (B), and may be formed so as to surround each nMOSQn as viewed in its plane and formed so as to extend from the main surface of the epitaxial layer 1EP to the substrate 1S, as viewed in its section. In the present embodiment, the n<sup>+</sup> type semiconductor region 9 for the source of each nMOSQn may be electrically connected to its corresponding p<sup>++</sup> type semiconductor region 11a through a plug PL1 and electrically connected to the low resistance p<sup>+</sup> type substrate 1S through the p<sup>++</sup> type semiconductor region

11a. As will be described later, the substrate 1S may be electrically connected to wirings of a module board with the IC chip 1C packaged thereon, through an electrode 12 formed over the whole back surface of the substrate 1S and electrically connected to a reference potential (e.g., ground potential GND, that is 0V: fixed potential) through the wirings. That is, the substrate 1S may be used as a ground portion common to the plurality of nMOSQn formed in the IC chip 1C.

[0050] An equivalent circuit illustrative of this is seen in FIG. 7, where nMOSQn1 and Qn2 of two amplifying stages 2A1 and 2A2 (or amplifying stages 2B1 and 2B2) of the same power amplifier circuit 2A (or power amplifier circuit 2B) are shown. Signs G1 and G2 may indicate gate electrodes 8 of the MOSQn1 and Qn2. Since sources S1 and S2 (each corresponding to the n+ type semiconductor region 9) of the two nMOSQn1 and Qn2 may be electrically connected to a ground potential GND via the p++ type semiconductor regions 11a and the p<sup>+</sup> type substrate 1S, the power amplifier circuit may have resistive components R11 and R21 of the p++ type semiconductor regions 11a and resistive components R12, R22 and R3 of the p+ type substrate 1S. Since the resistivity of a substrate for the normal CMOS•LSI (Complementary MOS•Large Scale Integrated circuit) may be high, such as multiples of 10  $\Omega$ cm, the resistive components R11, R21, R12, R22 and R3 may become high if such a configuration as described in the present embodiment 1 is taken, and signal gain of the source S1 of the nMOSQn1 with respect to the source S2 of the nMOSQn2 may be produced. Therefore, interference may occur between the nMOSQn1 and Qn2, oscillations and a gain reduction may occur, resulting in degradation of input/output isolation. On the other hand, since the resistance of the substrate 1S may be low in the present embodiment, the resistive components R21, R22 and R3 may be brought close to zero (0). In other words, the sources S1 and S2 of the two nMOSQn1 and Qn2 may become equivalent to the fact that they are both directly connected to a stable ground. It may therefore be possible to avoid occurrence of interference between connected elements in the substrate 1S. For example, crosstalk between each of nMOSQn3 of the final-stage amplifying stages 2A3 and 2B3 and each of the amplifying stages 2A1, 2A2, 2B1 and 2B2 corresponding to the first and second stages and the peripheral circuit 3 may be reduced. That is, since the characteristics of isolation among the nMOSQn1 through Qn3 of the respective amplifying stages 2A1 through 2A3 and 2B1 through 2B3 may be improved, oscillations may be suppressed and the stability of amplifying characteristics of the nMOSQn1 through Qn3 may be enhanced. This means that similar isolation characteristics may be obtained not only among the amplifying stages 2A1 through 2A3 and 2B1 through 2B3 but also among other circuit elements, and crosstalk between the circuit elements may be reduced.

[0051] Included in the present invention are connections among the nMOSQn1 and Qn2, inductors L1 and capacitors C1, as shown in FIGS. 5 and 6. The plug PL1 connected to the n<sup>+</sup> type semiconductor region 9 for the source of the pre-stage nMOSQn1 may be electrically connected to its corresponding first layer wiring M11. The gate electrode 8 of the nMOSQn1 may be electrically connected to its corresponding second layer wiring M21 (M) via a plug PL2 and a first layer wiring M12 (M). The second layer wiring M21 may be a wiring for the input of the nMOSQn1. The n<sup>+</sup> type semiconductor region 11 for the drain of the nMOSQn1 may be electrically connected to its corresponding first layer wiring

M13~(M) via a plug PL3. The first layer wiring M13~may be electrically connected to one end of its corresponding inductor L1.

[0052] The inductor L1 may be formed of, for example, a spiral second layer wiring M22. The outer periphery of the inductor L1 may be surrounded by a first layer wiring M14, a second layer wiring M23, plugs PL4 and p++ type semiconductor regions 11b for shielding. The first layer wiring M14, the second layer wiring M23, the plugs PL4 and the p<sup>++</sup> type semiconductor regions 11b may be electrically connected to one another (insulated from the inductor L1). Further, they may be electrically connected to the low resistance substrate 1S via the  $p^{++}$  type semiconductor regions 11b and may be set to the ground potential GND. Thus, it may be possible to suppress or prevent leakage of a magnetic field developed in the inductor L1 into the outside. Since the coupling between the inductor L1 and each nMOSQn, or the like, provided may be suppressed or prevented, the influence of external crosstalk may be suppressed or prevented. The other end of the inductor L1 may be electrically connected to its corresponding upper electrode C1a of the capacitor C1 via a second layer wiring M24 (M).

[0053] A lower electrode C1b may be provided in a wiring layer below the upper electrode C1a of the capacitor C1 so as to be opposite to the upper electrode C1a with an insulating film interposed therebetween. The lower electrode C1b may be electrically connected to its corresponding p++ semiconductor region 11c via a plug PL5. Further, the lower electrode C1b may be electrically connected to the low resistance p+ type substrate 1S via the  $p^{++}$  type semiconductor region 11c. The outer periphery of the capacitor C1 may also be surrounded by a first layer wiring M15, second layer wiring M25, plugs PL6 and  $p^{++}$  type semiconductor regions 11d for shielding. The first layer wiring M15, the second layer wiring M25, the plugs PL6 and the p<sup>++</sup> type semiconductor regions 11d for the shielding may be electrically connected to one another (insulated from the capacitor C1). Further, they may be electrically connected to the low resistance substrate 1S via the  $p^{++}$  type semiconductor regions 11d and may be set to the ground potential GND. Thus, since the coupling between the capacitor C1 and each nMOSQn or the like provided thereoutside may be suppressed or prevented, the influence of external crosstalk may be suppressed or prevented. Accordingly, the Q value of the capacitor C1 placed over the substrate 1S may be set high. The upper electrode C1a of the capacitor C1 may be electrically connected to its corresponding gate electrode 8 of the nMOSQn2 via a second layer wiring M26 (M). Incidentally, the plugs PL1 through PL6 may be respectively formed of a metal, such as tungsten, or the like. Also, the first layer wirings M11 through M15 and the second layer wirings M21 through M26 may be respectively formed of a metal with, for example, aluminum (Al) or copper (Cu), as a main wiring material. The p<sup>++</sup> type semiconductor regions 11b through 11d may be formed simultaneously upon the process of forming the p++ type semiconductor regions 11a. [0054] Next, FIG. 8 shows an overall plan view of an example of an RF power module PM in which the IC chip 1C may be mounted on a module board MCB. FIG. 9 is a crosssectional view of a surface cut along the horizontal direction of the power module PM shown in FIG. 8. FIG. 10 shows a circuit diagram of the power module shown in FIGS. 8 and 9. Incidentally, the chip mounting surface of the module board MCB is shown in FIG. 8 so as to be brought into sight with an

encapsulating member being eliminated therefrom.

[0055] The IC chip 1C may be mounted over a main surface of the module board MCB in a state of being held in a recess called "cavity CBT" formed over the main surface of the module board MCB in a state in which the back surface of the substrate 1S may be being directed to the main surface of the module board MCB. The IC chip 1C may be placed slightly near the input (left side in FIG. 8) as viewed from the center of the main surface of the module board MCB. A region on the output side of the main surface of the module board MCB may be wider than a region on the input side thereof. Thus, since an output matching circuit placed in the module board MCB of the RF power module PM may be designed to a low loss, the output loss of the RF power module PM may be lessened and hence a high output may be fetched out.

[0056] Bonding pads Pin and Pout of the IC chip 1C are electrically connected to transmission lines 15a (15a1 through 15a5), 15b (15b1 through 15b5) and 15c over the main surface of the module board MCB through bonding wires BW. The transmission lines 15a1 and 15b1 connected via the bonding wires BW to their corresponding gate electrodes (inputs) of the amplifying stages 2A1 and 2B1, corresponding to the first stage may be electrically connected to their corresponding input terminals 17a and 17b via capacitors Cm1 and Cm2. The transmission lines 15a2 and 15b2 electrically connected via the bonding wires BW to their corresponding drains (outputs) of the amplifying stages 2A1 and 2B1, each corresponding to the first stage may be electrically connected to their corresponding power supply terminals 18a1 and 18b1 on the high potential side, and may be electrically connected to a ground potential GND via capacitors Cm3 and Cm4 placed in the vicinity of the power supply terminals 18a1 and 18b1. The transmission lines 15a3 and 15b3 electrically connected via the bonding wires BW to their corresponding drains (outputs) of the amplifying stages 2A2 and 2B2, each corresponding to the second stage may be electrically connected to their corresponding power supply terminals 18a2 and 18b2 on the high potential side and electrically connected to the ground potential GND via capacitors Cm5 and Cm6 disposed in the neighborhood of the power supply terminals 18a2 and 18b2. The transmission lines 15a4 and 15b4 electrically connected via the bonding wires BW to their corresponding drains (outputs) of the amplifying stages 2A3 and 2B3 each corresponding to the final stage may be electrically connected to their corresponding power supply terminals 18a3 and 18b3 on the high potential side and electrically connected to the ground potential GND via capacitors Cm7 and Cm8 placed in the vicinity of the power supply terminals 18a3 and 18b3. Further, the transmission lines 15a5 and 15b5 electrically connected via the bonding wires BW to their corresponding drains (outputs) of the amplifying stages 2A3 and 2B3 each corresponding to the final stage may be electrically connected to their corresponding output terminals 19a and 19b via capacitors Cm9 and Cm10, and may be electrically connected to the ground potential GND via capacitors Cm11 and Cm12 placed in the middle of their lines. The transmission line 15c electrically connected to its corresponding control bonding pad Pin of the peripheral circuit 3 via a bonding wire may be electrically connected to a control terminal 20. Incidentally, each of the bonding wires BW may be constituted of a thin line, such as gold (Au), and functions as an inductor. Also the transmission lines 15a and 15b, respectively, may function as impedance matching inductors. The capacitors Cm1 through Cm12 may function as impedance matching capacitors and may be configured as chip parts.

[0057] On the other hand, the electrode 12 over the back surface of the IC chip 1C may be bonded to a chip mounting electrode 21 at the bottom face of the cavity CBT of the module board MCB. Electrode 21 may be electrically and thermally bonded to an electrode 23G over the back surface of the module board MCB via conductors lying within a plurality of thermal vias 22. The electrode 23G may be supplied with a reference potential (e.g., ground potential GND, i.e., about 0V). That is, the reference potential supplied to the electrode 23G over the back surface of the module board MCB may be supplied to the low resistance substrate 1S through the thermal vias 22 and the electrode 21. However, heat generated upon the operation of the IC chip 1C may be transferred via the electrode 21 and the thermal vias 22 from the back surface of the substrate 1S to the electrode 23G placed over the back surface of the module board MCB, from which the heat may be dissipated. Electrodes 23S located near the outer periphery of the back surface of the module board MCB may indicate signal electrodes. Incidentally, the module board MCB may have a multi-layered wiring structure formed by laminating a plurality of insulator plates and integrating them. Although the insulator plates may be respectively made of ceramics, such as alumina (aluminum oxide: Al<sub>2</sub>O<sub>3</sub> and dielectric constant=9 to 9.7) low in dielectric loss up to, for example, a millimeter wave region, the present invention is not limited to it. Various changes may be made thereto and a glass epoxy resin or the like may be used.

[0058] As seen in FIG. 11, an example of a digital cellular phone system DPS using the RF power module PM according to the present invention is shown. Sign ANT in FIG. 11 may indicate a signal wave transmitting/receiving antenna; reference numeral 25 may indicate a frontend module; reference numeral 26 may indicate the baseband circuit, which may convert a voice or audio signal to a baseband signal, may convert a receive signal to an audio signal and may generate a modulation scheme switching signal and a baseband switching signal; reference numeral 27 may indicate a modulator-demodulator, which may down-convert the receive signal to demodulate it, thereby generating a baseband signal and may modulate a transmit signal; and FLT1 and FLT2 may indicate filters which may eliminate noise and an interference wave from the receive signal, respectively. The filter FLT1 may be used for GSM and the filter FLT2 may be used for DCS. The baseband circuit 26 may include of a plurality of semiconductor integrated circuits, such as a DSP (Digital Signal Processor), a microprocessor, a semiconductor memory, etc., for example. The frontend module 25 may include impedance matching circuits MN1 and MN2, low pass filters LPF1 and LPF2, switch circuits 28a and 28b, capacitors C5 and C6 and a duplexer 29. The impedance matching circuits MN1 and MN2 may be circuits that are connected to transmission output terminals of the RF power module PM to perform impedance matching. The low pass filters LPF1 and LPF2 may be circuits which attenuate higher harmonics; the switch circuits 28a and 28b may be transmission/reception changeover switch circuits; the capacitors C5 and C6 may be elements which cut dc components from the receive signal, and the duplexer 29 may be a circuit which perform branching into a signal lying in the GSM900 band and a signal lying in the DCS1800 band. These circuits and elements may be mounted on one wiring board so as to be configured as a module. Incidentally, select or changeover signals CNT1 and CNT2 of the switch circuits 28a and 28b may be supplied from the baseband circuit 26.

[0059] As seen in FIG. 12, a packaged example of the RF power module employed in the digital cellular phone system DPS shown in FIG. 11 is shown. The motherboard 30 may comprise, for example, a printed wiring board, or the like, having a multi-layered wiring structure. The RF power module PM and a plurality of chip parts 31 may be mounted over a main surface of the motherboard 30. The RF power module PM may be mounted over the motherboard 30 in a state in which the electrodes 23G and 23S, and the like, placed over the back surface of the module board MCB may be being directed to the main surface of the motherboard 30. The electrodes 23G and 23S, and the like, of the RF power module PM may be connected to their corresponding wiring patterns of the motherboard 30 via jointing materials 32, such as solder, for example. Incidentally, the main surface of the mother board MCB of the RF power module PM may be covered with an encapsulating member 33 made of, for example, silicon rubber, or the like. Thus, the IC chip 1C and the like placed over the main surface of the module board MCB may be sealed with the encapsulating member 33.

[0060] In another exemplary embodiment of the present invention, ground bonding pads may be laid out among output bonding pads of adjacent amplifying stages in the same system of an IC chip.

[0061] As seen in FIG. 13, one example of an overall plan view of the IC chip 1C according to the present embodiment is shown. In the present embodiment, ground bonding pads Pg may be disposed among output bonding pads Pout of a plurality of adjacent amplifying stages 2A1 through 2A3 and 2B1 through 2B3 in respective power amplifier circuits 2A and 2B provided within the IC chip 1C. The ground bonding pads Pg may be pads which supply a reference potential (e.g., ground potential GND: 0V) to the IC chip 1C. Thus, since the feedback of a signal by emission from a next-stage amplifying element to a pre-stage amplifying element after signal amplification may be lessened, the suppression of oscillations and stabilization of amplifying characteristics may be achieved.

[0062] As seen in FIG. 14, an overall plan view of one example in which the IC chip 1C shown in FIG. 13 may be mounted over a module board MCB to configure an RF power module PM is shown. A chip mounting surface of the module board MCB may be shown so as to be brought into sight with an encapsulating member being eliminated therefrom. The ground bonding pads Pg may be electrically connected to their corresponding ground terminals 35 of the module board MCB through bonding wires BW. The reference potential (e.g., ground potential GND: 0V) may be supplied to the ground terminals 35. Owing to the provision of such a configuration, power radiated into space upon the operation of the RF power module PM may be absorbed by the bonding wires BW each electrically connected to the bonding pad Pg and may be brought to the ground state, so that the power may be greatly attenuated. Therefore, it may be possible to achieve suppression of oscillations and stabilization of amplifying characteristics.

[0063] In yet another exemplary embodiment of the present invention, a modification illustrative of the layout of input and output bonding pads of adjacent amplifying stages in the same system of an IC chip may be made.

[0064] As seen in FIG. 15, an overall plan view of the IC chip according to the present invention is shown. In an exemplary embodiment, input and output bonding pads Pin and Pout of a plurality of adjacent amplifying stages 2A1 through 2A3 and 2B1 through 2B3 may be laid out in respective power amplifier circuits 2A and 2B lying within the IC chip 1C so as to be reversed by 180°. In the example shown in FIG. 15, the output bonding pads Pout of the amplifying stages 2A2 and 2B2, each corresponding to a second stage, may be disposed near the center of the IC chip 1C, and the input bonding pads Pin thereof may be laid out in the neighborhood of the sides of the IC chip 1C. In such a configuration, interstage wirings M for connecting the input bonding pads Pin of the amplifying stages 2A1 through 2A3 and 2B1 through 2B3 adjacent to one another and the output bonding pads Pout thereof may extend substantially linearly without bending. In such a configuration, the interstage wirings M may be shortened, and the interstage wirings M and interstage matching circuits 2AM2, 2AM3, 2BM2 and 2BM3 may be located away from the output bonding pads Pout of the next-stage amplifying stages as compared with exemplary embodiments described herein. Therefore, it may be possible to reduce crosstalk from the next-stage amplifying stages to the interstage wirings M and the interstage matching circuits 2AM2, 2AM3, 2BM2 and 2BM3. Thus, it may be possible to achieve suppression of oscillations and stability of amplifying characteristics.

[0065] As seen in FIG. 16, an overall plan view of an aspect of the present invention is shown, in which the IC chip 1C shown in FIG. 15 may be mounted over a module board MCB to configure an RF power module PM. In FIG. 16, a chip mounting surface of the module board MCB may be shown so as to be brought into sight with an encapsulating member being eliminated therefrom. Since the output bonding pads Pout of the amplifying stages 2A2 and 2B2, each corresponding to the second stage may be placed near the center of the IC chip 1C in the present embodiment as described above, the lengths of power supply bonding wires BW for connecting the output bonding pads Pout of the amplifying stages 2A2 and 2B2, each corresponding to the second stage, and power supply transmission lines 15a3 and 15b3 of the module board MCB, may be set longer than those of other bonding wires BW. Therefore, inductance components for power lines to the amplifying stages 2A2 and 2B2, each corresponding to the second stage, may be increased by means of the bonding wires BW. Also, the lengths of the power supply transmission lines 15a3 and 15b3 placed over the module board MCB may be shortened as compared with other exemplary embodiments described herein. Thus, a reduction in the overall size of the RF power module PM may be promoted.

[0066] In another exemplary embodiment of the present invention, the layouts of power amplifier circuits in different systems of an IC chip may be opposite in direction to each other. As may be seen in FIG. 17, an overall plan view of an IC chip 1C according to the present invention is shown. In the present exemplary embodiment, power amplifier circuits 2A and 2B in different systems provided within an IC chip 1C may be disposed so as to be opposite in input/output direction to each other. In particular, amplifying stages 2A3 and 2B3, each corresponding to a final stage of the power amplifier circuits 2A and 2B of the different systems, may be disposed in the vicinity of diagonally-located ends of the IC chip 1C so as to be point-symmetric with each other. Thus, since the distance between the final amplifying stages 2A3 and 2B3 of the power amplifier circuits 2A and 2B of the different sys-

tems may be made long, crosstalk (emission or interference) from, for example, the operated power amplifier circuit to the non-operated power amplifier circuit, may be suppressed in a manner similar to previously described exemplary embodiments, and the unnecessary occurrence of an output from the power amplifier circuit being in non-operation may be suppressed. Even if the power amplifier circuits 2A and 2B different in system are provided in the same IC chip 1C, the crossband isolation characteristic between the power amplifier circuits 2A and 2B may be improved.

[0067] Although the exemplary embodiments described herein have explained the case in which the present invention may be applied to the dual band system capable of handling the radio waves lying in the two frequency bands of GSM900 and GSM1800, the present invention may also be applied to a triple band system capable of handling radio waves lying in three frequency bands of GSM900, GSM1800 and GSM1900, for example. Also, the present invention may additionally handle an 800 MHz band and an 850 MHz band.

[0068] Although the above description has principally been described as applied to digital cellular phone systems, the present invention may also be applied to, for example, a mobile information processing apparatus, such as PDA (Personal Digital Assistants), or the like, having a communication function and an information processing apparatus similar to a personal computer, or the like, having a communication function. Further, the semiconductor device according to the present invention may be further applied to a semiconductor device having power amplifier circuits of plural systems.

**[0069]** Those of ordinary skill in the art may recognize that many modifications and variations of the present invention may be implemented without departing from the spirit or scope of the invention. Thus, it is intended that the present invention covers the modifications and variations of this invention provided they come within the scope of the appended claims and their equivalents.

- 1. (canceled)

- 2. A radio frequency power module, comprising:

- a module board; and

- a semiconductor chip comprising:

- a first power amplifier circuit for first frequency band, and including a first amplifying stage, a second amplifying stage and a third amplifying stage;

- a second power amplifier circuit for a second frequency band which is different from the first frequency band, and including a first amplifying stage, a second amplifying stage and a third amplifying stage;

- a control circuit providing a bias voltage to the first to third amplifying stages of the first power amplifier and the first to third amplifying stages of the second power amplifier;

- a first input terminal electrically coupled to the first amplifier circuit;

- a first output terminal electrically coupled to the first amplifier circuit;

- a second input terminal electrically coupled to the second amplifier circuit; and

- a second output terminal electrically coupled to the second amplifier circuit.

- A radio frequency power module according to claim 2, wherein the control circuit includes a bias circuit which provides the bias voltage.

- 4. A radio frequency power module according to claim 3, wherein the bias circuit is electrically coupled to inputs of the first to third amplifying stages of the first power amplifier, and electrically coupled to inputs of the first to third amplifying stages of the second power amplifier.

- A radio frequency power module according to claim 4, wherein the semiconductor chip is composed of laterally diffused MOSFETs.

- A radio frequency power module according to claim 5, wherein the semiconductor chip is mounted over the module board.

- 7. A radio frequency power module according to claim 6, further comprising:

- a first matching circuit electrically coupled between the first amplifying stage and the second amplifying stage of the first power amplifier; and

- a second matching circuit electrically coupled between the first amplifying stage and the second amplifying stage of the second power amplifier.

- **8**. A radio frequency power module for multiple frequency bands, comprising:

- a module board; and

- a semiconductor chip mounted over the module board, the semiconductor chip comprising:

- a first amplifier circuit for a first frequency band;

- a second amplifier circuit for a second frequency band which is different from the frequency of the first frequency band; and

- a control circuit controlling the first and second amplifier circuits, and including a bias circuit which provides a bias voltage to the first and second amplifier circuits;

- wherein the semiconductor chip includes a first surface having a first side and a second side opposite the first side,

- wherein the first amplifier circuit is arranged closer to the first side than the second side and arranged along the first side in plan view,

- wherein the second amplifier circuit is arranged closer to the second side than the first side and arranged along the second side in plan view,

- wherein the first power amplifier circuit includes a first amplifying stage, a second amplifying stage and a third amplifying stage; and

- wherein the second power amplifier circuit includes a first amplifying stage, a second amplifying stage and a third amplifying stage.

- A radio frequency power module according to claim 8, wherein the semiconductor chip is composed of laterally diffused MOSFETs.

- 10. A radio frequency power module according to claim 9, wherein the bias circuit is electrically coupled to inputs of the first to third amplifying stages of the first power amplifier, and electrically coupled to inputs of the first to third amplifying stages of the second power amplifier.

- $11.\,\mathrm{A}$  radio frequency power module according to claim 10, further comprising:

- a first matching circuit electrically coupled between the first amplifying stage and the second amplifying stage of the first power amplifier; and

- a second matching circuit electrically coupled between the first amplifying stage and the second amplifying stage of the second power amplifier,

- wherein the first matching circuit and the second matching circuit are mounted over the module board.

\* \* \* \* \*