(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5539029号

(P5539029)

(45) 発行日 平成26年7月2日(2014.7.2)

(24) 登録日 平成26年5月9日(2014.5.9)

(51) Int.Cl.

H01L 27/146 (2006.01)

H04N 5/374 (2011.01)

F 1

H01L 27/14

H04N 5/335 740

請求項の数 6 (全 10 頁)

(21) 出願番号 特願2010-123297 (P2010-123297)

(22) 出願日 平成22年5月28日 (2010.5.28)

(65) 公開番号 特開2011-249680 (P2011-249680A)

(43) 公開日 平成23年12月8日 (2011.12.8)

審査請求日 平成25年5月17日 (2013.5.17)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 固体撮像装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

電荷を蓄積する蓄積領域を含む光電変換素子と、前記蓄積領域に蓄積された電荷を電荷電圧変換部に転送するためのチャネルを形成する転送ゲートとを含む複数の画素が半導体基板に形成され、前記蓄積領域が、前記蓄積領域に対応する前記転送ゲートの下まで延びていて、前記複数の画素が、隣接するN個の画素 (Nは2以上の自然数)を各々が含む、複数の画素グループで構成され、各画素グループにおいて、N個の画素のそれぞれの前記チャネルによる電荷の転送方向が相互に遠ざかる方向であるように、前記蓄積領域と前記転送ゲートとが配された固体撮像装置の製造方法であって、

各画素グループに対して1つの開口を有するレジストパターンを形成するレジストパターン形成工程と、

各画素グループにおけるN個の画素のそれぞれの前記転送ゲートの下にイオンが注入されるようなN個のイオン注入方向で、前記開口を通して前記半導体基板にイオンを注入することによって、各画素グループにおけるN個の画素の前記蓄積領域を形成する蓄積領域形成工程と、

を含み、

前記N個のイオン注入方向のそれぞれが、各画素グループにおけるN個の画素のうち当該イオン注入方向に対応する少なくとも1つの画素の前記転送ゲートの下にイオンが注入される方向であることを特徴とする固体撮像装置の製造方法。

## 【請求項 2】

10

20

前記蓄積領域形成工程において、前記N個のイオン注入方向でのイオンの注入は、イオン注入方向の互いに異なるN回のイオンの注入によって行われる、

ことを特徴とする請求項1に記載の固体撮像装置の製造方法。

【請求項3】

前記転送ゲートのゲート幅に沿った方向をX軸、前記転送ゲートのゲート長に沿った方向をY軸、前記半導体基板の表面の法線をZ軸とし、XZ平面と前記イオン注入方向とのなす角度をθ、前記レジストパターンの高さをH、前記レジストパターンの前記開口のY軸方向における幅をL、前記レジストパターンの前記開口に露出した2つの前記転送ゲートの間の距離をWとしたときに、

$$L / 2 < H \cdot \tan \theta < (L + W) / 2$$

10

を満たすことを特徴とする請求項1又は2に記載の固体撮像装置の製造方法。

【請求項4】

各画素グループにおけるN個の画素の前記蓄積領域を相互に分離する半導体領域を形成する工程を更に含む、

ことを特徴とする請求項1乃至3のいずれか1項に記載の固体撮像装置の製造方法。

【請求項5】

N=2又は4である、

ことを特徴とする請求項1乃至4のいずれか1項に固体撮像装置の製造方法。

【請求項6】

各画素グループを構成する画素が相互に面对称性を有する、

20

ことを特徴とする請求項1乃至5のいずれか1項に記載の固体撮像装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、固体撮像装置の製造方法に関する。

【背景技術】

【0002】

特許文献1には、チャネル領域およびゲート電極を含むMOSトランジスタと、該ゲート電極の下で該チャネル領域に接したフォトダイオード領域とを含む画素を有する固体撮像装置の製造方法が開示されている。特許文献2には、複数の画素を面对称に配置したセンサアレイが開示されている。

30

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008-060380号公報

【特許文献2】特開2006-222427号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1の方法を特許文献2に記載のセンサアレイの製造に適用すると、隣接する画素の不純物領域を形成するために、互いに異なる方向からイオン注入を実施することになる。この場合、通常は、それぞれのイオン注入において互いに異なるレジストパターンを形成することになるであろう。ところが、フォトダイオード領域を形成するためのイオン注入の回数分のレジストパターンを形成すると、工程数が増加したり、レジストパターン間の位置合わせ誤差による画素の特性のばらつきなどの問題が発生する。

40

【0005】

本発明は、固体撮像装置の製造の簡略化および/または画素の特性のばらつきの低減に有利な製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

50

本発明の 1 つの側面は、電荷を蓄積する蓄積領域を含む光電変換素子と、前記蓄積領域に蓄積された電荷を電荷電圧変換部に転送するためのチャネルを形成する転送ゲートとを含む複数の画素が半導体基板に形成され、前記蓄積領域が、前記蓄積領域に対応する前記転送ゲートの下まで延びていて、前記複数の画素が、隣接する  $N$  個の画素 ( $N$  は 2 以上の自然数) を各々が含む、複数の画素グループで構成され、各画素グループにおいて、 $N$  個の画素のそれぞれの前記チャネルによる電荷の転送方向が相互に遠ざかる方向であるように、前記蓄積領域と前記転送ゲートとが配された固体撮像装置の製造方法であって、各画素グループに対して 1 つの開口を有するレジストパターンを形成するレジストパターン形成工程と、各画素グループにおける  $N$  個の画素のそれぞれの前記転送ゲートの下にイオンが注入されるような  $N$  個のイオン注入方向で、前記開口を通して前記半導体基板にイオンを注入することによって、各画素グループにおける  $N$  個の画素のそれぞれの前記蓄積領域を形成する蓄積領域形成工程と、を含み、前記  $N$  個のイオン注入方向のそれぞれが、各画素グループにおける  $N$  個の画素のうち当該イオン注入方向に対応する少なくとも 1 つの画素の前記転送ゲートの下にイオンが注入される方向である。

【発明の効果】

【0007】

本発明によれば、固体撮像装置の製造の簡略化および / または画素の特性のばらつきの低減に有利な製造方法が提供される。

【図面の簡単な説明】

【0008】

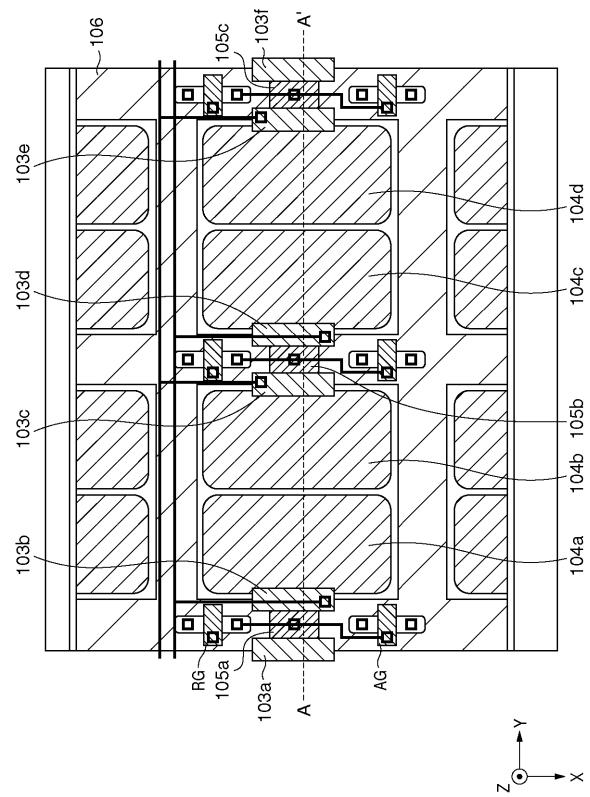

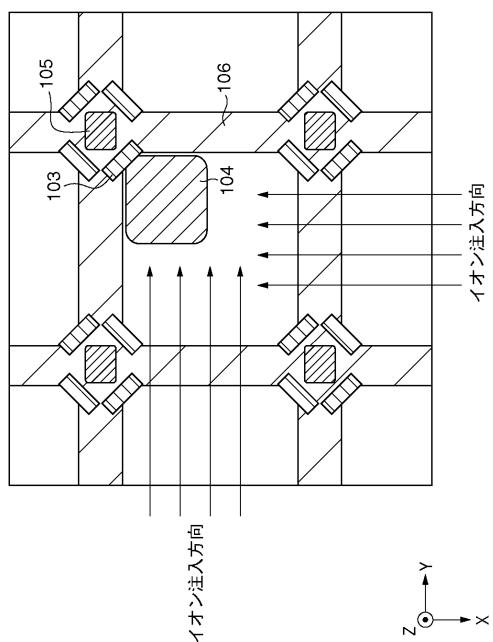

【図 1】本発明の第 1 実施形態の固体撮像装置およびその製造方法を説明するためのレイアウト図である。

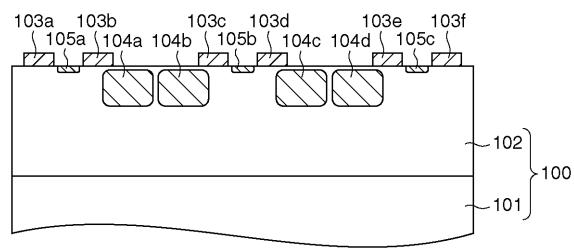

【図 2】本発明の第 1 実施形態の固体撮像装置およびその製造方法を説明するための断面図である。

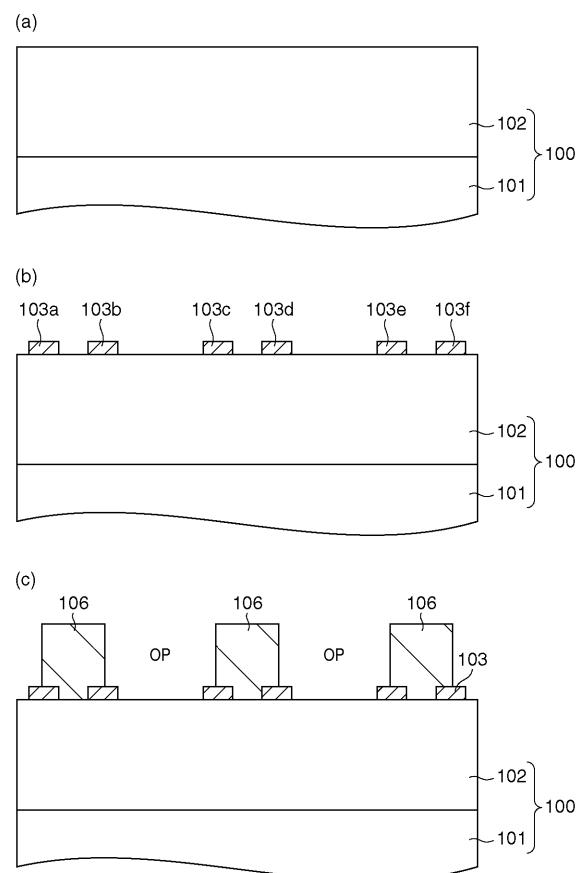

【図 3】本発明の第 1 実施形態の固体撮像装置およびその製造方法を説明するための断面図である。

【図 4】本発明の第 1 実施形態の固体撮像装置およびその製造方法を説明するための断面図である。

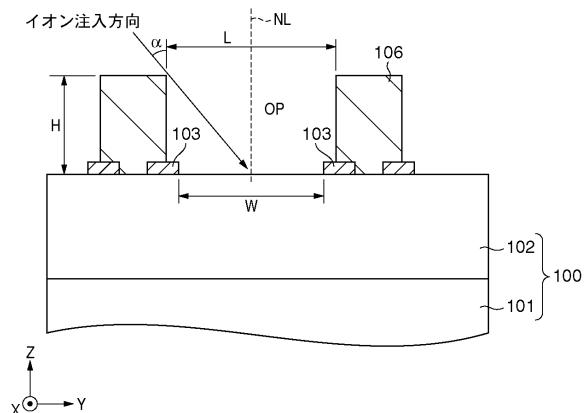

【図 5】注入工程における望ましい条件について説明するための図である。

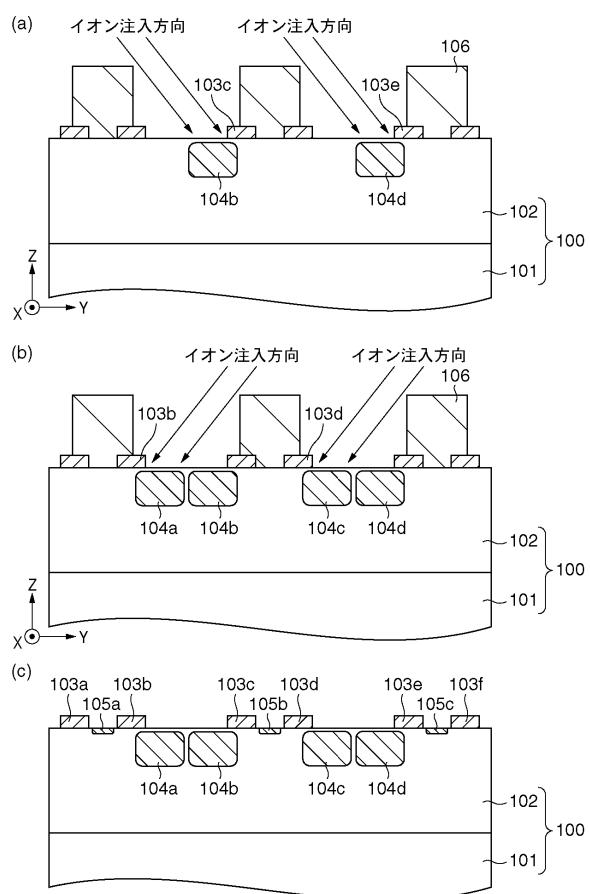

【図 6】本発明の第 2 実施形態の固体撮像装置およびその製造方法を説明するための断面図である。

【図 7】本発明の第 3 実施形態の固体撮像装置およびその製造方法を説明するためのレイアウト図である。

【図 8】本発明の第 3 実施形態の固体撮像装置およびその製造方法を説明するためのレイアウト図である。

【図 9】本発明の第 3 実施形態の固体撮像装置およびその製造方法を説明するためのレイアウト図である。

【発明を実施するための形態】

【0009】

本発明の実施形態の固体撮像装置は、複数の画素が二次元状に配置された画素アレイ、該画素アレイにおける行を選択する行選択回路、該画素アレイにおける列を選択する列選択回路、該画素アレイから信号を列信号線を介して読み出す読み出し回路を含みうる。画素アレイ、行選択回路、列選択回路および読み出し回路は、半導体基板に形成される。典型的には、読み出し回路は、該画素アレイにおける該行選択回路によって選択された行の画素の信号を読み出し、該列選択回路は、該読み出し回路によって読み出された 1 行分の画素の信号の中から外部に出力すべき信号を選択する。

【0010】

各画素は、電荷を蓄積する蓄積領域を含む光電変換素子と、該蓄積領域に蓄積された電荷を電荷電圧変換部 (フローティングディフュージョン) に転送するためのチャネルを形成する転送ゲートとを含む。ここで、複数の画素によって電荷電圧変換部が共有されても

10

20

30

40

50

よいし、各画素が電荷電圧変換部を有していてもよい。各画素、または、電荷電圧変換部を共有する複数の画素は、電荷電圧変換部の電圧をリセットするリセットスイッチと、電荷電圧変換部の電圧に応じた信号を列信号線に出力する増幅部とを含みうる。

#### 【0011】

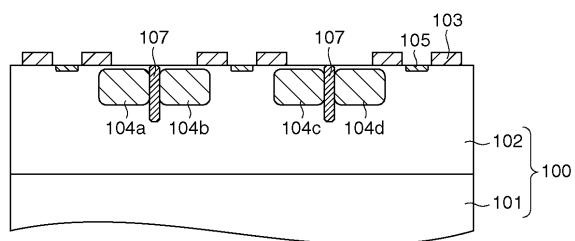

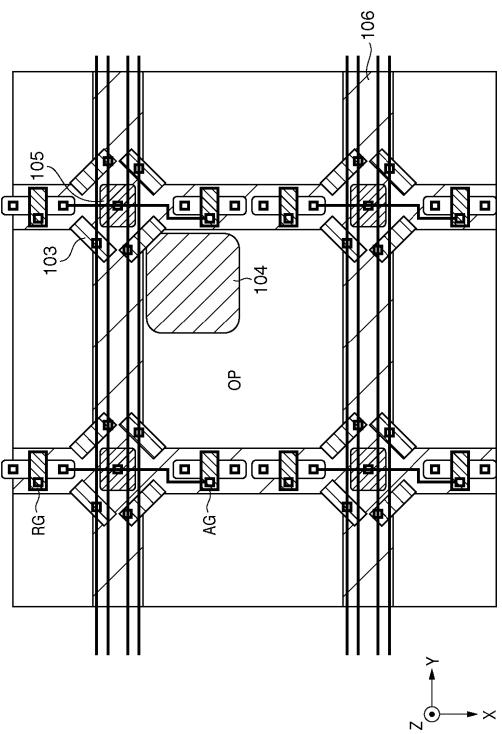

図1は、本発明の第1実施形態の固体撮像装置およびその製造方法を説明するためのレイアウト図である。図2は、図1のA-A'線における断面図である。なお、図1において、レジストパターン106は、転送ゲート103の形成の後に転送ゲート103の上に形成される。第1実施形態の固体撮像装置では、電荷を蓄積する蓄積領域104を含む光電変換素子と、蓄積領域104に蓄積された電荷を電荷電圧変換部105に転送するためのチャネルを形成する転送ゲート103とを含む複数の画素が半導体基板100に形成されている。図面中では、転送ゲート103は、相互に区別するために103a～103fとして、蓄積領域104は、相互に区別するために104a～104fとして、電荷電圧変換部105は、相互に区別するために105a～105cとして記載されている。図1および図2に示す例では、2つの画素によって1つの電荷電圧変換部、1つのリセットスイッチおよび1つの増幅部が共有されている。リセットスイッチは、ゲートRGを有するMOSトランジスタによって構成されうる。増幅部は、ゲートAGを有するMOSトランジスタによって構成されうる。

#### 【0012】

半導体基板100は、例えば、半導体領域101とその上に配置されたウェル領域102とを含みうる。半導体領域101は、第1導電型のシリコン基板でありうる。ウェル領域(或いは、不純物半導体領域)102は、第2導電型でありうる。ウェル領域102の中には、第1導電型の蓄積領域104が形成されうる。ここで、第1導電型がN型、第2導電型がP型であってもよいし、第1導電型がP型、第2導電型がN型であってもよい。半導体基板101の表面(ウェル領域102の表面)の上には酸化膜等の絶縁膜が形成され、該絶縁膜の上には転送ゲート103が形成されている。第1導電型がN型であり第2導電型がP型である場合は、蓄積領域104には電子が蓄積され、第1導電型がP型であり第2導電型がN型である場合は、蓄積領域104には正孔が蓄積される。

#### 【0013】

蓄積領域104は、ウェル領域102における転送ゲート103の下まで延びている。これにより、蓄積領域104の電荷を電荷電圧変換部105に転送するために転送ゲート103に与えるべき電圧を小さく抑えることができ、低電源電圧化が可能になる。蓄積領域104は、その上面が半導体基板100の表面(ウェル領域102の表面)よりも深い位置に配置されることが好ましい。このような構成を有する光電変換素子は、埋め込み型と呼ばれ、半導体基板100の表面と絶縁膜(酸化膜)との界面で生じうる暗電流によるノイズを低減することができる。

#### 【0014】

図1および図2に示す例では、隣接する2つの画素でそれぞれ構成される複数の画素グループが規則的に配列されている。この例では、各画素グループは、2つの電荷蓄積領域104(例えば、104a、104b)と、2つの転送ゲート103(例えば、103b、103c)とを含む。各画素グループにおいて、転送ゲート103(例えば、103b、103c)の下に形成されるチャネルによる電荷の転送方向は、相互に遠ざかる方向である。各画素グループにおいて、それを構成する2つの画素(或いは、2つの蓄積領域104)は、典型的には、相互に対称に配置されうる。また、図1および図2に示す例では、1つの画素グループに属する1つの画素とそれに隣接する1つの画素グループに属する1つの画素とによって1つの電荷電圧変換部、1つのリセットスイッチおよび1つの増幅部が共有されている。このような構成は、画素密度の向上に有利である。

#### 【0015】

図2に示す例では、共通のウェル102と蓄積領域104とによって光電変換素子が形成されている。光電変換素子で発生した電荷は、当該光電変換素子の蓄積領域104に蓄積される。転送ゲート103は、MOSトランジスタのゲートとして機能する。行選択回

路から転送ゲート 103 にアクティブループルの電圧が供給されることによって転送ゲート 103 の下にMOSトランジスタのチャネルが形成され、蓄積領域 103 に蓄積された電荷が該チャネルを通して電荷電圧変換部 105 に転送される。

【0016】

以下、図3、4を参照しながら第1実施形態の固体撮像装置の製造方法を説明する。ここでは、より具体的な例を提供するために、第1導電型がN型であり第2導電型がP型である場合について説明するが、その反対の場合にも本発明は成立する。まず、図3(a)に示す工程において、N型の半導体基板を準備し、該半導体基板にボロンを注入する。これにより、N型の半導体領域 101 の上にP型のウェル領域 102 が配置された半導体基板 100 が得られる。次に、図3(b)に示す工程において、半導体基板 100 の表面(ウェル領域 102 の表面)の上に不図示の絶縁膜(酸化膜)を形成した後、その上にポリシリコン膜を形成する。そして、該ポリシリコン膜をパターニングすることによって転送ゲート 103 を形成する。

【0017】

次に、図3(c)に示すレジストパターン形成工程を実施する。レジストパターン形成工程では、転送ゲート 103 が形成された半導体基板 100 の上にフォトリソグラフィー工程によってレジストパターン 106 を形成する。ここで、レジストパターン 106 は、各画素グループに対して1つの開口OPを有する。図3(c)において、各開口OPは、2画素分の蓄積領域に対応する面積を有する。第1実施形態では、各画素グループは、隣接する2つの画素で構成され、各画素グループは、2つの転送ゲート 103 の下に形成されるチャネルによる電荷の転送方向が相互に遠ざかる方向であるように構成される。

【0018】

次に、図4(a)、(b)に示す蓄積領域形成工程を実施する。まず、図4(a)に示す工程において、転送ゲート 103 の下にイオンが注入されるイオン注入方向で、レジストパターン 106 の各開口OPを通して、各画素グループにおける2つの画素から選択される1つの画素の蓄積領域(ここで、104b、104d。)を形成すべき領域にイオン(例えば、砒素または燐)を注入する。次に、図4(b)に示す工程において、転送ゲート 103 の下にイオンが注入されるイオン注入方向で、レジストパターン 106 の各開口OPを通して、各画素グループにおける2つの画素から選択される他の1つの画素の蓄積領域(ここで、104a、104c。)を形成すべき領域にイオン(例えば、砒素または燐)を注入する。即ち、各画素グループにおける2つの画素の全ての蓄積領域 104 が形成されるようにレジストパターン 106 を用いて2回の注入工程が実施される。ここで、2回の注入工程のそれぞれにおいて、各画素グループにおける2つの画素のうち該当する1つの画素の転送ゲート 103 の下にイオンが注入されるようにイオン注入方向が設定される。

【0019】

図4(a)に示す注入工程におけるイオン注入方向の半導体基板 100 の表面に沿った方向の成分(+Y方向)は、図4(b)に示す注入工程におけるイオン注入方向の半導体基板 100 の表面に沿った方向の成分(-Y方向)の反対でありうる。また、図4(a)に示す注入工程におけるイオン注入方向と図4(b)に示す注入工程におけるイオン注入方向とは、図4(a)、(b)のXZ平面に平行な面を対称面として対称な関係でありうる。ここで、1つの画素グループの2つの転送ゲート 103 は、当該対称面に関して面対称でありうる。このように、2つのイオン注入工程におけるイオン注入方向を対称面に関して対称にするとともに、1つの画素グループの2つの転送ゲート 103 を当該対称面に関して対称にすることにより、画素間の特性ばらつきを低減することができる。また、2つのイオン注入工程で共通のレジストパターン 106 を使用することにより、レジストパターンの形成工程および剥離工程を減らすことができるとともに、レジストパターン同士の位置合わせ誤差による画素間の特性ばらつきの問題を解決することができる。

【0020】

なお、半導体基板の表面の法線に対してイオン注入方向を傾けるイオン注入(以下、斜

10

20

30

40

50

めイオン注入)では、レジストパターンの影になる領域にはイオンが注入されない。よって、画素ごとに開口を有するレジストパターンを使って斜めイオン注入を行うと、光電変換素子の蓄積領域の面積が制限され、飽和電荷量が低下しうる。一方、第1実施形態によれば、2つの画素で構成される各画素グループに対して1つの開口の設けて該開口を通して斜めイオン注入を行うので、光電変換素子の蓄積領域の面積を大きくすることができ、飽和電荷量を改善することができる。

#### 【0021】

上記の2つのイオン注入工程は、同時に実施されてもよい。そのためには、例えば、イオンを発生するイオン源、イオンを輸送するビームライン、イオンを加速する加速管を含むイオン注入機構を2系統有するイオン注入装置を準備すればよい。

10

#### 【0022】

次に、図4(c)に示す工程において、蓄積領域104が形成された半導体基板100の上にレジストパターンを形成し、該レジストパターンの開口を通して半導体基板100(ウェル領域102)にイオンを注入する。これによって、第1導電型の電荷電圧変換部105が形成される。なお、図4(a)、(b)、(c)に示すイオン注入工程は、熱処理工程を伴っていてもよい。

#### 【0023】

以下、図4(a)、(b)における注入工程における望ましい条件について説明する。図5に示すように、転送ゲート103のゲート幅に沿った方向をX軸、転送ゲート103のゲート長方向に沿った方向をY軸、半導体基板100の表面の法線NLをZ軸とし、X-Z平面と蓄積領域104の形成時におけるイオン注入方向とのなす角度(注入角度)をとする。また、レジストパターン106の高さをH、レジストパターン106のY軸方向における開口幅をL、レジストパターン106の開口OPに露出した2つの転送ゲート103間の距離をWとする。このとき、

$$L/2 < H \cdot \tan < (L + W)/2 \quad \dots \quad (1)$$

を満たすことが望ましい。式(1)における $H \cdot \tan < (L + W)/2$ の条件を満たすことにより、半導体基板100に向けて照射されたイオンの少なくとも一部を半導体基板100に到達させること、即ち、蓄積領域103を形成することができる。式(1)における $L/2 < H \cdot \tan$ の条件を満たすことにより、対称性を有する隣接画素間でイオンが注入される領域を空間的に分離することができる。式(1)を満たすためには、画素に対してレジストパターンの高さH、開口幅L、注入角度、転送ゲート103間の距離Wの全部または一部を調整すればよい。

20

#### 【0024】

なお、第1実施形態は、2つの画素が対称に配置されている場合のみならず、電荷の転送方向が相互に遠ざかる方向(例えば、反対方向)である場合に適用可能である。

#### 【0025】

図6を参照しながら本発明の第2実施形態の固体撮像装置およびその製造方法を説明する。なお、第2実施形態として言及しない事項は、第1実施形態に従う。第2実施形態の製造方法は、前述のフォトレジスト106の1つの開口を通して形成される2つの画素(換言すると、1つの画素グループを構成する2つの画素。)のそれぞれの蓄積領域104(例えば、104a、104b)を相互に分離する半導体領域107を形成する工程を含む。半導体領域107は、蓄積領域104の導電型(第1導電型)とは反対の導電型(第2導電型)を有する。半導体領域107は、混色の防止、感度の向上に寄与する。半導体領域107は、特に、相互に異なるイオン注入方向でなされるイオン注入で形成される2つの蓄積領域104が相互にオーバラップする場合、或いは、イオンの拡散によって2つの蓄積領域104が相互にオーバラップする場合に有用である。第2実施形態では、例えばレジストパターン106の高さHが式(1)を満たさない場合においても、隣接する2つの蓄積領域104を相互に分離することができる。

30

#### 【0026】

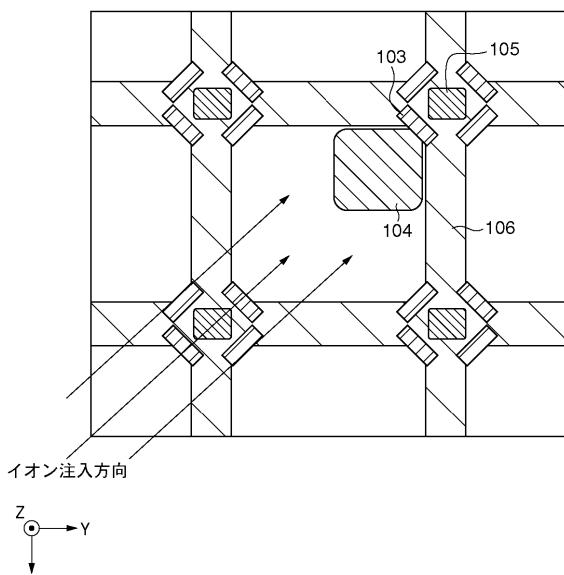

図7～図9を参照しながら本発明の第3実施形態の固体撮像装置およびその製造方法を

40

50

説明する。なお、第2実施形態として言及しない事項は、第1又は第2実施形態に従う。第3実施形態では、レジストパターン106の1つの開口はOPは、4画素分の蓄積領域104に対応する面積を有する。第3実施形態では、各画素グループは、隣接する4つの画素で構成され、各画素グループは、4つの転送ゲート103の下に形成されるチャネルによる電荷の転送方向が相互に遠ざかる方向であるように構成される。図7に示す例では、1つの画素グループを構成する4つの画素の面対称性がX軸に沿った対称面、および、Y軸に沿った対称面に関して成り立つ。第3実施形態では、XZ平面だけでなく、YZ平面にも交差するイオン注入方向を選択することができる。

#### 【0027】

例え、図8に例示するように、転送ゲート103が画素の配列方向に対して斜め方向に延びるように構成されている場合において、XZ平面およびYZ平面の双方に交差するようにイオン注入方向を設定することができる。この場合においても、転送ゲート103の下まで光電変換素子の蓄積領域104を延ばすことができ、電荷の転送性能を向上させることができ。図8に示す例では、1つのレジストパターン106の1つの開口を通して4つのイオン注入方向で半導体基板にイオンを注入することによって1つの画素グループを構成する4つの画素の蓄積領域104を形成することができる。4つのイオン注入方向でのイオン注入は、典型的には、4回のイオン注入でなされうる。

#### 【0028】

XZ平面およびYZ平面の双方に交差するようにイオン注入方向を決定する代わりに、図9に模式的に例示されるように、X軸に平行なイオン注入方向とY軸に平行なイオン注入方向とを別個に実施してもよい。この場合、X軸に平行なイオン注入方向とY軸に平行なイオン注入方向との双方でイオンが注入される領域の不純物濃度が高くなる。この方法においては、第2実施形態における分離用の半導体領域107のように、4つの蓄積領域104を相互に分離するように半導体領域を形成することが好ましい。

#### 【0029】

本発明は、更に、隣接するN個の画素（Nは2以上の自然数）で構成される各画素グループにおいて転送ゲート103の下に形成されるチャネルによる電荷の転送方向が相互に遠ざかる方向である場合にも適用可能である。この場合、各注入工程では、転送ゲートの下にイオンが注入されるイオン注入方向で、レジストパターン106の各開口OPを通して、各画素グループにおけるN個の画素から選択される1つの画素の蓄積領域103を形成すべき領域にイオンが注入される。そして、このような注入工程は、各画素グループにおけるN個の画素の全ての蓄積領域104が形成されるように、選択された画素（即ち、蓄積領域を形成すべき画素）に応じてイオン注入方向を変更しながらN回にわたって実施される。なお、第1～第3実施形態は、Nが偶数である場合の例であるが、Nは奇数であってもよい。ただし、Nが奇数である場合には、レイアウト効率が悪くなるかもしれない。

#### 【0030】

第1～第3実施形態は、複数の画素によって1つの電荷電圧変換部、1つのリセットスイッチおよび1つの増幅部が共有されている。本発明は、このような例に限られるものではなく、画素毎に1つの電荷電圧変換部、1つのリセットスイッチおよび1つの増幅部が配されてもよい。

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 曽田 岳彦

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 今井 聖和

(56)参考文献 特開2006-303328 (JP, A)

国際公開第2006/025079 (WO, A1)

特開平11-274454 (JP, A)

特開平10-321550 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H04N 5/374