【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成19年2月8日(2007.2.8)

【公開番号】特開2005-183686(P2005-183686A)

【公開日】平成17年7月7日(2005.7.7)

【年通号数】公開・登録公報2005-026

【出願番号】特願2003-422762(P2003-422762)

【国際特許分類】

|        |         |           |

|--------|---------|-----------|

| H 01 L | 21/822  | (2006.01) |

| H 01 L | 27/04   | (2006.01) |

| H 01 L | 27/08   | (2006.01) |

| H 01 L | 29/786  | (2006.01) |

| H 01 L | 21/8234 | (2006.01) |

| H 01 L | 27/06   | (2006.01) |

| H 01 L | 21/76   | (2006.01) |

| H 01 L | 21/762  | (2006.01) |

【F I】

|        |       |         |

|--------|-------|---------|

| H 01 L | 27/04 | P       |

| H 01 L | 27/08 | 3 3 1 A |

| H 01 L | 27/08 | 3 3 1 E |

| H 01 L | 29/78 | 6 2 1   |

| H 01 L | 29/78 | 6 1 3 Z |

| H 01 L | 29/78 | 6 1 8 F |

| H 01 L | 27/04 | L       |

| H 01 L | 27/06 | 1 0 2 A |

| H 01 L | 21/76 | L       |

| H 01 L | 21/76 | D       |

【手続補正書】

【提出日】平成18年12月18日(2006.12.18)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

土台となる基板部、該基板部上に配設された埋め込み酸化膜、および該埋め込み酸化膜上に配設されたSOI層を有するSOI基板と、

前記SOI基板上の第1の領域の前記SOI層の主面内に、間に前記SOI層を挟んで配設された複数の第1の素子分離絶縁膜と、

前記第1の領域の前記複数の第1の素子分離絶縁膜上にそれぞれ配設された、複数の抵抗素子と、を備え、

前記複数の第1の素子分離絶縁膜のそれぞれは、少なくとも一部分が前記SOI層を貫通して前記埋め込み酸化膜に達する完全分離構造をなす、半導体装置。

【請求項2】

土台となる基板部、該基板部上に配設された埋め込み酸化膜、および該埋め込み酸化膜上に配設されたSOI層を有するSOI基板と、

前記SOI基板上の第1の領域の前記SOI層の主面内に、間に前記SOI層を挟んで

配設された複数の第1の素子分離絶縁膜と、

前記複数の第1の素子分離絶縁膜の間の前記SOI層上に、それぞれ絶縁膜を介して配設された、複数の抵抗素子と、を備え、

前記複数の第1の素子分離絶縁膜のそれぞれは、少なくとも一部分が前記SOI層を貫通して前記埋め込み酸化膜に達する完全分離構造をなす、半導体装置。

【請求項3】

前記複数の第1の素子分離絶縁膜のそれぞれは、その断面形状において、中央部分は前記完全分離構造をなし、両端部分は、その下部に前記SOI層を有する部分分離構造をなす、併合分離構造を有する、請求項1または請求項2記載の半導体装置。

【請求項4】

前記複数の第1の素子分離絶縁膜のそれぞれは、その断面形状において、全体が前記完全分離構造を有する、請求項1または請求項2記載の半導体装置。

【請求項5】

前記第1の領域の前記SOI層は、完全空乏化状態を可能とする濃度に不純物を含む、請求項1または請求項2記載の半導体装置。

【請求項6】

複数の半導体素子が配設される第2の領域の前記SOI層の主面内に配設された第2の素子分離絶縁膜を備え、

前記複数の第1の素子分離絶縁膜は、前記第2の素子分離絶縁膜の厚さよりも厚い、請求項5記載の半導体装置。

【請求項7】

前記複数の第1の素子分離絶縁膜のそれぞれの平面視形状は、第1の方向に細長く延在する細長形状を有し、

前記複数の第1の素子分離絶縁膜は、前記第1の方向とは直交する第2の方向に並列して配列され、

前記第1の領域の前記SOI層は、前記複数の第1の素子分離絶縁膜の配列間に少なくとも配設される、請求項1または請求項2記載の半導体装置。

【請求項8】

前記第1の領域の前記SOI層は、前記複数の第1の素子分離絶縁膜の前記第1の方向の両端部外側の位置にも配設される、請求項7記載の半導体装置。

【請求項9】

前記第1の領域とは異なる第2の領域に配設されたMOSトランジスタを備え、

前記MOSトランジスタは、第2の領域の前記SOI層上に配設されたゲート絶縁膜を有し、

前記第1の領域の前記SOI層上の前記絶縁膜の厚さは、前記ゲート絶縁膜よりも厚い、請求項2記載の半導体装置。

【請求項10】

前記複数の抵抗素子はポリシリコンで構成される、請求項1または請求項2記載の半導体装置。

【請求項11】

前記SOI基板の上方に配設されたインダクタンス素子をさらに備え、

前記第1の領域は、前記インダクタンス素子の下部に相当する領域である、請求項1または請求項2記載の半導体装置。

【請求項12】

前記SOI層の素子形成領域に設けられるMOSトランジスタと、

前記SOI層に設けられた、部分分離領域とを備え、

前記部分分離領域は、

前記SOI層の上層部に設けられる部分絶縁膜と下層部に存在する前記SOI層の一部である第2導電型の部分絶縁膜下半導体領域とを含み、

前記MOSトランジスタは、

各々が前記S O I層内に選択的に形成される第1導電型のソースおよびドレイン領域と、

前記ソースおよびドレイン領域間の前記S O I層の領域上にゲート酸化膜を介して形成されるゲート電極と、

前記ソースおよびドレイン領域間の前記S O I層の第2導電型の領域であるチャネル形成領域とを備え、

前記部分絶縁膜下半導体領域を介して前記チャネル形成領域に接続された第2導電型のボディ固定領域とを有する、請求項1または請求項2記載の半導体装置。

【請求項13】

土台となる基板部、該基板部上に配設された埋め込み酸化膜、および該埋め込み酸化膜上に配設されたS O I層を有するS O I基板と、前記S O I基板上の第1の領域の前記S O I層の主面内に、間に前記S O I層を挟んで配設された複数の素子分離絶縁膜と、前記第1の領域の前記複数の素子分離絶縁膜上または前記複数の素子分離絶縁膜間の前記S O I層上にそれぞれ配設された、複数の抵抗素子と、前記第1の領域とは異なる第2の領域に配設されたM O Sトランジスタとを備えた半導体装置の製造方法であって、

(a)前記第1の領域の前記S O I層の主面内に、前記複数の素子分離絶縁膜を形成する工程と、

(b)前記第2の領域の前記S O I層内に、イオン注入により前記M O Sトランジスタのしきい値電圧を設定するための不純物を導入する工程と、

(c)前記工程(b)の後に、前記第1および第2の領域に渡るようにポリシリコン層を形成する工程と、

(d)前記第1および第2の領域の前記ポリシリコン層をそれぞれパターニングして、前記複数の抵抗素子および前記M O Sトランジスタのゲート電極を形成する工程と、を備え、

前記工程(b)は、前記第1の領域上をマスクで覆い、前記第1の領域への前記不純物の導入を防止する工程を含む、半導体装置の製造方法。

【請求項14】

(e)前記工程(d)の後に、前記第2の領域の前記S O I層内に、イオン注入により前記M O Sトランジスタのソース・ドレイン層を形成するためのソース・ドレイン不純物を導入する工程をさらに備え、

前記工程(e)は、前記第1の領域上をマスクで覆い、前記第1の領域への前記ソース・ドレイン不純物の導入を防止する工程を含む、請求項13記載の半導体装置の製造方法。

【請求項15】

前記S O I基板の上方に配設されたインダクタンス素子をさらに備え、

前記第1の領域は、前記インダクタンス素子の下部に相当する領域である、請求項13記載の半導体装置の製造方法。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0 0 1 0

【補正方法】変更

【補正の内容】

【0 0 1 0】

そして、このような構造を採用する場合、完全トレンチ分離絶縁膜の形成時にC M P (Chemical Mechanical Polishing)処理を行うと、完全トレンチ分離絶縁膜が所望の研磨量よりも過剰に除去され、完全トレンチ分離絶縁膜の厚みが中央部になるほど薄くなる、いわゆるディッシングが発生する。そして、ディッシングが発生した完全トレンチ分離絶縁膜上に抵抗素子を配設すると、完全トレンチ分離絶縁膜の端縁部近傍に配置される抵抗素子は、寸法異常や形状異常などを引き起こす問題があった。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0015

【補正方法】変更

【補正の内容】

【0015】

上記のように、大きな面積を有するトレンチ分離絶縁膜を形成する際には、ディッシングの発生を防止することが課題であるが、そのために特許文献2のようにトレンチ分離絶縁膜の形成領域に複数のダミー素子領域を分散配置すると抵抗素子を配設することができず、高周波アナログ回路等には不向きな構成となってしまう。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0017

【補正方法】変更

【補正の内容】

【0017】

本発明に係る請求項1記載の半導体装置は、土台となる基板部、該基板部上に配設された埋め込み酸化膜、および該埋め込み酸化膜上に配設されたSOI層を有するSOI基板と、前記SOI基板上の第1の領域の前記SOI層の主面内に、間に前記SOI層を挟んで配設された複数の第1の素子分離絶縁膜と、前記第1の領域の前記複数の第1の素子分離絶縁膜上にそれぞれ配設された、複数の抵抗素子とを備え、前記複数の第1の素子分離絶縁膜のそれぞれは、少なくとも一部分が前記SOI層を貫通して前記埋め込み酸化膜に達する完全分離構造をなしている。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0018

【補正方法】変更

【補正の内容】

【0018】

本発明に係る請求項2記載の半導体装置は、土台となる基板部、該基板部上に配設された埋め込み酸化膜、および該埋め込み酸化膜上に配設されたSOI層を有するSOI基板と、前記SOI基板上の第1の領域の前記SOI層の主面内に、間に前記SOI層を挟んで配設された複数の第1の素子分離絶縁膜と、前記複数の第1の素子分離絶縁膜の間に前記SOI層上に、それぞれ絶縁膜を介して配設された、複数の抵抗素子とを備え、前記複数の第1の素子分離絶縁膜のそれぞれは、少なくとも一部分が前記SOI層を貫通して前記埋め込み酸化膜に達する完全分離構造をなしている。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0019

【補正方法】変更

【補正の内容】

【0019】

本発明に係る請求項13記載の半導体装置の製造方法は、土台となる基板部、該基板部上に配設された埋め込み酸化膜、および該埋め込み酸化膜上に配設されたSOI層を有するSOI基板と、前記SOI基板上の第1の領域の前記SOI層の主面内に、間に前記SOI層を挟んで配設された複数の素子分離絶縁膜と、前記第1の領域の前記複数の素子分離絶縁膜上または前記複数の素子分離絶縁膜間に前記SOI層上にそれぞれ配設された、複数の抵抗素子と、前記第1の領域とは異なる第2の領域に配設されたMOSトランジスタとを備えた半導体装置の製造方法であって、以下の工程(a)ないし(e)を備えている。すなわち、前記第1の領域の前記SOI層の主面内に、前記複数の素子分離絶縁膜を形成する工程(a)と、前記第2の領域の前記SOI層内に、イオン注入により前記MOSトランジスタのしきい値電圧を設定するための不純物を導入する工程(b)と、前記工程(b)の

後に、前記第1および第2の領域に渡るようにポリシリコン層を形成する工程(c)と、前記第1および第2の領域の前記ポリシリコン層をそれぞれパターニングして、前記複数の抵抗素子および前記MOSトランジスタのゲート電極を形成する工程(d)とを備えている。そして前記工程(b)は、前記第1の領域上をマスクで覆い、前記第1の領域への前記不純物の導入を防止する工程を含んでいる。

【手続補正7】

【補正対象書類名】明細書

【補正対象項目名】0020

【補正方法】変更

【補正の内容】

【0020】

本発明に係る請求項1記載の半導体装置によれば、第1の領域の複数の第1の素子分離絶縁膜上には、それぞれ複数の抵抗素子が配設されているので、スパイラルインダクタの下方に対応する領域を有効に利用することができ、装置面積が増大する事なく、かつ高周波アナログ回路等の形成に有利な構成となる。

【手続補正8】

【補正対象書類名】明細書

【補正対象項目名】0021

【補正方法】変更

【補正の内容】

【0021】

本発明に係る請求項2記載の半導体装置によれば、複数の第1の素子分離絶縁膜の間のSOI層上に、それぞれ絶縁膜を介して抵抗素子が配設されているので、スパイラルインダクタの下方に対応する領域を有効に利用することができ、装置面積が増大する事なく、かつ高周波アナログ回路等の形成に有利な構成となる。

【手続補正9】

【補正対象書類名】明細書

【補正対象項目名】0022

【補正方法】変更

【補正の内容】

【0022】

本発明に係る請求項13記載の半導体装置の製造方法によれば、第1の領域のSOI層内には、半導体素子の形成時に不純物が導入されることが防止されるので、第1の領域のSOI層を高抵抗に保つことができ、また、電圧条件によっては完全空乏化が可能となり、抵抗素子の寄生容量の低容量化が可能となり、高周波動作に有利な半導体装置を得ることができる。

【手続補正10】

【補正対象書類名】明細書

【補正対象項目名】0071

【補正方法】変更

【補正の内容】

【0071】

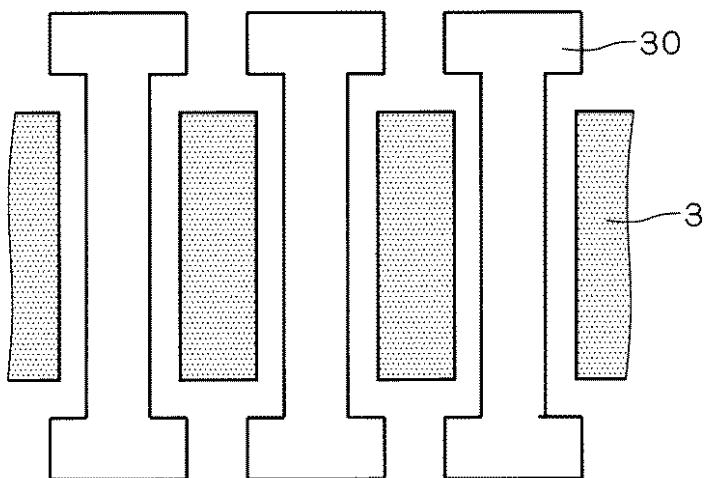

図15に示すように、抵抗素子30の平面視形状はアルファベットのI字形状をなし、細長形状の胴体部が図14に示した第1の領域P1に対応する位置に配置され、長手方向両端の面積が広くなっている部分が図14に示した第2の領域P2に対応する位置に配置され、当該部分が電気的なコンタクト部となる。

【手続補正11】

【補正対象書類名】明細書

【補正対象項目名】0081

【補正方法】変更

**【補正の内容】****【0081】**

次に、レジストマスクRM12を除去した後パッド酸化膜PDX1を全て除去し、図18に示す工程において、露出したSOI層3の表面に、ゲート絶縁膜となるシリコン酸化膜OX11を形成する。その後、SOI基板SBの全面に例えればCVD法により、後にゲート電極12、22および抵抗素子30となるポリシリコン層PS1を堆積する。このときの堆積温度は600～800が選択される。また、400～600の温度条件でスパッタリング法により形成しても良い。

**【手続補正12】****【補正対象書類名】明細書****【補正対象項目名】0111****【補正方法】変更****【補正の内容】****【0111】**

次に、レジストマスクRM21を除去した後、図28に示す工程において、SOI基板全域に渡って厚さ150～600nmのシリコン酸化膜OX2を形成し、シリコン酸化膜OX2によりトレンチTR21およびTR1を完全に埋め込む。なお、この工程は図11を用いて説明した工程と同じであるので、重複する説明は省略する。

**【手続補正13】****【補正対象書類名】明細書****【補正対象項目名】0127****【補正方法】変更****【補正の内容】****【0127】**

このような構成を採ることによっても、スパイラルインダクタSIの下方に抵抗素子30Aを配設できる。

**【手続補正14】****【補正対象書類名】明細書****【補正対象項目名】0129****【補正方法】変更****【補正の内容】****【0129】**

なお、絶縁膜35は、図16に示したパッド酸化膜PDX1を、抵抗領域RRにおいては除去せずに残し、図19を用いて説明したシリコン酸化膜OX11の形成に際しては、パッド酸化膜PDX1上にシリコン酸化膜OX11を形成することで実現できる。これにより、絶縁膜35の厚さはパッド酸化膜PDX1とシリコン酸化膜OX11の厚さの合計の厚さにすることができ、その上に形成される抵抗素子30Aの寄生容量を低減することができる。

**【手続補正15】****【補正対象書類名】明細書****【補正対象項目名】0130****【補正方法】変更****【補正の内容】****【0130】**

また、例えば、3.3Vの入出力(I/O)トランジスタなどのように、ゲート絶縁膜の厚さ異なるデバイスが複数種類存在する場合には、素子領域では厚さの異なるゲート絶縁膜を形成するが、その場合には、シリコン酸化膜の除去や形成を繰り返すこと(デュアルオキサイドプロセス)がある。このとき、素子領域でのシリコン酸化膜の除去に際しては抵抗領域RRはレジストマスクで覆うなどして、抵抗領域RRのSOI層3上においては一旦形成したシリコン酸化膜は除去しないこととする。これにより、SOI層3上には分

厚いシリコン酸化膜が形成されることになり、その上に抵抗素子 30 Aを形成すれば抵抗素子 30 Aの寄生容量を大幅に低減することができる。

【手続補正 16】

【補正対象書類名】図面

【補正対象項目名】図 15

【補正方法】変更

【補正の内容】

【図 15】