(12) 发明专利

(10) 授权公告号 CN 112925177 B

(45) 授权公告日 2022.09.06

(21) 申请号 202110404661.0

(74) 专利代理机构 北京律盟知识产权代理有限

(22) 申请日 2017.01.06

责任公司 11287

(65) 同一申请的已公布的文献号

专利代理人 张世俊

申请公布号 CN 112925177 A

(51) Int.CI.

(43) 申请公布日 2021.06.08

G03F 7/20 (2006.01)

(30) 优先权数据

G03F 1/44 (2012.01)

62/277,274 2016.01.11 US

G06F 30/39 (2020.01)

(62) 分案原申请数据

审查员 朱雅琛

201780005930.8 2017.01.06

(73) 专利权人 科磊股份有限公司

权利要求书2页 说明书7页 附图7页

地址 美国加利福尼亚州

(72) 发明人 B·戈洛瓦尼夫斯基

(54) 发明名称

热点及工艺窗监测

(57) 摘要

本申请实施例涉及热点及工艺窗监测。本申请提供计量叠加目标以及监测工艺缺点的方法。目标包括周期性结构，所述周期性结构中的至少一者包括沿着所述周期性结构的对应分段方向的重复不对称元件。举例来说，可以不同方式将所述元件的不对称性设计为沿着垂直于所述元件的所述分段方向的方向重复的不对称子元件。可根据所监测工艺缺点的类型（例如各种类型的热点、线边缘缩短、工艺窗参数等等）来以不同方式设计所述子元件的不对称性。测量的结果可用于改进工艺及/或提高计量测量的精度。

## 1. 一种监测工艺缺点的方法,其包括:

使用具有计量目标的叠加工具,其中所述计量目标包括晶片和安置于所述晶片上的至少两个周期性结构,其中所述周期性结构中的至少一者包括沿着所述周期性结构的对应分段方向的重复不对称元件,其中所述重复不对称元件沿着垂直于所述分段方向的方向在内部是周期性的,其中所述重复不对称元件包括沿着所述垂直于所述分段方向的方向的重复子元件,所述子元件在所述分段方向上是不对称的,其中所述子元件包括至少断开一次的线,且其中所述子元件中的至少一些包括沿着所述垂直于所述分段方向的方向的垂直线,所述垂直线连接到所述至少断开一次的线;以及

使用所述叠加工具从所述计量目标导出计量信号。

2. 根据权利要求1所述的方法,其中所述子元件包括至少两个平行线段。

3. 根据权利要求2所述的方法,其中所述平行线段中的至少一些是互连的。

4. 根据权利要求1所述的方法,其中所述线的至少一些互连到所述垂直线中的至少一些。

5. 根据权利要求1所述的方法,其中所述子元件中的至少一些沿着所述垂直于所述分段方向的方向互连。

6. 根据权利要求1所述的方法,其中所述子元件中的至少一些沿着所述垂直于所述分段方向的方向彼此隔开。

7. 根据权利要求1所述的方法,其中所述不对称元件包括垂直于所述分段方向的至少一个不对称定位的线。

8. 根据权利要求1所述的方法,其中所述子元件中的至少一者为具有至少六个边的多边形。

9. 根据权利要求1所述的方法,其进一步包括使用所述计量信号监测热点。

10. 根据权利要求1所述的方法,其进一步包括使用所述计量信号监测工艺窗。

## 11. 一种监测工艺缺点的设备,其包括:

叠加工具,其包括处理器和计算机可读存储介质,其中所述处理器经配置以从计量目标导出计量信号,其中所述计量目标包括晶片和安置于所述晶片上的至少两个周期性结构,其中所述周期性结构中的至少一者包括沿着所述周期性结构的对应分段方向的重复不对称元件,其中所述重复不对称元件沿着垂直于所述分段方向的方向在内部是周期性的,其中所述重复不对称元件包括沿着所述垂直于所述分段方向的方向的重复子元件,所述子元件在所述分段方向上是不对称的,其中所述子元件包括至少断开一次的线,且其中所述子元件中的至少一些包括沿着所述垂直于所述分段方向的方向的垂直线,所述垂直线连接到所述至少断开一次的线。

12. 根据权利要求11所述的设备,其中所述子元件包括至少两个平行线段。

13. 根据权利要求12所述的设备,其中所述平行线段中的至少一些是互连的。

14. 根据权利要求11所述的设备,其中所述线的至少一些互连到所述垂直线中的至少一些。

15. 根据权利要求11所述的设备,其中所述子元件中的至少一些沿着所述垂直于所述分段方向的方向互连。

16. 根据权利要求11所述的设备,其中所述子元件中的至少一些沿着所述垂直于所述

分段方向的方向彼此隔开。

17. 根据权利要求11所述的设备,其中所述不对称元件包括垂直于所述分段方向的至少一个不对称定位的线。

18. 根据权利要求11所述的设备,其中所述子元件中的至少一者为具有至少六个边的多边形。

19. 根据权利要求11所述的设备,其中所述叠加工具进一步经配置以监测热点。

20. 根据权利要求11所述的设备,其中所述叠加工具进一步经配置以监测工艺窗。

## 热点及工艺窗监测

[0001] 本申请是申请日为2017年1月6日,申请号为“201780005930.8”,而发明名称为“热点及工艺窗监测”的发明专利申请的分案申请。

[0002] 相关申请案的交叉参考

[0003] 本申请案主张2016年1月11日申请的第62/277,274号美国临时专利申请案的权益,所述美国临时专利申请案以全文引用方式并入本文中。

### 技术领域

[0004] 本发明涉及成像及散射测量叠加计量的领域,且更特定来说,本发明涉及目标设计及生产的各种工艺缺点的监测。

### 背景技术

[0005] 次波长间隙随着技术节点缩小且光刻波长保持于193nm而增大。随着此间隙增大,印刷晶片形状显得越来越不像设计布局形状,即使使用光学近接校正(OPC)及其它分辨率增强技术(RET)也是这样。尽管RET工具能够很好理解此形状失真,但其无法改变所绘制的布局。尽管设计工具具有更多余地来修改所绘制的布局,但其对光刻效应的理解是有限的,表现为试图防止“热点”的设计规则形式。热点是可说明一些光刻印刷问题(例如捏缩、桥接或线端缩短)的位置,这些问题导致装置故障或工艺窗的不可接受缩小,如下文图1B中所示范。

[0006] 同时,设计规则变得越来越复杂且最终无法用于解决光刻挑战。此外,设计规则复杂性导致热点问题变成限制当代多重图案化工艺的良率的重要因素。

[0007] 典型掩模制造及热点管理流程从设计规则清洁布局开始,接着进行OPC及基于模型的验证(MBV)。尽管在OPC及MBV的若干迭代之后,后OPC布局可通过MBV,但其无法保证晶片上不存在缺陷,这是因为模型并非完美的,尤其当图案复杂性增加时。因此,在晶片处理之后,晶片检验变成用于找到缺陷位置的必要步骤。

[0008] 在20nm节点及之外的节点(即,更小节点)中,归因于系统缺陷的良率损失部分已增加且多样化。设计复杂性及复杂高阶OPC会引起系统缺陷,且来自蚀刻、化学抛光(CMP)等等的物理故障也会引起系统缺陷。当边沿结构遇到工艺变化时,所得图案会最终成为以捏缩、桥接及线端缩短为特征的变形结构。

[0009] 此类现象引起热点的数目增加,且需要付出大量努力来识别及减轻热点。为减少热点发生且在大量生产时获得具有较高良率的生产率,需要投入大量努力来预测及消除薄弱设计,例如,使用模拟。然而,即使模拟经校准以达到设计者的目标,但20nm节点及之外的节点(更小节点)中的高阶工艺导致模拟的结果与晶片上的实际印刷图案之间的巨大差异。这意味着:模拟器由于较小制程裕度而无法预测发生于实际晶片处理中的实际缺陷。

[0010] 此外,2D(二维)设计图案提供比1D定向图案宽得多的临界特征组合范围。获得依据工艺而变化的两个对置线端(末端到末端)之间或线端垂线到沟槽(末端到沟槽)之间的距离测量。

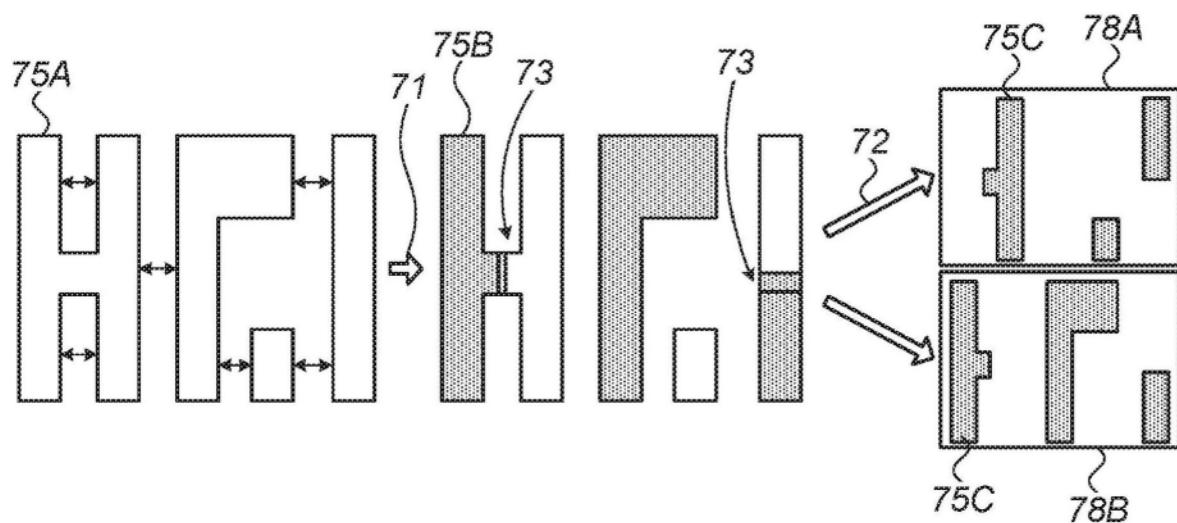

[0011] 图1A示意性地说明根据现有技术的使用单独掩模78A、78B来将2D图案75A分裂成较简单图案75B且进一步分裂成经处理元件75C。多重图案化方案将2D区域(多边形)分裂(71)成具有拼接段73的两个或更多个多个多边形(称为层分解)且将结构进一步分裂(72)成用于处理的单独掩模(例如,通过双重图案化,例如LELE(光刻蚀刻-光刻蚀刻))。此类方案对OVL误差及工艺变化非常敏感,且大幅增加热点的重要性。

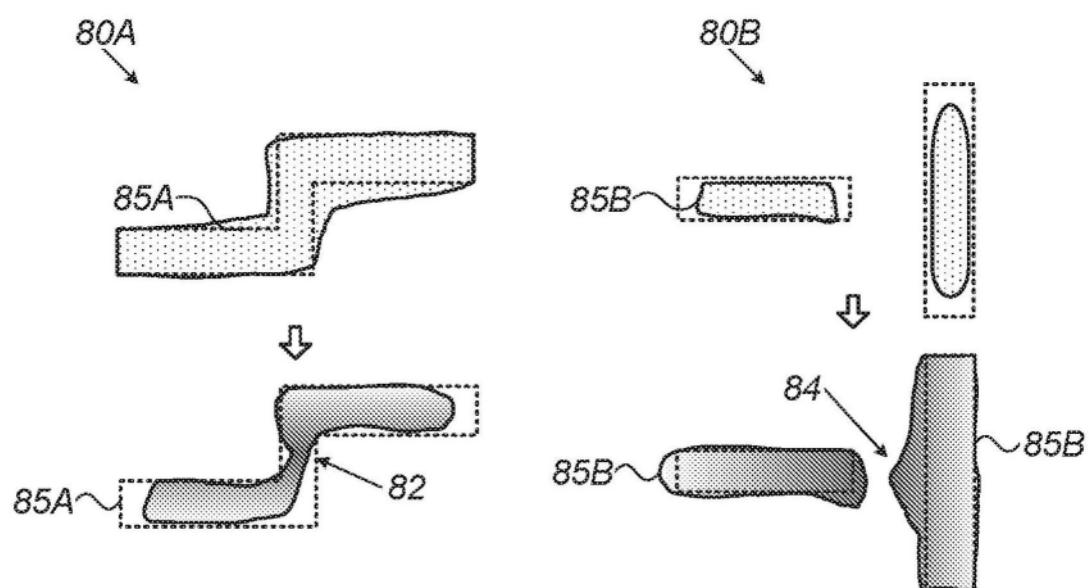

[0012] 图1B示意性地说明根据现有技术的与工艺窗结合的热点行为。说明80A、80B分别示意性地展示分别具有颈缩热点82及桥接热点84的工艺拐点及工艺间隙中的两个非限制性热点实例作为现有技术的非限制性实例。

## 发明内容

[0013] 下文是提供本发明的初步理解的简明概要。所述概要未必识别关键元件且也不限制本发明的范围,而是仅为以下描述的简介。

[0014] 本发明的一个方面提供包括至少两个周期性结构的叠加计量目标,其中所述周期性结构中的至少一者包括沿着所述周期性结构的对应分段方向的重复不对称元件。

[0015] 本发明的这些、额外及/或其它方面及/或优点陈述于以下详细描述中,可从详细描述推知,及/或可通过实践本发明而获知。

## 附图说明

[0016] 为更佳理解本发明的实施例且展示可如何有效实施本发明的实施例,现将仅以实例方式参考附图,其中相同元件符号标示全部图中的对应元件或区段。

[0017] 在附图中:

[0018] 图1A示意性地说明根据现有技术的使用单独掩模来将2D图案分裂成较简单图案且进一步分裂成处理元件。

[0019] 图1B示意性地说明根据现有技术的与工艺窗结合的热点行为。

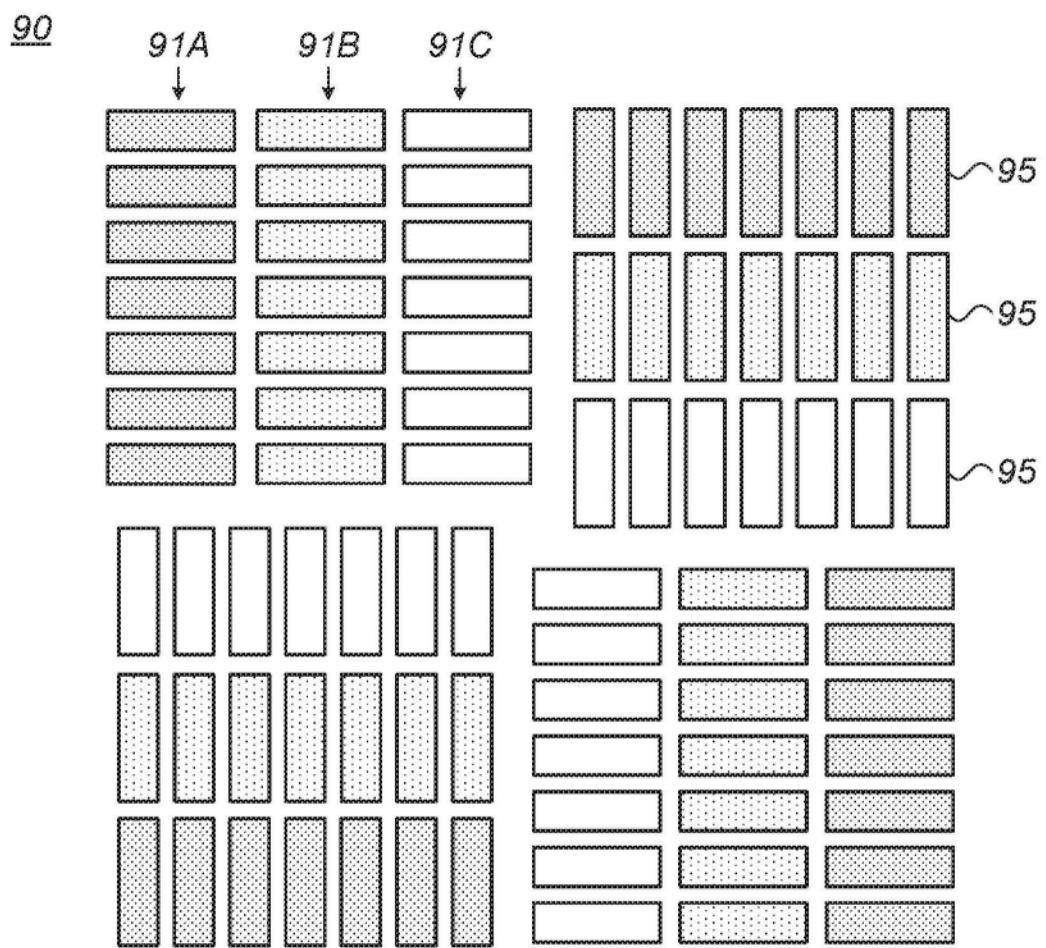

[0020] 图2是根据现有技术的成像目标的周期性结构的示意性说明。

[0021] 图3是根据现有技术的成像目标中的周期性结构的元件的高阶示意性说明。

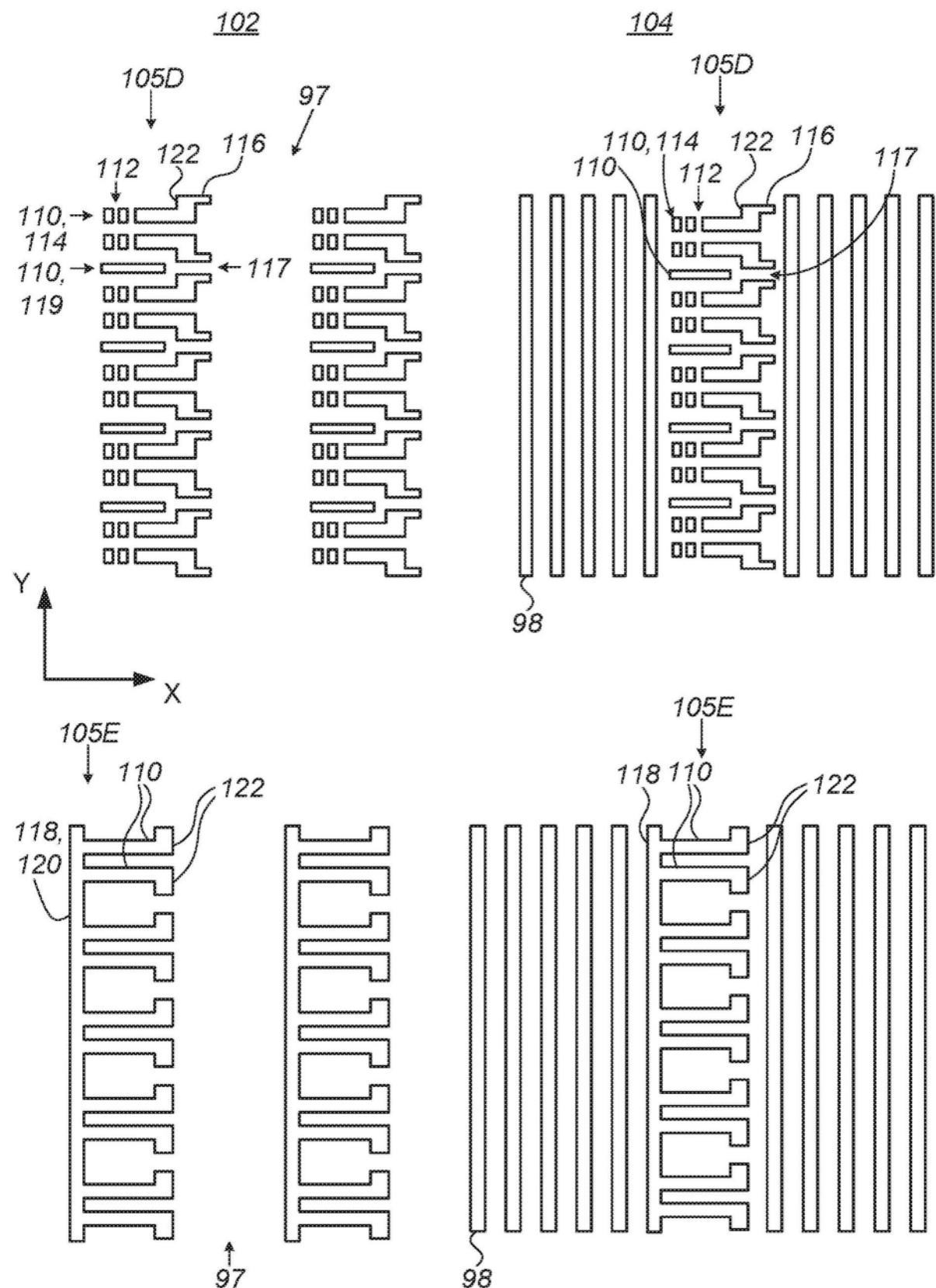

[0022] 图4(a) - 4(d)是根据本发明的一些实施例的叠加目标及其部分中的周期性结构及叠加目标的周期性结构的元件的各种示范性、非限制性元件设计的示意性说明。

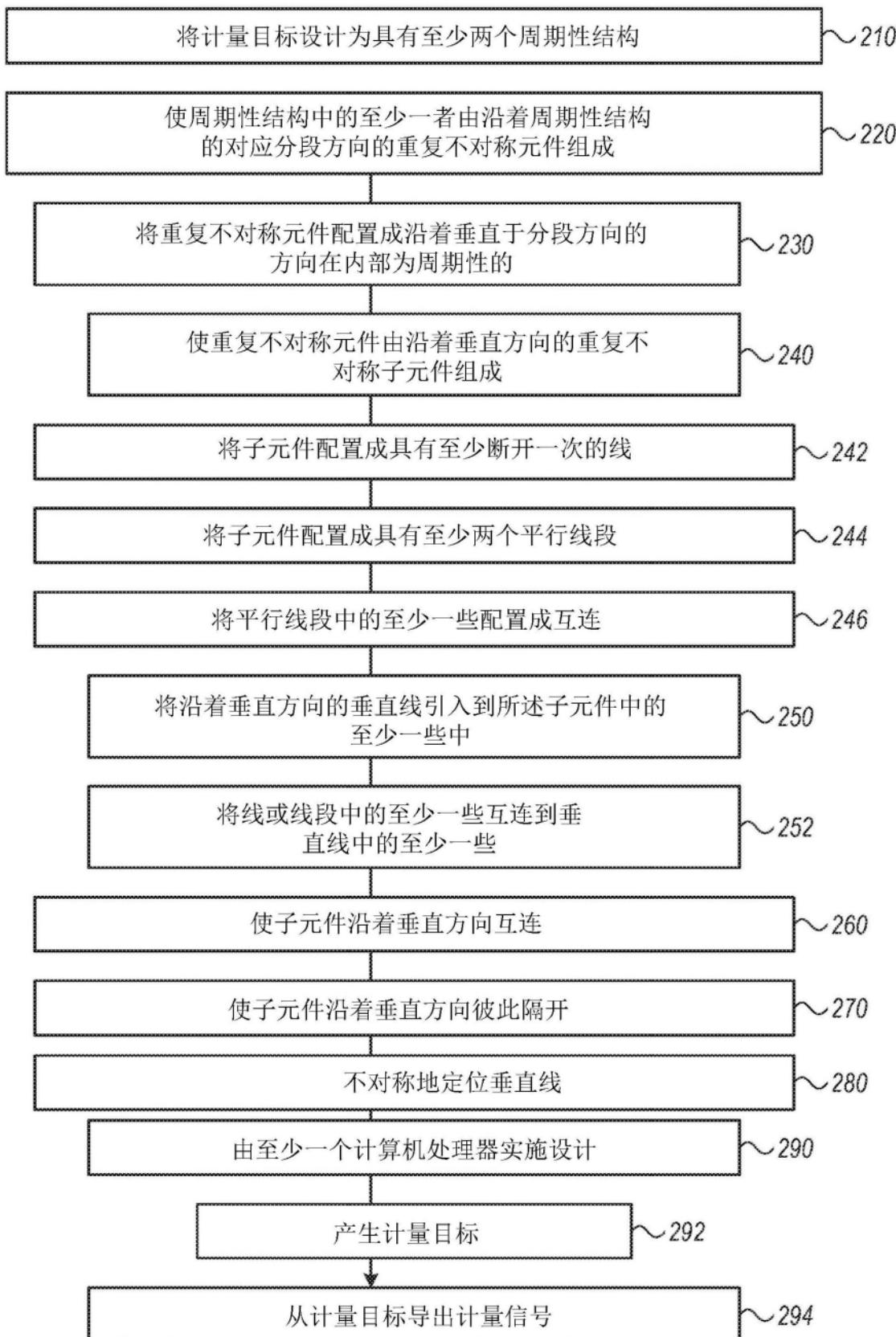

[0023] 图5是说明根据本发明的一些实施例的方法的高阶流程图。

## 具体实施方式

[0024] 在以下描述中,描述本发明的各种方面。出于解释的目的,陈述特定配置及细节以提供对本发明的透彻理解。然而,所属领域的技术人员还应明白,可在无本文所呈现的特定细节的情况下实践本发明。此外,已省略或简化众所周知的特征以免混淆本发明。应强调,在参考特定图式时,所展示的详细情况仅通过实例且仅用于本发明的说明性论述,且为了提供被认为是本发明的原理及概念方面的最有用且最容易理解的描述的内容而呈现。就此而言,不会试图展示比基本理解本发明所需的结构细节更详细的本发明的结构细节,结合图式的描述使所属领域的技术人员明白可如何在实践中体现本发明的若干形式。

[0025] 在详细解释本发明的至少一个实施例之前,应理解,本发明的应用不受限于以下

描述中所陈述或图式中所说明的组件的构造及布置的细节。本发明可应用于可以各种方式实践或实施的其它实施例及所揭示实施例的组合。此外,应理解,本文所采用的词组及术语是出于描述的目的且不应被视为限制。

[0026] 除非另外明确说明(如从以下论述所明白),否则应了解,在本说明书中,利用例如“处理”、“计算(computing/calculating)”、“确定”、“增强”或其类似物的术语的论述是指计算机或计算系统或类似电子计算装置的动作及/或过程,所述计算机或计算系统或类似电子计算装置将表示为计算系统的寄存器及存储器内的物理(例如电子)量的数据操纵及/或变换成类似地表示为计算系统的存储器、寄存器或其它此类信息存储、传输或显示器装置内的物理量的其它数据。

[0027] 尽管本发明可应用于成像叠加目标及散射测量叠加目标两者,但本文所呈现的目标设计实例以非限制性方式与成像技术相关。类似方法可用于设计散射测量目标。

[0028] 叠加(OVL)成像工具的光学分辨率相对较低且需要使用微米级特征作为叠加目标的可解析元件。然而,非成像或非解析技术(例如散射测量)将类似蕴涵强加于目标设计。这些“大”特征与当代工艺设计规则不兼容且需要对应分段/虚设化(例如,使用具有较小尺度的子元件来填充通常形成周期性图案的“较大”微米级的目标元件,参见图3)。适当分段使叠加目标行为更接近装置行为。然而,正交线段(参见图3的96中的非限制性说明)遭受类似于装置的线端缩短(LES),且如果遭受归因于光刻光学像差或偏轴照明的不对称LES,那么此LES会影响叠加测量。此外,平行线段(参见图3的98中的非限制性说明)遭受一种PPE(图案放置误差),其中分段条的外线宽度不同于内线宽度。

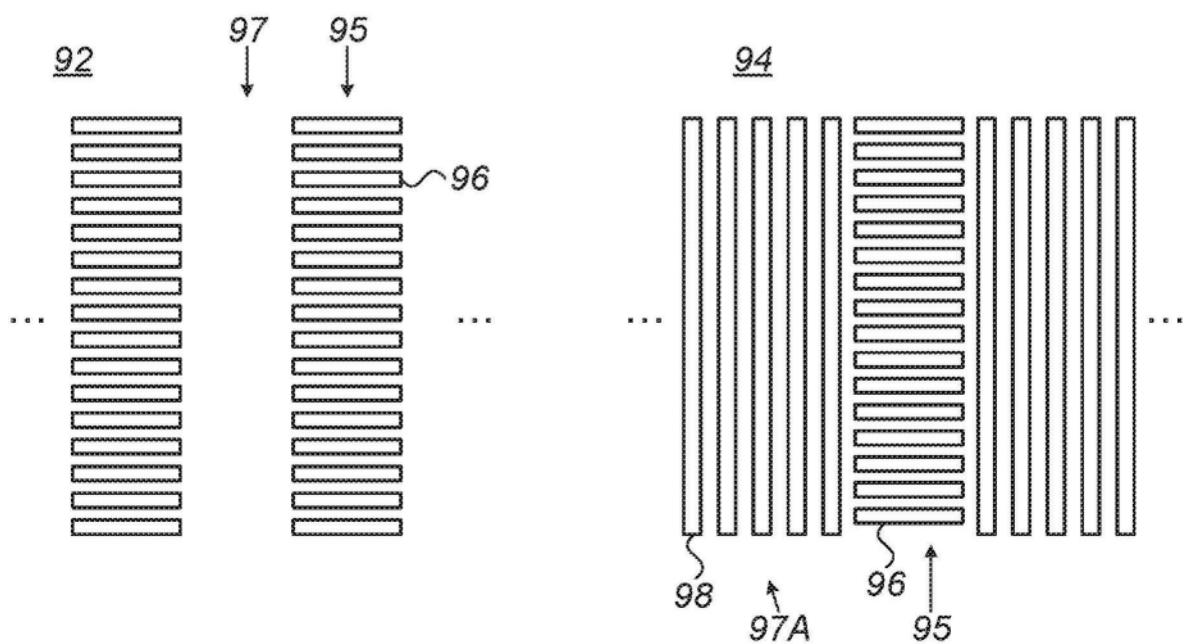

[0029] 图2是根据现有技术的高阶成像目标90的周期性结构的示意性说明。在现有技术中,成像目标90(例如AIM目标(高阶成像计量目标))能够测量多于两个层的OVL。AIM目标的现实实例包含周期性结构91A、91B、91C。AIM目标通常包含负责X方向及Y方向两者的OVL测量的块。图2上的实例具有以顺时针对称性用于每一方向的两个块。所述块通常被分别设计为在晶片中为不同层的外层、中间层及内层,例如两个先前产生层及抗蚀剂层。周期性结构91A、91B、91C由元件95组成,元件95可根据与特定层相关的DR(设计角色)要求而在不同周期性结构91A、91B、91C中彼此类似或不同。图3是根据现有技术的成像目标90中的周期性结构91A、91B、91C的元件95的高阶示意性说明。元件95通常为具有形成元件95的分段的子元件96的分段条,且间隔97被留空(如同设计92)或填充有具有子元件98的分段虚设化设计97A(如同设计94)。条95的分段可为正交条96或平行条98。在两个现有技术案例中,子元件96、98是对称条。

[0030] 本发明的实施例提供转换“大”目标特征且使用特殊设计目标来使热点(如LES)与叠加一起(或与叠加分开)被监测且减少所需CD-SEM(临界尺寸-扫描电子显微术)测量(其是研究LES及热点的现有技术方式)的数目的高效且经济方法。

[0031] 某些实施例包括使OVL工具及OVL算法与特殊设计目标一起用于监测热点及/或工艺窗。有利地,与使用CD-SEM类工具来进行热点在线检测及监测的现有技术(其具有非常低产出率及高工具拥有成本(CoO))相比,所揭示的方法及目标提供导致良率改进的有效热点监测。另外,组合热点监测及OVL测量允许改进晶片测量产出率及晶片有效面积。

[0032] 提供计量成像目标作为非限制性实例且提供监测工艺缺点的方法。目标包括周期性结构,其至少一者包括沿着所述周期性结构的对应分段方向的重复不对称元件。举例来

说,可以不同方式将所述元件的不对称性设计为沿着垂直于所述元件的所述分段方向的方向重复不对称子元件。可根据监测工艺缺点的类型(例如各种类型的热点、线边缘缩短、工艺窗参数等等)来以不同方式设计所述子元件的不对称性。测量的结果可用于改进工艺及/或提高计量测量的精度。

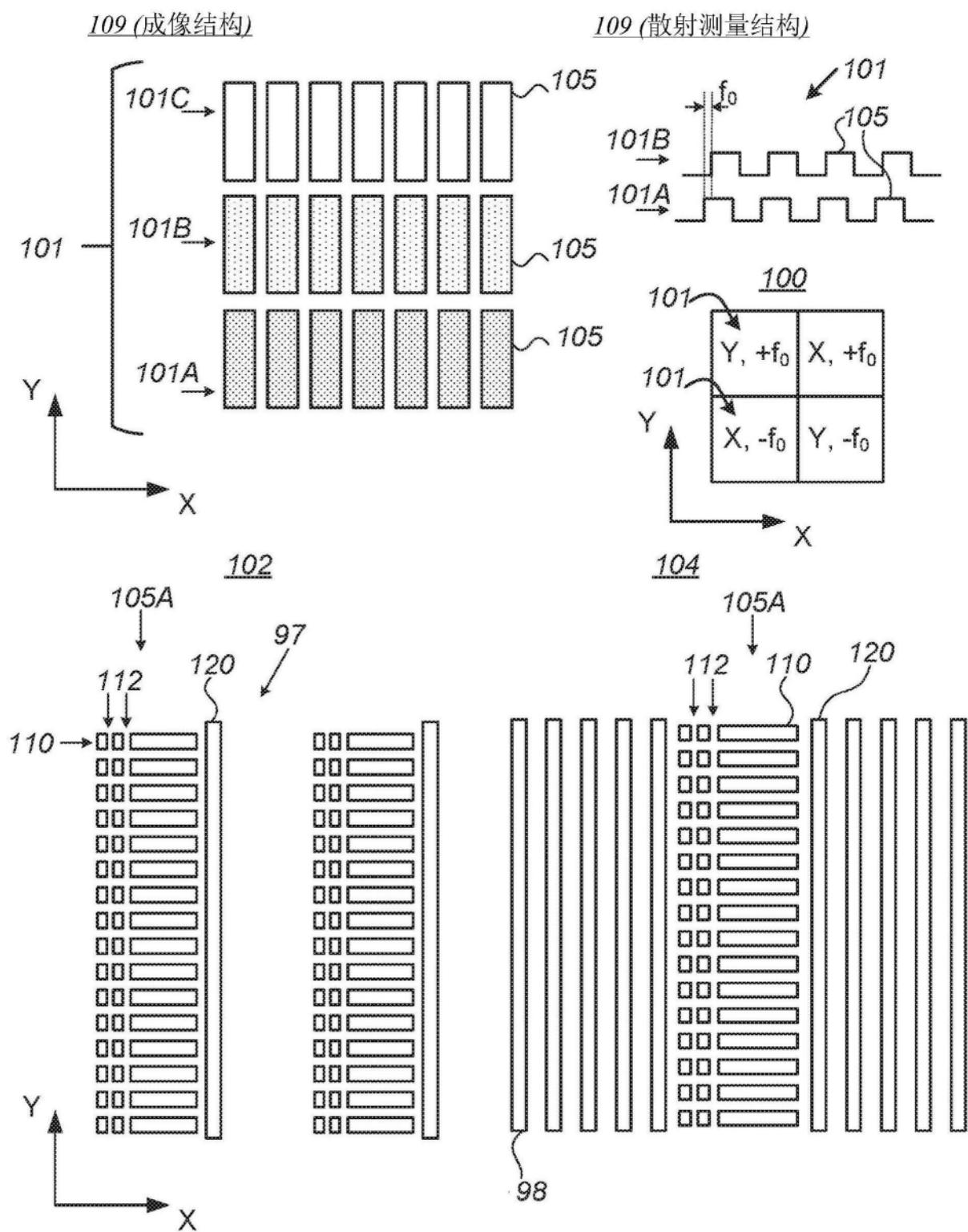

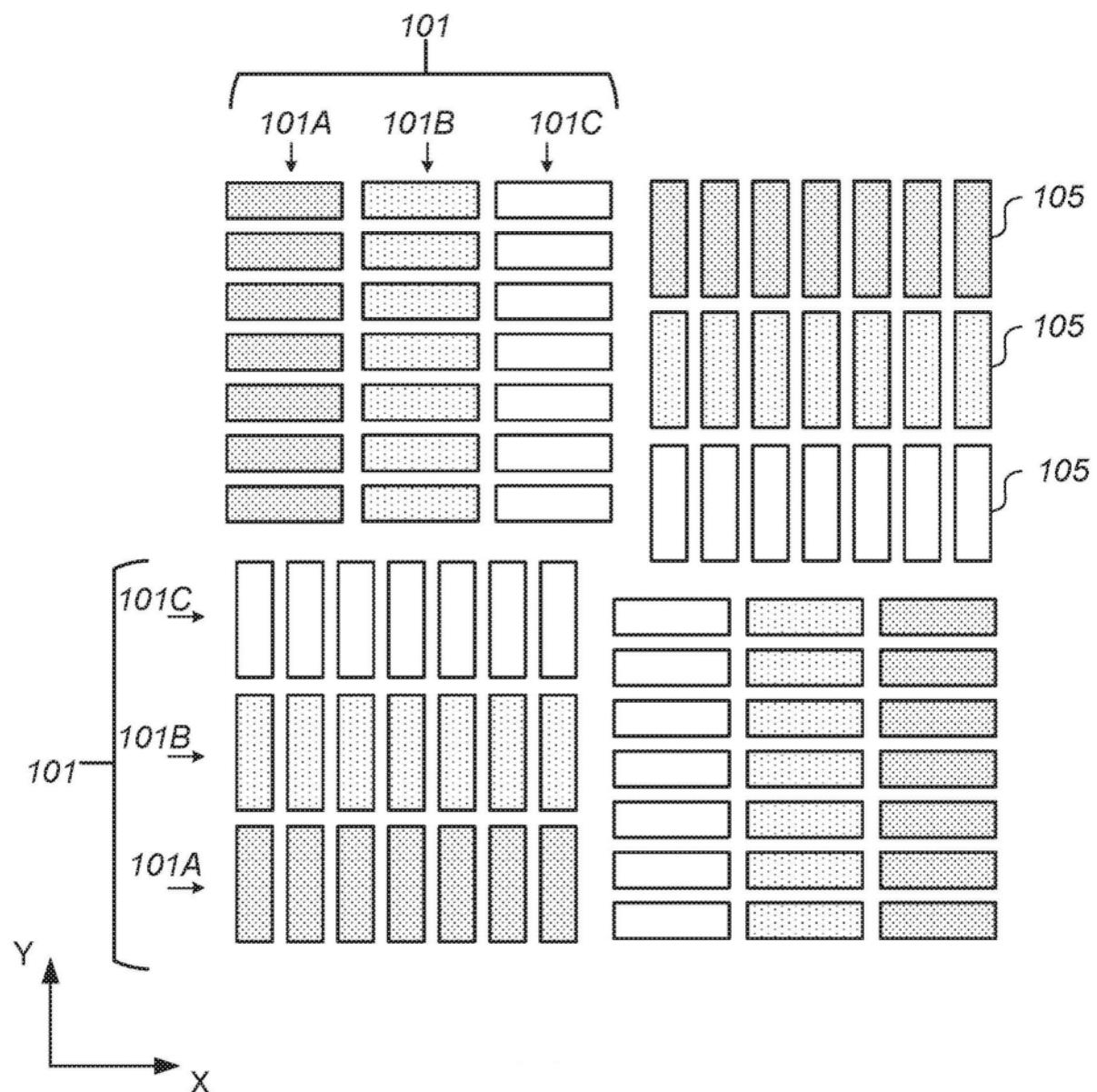

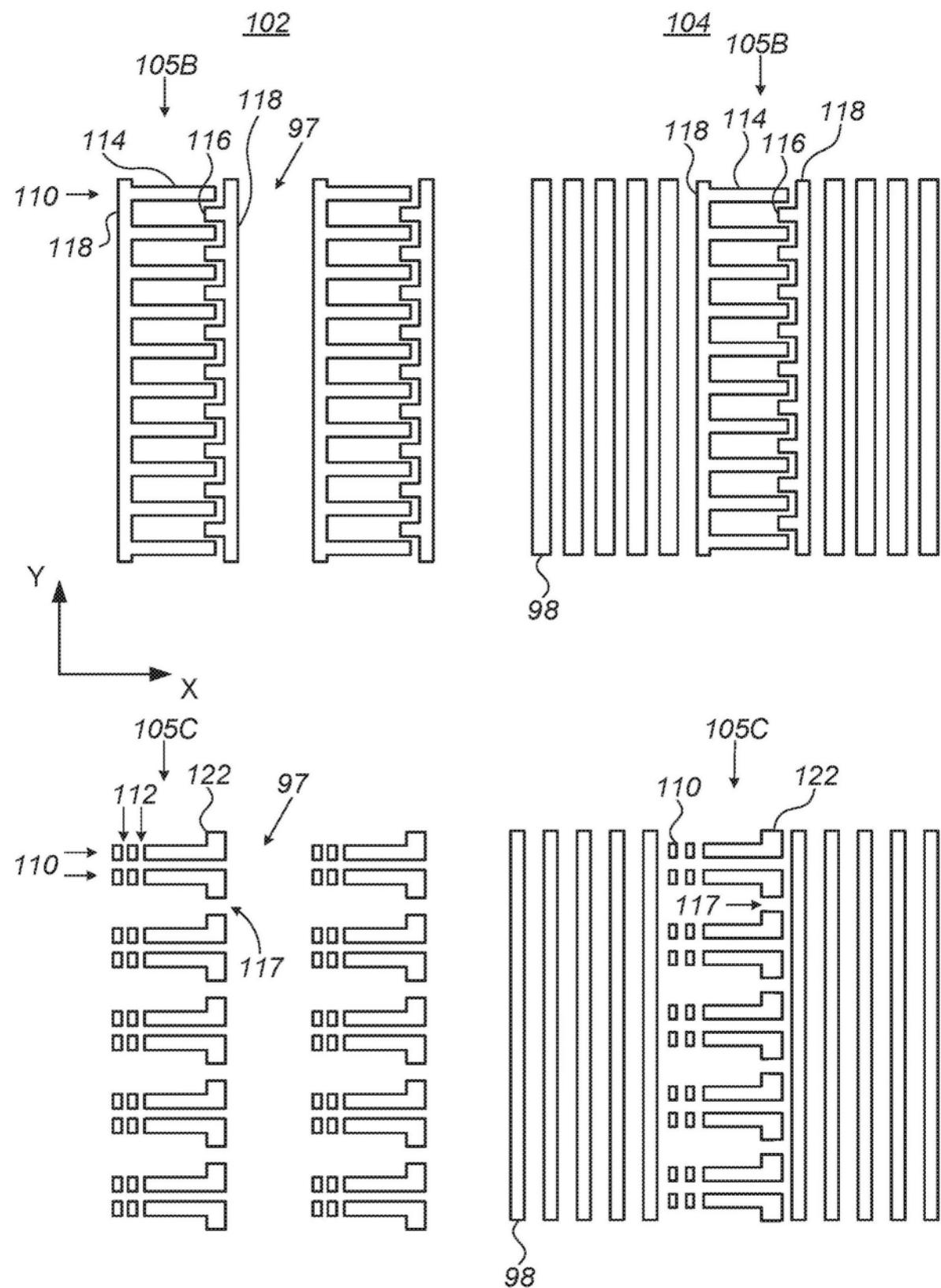

[0033] 图4(a)-4(d)是根据本发明的一些实施例的叠加目标100及其部分109中的周期性结构101及叠加目标100的周期性结构101的元件105的各种示范性、非限制性元件设计105A到105E的示意性说明。叠加目标100可包括具有多个说明部分109的成像目标100及/或散射测量目标100,部分109可布置成各种布局,例如,布置成类似于图2的成像目标90的配置或布置成其它配置。成像目标及散射测量目标的任何设计可采用如本文所揭示的周期性结构,示意性说明不限制本发明的实施例。所说明的周期性结构的任一者可为成像或散射测量叠加目标100的部分。周期性结构101A、101B、101C中的至少一者可由在不同周期性结构101A、101B、101C中可彼此类似或不同的元件105组成。周期性结构101A、101B、101C可设计于不同层中及/或相对于不同工艺步骤来设计,例如,周期性结构101A、101B、101C可处于以下每一者中:(i)用于叠加测量的所要工艺层;(ii)具有用于LES监测的分段的锚定相同抗蚀剂层(例如105A到105E或等效设计的任一者);及(iii)锚定抗蚀剂层(无分段)。可将任何数目个不同周期性结构101(2个、3个、4个或4个以上周期性结构101)设计于成像及/或散射测量叠加目标100中,且可根据测量的目的(例如LES)、不同类型的热点(参见上文)及下文可结合叠加测量来描述的额外目的来选择元件105的设计细目。

[0034] 可将目标分段(即,元件105的分段)设计为装置类结构的可重复图案。这些结构可远低于叠加成像工具的光学分辨率且可以使得分段条(边缘或质心)由于LES效应(或用于监测的其它所要类型的热点)(因此指示LES及/或热点的存在及可能程度)而移动的方式被设计。

[0035] 图4(a)-4(d)以非限制性方式示意性地示范各种此类图案105A到105E。所说明的实例可应用于负责X方向上的OVL测量(根据所说明的方向性)的OVL目标的部分109及负责Y方向上的OVL测量的OVL目标的部分109(其可(例如)通过使实例旋转90°来产生)两者。每一展示图包含:实例102,其具有相应元件105A到105E之间的间隙97;及实例104,其说明相应元件105A到105E之间的平行分段98。分段条98可用作为填充虚设物、锚定条或测量目标的任何其它功能部分。平行条分段经选取以使此实例仅用于可视化,且可基于所需条功能及特定层的设计规则来进行不同设计。条甚至可为未分段条或不对称分段条。

[0036] 元件105(以非限制性方式示范为条)可沿着结构101A、101B及/或101C的对应测量方向(在图4(a)-4(d)中标示为“Y”)分段、重复及不对称。重复不对称元件105可沿着垂直于测量(重复)方向的方向(在图4(a)-4(d)中标示为“Y”)的方向内部分段。重复不对称元件105可包括沿着垂直方向(Y)的重复子元件110,子元件在分段方向(X)上不对称,如示范性设计105A到105E中所说明。

[0037] 在某些实施例中,子元件110可包括至少断开一次的线,如在设计105A、105C及105D中由间隙112所说明。子元件110可包括用于子元件110的设计的任何OPC特征(其减小子元件110的一个侧的PPE),而子元件110的对置侧可为简单线或包含经设计以监测所要热点的特征。

[0038] 在某些实施例中,子元件110可包括至少两个平行线段,如设计105B到105E中所说

明,例如在105B中由不等线114、116所说明、在105D中的不等线114、116所说明及在105C、105E中由具有相等长度的线110所说明。

[0039] 在某些实施例中,平行线段中的至少一些可互连,如在设计105D中由线段114、116所说明及在设计105B及105E中经由互联线118所说明。

[0040] 在某些实施例中,子元件110中的至少一些可包括沿着垂直方向(Y)的垂直线122,如设计105C、105D及105E中所说明。

[0041] 在某些实施例中,线110及/或线段114、116、119中的至少一些可互连到垂直线122的至少一些,如设计105C中所示范。

[0042] 在某些实施例中,子元件110中的至少一些可沿着垂直方向(Y)互连,如(例如)设计105B及105E中所说明。

[0043] 在某些实施例中,子元件110可沿着垂直方向(Y)彼此隔开(参见间隔117),如(例如)设计105A、105C及105D中所说明。

[0044] 在某些实施例中,不对称元件105可包括垂直于分段方向(X)而不对称定位的至少一个线120。举例来说,设计105A中展示单个垂直线120(其沿着垂直方向Y延伸),且设计105E中类似地定位线118。特征的尺寸(主要为CD)取决于特定层的设计规则且可改变于工艺允许的最小值(例如用于当前最高阶工艺的7nm)直到工艺允许的最大值(例如非限制性实例中的300nm)之间,且考虑禁用节距。

[0045] 应明确注意,用于指示设计特性的类型的数字不互斥,且某些设计特征可实施上述设计原理的一者以上。此外,来自不同设计105A到105E的元件可经组合以产生额外设计及根据上文所列原理的不同设计且同样被视为本发明的部分。来自设计105A到105E的元件可组合成任何可操作组合,且某些图而非其它图中的某些元件的说明仅供说明且不具限制性。

[0046] 某些实施例包括具有至少一个周期性结构的散射测量叠加目标,其具有含揭示设计图案的任一者的元件105。

[0047] 某些实施例包括目标100的目标设计文件及从目标100的任一者测量的计量信号(全目标设计由根据各种图案的多个目标元件105组成,参见(例如)现有技术目标图案90)。

[0048] 可对元件设计作出修改以测量图案放置误差(PPE)。不同特征形状、大小、节距及线间隔比具有不同PPE且可设计于子元件110中以提供PPE测量。

[0049] 在某些实施例中,目标100(及其导出目标设计)可经设计以能够监测任何类型的热点及监测处理步骤的任一者(例如蚀刻及CMP)及光刻步骤中的工艺窗。

[0050] 在某些实施例中,目标100(及其导出目标设计)可用于通过测量不对称LES、PPE或CMP效应且从叠加结果减去来改进叠加测量的精度。

[0051] 有利地,所揭示的2D图案提供比单个定向图案宽得多的临界特征组合。可获得依据工艺而变化的两个对置线端(末端到末端)之间或线端垂线与沟槽(末端到沟槽)之间的距离测量。

[0052] 可使用将目标图像一直传播到叠加工具的成像装置的任何光刻模拟软件(其可为提供完全目标模拟及叠加工具设置优化的模拟工具)来优化目标设计。

[0053] 有利地,本发明可利用标准叠加工具及算法且对晶片有效面积及Co0无任何显著影响。归因于高产出率、使用简单及短时间出结果,本发明可提供显著增加的热点取样且因

此提供较佳工艺监测。

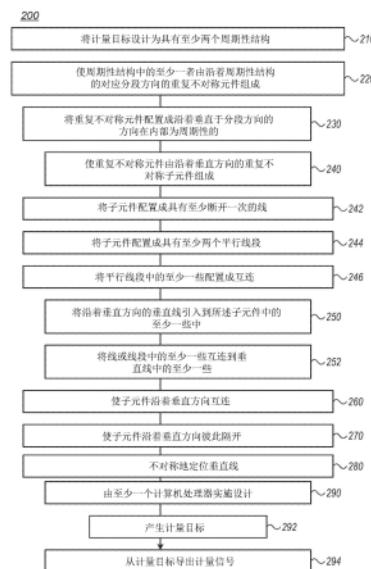

[0054] 图5是说明根据本发明的一些实施例的方法200的高阶流程图。可相对于上文所描述的目标100来实施方法阶段,其可任选地设计成方法200。方法200可至少部分由(例如)位于目标设计模块(未展示)中的至少一个计算机处理器(未展示)实施。某些实施例包括计算机程序产品,其包括计算机可读存储介质,所述计算机可读存储介质具有由其体现且经配置以实施方法200的相关阶段的计算机可读程序。某些实施例包括由方法200的实施例设计的相应目标的目标设计文件。某些实施例包括从目标100测量的信号及/或由方法200的实施例设计的目标。方法200可包含通过光刻模拟来设计目标100且进一步包括优化目标设计。

[0055] 方法200可包括:将计量成像目标设计为具有至少两个周期性结构(阶段210);及使所述周期性结构中的至少一者由沿着所述周期性结构的对应分段方向的重复不对称元件组成(阶段220)。

[0056] 方法200可包括:将所述重复不对称元件配置成沿着垂直于所述分段方向的方向周期性的(阶段230);及可使所述重复不对称元件由沿着所述垂直方向的重复不对称子元件组成(阶段240)。

[0057] 方法200可包括以下的任一者:将所述子元件配置成具有至少断开一次的线(阶段242);将所述子元件配置成具有至少两个平行线段(阶段244);将所述平行线段中的至少一些配置成互连的(阶段246);将沿着所述垂直方向的垂直线引入到所述子元件中的至少一些中(阶段250);及将所述线或线段中的至少一些互连到与所述垂直线中的至少一些(阶段252)。

[0058] 方法200可包括:使所述子元件中的至少一些沿着所述垂直方向互连(阶段260);及/或使所述子元件中的至少一些沿着所述垂直方向彼此隔开(阶段270)。

[0059] 方法200可包括:不对称地定位垂直线,即,不对称地定位垂直于所述分段方向的至少一个线(阶段280)。

[0060] 方法200可包括:由至少一个计算机处理器实施设计210(阶段290);及/或产生计量成像目标(阶段292);及/或从所述计量成像目标导出计量信号(阶段294)。

[0061] 上文已参考根据本发明的实施例的方法、设备(系统)及计算机程序产品的流程说明及/或部分图来描述本发明的方面。应理解,流程说明及/或部分图的每一部分及流程说明及/或部分图中的部分的组合可由计算机程序指令实施。可将这些计算机程序指令提供到通用计算机、专用计算机或其它可编程数据处理设备的处理器以产生机器,使得经由所述计算机或其它可编程数据处理设备的所述处理器执行的所述指令产生用于实施流程图及/或部分图或其部分中所指定的功能/动作的方法。

[0062] 也可将这些计算机程序指令存储于计算机可读介质中,所述计算机程序指令可指导计算机、其它可编程数据处理设备或其它装置以特定方式运行,使得存储于所述计算机可读介质中的所述指令产生包含实施流程图及/或部分图或其部分中所指定的功能/动作的指令的制品。

[0063] 也可将所述计算机程序指令加载到计算机、其它可编程数据处理设备或其它装置上以引起对所述计算机、其它可编程设备或其它装置执行一系列操作步骤以产生计算机实施过程,使得在所述计算机或其它可编程设备上执行的所述指令提供用于实施流程图及/

或部分图或其部分中所指定的功能/动作的过程。

[0064] 上述流程图及图式说明根据本发明的各种实施例的系统、方法及计算机程序产品的可能实施方案的架构、功能性及操作。就此而言，流程图或部分图中的每一部分可表示模块、分段或编码部分，其包括用于实施指定逻辑功能的一或多个可执行指令。还应注意，在一些替代实施方案中，部分中所提及的功能可不以图中所提及的次序发生。举例来说，取决于所涉及的功能性，实际上可基本上同时执行连续展示的两个部分或有时可以相反次序执行所述部分。还应注意，部分图及/或流程说明的每一部分及部分图及/或流程说明中的部分的组合可由执行指定功能或动作的基于专用硬件的系统或专用硬件及计算机指令的组合实施。

[0065] 在以上描述中，实施例是本发明的实例或实施方案。各种形式的“一个实施例”、“实施例”、“某些实施例”或“一些实施例”未必全部是指相同实施例。尽管可在单个实施例的上下文中描述本发明的各种特征，但也可单独地或以任何适合组合提供所述特征。相反地，尽管可为了清楚而在本文的单独实施例的上下文中描述本发明，但也可在单个实施例中实施本发明。本发明的某些实施例可包含来自上文所揭示的不同实施例的特征，且某些实施例可并入来自上文所揭示的其它实施例的元件。在特定实施例的上下文中揭示本发明的元件不应被视为使所述元件仅限于用于所述特定实施例中。此外，应理解，可以各种方式实施或实践本发明且可在除以上描述中所概述的实施例之外的某些实施例中实施本发明。

[0066] 本发明不受限于所述图式或对应描述。举例来说，流程无需移动通过每一说明框或状态或以完全相同于所说明及所描述的次序的次序进行。除非另外定义，否则本文所使用的科技术语的含义应为本发明所属技术领域的技术人员通常所理解的含义。尽管已相对于有限数目个实施例来描述本发明，但这些不应被解释为对本发明的范围的限制，而是作为一些优选实施例的范例。其它可能变化、修改及应用也在本发明的范围内。相应地，本发明的范围不应受限于到目前为止已描述的内容，而是受限于所附权利要求书及其合法等效物。

70

图1A

图1B

图2

图3

图4 (a)

100

图4(b)

图4 (c)

图4 (d)

200

图5