(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6158942号

(P6158942)

(45) 発行日 平成29年7月5日(2017.7.5)

(24) 登録日 平成29年6月16日(2017.6.16)

|                     |             |

|---------------------|-------------|

| (51) Int.Cl.        | F 1         |

| HO3H 9/64 (2006.01) | HO3H 9/64 Z |

| HO3H 9/54 (2006.01) | HO3H 9/54 Z |

| HO3H 9/17 (2006.01) | HO3H 9/17 F |

請求項の数 25 (全 28 頁)

|               |                               |           |                                                                                                                      |

|---------------|-------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2015-545535 (P2015-545535)  | (73) 特許権者 | 514326649<br>レゾナント インコーポレイテッド<br>RESONANT INC.<br>アメリカ合衆国 カリフォルニア州 93<br>117, サンタバーバラ, カスティリアン<br>ドライブ 110, スイート 100 |

| (86) (22) 出願日 | 平成26年3月14日 (2014.3.14)        | (74) 代理人  | 110001302<br>特許業務法人北青山インターナショナル                                                                                      |

| (65) 公表番号     | 特表2016-508303 (P2016-508303A) | (72) 発明者  | ターナー, パトリック, ジェー.<br>アメリカ合衆国 カリフォルニア州 93<br>103, サンタバーバラ, エヌ. サリナス<br>ストリート 111                                      |

| (43) 公表日      | 平成28年3月17日 (2016.3.17)        |           |                                                                                                                      |

| (86) 國際出願番号   | PCT/US2014/029800             |           |                                                                                                                      |

| (87) 國際公開番号   | W02014/145113                 |           |                                                                                                                      |

| (87) 國際公開日    | 平成26年9月18日 (2014.9.18)        |           |                                                                                                                      |

| 審査請求日         | 平成27年6月1日 (2015.6.1)          |           |                                                                                                                      |

| (31) 優先権主張番号  | 13/838, 943                   |           |                                                                                                                      |

| (32) 優先日      | 平成25年3月15日 (2013.3.15)        |           |                                                                                                                      |

| (33) 優先権主張国   | 米国(US)                        |           |                                                                                                                      |

最終頁に続く

(54) 【発明の名称】マイクロ音響波フィルタのネットワーク合成設計

## (57) 【特許請求の範囲】

## 【請求項 1】

周波数応答要求(ステップ52)に応じて音響マイクロ波フィルタを設計する方法において：

少なくとも一の共振エレメント(114)と少なくとも一の他のリアクタンス回路エレメント(116-120)を含む複数の回路エレメント(114-120)を具える初期フィルタ回路構造(100)を選択するステップ(ステップ56)と；

前記周波数応答要求に基づいてロスが少ない回路応答変数を選択するステップ(ステップ60)と；

前記選択したロスが少ない回路応答変数に基づいて前記各回路エレメント(114-120)の値を選択して初期フィルタ回路設計を作成するステップ(ステップ62)と；

前記少なくとも一の共振エレメント(114)と、前記初期フィルタ回路設計の前記少なくとも一の他のリアクタンス回路エレメント(116-120)を少なくとも一の音響共振器モデル(122)に変換して、音響フィルタ回路設計を作成するステップ(ステップ64)と；

寄生効果を前記音響フィルタ回路設計に加えて、予め最適化したフィルタ回路設計を作成するステップ(ステップ68)と；

前記予め最適化したフィルタ回路設計を最適化して最終フィルタ回路設計を作成するステップ(ステップ70)と；

前記最終フィルタ回路設計に基づいて前記音響マイクロ波フィルタを構築するステップ

10

20

(ステップ72)と;

を具えることを特徴とする方法。

【請求項2】

請求項1に記載の方法において、前記周波数応答要求が、周波数依存型リターンロスと、挿入口スと、阻止率と、直線性のうちの一またはそれ以上を具えることを特徴とする方法。

【請求項3】

請求項1に記載の方法において、前記周波数応答要求が、500-3500MHzの範囲の通過帯域を具えることを特徴とする方法。

【請求項4】

請求項1に記載の方法において、前記周波数応答要求が、通過帯域と阻止帯域を具えることを特徴とする方法。

【請求項5】

請求項1に記載の方法において、前記少なくとも一の共振エレメント(114)が、キャパシタ( $C^{R^1}$ )とインダクタ( $L^{R^1}$ )からなる並列L-C共振器組合せを具えることを特徴とする方法。

【請求項6】

請求項1に記載の方法において、前記少なくとも一のその他のリアクタンス回路エレメント(116)が、キャパシタ( $C_{11}$ )を具えることを特徴とする方法。

【請求項7】

請求項1に記載の方法において、前記初期フィルタ回路構造(100)が、インライン非共振ノード回路構造であることを特徴とする方法。

【請求項8】

請求項1に記載の方法において、前記ロスが少ない回路応答変数が、伝送ゼロ点を規定する分子多項式と、反射ゼロ点を規定する分母多項式の比にスケールファクタを乗じた形であることを特徴とする方法。

【請求項9】

請求項8に記載の方法において、伝送ゼロ点の総数が、反射ゼロ点の総数に等しいかこれより大きいことを特徴とする方法。

【請求項10】

請求項1に記載の方法において、前記少なくとも一の音響共振モデル(122)が、Butterworth-Van Dyke(BVD)モデルであることを特徴とする方法。

【請求項11】

請求項10に記載の方法において、前記少なくとも一共振器(114)の一つが、内部シャント並列L-C共振器組合せ( $C^{R^1}$ ,  $L^{R^1}$ )を具え、前記少なくとも一のその他のリアクタンス回路エレメント(116)が、前記内部シャント並列L-C共振器組合せ( $C^{R^1}$ ,  $L^{R^1}$ )と直列に接続した内部シャントアドミッタンスインバータ( $J_{11}$ )を具え、少なくとも一のその他のリアクタンス回路エレメント(118)が、前記内部シャント並列L-C共振器組合せ( $C^{R^1}$ ,  $L^{R^1}$ )と並列に接続した内部シャント非共振サスセプタンス( $B^{N^1}$ )を具え、前記内部シャント並列L-C共振器組合せ( $C^{R^1}$ ,  $L^{R^1}$ )と、内部シャントアドミッタンスインバータ( $J_{11}$ )と、内部シャント非共振サスセプタンス( $B^{N^1}$ )とが、少なくとも一のBVDモデル(122)の一つに変換されることを特徴とする方法。

【請求項12】

請求項11に記載の方法において、前記内部シャント並列L-C共振器組合せ( $C^{R^1}$ ,  $L^{R^1}$ )と前記内部シャントアドミッタンスインバータ( $J_{11}$ )が、内部シャント直列L-C共振器組合せ(134)に変換され、前記内部シャント直列L-C共振器組合せ(134)と内部シャント非共振サスセプタンス( $B^{N^1}$ )が、一のBVDモデル(122)に変換されることを特徴とする方法。

10

20

30

40

50

## 【請求項 13】

請求項 11 に記載の方法において、前記 BVD モデル (122) が内部シャント BVD モデルであることを特徴とする方法。

## 【請求項 14】

請求項 13 に記載の方法において、前記少なくとも一のリアクタンス回路エレメント (120) が更に、前記内部シャント並列 L-C 共振器組合せ (C<sup>R1</sup>, L<sup>R1</sup>) と内部シャント非共振サスセプタンス (B<sup>N1</sup>) との間のノード (1) に接続された 2 つのインラインアドミッタンスインバータ (J<sub>S1</sub>, J<sub>12</sub>) を具え、前記内部シャント BVD モデル (122) と前記二つのインラインアドミッタンスインバータ (J<sub>S1</sub>, J<sub>12</sub>) が、一のインライン BVD モデル (122a) と当該インライン BVD モデル (122a) と直列に接続されたリアクタンス (X<sub>1</sub>) に変形されることを特徴とする方法。10

## 【請求項 15】

請求項 1 に記載の方法において、前記少なくとも一の共振エレメント (114) が、複数の共振エレメントを具え、前記少なくとも一のその他のリアクタンス回路エレメント (116-120) が複数のリアクタンス回路エレメントを具え、前記少なくとも一の音響共振器モデルが複数の共振器モデル (122) を具えることを特徴とする方法。

## 【請求項 16】

請求項 15 に記載の方法が更に、前記初期フィルタ回路設計を複数のサブセット回路設計 (130a, 130b) に分割するステップを具え、当該サブセット回路設計 (130a, 130b) の各々が、前記共振エレメント (114) の一つと前記複数のリアクタンス回路エレメント (116-120) のうちの一またはそれ以上を具え、各サブセット回路設計について、前記共振エレメント (122) と前記一またはそれ以上のリアクタンス回路エレメント (116-120) が、各々前記音響共振器モデル (122) の一つに変換されることを特徴とする方法。20

## 【請求項 17】

請求項 1 に記載の方法が更に、表面音響波 (SAW) 共振器と、バルク音響波 (BAW) 共振器と、フィルムバルク音響共振器 (FBAR) と、マイクロ電気機械システム (MEMS) 共振器のうちの一つから前記少なくとも一の各共振エレメントのタイプを選択するステップ (ステップ 54) を具えることを特徴とする方法。

## 【請求項 18】

請求項 1 に記載の方法が更に：

前記周波数応答要求を正規化した設計スペースにマッピングするステップであって、前記回路エレメント値が、このマッピングした周波数応答要求に基づいて決定した正規化した値である、ステップ (ステップ 58) と；

前記音響フィルタ回路設計の前記正規化した回路エレメント値を、実際の設計スペースにアンマッピングするステップ (ステップ 66) と；

を具えることを特徴とする方法。

## 【請求項 19】

請求項 1 に記載の方法において、前記少なくとも一の共振エレメント (114) が、複数の共振エレメントであることを特徴とする方法。40

## 【請求項 20】

請求項 19 に記載の方法において、前記予め最適化しフィルタ回路設計の前記複数の共振エレメント (114) が、信号伝送路に沿って配置されて、複数のフィルタソリューションを作成しているオーダを変更するステップと；

前記フィルタソリューションの各々についてパフォーマンスパラメータを計算するステップと；

このパフォーマンスパラメータを互いに比較するステップと；

前記計算したパフォーマンスパラメータの比較に基づいて、前記フィルタソリューションのうちの一つを前記予め最適化した回路設計として選択するステップと；

を具えることを特徴とする方法。50

## 【請求項 2 1】

請求項 1 に記載の方法が更に、前記予め最適化したフィルタ回路設計のエレメントを除去する最適化を行って、前記最終フィルタ回路設計を作成するステップ(ステップ 70)を具えることを特徴とする方法。

## 【請求項 2 2】

請求項 1 に記載の方法において、前記最終フィルタ回路設計が、複数の音響共振器(Res 1 - Res 8)を具え、前記最終フィルタ回路設計の複数の音響共振器(Res 1 - Res 8)の最小共振周波数と最大共振周波数との差が、前記複数の音響共振器(Res 1 - Res 8)の中の单一共振器の最大周波数分離の少なくとも 1 倍であることを特徴とする方法。

10

## 【請求項 2 3】

請求項 2 2 に記載の方法において、前記最終フィルタ回路設計における複数の共振器(Res 1 - Res 8)の最小共振周波数と前記最大共振周波数間の差が、前記複数の共振器(Res 1 - Res 8)の中の单一共振器の最大周波数分離の少なくとも 2 倍であることを特徴とする方法。

## 【請求項 2 4】

請求項 2 2 に記載の方法において、前記最終フィルタ回路設計における複数の共振器(Res 1 - Res 8)の最小共振周波数と前記最大共振周波数間の差が、前記複数の共振器(Res 1 - Res 8)の中の单一共振器の最大周波数分離の少なくとも 3 倍であることを特徴とする方法。

20

## 【請求項 2 5】

請求項 1 に記載の方法において、前記予め最適化したフィルタ回路設計を最適化するステップが、前記予め最適化したフィルタ回路設計をフィルタオプティマイザに入力して前記最終フィルタ回路設計を作成するステップを具えることを特徴とする方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は一般的にマイクロ波フィルタに関し、特に、音響波マイクロ波フィルタに関する。

30

## 【背景技術】

## 【0002】

ロスが小さく、周波数選択性通信アプリケーション用電気信号は、1910年頃から電信電話技術用、特に、長距離ケーブルとワイヤレスリンクに載せた通信信号チャネルの多重化と逆多重化用に開発された。「イメージ」又は「イメージパラメータ」と呼ばれるフィルタの設計法は、Bell Laboratories、とりわけ、George A. Campbell, "Physical Theory of the Electric Wave Filter", The Bell System Technical Journal, Volume I, No. 2 (November 1922); Otto J. Zobel, "Theory and Design of Uniform and Composite Electric Wave-Filters", The Bell System Technical Journal, Volume II, No. 1 (January 1923)によって開発された。これらのフィルタ回路は、インダクタ、キャパシタ、及びトランスフォーマを含む回路エレメントを使用している。

40

## 【0003】

1920年代には、音響波(AW)共振回路、特に、クオーツバルク音響波(BAW)共振回路がいくつかの電気回路フィルタで使用され始めた。AW共振回路の等価回路は、共振振動数と反共振振動数と呼ばれる間隔の狭い二つの周波数を有する。(K. S. Van Dyke, "Piezo-Electric Resonator and its

50

Equivalent Network" Proc. IRE, Vol. 16, 1928, pp. 742 - 764 参照)。このイメージフィルタ設計法は、これらのクオーツ共振回路を用いるフィルタ回路に適用され、「ラダー」と「ラティス」AWフィルタ設計という二つのタイプのAWフィルタ回路となった (L. Espenschied, Electrical Wave Filter, 米国特許第1,795,204号; および、W. P. Mason, "Electrical Wave Filters Employing Quartz Crystals as Elements", The Bell System Technical Journal (1934) 参照)。

## 【0004】

1920年代及び1930年代には、通信アプリケーション用の周波数選択性電気信号フィルタの設計用に、「ネットワーク合成」と呼ばれるようになった、別のアプローチが開発された。この新規なフィルタ回路設計法は、米国のFosterとDarlington (Ronald M. Foster, "A Reactance Theorem," Bell Syst. Tech. J., Vol 3, 2924, pp. 259 - 267 及び S. Darlington, "Synthesis of Reactance 4-poles which produce prescribed insertion loss characteristics", J. Math. Phys., Vol 18, 1939, pp. 257 - 353 参照)、及び、とりわけドイツのCauer (W. Cauer, 米国特許第1,989,545号、1935) によって開発された。

## 【0005】

「ネットワーク合成」では、回路エレメントのタイプと、これらエレメントを相互接続する方法を含む最初の回路構成を選択した後、所望のロスが少ないフィルタ応答を例えれば S21 と S11 といった散乱パラメータなどの複素数周波数依存型回路応答パラメータの形で複素多項式比に変換する。S21 散乱パラメータは、以下の式で表す：

$$[1] H(s) = \frac{N(s)}{D(s)} = K \frac{(s - z_1)(s - z_2) \cdots (s - z_{m-1})(s - z_m)}{(s - p_1)(s - p_2) \cdots (s - p_{n-1})(s - p_n)}$$

ここで、N(s) は分子多項式、D(s) は分母多項式、 $z_i$  ' s は式  $N(s) = 0$  のルート (伝送ゼロ点)、 $p_i$  ' s は式  $D(s) = 0$  のルート (反射ゼロ点)、m は伝送ゼロ点の数、n は反射ゼロ点の数、K は倍率である。(ロスが少ない場合は、伝送ゼロ点は、S21 のゼロ点であり、反射ゼロ点は、S11 のゼロ点である。小さいが無限大の実損が後に回路設計プロセスに加えられると、これらゼロ点が小さくなるが、正確にはゼロではなくなり、最終フィルタの固有振動周波数に対応する。) 次いで、複素多項式比からフィルタ回路エレメントの値を、ロスが少ない場合において正確に「合成」(計算) する。実際は小さく保たれているロスを無視すると、「合成した」回路の応答は、所望の応答関数に合致する。

## 【0006】

1950年代と1960年代には、通信及びその他のアプリケーション用マイクロ波フィルタの設計にネットワーク合成が成功裏に適用された。これらの新しいフィルタは、高 Q 値 (低ロス) 電磁共振器と、これらの共振器間の電磁カップリングを回路エレメントとして使用した (George L. Matthaei et al., Microwave Filters, Impedance-Matching Networks, 及び Coupling Structures, McGraw-Hill Book Company, pp. 95 - 97, 438 - 440 (1964); 及び Richard J. Cameron et al., Microwave Filters for Communication Systems: Fundamentals, Design and Applications, Wiley-Interscience 2007) 参照)。ネットワーク合成は、1960年代の初めには通信及びその他のアプリケーション用の音響波フィルタ設計にも提供された。 (Anatol I. Zverev, Han

10

20

30

40

50

book of Filter Synthesis, John Wiley & Sons, pp. 414 - 498 (1967); 及び Robert G. Kinsman, Crystal Filters: Design, Manufacture, and Application, John Wiley & Sons, pp. 37 - 105 and 117 - 155 (1987) 参照。) この研究では、音響波共振器の共振のみが初期回路構造に含まれている。反共振は、初期回路のエレメント値をネットワーク合成法によって計算した後に回路に加えられた寄生効果として扱われていた。

#### 【0007】

1992年ごろの初めに、薄膜表面音響波(SAW)共振器と薄膜BAW共振器が開発され、マイクロ波周波数(>500MHz)で使用され始めた。Eschenbach 10 タイプのラダー型音響波フィルタ設計の一例であるAWインピーダンスエレメントフィルタ(IEF)設計が用いられた。(O. Ikata, et al., "Development of Low-Loss Bandpass Filters Using Saw Resonators for Portable Telephones", 1992 Ultrasonics Symposium, pp. 111 - 115; 及びKenya Hashimoto, Surface Acoustic Wave Devices in Telecommunications: Modeling and Simulation, Springer (2000), pp. 149 - 161 参照)。SAWやBAW実装におけるイメージ設計AW IEFバンドパスフィルターが、モバイル通信装置の無線周波数(RF)フロントエンドにおけるマイクロ波フィルタリングアプリケーションにしばしば使用されている。モバイル通信工業において最も重要なことは、約500 - 3,500MHzの周波数レンジである。米国では、セルラ通信用の多くの標準周波数帯がある。これらは、帯域2(~1800 - 1900MHz)、帯域4(~1700 - 2100MHz)、帯域5(~800 - 900MHz)、帯域13(~700 - 800MHz)、及び帯域17(~700 - 800MHz)を含み、その他の新たな帯域を含む。

#### 【0008】

特殊なフィルタであるデュプレクサは、モバイル装置のフロントエンドにおける重要な部品である。モデムモバイル通信装置は、同時に送受信を行う(Code Division Multiple Access(CDMA)、Wide-Band Code Division Multiple Access(WCDMA), 又は、Long Term Evolution(LTE)を使い、同じアンテナを使って)。デュプレクサは、ピコワットと同じくらい小さい受信信号から最大パワー0.5Wの送信信号を、分離する。この送信及び受信信号は、搬送波上で異なる周波数で変調され、デュプレクサはこれを選択することができる。そうであっても、デュプレクサは挿入損失が低く、選択性が高く、回路面積が小さく、高パワー処理であり、直線性が高く、低コストでなくてはならない。イメージ設計されたバンドパスAW IEFフィルタは、これらの条件を満たしており、タップ遅延ライン(ロスが大きい)や共振単向性トランステューサ(SPUT)フィルタ(マイクロ波周波数へのスケーリングを防止するのに細線が必要である)のような代替物より良好であり、一般的にデュプレクサでの使用が好まれている。二重モードSAW(DMS)(縦に結合した共振器(LCR)とも呼ばれる)フィルタは、出力のバランスが取れており、阻止率が改善されているため、デュプレクサで受信フィルタとして使用されることがある。(David Morgan, Surface Acoustic Wave Filters With Applications to Electronic Communications and Signal Processing, pp. 335 - 339, 352 - 354 (2007) 参照)。

#### 【0009】

これらの従来のAW IEFフィルタ設計の軽微な変形もこれらのアプリケーションに考えられており(例えば、米国特許第8,026,776号及び米国特許第8,063,717号)、これらは通常、一又はそれ以上の回路エレメント(例えば、キャパシタ、イ

10

20

30

40

50

ンダクタ、又は A W 共振器)を I E F 設計に加えて、特定の回路特性を強化又は追加している。これは、A W I E F 回路への影響が、現在使用しているコンピュータの最適化ツールが、最適化した I E F と比較したときに追加工レメントを加えた後に設計を改良するのに十分小さい場合に行うことができる。このことは、隣接した共振器と反共振器を持つ A W 共振器を含むあらゆる回路における厳しい条件であり、従って、A W I E F の基本的な設計と機能に対しては非常にわずかな変形のみが許される。

【 0 0 1 0 】

パフォーマンスを上げ、サイズの小型化、低コスト化を図り、同調性を持たせるために、改良したマイクロ音響波フィルタが求められている。音響波共振器の合成特性が直接的にネットワーク合成に組み込まれている経路を提供するネットワーク合成が、本発明の主題である。

10

【発明の概要】

【 0 0 1 1 】

本発明によれば、周波数応答要求(例えば、一またはそれ以上の周波数に依存した反射減衰量、入射減衰量、阻止率、及び直線性又は通過帯域(例えば、500 - 3500 MHz レンジ)、及び帯域消去)に応じた音響マイクロ波フィルタの設計方法が提供されている。この方法は、少なくとも一の共振エレメント(例えば、キャパシタとインダクタの並列 L - C 共振器組み合わせ)と少なくとも一の他のリアクタンス回路エレメント(例えば、キャパシタ)を含む複数の回路エレメントを有する初期フィルタ回路構造を選択するステップを具える。

20

【 0 0 1 2 】

選択的な方法は更に、各共振エレメントの構造型を、表面音響波(SAW)共振器、バルク音響波(BAW)共振器、薄膜バルク音響共振器(FBAR)、及びマイクロ電気機械システム(MEMS)共振器のうちから一つを選択するステップを具える。もう一つの選択的な方法は更に、周波数応答要求を正規化した設計スペースにマッピングするステップであって、この場合、回路エレメント値が、マッピングした周波数応答要求に基づいて決定した正規化値であるステップと、音響フィルタ回路設計の正規化した回路エレメント値を実際の設計スペースにアンマッピングするステップを具える。

【 0 0 1 3 】

この方法は更に、周波数応答要求に基づいたロスのない回路応答変数(例えば、スケルファクタを乗じた、伝送ゼロ点を規定する多項式分子と反射ゼロ点を規定する多項式分母の比率の形で)を選択するステップと、この選択した回路応答変数に基づいて各回路エレメント値を選択して初期フィルタ回路設計を行うステップと、を具える。

30

【 0 0 1 4 】

この方法は更に、共振エレメントと他のリアクタンス回路設計を少なくとも一の音響共振器モデルに変形して、音響フィルタ回路設計を成すステップを具える。一実施例では、音響共振器モデルが Butterworth - Van Dyke(BVD) モデルである。この場合、他のリアクタンス回路エレメントが、内部シャント並列 L - C 共振器と組み合わせて直列に接続した内部シャントアドミッタンスインバータと、この内部シャント並列 L - C 共振器と組み合わせて並列につないだ内部シャント非共振性サスセプタンスとを具えており、内部シャントアドミッタンスインバータと、内部シャント非共振性サスセプタンスを BVD モデルの一つに変換するようにしてもよい。例えば、内部シャント並列 L - C 共振器の組み合わせと内部シャントアドミッタンスインバータは、内部シャント直列 L - C 共振器の組み合わせに変換することができ、内部シャント直列 L - C 共振器の組み合わせと内部シャント非共振性サスセプタンスは、一の BVD モデルに変換できる。この場合、一の BVD モデルは、内部シャント BVD モデルであってもよい。この実施例では、リアクタンス回路エレメントが更に、内部シャント並列 L - C 共振器と内部シャント非共振性サスセプタンスとの間のノードに接続した二つのインラインのアドミッタンスインバータを具え、内部シャント BVD モデルとこの二つのインラインアドミッタンスインバータを、一のインライン BVD モデルと、このインライン BVD モデルに直列に

40

50

接続したリアクタンスとに変換することができる。

【0015】

一実施例では、複数の共振エレメントと、複数のリアクタンス回路エレメントと、複数の共振器モデルが設けられている。この場合、本方法は更に、初期フィルタ回路設計を、各々が共振エレメントの一つと、複数のリアクタンス回路エレメントを一またはそれ以上有する複数のサブセット回路設計に分けるステップを具え、各サブセット回路設計について、共振エレメントとリアクタンス回路エレメントが、音響共振器モデルの一つに変換される。

【0016】

この方法は更に、音響フィルタ回路設計に寄生効果を加えて予め最適化したフィルタ回路設計を作るステップと、予め最適化したフィルタ回路設計を最適化して、最終フィルタ回路設計を作るステップ(例えば、予め最適化したフィルタ回路設計をフィルタオプティマイザに入力して、最終フィルタ回路設計を作ることによる)と、この最終フィルタ回路設計に基づいて音響マイクロ波フィルタを構築するステップと、を具える。選択的な方法は更に、予め最適化したフィルタ回路設計のエレメント除去最適化を実行して最終フィルタ回路設計を作るステップを具える。

【0017】

複数の共振エレメントが提供されている場合は、この方法は、選択的に、予め最適化したフィルタ回路設計中の複数の共振エレメントを信号伝送路に沿って配置して、複数のフィルタソリューションを作る順序を変更するステップと、各フィルタソリューションについてパフォーマンスパラメータを計算するステップと、このパフォーマンスパラメータを互いに比較するステップと、計算したパフォーマンスパラメータの比較に基づいて、フィルタソリューションの一つを予め最適化したフィルタ回路設計として選択するステップと、を具える。一の方法において、最終回路設計は、複数の音響共振器を具え、この最終回路設計の複数の音響共振器の最低共振周波数と最高共振周波数との差が、この複数の音響共振器の中の单一共振器の最大周波数分離の、少なくとも1倍、好ましくは少なくとも1の倍、より好ましくは少なくとも3倍である。

【0018】

本発明のその他の及び更なる態様と特徴は、説明のためのものであり、本発明を限定するものではない、好ましい実施例の以下の詳細な説明を読むことで明らかになる。

【図面の簡単な説明】

【0019】

図面は、本発明の好ましい実施例の設計と有用性を示しており、図中、同じ要素には共通の符号が付されている。本発明の上述の及び他の利点と目的がどのように得られるかをよりわかりやすくするために、上記の本発明のより詳細な説明は、貼付図面に記載されている特定の実施例を参照して行う。これらの図面が本発明の典型的な実施例のみを示すものであり、発明の範囲を限定すると考えるべきでないと考えられ、本発明は、貼付図面の使用を通じて追加の特性及び詳細を用いて説明する。

【0020】

【図1】図1は、無線遠隔通信システムを示すブロック図である。

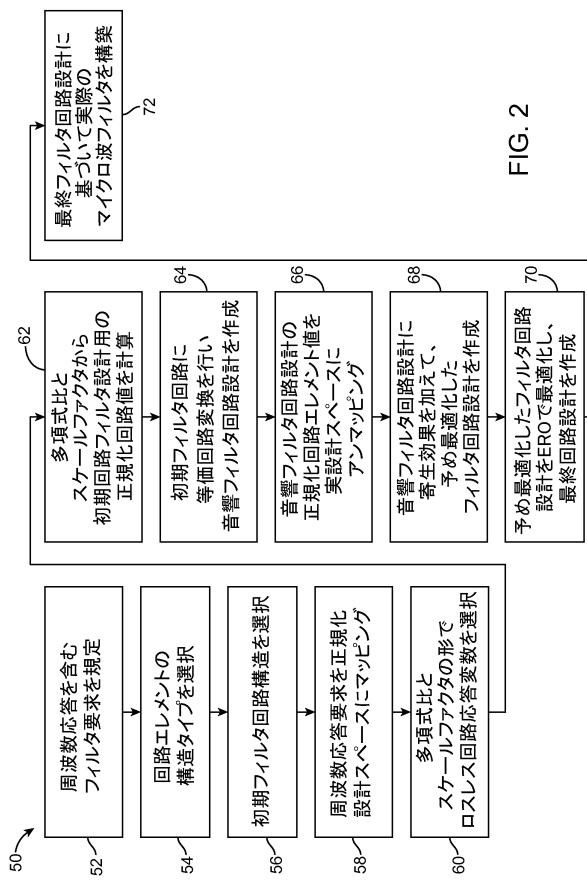

【図2】図2は、本発明の一方法による音響フィルタの設計に用いたネットワーク合成技術を示すフロー図である。

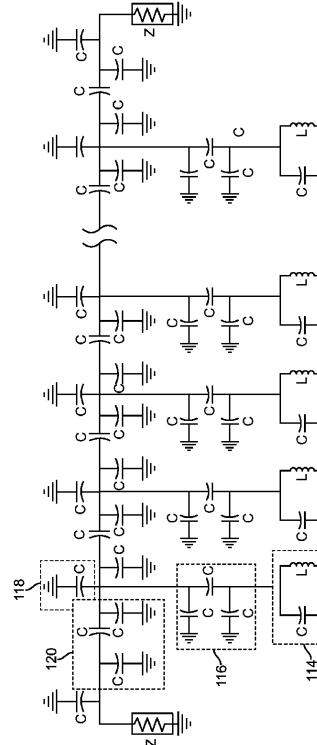

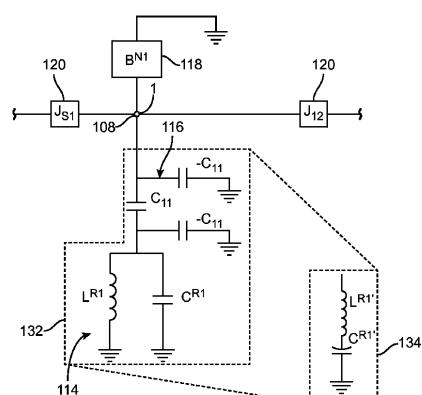

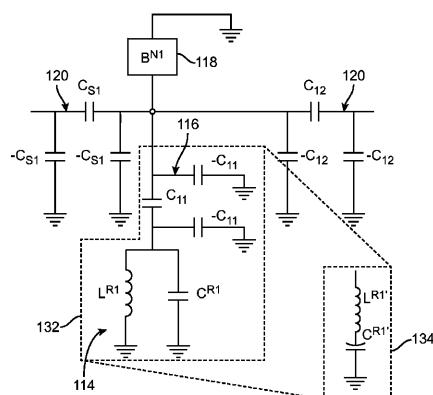

【図3】図3は、図2に示すネットワーク合成技術に用いる初期フィルタ回路構造として使用するインライン非共振ノードフィルタを示す概略図である。

【図4】図4は、図3に示す初期フィルタ回路構造の並列L-C共振器組合せを示す概略図である。

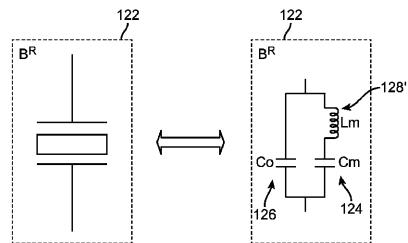

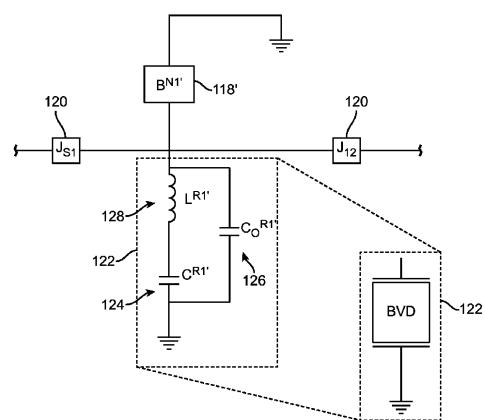

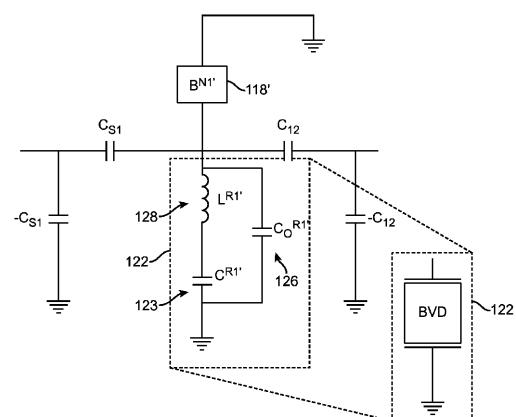

【図5】図5は、Butterworth-Van Dyke(BVD)音響共振器モデルの等価回路を示す概略図である。

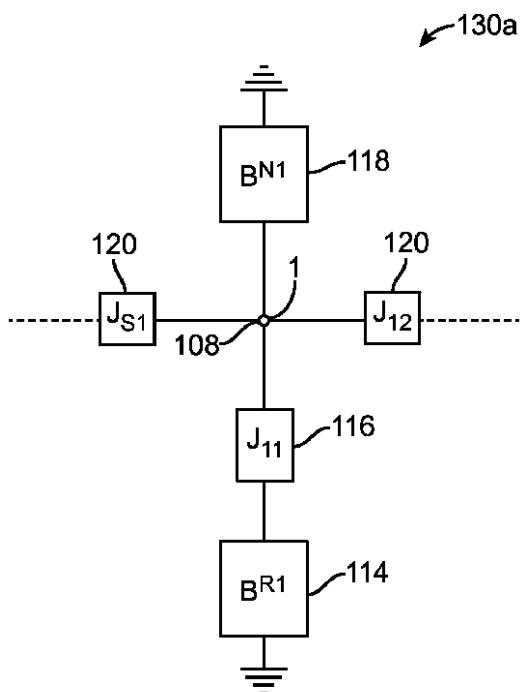

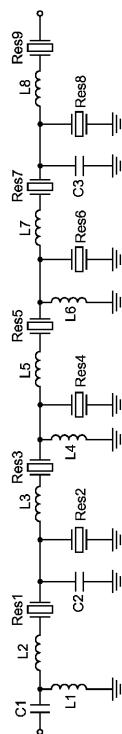

【図6】図6は、図2に示すネットワーク合成技術によって、図3に示す初期フィルタ回路構造(設計)から得た、サブセット回路設計であって、インライン音響共振器が図3の

10

20

30

40

50

初期フィルタ回路設計に組み込まれている。

【図 7】図 7 は、図 2 に示すネットワーク合成技術に応じて、図 6 のサブセット回路設計とシーケンシャルに作った回路変換である。

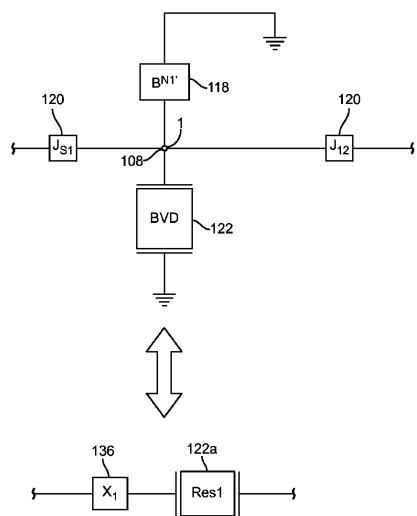

【図 8】図 8 は、図 2 に示すネットワーク合成技術に応じて、図 6 のサブセット回路設計とシーケンシャルに作った回路変換である。

【図 9】図 9 は、図 2 に示すネットワーク合成技術に応じて、図 6 のサブセット回路設計とシーケンシャルに作った回路変換である。

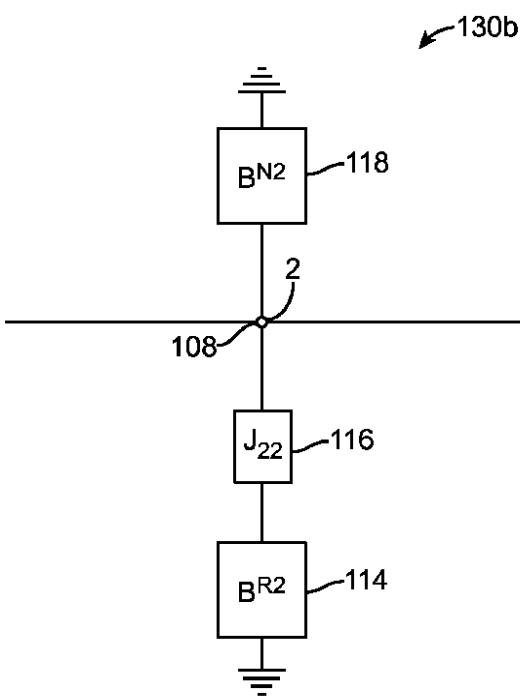

【図 10】図 10 は、図 2 に示すネットワーク合成技術に応じて図 3 の初期フィルタ回路構造からとった別のサブセット回路設計である。

【図 11】図 11 は、図 2 に示すネットワーク合成技術に応じて図 10 のサブセット回路設計にシーケンシャルになされた回路変換であり、図 3 に示す初期フィルタ回路構造に内部シャント音響共振器が組み込まれている。 10

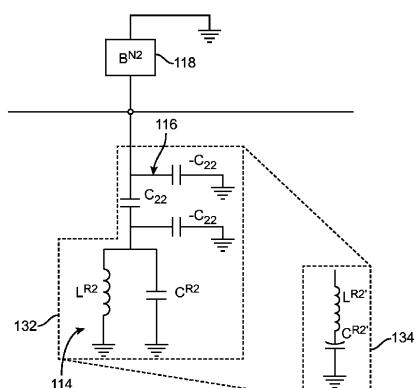

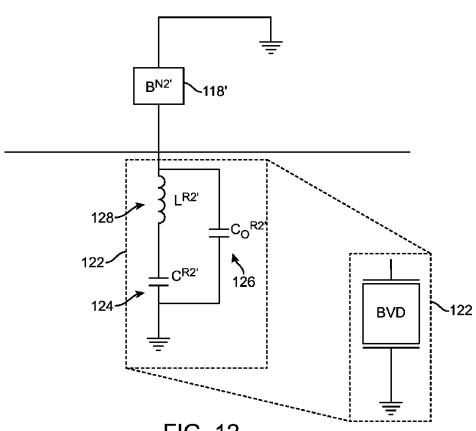

【図 12】図 12 は、図 2 に示すネットワーク合成技術に応じて図 10 のサブセット回路設計にシーケンシャルになされた回路変換であり、図 3 に示す初期フィルタ回路構造に内部シャント音響共振器が組み込まれている。

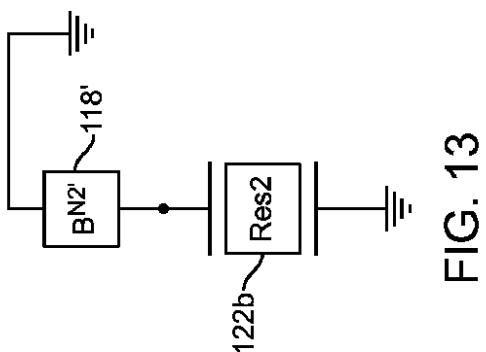

【図 13】図 13 は、図 2 に示すネットワーク合成技術に応じて図 10 のサブセット回路設計にシーケンシャルになされた回路変換であり、図 3 に示す初期フィルタ回路構造に内部シャント音響共振器が組み込まれている。

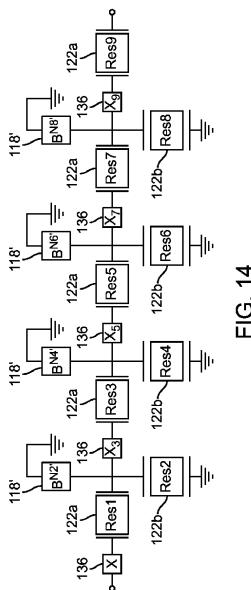

【図 14】図 14 は、図 2 のネットワーク合成技術に応じて図 9 及び 13 に示すサブセット音響回路設計から作った音響フィルタ回路設計の概略図である。 20

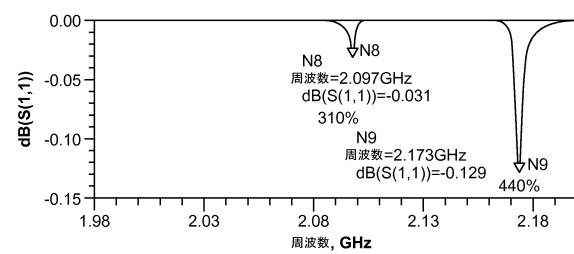

【図 15】図 15 は、図 2 のネットワーク合成技術に応じて、図 14 に示す音響フィルタ回路設計から実現させた予め最適化したフィルタ回路設計を示す概略図である。

【図 16】図 16 は、図 15 に示す予め最適化したフィルタ回路設計のエレメント値を示す表である。

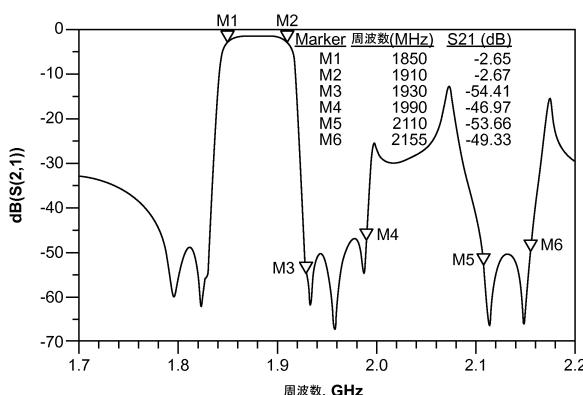

【図 17】図 17 は、図 15 に示す予め最適化したフィルタ回路設計の S 2 1 周波数応答プロットである。

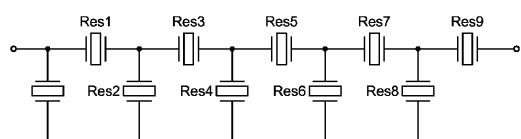

【図 18】図 18 は、図 2 に示すネットワーク合成技術に応じて、予め最適化したフィルタ回路設計をコンピュータ化したフィルタオプティマイザに入力し、エレメント除去設計技術を実行することによって作成した、最適化したフィルタ回路設計の概略図である。 30

【図 19】図 19 は、図 18 に示す最適化したフィルタ回路設計のエレメント値を示す表である。

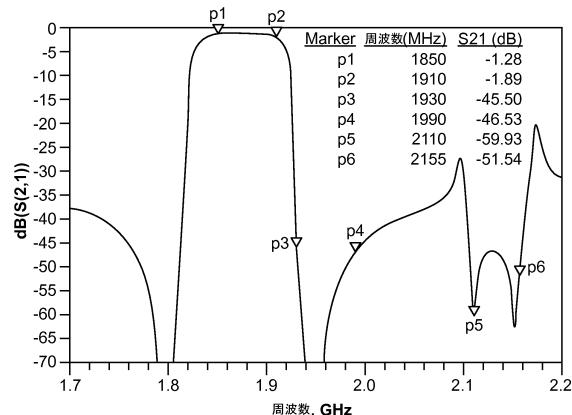

【図 20】図 20 は、図 18 に示す最適化したフィルタ回路設計の S 2 1 周波数応答プロットである。

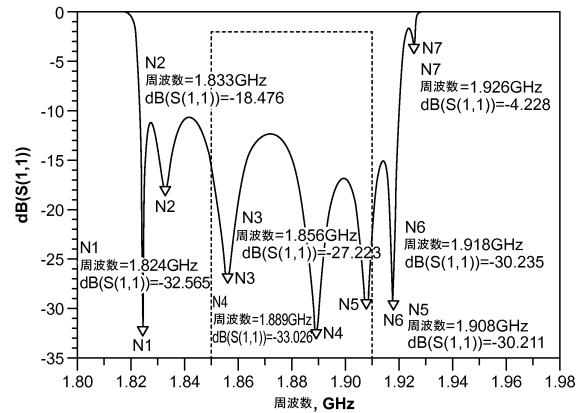

【図 21】図 21 a 及び 21 b は、図 18 に示す最適化したフィルタ回路設計の S 1 1 周波数応答プロットである。

【図 22】図 22 は、図 2 に示すネットワーク合成技術に応じて、図 10 に示すサブセット回路設計にシーケンシャルになされた回路変換であり、図 3 に示す初期フィルタ回路構造に内部シャント音響共振器が組み込まれている。

【図 23】図 23 は、図 2 に示すネットワーク合成技術に応じて、図 10 に示すサブセット回路設計にシーケンシャルになされた回路変換であり、図 3 に示す初期フィルタ回路構造に内部シャント音響共振器が組み込まれている。 40

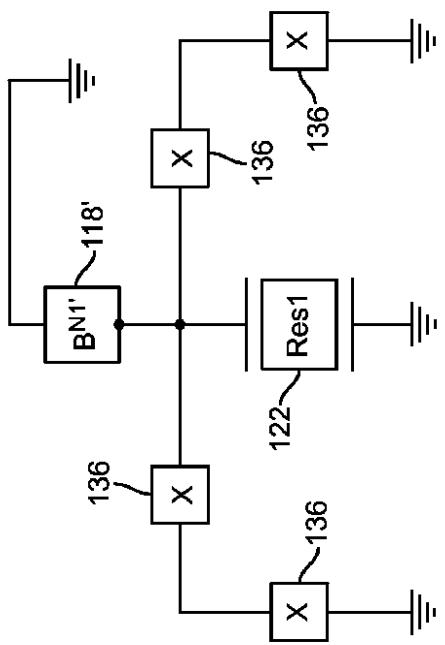

【図 24】図 24 は、図 2 に示すネットワーク合成技術に応じて、図 10 に示すサブセット回路設計にシーケンシャルになされた回路変換であり、図 3 に示す初期フィルタ回路構造に内部シャント音響共振器が組み込まれている。

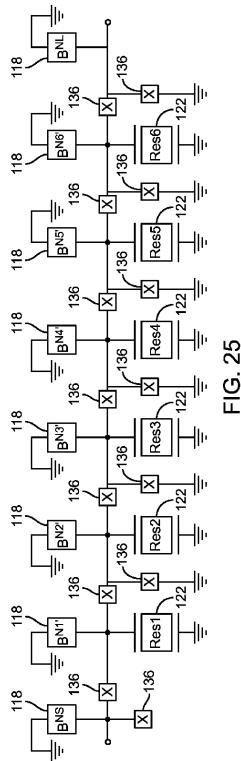

【図 25】図 25 は、図 2 に示すネットワーク合成技術に応じて、図 24 に示すサブセット音響回路設計から作った音響フィルタ回路設計を示す概略図である。

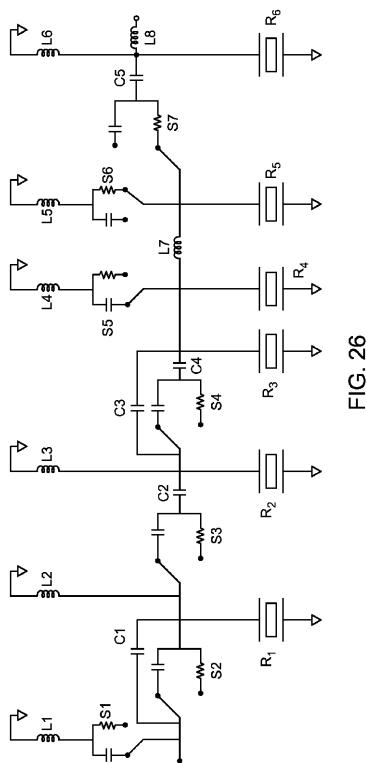

【図 26】図 26 は、図 2 に示すネットワーク合成技術に応じて、図 25 に示す音響フィルタ回路構造から実現した別の予め最適化したフィルタ回路設計の概略図である。

【図 27】図 27 は、図 26 に示す予め最適化したフィルタ回路設計のエレメント値を示す表である。 50

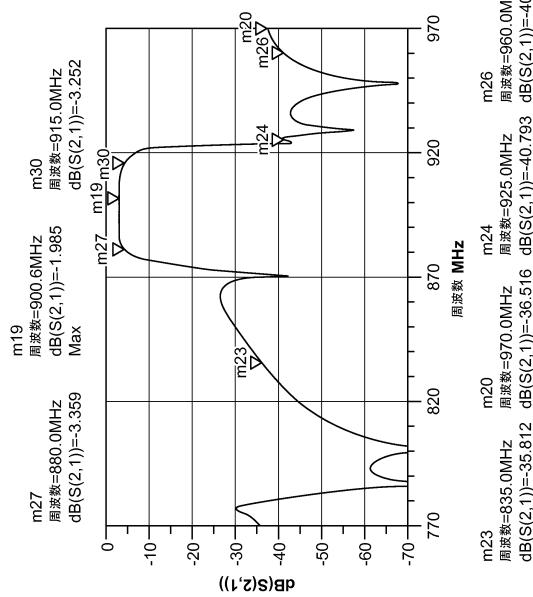

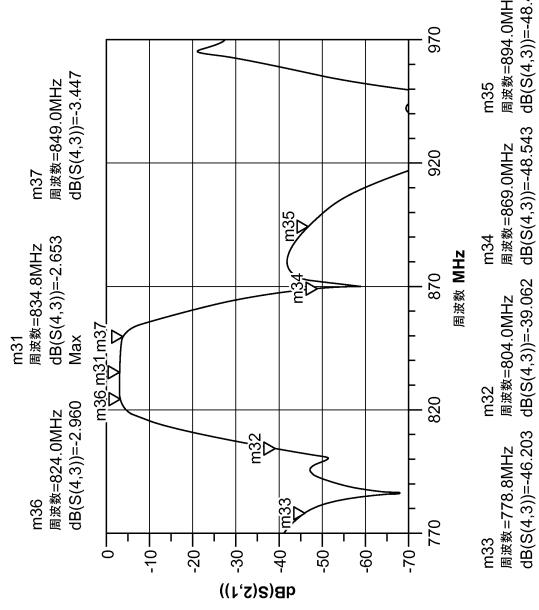

【図28】図28は、最適化を行った後の図25に示すフィルタ回路設計のS21帯域5の周波数応答プロットである。

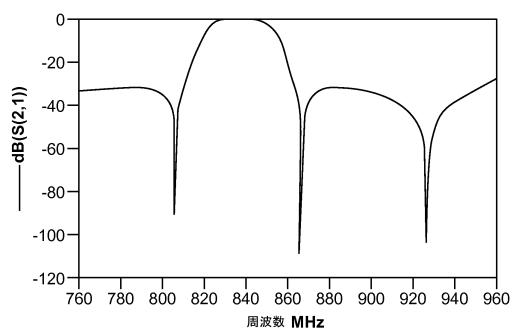

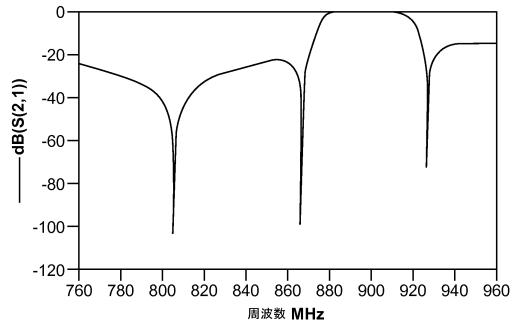

【図29】図29は、最適化を行った後の図25に示すフィルタ回路設計のS21帯域8の周波数応答プロットである。

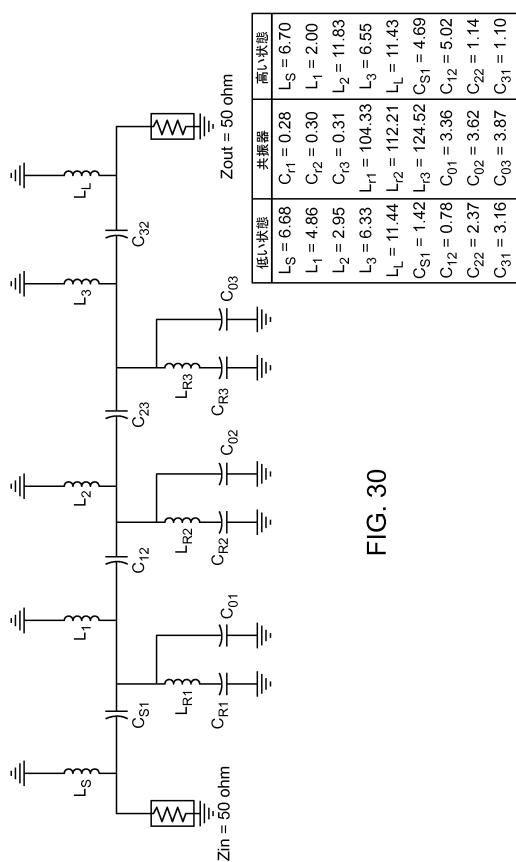

【図30】図30は、図2に示すネットワーク合成技術に応じて作成した、さらに別の求め最適化したフィルタ回路設計を示す概略図である。

【図31】図31は、最適化を行った後の図30に示すフィルタ回路設計のS21帯域5の周波数応答プロットである。

【図32】図32は、最適化を行った後の図30に示すフィルタ回路設計のS21帯域8の周波数応答プロットである。

#### 【発明を実施するための形態】

##### 【0021】

本開示は、音響波(AW)マイクロ波フィルタ(表面音響波(SAW)、バルク音響波(BAW)、膜バルク音響共振器(FBAR)、マイクロ電気機械システム(MEMS)フィルタ、など)を設計するネットワーク合成技術を記載している。このネットワーク合成技術は、以前のAWマイクロ波フィルタ(設計法を超えて、より良好なパフォーマンス、及び/又は、より低コストのAWマイクロ波フィルタ(すなわち、500MHzより大きい周波数)を作る。このようなAWマイクロ波フィルタは固定周波数であっても、及び/又は、調整可能なフィルタ(周波数及び/又は帯域及び/又は入カインピーダンス及び/又は出カインピーダンスが調整可能)であってもよく、単帯域又は複数帯域バンドパスフィルタリング及び/又はバンドストップ用に使用できる。このようなAWマイクロ波フィルタは、セルホン、スマートホン、ラップトップコンピュータ、タブレットコンピュータ、その他を含むモバイル通信装置の無線周波数(RF)フロントエンド、または、M2Mデバイス、無線ベース基地、衛星通信システム、その他を含む固定通信装置のRFフロントエンドに見られるような、電気的及び/又は環境的パフォーマンス条件及び/又はコスト/サイズに厳しい制限が要求されるアプリケーションにおいて有利である。

##### 【0022】

ここに述べた例示のAWマイクロ波フィルタ(例えば、図28-29)は、単通過帯域及び単阻止帯域をもつ周波数応答を示しており、これは、阻止帯域が近接した通過帯域が求められる通信システムデュプレクサに特に有用である。例えば、図1を参照すると、モバイル通信装置に用いる通信システム10は、無線信号を送受信できるトランシーバ12と、トランシーバ12の機能を制御できるコントローラ/プロセッサ14を具える。トランシーバ12は、一般的に、広帯域アンテナ16、送信フィルタ24と受信フィルタ26を有するデュプレクサ18、デュプレクサ18の送信フィルタ24を介してアンテナ16に接続されているトランスマッタ20、及びデュプレクサ18の受信フィルタ26を介してアンテナ16に接続されているレシーバ22、を具える。

##### 【0023】

トランスマッタ20は、コントローラ/プロセッサ14によって提供されるベースバンド信号を無線(RF)信号に変換するように構成したアップコンバータ28と、このRF信号を増幅するように構成された可変利得増幅器(VGA)30と、このRF信号をコントローラ/プロセッサ14によって選択された動作周波数で出力するように構成したバンドパスフィルタ32と、次いでフィルタにかけてデュプレクサ18の送信フィルタ24を介してアンテナ16に提供されるRF信号を増幅するように構成した電力増幅器34を具える。

##### 【0024】

受信器22は、受信フィルタ26を介してアンテナ16から入力したRF信号からの送信信号干渉を阻止するよう構成したノッチ又は阻止帯域フィルタ36と、比較的ノイズが低い阻止帯域フィルタ36からのRF信号を増幅するように構成した低ノイズ増幅器(LNA)38と、増幅したRF信号をコントローラ/プロセッサ14によって選択された周波数で出力するように構成したバンドパスフィルタ40と、RF信号をコントローラ/プロ

10

20

30

40

50

ロセッサ 14 に提供されるベースバンド信号にダウンコンバートするように構成されたダウンコンバータ 42 と、を具える。代替的に、阻止帯域フィルタ 36 によって実行される送信信号干渉を阻止する機能は、デュプレクサ 18 によって代わりに行うことができる。あるいは、トランスマッタ 20 の電力増幅器 34 は、送信信号干渉を低減するように設計することができる。

【0025】

図 1 のブロック図は、自然に機能しており、いくつかの機能を一の電子部品で実行できる、又は一の機能をいくつかの電子部品で実行できることは自明である。例えば、アップコンバータ 28、VAG 30、バンドパスフィルタ 40、ダウンコンバータ 42、及びコントローラ / プロセッサ 14 によって実行される機能は、単一のトランシーバチップで実行されることがある。バンドパスフィルタ 32 の機能は、電力増幅器 34 とデュプレクサ 18 の送信フィルタ 24 によって実行することができる。

【0026】

本明細書に記載の例示的なネットワーク合成技術は、遠隔通信システム 10 のフロントエンド用音響マイクロ波フィルタ、特にデュプレクサ 18 の送信フィルタ 24 を設計するのに使用されるが、同じ技術を、デュプレクサ 18 の受信フィルタ 26 及びその他の RF フィルタの音響マイクロ波フィルタを設計するのに使用することができる。

【0027】

ここで、図 2 を参照して、AW マイクロ波フィルタを設計する一例示的ネットワーク合成技術を説明する。まず、周波数応答要求（通過帯域、リターンロス、挿入口ス、阻止率、直線性、ノイズ指数、入力及び出力インピーダンス、その他を含む）、並びにサイズ及びコスト要求、及び、動作温度範囲、振動、欠陥率、その他といった環境要求を含む、フィルタ条件が、フィルタのアプリケーションによって設定される（ステップ 52）。図に示す実施例では、この設計は、以下の条件：最大挿入口ス要求が 2 dB の 1850 MHz 乃至 1910 MHz までの第一の通過帯域と、最小阻止率が 44 dB の 1930 MHz から 1990 MHz までの第 1 の阻止帯域と、最小阻止率が 20 dB の 2010 MHz から 2025 MHz までの第 2 の阻止帯域と、最小阻止率が 45 dB の 2110 MHz から 2155 MHz までの第 3 の阻止帯域である 3 つの阻止帯域、をターゲットにしている。

【0028】

次いで、AW フィルタに使用している回路エレメントの構造タイプを選択する。例えば、共振器の構造タイプ（SAW、BAW、FBAR、MEMS、その他）と、インダクタ、キャパシタ、及びスイッチのタイプ、及びこれらの回路エレメントの製造に使用する、パッケージを含む材料、及びフィルタを製造する組み立て技術、を選択する（ステップ 54）。この明細書に記載した特定の例での回路エレメントタイプの選択は、42 度 XY - カット LiTaO<sub>3</sub> でできた基体上に構成した SAW 共振器とキャパシタである。

【0029】

次いで、インライン非共振ノード、又はインライン、又はクロスカップリングを有するインライン、又はクロスカップリングを有するインライン非共振ノード、といった初期回路構造を、周波数応答要求から得られる通過帯域及び / 又は阻止帯域に基づいて選択する（ステップ 56）。図に示す実施例では、選択した初期回路構造が、米国特許第 7,719,382 号、7,639,101 号、7,863,999 号、7,924,114 号、8,063,714 号や、米国暫定特許出願第 61/802,114 号の「マイクロ波フィルタにおけるエレメント除去設計」に記載されているような、インライン非共振ノード構造である。本明細書の目的では、用語「構造」とは、エレメントの値には関係なく、エレメントタイプとその内部接続を意味する。

【0030】

図 3 を参照すると、インライン非共振ノードタイプの初期フィルタ回路構造 100 の一実施例は一般的に、入力 104（ノード S で示す）と出力 106（ノード L で示す）を有する信号伝送路 102 と、この信号伝送路 102 に沿って配置した複数のノード（ノード S, 1, 2, ..., n で示す）108 と、ノード 108 をそれぞれ接続している複数の共

10

20

30

40

50

振ブランチ 110 と、共振ブランチ 110 に並列にノード 108 をそれぞれ設置している複数の非共振ブランチ 112 と、を具える。

【0031】

初期フィルタ回路構造 100 は更に、それぞれ共振ブランチ 110 に配置した複数の内部シャント共振エレメント 114 (サセプタンス  $B^R_1, B^R_2, \dots, B^R_n$  で示す) と、共振エレメント 114 と直列に接続した複数の内部シャント非共振エレメント 116 (アドミッタンスインバータ  $J_{11}, J_{22}, \dots, J_{nn}$  で示す) とを具える。初期フィルタ回路構造 100 は更に、複数の内部シャント非共振エレメント 118 を見え、このうちの二つがノード S とノード L を接地しており (それぞれ、サセプタンス  $B^N_S$  と  $B^N_L$  で示す)、4 つはそれぞれ非共振ブランチ 110 に位置している ( $B^N_1, B^N_2, \dots, B^N_n$  で示す)。初期フィルタ回路構造 100 は更に、それぞれ、ノード S、1、2、…、n、L を互いに接続している、複数のインライン非共振エレメント 120 (アドミッタンスインバータ  $J_{S1}, J_{12}, J_{23}, \dots, J_{n-1}, J_n, J_{nL}$  で示す) を具える。

【0032】

初期フィルタ回路構造 100 は更に、共振エレメント 114 の周波数、及び / 又は非共振エレメント 120 の値を調整する複数の調整エレメント (図示せず) と、初期フィルタ回路構造 100 を、非共振エレメント 116 - 120 の選択した周波数レンジを変化させて所望の周波数レンジ内で選択した狭帯域に調整するように構成した電気コントローラ (図示せず) を具えていてもよい。このように、初期フィルタ回路構造 100 は、サスセプタンス  $B^R$  の値を実現するのに使用した高 Q ファクタ共振エレメント 114 が、図 4 に示すように、並列 L - C 共振器組み合わせ、すなわちタンク回路によって特徴づけられるのであれば、再構成可能なバンドパスフィルタのネットワーク合成用に有益である。

【0033】

高 Q ファクタ共振エレメント 114 は、図 5 に示す Butterworth-Van Dyke (BVD) モデル 122 を用いて説明できる。BVD モデル 122 は、SAW 共振器を説明でき、この共振器は、クリスタルクォーツ、リチウムニオベート (LiNbO<sub>3</sub>)、リチウムタンタレート (LiTaO<sub>3</sub>) クリスタルといった圧電基体上に櫛形変換器 (IDTs)、あるいは、クォーツ又は窒化アルミニウムといった物質に作った BAW (FBAR を含む) 共振器、又は MEMS 共振器を配置することによって作成できる。BVD モデル 122 は、直列容量  $C_m 124$  と、静電容量  $C_0 126$  と、直列インダクタンス  $L_m 128$  を具える。直列容量  $C_m 124$  と直列インダクタンス  $L_m 128$  は、電気的及び音響的挙動の相互作用の結果であり、従って、BVD モデル 122 の動作アームと呼ばれる。静電容量  $C_0 126$  は、その構造単独 (コンダクタ、誘電体及びギャップ) の電気的挙動から生じるため、BVD モデル 122 の静電 (非モーション) 容量と呼ばれる。パラメータは以下の式による。

$$[2] \omega_R = \frac{1}{\sqrt{L_m C_m}};$$

$$[3] \frac{\omega_A}{\omega_R} = \sqrt{1 + \frac{1}{\gamma}},$$

ここで、 $\omega_R$  と  $\omega_A$  は、それぞれ所定の音響共振器についての共振周波数と非共振周波数であり、 $\gamma$  は、材料の特性により、更に

$$[4] \frac{C_0}{C_m} = \gamma.$$

によって規定される。

典型的な  $\gamma$  値は、42 度 XY カット LiTaO<sub>3</sub> について、約 12 から約 18 の範囲である。音響共振器の周波数分離は、共振周波数と非共振周波数間の差を意味する。音響波共

10

20

30

40

50

振器のパーセンテージ分離は、共振周波数と非共振周波数間のパーセンテージ周波数分離であり、以下の式で計算できる。

$$[8] \text{ パーセンテージ分離} = \sqrt{1 + \left(\frac{1}{\gamma}\right)} - 1$$

ここで、 $\gamma$  は、共振器の直列容量に対する静電容量の比（式（4））であり、圧電材料の材料特性によって決まると共に、デバイスのジオメトリによって変化する。

#### 【0034】

音響共振器の共振周波数  $\omega_R$  は、インピーダンスの大きさが極小になり、インピーダンスの位相がゼロ交差する周波数を意味する。音響共振器の非共振周波数  $\omega_A$  は、インピーダンスの大きさが極大になり、インピーダンスの位相がゼロ交差する周波数を意味する。 10

#### 【0035】

式（1）より、各音響共振器の共振周波数が B V D モデル 122 の動作アームに依存しており、一方で、フィルタ特性（例えば、帯域幅）は、式（2）の  $\gamma$  によって強く影響を受けることが明らかである。音響共振器 122 の品質係数（Q）は、フィルタ内のエレメントのロスに関連して、音響フィルタ設計における利点の重要な特徴である。回路エレメントの Q は、サイクルごとに保存されるエネルギーと、サイクルごとに消えるエネルギーとの比率を表す。Q 因子は、各音響共振器中の実際のロスをモデルにし、音響共振器中のロスを述べるのには、一般的に一以上の Q ファクタが必要である。Q ファクタは、フィルタの実施例について以下のように規定することができる。直列キャパシタンス  $C_{cm}$  は、 $Q_{cm} = 10^8$  と規定される関連する Q を有していてもよく、静電容量  $C_0$  は、 $Q_{c0} = 200$  で規定される関連する Q を有していてもよく、直列インダクタンス  $L_m$  は、 $Q_{Lm} = 1000$  で規定された関連する Q を有する。（ここで、明確化のために、直列共振におけるロスは、直列インダクタンスにまとめられ、直列容量は、実質的にロスがないと考えられる。回路設計者は、通常、S A W 共振器を、共振周波数  $\omega_R$ 、静電容量  $C_0$ 、 $\gamma$ 、及び品質ファクタ  $Q_{Lm}$  によって特徴づける。市販のアプリケーション用には、 $Q_{Lm}$  が S A W 共振器については約 1000、S A W 共振器については、約 1000、B A W 共振器については約 3000 である。 20

#### 【0036】

図 2 を参照すると、周波数応答要求を次いで、正規化設計スペースにマッピングする（ステップ 58）。このマッピングは、平方二乗根 / 二次マッピング技術（George L. Matthaei, Microwave Filters, Impedance-Matching Networks, and Coupling Structures, McGraw-Hill Book Company, pp. 95-97, 437-440 (1964) 参照）、又は、音響波共振器により適している、対数 / 指数マッピング技術など、適切なアルゴリズムを使用して行う。 30

#### 【0037】

好みの対数マッピング技術の一つに、以下の式を使用する。

$$[5] \Omega = \ln\left(\frac{\omega^2}{\omega_p^2}\right) / \ln\left(1 + \frac{1}{\gamma}\right),$$

$$[6] |\Omega_R - \Omega_A| = 1$$

ここで、 $\omega_p / 2$  は、通過帯域又は阻止帯域の幾何学的中心周波数であり、 $\omega_R / 2$  は、実際の周波数であり、 $\omega_A$  はマッピングした周波数であり、 $\omega$  は、共振器の静電容量と直列容量の比であり、 $\omega_R$  は、共振器のマッピングした共振周波数であり、 $\omega_A$  は、共振器のマッピングした非共振周波数である。 40

#### 【0038】

次いで、ロスの内回路応答変数が、式（1）にあるように、スケールファクタを乗じた

、伝達ゼロ点を規定する分子多項式と反射ゼロ点を規定する分母多項式の比の形式で提供される(ステップ60)。一般的に、伝達ゼロ点の総数が、反射ゼロ点の総数と同じかそれ以上であり、しばしば一またはそれ以上の反射ゼロ点がフィルタの通過帯域外にある。

#### 【0039】

次いで、カップリングマトリックス又はパラメータ抽出法あるいは同等の回路合成技術を用いて、初期フィルタ回路構造100のマッピングして正規化した回路エレメント値をこれらの多項式から計算し(ステップ62)、初期ロスレス回路設計を作成する。この明細書の目的では、「回路設計」とは、回路構造を作り上げるエレメントの値を考慮した回路構造を意味する。

#### 【0040】

次いで、等価回路変換を行って、回路エレメント数を減らす、あるいは、回路エレメントのタイプ、回路のサイズ、あるいは個々の回路エレメントの実現可能性を変更して、音響フィルタ回路設計を作成する(ステップ64)。これらの変換は、初期のロスレス回路設計の応答性を実質的に変更するものではなく、Jインバータを等価容量性又は導電性P1-又はT-ネットワークに透過するといった、等価回路変換を用いることができる。例えば、シャント共振器/2つのJインバータ組み合わせは、単一の直列共振器に変換でき、単一の共振器/二つのJ-インバータ組み合わせは、単一のシャント共振器に変換でき、多重並列キャパシタンスは、単一のキャパシタに組み合わせることができ、あるいは、キャパシタを減らすために、正の並列キャパシタと組み合わせて負キャパシタを外し、単一の正キャパシタとしてもよく、複数の直列インダクタは、組み合わせて単一のインダクタにするか、あるいは、インダクタを減らすために、正の直列インダクタと組み合わせることによって負のインダクタを外し、単一の正インダクタとする、または、その他の等価回路変換を行って、初期ロスレス回路設計より、より小さく、コストがより低く、及び/又は、より実現可能性が高いが、目的の回路応答を有するロスのない回路を得ることができる。

#### 【0041】

音響共鳴エレメントB<sup>R</sup>は、図5に示すBVDモデル122によって詳しく説明されているが、BVDモデル122は、追加の静電容量C<sub>0</sub>があるため、図4に示すL-C等価初期フィルタ回路設計100に直接組み込むことができないという問題がある。特定タイプの回路変換には、初期フィルタ回路設計100を、音響共振器モデルと、この場合はBVDモデル122を組み込むことができる適宜の構造に変換するステップが含まれる。この回路変換は、初期フィルタ回路設計100を共振エレメント114の数に等しい複数のサブセットに分けることによって最もよく実行される。各サブセットは、各ノードに接続された回路エレメントを具えており、このノードは共振ブランチ110と非共振ブランチ112が接続されている。各サブセットの性質は、シャント音響共振器が必要か、又はインライン音響共振器が必要かによって決まる。

#### 【0042】

例えば、インライン音響共振器を初期フィルタ回路設計100に組み入れている変換技術では、特定のサブセット回路設計が、各ノード108から接地された共振エレメント114(サスセプタンスB<sup>R</sup>)、この共振エレメント114と直列に接続された非共振エレメント116(アドミッタンスインバータJ)、各ノード108から共振エレメント(サスセプタンスB<sup>R</sup>)と並列に接地された非共振エレメント118(サスセプタンスB<sup>N</sup>)と、各ノード108にインラインで接続された二つの非共振エレメント120(アドミッタンスインバータJ)を具える。例えば、図6に示すように、サブセット130aはノード1を具えており、従って、共振エレメントB<sup>R1</sup>は各ノード108からグラウンドに接続されており、アドミッタンスインバータエレメントJ<sub>11</sub>は、共振エレメントB<sup>R1</sup>に直列に接続されており、非共振エレメントB<sup>N1</sup>は、各ノード108から共振エレメントB<sup>R1</sup>と並列にグラウンドに接続されており、二つのアドミッタンスインバータJ<sub>s1</sub>とJ<sub>12</sub>が、各ノード108とインラインで接続されている。

#### 【0043】

10

20

30

40

50

図7に示すように、アドミッタンスインバータ $J_{1,1}$ は、容量性PI-ネットワーク(キャパシタ- $C_{1,1}$ 、 $C_{1,1}$ 、及び- $C_{1,1}$ )と入れ替わっており、共振エレメント $B_{1,R}$ は、インダクタンス(インダクタ $L^{R,1}$ )とキャパシタンス(キャパシタ $C^{R,1}$ )の並列L-C共振器組合せで置き換えられている。キャパシタ- $C_{1,1}$ 、 $C_{1,1}$ 及び- $C_{1,1}$ からなるPI-ネットワークと、インダクタ $L^{R,1}$ とキャパシタ $C^{R,1}$ の並列L-C共振器組合せで表される回路サブ構造132は、インダクタンス(インダクタ $L^{R,1}$ )とキャパシタンス(キャパシタ $C^{R,1}$ )でできた直列L-C共振器組合せに変換できる。重要なことに、この直列L-C組み合わせ134が、BVDモデル122の直列共振レッグによって実現でき、従って、回路サブ構造132により良好に組み入れることができる。

## 【0044】

10

BVDモデル122を回路サブ構造132に組み入れるためには、BVDモデル122の静電容量 $C_0$ が対応していなければならぬ。これは、図8に示すように、並列サスセプタンス $B_{1,N}$ をキャパシタンス( $C_0^{R,1}$ とサスセプタンス $B^{N,1}$ )で置き換えることによって対応する。 $C_0^{R,1}$ は、BVDモデル122の静電容量であり、 $B^{N,1}$ は、 $B^{N,1} - (C_0^{R,1})$ の関係式で与えられる。サスセプタンス $B^{N,1}$ と、二つのインライニアドミッタンスインバータ $J_{S,1}$ 及び $J_{1,2}$ と、シャント音響共振器122は、図9に示すように、インライイン音響共鳴器122aと直列リアクタンス136( $X_1$ で示す)に変換できる。

## 【0045】

20

内部シャント音響共鳴器を初期フィルタ回路設計100に組み入れる変換技術では、特定のサブセットが、各ノード108から接地している共振エレメント114(サスセプタンス $B^R$ )と、共振エレメント114に直列に接続している非共振エレメント116(アドミッタンスインバータ $J$ )と、各ノード108から、共振エレメント114(サスセプタンス $B^R$ )と並列に接地している非共振エレメント118(サスセプタンス $B^N$ )を具える。例えば、図10に示すように、サブセット130bは、ノード2を具え、従って、共振エレメント $B^{R,2}$ は、各ノード108から接地されており、アドミッタンスインバータ $J_2$ は、各ノード108から接地されており、アドミッタンスインバータエレメント $J_2$ は、共振エレメント $B^{R,2}$ と直列に接続されており、非共振エレメント $B^{N,2}$ は、各ノード108から共振エレメント $B^{R,2}$ と並列に接地されている。

## 【0046】

30

図11に示すように、アドミッタンスインバータ $J_{2,2}$ は、容量性PI-ネットワーク(キャパシタ- $C_{2,2}$ 、 $C_{2,2}$ 、及び- $C_{2,2}$ )に交換されており、共振エレメント $B^{R,2}$ は、インダクタンス(インダクタ $L^{R,2}$ )とキャパシタンス(キャパシタ $C^{R,2}$ )の並列L-C共振器組合せに交換されている。キャパシタ- $C_{2,2}$ 、 $C_{2,2}$ 及び- $C_{2,2}$ からなるPI-ネットワークで表される回路サブ構造132と、インダクタ $L^{R,2}$ とキャパシタ $C^{R,2}$ の並列L-C共振器組合せは、インダクタンス(インダクタ $L^{R,2}$ )とキャパシタンス(キャパシタ $C^{R,2}$ )の直列L-C組み合わせ134に変換できる。重要なことは、直列L-C組み合わせ134は、BVDモデル122の直列共振レッグで実現でき、従って、回路サブ構造132により良好に組み込むことができる。

## 【0047】

40

BVDモデル122を回路サブ構造132に組み入れるためには、BVDモデル122の静電容量 $C_0$ に対応していなくてはならない。これは、図12に示すように、並列サスセプタンス $B^{2,N}$ をキャパシタンス( $C_0^{R,1}$ とサスセプタンス $B^{N,1}$ )で置き換えることによって対応する。 $C_0^{R,2}$ は、BVDモデル122の静電容量であり、 $B^{N,2}$ は、 $B^{N,2} - (C_0^{R,2})$ の関係式で与えられる。このように、内部シャント音響共振器122bは、図13に示すようにして実現できる。

## 【0048】

初期フィルタ回路設計100を、代替のサブセット130aと130bに分割することができ、代替のインライイン音響共振器122aと内部シャント共振器122bを有するフィルタ回路設計100ができることは、自明である。例えば、9個の共振器 $B^R$ を有する

50

初期フィルタ回路設計 100 は、図 14 に示すように、代替の態様に設置された 5 個のインライン音響共振器 122a と 4 個の内部シャント音響共振器 122b を有する音響フィルタ回路構造 150a に変換できる。

#### 【0049】

回路変換ステップは、初期フィルタ回路設計上で実行できる（すなわち、マッピングし、正規化した回路エレメント値を計算した後）として説明したが、この回路変換ステップが初期フィルタ回路構造（すなわち、マッピングし、正規化した回路エレメント値を計算する前）上で実行して、音響回路構造を作ることができることは明らかである。この場合、音響フィルタ回路構造についてマッピングして正規化した回路エレメント値を計算して、音響フィルタ回路設計を行うことができる。

10

#### 【0050】

図 2 に戻ると、音響フィルタ回路設計 150a の回路エレメントは、正規化した設計スペースにマッピングするのに初期に使用したマッピング技術の逆となり、実際の設計スペース（すなわち、実周波数をもつロスのない回路エレメント（L' 及び C'）にマッピングされていない（ステップ 66）。例えば、式（5）の対数マッピング技術を用いて、周波数応答要求を正規化したスペースにマッピングして、以下の対数アンマッピング式を用いて、正規化した回路エレメント値を実際の設計スペースにアンマッピングすることができる。

$$[7] \omega = \omega_p \left( 1 + \frac{1}{\gamma} \right)^{\Omega/2}$$

20

特に、B の値は、B のサインに応じて L 又は C のいずれによっても実現できる。正規化した回路値のアンマッピングは、図 16 に示す共振周波数  $\omega_R$  の値及び各共振器の静電容量  $C_0$ 、及びキャパシタ及びインダクタのキャパシタンスとインダクタンスと共に、図 15 に示す現実の回路を作る。これは、シミュレーションを行ったときに、図 17 に示す周波数応答となる。（インダクタ L1 とキャパシタ C1 を、極性抽出によって合成の最後に加え、ネットワークの等価入力及び出力インピーダンスを提供する）。

#### 【0051】

次いで、Sonnet（登録商標）ソフトウェアなどの電磁シミュレータを用い、予め最適化したフィルタ回路設計に到達する母線（相互接続）ロスを加えて、寄生効果を音響フィルタ回路設計 150a に加える（ステップ 68）。音響共振器のロスは、各回路エレメントの Q ファクタを関連させることによって含めることができる。この実施例では、等価直列容量  $C_{m124}$  は、 $Q_{c_{m124}} = 10^8$  で規定される関連する Q ファクタを有しており；静電容量  $C_{0126}$  は、 $Q_{c_{0126}} = 200$  で規定される関連する Q ファクタを；及び、等価直列インダクタンス  $L_{m128}$  は  $Q_{L_{m128}} = 1000$  で規定される関連する Q ファクタを有している。残りのインダクタは、 $Q_u = 60$  で規定される関連する Q ファクタを有し、残りのキャパシタは、 $Q_u = 200$  で規定される関連する Q ファクタを有する。RS = 0.5 オームの母線（相互接続）抵抗も、各音響共振器に加わる。

30

#### 【0052】

予め最適化したフィルタ回路設計を、次いで、電子化したフィルタオプティマイザに入れて、最終フィルタ回路設計を作る（ステップ 70）。選択的方法では、最適化の間にエレメント除去最適化（ERO）技術を実装する。ここでは、不必要なあるいは「消えてゆく」回路エレメントを除去し、あるいは、少なくし、より簡素な回路エレメントとして、図 18 に示す最終フィルタ回路設計となる。ERO 技術は、米国暫定特許出願第 61/802,114 号の “Element Removal Design in Microwave Filters” に記載されている。最適化及び ERO 技術によって、図 19 に示すような、各共振器について、共振周波数  $\omega_R$  と静電容量  $C_0$  となり、図 19 に示すように、キャパシタの容量は、シミュレーションを行った場合に、図 20 に示す周波数応答となる。これは、目的の周波数応答要求に合致する。

40

#### 【0053】

50

特に、図2に示すネットワーク合成技術によって設計したマルチバンドフィルタは、従来の設計技術及びその簡単な拡張機能に応じて設計したマイクロ波音響フィルタとは逆に、比較的大きな共振周波数レンジを有する共振及び共振器を有することになる。

#### 【0054】

例えば、フィルタ又はその共振器の共振周波数のスパンを比較できる一手段は、最高の共振周波数を有するフィルタの共振器の周波数分離である。42度XY-cut LiT a O 3 基板では、が約12以上である。音響共振器の実現による寄生容量は、を増やし、従って、パーセンテージ分離を小さくするが、規制インダクタンスはを効果的に減らす。この例では、=12に対して、パーセンテージ分離は4.0833%であり、従って、最も高い共振周波数を有する共振器の分離は、約88.1MHzである(すなわち、2151.57MHzの共振周波数×パーセンテージ分離4.0833%)。フィルタ又はその共振器の共振周波数のスパンを比較する別の方法は、共振器の平均集は酢分離であり、この場合は、77.32MHzである。

#### 【0055】

音響共振器の周波数分離と対照的に、二つの音響共振器間の「周波数差」は、二つの共振器の共振周波数間の全体周波数差を意味し、フィルタの二つの周波数間の周波数差は、二つの共振器間の絶対周波数差である。図21(a)及び21(b)は、図18-19に規定するフィルタのリターンロス(S11)を示す。リターンロス最小は、フィルタ回路の共振に対応し、また、初期フィルタ設計の反射ゼロ点に対応する。図21(a)は、フィルタ通過帯域N1からN7の形成を主に担うフィルタの共振を示す。図21(a)に示す最高及び最低の共振間の周波数差は、102MHzであり、又は共振器の平均周波数分離の約1.32倍である。更に、組み合わせた図21(a)及び21(b)の最高及び最低の共振間の周波数差は、349MHz(2173-1824MHz)であり、又は共振器の平均周波数分離の約4.51倍である。一方、フィルタ内の最高及び最低の共振間の周波数差は、459.37MHz(2151.57-1892.2MHz)であり、又は共振器の平均周波数分離の5.94倍である。

#### 【0056】

このように、最終フィルタ回路設計における通過帯域共振の最低共振周波数と最高共振周波数との間の差異は、共振器の平均分離の1.25倍になると考えられる。

#### 【0057】

図2に示すネットワーク合成技術に従って設計したマルチバンドフィルタは、従来技術のイメージ設計技術に従って設計したフィルタと対照的に、通過帯域から比較的離れたところにある反射ゼロ点に対応する共振器並びに共振を有すると考えられる。従来の技術では、反射ゼロ点に対応する共振器及び共振は、通過帯域内にあるか、あるいはこれに非常に近い。

#### 【0058】

特に、反射ゼロ点に対応する共振は、局所リターンロス(及び/又はS11)最小及び局所挿入口ス(及び/又はS21)最大が、最大周波数分離の約5パーセント以内に合致している周波数、この例では、約4.405MHz以下で生じる。代替的に、反射ゼロ点に対応する共振は、S11の遅延(図示せず)の局所最小値及び最大値で生じる。図21bに見られるように、反射ゼロ点に対応するいくつかの共振(特に、マーカN1、N2及びN6-N9に対応する共振)は、通過帯域(1850MHz乃至1910MHz)の外でこの帯域から遠くに位置している。反射ゼロ点に対応する共振と最も近い通過帯域エッジ間の周波数差は、最大周波数分離(この例では約88.1MHz)の1倍以上、おそらく1.25倍より大きく、おそらく2倍以上である。この特定の例では、反射ゼロ点が、通過帯域のエッジから、最大で平均共振器分離(77.32MHz)の3.40倍に位置している。通過帯域幅(60MHz)に対して、反射ゼロ点N1、N2は、通過帯域の下側エッジの下43.33%と28.33%であり、反射ゼロ点N6、N7は、通過帯域上側エッジの上13.33%及び26.67%である。反射ゼロ点N1、N2、N6及びN7は、互いに近接している。通過帯域反射ゼロ点N1、N2、N6及びN7に近接してい

10

20

30

40

50

ない反射ゼロ点 N 8、N 9 は、通過帯域の上側エッジの上 311.67% と 438.33% である。最終フィルタ回路設計の挿入口スは、好ましくは 3 dB より小さく、より好ましくは 2 dB より小さい。

#### 【 0059 】

図 2 を参照すると、最終フィルタ回路設計が達成されると、実際のマイクロ波フィルタが最終フィルタ回路設計に基づいて構築される（ステップ 72）。好ましくは、実際のマイクロ波フィルタの回路エレメント値が、最終フィルタ回路設計の対応する回路エレメント値に合致する。

#### 【 0060 】

特に、異なる周波数応答の測定は、ネットワーク合成技術 50 の様々なポイントで分析され、比較される。一の実施例では、異なる周波数応答の測定が、ステップ 68 で生成した音響フィルタ回路設計 150a の様々なバージョンに基づいて分析及び比較され、コンピュータ化したフィルタオプティマイザへ入力される予め最適化した回路設計に到達して、ステップ 70 において最終フィルタ回路設計を作る。例えば、入力と出力間で異なる音響共振器周波数の注文を実施できる。特に、音響共振器が信号伝送路に沿って配置されているオーダは、変更して複数フィルタソリューションを作ることができ、一またはそれ以上のパフォーマンスパラメータを、各フィルタソリューションについて計算することができ、異なるフィルタソリューションについてのパフォーマンスパラメータを互いに比較して、最も良好なフィルタソリューション（及び、したがって、共振器のオーダー）をこの比較に基づいて選択することができる。パフォーマンスパラメータは、例えば、フィルタ要求における所望のパフォーマンス特性に対する各回路応答を評価するための、特定の周波数あるいは複数の周波数の何れかにおける、挿入口ス、リターンロス、阻止率、グループ遅延、ノード電圧、プランチ電流、の一つ又はそれ以上である。

10

20

#### 【 0061 】

その他の実施例では、調査プロセスが共振器の静電容量  $C_0$  の実現可能な値、J-インバータの正（誘電性）及び負（容量性）の値（パリティ）の配列、及びその応答機能を変更しないが、実現可能な低ロス回路の応答を変更する、ロスレス設計において可変であるその他のパラメータに取り組むものである。共振周波数を再配列する調査プロセスについての更なる詳細は、米国特許第 7,924,114 号に開示されている。

30

#### 【 0062 】

固定通過帯域と阻止帯域を規定するフィルタ条件についてこの実施例で述べたが、フィルタ条件が複数の再構築できる通過帯域及び/又は阻止帯域を規定できることは自明である。例えば、一実施例では、この設計が二つの状態間で再構築可能である。第 1 の状態（帯域 5 と呼ぶ）は、824 MHz と 849 MHz 間の周波数を 3.5 dB より小さい挿入口スで通過させ、869 MHz と 894 MHz 間の周波数を少なくとも 40 dB で阻止し、第 2 の状態（帯域 8 と呼ぶ）は、880 MHz と 915 MHz の間の周波数を 3.5 dB より小さい挿入口スで通過させ、925 MHz と 960 MHz 間の周波数を少なくとも 40 dB で阻止する（ステップ 52）。回路エレメントタイプは、15 度 Y-cut LiTaO<sub>3</sub> 基板上に構築した SAW 共振器と、15 度 Y-cut LiTaO<sub>3</sub> 基板上に集積したキャパシタとして選択される（ステップ 54）。

40

#### 【 0063 】

次いで、図 3 に示す初期フィルタ回路構造 100 が、周波数応答要求から得られる通過帯域及び/又は阻止帯域に基づいて選択される（ステップ 56）。この場合、共振器の数は 6 個である。次いで、周波数要求を正規化したスペースにマッピングして（ステップ 58）、ロスレス回路応答が多項比の形で選択され（ステップ 60）、初期フィルタ回路構造 100 のマッピングして正規化した回路エレメント値を、結合マトリックス又はパラメータ抽出法を用いて、あるいは等価回路合成技術を用いてこれらの多項式から計算して、初期フィルタ回路設計を作成する（ステップ 62）。

#### 【 0064 】

次いで、等価回路変換を初期フィルタ回路設計 100 に行って、音響共振器を適応させ

50

る（ステップ64）。同様に、回路変換を行って、初期フィルタ回路石器100を、共振エレメント114の数（この場合は、6個）と同じ複数のサブセット回路設計に分割して、6個のシャント音響共振器を得る。

#### 【0065】

内部シャント音響共振器を初期フィルタ回路設計100に組み入れた一の変換技術においては、図6に示すサブセット130は、図22に示すように、アドミッタンスインバータ $J_{S1}$ を容量性PI-ネットワーク（キャパシタ- $C_{S1}$ 、 $C_{S1}$ 及び- $C_{S1}$ ）で、アドミッタンスインバータ $J_{12}$ を容量性PI-ネットワーク（キャパシタ- $C_{12}$ 、 $C_{12}$ 及び- $C_{12}$ ）で、アドミッタンスインバータ $J_{11}$ を容量性PI-ネットワーク（キャパシタ- $C_{11}$ 、 $C_{11}$ 及び- $C_{11}$ ）で、及び共振エレメント $B_1^R$ を、インダクタンス（インダクタ $L^{R1}$ ）とキャパシタンス（キャパシタ $C^{R1}$ ）の並列L-C共振器組合せで置き換えることによって、変換できる。同様に、図7について述べたとおり、キャパシタ- $C_{11}$ 、 $C_{11}$ 及び- $C_{11}$ からなるPI-ネットワークと、インダクタ $L^{R1}$ とキャパシタ $C^{R1}$ の並列L-C共振器組合せで表す回路サブ構造132は、インダクタンス（インダクタ $L^{R1}$ ）とキャパシタンス（キャパシタ $C^{R1}$ ）でできた直列L-C組み合わせ134に変換できるBVDモデル122の静電容量 $C_0$ を適用するためには、図23に示すように3つの隣接した並列キャパシタンスとサスセプタンス（- $C_{S1}$ 、- $C_{12}$ 、及び $B_1^N$ ）を、キャパシタンス（ $C_0^{R1}$ ）とサスセプタンス（ $B_1^N$ ）で置き換える。 $C_0^{R1}$ は、BVDモデル122の静電容量を表し、 $B_1^N$ は、 $B_1^N - (C_{S1} + C_{12} + C_0^{R1})$ の関係式で与えられる。このように、図24に示すように、内部シャント音響共振器122が実現できる。初期フィルタ回路設計100のその他のサブセット130も、同様にして変換し、図25に示すような、6個の内部シャント音響共振器122を有する音響フィルタ回路構造150bが得られる。

#### 【0066】

音響フィルタ回路構造150bの回路構造は、次いで実スペースにアンマッピングされ（ステップ66）、音響フィルタ回路構造150bに寄生効果を加えて、予め最適化した回路設計とする（ステップ68）。上述した通り、回路エレメントのロスを、各回路エレメントのQファクタを関連させることによって含めることができる。この実施例では、直列キャパシタンス $C_m$ は、 $Q_{cm} = 10^8$ で規定される関連するQを有し、静電キャパシタンス $C_0$ は、 $Q_{c0} = 140$ で規定される関連するQを有し、直列インダクタンス $L_m$ が $QL_m = 3000$ で規定される関連するQを有する。残りのインダクタは、 $Q_u = 60$ で規定される関連するQを有し、残りのキャパシタは、 $Q_u = 200$ で規定される関連するQを有する。母線（内部接続）抵抗 $R_s = 0.5$ オームも各音響共振器に加わる。この実施例では、3pF/（mmゲート幅）と1.0オーム\*（mmゲート幅）のスイッティングパラサイトも加えられる。

#### 【0067】

次いで、予め最適化されたフィルタ回路設計を、光ERO技術を用いてコンピュータフィルタオプティマイザに入力して、最終回路設計を作成する（ステップ70）。最適化の前に、図26に示すように、二つの帯域間でインピーダンスが異なる各ブランチにスイッチを加えて、最適化するべき二つの別の設計から单一回路を作成する。各スイッチのゲート幅、インダクタ又はキャパシタ（必要であれば）の値、及びこのブランチの回路構成を選択して、所定のブランチのインピーダンスが、一方のスイッチ状態で所望の帯域5のインピーダンスになり、他方のスイッチ状態で所望の帯域8のインピーダンスになるようする。ついで、組み合わせた回路上でERO技術を繰り返す。最適化プロセスによって、各共振器について共振周波数 $\omega_R$ と静電キャパシタンス $C_0$ となり、図27に示すようなこのキャパシタとインダクタのキャパシタンスとインダクタンスとなる。これらは、シミュレーションを行ったときに、図28に示す帯域5の周波数応答と、図29に示す帯域8の周波数応答となる。

#### 【0068】

上述した通り、異なる周波数応答の調査を、ネットワーク合成技術50における様々な

10

20

30

40

50

ポイントで分析し、比較する。一実施例では、異なる周波数応答の調査を、ステップ 68 で作成した音響フィルタ回路設計 150a の異なるバージョンに基づいて分析し、比較して、コンピュータ化したフィルタオプチマイザに入力し、ステップ 70 において予め最適化した回路設計を作成した。例えば、回路対（一の帯域 5 と一の帯域 8）を、共振器周波数の各オーダリングと、インバータ（インダクタ又はキャパシタ）の各パリティと、共振器の静電容量  $C_0$  の値の選択とによって生成する。この調査プロセスにおいては、共振周波数のオーダリングの可能な配列全て、可能なパリティすべて、実際の静電容量  $C_0$  の値の範囲である、0.95、1.9、3.8、及び 7.6 pF を用いて、各設計について通過帯域中心周波数における挿入口スを計算する。一の設計対（共振器のオーダと静電容量  $C_0$  の値が同じである一の帯域 5 と一の帯域 8）を選択する。

10

#### 【0069】

これまでに述べた実施例は、動的に再構築可能である通過帯域及び/又は阻止帯域をえるが、ネットワーク合成技術に従って構築したフィルタが、フィルタが最終的に完成する前に再構築可能であるが、フィルタの完成後は固定されている固定通過帯域及び/又は阻止帯域を有していてもよいことは自明である。例えば、図 30 に示す一実施例では、ロスレス回路モデルを実現でき、中心周波数が 836.5 MHz（帯域 5）又は 897.5 MHz（帯域 8）の通過帯域を有するフィルタができる。このロスレス回路は、SAW 共振器を用いて図 3 に示す初期フィルタ回路設計 100 を変換することによって作った。

#### 【0070】

3 つの内部シャント音響共振器を初期フィルタ回路設計 100 に組み込んだ変換技術では、図 10 - 13 に示す変換技術を用いて、回路サブセット（各々、各ノード 108 から設置した共振エレメント 114（サスセプタンス  $B^R$ ）と、共振エレメント 114 に直列に接続した非共振エレメント 116（アドミッタンスインバータ  $J$ ）と、各ノード 108 から共振エレメント 114（サスセプタンス  $B^R$ ）に並列に設置した非共振エレメント 118（サスセプタンス  $B^N$ ）を組み込む）を、3 個の内部シャント音響共振器に変換できる。この回路エレメントタイプは、42 度 Y-cut LiTaO3 基板上に構築した SAW 共振器と、42 度 Y-cut LiTaO3 基板に集積したキャパシタとして選択される。

20

#### 【0071】

フィルタは、共振器（この場合、 $C_{S1}, C_{12}, C_{23}, C_{3L}$ ）と非共振シャントエレメント（この場合、 $L_S, L_1, L_2, L_3, L_L$ ）間の直列エレメントの値を変えることによって完成前に再構築できる。次いで、フィルタは、帯域 5 についての非共振エレメントの値か、帯域 8 についての非共振エレメントの値を用いて、構築できる。最適化プロセスにより、各共振器に静電容量  $C_0$  が生まれ、キャパシタとインダクタのキャパシタンス及びインダクタンスは、図 30 に示すように、シミュレーションをしたときに、図 31 に示す帯域 5 の周波数応答及び図 32 に示す帯域 8 の周波数応答になる。

30

#### 【0072】

本発明の特定の実施例を説明したが、上述の説明は本発明をこれらの実施例に限定するものではない。当業者には、本発明の精神と範囲から外れることなく、様々な変更及び変形ができるることは自明である。例えば、本発明は単入力及び単出力のフィルタをはるかに超えており、本発明の特定の実施例は、デュプレクサ、マルチプレクサ、チャネライザ、リアクティブスイッチ、その他といった、低ロス選択制回路を使用できるものを形成するのに使用できる。従って、本発明は、特許請求の範囲に規定した本発明の精神及び範囲内にある、代替、変形及び均等物をカバーすることを意図している。

40

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図11】

FIG. 11

【図12】

FIG. 12

【図13】

FIG. 13

【図 1 4】

FIG. 14

【図 1 5】

FIG. 15

【図 1 6】

| エレメント | Ind (nH) | エレメント | Cap (pF) | エレメント | CO (pF) | 共振周波数(MHz) |

|-------|----------|-------|----------|-------|---------|------------|

| L1    | 9.05     | C1    | 2.45     | Res1  | 1.96    | 1858.13    |

| L2    | 1.43     | C2    | 0.89     | Res2  | 0.84    | 1825.00    |

| L3    | 0.38     | C3    | 0.14     | Res3  | 0.31    | 1881.19    |

| L4    | 11.93    |       |          | Res4  | 0.61    | 1831.00    |

| L5    | 0.09     |       |          | Res5  | 0.89    | 1910.00    |

| L6    | 63.42    |       |          | Res6  | 0.16    | 2150.00    |

| L7    | 7.18     |       |          | Res7  | 0.54    | 2032.00    |

| L8    | 0.21     |       |          | Res8  | 4.42    | 1797.00    |

|       |          |       |          | Res9  | 4.69    | 1852.36    |

FIG. 16

【図 1 7】

FIG. 17

【図 1 8】

FIG. 18

【図 1 9】

| エレメント | CO (pF) | 共振周波数(MHz) |

|-------|---------|------------|

| Res1  | 6.51    | 1854.78    |

| Res2  | 2.93    | 1792.20    |

| Res3  | 0.81    | 1877.00    |

| Res4  | 3.48    | 1800.00    |

| Res5  | 1.13    | 1866.30    |

| Res6  | 0.61    | 2151.57    |

| Res7  | 6.14    | 2026.79    |

| Res8  | 1.63    | 1806.38    |

| Res9  | 1.74    | 1867.06    |

FIG. 19

【図20】

FIG. 20

【図21】

FIG. 21a

FIG. 21b

【図22】

FIG. 22

【図23】

FIG. 23

【図24】

FIG. 24

## 【図25】

FIG. 25

## 【図26】

FIG. 26

【図27】

| レジメント | Ind(nH) | エレメント Cap(pF) | エレメント Co(pH) | 共振周波数(MHz) | エレメント(mm) |

|-------|---------|---------------|--------------|------------|-----------|

| L1    | 8.3     | C1 0.85       | Res1 0.95    | 929.02     | S1 3.3    |

| L2    | 7.9     | C2 3.80       | Res2 0.95    | 870.21     | S2 4.0    |

| L3    | 5.7     | C3 0.27       | Res3 0.97    | 924.11     | S3 4.0    |

| L4    | 2.4     | C4 4.60       | Res4 1.79    | 787.07     | S4 4.0    |

| L5    | 15.3    | C5 3.90       | Res5 4.51    | 800.95     | S5 4.0    |

| L6    | 12.6    |               | Res6 0.95    | 947.94     | S6 4.0    |

| L7    | 13.0    |               |              |            | S7 3.3    |

| L8    | 13.6    |               |              |            |           |

FIG. 27

【図 2 8】

【図 2 9】

FIG. 28

FIG. 29

【図 3 0】

FIG. 30

【図 3 1】

FIG. 31

【図 3 2】

FIG. 32

---

フロントページの続き

- (72)発明者 シルヴァー, リチャード, エヌ.

アメリカ合衆国 カリフォルニア州 94116, サンフランシスコ, パチェコストリート 36

9

- (72)発明者 ウィレムセン コルテス, バラム キチュー アンドレス

アメリカ合衆国 マサチューセッツ州 02420, レキシントン, マサチューセッツアヴェニュー

- 1009

- (72)発明者 ライン, カート, エフ.

アメリカ合衆国 カリフォルニア州 93117, ゴレタ, キャノングリーンドライブ 487

- (72)発明者 フェンジー, ニール, オー.

アメリカ合衆国 カリフォルニア州 93111, サンタバーバラ, パーティスストリート 65

0

- (72)発明者 ハモンド, ロバート, ビー.

アメリカ合衆国 カリフォルニア州 93109, サンタバーバラ, カンパニールドライブ 32

45

審査官 河合 弘明

- (56)参考文献 特表2010-532147 (JP, A)

米国特許出願公開第2009/0002102 (US, A1)

特表2010-532146 (JP, A)

米国特許出願公開第2008/0309430 (US, A1)

特表2008-522504 (JP, A)

特表2002-510928 (JP, A)

国際公開第99/052208 (WO, A1)

特開2000-286603 (JP, A)

特開2009-207116 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H03H 3/00-9/76