(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5634713号

(P5634713)

(45) 発行日 平成26年12月3日(2014.12.3)

(24) 登録日 平成26年10月24日(2014.10.24)

|              |           |            |   |

|--------------|-----------|------------|---|

| (51) Int.Cl. | F 1       |            |   |

| HO3H 11/04   | (2006.01) | HO3H 11/04 | H |

| HO4B 1/16    | (2006.01) | HO4B 1/16  | Z |

| HO4B 1/03    | (2006.01) | HO4B 1/03  | A |

請求項の数 3 (全 20 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2009-533418 (P2009-533418)  |

| (86) (22) 出願日 | 平成19年8月30日 (2007.8.30)        |

| (65) 公表番号     | 特表2010-507342 (P2010-507342A) |

| (43) 公表日      | 平成22年3月4日 (2010.3.4)          |

| (86) 國際出願番号   | PCT/US2007/077169             |

| (87) 國際公開番号   | W02008/048744                 |

| (87) 國際公開日    | 平成20年4月24日 (2008.4.24)        |

| 審査請求日         | 平成22年8月6日 (2010.8.6)          |

| (31) 優先権主張番号  | 11/550,534                    |

| (32) 優先日      | 平成18年10月18日 (2006.10.18)      |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 テキサス州 78735<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (74) 代理人  | 100142907<br>弁理士 本田 淳                                                                                      |

| (72) 発明者  | ラーマン、マヒプール<br>アメリカ合衆国 33467 フロリダ州<br>レイク ワース シェル リッジ テラ<br>ス 7289                                          |

前置審査

最終頁に続く

(54) 【発明の名称】アナログフィルタの帯域幅制御方法、帯域幅制御装置、および集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

無線装置においてアナログフィルタ(132)の所望帯域幅を得るために帯域幅制御方法であって、前記アナログフィルタ(132)はフィルタ入力(130)、フィルタ出力(131)、帯域幅決定構成要素、および品質係数を有し、前記帯域幅制御方法は、

a) 第1周波数における前記アナログフィルタ(132)の振幅応答の振幅と、前記第1周波数よりも高い第2周波数における同アナログフィルタ(132)の振幅応答の振幅との差を、同アナログフィルタ(132)の設計から算出した前記各周波数における同アナログフィルタ(132)の理想応答に基づき、予め決定するステップと；

b) ノーマルQ値から高Q値に前記アナログフィルタ(132)の前記品質係数を増大させることによって、前記第1周波数と前記第2周波数との間のピーク周波数においてピーク応答を生成するステップと；

c) 前記帯域幅決定構成要素の値を複数の値の1つに順次設定し、前記帯域幅決定構成要素が各値に設定される間に、

c1) 前記第1周波数の第1入力信号と、前記第2周波数の第2入力信号とを同時に前記アナログフィルタ(132)の前記フィルタ入力(130)に印加することによって、前記アナログフィルタ(132)の前記フィルタ出力(131)において振幅応答を生成するステップと；

c2) 前記第1周波数の振幅応答の振幅及び前記第2周波数の振幅応答の振幅を離散フーリエ変換検波回路によって検出するステップと、

10

20

c 3 ) 検出された前記第 1 周波数の振幅応答の振幅と、検出された前記第 2 周波数の振幅応答の振幅との間の差を計算するステップと；

d ) 前記ステップ c 3 ) で計算した差を前記予め決定した差と比較することによって、複数の誤差を得るステップであって、各誤差は、前記帯域幅決定構成要素の同一の値に対するステップ c 3 ) で計算した差と前記予め決定された差との数的差異を表す前記ステップと；

e ) 前記複数の誤差に基づき、前記複数の値から 1 つを前記帯域幅決定構成要素の最適値として選択するステップであって、前記選択された 1 つの値は、最小誤差と関連する前記帯域幅決定構成要素の値である前記ステップと；

f ) 前記品質係数が前記ノーマル Q 値の場合の前記アノログフィルタ (132) の前記所望帯域幅を得るために、前記帯域幅決定構成要素の値を前記選択された 1 つの値に設定するステップとを含み、10

周波数に対する振幅応答の変化を表す曲線において、前記第 1 周波数における振幅応答の曲線の傾きと前記第 2 周波数における振幅応答の曲線の傾きとが、前記品質係数が高 Q 値の場合に前記ノーマル Q 値の場合よりも大きい、ことを特徴とする、帯域幅制御方法。

### 【請求項 2】

アノログフィルタ (132) 、アノログ - デジタル相互変換器 (134) 、およびデジタルチューニングシステム (250) を有する帯域幅制御装置であって、

前記アノログフィルタ (132) は、アノログ入力信号を受信するフィルタ入力 (130) と；フィルタリングした出力信号を提供するフィルタ出力 (131) と；前記アノログフィルタ (132) の帯域幅を所定帯域幅に調整するための制御信号を受信するフィルタ制御入力とを有し、20

前記アノログ - デジタル相互変換器 (134) は、前記フィルタ出力 (131) に結合された変換器入力と；変換器出力とを有し、

前記デジタルチューニングシステム (250) は、前記アノログフィルタ (132) の品質係数を、ノーマル Q 値と高 Q 値の何れかに切換える Q 値切換手段 (304, 306) と；前記変換器出力に結合されたチューニング入力と；離散フーリエ変換検波回路 (253, 254) と；較正信号を生成する較正信号シンセサイザと；前記フィルタ入力 (130) に結合された較正信号出力と；前記フィルタ制御入力に結合された制御出力とを有し、前記較正信号は高周波数トーンと前記高周波数トーンよりも低い低周波数トーンを含み、前記品質係数が高 Q 値の場合に、前記高周波数トーンと前記低周波数トーンとの間のピーク周波数においてピーク応答を生成し。30

前記デジタルチューニングシステム (250) は、前記低周波数トーンでの前記フィルタ出力 (131) の振幅である低周波数振幅と、前記高周波数トーンでの前記フィルタ出力 (131) の振幅である高周波数振幅とを前記離散フーリエ変換検波回路 (253, 254) によって検出し、前記低周波数振幅と前記高周波数振幅の間の差を、前記アノログフィルタ (132) の設計から算出した前記各周波数トーンにおける同アノログフィルタ (132) の理想応答に基づき予め決定した差と比較することによって、前記制御信号を生成し、

周波数に対する振幅応答の変化を表す曲線において、前記高周波数トーンにおける振幅応答の曲線の傾きと前記低周波数トーンにおける振幅応答の曲線の傾きとが、前記品質係数が高 Q 値の場合に前記ノーマル Q 値の場合よりも大きい、ことを特徴とする、帯域幅制御装置。40

### 【請求項 3】

アノログフィルタ (132) とデジタルチューニング回路 (250) を備える集積回路であって、前記デジタルチューニング回路 (250) は前記アノログフィルタ (132) に結合され、

前記アノログフィルタ (132) はフィルタ入力 (130) を有し、

前記デジタルチューニング回路 (250) は、

前記アノログフィルタ (132) の品質係数を、ノーマル Q 値と高 Q 値の何れかに切換50

えるQ値切換手段(304, 306)と;

高周波数トーンと前記高周波数トーンよりも低い低周波数トーンとを生成するトーン生成手段であって、前記品質係数が高Q値の場合に、前記高周波数トーンと前記低周波数トーンとの間のピーク周波数においてピーク応答を生成する、トーン生成手段と;

前記品質係数が高Q値の場合に、前記フィルタ入力(130)に前記2つのトーンを同時に印加するトーン印加手段と;

前記2つのトーンそれぞれについて、前記アナログフィルタ(132)の振幅応答を検出する、離散フーリエ変換検波回路からなる応答検出手段と;

前記高周波数トーンについて検出された振幅応答の振幅と、前記低周波数トーンについて検出された振幅応答の振幅との差を、前記アナログフィルタ(132)の設計から算出した前記各周波数トーンにおける同アナログフィルタ(132)の理想応答に基づき予め決定した差と比較する比較手段と;

前記比較に応答して、前記アナログフィルタ(132)の帯域幅を変更する帯域幅変更手段とを含み、

周波数に対する振幅応答の変化を表す曲線において、前記高周波数トーンにおける振幅応答の曲線の傾きと前記低周波数トーンにおける振幅応答の曲線の傾きとが、前記品質係数が高Q値の場合に前記ノーマルQ値の場合よりも大きい、ことを特徴とする、集積回路。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

本発明は、概してアナログフィルタに関し、特にデジタル回路を用いたアナログフィルタの同調(チューニング)に関する。

##### 【背景技術】

##### 【0002】

連続時間すなわちアナログについてのフィルタは、多くの場合、携帯電話などの無線装置に使用される。通常、アナログフィルタおよび受信機または送信機を備える他の回路は、相補型金属酸化膜半導体(CMOS)技術を用いて製造される単一の集積回路上にある。アナログフィルタは、アナログフィルタの帯域幅に影響する抵抗およびコンデンサを含む構成要素を備える。

30

##### 【0003】

集積回路製造または製造プロセスによって、そのような構成要素の実測値は、公称値から30%も変動することがあり、その結果、帯域幅は50%も変動する場合がある。この帯域幅の変動は、温度または電圧の変化によっても引き起こされることがある。アナログフィルタの帯域幅の変動によって、無線装置の受信信号経路と送信信号経路の両方の性能が大幅に低下することがある。

##### 【0004】

受信信号経路では、ベースバンド・アナログフィルタの帯域幅の変動は、静電感度、干渉源がある場合の感度、受信機の3次インターセプト・ポイント、アンチエイリアシング性能、およびエラーベクトル度(EVM: error vector magnitude)の性能低下を引き起こす。また送信信号経路では、ベースバンド・アナログフィルタの帯域幅の変動は、エラーベクトル度の性能低下、隣接チャネル漏洩率、および静電/過渡電力マスク性能の性能低下を引き起こす。

40

##### 【0005】

帯域幅トラッキング精度および性能は、広帯域符号分割多元接続(WCDMAすなわち第3世代)と高速ダウンリンク・パケットアクセス(HSDPAすなわち第3.5世代)受信機で必要な、0.1%のビット誤り率(BER)、5%のエラーベクトル度、干渉源除去、およびアナログ・デジタル(A/D)アンチエイリアシング保護を維持するためには必須である。周知の第3世代および第3.5世代送受信機では、0.1%のビット誤り率感度は0.5デシベル(dB)だけ劣化し、エラーベクトル度は、最大12.5%の大き

50

な受信機帯域幅トラッキング・エラーのために 2 % から 8 . 4 % まで劣化する。

【 0 0 0 6 】

アナログフィルタの R / C フィルタ・パラメータを変更するためには、一般にトラッキング・ループが用いられる。トラッキング・ループは、発生する可能性がある構成要素の値の変化を追跡する。幾つかの周知の方法のトラッキング精度は、疑似ランダム較正信号の変化と、トラッキング・ループが収束するために必要な長期平均とのために、限界がある。疑似ランダム較正信号を用いる周知の方法の総較正時間は、約 1 0 m s e c であり、長過ぎる。周知の方法の長い較正時間にもかかわらず、疑似ランダム信号の変化のため、周知の方法は高い較正精度を達成するのが困難である。

【 0 0 0 7 】

他の周知の帯域幅トラッキング技術は、マスター・スレーブ・トラッキングの概念に的を絞る。そのような技術は、メインフィルタの各部で使用される回路と同じトポロジーを有する発振器として構成された、フィルタ段を使用する。いかなる製造工程および / または温度の変動も、メインフィルタとスレーブ回路に同じ量だけ影響しなければならない。この技術は、本質的にスレーブの周囲に位相ロックループを確立し、メインフィルタのすべての抵抗（またはコンデンサ）の同調（チューニング）をとることによって、発振器の発振（またはフィルタの位相差）を常に安定した値に近接させて維持する。そのような技術は、メインフィルタとスレーブ回路の種々の部分間の整合に依存する。しかし、精度の良い整合は、常に可能なわけではない。何故ならメインフィルタは、発振器とは異なるダイ部分（不感部分）を占めているため、整合が得られないとトラッキング精度の性能劣化が生じるからである。

【 0 0 0 8 】

他の周知の設計では、インバンド・トーン ( i n - B a n d t o n e ) とバンドエッジ・トーン ( B a n d - e d g e t o n e ) を用いてフィルタを同調させる。そのような設計では、インバンド・トーンは、バンドエッジ・トーンの測定基準を提供する。しかし、そのような設計は、信号が複合フォーマットで提示されないことによって別の非同時測定が必要であるため、追加時間を必要とする。更に、フィルタの振幅応答が低いため、補正精度が失われる。更にフィルタは、周波数の低いほうへ同調するため、バンドエッジ較正信号の振幅が低下し、分解能は更に低下する。

【 0 0 0 9 】

幾つかの周知の抵抗 / コンデンサ・チューニングシステム ( R / C チューニングシステム ) は、同調を必要とする R / C 時定数段（バイクワッドとミキサ極）をトラッキングする専用のアナログ発振器を使用する。発振器の R / C 時定数は、チューニングシステムの制御論理においてデジタルタイム値をチェックし、発振器の R / C 時定数が最適に同調するか否か判定するコンパレータ出力を用いて測定される。R / C 時定数が遅すぎる場合、速すぎる場合、あるいは許容値範囲内の場合であるかに基づき、デジタルアキュムレータはそれぞれカウントダウンされるか、カウントアップされるか、または変化されない。

【先行技術文献】

【特許文献】

【 0 0 1 0 】

【特許文献 1】米国特許第 6 , 5 6 0 , 4 4 7 号明細書

【発明の概要】

【発明が解決しようとする課題】

【 0 0 1 1 】

不利なことに、R / C 時定数の測定を実行するためには、専用のアナログ回路が必要である。更に、必要なアナログ回路の複雑さは、デジタル回路の複雑さを凌駕してしまう。アナログ回路を増設すると、不利なことに、設計時間、不感領域（ダイ領域）、および消費電流が増えてしまう。

【 0 0 1 2 】

周知のデジタルトラッキング方法は、電力検波のために高速フーリエ変換 ( F F T ) 方

10

20

30

40

50

法を使用する。しかし不利なことに、FFT方法は、膨大なハードウェアコストと消費電流を必要としてしまう。

【0013】

更に、周知のすべての方法では、トラッキング性能向上のための能動フィルタの品質係数（Q値）の動的制御ができない。

【課題を解決するための手段】

【0014】

本発明によれば、アナログフィルタの好適な帯域幅制御方法、帯域幅制御装置、および集積回路が提供される。

【図面の簡単な説明】

10

【0015】

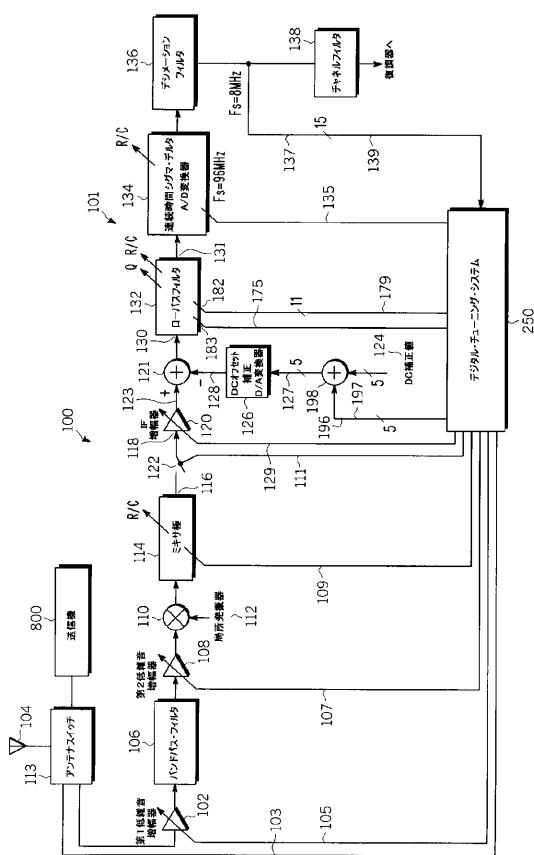

【図1】受信機アナログフィルタを備えた受信機を含む送受信機の一部と、受信機アナログフィルタを同調させる受信機デジタルチューニングシステムとを示す、簡略化した機能ブロック図。

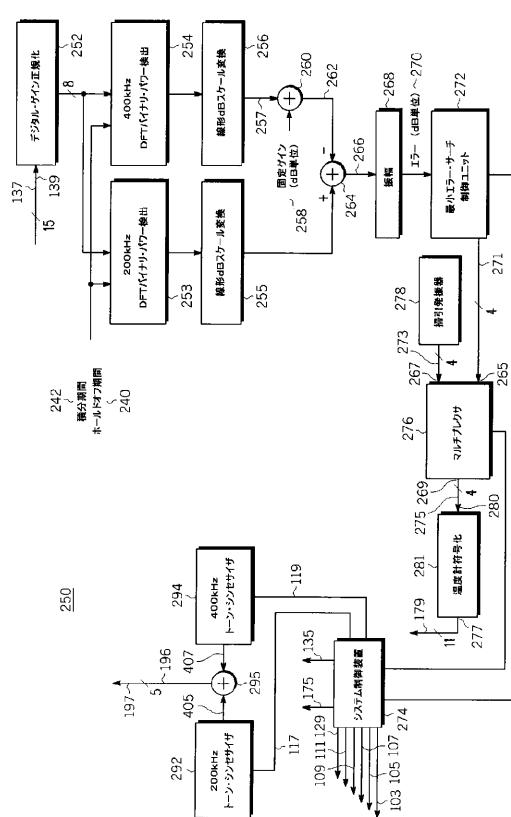

【図2】図1の受信機デジタルチューニングシステムの、簡略化した機能ブロック図。

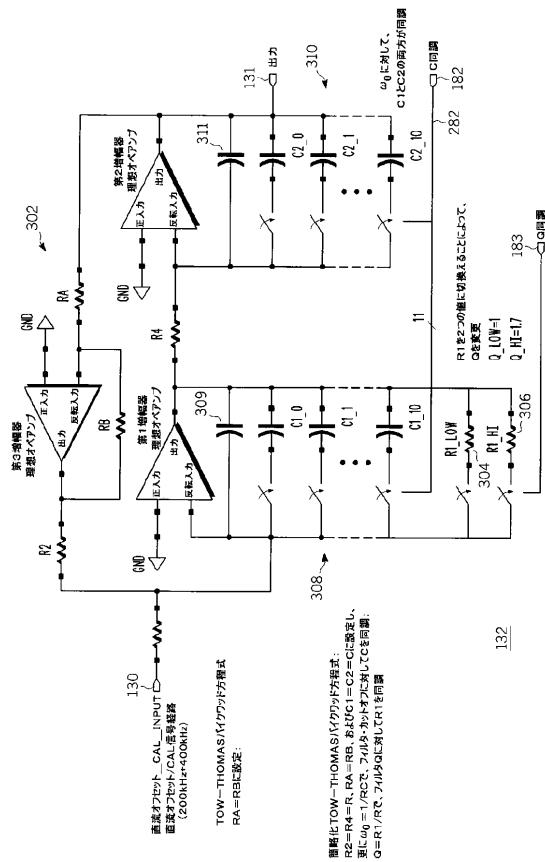

【図3】図1の受信機アナログフィルタの、概略図。

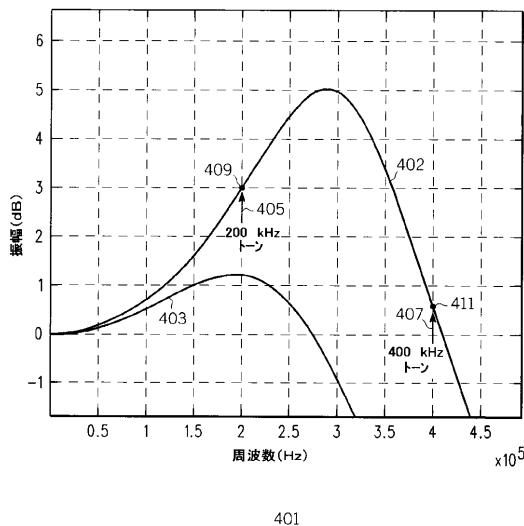

【図4】図1の受信機アナログフィルタの、R/C較正動作時と通常動作時それぞれの振幅応答のグラフ。

【図5】図1の受信機アナログフィルタの、振幅応答曲線群のグラフ。

【図6】図1の受信機デジタルチューニングシステムの、稼働方法のフローチャート。

20

【図7】図1の受信機デジタルチューニングシステムの、例示的なシミュレーション結果。

【図8】送信機アナログフィルタを含む送信機の一部の簡略化した機能ブロック図と、送信機アナログフィルタを同調させる送信機デジタルチューニングシステムとの簡略化した機能ブロック図。

【発明を実施するための形態】

【0016】

図1は、送受信機100の簡略化した機能ブロック図である。送受信機100は、ゼロ中間周波数受信機（ゼロIF受信機）またはベースバンド受信機としての受信機101の一部を含む。本実施形態では、送受信機100は、移動体または無線電話機である。

30

【0017】

受信機101は、受信機アンテナスイッチ113を介して受信機アンテナ104に結合された第1低雑音増幅器（LNA）102と、第1低雑音増幅器102に結合された受信機バンドパスフィルタ106と、受信機バンドパスフィルタ106に結合された第2低雑音増幅器108と、局部発振器112と第2低雑音増幅器108の両方に結合された受信機ミキサ110と、受信機ミキサ110に結合された受信機ミキサ極114とを含む。受信機ミキサ極114の出力であるミキサ極出力116は、中間周波数スイッチ122を介して、ベースバンドまたは中間周波数増幅器（IF A）120への入力である中間周波数入力118に結合される。中間周波数増幅器120は、出力としての中間周波数出力123を有する。

40

【0018】

デジタルDC補正值としてのDC補正值124は、5ビットの第1結合回路127を介して、DCオフセット補正D/A変換器126の入力に挿入される。DCオフセットは直流オフセット（DCOC）であり、D/A変換器は、デジタル-アナログ相互変換器のうちの、デジタルからアナログへの変換器である。DCオフセット補正D/A変換器126の出力信号は、直流オフセットD/A変換出力128（dcoc\_dac\_out）である。以下に詳細に述べるように、DC補正值124は、本発明に従って2トーン・トレーニングすなわち2トーン較正信号196に結合する。

【0019】

中間周波数出力123と、直流オフセットD/A変換出力128とは、第1加算器12

50

1で結合し、ベースバンド連続時間すなわち受信機アナログフィルタ132の入力である受信機フィルタ入力130に供給される。受信機アナログフィルタ132はローパスフィルタであり、少なくとも1つの帯域幅決定R/C回路を含む。受信機アナログフィルタ132の出力である受信機フィルタ出力131は、本実施形態では96MHzのサンプリング周波数を有する連続時間シグマデルタA/D変換器としての受信機A/D変換器134に結合される。A/D変換器は、デジタル・アナログ相互変換器のうちの、アナログからデジタルへの変換器である。

【0020】

受信機A/D変換器134は、低サンプリング周波数のエイリアスを除去する受信機デシメーションフィルタ136に結合される。本実施形態の低サンプリング周波数は、8MHzである。受信機デシメーションフィルタ136は、受信機チャネルフィルタ138に結合される。受信機チャネルフィルタ138は、復調器(図示略)に結合される。また、送信機800は、受信機アンテナスイッチ113に結合される。

【0021】

受信機デジタルチューニング回路としての受信機デジタルチューニングシステム250は、受信機101に結合される。受信機デジタルチューニングシステム250は、受信機アナログフィルタ132の帯域幅周波数を制御すなわち同調するデジタルトラッキングを行なう。受信機デジタルチューニングシステム250は、第2結合回路103、第3結合回路105、第4結合回路107、第5結合回路109、第6結合回路111、第7結合回路129、第8結合回路135、第9結合回路137、第10結合回路175、第11結合回路179、および第12結合回路197をそれぞれ介して、受信機101に結合される。

【0022】

図2は、受信機デジタルチューニングシステム250の簡略化した機能ブロック図を示す。受信機デジタルチューニングシステム250は、受信機101から信号を受信するデジタルゲイン正規化回路としての正規化回路252を備える。受信機101からの信号は、受信機デシメーションフィルタ136の出力としてのコンデンサ同調デジタル入力139(cap\_tune\_din)である。受信機デシメーションフィルタ136は、15ビットの第9結合回路137を介して、正規化回路252に結合される。正規化回路252は、8ビットの結合回路を介して、200kHzDFT検波回路253と400kHzDFT検波回路254とに並列に結合される。

【0023】

200kHzDFT検波回路253は、200kHz離散フーリエ変換(DFT)単一周波数バイナリ電力検波回路であり、400kHzDFT検波回路254は、400kHz離散フーリエ変換(DFT)単一周波数バイナリ電力検波回路である。200kHzDFT検波回路253は、第1線形-dBスケール変換回路255に結合され、400kHzDFT検波回路254は、第2線形-dBスケール変換回路256に結合される。第2線形-dBスケール変換回路256の出力と、固定ゲイン258とは、第2加算器260に結合される。第2加算器260の出力は、入力よりも大きな大ゲイン信号262である。大ゲイン信号262と、第1線形-dBスケール変換回路255の出力とは、第3加算器264に供給される。大ゲイン信号262は、第3加算器264の入力に供給される前に、負の値にされる。

【0024】

第3加算器264の出力信号は、コンデンサ同調電力差分信号266(cap\_tune\_pow\_dif)である。コンデンサ同調電力差分信号266は、200kHz応答の電力推定値と、400kHz応答の電力推定値との間の差である。コンデンサ同調電力差分信号266は、デシベル単位の測定値である。第3加算器264の出力は、振幅回路268の入力に結合される。振幅回路268の出力は、振幅回路268の入力の絶対値としてのエラー値270である。振幅回路268の出力は、最小エラー・サーチ制御ユニット272の入力に結合される。最小エラー・サーチ制御ユニット272は、結合され

10

20

30

40

50

たシステム制御装置としてのシステムコントローラ 274 の制御の下での組合せでシーケンシャル論理回路を備える。本実施形態では、システムコントローラ 274 はマイクロプロセッサである。最小エラー・サーチ制御ユニット 272 の出力は、4 ビットの第 13 結合回路 271 を介して、受信機マルチブレクサ 276 の第 1 入力 265 に結合される。最小エラー・サーチ制御ユニット 272 は、受信機アナログフィルタ 132 の少なくとも 1 つの R / C 回路の最適静電容量設定を表す 4 ビット値を出力する。受信機マルチブレクサ 276 の第 2 入力 267 には、4 ビットの第 14 結合回路 273 を介して、掃引発振器 278 が結合される。

【0025】

閉ループトレーニングすなわち較正期間中、掃引発振器 278 は、受信機アナログフィルタ 132 のそれぞれ可能な R / C 設定に可変するが、受信機 A / D 変換器 134 の R / C 設定は公称設定に保持される。本実施形態では、受信機 A / D 変換器 134 の公称設定は、受信機 A / D 変換器 134 がクリッピングしないように最大静電容量になっている。掃引発振器 278 は、バイナリ「0000」からバイナリ「1011」までの一連の 4 ビット値を出力する。受信機マルチブレクサ 276 の出力であるマルチブレクサ出力 269 は、4 ビットの第 15 結合回路 275 を介して、温度計符号化回路 281 に結合される。

【0026】

受信機マルチブレクサ 276 は、結合されたシステムコントローラ 274 によって制御される。閉ループ較正期間中、受信機マルチブレクサ 276 の出力信号は、掃引発振器 278 の出力信号である。本発明の受信機デジタルチューニングシステム 250 による最適静電容量設定の決定後は、受信機マルチブレクサ 276 の出力信号は、最小エラー・サーチ制御ユニット 272 の出力である。

【0027】

受信機マルチブレクサ 276 の出力信号を、コンデンサ同調設定信号 280 (cap\_tune\_setting) と称する。コンデンサ同調設定信号 280 は、バイナリ「0000」からバイナリ「1011」までの 4 ビット値である。コンデンサ同調設定信号 280 の各々の値は、受信機アナログフィルタ 132 の R / C 回路の静電容量設定を表す。

【0028】

温度計符号化回路 281 の出力である温度符号出力 277 は、11 ビットの第 11 結合回路 179 を介して、受信機アナログフィルタ 132 のコンデンサ同調入力 182 (C\_tune 入力) に結合される。温度計符号化回路 281 は、4 ビットのコンデンサ同調設定信号 280 を、11 ビットの第 11 結合回路 179 上の制御信号に、マッピングすなわち変換する。

【0029】

システムコントローラ 274 は、第 10 結合回路 175 を介して、受信機アナログフィルタ 132 の Q 値同調入力 183 (Q\_tune 入力) に結合される。更にシステムコントローラ 274 は、第 2 結合回路 103 を介して受信機アンテナスイッチ 113 に結合され、第 3 結合回路 105 を介して第 1 低雑音増幅器 102 に結合され、第 4 結合回路 107 を介して第 2 低雑音増幅器 108 に結合され、第 5 結合回路 109 を介して受信機ミキサ極 114 に結合され、第 6 結合回路 111 を介して中間周波数スイッチ 122 に結合され、そして第 7 結合回路 129 を介して中間周波数増幅器 120 に結合される。

【0030】

受信機デジタルチューニングシステム 250 は、200 kHz シンセサイザ 292 と、400 kHz シンセサイザ 294 を備える。200 kHz シンセサイザ 292 は、200 kHz トーン 405 (図 4 を参照) を生成する 200 kHz トーンデジタルシンセサイザであり、400 kHz シンセサイザ 294 は、400 kHz トーン 407 (図 4 を参照) を生成する 400 kHz トーンデジタルシンセサイザである。システムコントローラ 274 は、第 16 結合回路 117 を介して 200 kHz シンセサイザ 292 に結合され、また第 17 結合回路 119 を介して 400 kHz シンセサイザ 294 に結合される。200 kHz トーン 405 と 400 kHz トーン 407 は、第 4 加算器 295 において結合される

10

20

30

40

50

。第4加算器295の出力信号は、2トーン較正信号196である。第4加算器295の出力は、5ビットの第12結合回路197を介して、第5加算器198の入力に結合される。

#### 【0031】

2トーン較正信号196は、第5加算器198内において、DC補正值124と結合される。任意選択で、2トーン較正信号196は、DC補正值124との結合前にスケーリングされる。受信機デジタルチューニングシステム250は、DCオフセット補正D/A変換器126を通過することによって、受信機フィルタ入力130に2トーン較正信号196を印加する。つまり2トーン較正信号196は、受信機101内に既に存在するDCオフセット補正D/A変換器126を通過することによって受信機101内に印加されるため、追加のD/A変換器は不要である。受信機デジタルチューニングシステム250は、受信機101の電源投入中に動作する。別の方法としては、受信機デジタルチューニングシステム250は、受信機101が信号受信中ではない信号非受信期間において動作する。

10

#### 【0032】

本実施形態では、帯域幅周波数に影響する受信機アナログフィルタ132、抵抗とコンデンサを含む受信機101の全体、および受信機デジタルチューニングシステム250の全体は、相補型金属酸化膜半導体(CMOS)技術を用いて製造された単一の集積回路上にある。本実施形態では、受信機101の動作周波数範囲は、約800MHz～2000MHzである。

20

#### 【0033】

図3は、受信機アナログフィルタ132の概略図である。受信機アナログフィルタ132は、受信機アナログフィルタ132の品質係数すなわちQ値を切換えるQ値切換手段を含む。Q値切換手段は、低抵抗304、高抵抗306、および抵抗切換手段を含む。抵抗切換手段は、低抵抗304と高抵抗306のうちの何れか1つを、少なくとも1つのR/C回路に切換える。本実施形態では、受信機アナログフィルタ132は、バイクワッド段302(biquad stage、双2次段)を備える能動フィルタである。バイクワッド段302は、少なくとも1つの演算増幅器を備える。本実施形態では、能動フィルタは、2次Tow-Thomasフィルタである。Tow-Thomas能動フィルタの動作と、バイクワッド段302の動作は、能動フィルタの当業者には周知であるため、詳述しない。

30

#### 【0034】

受信機アナログフィルタ132の少なくとも1つのR/C回路の各々は、複数の帯域幅決定構成要素を備える。本実施形態では、帯域幅決定構成要素は、第1コンデンサアレイ308と第2コンデンサアレイ310を備える。第1コンデンサアレイ308は、切換可能な複数の第1コンデンサ309を備え、第2コンデンサアレイ310は、切換可能な複数の第2コンデンサ311を備える。第1コンデンサアレイ308は、第1時定数を有する第1R/C回路に関連し、第2コンデンサアレイ310は、第2時定数を有する第2R/C回路に関連する。つまり第1R/C回路は、切換不能な複数の第1コンデンサ309を含み、第2R/C回路は、切換不能な複数の第2コンデンサ311を含む。

40

#### 【0035】

任意の時点で、低抵抗304と高抵抗306のうちの1つが、受信機アナログフィルタ132において使用される。低抵抗304を使用すると、ローパスフィルタはノーマルQ値としての低Q値(low-Q値)、すなわち通常モードで動作する。高抵抗306を使用すると、ローパスフィルタは高Q値(high-Q値)、すなわち同調モードで動作する。本実施形態では、低Q値モードの低Q値は1.0であり、高Q値モードの高Q値は1.7である。アナログ回路で使用するように選択された抵抗(低抵抗304と高抵抗306の何れか)は、Q値同調入力183(Q\_tune入力)の信号によって制御される。

#### 【0036】

本実施形態では、第1コンデンサアレイ308は、11個のコンデンサC1～C1

50

—10を備え、各コンデンサは、互いに等しい第1基準静電容量値と、コンデンサC1\_0～C1\_10をそれぞれ受信機アナログフィルタ132の第1R/C回路に接続する11個のスイッチS1\_0～S1\_10とを有する。本実施形態では、第2コンデンサアレイ310は、11個のコンデンサC2\_0～C2\_10を備え、各コンデンサは、互いに等しい第2基準静電容量値と、コンデンサC2\_0～C2\_10をそれぞれ受信機アナログフィルタ132の第2R/C回路に接続する11個のスイッチS2\_0～S2\_10とを有する。

#### 【0037】

第1コンデンサアレイ308において選択された第1静電容量は、C1\_0, C1\_0 + C1\_1, C1\_0 + C1\_1 + C1\_2, C1\_0 + C1\_1 + C1\_2 + C1\_3, . . . , のうちの何れか1つである。同様に、第2コンデンサアレイ310において選択された第2静電容量は、C2\_0, C2\_0 + C2\_1, C2\_0 + C2\_1 + C2\_2, C2\_0 + C2\_1 + C2\_2 + C2\_3, . . . , のうちの何れか1つである。第1コンデンサアレイ308において選択された第1静電容量は、第2コンデンサアレイ310において選択された第2静電容量に関連する。

#### 【0038】

コンデンサ同調設定信号280(cap\_tune\_setting)は、コンデンサ同調入力182(C\_tune入力)の単一の信号である。コンデンサ同調設定信号280が、受信機アナログフィルタ132のR/C回路で使用する第1コンデンサアレイ308の選択された第1静電容量と、第2コンデンサアレイ310の選択された第2静電容量との両方を選択できるように、第1コンデンサアレイ308と第2コンデンサアレイ310は連動する。11ビットの第11結合回路179の各ビットは、第1コンデンサアレイ308と第2コンデンサアレイ310の各コンデンサに関連するスイッチの1つを起動する。

#### 【0039】

図4は、振幅応答(デシベル単位)と周波数(ヘルツ単位)との関係を示す第1グラフ401である。図4は、R/C較正時の受信機アナログフィルタ132の代表的な振幅応答である高Q値応答402と、通常受信動作時の受信機アナログフィルタ132の代表的な振幅応答である低Q値応答403とを示す。受信機アナログフィルタ132は、更に位相応答(図示略)を有する。振幅は、電力の平方根である。以下、「応答」という用語は、「振幅応答」を意味する。図4は、受信機アナログフィルタ132が低Q値モードではなく、高Q値モードの場合の受信機アナログフィルタ132の同調の利点を示すグラフである。

#### 【0040】

受信機アナログフィルタ132を高Q値モードにすると、有利なことに、高Q値応答402の曲線に高いピークが生まれる。高Q値応答402において、高いピーク付近の周波数の曲線の傾きは、同じ周波数の低Q値応答403の曲線の傾きよりも遥かに大きい。2トーン較正信号196は、200kHzトーン405と400kHzトーン407とを含む。200kHzトーン405と400kHzトーン407は、受信機アナログフィルタ132のカットオフ周波数よりも低周波数領域か高周波数領域かにそれぞれ位置するよう選択される。

#### 【0041】

本実施形態では、通常動作モード時つまり低Q値応答403の受信機アナログフィルタ132の-3dB帯域幅(マイナス3dB帯域幅)は、350kHzである。較正モード時つまり高Q値応答402の受信機アナログフィルタ132の-3dB帯域幅は、約460kHzである。

#### 【0042】

本実施形態では、200kHzトーン405と400kHzトーン407の正確な周波数は、システムクロックの1つに関連する整数によって分割できる周波数である。しかし、一般に、較正モード時に460kHzのカットオフ周波数を有する受信機アナログフィ

10

20

30

40

50

ルタ 132と一緒に使用する低周波数のトーン(200 kHz トーン 405)は、150 kHz 以上且つ250 kHz 以下であればよく、高周波数のトーン(400 kHz トーン 407)は、350 kHz 以上且つ450 kHz 以下であればよい。

#### 【0043】

図4の2本の垂直線は、200 kHz トーン 405 と 400 kHz トーン 407 を示す。200 kHz トーン 405 と 400 kHz トーン 407 は、高Q値モードの受信機アナログフィルタ132において、高Q値応答402の高ピークの低周波数領域と高周波数領域それぞれに均等に配置される。

#### 【0044】

受信機アナログフィルタ132の高Q値モード同調時には、2つの効果がある。第1効果は、同調ステップごとの高Q値応答402の大きな変化量である。高Q値応答402は、電力として測定される。受信機アナログフィルタ132を高Q値モードにする結果、周波数の所与の変化について、有利なこととしては、大きな電力変化が起こる。周波数の所与の変化に対して大きな電力変化が起こる理由は、200 kHz トーン 405 と 400 kHz トーン 407 の周波数が高Q値応答402の曲線の急勾配部分、すなわち急峻部分に位置するからである。他方、受信機アナログフィルタ132の低Q値モード時には、周波数の所与の変化について小さい電力変化が起こる。

10

#### 【0045】

第2効果としては、受信機アナログフィルタ132が同調すると、200 kHz トーン 405 への応答である 200 kHz 応答 409 の電力変化が、400 kHz トーン 407 への応答である 400 kHz 応答 411 の電力変化に対して、逆方向に動き、従って両方の応答の差が各同調ステップで強調されることである。これら第1効果と第2効果の影響は、有利にはそれぞれ 200 kHz 応答 409 と 400 kHz 411 の間の曖昧さを解決するのに貢献する。

20

#### 【0046】

受信機デジタルチューニングシステム250は、200 kHz トーン 405 と 400 kHz トーン 407 の間の複数の絶対差のうちから、1つの絶対差を選択する。更に受信機デジタルチューニングシステム250が、1つのトーンだけではなく、2つのトーン(200 kHz トーン 405 と 400 kHz トーン 407)を使用することによって、受信機アナログフィルタ132内にあるゲイン変動は除去される。ゲイン変動は、部分変動および/または温度などの環境によって生じる。いかなるゲイン変動も、200 kHz 応答 409 と 400 kHz 応答 411 にそれぞれほぼ同じ量だけ影響する。従って、ゲインの存在もゲイン量も、それぞれ 200 kHz 応答 409 と 400 kHz 応答 411 の差すなわち絶対差には、寄与しない。

30

#### 【0047】

図1と図4を参照すると、閉ループ較正工程を起動する前に、中間周波数入力118の信号は、受信機デジタルチューニングシステム250の性能に干渉しないように十分に減衰される。この減衰は、受信機アンテナスイッチ113、第1低雑音増幅器102、第2低雑音増幅器108、受信機ミキサ110、および受信機ミキサ極114を最小ゲイン状態にすることによって、中間周波数入力118を遮断すると達成される。一方、閉ループ較正工程中には、システムコントローラ274は、中間周波数増幅器120を最大ゲインに固定設定にする(本実施形態では、12dB 固定ゲインに設定)。

40

#### 【0048】

更に、受信機アナログフィルタ132は、高Q値応答402を生成する高Q値モードにされる。高Q値モードでは、200 kHz トーン 405 と 400 kHz トーン 407 が、高Q値応答402の高いピークから生まれる急峻な勾配の両側の周波数に同時に印加される。200 kHz トーン 405 と 400 kHz トーン 407 が同時に印加されることによって、トラッキング性能は一層高速で正確になる。なお、通常の受信機動作時には、低Q値を表す低Q値応答403を用いて、フラッタ帯域内応答と帯域外選択性能の改善が達成される。

50

## 【0049】

閉ループ較正期間では、200 kHzトーン405と400 kHzトーン407は結合され、任意選択でスケーリングされ、DC補正值124に追加され、そして所与のI/Q直交チャネルのDCオフセット補正D/A変換器126に印加される。次に、200 kHzトーン405と400 kHzトーン407は、高Q値モードの受信機アナログフィルタ132を通過する。

## 【0050】

200 kHzトーン405と400 kHzトーン407が受信機アナログフィルタ132を通過することによってフィルタリングされた後、2トーン較正信号196は、受信機A/D変換器134を通過することによって処理され、受信機デシメーションフィルタ136によって低サンプリングレートまでデシメートされる。次に、低サンプリングレート信号は、正規化回路252によって適切に正規化される。

10

## 【0051】

正規化回路252への入力信号は、15ビットのダイナミックレンジを有するコンデンサ同調デジタル入力139(cap\_tune\_din)である。デジタルゲイン正規化後に、正規化回路252の出力信号は、8ビットのダイナミックレンジを有する。このようなダイナミックレンジ低減によって、受信機デジタルチューニングシステム250に必要なハードウェアは、最小限になる。

## 【0052】

正規化回路252の出力信号は、2つの單一周波数バイナリDFT電力検波回路、すなわち200 kHz DFT検波回路253と、400 kHz DFT検波回路254とに供給され、従って200 kHzトーン405の振幅と、400 kHzトーン407の振幅とが検出される。振幅検出に続いて、検出結果がデシベルスケールに変換される。従って、高コストの分割動作は無しで、得られた振幅結果が比較される。

20

## 【0053】

デシベル単位の固定ゲイン258は、400 kHzトーン407の測定振幅に追加される。従って理想的なケースでは、400 kHzトーン407の測定振幅は、200 kHzトーン405の測定振幅に等しい値に、すなわち受信機アナログフィルタ132の応答の帯域幅エラー無しに正規化される。設計者は、受信機アナログフィルタ132の極と周波数応答の既存の知識を有する。従って、設計者は、受信機アナログフィルタ132が理想的に動作する場合の、200 kHzトーン405への受信機アナログフィルタ132の応答に対する、400 kHzトーン407への受信機アナログフィルタ132の応答の予想差(デシベル単位)を認識する。

30

## 【0054】

本実施形態では、設計者は、400 kHzトーン407への受信機アナログフィルタ132の理想的な応答は、200 kHzトーン405へのアナログフィルタの応答よりも2.5 dBだけ小さいことを認識する。従って、本実施形態では、受信機デジタルチューニングシステム250は、400 kHz DFT検波回路254の出力である400 kHz検波出力257に、固定ゲイン2.5 dBを追加する。一般に、他の実施形態では、異なる量の固定ゲインが追加される。

40

## 【0055】

図4に示す400 kHz応答411は、200 kHz応答409よりも2.5 dBだけ小さい。従って、高Q値応答402は最適応答である。400 kHz応答411は、400 kHzトーン407への受信機アナログフィルタ132の応答であり、200 kHz応答409は、200 kHzトーン405への受信機アナログフィルタ132の応答である。

## 【0056】

正規化に続いて、2つのDFT單一周波数バイナリの測定振幅は、第3加算器264を用いて比較され、エラー信号の振幅が計算される。振幅回路268の出力は、受信機デジタルチューニングシステム250のエラー信号である。理想的なケースでは、エラー信号

50

の振幅はゼロである。従って、閉ループ較正工程は、そのすべての可能な抵抗および／またはコンデンサ設定について受信機アナログフィルタ132に段を設けるステップと、最小のエラー測定を反映するコンデンサ同調設定信号280(cap\_tune\_setting)を選択するステップとを含む。

#### 【0057】

閉ループ較正工程の目的は、受信機アナログフィルタ132の複数のコンデンサ値のうち、どのコンデンサ値が本実施形態の受信機アナログフィルタ132の理想的な性能に予想される2.5dBの差を提供するかを決定することにある。別の方針としては、閉ループ較正工程の目的は、本実施形態の受信機アナログフィルタ132の理想的な性能に予測される2.5dBの差に最も近い差を提供するコンデンサ値を、受信機アナログフィルタ132の複数のコンデンサ値のうちから決定することである。

10

#### 【0058】

図5は、振幅応答(デシベル単位)と、周波数の対数(ヘルツ単位)との関係を示す第2グラフ500である。図5は、受信機アナログフィルタ132の12個の典型的な高Q値応答曲線群501と、12個の典型的な低Q値応答曲線群503とを示す。各応答の形状は、コンデンサ同調設定信号280(cap\_tune\_setting)の値に依存する。本実施形態では、高Q値応答曲線群501と低Q値応答曲線群503の応答の数は、受信機アナログフィルタ132の各R/C回路内のコンデンサの数に等しい。一般に、高Q値応答曲線群501と低Q値応答曲線群503の応答の数は、受信機デジタルチューニングシステム250によって制御可能な受信機アナログフィルタ132の周波数決定構成要素の数に等しい。

20

#### 【0059】

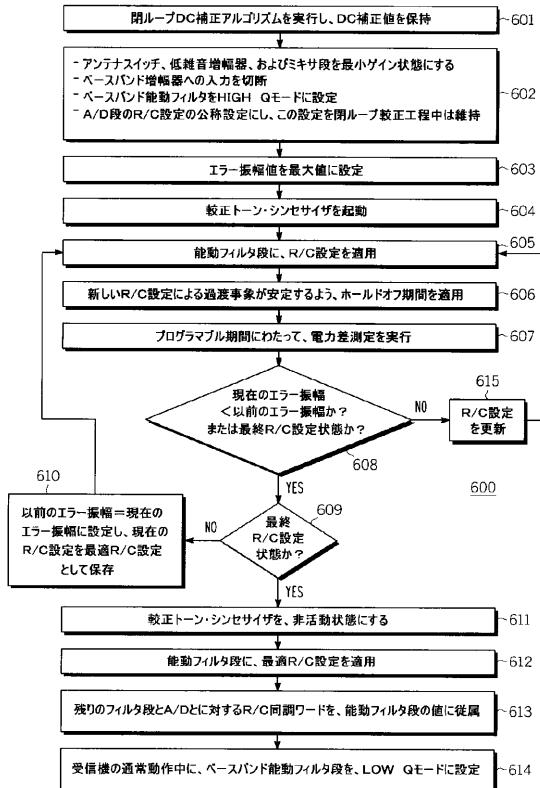

図6は、本発明の受信機デジタルチューニングシステム250の、稼働方法のフローチャート600である。この方法は、以下のステップを含む。ステップS601で、閉ループDC補正アルゴリズムが実行され、DC補正值が保持される。受信機101と一緒に使用できるDC補正アルゴリズムの一例が、「無線受信機のDCオフセット補正方法」(DC OFFSET CORRECTION SCHEME FOR WIRELESS RECEIVERS)と題されたRahman他の、本願の譲受人に譲渡される2003年5月6日付けの特許文献1に記載される。その内容全体は、参照によって本明細書に組込まれる。

30

#### 【0060】

ステップS602では、システムコントローラ274は以下の制御を行なう。すなわち受信機アンテナスイッチ113、第1低雑音増幅器102、第2低雑音増幅器108、およびミキサ段を最小ゲイン状態にするステップと；中間周波数入力118を遮断することによってミキサ極出力116を無効にするステップと；受信機アナログフィルタ132を高Q値モードに設定するステップと；受信機A/D変換器134のR/C設定を公称設定にし、公称設定を閉ループ較正期間中維持するステップとが実行される。

#### 【0061】

ステップS603では、エラー値270が最大設定に設定される。ステップS604では、システムコントローラ274は、200kHzシンセサイザ292と、400kHzシンセサイザ294とを起動する。ステップS605では、R/C設定が適用される。ステップS606では、ホールドオフ期間240が使用され、受信機アナログフィルタ132の新しいフィルタ帯域幅設定に関連する過渡事象が安定化される。本実施形態では、ホールドオフ期間240は10μsecである。

40

#### 【0062】

ステップS607では、ホールドオフ期間240後のプログラマブル積分期間242(蓄積期間)において、200kHzトーン405と400kHzトーン407の間の電力差が測定される。通常、プログラマブル積分期間242は、200kHzトーン405と400kHzトーン407それぞれのサイクル期間の公倍数になるように選択される。一般に、プログラマブル積分期間242は、2トーン較正信号196のうちの低いトーンの

50

約 10 サイクル分である。本実施形態では、プログラマブル積分期間 242 は、 $50 \mu s$  である。有利には、総較正時間、すなわち閉ループ R / C 同調アルゴリズムの完了時間は、約  $720 \mu s$  に過ぎない。

#### 【 0063 】

ステップ S608 において、最小エラー・サーチ制御ユニット 272 は、現在の測定エラー振幅を、以前のエラー振幅と比較する。現在のエラー振幅が以前に格納されたエラー振幅よりも小さい場合 (S608 において YES)、更にステップ S609 において最終 R / C 設定状態でなければ (S609 において NO)、ステップ S610 において、最小エラー・サーチ制御ユニット 272 は、現在の測定エラー振幅によって以前のエラー振幅を更新し、更に現在の R / C 設定を、最適 R / C 設定として保存する。

10

#### 【 0064 】

他方、ステップ S609 において最終 R / C 設定状態になっている場合、ステップ S611 において、システムコントローラ 274 は、較正シンセサイザとしての  $200 \text{ kHz}$  と  $292$  と  $400 \text{ kHz}$  シンセサイザ 294 を、両方とも非活動状態にする。

#### 【 0065 】

ステップ S608 を再度参照して、現在のエラー振幅が、以前に格納したエラー振幅よりも大きい場合 (S608 において NO)、ステップ S615 において R / C 設定を更新し、フローはステップ S605 に戻る。これら工程は、最終 R / C 設定ステップが完了するまで、各々の可能な R / C 設定について繰返す。

#### 【 0066 】

ステップ S612 において、最小エラー・サーチ制御ユニット 272 は、受信機アナログフィルタ 132 に、最適 R / C 設定を適用する。ステップ S613 では、残りの受信機段と、受信機 A / D 変換器 134 の R / C 設定とを、最適 R / C 設定に従属させる。最後にステップ S614 では、通常の受信機動作中に、受信機アナログフィルタ 132 の Q 値は、低 Q 値モードに設定され、帯域外選択性を最大限にしながら帯域内ピークを最小限にする。

20

#### 【 0067 】

受信機アナログフィルタ 132 について最適 R / C 設定を達成すると、受信機 A / D 変換器 134 と、他の受動または能動フィルタ段を含む他のベースバンド受信機ブロックとは、最適 R / C 設定に従属させられる。本実施形態では、受信機 A / D 変換器 134 は、第 8 結合回路 135 を介して最適 R / C 設定に従属するコンデンサの、1 つまたは複数のアレイ (図示略) を有する。

30

#### 【 0068 】

受信機 A / D 変換器 134 の各アレイ内のコンデンサの数は、受信機アナログフィルタ 132 の第 1 コンデンサアレイ 308 または第 2 コンデンサアレイ 310 のコンデンサ数に等しくなくてもよい。受信機アナログフィルタ 132 の最適静電容量設定に従属する値である、残りの受信機ブロック内の従属コンデンサの静電容量は、受信機アナログフィルタ 132 内のコンデンサの最適静電容量値と必ずしも同じでなくてもよい。しかし、残りの受信機ブロック内の従属コンデンサの静電容量は、コンデンサ同調設定信号 280 (c a p\_tune\_setting) が変化するたびに起こる受信機アナログフィルタ 132 内のコンデンサ値の変化率と同じ値の変化率を有する。更に、残りの受信機ブロックでは、静電容量ではなく、抵抗を従属させることもできる。

40

#### 【 0069 】

何れにせよ、システムコントローラ 274 は、残りの受信機ブロック内の従属構成要素 (抵抗および / または静電容量) の適切値を選択すべく、事前にプログラミングされる。別の実施形態 (図示略) では、受信機 101 の最適設定が、送信機 800 の構成要素ではなく、受信機 101 の構成要素に基づくにもかかわらず、送信機 800 内の R / C 構成要素の値も、受信機 101 内の受信機アナログフィルタ 132 から引出された最適設定に従属させ得る。

#### 【 0070 】

50

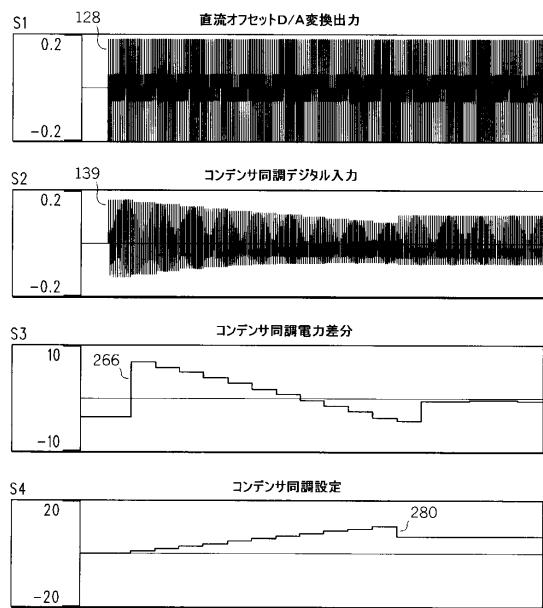

図7は、受信機デジタルチューニングシステム250の例示的なシミュレーション結果を示す。図7の第1プロットS1は、アナログ信号である直流オフセットD/A変換出力128(dcooc\_dac\_out)のタイムドメイン・プロットを示す。第1プロットS1の縦軸は電圧(ミリボルト)を表し、横軸は時間を表す。図7の第2プロットS2は、コンデンサ同調デジタル入力139(デジタル信号cap\_tune\_din)のタイムドメイン・プロットを示す。第2プロットS2の縦軸は、全範囲が+/-1の符号付小数デジタル値を表し、横軸は時間を表す。コンデンサ同調デジタル入力139(cap\_tune\_din)は、受信機デジタルチューニングシステム250へのデジタル入力信号である。

【0071】

10

図7の第3プロットS3は、コンデンサ同調電力差分信号266(デジタル信号cap\_tune\_pow\_difff)のタイムドメイン・プロットを示す。第3プロットS3の縦軸はデシベルを表し、横軸は時間を表す。第3プロットS3は、本発明の方法における、各ステップのエラー信号の振幅(デシベル単位)を表す。上記方法の第8ステップにおいて発生する最小エラー信号を、左から8番目の設定として、第3プロットS3上に示す。

【0072】

20

図7の第4プロットS4は、上記方法の各ステップのデジタル信号である、コンデンサ同調設定信号280(cap\_tune\_setting)のタイムドメイン・プロットを示す。第4プロットS4の縦軸はコンデンサアレイ設定を表し、横軸は時間を表す。本実施形態では、設定の最大数は12である。本発明によれば、8番目の設定が、図7に示す例示的なシミュレーションの最適設定として選択される。何故なら、8番目の設定において、受信機デジタルチューニングシステム250は、最小エラー振幅を反映する状態に安定するからである。

【0073】

30

設定の数は、同調する受信機アナログフィルタ132のR/C回路内の帯域幅決定コンデンサまたは抵抗の数、集合的には「構成要素」の数に等しい。帯域幅決定構成要素の数は、各要素の製造誤差と、受信機アナログフィルタ132を同調可能な絶対精度とによって決定される。本実施形態では、帯域幅決定構成要素の数は12個であり、そのうち11個は切換可能である。しかし、本発明は、12個よりも大きいかまたは小さい数の帯域幅決定構成要素を用いても、同様に適用可能である。

【0074】

本発明の受信機デジタルチューニングシステム250は、専用のアナログ回路を使用せずに、如何なる周知のトラッキング方法の実行時間よりも短い実行時間を達成する、一層正確なR/Cトラッキング・アルゴリズムを含む。本発明の利点は、受信機アナログフィルタ132のQ値の動的制御と、2トーン較正信号196に2つのトーンを使用することと、R/Cトラッキングデジタル測定および制御にDFT方法を使用することとを含む。

【0075】

40

本発明のDFT方法は、性能を改善し、すなわち不一致を発生させずに、高集積度CMOS工程における不感領域を最小限にする。本発明によって不感領域を小さくすると、製造コストを低減できる。その結果、たとえば高速フーリエ変換(FFT)を用いて平均電力を計算する方法によって不感領域が大きくなるような場合と比較して、消費電力を大幅に少なくできる。

【0076】

本発明の受信機デジタルチューニングシステム250では、200kHzDFT検波回路253と400kHzDFT検波回路254のそれぞれが、ゲルツェルフィルタ(Goertzel filter)によって実施される。本発明で使用されるゲルツェルフィルタは、3回の乗算のみ必要とする。しかし、周知のFFT方法は、不利なことに $N/2 \times \log_2 N$ 回の複素乗算を必要とする。つまり本発明の2ポイントDFT方法では、振幅は2バイナリまでの計算されるが、周知のNポイントFFT方法では、振幅はN(N

50

は2よりも大きな数)まで計算する必要がある。よって、本発明の受信機デジタルチューニングシステム250は、DFT方法を使用することによって、周知のトラッキング方法よりも迅速に平均電力を計算できる。

【0077】

有利には、本発明の受信機デジタルチューニングシステム250は、高集積度CMOSタイプの技術における不感領域の増大と、消費電流の増大とを抑制する。たとえばアナログ回路を使用するような幾つかの周知のトラッキング回路とは異なり、本発明の受信機デジタルチューニングシステム250は、デジタルハードウェアを使用する。つまり、本発明に必要なデジタル回路の複雑さは、周知の方法で使用するアナログ回路の複雑さよりも決定的ではない。アナログ回路の削減によって、有利には、設計時間、不感領域、および消費電流を低減できる。

【0078】

幾つかの周知のトラッキング回路とは異なり、本発明の受信機デジタルチューニングシステム250は、疑似ランダム信号を使用しない。つまり本発明の受信機デジタルチューニングシステム250は、有利なことに、変動しない2つの固定周波数トーン(200kHzトーンおよび400kHzトーン)を使用する。トラッキング達成時間は、周知のトラッキング回路によって大幅に低減される。何故なら、受信機デジタルチューニングシステム250は、平均電力を計算するたびに、固定周波数を備える一層小さい帯域幅についての計算を実行するからである。本発明は、低コスト且つ実用的なデジタル方法を用いてコンデンサアレイを同調(チューニング)させることによって、高度な帯域幅トラッキングを達成する。本発明は、相補型金属酸化膜半導体(CMOS)技術によって、不感領域と消費電流とを最小限にしながら、高度なデジタル測定および制御方法を用いて6%未満の補正精度で、受信機帯域幅エラーをトラッキングできる。補正精度は、0.1%のピット誤り率感度レベルを劣化させずに、第3世代および第3.5世代動作モードの両方について5%未満のエラーベクトル度を達成できる。本発明は、高データ速度の高速ダウンリンク・パケットアクセス(HSDPA)をサポートするために望ましい、5%未満の受信機エラーベクトル度性能を提供する手助けをし、本発明は受信機感度の要件を維持する。

【0079】

受信機デジタルチューニングシステム250は、受信機アナログフィルタ132の理想的な目標カットオフ周波数の4%以内のバイクワッドおよびミキサ極段の同調後の精度を提供する。受信機デジタルチューニングシステム250によって、温度および電圧変動(受信機101の指定電圧および指定温度動作範囲内)において引き起こされる受信機アナログフィルタ132のカットオフ周波数の変化は、1.5%以下である。

【0080】

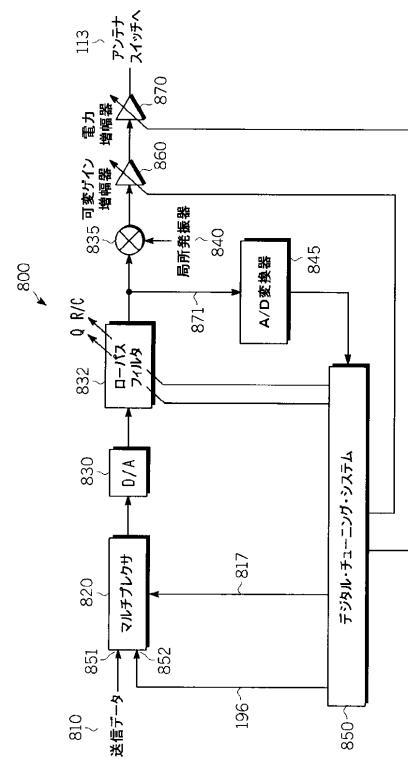

図8は、送信機アナログフィルタ832を含む送信機800と、送信機アナログフィルタ832の帯域幅周波数を制御する送信機デジタルチューニングシステム850との簡略化した機能ブロック図である。送信機800は、ベースバンド送信機、すなわち直接起動送信機である。送信機800は、送信機D/A変換器830と、送信機アナログフィルタ832と、送信機ミキサ835と、送信機局部発振器840とを備える。

【0081】

送信機アナログフィルタ832の出力信号は、送信機ミキサ835において、送信機局部発振器840からの信号と結合される。送信機ミキサ835の出力信号は、可変ゲイン増幅器(VGA)860に供給される。可変ゲイン増幅器860の出力は、電力増幅器(PA)870に供給される。電力増幅器870の出力は、受信機アンテナスイッチ113または直接に受信機アンテナ104に結合される。

【0082】

送信機800は、送信機マルチプレクサ820を含むことによって、送信機デジタルチューニングシステム850を収容するように修正される。送信機マルチプレクサ820は、選択ライン817によって、送信機デジタルチューニングシステム850に結合される

10

20

30

40

50

。通常のデータ送信動作中、送信機マルチブレクサ820の第1入力851には、送信データ810が供給される。送信機マルチブレクサ820の第2入力852には、2トーン較正信号196が供給される。

【0083】

送信閉ループ較正工程の実行前に、可変ゲイン増幅器860と電力増幅器870は最小ゲイン状態にされ、2トーン較正信号196は送信されないように設定する。何故なら、その場合の2トーン較正信号196の送信は、他の装置にとって干渉源になるからである。送信閉ループ較正工程では、

送信機デジタルチューニングシステム850のシステムコントローラ(図示略)は、送信機アナログフィルタ832を高Q値モードにする。更に送信機D/A変換器830に2トーン較正信号196を供給すべく、送信機マルチブレクサ820の第2入力852を選択する。送信機D/A変換器830の出力信号は、送信機アナログフィルタ832のフィルタ入力に供給される。

【0084】

次に、送信機デジタルチューニングシステム850のシステムコントローラは、閉ループR/C同調工程を起動する。送信機デジタルチューニングシステム850は、送信機アナログフィルタ832の出力であるアナログ信号871を、デジタル形式に変換する帰還A/D変換器845を含む。なお、別の方法として、たとえば半二重送受信機(図示略)では、半二重送受信機の受信機が使用した受信機A/D変換器134などが、半二重送受信機の送信機内において帰還A/D変換器845として再使用される。

10

20

【0085】

送信機800内のR/C構成要素の値は、受信機アナログフィルタ132の最適設定から引出された最適設定ではなく、送信機アナログフィルタ832の最適設定から引出された最適設定に従属する。なお、送信機デジタルチューニングシステム850の構成と制御方法は、受信機デジタルチューニングシステム250の構成と受信機101の制御方法にほぼ同様である。従って、送信機デジタルチューニングシステム850の構成と制御方法は、本明細書では詳述しない。

【0086】

以上、本発明の原理について、特定の装置に関連して説明してきた。しかし、この説明は例示的なものに過ぎず、本発明の範囲を限定するものではないことをはっきりと理解されたい。例えば、本実施形態は互いに同じ値のコンデンサのアレイを用いてフィルタのカットオフ周波数を制御するが、本発明では代替的に、互いに異なる値のコンデンサのアレイを用いてフィルタのカットオフ周波数を制御してもよい。

30

【0087】

また本実施形態は、コンデンサのアレイを用いてフィルタのカットオフ周波数を制御するが、本発明では代替的に抵抗の回路網またはコンデンサと抵抗の組合せを用いてフィルタのカットオフ周波数を制御してもよい。本実施形態はバイクワッド段を有する能動フィルタと一緒に使用するように示すが、本発明はバイクワッド段を備えていない能動フィルタと一緒に使用する場合にも同様に適用できる。本実施形態は能動フィルタと一緒に使用するように示すが、本発明は受動フィルタと一緒に使用する場合にも同様に適用できる。

40

【0088】

本実施形態は2次ローパスフィルタの例示的実施形態であるが、本発明は別の次数のローパスフィルタにも同様に適用できる。本実施形態はローパスフィルタと一緒に使用するように示すが、本発明はハイパスまたはバンドパスフィルタと一緒に使用する場合にも同様に適用できる。その場合、2トーン較正信号の周波数はそれに応じて調整される。本実施形態では、本発明をゼロ中間周波数受信機すなわちベースバンド受信機と一緒に使用するが、本発明は超低周波の中間周波数受信機でも使用でき、その場合、アナログフィルタは、ローパスフィルタではなくバンドパスフィルタである。

【0089】

本実施形態は、相補型金属酸化膜半導体(CMOS)技術を用いて製造された单一の集

50

積回路上に示すが、本発明は他の製造技術を用いて製造した単一の集積回路上でも使用できる。本実施形態では、同じ单一の集積回路上にアナログフィルタとデジタルチューニングシステムの両方を示すが、本発明は別々の集積回路上のアナログフィルタとデジタルチューニングシステムにも同様に適用可能である。

【 义 1 】

【 义 2 】

〔 図 3 〕

【 図 5 】

【 四 4 】

【 四 6 】

【图7】

【 四 8 】

---

フロントページの続き

(72)発明者 パークス、ジョン ジェイ .

アメリカ合衆国 33436 フロリダ州 ポイントン ビーチ ブチダ ロード 4592

(72)発明者 リッチズ、ジェームズ ジェイ .

アメリカ合衆国 33467 フロリダ州 レイク ワース ブランチウッド ドライブ 612

1

審査官 橋本 和志

(56)参考文献 國際公開第2007/069360 (WO, A1)

特開昭63-167513 (JP, A)

特開平09-036703 (JP, A)

特開2002-232251 (JP, A)

特開昭63-169807 (JP, A)

特開2005-197975 (JP, A)

米国特許出願公開第2005/0123036 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H03H 11/04

H04B 1/03

H04B 1/16