(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7679169号**

**(P7679169)**

(45)発行日 令和7年5月19日(2025.5.19)

(24)登録日 令和7年5月9日(2025.5.9)

(51)国際特許分類

|         |                  |     |         |        |   |

|---------|------------------|-----|---------|--------|---|

| H 1 0 F | 39/18 (2025.01)  | F I | H 1 0 F | 39/18  | F |

| H 0 4 N | 25/70 (2023.01)  |     | H 0 4 N | 25/70  |   |

| H 1 0 F | 30/225 (2025.01) |     | H 1 0 F | 30/225 |   |

| H 1 0 F | 39/12 (2025.01)  |     | H 1 0 F | 39/12  | D |

請求項の数 17 (全23頁)

(21)出願番号 特願2019-146308(P2019-146308)

(22)出願日 令和1年8月8日(2019.8.8)

(65)公開番号 特開2021-27277(P2021-27277A)

(43)公開日 令和3年2月22日(2021.2.22)

審査請求日 令和4年8月5日(2022.8.5)

審判番号 不服2024-2508(P2024-2508/J1)

審判請求日 令和6年2月13日(2024.2.13)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100126240

弁理士 阿部 琢磨

(74)代理人 100223941

弁理士 高橋 佳子

(74)代理人 100159695

弁理士 中辻 七朗

(74)代理人 100172476

弁理士 富田 一史

(74)代理人 100126974

弁理士 大朋 靖尚

(72)発明者 岩田 旬史

東京都大田区下丸子3丁目30番2号キ

最終頁に続く

(54)【発明の名称】 光電変換装置、光電変換システム

**(57)【特許請求の範囲】****【請求項1】**

光電変換装置であって、

アバランシェダイオードを備えた第1半導体層と、第1多層配線層とを有する第1チップと、

前記アバランシェダイオードからの出力に基づく信号を処理する信号処理部を備えた第2半導体層と、第2多層配線層とを有する第2チップと、を備え、

前記第1チップと、前記第2チップは積層され接合されており、

前記第1チップは、第1接合部を有し、前記第2チップは、前記第1接合部と接触する第2接合部を有し、

前記アバランシェダイオードには、第1電圧と第2電圧が供給され、

前記信号処理部には、第3電圧が供給され、

前記第1電圧と前記第3電圧の電位差は、前記第2電圧と前記第3電圧の電位差よりも大きく、

前記第1チップおよび前記第2チップの外部から前記第1電圧が供給される第1電極が、前記第1多層配線層に設けられており、

前記第1チップおよび前記第2チップの外部から前記第2電圧が供給される第2電極が、前記第1多層配線層のうちの前記第1電極が設けられる配線層と同じ配線層に設けられており、前記第1電圧は、前記第1チップと前記第2チップとの接合面に印加されず、

10

20

前記第1電極は、前記第2半導体層と電気的に接続されていないことを特徴とする光電変換装置。

**【請求項2】**

前記第1電圧は負電圧であることを特徴とする請求項1に記載の光電変換装置。

**【請求項3】**

前記第1電圧と前記第2電圧の電位差は前記アバランシェダイオードの降伏電圧よりも大きいことを特徴とする請求項1または2に記載の光電変換装置。

**【請求項4】**

光電変換装置であって、

アバランシェダイオードを備えた第1半導体層を有する第1チップと、

前記アバランシェダイオードからの出力に基づく信号を処理する信号処理部を備えた第2半導体層を有する第2チップと、を備え、

前記第1チップと、前記第2チップは積層され接合されており、

前記第1チップは、第1接合部を有し、

前記第2チップは、前記第1接合部と接触する第2接合部を有し、

前記アバランシェダイオードには、負電圧である第1電圧と正電圧である第2電圧が供給され、

前記第1チップおよび前記第2チップの外部から前記第1電圧が供給される第1電極が、前記第1半導体層の表面から前記第1チップと前記第2チップとの接合面までの間に設けられており、

前記第1チップおよび前記第2チップの外部から前記第2電圧が供給される第2電極が、前記第1半導体層の表面から前記接合面までの間において前記第1電極と同じ高さに設けられており、

前記第1電圧は、前記接合面に印加されず、

前記第1電極は、前記第2半導体層と電気的に接続されていないことを特徴とする光電変換装置。

**【請求項5】**

前記第1チップが第1多層配線層を有し、

前記第2チップは第2多層配線層を有することを特徴とする請求項4に記載の光電変換装置。

**【請求項6】**

前記第1チップおよび前記第2チップの外部から第3電圧が供給され、

前記第1電圧と前記第3電圧の電位差は、前記第2電圧と前記第3電圧の電位差よりも大きいことを特徴とする請求項5に記載の光電変換装置。

**【請求項7】**

前記第1電圧と前記第2電圧の電位差は、前記アバランシェダイオードの降伏電圧よりも大きいことを特徴とする請求項6に記載の光電変換装置。

**【請求項8】**

前記アバランシェダイオードのアバランシェ増倍を抑制するクエンチ素子は、前記第2チップに配されていることを特徴とする請求項1から7のいずれか1項に記載の光電変換装置。

**【請求項9】**

前記第1チップおよび前記第2チップの外部から前記第3電圧が供給される第3電極が、前記第1多層配線層に設けられていることを特徴とする請求項1から3、6、7のいずれか1項に記載の光電変換装置。

**【請求項10】**

前記第3電圧は、接地電圧であることを特徴とする請求項1から3、6、7、9のいずれか1項に記載の光電変換装置。

**【請求項11】**

前記第1電極を露出させる第1開口の底部は、前記第1チップの第1面と、前記第1面

10

20

30

40

50

とは反対側の前記第1チップの第2面との間に設けられ、

前記第2電極を露出させる第2開口の底部は、前記第1面と前記第2面との間に設けら

れていることを特徴とする請求項1から10のいずれか1項に記載の光電変換装置。

**【請求項12】**

前記第1開口および前記第2開口は、前記第2半導体層を貫通して形成されており、

前記第1開口および前記第2開口には電極が充填されていることを特徴とする請求項1

1に記載の光電変換装置。

**【請求項13】**

前記電極は、前記第1開口の底部で前記第1電極と接触しており、かつ、前記第2開口

の底部で前記第2電極と接触していることを特徴とする請求項12に記載の光電変換装置。 10

**【請求項14】**

前記第1チップは、第1接合部を有し、

前記第2チップは、前記第1接合部と接触する第2接合部を有し、

前記アバランシェダイオードは、前記第1接合部と前記第2接合部とを介して、前記ク

エンチ素子と電気的に接続されており、

平面視において、所定の方向の前記第1電極の長さは、前記第1接合部の長さよりも大

きいことを特徴とする請求項8に記載の光電変換装置。

**【請求項15】**

請求項1から14のいずれか1項に記載の光電変換装置と、

前記光電変換装置が出力する信号を処理する信号処理装置と、を有することを特徴とす

る光電変換システム。 20

**【請求項16】**

前記信号処理装置は、前記光電変換装置からの信号に基づき、測距および撮像を行うこ

とを特徴とする請求項15に記載の光電変換システム。

**【請求項17】**

請求項1から14のいずれか1項に記載の光電変換装置と、

前記光電変換装置からの信号に基づく測距情報から、対象物までの距離情報を取得する

距離情報取得手段と、を有する移動体であって、

前記距離情報に基づいて前記移動体を制御する制御手段をさらに有することを特徴とす

る移動体。 30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、光電変換装置および光電変換システムの構造に関する。

**【背景技術】**

**【0002】**

アバランシェ（電子なだれ）増倍を利用し、単一光子レベルの微弱光を検出可能な光電

変換装置が知られている。特許文献1は、複数の画素が配列されたセンサチップと、信号

処理を行う回路が形成された回路チップの双方を積層構造で電気的に接続した光電変換装

置が開示されている。この光電変換装置のセンサチップ内の画素には、電荷がアバランシ

エ増倍を起こすアバランシェダイオードが用いられることが開示されている。 40

**【先行技術文献】**

**【特許文献】**

**【0003】**

**【文献】**米国特許出願公開第2017/0186798号明細書

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

特許文献1では、積層構造のアバランシェダイオードを駆動する高電圧を供給する際の

配線に関する検討がなされておらず、光電変換装置の信頼性の確保が十分ではなかった。 50

**【課題を解決するための手段】**

**【0005】**

本発明に係る光電変換装置は、アバランシェダイオードを備えた第1半導体層と、第1多層配線層とを有する第1チップと、前記アバランシェダイオードからの信号を処理する信号処理部を備えた第2半導体層と、第2多層配線層とを有する第2チップと、を備え、前記第1チップと、前記第2チップは積層されており、前記アバランシェダイオードには、第1電圧と第2電圧が供給され、

前記信号処理部には、第3電圧が供給され、前記第1電圧と前記第3電圧の電位差は、前記第2電圧と前記第3電圧の電位差よりも大きく、前記光電変換装置の外部から前記第1電圧が供給される第1電極が、前記第1多層配線層または前記第2多層配線層に設けられており、前記第1電極は、前記第2半導体層と電気的に接続されていないことを特徴とする。

10

**【発明の効果】**

**【0006】**

本発明に係る光電変換装置によれば、信頼性を確保することのできるアバランシェダイオードを有する光電変換装置を提供することが可能になる。

**【図面の簡単な説明】**

**【0007】**

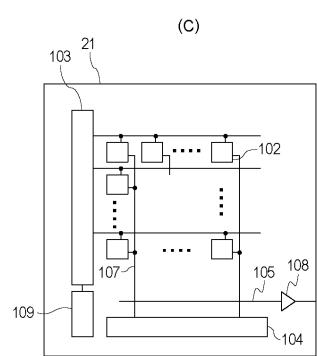

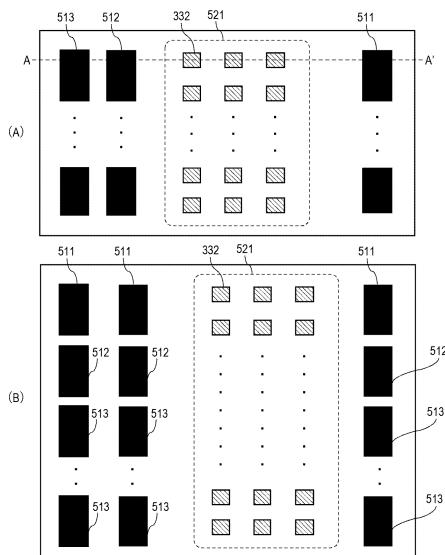

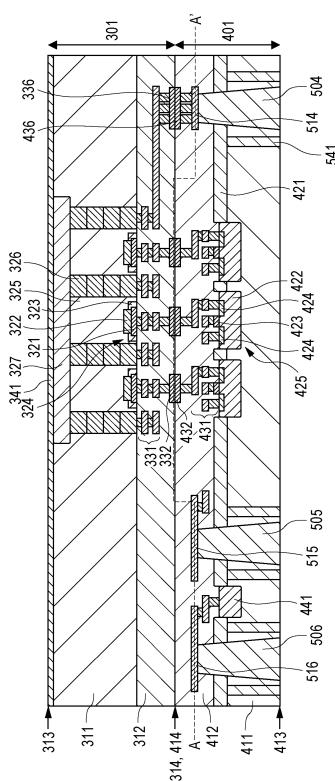

【図1】第1の実施形態に係る光電変換装置、画素チップ、回路チップの概略図である。

【図2】第1の実施形態に係る画素のブロック図である。

20

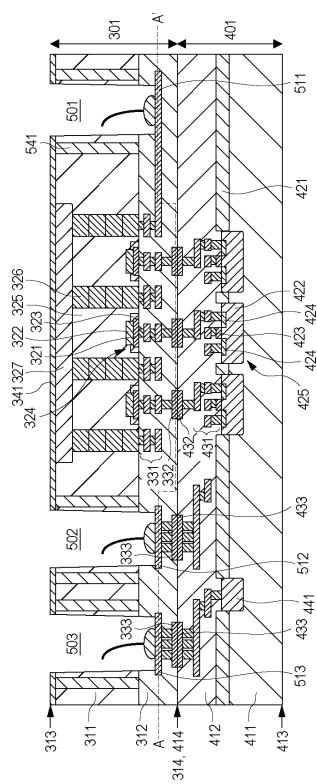

【図3】第1の実施形態に係る光電変換装置の断面図である。

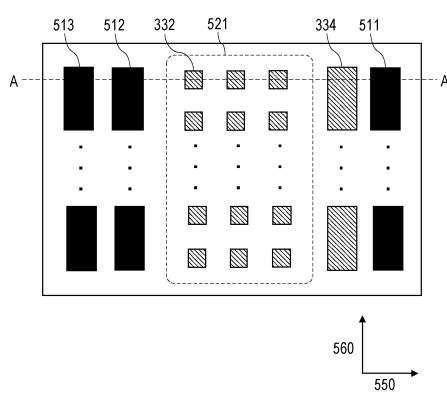

【図4】第1の実施形態に係る光電変換装置の平面図である。

【図5】第2の実施形態に係る光電変換装置の断面図である。

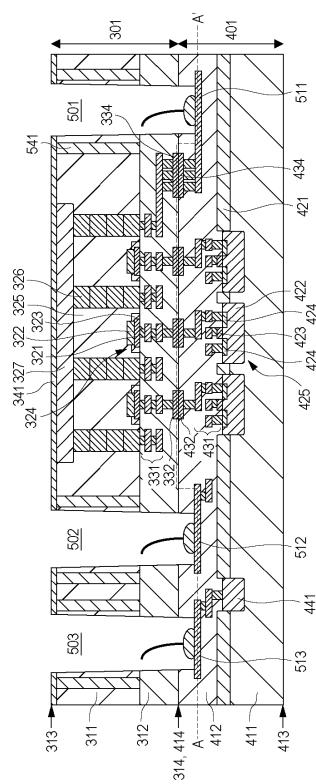

【図6】第3の実施形態に係る光電変換装置の断面図である。

【図7】第3の実施形態に係る光電変換装置の平面図である。

【図8】第4の実施形態に係る光電変換装置の断面図である。

【図9】第4の実施形態に係る光電変換装置の平面図である。

【図10】第5の実施形態に係る光電変換装置の断面図である。

【図11】第5の実施形態に係る光電変換装置の平面図である。

【図12】第6の実施形態に係る光電変換装置の断面図である。

30

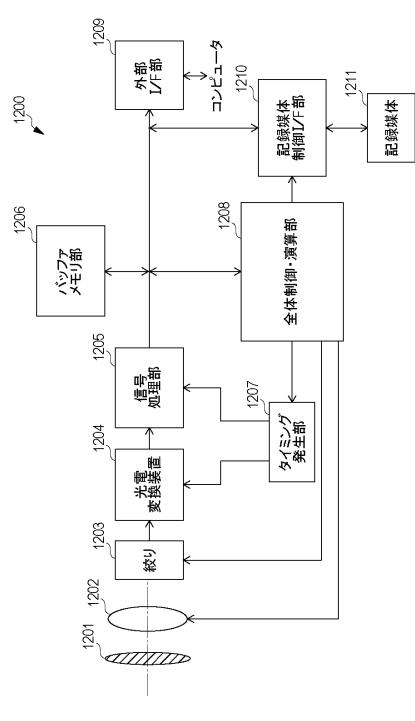

【図13】第7の実施形態の概略構成を示すブロック図である。

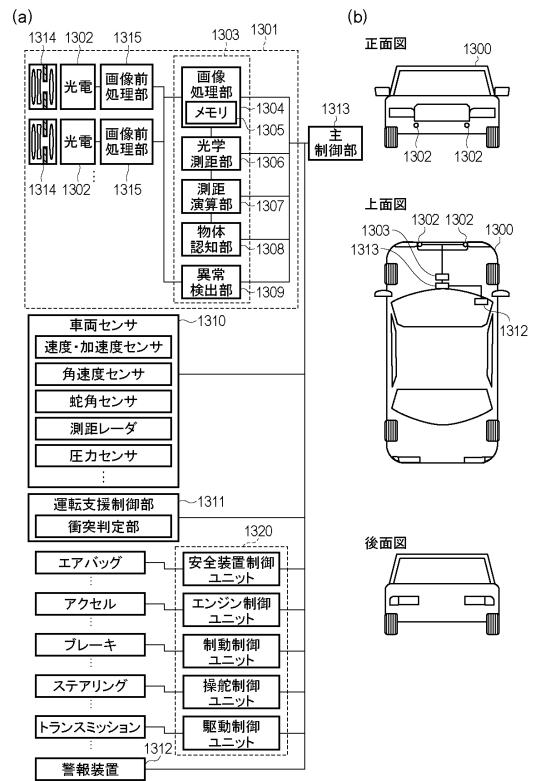

【図14】第8の実施形態の光電変換システムおよび移動体の概略図である。

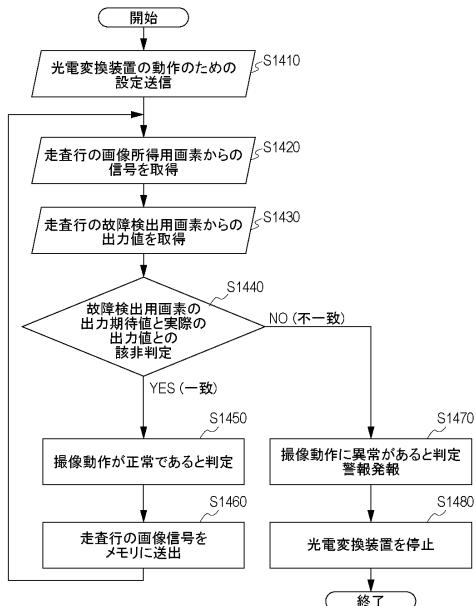

【図15】第8の実施形態の光電変換システムの動作を示すフロー図である。

**【発明を実施するための形態】**

**【0008】**

本発明に係る実施形態に係る光電変換装置について説明する。各実施形態の共通している符号は同じ部材または同じ機能・効果を奏する部材であるため、説明を省略することがある。また、各実施形態で説明した構成は、その他の実施形態で説明した構成と相互に置換することが可能である。

**【0009】**

40

[第1の実施形態]

図1(A)は、本発明の実施形態に係る積層型の光電変換装置の構成を示す図である。光電変換装置1010は、センサチップ11と、回路チップ21の2枚のチップが積層され、且つ電気的に接続されることにより構成される。

**【0010】**

センサチップ11には、画素領域12が配され、回路チップ21には、画素領域12で検出された信号を処理する回路領域22が配される。

**【0011】**

図1(B)は、センサチップ11の配置図である。光を電気信号へ変換する光電変換部101を有する画素100が二次元状に配列され、画素領域12を形成する。画素100

50

は、典型的には、画像を形成するための画素であるが、T O F ( Time of Flight )に用いる場合には、必ずしも画像を形成しなくてもよい。すなわち、画素 100 は、光が到達した時刻と光量を測定するための画素であってもよい。

#### 【 0 0 1 2 】

図 1 ( C ) は、回路チップ 21 の構成図である。図 1 ( B ) の光電変換部 101 で光電変換された電荷を処理する信号処理部 102 、制御パルス生成部 109 、水平走査回路部 104 、信号線 107 、垂直走査回路部 103 を有している。

#### 【 0 0 1 3 】

図 1 ( B ) の光電変換部 101 と、図 1 ( C ) の信号処理部 102 は、画素毎に設けられた接続配線を介して電気的に接続される。

10

#### 【 0 0 1 4 】

垂直走査回路部 103 は、制御パルス生成部 109 から供給された制御パルスを受け、各画素に制御パルスを供給する。垂直走査回路部 103 にはシフトレジスタやアドレスデコーダといった論理回路が用いられる。

#### 【 0 0 1 5 】

各画素の光電変換部 101 から出力された信号は、信号処理部 102 で処理される。信号処理部 102 は、カウンタとメモリが設けられており、メモリにはデジタル信号が保持される。

#### 【 0 0 1 6 】

水平走査回路部 104 は、デジタル信号が保持された各画素のメモリから信号を読み出すために、各列を順次選択する制御パルスを信号処理部 102 に入力する。

20

#### 【 0 0 1 7 】

信号線 107 と信号線 105 には、選択されている列について、垂直走査回路部 103 により選択された画素の信号処理部 102 から信号が出力される。

#### 【 0 0 1 8 】

信号線 105 に出力された信号は、出回路 108 を介して、光電変換装置 1010 の外部の記録部または信号処理部に出力する。

#### 【 0 0 1 9 】

図 1 ( B ) において、画素領域 12 における画素 100 の配列は 1 次元状に配されていてよい。また、垂直走査回路部 103 と水平走査回路部 104 は、回路領域 22 を複数の領域に分けて、領域毎に配してもよい。信号処理部 102 の機能は、必ずしも全ての画素 100 に 1 つずつ設けられる必要はなく、例えば、複数の画素 100 によって 1 つの信号処理部 102 が共有され、順次信号処理が行われてもよい。

30

#### 【 0 0 2 0 】

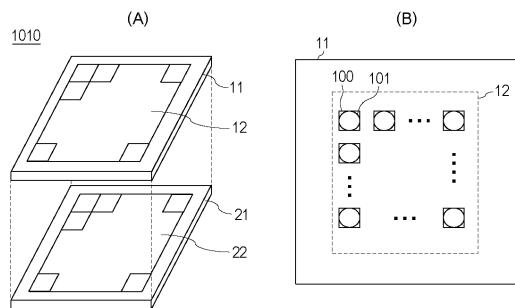

図 2 は、図 1 ( B ) 及び図 1 ( C ) の等価回路を含むブロック図の一例である。図 2 において、フォトダイオード 201 を有する光電変換部 101 は、センサチップ 11 に設けられており、その他の部材は、回路チップ 21 に設けられている。

#### 【 0 0 2 1 】

フォトダイオード 201 は、光電変換により入射光に応じた電荷対を生成する。フォトダイオード 201 のアノードには、電圧 VL ( 第 1 電圧 ) が供給されている。また、フォトダイオード 201 のカソードには、アノードに供給される電圧 VL よりも高い電圧 VH ( 第 2 電圧 ) が供給される。不図示であるが、電圧 VH ( 第 2 電圧 ) は、回路チップ 21 に設けられている回路にも供給される。フォトダイオード 201 のアノードとカソードには、フォトダイオード 201 がアバランシェダイオードとなるような逆バイアスの電圧が供給される。このような電圧を供給した状態とすることで、入射光によって生じた電荷がアバランシェ増倍を起こし、アバランシェ電流が発生する。逆バイアスの電圧が供給される場合において、アノードおよびカソードの電位差が降伏電圧より大きいときには、アバランシェダイオードはガイガーモード動作となる。例えば、電圧 VL ( 第 1 電圧 ) は、 -30V 、電圧 VH ( 第 2 電圧 ) は、 1.1V である。

40

#### 【 0 0 2 2 】

50

クエンチ素子 202 は、電圧 V<sub>H</sub> を供給する電源とフォトダイオード 201 に接続される。クエンチ素子 202 は、フォトダイオード 201 で生じたアバランシェ電流の変化を電圧信号に置き換える機能を有する。クエンチ素子 202 は、アバランシェ増倍による信号増倍時に負荷回路（クエンチ回路）として機能し、フォトダイオード 201 に供給する電圧を抑制して、アバランシェ増倍を抑制する働きを持つ（クエンチ動作）。センサチップ 11 に設けられているフォトダイオード 201 と、回路チップ 21 に設けられているクエンチ素子 202 は、画素毎に設けられた接続配線を介して電気的に接続される。

#### 【 0023 】

信号処理部 102 は、波形整形部 203、カウンタ回路 209、選択回路 206 を有する。本明細書において、信号処理部 102 は、波形整形部 203、カウンタ回路 209、選択回路 206 のいずれかを有していればよい。例えば、カウンタ回路 209 も信号処理部 102 である。

10

#### 【 0024 】

波形整形部 203 は、光子検出時に得られるフォトダイオード 201 のカソードの電位変化を整形して、パルス信号を出力する。波形整形部 203 としては、例えば、インバータ回路が用いられる。図 2 においては、波形整形部 203 として、インバータを一つ用いた例を示したが、複数のインバータを直列接続した回路を用いてもよいし、波形整形効果があるその他の回路を用いてもよい。

#### 【 0025 】

カウンタ回路 209 は、波形整形部 203 から出力されたパルス信号をカウントする。カウンタ回路 209 は、例えば N - bit カウンタ（N：正の整数）の場合、単一光子によるパルス信号を最大で約 2 の N 乗個までカウントすることが可能である。カウントした信号は、検出した信号として保持される。また、駆動線 207 を介して制御パルス pRES が供給されたとき、カウンタ回路 209 に保持された信号がリセットされる。

20

#### 【 0026 】

選択回路 206 には、図 1 (C) の垂直走査回路部 103 から、図 2 の駆動線 208（図 1 (C) では不図示）を介して制御パルス pSEL が供給され、カウンタ回路 209 と信号線 107 との電気的な接続、非接続を切り替える。選択回路 206 には、例えば、信号を出力するためのバッファ回路などを含む。

#### 【 0027 】

クエンチ素子 202 とフォトダイオード 201 との間や、光電変換部 101 と信号処理部 102 との間にトランジスタ等のスイッチを配して、電気的な接続を切り替えてよい。同様に、光電変換部 101 に供給される電圧 V<sub>H</sub> または電圧 V<sub>L</sub> の供給をトランジスタ等のスイッチを用いて電気的に切り替えてよい。

30

#### 【 0028 】

複数の画素が行列状に配された画素領域 12 においては、カウンタ回路 209 のカウントを行毎に順次リセットし、カウンタ回路 209 に保持された信号を行毎に順次出力するローリングシャッタ動作によって撮像画像を取得してもよい。あるいは、全画素行のカウンタ回路 209 のカウントを同時にリセットし、カウンタ回路 209 に保持された信号を行毎に順次出力するグローバル電子シャッタ動作によって撮像画像を取得してもよい。グローバル電子シャッタ動作を行う場合には、カウンタ回路 209 のカウントを行う場合と、行わない場合を切り替える手段を設けたほうがよい。切り替える手段とは、例えば前述したスイッチである。

40

#### 【 0029 】

本実施形態では、カウンタ回路 209 を用いる構成を示した。しかし、カウンタ回路 209 の代わりに、時間・デジタル変換回路（Time-to-Digital Converter：以下、TDC）、メモリを用いて、パルス検出タイミングを取得する光電変換装置 1010 としてもよい。このとき、波形整形部 203 から出力されたパルス信号の発生タイミングは、TDC によってデジタル信号に変換される。TDC には、パルス信号のタイミングの測定に、図 1 (C) の垂直走査回路部 103 から駆動線を介して、制御パル

50

ス p R E F ( 参照信号 ) が供給される。 T D C は、制御パルス p R E F を基準として、波形整形部 2 0 3 を介して各画素から出力された信号の入力タイミングを相対的な時間としたときの信号をデジタル信号として取得する。

#### 【 0 0 3 0 】

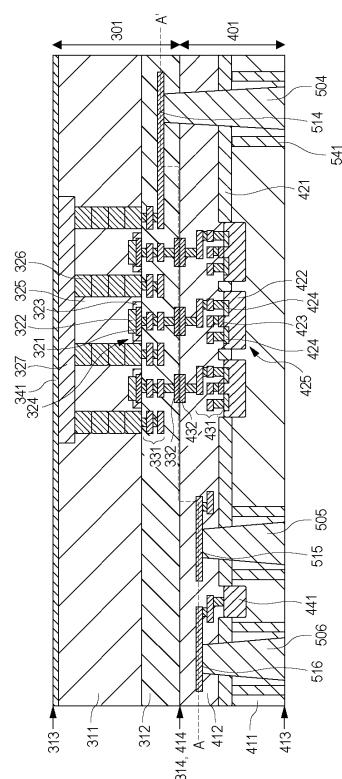

( 本実施形態に係る光電変換装置の断面図 : 図 3 )

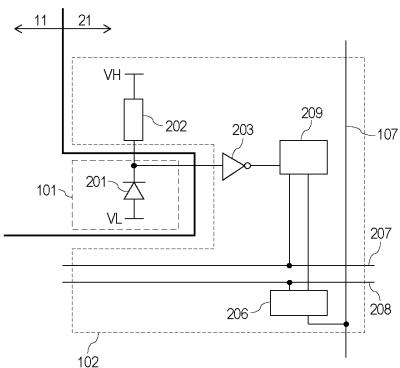

図 3 は、本実施形態の光電変換装置の断面図である。本実施形態は、第 1 チップ 3 0 1 と第 2 チップ 4 0 1 が積層され、電気的に接続された構造である。

#### 【 0 0 3 1 】

( 第 1 チップ 3 0 1 の構成 )

第 1 チップ 3 0 1 は、画素領域 5 2 1 が配される。第 2 チップ 4 0 1 には、画素領域 5 2 1 で検出された信号を処理する回路領域 5 3 1 が配される。第 1 チップ 3 0 1 、第 2 チップ 4 0 1 は、図 1 ( A ) のセンサチップ 1 1 、回路チップ 2 1 にそれぞれ対応する。

#### 【 0 0 3 2 】

第 1 チップ 3 0 1 は、半導体層 3 1 1 ( 第 1 半導体層 ) と配線層 3 1 2 ( 第 1 配線層 ) から構成される。第 1 チップ 3 0 1 の光入射面を面 3 1 3 ( 第 1 面 ) とし、面 3 1 3 とは反対側の面を面 3 1 4 ( 第 2 面 ) として、以下説明を行う。

#### 【 0 0 3 3 】

第 1 チップ 3 0 1 の半導体層 3 1 1 には、第 1 導電型の第 1 半導体領域 3 2 1 、第 2 導電型の第 2 半導体領域 3 2 2 が配される。第 1 半導体領域 3 2 1 と第 2 半導体領域 3 2 2 は、 P N 接合を形成し、アバランシェダイオード 3 2 4 となる。

#### 【 0 0 3 4 】

ここで、光電変換部で生じる電荷対のうち、信号電荷として用いられる電荷を多数キャリアとする半導体領域を第 1 導電型の半導体領域と呼ぶ。また、信号電荷として用いられない電荷を多数キャリアとする半導体領域を第 2 導電型の半導体領域と呼ぶ。例えば、電子を信号電荷として用いる場合、第 1 導電型の半導体領域は n 型半導体で構成され、第 2 導電型の半導体領域は p 型半導体で構成される。正孔を信号電荷として用いる場合は、その逆である。本実施形態では、電子を信号電荷として用いるものとして説明する。

#### 【 0 0 3 5 】

第 1 半導体領域 3 2 1 の両端部には、電界集中を緩和するための第 1 導電型または第 2 導電型の第 3 半導体領域 3 2 3 が配される。このとき、第 3 半導体領域 3 2 3 の不純物濃度は、第 1 半導体領域 3 2 1 の不純物濃度よりも低くする。例えば、第 1 半導体領域 3 2 1 の不純物濃度が  $6.0 \times 10^{18}$  [ a t m s / c m<sup>3</sup> ] 以上の場合に、第 3 半導体領域 3 2 3 の不純物濃度は  $1.0 \times 10^{16}$  [ a t m s / c m<sup>3</sup> ] 以上、  $1.0 \times 10^{18}$  [ a t m s / c m<sup>3</sup> ] 以下とする。

#### 【 0 0 3 6 】

第 2 半導体領域 3 2 2 よりも深部の面 3 1 3 側の領域には、第 2 導電型の第 4 半導体領域 3 2 5 が配される。さらに、隣接画素間には、画素間分離領域として第 2 導電型の第 5 半導体領域 3 2 6 を配し、第 4 半導体領域 3 2 5 よりも深部の面 3 1 3 側の領域には、第 2 導電型の第 6 半導体領域 3 2 7 が配される。

#### 【 0 0 3 7 】

ここで、第 4 半導体領域 3 2 5 の不純物濃度よりも、第 5 半導体領域 3 2 6 、第 6 半導体領域 3 2 7 の不純物濃度の方が高くなるようにする。これにより、第 4 半導体領域 3 2 5 で光電変換された電荷は、隣接画素へ漏れ込むことなく、アバランシェダイオード 3 2 4 に収集され、アバランシェ増幅することが可能となる。

#### 【 0 0 3 8 】

第 1 チップ 3 0 1 の面 3 1 3 側の界面には、チップ界面で発生する暗電流を抑制するためのピニング膜 3 4 1 が配される。

#### 【 0 0 3 9 】

第 1 チップ 3 0 1 の配線層 3 1 2 には、多層配線層 3 3 1 ( 第 1 多層配線層 ) が配される。この多層配線層 3 3 1 は、例えば、アバランシェダイオード 3 2 4 にアノード電位を

10

20

30

40

50

与える配線層や、カソード電位を与える配線層である。アバランシェダイオード324で検出された信号は、多層配線層331、接合部332（第1接合部）を介して、第2チップ401へ送られる。

#### 【0040】

パッド開口501（第1開口）の底部には、パッド電極511（第1電極）が設けられている。パッド開口501は、パッド電極511と外部電源とを導通するために、パッド電極511を露出させる開口である。パッド開口501の底部は、第1チップ301の面313（第1面）と面314（第2面）との間に設けられている。パッド電極511（第1電極）には、第1導電型の第1半導体領域321と第2導電型の第2半導体領域322の接合部にアバランシェ増倍を起こすために必要な電圧が、ワイヤーボンディングを介して印加される。多層配線層331の最上層をパッド電極511とする場合、多層配線層331の最上層をアルミ配線で構成し、それ以外の配線層を銅配線で構成してもよい。10

#### 【0041】

トレンチ酸化膜541が、半導体層311に配されている。各種回路や画素を有する半導体チップは、半導体チップの周囲の雰囲気等から侵入する水分やイオンから素子を保護する必要がある。そこで、パッド開口501等から侵入する水分やイオンからの保護をするために、パッド開口501の周辺の半導体層311にトレンチ酸化膜541が配されている。また、後述するパッド開口502および503の周辺の半導体層311にもトレンチ酸化膜541が配されている。防湿性を高めるためには、トレンチ酸化膜に替えて、あるいは、加えて、金属配線を配してもよい。この金属配線により、配線層に侵入する水分やイオンから素子を保護することができる。20

#### 【0042】

##### （第2チップ401の構成）

第2チップ401は、半導体層411（第2半導体層）と配線層412（第2配線層）を有する。第2チップ401において、第1チップ301側を面414（第3面）とし、面414とは反対側の面を面413（第4面）として、以下説明を行う。

#### 【0043】

第2チップ401の半導体層411には、第1チップ301から送られてきた信号を処理する回路が配される。具体的には、ウェル領域422、ゲート電極423、ソース・ドレイン領域424が配され、一つのMOSトランジスタ425を形成する。第2チップ401に配するMOSトランジスタ425の一例としては、クエンチ素子が挙げられる。クエンチ素子は、図2の素子202に相当し、光電変換された電荷がアバランシェ増倍する際の負荷回路として機能する。アバランシェダイオード324に供給する電圧を抑制して、アバランシェ増倍を抑制するクエンチ動作としての働きを持つ。30

#### 【0044】

隣接するMOSトランジスタの間には、素子分離領域421が配される。素子分離領域421は、例えばLOCOS（Local Oxidation of Silicon）、STI（Shallow Trench Isolation）などが挙げられる。

#### 【0045】

第2チップ401の配線層412に配される接合部432（第2接合部）は、第1チップ301の接合部332（第1接合部）と接触し、第1チップ301のアバランシェダイオード324の出力を、第2チップ401へ送る役割を有する。この接合部は、銅配線などの金属配線である。40

#### 【0046】

第2チップ401の配線層412には、多層配線層431（第2多層配線層）が配される。この多層配線層431は、例えば、第1チップ301から送られる信号を第2チップ401の処理回路へ伝えるための配線や、第2チップ401に搭載する信号処理部102を駆動するための電源配線や接地配線である。

#### 【0047】

第2チップ401の半導体層411には接地領域441が配される。接地領域441へ50

の接地電位の電圧（接地電圧；第3電圧）の供給は、パッド開口503（第3開口）の底部に配されるパッド電極513（第3電極）を通じて行われる。パッド開口503の底部は、第2チップ401の面414（第3面）と面413（第4面）との間に設けられている。第3電圧は、例えば、0Vである。なお、図3では、パッド電極513（第3電極）から印加される電圧は、接地領域41に供給されているが、必ずしも接地領域411を設けなくてもよい。この場合、パッド電極513（第3電極）から印加される電圧は、直接的に他の回路素子に供給される。

#### 【0048】

また、第2チップ401に配されるMOSトランジスタ425のドレイン電極には、パッド開口502（第2開口）の底部に配されるパッド電極512（第2電極）を通じて、所定の電位が供給される。パッド開口502の底部は、第2チップ401の面414（第3面）と面413（第4面）との間に設けられている。前記のとおり、MOSトランジスタ425は、例えば、アバランシェ増倍による信号増倍時に負荷回路として機能するクエンチ素子である。この場合、所定の電位は、電圧VH（第2電圧）は、例えば1.1Vである。電圧VL（第1電圧）は、例えば-30Vであるため、電圧VL（第1電圧）と電圧VH（第2電圧）の電位差は、電圧VH（第2電圧）と接地電位の電圧（第3電圧）の電位差よりも大きい。また、電圧VL（第1電圧）と接地電位の電圧（第3電圧）の電位差は、電圧VH（第2電圧）と接地電位の電圧（第3電圧）の電位差よりも大きい。

#### 【0049】

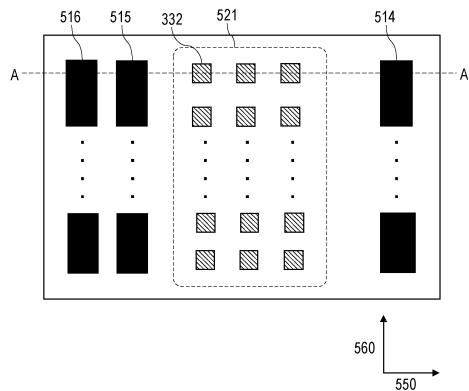

図4(A)は、図3の破線AA'について、平面視した際の平面図を示している。平面視とは、半導体層311または411の正面に対して垂直な方向（正面の法線方向）から光電変換装置1010を覗いた際の配置である。平面視した場合に、重なっている部材については、透視可能であるものとする。

#### 【0050】

図4(A)において、画素領域521内には、各画素で発生した信号を第2チップ401に送るための接合部332が二次元状に配列される。すなわち、複数の接合部332は、第1方向550（行方向）と、第1方向550と直交する第2方向560（列方向）の両方にわたって配されている。画素領域521の外側には、複数のパッド電極511、512、513が配される。

#### 【0051】

第2方向560（列方向）において、パッド電極511、512、513のそれぞれの長さは、接合部332の長さよりも大きい。すなわち、複数行（図4(A)では2行）に設けられている接合部332に対応して、1つのパッド電極が設けられている。これは、各パッド電極から供給される電位は、複数行の画素に対して共通に供給するように構成できるからである。また、仮に、1つの行に対応して1つのパッド電極を配置する場合、画素ピッチ毎にパッド電極を配置する必要があるため、微細化に対して不向きだからである。

#### 【0052】

また、図4(A)においては、第1方向550（行方向）においても、パッド電極511、512、513のそれぞれの長さは、接合部332の長さよりも大きい。この結果、パッド電極511、512、513のそれぞれの面積は、接合部332の面積よりも大きくなっている。

#### 【0053】

さらに、図4(A)においては、全行分の接合部332に対して1つのパッド電極を配するのではなく、全行よりも少ない所定の複数行の接合部332に対して1つのパッド電極が配されている。本実施形態では、画素部にアバランシェダイオードを含むため、画素に対して電位を与えるパッド電極には、アバランシェ電流が流れることになる。仮に、全行に対して1つのパッド電極を配するとすると、1つのパッド電極に流せる許容電流量の制約を越えてしまう可能性がある。そのため、全行ではない所定行数の接合部に対して、1つのパッド電極が設けられている。

#### 【0054】

10

20

30

40

50

なお、図4(A)では、第1方向550および第2方向560の両方について、パッド電極の長さを接合部の長さよりも大きくした例を示したが、どちらか一方の方向について長さを大きくするようにして、ピッチを大きくしてもよい。

#### 【0055】

また、図4(A)では、複数行に対して1つのパッド電極を配していたが、複数列に対して1つのパッド電極を配するように構成してもよい。

#### 【0056】

さらに、図4(A)では、画素領域の右側にパッド電極511を集約し、画素領域の左側にパッド電極512と513を集約して配している。他方、図4(B)に示すように、画素領域の右側と左側のそれぞれに、パッド電極511、512、513からなるユニットを配してもよい。各画素のアバランシェ増倍された電荷(電子および正孔)は、例えば、電子がパッド電極512に収集され、正孔がパッド電極511に収集される。例えば、図4(A)において、画素領域の左上の画素から電子と正孔が生じるとすると、電子は左側に配されているパッド電極512にすぐに収集されるが、正孔は右側に配されているパッド電極511に所定の時間経過して収集される。この場合、特に正孔に関しては、右側に配されるパッド電極511に収集されるまでに、画素毎にアバランシェ電荷が積算されるため、電圧降下が生じる原因となる。他方、図4(B)においては、パッド電極511および512が、右側と左側の両方に配されていることから、アバランシェ増倍された電子および正孔の両方が短時間で収集され、上記のような電圧降下が生じにくい。図4(B)に示した配置によれば、シェーディングの発生が抑制できるというメリットがある。

10

20

30

#### 【0057】

第1チップ301に配するアバランシェダイオード324の第1導電型の第1半導体領域321には、パッド電極512から電圧VH(第2電圧)が供給される。この電圧供給には、MOSトランジスタ425、第2チップの多層配線層431、第2チップの接合部432、第1チップの接合部332、第1チップの多層配線層331が介在する。また、第2導電型の第2半導体領域322には、第1チップに配されるパッド電極511、多層配線層331、第2導電型の第5半導体領域326、第2導電型の第4半導体領域325を介して、電圧VL(第1電圧)が供給される。電圧VL(第1電圧)と電圧VH(第2電圧)の電圧差は、第1導電型の第1半導体領域321と第2導電型の第2半導体領域322の接合部にアバランシェ増倍を起こすだけの十分な電界がかかるものとする。必要な電圧差は、例えば、6V以上であり、上記では、31.1Vの例を説明した。

#### 【0058】

ところで、第2チップの回路領域531は、処理回路の集積度を上げるために、駆動電圧の低い微細なトランジスタを配する必要がある。他方、パッド電極511へ印加する電圧VL(第1電圧)は、アバランシェフォトダイオードが設けられている第1チップ301のみに必要な電圧であり、第2チップの回路領域531には供給する必要がない。そこで、本実施形態では、パッド電極511は、第2チップ401の半導体層411と電気的に接続されていない構成としている。具体的には、パッド電極511と電気的に接続される配線が、第1チップ301と第2チップ401との接合面の境界を越えない構成とされている。これにより、第2チップの回路領域531の信頼性低下を抑制することができる。

40

#### 【0059】

また、パッド電極512へ印加する電位は、MOSトランジスタ425に供給される以外にも、第2チップ401に配する各種の処理回路に供給される。処理回路に求められる機能が増加し、第2チップ401に搭載される素子数が増加すると、高速性が課題となりうる。この場合、パッド電極512を第1チップ301に配して、接合部を介して電位を供給するよりも、図3で示すように、パッド電極512を第2チップ401に配して電位を供給する方が好ましい。この構成により、配線による伝搬遅延が低減できるため、第2チップ401に配する各種処理回路を、より高速に動作させることが可能となる。

#### 【0060】

また、第1チップ301に配するパッド電極511は、第1チップ301の多層配線層

50

331の最上層配線と同じ高さの配線層に配する。第2チップ401に配するパッド電極512、513は、第2チップの多層配線層431の最上層配線と同じ高さの配線層に配する。なお、本明細書においては、多層配線層331、431には、接合部332、432は含まれないものとしている。これにより、第1チップ301と第2チップ401に配するパッド電極の段差が減少し、パッド開口時のエッティングプロセスを容易することができる。また、この構成によれば、パッド開口部のワイヤーボンディング形成を容易にすることができる。

#### 【0061】

##### [第2の実施形態]

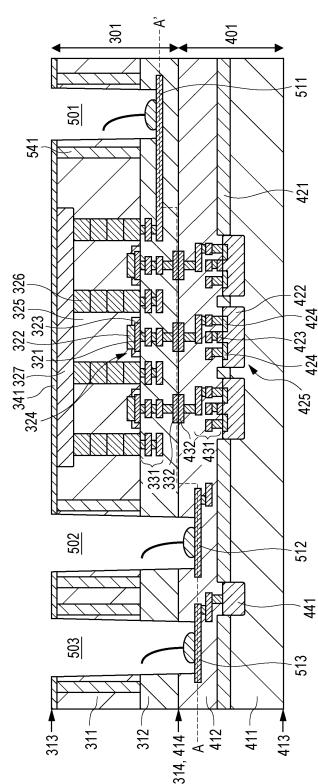

図5は、第2の実施形態に係る光電変換装置の断面図である。第1の実施形態との違いは、パッド電極512、513が第1チップ301に配され、接合部333、433を介して第2チップに電位が供給される点である。第1の実施形態と同じ部材についての説明は省略する。

10

#### 【0062】

図3に示すように、第1の実施形態では、パッド開口501と、パッド開口502、503の深さが異なるため、それぞれのパッド開口深さに最適なエッティング条件や、ワイヤーボンディング条件を適用する必要がある。一方、図5に示す第2の実施形態では、パッド電極511、512、513を第1チップ301に形成している。すなわち、パッド開口501、502、503の底部は、第1チップ301の面313(第1面)と面314(第2面)との間に設けられている。この構成によれば、第1の実施形態と比較して、パッド開口501、502、503の深さを揃えることが可能となる。そのため、パッド開口形成時のエッティング条件、ワイヤーボンディング条件を、パッド毎に最適化する必要がなくなる。

20

#### 【0063】

パッド電極511、512、513は、第1チップ301の多層配線層331のうち、同じ配線層に設けることが望ましい。具体的には、図5において、パッド電極511、512、513は、多層配線層331の最上層に設けられている。これにより、各パッド開口深さが同じになるため、パッド開口を形成する際のエッティング条件や、ワイヤーボンディングを形成する際の条件を同じにすることができる、これらを同一工程で形成することが可能となる。

30

#### 【0064】

図5において、パッド電極512、513と接合部333とは、複数のビアプラグによって接続されている。すなわち、1つのパッド電極と1つの接合部とは、複数のビアプラグによって接続されている。同様に、第2チップ401に設けられている多層配線層431の最上層に設けられている配線と、接合部433とは、複数のビアプラグで接続されている。これにより、電気抵抗を低減でき、信号の伝搬遅延を抑制することが可能となる。

#### 【0065】

ところで、第1の実施形態で説明したとおり、アバランシェダイオード324をアバランシェ増倍させる電圧のうち、第1チップのパッド電極511には、電圧VL(第1電圧)を印加する。この電圧は、第1チップ301に設けられる多層配線層331で引き回されるため、第2チップ401の回路領域531には供給されない。すなわち、第2チップ401に配する回路領域531の信頼性低下を抑制することができる。

40

#### 【0066】

なお、図5の破線AA'を含む平面図は、図3と同等であるため、詳細の説明を省略する。

#### 【0067】

以上により、第2の実施形態では、第2チップ401の回路領域531に対する信頼性低下を抑制することができる。また、パッド開口とワイヤーボンディングの形成プロセスの容易化を達成できる。

#### 【0068】

50

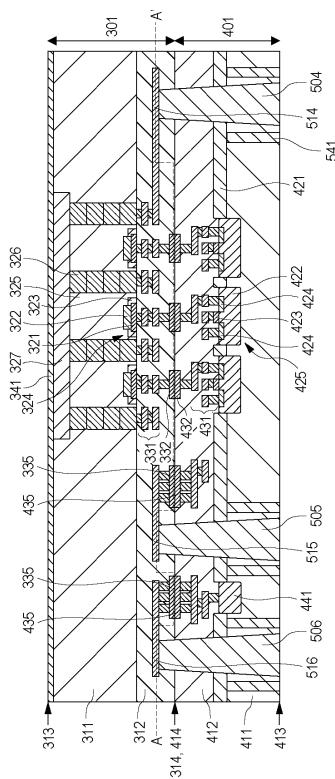

**[ 第 3 の実施形態 ]**

図 6 は、第 3 の実施形態に係る光電変換装置の断面図である。第 1 の実施形態との違いは、パッド電極 511 が第 2 チップ 401 に配され、接合部 434、334 を介して第 1 チップ 301 に電位が供給される点である。第 1 の実施形態と同じ部材についての説明は省略する。

**【 0 0 6 9 】**

第 1 の実施形態では、パッド開口 501 と、パッド開口 502、503 の深さが異なるため、それぞれのパッド開口深さに最適なエッチング条件や、ワイヤーボンディング条件を適用する必要がある。一方、図 6 に示す第 3 の実施形態では、パッド電極 511、512、513 を第 2 チップ 401 に形成している。すなわち、パッド開口 501、502、503 の底部は、第 2 チップ 401 の面 414（第 3 面）と面 413（第 4 面）との間に設けられている。この構成によれば、第 1 の実施形態と比較して、パッド開口 501、502、503 の深さを揃えることが可能となる。そのため、パッド開口形成時のエッチング条件、ワイヤーボンディング条件を、パッド毎に最適化する必要がなくなる。

10

**【 0 0 7 0 】**

第 1 の実施形態で説明したとおり、パッド電極 512 は第 2 チップ 401 に配され、その電位は、MOSトランジスタ 425 に供給される以外にも、第 2 チップ 401 に搭載される各種処理回路に供給される。また、処理回路に求められる機能が増加し、第 2 チップ 401 に搭載される素子数が増加すると、高速性が課題となる。この場合、パッド電極 512 を第 1 チップ 301 に配して、接合部を介して電位を供給するよりも、図 6 に示すように、パッド電極 512 を第 2 チップ 401 に配して電位を供給する方が好ましい。この構成により、配線による伝搬遅延が低減できるため、第 2 チップ 401 に配する各種処理回路を、より高速に動作させることが可能となる。

20

**【 0 0 7 1 】**

また、第 3 の実施形態では、パッド電極 511 は、第 2 チップ 401 の半導体層 411 と電気的に接続されていない構成としている。これにより、第 2 チップの回路領域 531 の信頼性悪化を回避することができる。

**【 0 0 7 2 】**

図 7 は、図 6 の破線 AA' について、平面視した際の平面図である。画素領域 521 内には、各画素で発生した信号を第 2 チップ 401 に送るための接合部 332 が二次元状に配列される。画素領域 521 の外側には、第 2 チップに配されるパッド電極 511、512、513 が配される。第 2 チップ 401 に配するパッド電極 511 に印加する電圧を、第 1 チップ 301 の画素領域 521 に供給するための接合部 334 が配される。第 1 方向 550 と第 2 方向 560 の両方向において、接合部 334 の長さは、接合部 332 の長さよりも大きい。このため、接合部 334 の面積は、接合部 332 の面積よりも大きい。図 4 (A) (B) に関する説明は、図 7 にも適用される。

30

**【 0 0 7 3 】**

以上により、第 3 の実施形態では、第 2 チップの回路領域 531 の信頼性低下を抑制しつつ、第 2 チップ 401 に搭載する各種処理回路の高速化を図ることができる。また、パッド開口とワイヤーボンディングの形成プロセスの容易化を達成することができる。

40

**【 0 0 7 4 】**

**[ 第 4 の実施形態 ]**

図 8 は、第 4 の実施形態に係る光電変換装置の断面図である。第 1 の実施形態との違いは、ワイヤーボンディングではなく、貫通電極 (TSV: Through-Silicon-Via) を用いている点である。以下、第 1 の実施形態と同じ部材についての説明は省略する。

**【 0 0 7 5 】**

具体的には、第 1 の実施形態のパッド開口 501 の底部に設けられていたワイヤーボンディング配線が、第 4 の実施形態の貫通電極 504 に対応している。同様に、パッド開口 502 の底部のワイヤーボンディング配線が貫通電極 505 に、パッド開口 503 の底部

50

のワイヤーボンディング配線が貫通電極 506 に、それぞれ対応する。

#### 【0076】

第 1 の実施形態のパッド電極 511（第 1 電極）が、第 4 の実施形態の電極 514（第 1 電極）に対応している。同様に、パッド電極 513（第 2 電極）が電極 516（第 2 電極）に、パッド電極 512（第 3 電極）が電極 515 に対応している。すなわち、これらの電極は、多層配線層 431（第 2 多層配線層）に設けられている電極であって、光電変換装置の外部から電圧が供給される電極である点で共通している。

#### 【0077】

第 4 の実施形態においては、電極 514 と外部電源とを導通するために、電極 514 を露出させるために形成される開口（第 1 開口）の底部が、第 1 チップ 301 の面 313（第 1 面）と面 314（第 2 面）との間に設けられている。この点も、第 1 の実施形態と共通している。同様に、電極 516 と 515 を露出させるために形成される開口（第 2 開口と第 3 開口）の底部は、第 2 チップ 401 の面 414（第 3 面）と面 413（第 4 面）との間に設けられている。この点も、第 1 の実施形態と共通している。なお、本願明細書では、開口（トレンチ）を形成した後に電極を充填した場合であっても、開口が形成された箇所について、「開口」と呼称することがある。

10

#### 【0078】

第 1 から第 3 の実施形態のように、電極構造をワイヤーボンディング配線にする場合、チップサイズに対してワイヤーを実装するためのスペースが余分に必要になるため、パッケージサイズの小型化が困難である。他方、貫通電極の場合には、バンプ等を介して貫通電極とパッケージ基板を接続するため、チップサイズとパッケージサイズを概ね同等のサイズにすることが可能となる。このため、ワイヤーボンディング配線と比較して、パッケージサイズの小型化が有利である

20

第 1 の実施形態と同様、貫通電極 504 に印加される電位は、電極 514 を介して第 1 チップ 301 の画素領域 521 に供給される。また、貫通電極 505、506 に印加される電位は、それぞれ電極 515、516 を介して、第 2 チップ 401 の回路領域 531 に相当する半導体層 411 に供給される。他方、貫通電極 504 に印加される電位は、第 2 チップ 401 の回路領域 531 には供給されない。そのため、第 1 の実施形態と同様、第 2 チップ 401 に配する回路領域 531 の信頼性低下を抑制することができる。また、貫通電極 505 は、第 2 チップ 401 に配されるため、第 2 チップ 401 に配する各種処理回路を、より高速に動作させることができる。

30

#### 【0079】

また、第 1 チップ 301 に配する電極 514 は、第 1 チップ 301 の多層配線層 331 の最上層配線と同じ高さの配線層に配し、第 2 チップ 401 に配する電極 515、516 は、第 2 チップ 401 の多層配線層 431 の最上層配線と同じ高さの配線層に配する。

#### 【0080】

貫通電極は、エッチングによって半導体層 411 を貫通する開口（トレンチ）を形成してから、電極材料となる金属を充填することにより形成する。複数の貫通電極に対応するトレンチをエッチングで形成する際、トレンチ深さの段差が少ない方が、プロセス的には簡便である。このため、前記のように、貫通電極と接触する電極を各チップの最上層配線と同じ高さの配線層に配することで、貫通電極の形成プロセスを容易化することができる。

40

#### 【0081】

図 9 は、図 8 の破線 A A' について、平面視した際の平面図である。画素領域 521 内には、各画素で発生した信号を第 2 チップ 401 に送るための接合部 332 が二次元状に配列される。画素領域 521 の外側には、第 1 チップ 301 内の電極 514、第 2 チップ 401 内の電極 515、516 がそれぞれ配される。図 4 (A) (B) に関する説明は、図 9 にも適用される。

#### 【0082】

以上により、第 4 の実施形態では、パッケージサイズの小型化、第 2 チップ 401 の回路領域 531 に対する信頼性低下の抑制、第 2 チップ 401 に搭載する各種処理回路の高

50

速化を達成することができる。

#### 【0083】

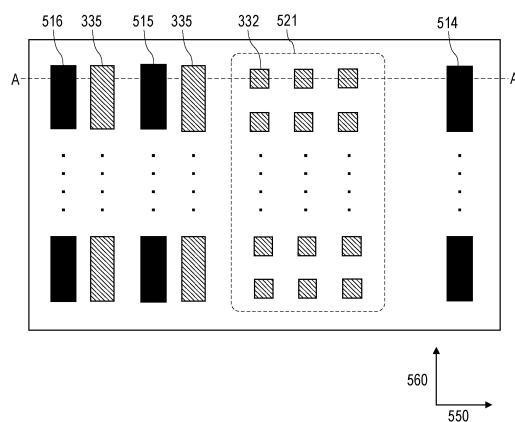

##### [第5の実施形態]

図10は、第5の実施形態の断面図である。第4の実施形態との違いは、電極515、516を第1チップ301に配する点である。第1の実施形態と同じ部材についての説明は省略する。

#### 【0084】

第4の実施形態では、第1チップの電極514と、第2チップの電極515、516が配されている場所が異なるため、トレンチ形成時のエッチング条件や、トレンチに金属を埋め込む際の成膜条件を、各電極の場所に応じて最適化する必要がある。他方、第5の実施形態では、貫通電極514、515、516を全て第1チップに配することで、各電極が設けられている場所に応じてプロセス条件を最適化する必要がなくなり、プロセスを容易化することができる。

10

#### 【0085】

また、電極514、515、516は、第1チップ301の多層配線層331のうち、同じ配線層に設けることが望ましい。具体的には、図10において、電極514、515、516は、多層配線層331の最上層に設けられている。これにより、各貫通電極のトレンチ深さが同じになるため、トレンチを形成する際のエッチング条件や、トレンチに電極材料となる金属を埋め込む際の成膜条件を同じにすることができる、これらを同一工程で形成することが可能となる。

20

#### 【0086】

図10において、電極515、516と接合部335とは、複数のビアプラグによって接続されている。すなわち、多層配線層に設けられている1つの電極と1つの接合部とは、複数のビアプラグによって接続されている。同様に、第2チップ401に設けられている多層配線層431の最上層に設けられている配線と、接合部433とは、複数のビアプラグで接続されている。これにより、電気抵抗を低減でき、信号の伝搬遅延を抑制することが可能となる。

20

#### 【0087】

ところで、第1の実施形態で説明したとおり、アバランシェダイオード324をアバランシェ増倍させる電圧のうち、第1チップの電極514には、電圧VL(第1電圧)を印加する。この電圧は、第1チップ301に設けられる多層配線層331で引き回されるため、第2チップ401の回路領域531には供給されない。すなわち、第2チップ401に配する回路領域531の信頼性低下を抑制することができる。

30

#### 【0088】

図11は、図10の破線AA'を含む平面図である。画素領域521内には、各画素で発生した信号を第2チップ401に送るための接合部332が二次元状に配列される。画素領域521の外側には、第1チップ301内の電極514、第1チップ301内の電極515、516、及び前記電極の印加電位を第2チップへ伝えるための接合部335が配列される。図4(A)(B)に関する説明は、図11にも適用される。

40

#### 【0089】

以上により、第5の実施形態では、第2チップ401の回路領域531に対する信頼性低下の抑制が可能である。また、貫通電極形成プロセスの容易化を達成することができる。

#### 【0090】

##### [第6の実施形態]

図12は、第6の実施形態に係る光電変換装置の断面図である。第4の実施形態との違いは、貫通電極514を第2チップ401に配する点である。第4の実施形態と同じ部材についての説明は省略する。

#### 【0091】

第6の実施形態では、第4の実施形態と比較して、電極514、515、516を第2チップに配するため、トレンチ形成時のエッチング条件や、トレンチへの金属充填時の成

50

膜条件を各電極深さに応じて最適化する必要がなく、プロセスを容易化できる。

#### 【0092】

電極514、515、516が配される深さは、第2チップ401内の同じ深さであることが望ましい。これにより、各貫通電極のトレンチ深さが同じになるため、トレンチ形成時のエッチング条件や、トレンチに電極材料となる金属を埋め込む際の成膜条件と同じにすることができる。

#### 【0093】

また、第6の実施形態では、貫通電極504に印加する電位が、接合部436、336を介して第1チップ301に供給されるため、第2チップ401の回路領域531に供給されることはない。従って、第2チップの回路領域531の信頼性低下を抑制することができる。

10

#### 【0094】

貫通電極515は第2チップ401に配され、その電位は、MOSトランジスタ425に供給される以外にも、第2チップ401に搭載される各種処理回路に供給される。処理回路に求められる機能が増加し、第2チップ401に搭載される素子数が増加すると、高速性が課題となる。その場合、貫通電極515を第1チップ301に配して、接合部を介して電位を供給するよりも、貫通電極515を第2チップ401に配して電位を供給する方が、第2チップに配する各種処理回路を、より高速に動作させることが可能となる。なお、図12の破線AA'を含む平面図は、図9と同等であるため、詳細の説明を省略する。

#### 【0095】

以上により、第6の実施形態では、第2チップ401の回路領域531に対する信頼性低下の抑制、第2チップ401に搭載する各種処理回路の高速化、貫通電極形成プロセスの容易化を達成することができる。

20

#### 【0096】

##### [第7の実施形態]

図13は、本実施形態に係る光電変換システム1200の構成を示す領域図である。本実施形態の光電変換システム1200は、光電変換装置1204を含む。光電変換装置1204は、上述の実施形態で述べた光電変換装置のいずれかを適用することができる。光電変換システム1200は例えば、撮像システムとして用いることができる。撮像システムの具体例としては、デジタルスチルカメラ、デジタルカムコーダー、監視カメラ等が挙げられる。図13では、光電変換システム1200としてデジタルスチルカメラの例を示している。

30

#### 【0097】

図13に示す光電変換システム1200は、光電変換装置1204、被写体の光学像を光電変換装置1204に結像させるレンズ1202、レンズ1202の通過光量を可変にする絞り1203、レンズ1202を保護するバリア1201を有する。レンズ1202および絞り1203は、光電変換装置1204に光を集光する光学系である。

#### 【0098】

光電変換システム1200は、光電変換装置1204から出力される出力信号の処理を行う信号処理部1205を有する。信号処理部1205は、必要に応じて入力信号に対して各種の補正、圧縮を行って出力する信号処理の動作を行う。光電変換システム1200は、更に、画像データを一時的に記憶するためのバッファメモリ部1206、外部コンピュータ等と通信するための外部インターフェース部(外部I/F部)1209を有する。更に光電変換システム1200は、撮像データの記録又は読み出しを行うための半導体メモリ等の記録媒体1211、記録媒体1211に記録または読み出しを行うための記録媒体制御インターフェース部(記録媒体制御I/F部)1210を有する。記録媒体1211は、光電変換システム1200に内蔵されていてもよく、着脱可能であってもよい。また、記録媒体制御I/F部1210から記録媒体1211との通信や外部I/F部1209からの通信は無線によってなされてもよい。

40

#### 【0099】

50

更に光電変換システム 1200 は、各種演算を行うとともにデジタルスチルカメラ全体を制御する全体制御・演算部 1208、光電変換装置 1204 と信号処理部 1205 に各種タイミング信号を出力するタイミング発生部 1207 を有する。ここで、タイミング信号などは外部から入力されてもよく、光電変換システム 1200 は、少なくとも光電変換装置 1204 と、光電変換装置 1204 から出力された出力信号を処理する信号処理部 1205 とを有すればよい。

#### 【0100】

全体制御・演算部 1208 およびタイミング発生部 1207 は、光電変換装置 1204 の制御機能の一部または全部を実施するように構成してもよい。

#### 【0101】

光電変換装置 1204 は、画像用信号を信号処理部 1205 に出力する。信号処理部 1205 は、光電変換装置 1204 から出力される画像用信号に対して所定の信号処理を実施し、画像データを出力する。また、信号処理部 1205 は、画像用信号を用いて、画像を生成する。また、信号処理部 1205 は、光電変換装置 1204 から出力される信号に対して測距演算を行ってもよい。信号処理部 1205 やタイミング発生部 1207 は、光電変換装置に搭載されていてもよい。つまり、信号処理部 1205 やタイミング発生部 1207 は、画素が配されたチップに設けられていてもよい。上述した各実施形態の光電変換装置を用いて撮像システムを構成することにより、より良質の画像が取得可能な撮像システムを実現することができる。

#### 【0102】

10

##### [第8の実施形態]

本実施形態の光電変換システム及び移動体について、図 14 および図 15 を用いて説明する。図 14 は、本実施形態による光電変換システム及び移動体の構成例を示す概略図である。図 15 は、本実施形態による光電変換システムの動作を示すフロー図である。本実施形態では、光電変換システムとして、車載カメラの一例を示す。

#### 【0103】

図 14 は、車両システムとこれに搭載される撮像を行う光電変換システムの一例を示したものである。光電変換システム 1301 は、光電変換装置 1302、画像前処理部 1315、集積回路 1303、光学系 1314 を含む。光学系 1314 は、光電変換装置 1302 に被写体の光学像を結像する。光電変換装置 1302 は、光学系 1314 により結像された被写体の光学像を電気信号に変換する。光電変換装置 1302 は、上述の各実施形態のいずれかの光電変換装置である。画像前処理部 1315 は、光電変換装置 1302 から出力された信号に対して所定の信号処理を行う。画像前処理部 1315 の機能は、光電変換装置 1302 内に組み込まれていてもよい。光電変換システム 1301 には、光学系 1314、光電変換装置 1302 及び画像前処理部 1315 が、少なくとも 2 組設けられており、各組の画像前処理部 1315 からの出力が集積回路 1303 に入力されるようになっている。

30

#### 【0104】

集積回路 1303 は、撮像システム用途向けの集積回路であり、メモリ 1305 を含む画像処理部 1304、光学測距部 1306、測距演算部 1307、物体認知部 1308、異常検出部 1309 を含む。画像処理部 1304 は、画像前処理部 1315 の出力信号に対して、現像処理や欠陥補正等の画像処理を行う。メモリ 1305 は、撮像画像の一次記憶、撮像画素の欠陥位置を格納する。光学測距部 1306 は、被写体の合焦や、測距を行う。測距演算部 1307 は、複数の光電変換装置 1302 により取得された複数の画像データから測距情報の算出を行う。物体認知部 1308 は、車、道、標識、人等の被写体の認知を行う。異常検出部 1309 は、光電変換装置 1302 の異常を検出すると、主制御部 1313 に異常を発報する。

40

#### 【0105】

集積回路 1303 は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよいし、これらの組合せによって実現されて

50

もよい。また、FPGA(Field Programmable Gate Array)やASIC(Application Specific Integrated Circuit)等によって実現されてもよいし、これらの組合せによって実現されてもよい。

#### 【0106】

主制御部1313は、光電変換システム1301、車両センサ1310、制御ユニット1320等の動作を統括・制御する。主制御部1313を持たず、光電変換システム1301、車両センサ1310、制御ユニット1320が個別に通信インターフェースを有して、それぞれが通信ネットワークを介して制御信号の送受を行う（例えばCAN規格）方法も取り得る。

#### 【0107】

集積回路1303は、主制御部1313からの制御信号を受け或いは自身の制御部によって、光電変換装置1302へ制御信号や設定値を送信する機能を有する。

#### 【0108】

光電変換システム1301は、車両センサ1310に接続されており、車速、ヨーレート、舵角などの自車両走行状態及び自車外環境や他車・障害物の状態を検出することができる。車両センサ1310は、対象物までの距離情報を取得する距離情報取得手段もある。また、光電変換システム1301は、自動操舵、自動巡回、衝突防止機能等の種々の運転支援を行う運転支援制御部1311に接続されている。特に、衝突判定機能に関しては、光電変換システム1301や車両センサ1310の検出結果を基に他車・障害物との衝突推定・衝突有無を判定する。これにより、衝突が推定される場合の回避制御、衝突時の安全装置起動を行う。

#### 【0109】

また、光電変換システム1301は、衝突判定部での判定結果に基づいて、ドライバーに警報を発する警報装置1312にも接続されている。例えば、衝突判定部の判定結果として衝突可能性が高い場合、主制御部1313は、ブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして、衝突を回避、被害を軽減する車両制御を行う。警報装置1312は、音等の警報を鳴らす、カーナビゲーションシステムやメーターパネルなどの表示部画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

#### 【0110】

本実施形態では、車両の周囲、例えば前方又は後方を光電変換システム1301で撮影する。図14(b)に、車両前方を光電変換システム1301で撮像する場合の光電変換システム1301の配置例を示す。

#### 【0111】

2つの光電変換装置1302は、車両1300の前方に配される。具体的には、車両1300の進退方位又は外形（例えば車幅）に対する中心線を対称軸に見立て、その対称軸に対して2つの光電変換装置1302が線対称に配されると、車両1300と被写対象物との間の距離情報の取得や衝突可能性の判定を行う上で好ましい。また、光電変換装置1302は、運転者が運転席から車両1300の外の状況を視認する際に運転者の視野を妨げない配置が好ましい。警報装置1312は、運転者の視野に入りやすい配置が好ましい。

#### 【0112】

次に、光電変換システム1301における光電変換装置1302の故障検出動作について、図15を用いて説明する。光電変換装置1302の故障検出動作は、図15に示すステップS1410～S1480に従って実施される。

#### 【0113】

ステップS1410は、光電変換装置1302のスタートアップ時の設定を行うステップである。すなわち、光電変換システム1301の外部（例えば主制御部1313）又は光電変換システム1301の内部から、光電変換装置1302の動作のための設定を送信し、光電変換装置1302の撮像動作及び故障検出動作を開始する。

#### 【0114】

10

20

30

40

50

次いで、ステップ S 1420において、有効画素から画素信号を取得する。また、ステップ S 1430において、故障検出用に設けた故障検出画素からの出力値を取得する。この故障検出画素は、有効画素と同じく光電変換部を備える。この光電変換部には、所定の電圧が書き込まれる。故障検出用画素は、この光電変換部に書き込まれた電圧に対応する信号を出力する。なお、ステップ S 1420とステップ S 1430とは逆でもよい。

#### 【0115】

次いで、ステップ S 1440において、故障検出画素の出力期待値と、実際の故障検出画素からの出力値との該非判定を行う。ステップ S 1440における該非判定の結果、出力期待値と実際の出力値とが一致している場合は、ステップ S 1450に移行し、撮像動作が正常に行われていると判定し、処理ステップがステップ S 1460へと移行する。ステップ S 1460では、走査行の画素信号をメモリ 1305に送信して一次保存する。その後、ステップ S 1420に戻り、故障検出動作を継続する。一方、ステップ S 1440における該非判定の結果、出力期待値と実際の出力値とが一致していない場合は、処理ステップはステップ S 1470に移行する。ステップ S 1470において、撮像動作に異常があると判定し、主制御部 1313、又は警報装置 1312に警報を発報する。警報装置 1312は、表示部に異常が検出されたことを表示させる。その後、ステップ S 1480において光電変換装置 1302を停止し、光電変換システム 1301の動作を終了する。

10

#### 【0116】

なお、本実施形態では、1行毎にフローチャートをループさせる例を例示したが、複数行毎にフローチャートをループさせてもよいし、1フレーム毎に故障検出動作を行ってもよい。ステップ S 1470の警報の発報は、無線ネットワークを介して、車両の外部に通知するようにしてもよい。

20

#### 【0117】

また、本実施形態では、他の車両と衝突しない制御を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。さらに、光電変換システム 1301は、自車両等の車両に限らず、例えば、船舶、航空機或いは産業用ロボットなどの移動体（移動装置）に適用することができる。加えて、移動体に限らず、高度道路交通システム（ITS）等、広く物体認識を利用する機器に適用することができる。

30

#### 【0118】

本発明は、上記実施形態に限らず種々の変形が可能である。例えば、いずれかの実施形態の一部の構成を他の実施形態に追加した例や、他の実施形態の一部の構成と置換した例も、本発明の実施形態である。

#### 【0119】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されなければならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

#### 【符号の説明】

#### 【0120】

40

301 第1チップ

401 第2チップ

324 アバランシェダイオード

521 画素領域

531 回路領域

501、502、503 パッド開口

511、512、513 パッド電極

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

10

20

30

40

50

【図5】

【図6】

10

20

【図7】

【図8】

30

40

50

【 四 9 】

【図10】

10

20

30

40

【図11】

【图 12】

50

【図13】

【図14】

10

20

【図15】

30

40

50

---

フロントページの続き

ヤノン株式会社内

合議体

審判長 恩田 春香

審判官 松永 稔

審判官 緑川 隆

- (56)参考文献 国際公開第18 / 186195号 (WO , A1)

特開2018 - 157387号公報 (JP , A)

特開2018 - 81945 (JP , A)

米国特許出願公開第2016 / 0020235 (US , A1)

特開2015 - 029047 (JP , A)

(58)調査した分野 (Int.Cl. , DB名)

H 10 F 39 / 18