(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4167313号

(P4167313)

(45) 発行日 平成20年10月15日(2008.10.15)

(24) 登録日 平成20年8月8日(2008.8.8)

|               |                   |

|---------------|-------------------|

| (51) Int.Cl.  | F 1               |

| HO 1 L 29/861 | (2006.01)         |

| HO 1 L 29/06  | (2006.01)         |

| HO 1 L 29/78  | (2006.01)         |

| HO 1 L 29/739 | (2006.01)         |

|               | HO 1 L 29/91 D    |

|               | HO 1 L 29/06 301M |

|               | HO 1 L 29/78 652P |

|               | HO 1 L 29/78 655F |

|               | HO 1 L 29/78 655D |

請求項の数 2 (全 34 頁)

|              |                       |                |           |

|--------------|-----------------------|----------------|-----------|

| (21) 出願番号    | 特願平10-50745           | (73) 特許権者      | 000003078 |

| (22) 出願日     | 平成10年3月3日(1998.3.3)   | 株式会社東芝         |           |

| (65) 公開番号    | 特開平10-321877          | 東京都港区芝浦一丁目1番1号 |           |

| (43) 公開日     | 平成10年12月4日(1998.12.4) | (74) 代理人       | 100058479 |

| 審査請求日        | 平成16年6月15日(2004.6.15) | 弁理士 鈴江 武彦      |           |

| (31) 優先権主張番号 | 特願平9-65151            | (74) 代理人       | 100084618 |

| (32) 優先日     | 平成9年3月18日(1997.3.18)  | 弁理士 村松 貞男      |           |

| (33) 優先権主張国  | 日本国(JP)               | (74) 代理人       | 100092196 |

|              |                       | 弁理士 橋本 良郎      |           |

|              |                       | (74) 代理人       | 100091351 |

|              |                       | 弁理士 河野 哲       |           |

|              |                       | (74) 代理人       | 100088683 |

|              |                       | 弁理士 中村 誠       |           |

|              |                       | (74) 代理人       | 100070437 |

|              |                       | 弁理士 河井 将次      |           |

最終頁に続く

(54) 【発明の名称】高耐圧電力用半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1と第2の主面を有し、前記第1および第2の主面のいずれかに少なくとも一つの段差により形成された凹部を有する高抵抗の第1導電型の半導体基板と、

前記半導体基板の前記凹部が形成された領域に少なくともその1部が形成された、低不純物濃度の第2導電型リサーフからなる電界緩和構造と、

前記半導体基板の前記凹部が形成された前記第1および第2の主面のいずれかの側に形成され、前記リサーフより高不純物濃度の第2導電型アノード層を有する電力用ダイオード、

とを具備し、

前記電力用ダイオードの前記アノード層が形成された前記半導体基板の高抵抗部分の厚さが、前記電界緩和構造下の前記半導体基板の高抵抗部分の厚さよりも小さく、

前記リサーフは、前記半導体基板の前記第1の主面または第2の主面に形成された前記凹部を取り囲み、前記電力用ダイオードの前記アノード層に接していることを特徴とする高耐圧電力用半導体装置。

## 【請求項 2】

前記電力用ダイオードの前記アノード層が、前記第1導電型の半導体基板との界面に複数の段差を有することを特徴とする請求項1に記載の高耐圧電力用半導体装置。

## 【発明の詳細な説明】

【0001】

**【発明の属する技術分野】**

本発明は、ダイオードやIGBT等の高耐圧電力用半導体素子を含む半導体装置に関する。

**【0002】****【従来の技術】**

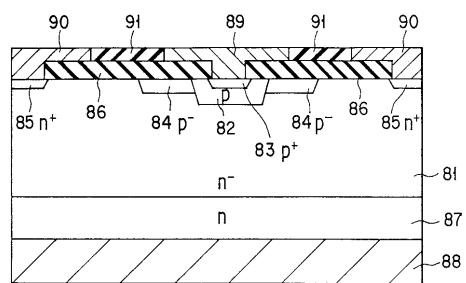

電力制御を行なう高耐圧半導体装置に用いられる高耐圧半導体素子の1つとして、高耐圧ダイオードがある。図55に、従来の高耐圧ダイオードの断面図を示す。

**【0003】**

図55において、81は高抵抗の第1のn型カソード層(半導体基板)を示しており、このn型カソード層81の表面には、第1のp型アノード層82が選択的に形成されている。この第1のp型アノード層82の表面には、高不純物濃度の第2のp型アノード層83が選択的に形成されている。

10

**【0004】**

また、n型カソード層81の表面には、電界緩和構造(接合終端構造)である低不純物濃度のp型リサーフ層84がp型アノード層に接してその周囲に形成されている。さらに、n型カソード層81の表面には、高不純物濃度のn型チャネルストッパ層85がp型リサーフ層84から所定距離離れてその外側に形成されている。

**【0005】**

また、第2のp型アノード層83の縁から第1のp型アノード層82、p型リサーフ層84、n型カソード層81、n型チャネルストッパ層85にまたがる領域上には高抵抗膜86が設けられている。なお、高抵抗膜86の代わりに、絶縁膜が設けられているものもある。

20

**【0006】**

一方、高抵抗の第1のn型カソード層81の裏面には、それよりも高不純物濃度の第2のn型カソード層87が形成されている。このn型カソード層87にはカソード電極88が設けられている。また、第2のp型アノード層83にはアノード電極89、n型チャネルストッパ層85には電極90が設けられている。91は絶縁膜を示している。

**【0007】**

しかしながら、この種の従来の高耐圧ダイオードには、以下のような問題がある。すなわち、高耐圧化を図るために、n型カソード層81を厚くする必要があるが、n型カソード層81が厚くなると、その分、順方向電圧降下、逆回復損失が大きくなるなど素子特性が劣化するという問題が起こる。最悪の場合、装置の破壊につながる。

30

**【0008】**

一方、インバータ回路やチョッパ回路等のスイッチング回路に対して、装置の小型化と高性能化のニーズが近年ますます強くなっている。

**【0009】**

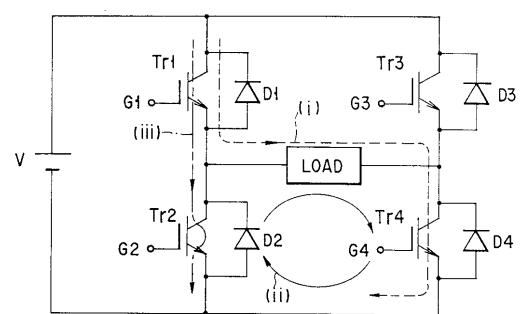

図56は、従来のIGBTを用いたインバータの主回路構成を示す。インバータ回路では、モータ制御のように負荷にインダクタンス成分を含むため、スイッチング素子(ここでは、IGBT)Tr1-Tr4を選択的にターンオフしたとき、負荷のインダクタンスに蓄えられたエネルギーを放出する必要がある。この電気エネルギーを還流するために、還流ダイオードD1-D4がIGBTに逆並列に接続される。

40

**【0010】**

このような従来の半導体装置では、IGBTと還流ダイオードのそれぞれにおいて、電源電圧以上の耐圧を得るために、半導体チップ内で一定面積以上の接合終端領域が必要となる。このため、チップ面積の縮小が難しく、高電流密度化が困難である。また、モジュールとする場合、IGBTに個別素子の還流ダイオードが外付けで接続される。すなわち、IGBTチップと還流ダイオードチップが同一基板上に載置され、それぞれチップ上の電極と外部導出電極の間が配線で接続される。この構成では、接続配線のインダクタンスのために、高速化が困難である。

**【0011】**

50

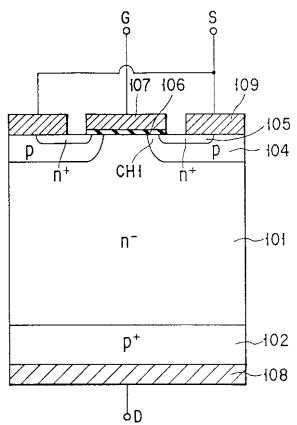

また、IGBT単体についても、低損失化が求められている。図57は、この種のIGBTの構成を示す断面図である。このIGBTでは、高抵抗のn型ベース層（半導体基板）101の一方の面にp型ドレイン層102が形成されている。一方、n型ベース層101の他方の面にp型ベース層104が選択的に形成され、p型ベース層104内にはn型ソース層105が形成されている。さらに、n型ベース層101とn型ソース層105との間のp型ベース層104上には、ゲート絶縁膜106を介してゲート電極107が形成されている。なお、これらゲート電極107、ゲート絶縁膜106、p型ベース層104、n型ベース層101及びn型ソース層105により、CH1をチャネル領域とする電子注入用MOSFETが構成されている。p型ドレイン層102上にはドレイン電極108が形成され、n型ソース層105上及びp型ベース層104上にはソース電極109が形成されている。

#### 【0012】

次に、このような半導体装置の動作を説明する。ドレイン電極108に正電圧、ソース電極109に負電圧が印加されている時、ソースよりも正となる正電圧をゲート電極107に印加すると、p型ベース層104のゲート電極107に接した表面がn型に反転し、電子eがn型ソース層105から反転層を介してn型ベース層101に注入されてp型ドレイン層102に到達する。これに伴い、p型ドレイン層2から正孔hがn型ベース層101に注入される。このようにn型ベース層101に電子eと正孔hの両方が注入され、伝導度変調が起こってオン電圧が低減可能となる。

#### 【0013】

一方、ターンオフ動作の際には、ソースに対して負である負電圧が絶縁ゲート107に印加される。これにより、ゲート電極107直下に形成されていた反転層が消失して電子注入が止まる。一方、n型ベース層101中の正孔hは、その一部がp型ベース層104を介してソース電極109に排出され、残りの正孔hは、電子eと再結合して消滅する。これにより、半導体装置はターンオフする。

#### 【0014】

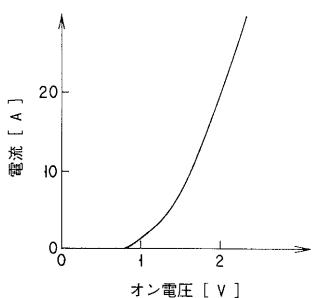

しかしながら、上述のような従来のIGBTでは、その導通状態において、電子e及び正孔hがnベース層101とp型ドレイン層102との間に形成されるpn接合によるポテンシャル障壁を越える必要がある。すなわち、図58の電流-電圧特性図に示すように、pn接合による電圧降下として、約0.7V程度のビルトイン電圧分だけオン抵抗が増大する。このため、従来のIGBTでは、導通状態のオン抵抗を十分に低減できないという問題がある。

#### 【0015】

##### 【発明が解決しようとする課題】

上述の如く、従来の高耐圧ダイオードは、高耐圧化を図るために、n型カソード層（半導体基板）を厚くする必要があった。しかしながら、n型カソード層が厚くなると、順方向電圧降下、逆回復損失等の素子特性が劣化するという問題があった。

#### 【0016】

本発明の第1の目的は、素子特性の劣化を招かずに、必要な耐圧を確保できる高耐圧電力用半導体装置を提供することにある。

#### 【0017】

また、従来の電力用半導体装置では、スイッチング素子に還流ダイオードを外付けで逆並列接続するために高電流密度化が難しく、接続配線のために高速化が困難であるという問題がある。

#### 【0018】

本発明の第2の目的は、従来よりも構成が簡素で小型化と高性能化が図れる電力用半導体装置を提供することにある。

#### 【0019】

また、従来の電力用半導体装置では、オン電圧をビルトイン電圧以下には低減し得ないという問題がある。

10

20

30

40

50

**【0020】**

本発明の第3の目的は、通電時に零電圧から電流が立上ると共に、低電流領域から高電流領域に亘ってオン抵抗が小さい電力用半導体装置を提供することにある。

**【0021】****【課題を解決するための手段】**

上記目的を達成するために、本発明の高耐圧電力用半導体装置は、第1と第2の主面を有し、前記第1および第2の主面のいずれかに少なくとも一つの段差により形成された凹部を有する高抵抗の第1導電型の半導体基板と、前記半導体基板の前記凹部が形成された領域に少なくともその1部が形成された、低不純物濃度の第2導電型リサーフからなる電界緩和構造と、前記半導体基板の前記凹部が形成された前記第1および第2の主面のいずれかの側に形成され、前記リサーフより高不純物濃度の第2導電型アノード層を有する電力用ダイオードとを具備し、前記電力用ダイオードの前記アノード層が形成された前記半導体基板の高抵抗部分の厚さが、前記電界緩和構造下の前記半導体基板の高抵抗部分の厚さよりも小さく、前記リサーフは前記半導体基板の前記第1の主面または第2の主面に形成された前記凹部を取り囲み前記電力用ダイオードの前記アノード層に接していることを特徴とする。

**【0023】**

前記電力用ダイオードの前記アノード層が、前記第1導電型の半導体基板との界面に複数の段差を有することを特徴とする。

**【0028】**

したがって、電界緩和構造の効率を高めるために半導体基板を厚くしても、高耐圧半導体素子の順方向電圧降下、逆回復損失等の素子特性の劣化を招かずに済む。

**【0029】**

また、半導体ウェハが大口径化するにつれ、強度の観点から半導体基板を厚くせざるを得ない場合でも、高耐半導体素子の厚さは凹部の深さに対応した薄いものとすることができる。これにより、素子特性の劣化を招かずに、半導体基板の厚さを任意に設定することができ、必要な耐圧を確保できる高耐圧半導体装置を実現できるようになる。

**【0030】**

また、本発明によれば、半導体基板との界面に複数の段差を有する電界緩和構が用いられているので、段差がない従来の電界緩和構造が用いられた場合に比べて、電界が集中する箇所が増し、電界を積分して得られる耐圧が高くなる。これにより、従来の電界緩和構造に比べて、耐圧の高い高耐圧半導体装置を実現できるようになる。

**【0031】**

また、本発明では、高抵抗の第1導電型の半導体基板として、第1の主面（表面）と第2の主面（裏面）に凹部が形成されたものを用いてもよい。そして、高耐圧半導体素子が表面と裏面の凹部との間に部分に形成されている。このため、半導体基板が厚くても、高耐圧半導体素子の厚さは凹部の深さに対応した薄いものとなる。

**【0032】**

表面に段差を設ける場合には、微細パターン形成プロセスによる制約で段差をあまり大きくできないのに対し、裏面に段差を設ける場合には、このような制約がなく、広範囲で半導体基板の厚さを設定することができる。これにより、素子特性の劣化を招かずに、半導体基板の厚さを広範囲で任意に設定することができ、必要な耐圧を確保できる高耐圧半導体装置を実現できるようになる。

**【0046】****【発明の実施の形態】**

以下、図面を参照しながら本発明の実施の形態を説明する。まず、本発明の第1の態様の実施形態（第1乃至第15の実施形態）を説明する。これらの実施形態では、第1導電型がn型の場合を説明するが、n型に代えてp型とすることも可能である。また、上記の実施形態を通じて、同一箇所には、同一番号を付して、重複する説明を省略する。

**【0047】**

10

20

30

40

50

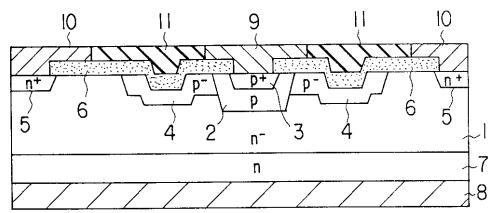

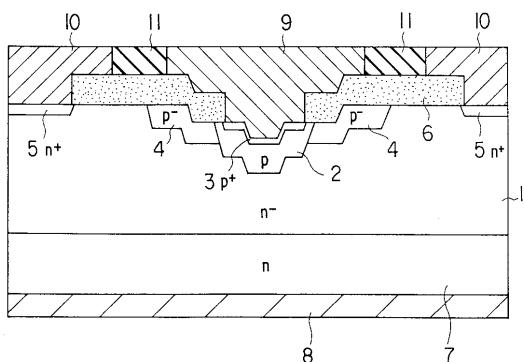

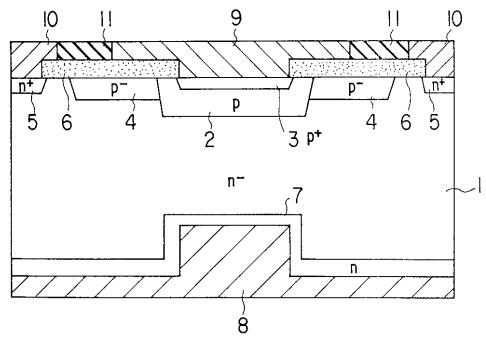

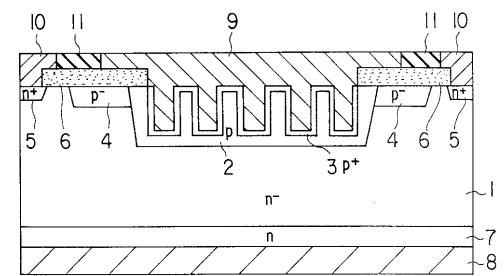

(第1の実施形態)

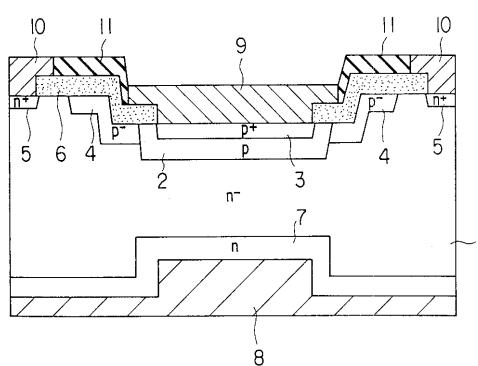

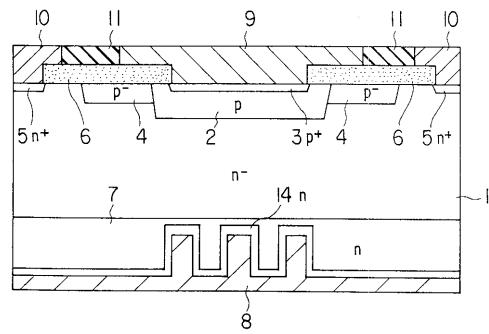

図1は、本発明の第1の実施形態に係る高耐圧半導体装置の要部を示す断面図である。本実施形態では、高耐圧半導体素子として高耐圧ダイオードを用いている。

【0048】

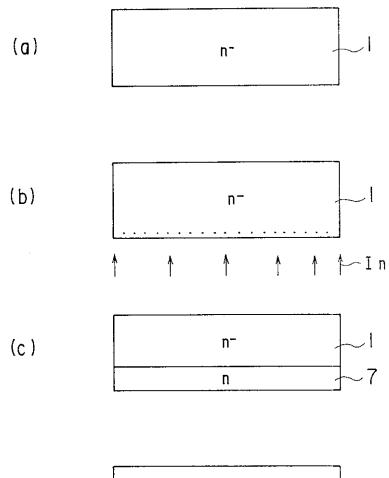

図1において、1は高抵抗の第1のn型カソード層(半導体基板)を示しており、このn型カソード層1の表面には、凹部が形成されている。この凹部の底部の表面には、第1のp型アノード層2が選択的に形成されている。この第1のp型アノード層2の表面には、高不純物濃度の第2のp型アノード層3が選択的に形成されている。

【0049】

また、n型カソード層1の表面には、電界緩和構造(接合終端構造)である低不純物濃度のp型リサーフ層4が第1のp型アノード層2に接してその周囲に形成されている。この場合、p型リサーフ層4は、n型カソード層1の凹部の底部および側面部からその外側の基板表面にかけて形成されている。

10

【0050】

さらに、n型カソード層1の表面には、接合終端構造である高不純物濃度のn型チャネルトップ層5がp型リサーフ層4から所定距離離れてその外側に形成されている。

【0051】

また、第2のp型アノード層3の縁から第1のp型アノード層2、p型リサーフ層4、n型カソード層1、n型チャネルトップ層5にまたがる領域上にはS I P O S(semi-insulating polycrystalline silicon)膜等の高抵抗膜6が設けられている。なお、高抵抗膜6の代わりに、絶縁膜を設けても良い。

20

【0052】

一方、第1のn型カソード層1の裏面には、それよりも高不純物濃度の第2のn型カソード層7が形成されている。このn型カソード層7にはカソード電極8が設けられている。また、第2のp型アノード層3にはアノード電極9、そしてn型チャネルトップ層5には電極10が設けられている。電極10は耐圧を安定させるために必要な予備電極であるが、これをカソード電極としてアノード電極9との間に横型ダイオード構造を構成することも可能である。なお、11は絶縁膜である。

【0053】

本実施形態では、n型カソード層1の表面に凹部が形成され、この凹部の厚さの薄い領域にダイオードが形成されている。すなわち、本実施形態では、n型カソード層1(半導体基板)が厚くても、ダイオードとして動作する部分の厚さは凹部の深さに対応した薄いものとなる。したがって、n型カソード層1を厚くしても、順方向電圧降下、逆回復損失等の素子特性の劣化を招かずには済む。

30

【0054】

また、本実施形態によれば、以下の理由によっても、上記の特徴が得られる。

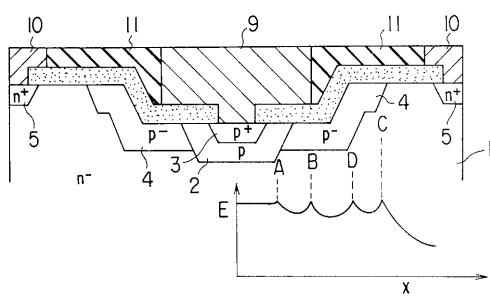

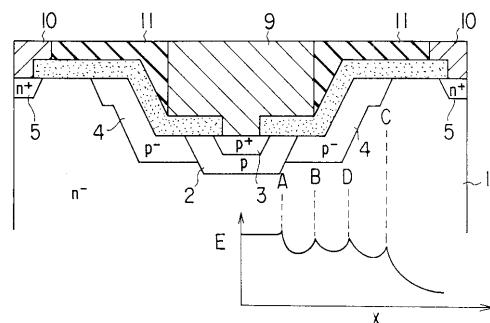

本実施形態の素子を従来構造のそれと比較する。まず、従来の場合、図2に示すように、p型リサーフ層4が形成される領域には段差がなく、電界が集中する箇所は図中A、B、Cで示した3つの箇所である。それぞれの箇所の電界強度を図2の下部に示す。従来は耐圧を高くするためには、基板厚を大きくする必要があり、このため定常オン損失、ターンオン損失が大きくなっていた。

40

【0055】

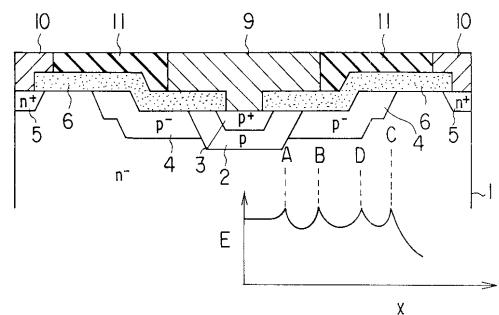

一方、本実施形態の場合、p型リサーフ層4が形成される領域に段差があり、図3に示すように、電界が集中する箇所はA、B、C、Dで示した4つの箇所である。すなわち、本実施形態では段差があるので、電界が集中する箇所が1つ増える。

【0056】

したがって、本実施形態によれば、従来に比べて、電界を積分して得られる耐圧が高くなるので、半導体基板の厚さが同じでもより高耐圧の半導体素子を実現することができる。

【0057】

なお、p型リサーフ層4を設けず、凹部の厚さの薄い領域に素子を形成することだけでも

50

、順方向電圧降下、逆回復損失等の素子特性の劣化を防止することは可能である。また、p型リサーフ層4が形成されている領域に、2個、3個と段差がある場合には更に高耐圧の半導体素子を実現することが可能である。

【0058】

次に凹部の深さと電界分布との関係について説明する。

【0059】

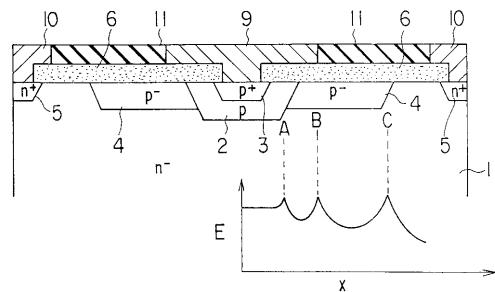

図4に、凹部の深さが浅い場合の電界分布を示す。この深さでは、半導体素子の内の主素子部分(A-A'間の領域)はp型リサーフ層4に比べて電界が低く余裕があるので、ブレークダウンはp型リサーフ層4で起こる。したがって、凹部をもっと深い領域まで形成し、通電損失とターンオフ損失を小さくしても耐圧は落ちることはない。

10

【0060】

図5に、凹部の深さが中間の場合の電界分布を示す。この深さでは、主素子の電界とp型リサーフ層4のそれとが同じ大きさであるため、ブレークダウンは素子とp型リサーフ層4とで同時に起こる。

【0061】

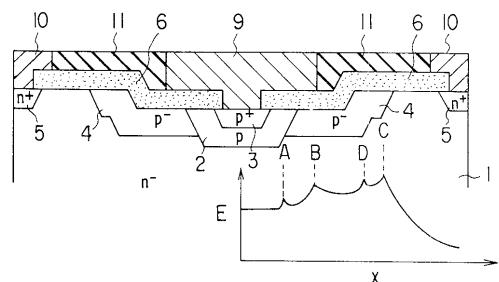

図6に、凹部の深さが深い場合の電界分布を示す。この深さでは、主素子はp型リサーフ層4に比べて電界が大きいので、ブレークダウンは主素子で起こる。すなわち、全体の耐圧は主素子耐圧(主素子設計)のみで決まり、p型リサーフ層4等の電界緩和構造にはよらない。この場合、図5の場合に比べて、耐圧の絶対値は低下するが、同時に順方向電圧降下、逆回復損失が減少し、損失特性が格別に優れた半導体素子を得ることができる。また、ブレークダウンが半導体表面から離れたA点で起こるので、表面の影響を受けにくく耐圧の安定した半導体素子を実現することができる。

20

【0062】

高耐圧素子としては、図5、図6のように設計することが望ましい。本発明によれば、電流通過部の基板厚を薄く、電界緩和構造(リサーフ層等)の基板厚を厚くすることにより、定常オン損失、ターンオン損失を小さくすることができ、平坦接合並みの耐圧を得ることが可能である。

【0063】

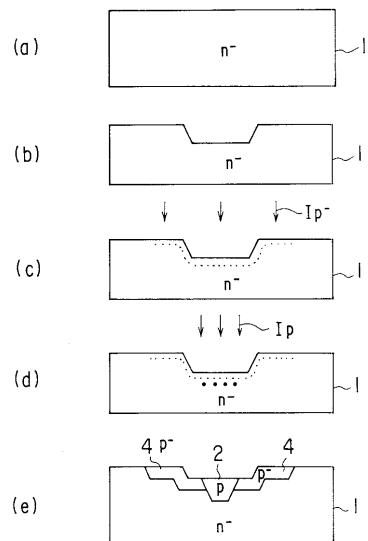

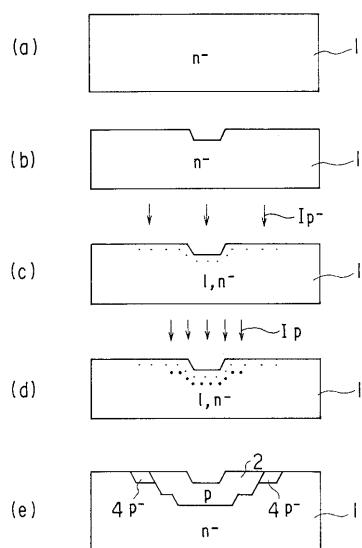

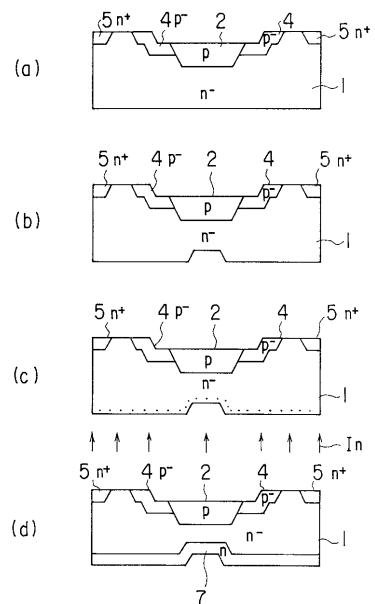

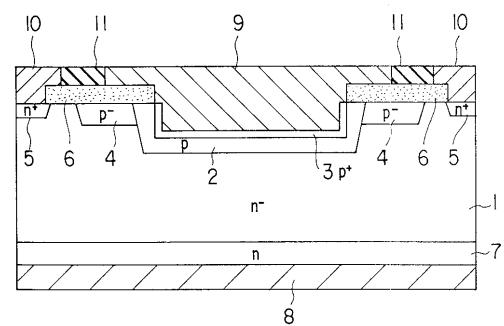

図7に、凹部の素子構造の形成方法を示す。

【0064】

30

まず、図7(a)に示すようにn型ベース層1(半導体基板)が用意され、次に図7(b)に示すように、n型ベース層1の表面に凹部が形成される。

【0065】

次に図7(c)に示すように、凹部およびその周囲のn型ベース層1の表面にp型不純物イオンIp-が図示しないマスクを用いて選択的に注入される。

【0066】

次に図7(d)に示すように、凹部底部のn型ベース層1の表面にp型不純物イオンIpが図示しないマスクを用いて選択的に注入される。この場合、p型不純物イオンIpのドーズ量は、p型不純物イオンIp-のそれよりも多くされる。

40

【0067】

最後に、図7(e)に示すように、アニールを行なうことによって、p型アノード層2、p型リサーフ層4が完成する。

【0068】

なお、この例では、p型アノード層3を省略したが、p型アノード層3を形成する場合には、例えば、図7(d)の工程の後に、p型不純物イオンIp-の注入領域の表面に、さらに高不純物濃度のp型不純物イオンを選択的に注入すれば良い。

【0069】

図8、図9に、本実施形態の変形例を示す。図8の素子では、凹部の段差が2段になっている。また、図9の素子では、凹部の段差が3段になっている。このように段差を多くすることにより、電界緩和構造の屈曲部の曲率半径が大きくなり、耐圧が向上する。これに

50

より、薄い基板厚の素子を容易に作製することができる。なお、凹部の段差は4段以上であっても良い。

【0070】

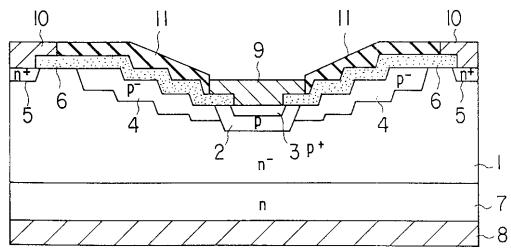

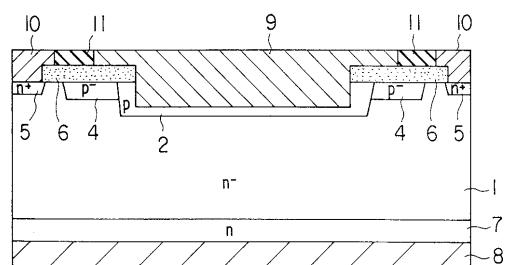

(第2の実施形態)

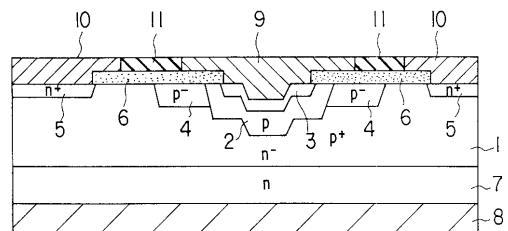

図10は、本発明の第2の実施形態に係る高耐圧半導体装置の要部を示す断面図である。

【0071】

本実施例が第1の実施例と異なる点は、半導体素子の内p型リサーフ層4を形成する領域のみに凹部を形成したことにある。p型リサーフ層4はn型カソード層1の凹部の底部および側面部からその外側の表面にかけて形成され、その結果、p型のリサーフ層4とn型カソード層1との界面に2段の段差が形成されている。したがって、本実施形態によれば、電界緩和構造における屈曲部の曲率半径が大きくなり、電界を積分して得られる耐圧が高くなる。

【0072】

(第3の実施形態)

図11は、本発明の第3の実施形態に係る高耐圧半導体装置の要部を示す断面図である。

【0073】

本実施形態が第2の実施形態と異なる点は、p型リサーフ層4の外周部が凹部の底部を越えないように形成したことにある。この場合も、電界を積分して得られる耐圧が高くなるので、第2の実施形態と同様な効果が得られる。

【0074】

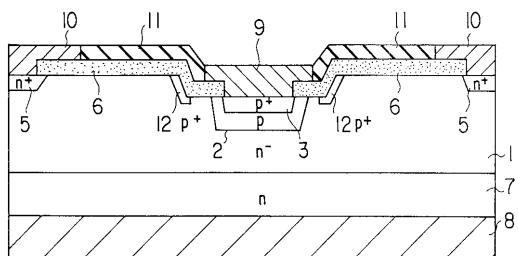

(第4の実施形態)

図12は、本発明の第4の実施形態に係る高耐圧半導体装置の要部を示す断面図である。

【0075】

本実施形態が第1の実施形態と異なる点は、電界緩和構造(接合終端構造)として、p型リサーフ層4の代わりに高不純物濃度のp型ガードリング層12を用いたことにある。なお、p型ガードリング層12は凹部以外の領域に形成しても良い。

【0076】

本実施形態でも、n型カソード層1(半導体基板)が厚くても、素子の厚さは凹部の深さに対応した薄いものとなる。したがって、必要な耐圧を確保するために、p型ガードリング層12を設けるとともに、n型カソード層1を厚くしても、順方向電圧降下、逆回復損失等の素子特性の劣化を招かずに済む。

【0077】

(第5の実施形態)

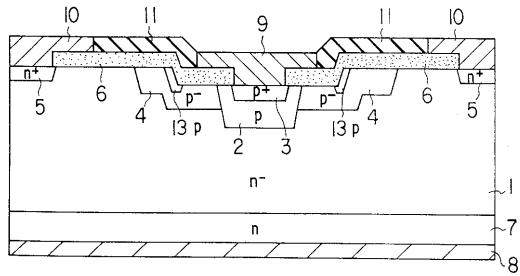

図13は、本発明の第5の実施形態に係る高耐圧半導体装置の要部を示す断面図である。

【0078】

本実施形態が第1の実施形態と異なる点は、p型リサーフ層4の表面に、凹部の段差部に接するように、高不純物濃度の第2のp型リサーフ層13を選択的に形成したことにある。第2のp型リサーフ層13は、基板段差部表面の不安定箇所を覆って安定化している。

【0079】

本実施形態でも第1の実施形態と同様な効果が得られるが、第2のp型リサーフ層13を設けた分その効果が安定して得られる。

【0080】

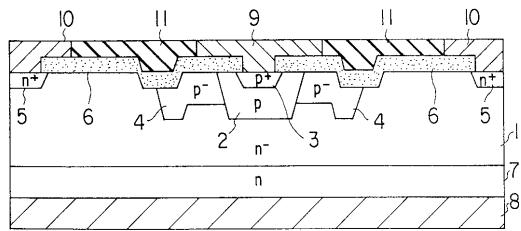

(第6の実施形態)

図14は、本発明の第6の実施形態に係る高耐圧半導体装置の要部を示す断面図である。

【0081】

本実施形態が第1の実施形態と異なる点は、p型リサーフ層4の形成領域に凹部の段差が存在せず、凹部の段差が主素子領域のみに存在することにある。その結果、p型アノード層2,3に段差が形成されている。

【0082】

本実施形態でも、n型カソード層1(半導体基板)が厚くても、主素子の厚さは凹部の深

10

20

30

40

50

さに対応した薄いものとなる。したがって、必要な耐圧を確保するために、p型リサーフ層4を設けるとともに、n型カソード層1を厚くしても、順方向電圧降下、逆回復損失等の素子特性の劣化を招かずに済む。

【0083】

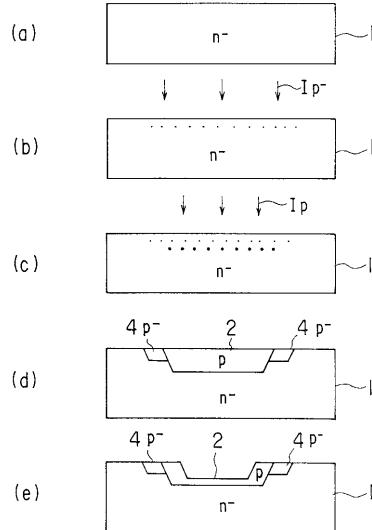

図15に、凹部の素子構造の形成方法を示す。

まず、図15(a)に示すようにn型ベース層1(半導体基板)が用意され、次に図15(b)に示すように、n型ベース層1の表面に凹部が形成される。

【0084】

次に図15(c)に示すように、凹部およびその周囲のn型ベース層1の表面にp型不純物イオンIp-が図示しないマスクを用いて選択的に注入される。

10

【0085】

次に図15(d)に示すように、凹部およびその周囲(ただし、p型不純物イオンIp-の注入領域よりも内側)のn型ベース層1の表面にp型不純物イオンIpが図示しないマスクを用いて選択的に注入される。この場合、p型不純物イオンIpのドーズ量は、p型不純物イオンIp-のそれよりも多くする。

【0086】

最後に、図15(e)に示すように、アニールを行なうことによって、p型アノード層2、p型リサーフ層4が完成する。

【0087】

なお、この例では、p型アノード層3を省略したが、p型アノード層3を形成する場合には、例えば、図15(d)の工程の後に、凹部およびその周囲(ただし、p型不純物イオンIpの注入領域よりも内側)の表面に、さらに高不純物濃度のp型不純物イオンを選択的に注入すれば良い。

20

【0088】

図16に、本実施形態の変形例を示す。この素子では、素子領域に段差が1つの凹部が2つ形成されている。ウェハ強度やエッチング加工での形状制御などプロセス上の制約から、凹部を形成する領域の寸法が制限されている場合に有効である。なお、凹部の数は3つ以上でも良い。

【0089】

(第7の実施形態)

30

図17は、本発明の第7の実施形態に係る高耐圧半導体装置を示す断面図である。本実施形態が第1の実施形態と異なる点は、凹部(第1の凹部)の底部にさらに第2の凹部が設けられ、この第2の凹部を含む第1の凹部の底部にp型アノード層2,3が形成されていることがある。本実施形態でも、第1の実施形態と同様な効果が得られる。

【0090】

(第8の実施形態)

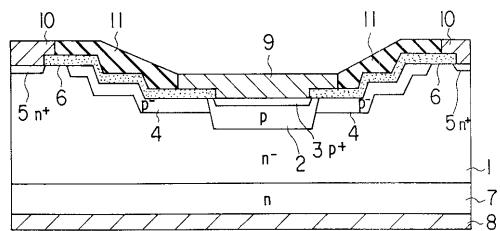

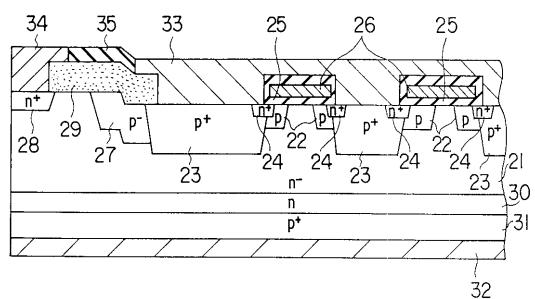

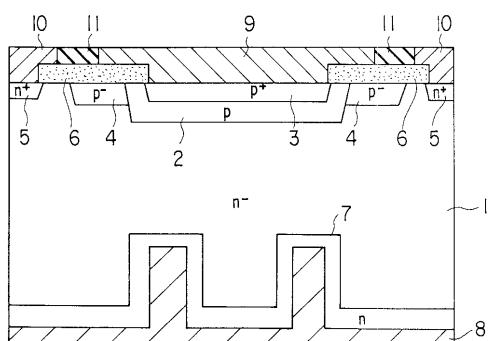

図18は、本発明の第8の実施形態に係る高耐圧半導体装置の要部を示す断面図である。本実施形態では、高耐圧半導体素子としてIGBTを用いている。

【0091】

図18において、21は高抵抗のn型ベース層を示しており、このn型ベース層21の表面には凹部が形成されており、この凹部の底部表面には第1のp型ベース層22が選択的に形成されている。この第1のp型ベース層22が形成された領域にはそれを貫通する深さの高不純物濃度の第2のp型ベース層23が選択的に形成されている。

40

【0092】

p型ベース層22,23の表面には高不純物濃度のn型ソース層24が選択的に形成されており、このn型ソース層24とn型ベース層21とで挟まれた領域のp型ベース層22上にはゲート絶縁膜25を介してゲート電極26が配設されている。

【0093】

また、n型ベース層21の表面には、電界緩和構造(接合終端構造)である低不純物濃度のp型リサーフ層27がp型ベース層23に接してその周囲に形成されている。この場合

50

、p型リサーフ層27は、n型ベース層21の凹部の底部および側面部からその外側の表面にかけて形成されている。なお、ここでのp型ベース層23は、凹部に形成された半導体装置のうち最も外側のものである。

【0094】

さらに、n型ベース層21の表面には、接合終端構造である高不純物濃度のn型チャネルストップ層28がp型リサーフ層27から所定距離離れてその外側に形成されている。また、第2のp型ベース層23の縁からp型リサーフ層27、n型ベース層21、n型チャネルストップ層28にまたがる領域上には、S I P O S膜等の高抵抗膜29が設けられている。なお、高抵抗膜29の代わりに、絶縁膜を設けても良い。

【0095】

一方、高抵抗の第1のn型ベース層21の裏面には、それよりも高不純物濃度の第2のn型ベース層30が形成されており、このn型ベース層30の表面には高不純物濃度のp型ドレイン層31が形成されている。このp型ドレイン層31にはドレイン電極32が設けられている。また、n型ソース層24にはソース電極33が設けられている。このソース電極33はp型ベース層23にもコンタクトしている。そして、n型チャネルストップ層28には電極34が設けられている。なお、35は絶縁膜を示している。

【0096】

本実施形態では、n型ベース層21の表面に凹部が形成され、この凹部の厚さの薄い領域にIGBTが形成されている。すなわち、n型ベース層21（半導体基板）が厚くても、IGBTの厚さは凹部の深さに対応した薄いものとなる。

【0097】

したがって、必要な耐圧を確保するため、p型リサーフ層27を設けるとともに、n型ベース層21を厚くしても、順方向電圧降下、ターンオフ特性等の素子特性の劣化を招かずに済む。

【0098】

また、本実施形態によれば、以下の理由によっても、上記の効果を得ることができる。すなわち、本実施形態の場合、p型リサーフ層27が形成される領域に段差があり、電界が集中する箇所が従来よりも増える。したがって、電界を積分して得られる耐圧が高くなる。

【0099】

なお、凹部の厚さの薄い領域に素子を形成すること単独でも、あるいはn型ベース層21との界面に複数の段差を有するp型リサーフ層27を形成すること単独でも、上記の効果を得ることが可能である。

【0100】

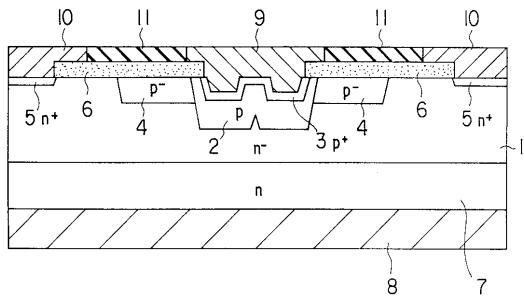

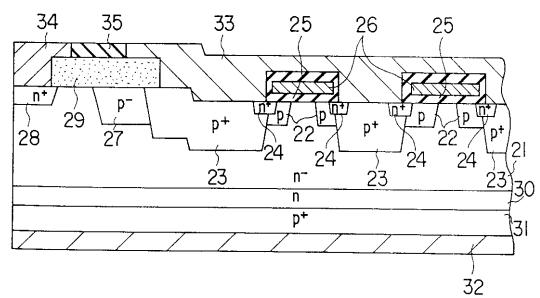

（第9の実施形態）

図19は、本発明の第9の実施形態に係る高耐圧半導体装置の要部を示す断面図である。本実施形態が第8の実施形態と異なる点は、p型リサーフ層27の形成領域に凹部の段差が存在せず、凹部の段差が主素子領域のみに存在することにある。

【0101】

本実施形態でも、n型ベース層21（半導体基板）が厚くても、主素子の厚さは凹部の深さに対応した薄いものとなる。したがって、必要な耐圧を確保するため、p型リサーフ層27を設けるとともに、n型ベース層21を厚くしても、順方向電圧降下、ターンオフ特性等の素子特性の劣化を招かずに済む。

【0102】

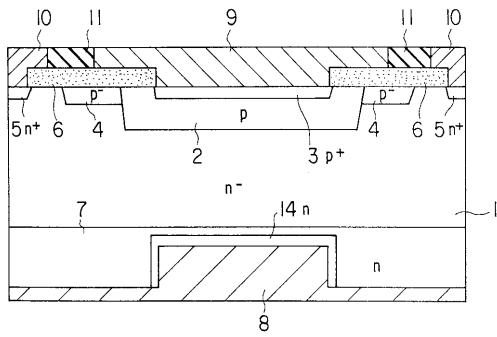

（第10の実施形態）

図20は、本発明の第10の実施形態に係る高耐圧半導体装置の要部を示す断面図である。本実施形態が第1の実施形態と異なる点は、凹部をn型カソード層1の裏面（アノード側の正面と反対側の面）に形成し、かつ凹部がp型アノード層2,3と対向するように形成したことがある。

【0103】

10

20

30

40

50

本実施形態によれば、n型カソード層1(半導体基板)が厚くても、主素子の厚さは裏面の凹部の深さに対応した薄いものとなる。したがって、必要な耐圧を確保するために、p型リサーフ層4を設けるとともに、n型カソード層1を厚くしても、順方向電圧降下、逆回復損失等の素子特性の劣化を招かずに済む。

【0104】

図21に、本実施形態の変形例を示す。この素子では、p型アノード層2,3と対向する領域のn型カソード層1の裏面に、段差が1つの凹部が2つ形成されている。ウェハ強度やエッチング加工での形状制約などプロセス上の制約から凹部を形成する場合の寸法が制限されている場合に有効である。

【0105】

(第11の実施形態)

図22は、本発明の第11の実施形態に係る高耐圧半導体装置の要部を示す断面図である。本実施形態の素子は、第10の実施形態と第1の実施形態とを組み合わせた例である。すなわち、図1の素子において、そのn型ベース層1の裏面に、アノード層2,3と対向するように凹部が設けられている。本実施形態でも第1、第10の実施形態と同様な効果が得られる。

【0106】

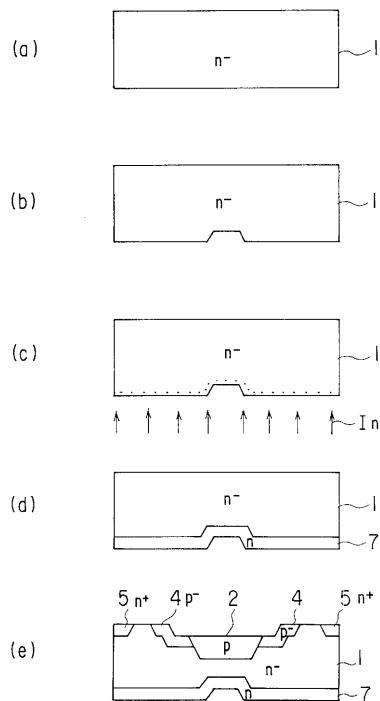

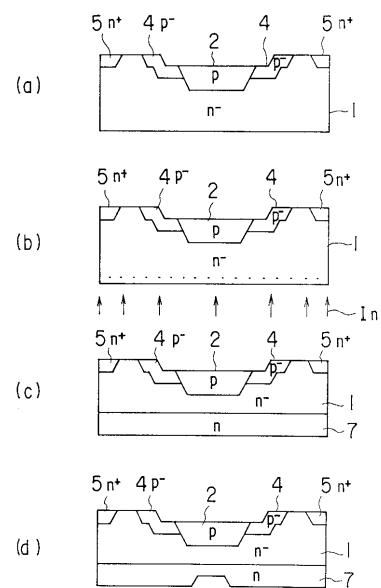

図23に、素子の基本構造の形成方法を示す。

まず、図23(a)に示すように、第1の実施形態で説明した方法に従って、表面(主接合側)に素子構造が形成される。

10

【0107】

次に図23(b)に示すように、n型ベース層1の裏面に凹部を形成した後、図23(c)に示すように、裏面全面にn型不純物イオンInが注入される。

【0108】

最後に、図23(d)に示すように、アニールを行なうことによって、n型カソード層7を形成して、素子の基本構造が完成する。

【0109】

図24に、他の形成方法を示す。図23に示した方法は、n型ベース層の表面に素子構造を形成した後に、その裏面に素子構造(n型カソード層7)を形成する方法であるが、図24に示す方法ではその形成順序が逆になっている。

30

【0110】

すなわち、まず、図24(a), (b)に示すように、n型ベース層1(半導体基板)が用意され、その裏面に凹部が形成される。

【0111】

次に図24(c), (d)に示すように、裏面全面にn型不純物イオンInを注入した後、アニールを行なうことによって、n型カソード層7が形成される。

【0112】

最後に、図24(e)に示すように、第1の実施形態で説明した方法に従って、表面(主接合側)に素子構造が形成される。

【0113】

図25、図26にそれぞれさらに別の形成方法を示す。図25の形成方法は、図23の形成方法とは逆に、裏面全面にn型不純物イオンInが注入され、n型カソード層7が形成された後に凹部が形成されるものである。同様に、図26の形成方法は、図24の形成方法とは逆に、裏面全面にn型不純物イオンInが注入され、n型カソード層7が形成された後に凹部が形成されるものである。

40

【0114】

図25、図26の形成方法によれば、素子領域のn型カソード層7の表面濃度を下げることができるので、ダイオードの逆回復時のテール電流が低減され、逆回復損失の小さなダイオードを実現することができる。

【0115】

50

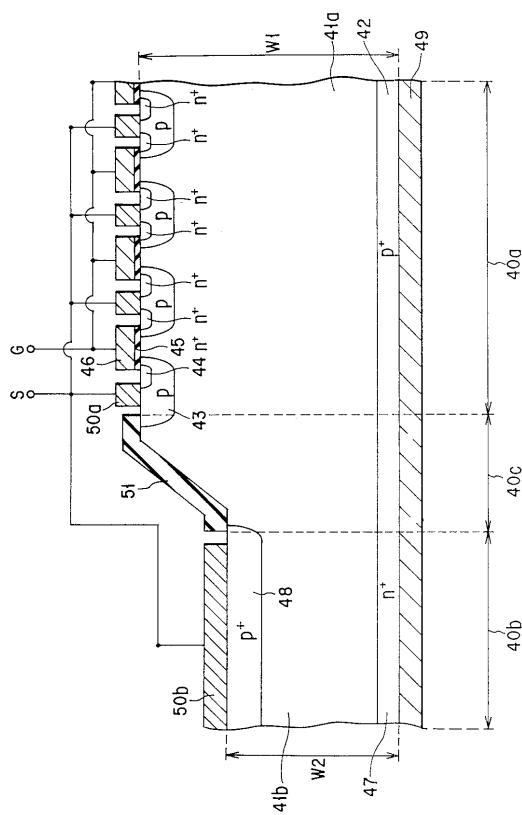

## (第12の実施形態)

図27は、本発明の第12の実施形態に係る高耐圧半導体装置の要部を示す断面図である。本実施形態が第6の実施形態と異なる点は、凹部の素子構造の形成方法にある。すなわち、本実施形態では、凹部の素子構造の形成方法で、p型アノード層2を形成した後に凹部を形成している点が異なっている。

## 【0116】

図28に、凹部の素子構造の形成方法を示す。まず、図28(a)、(b)に示すように、n型ベース層1(半導体基板)が用意され、その表面の一部にp型不純物イオンIp-が注入される。

## 【0117】

次に図28(c)に示すように、p型不純物イオンIp-が注入された領域の一部にp型不純物イオンIpが注入される。この場合、p型不純物イオンIpのドーズ量は、p型不純物イオンIp-のそれよりも多くされる。

## 【0118】

次に図28(d)に示すように、アニールを行なうことによって、p型アノード層2、p型リサーフ層4が形成される。

## 【0119】

最後に、図28(e)に示すように、p型アノード層2の表面がエッチングされ、凹部が形成されて、凹部領域の基本構造が完成する。

## 【0120】

なお、この例では、p型アノード層3を省略したが、p型アノード層3を形成する場合には、例えば、図28(e)の工程の後に、p型不純物イオンIpの注入領域の表面に、さらに高不純物濃度のp型不純物イオンを選択的に注入すれば良い。

## 【0121】

図29に、本実施形態の変形例を示す。この素子では段差が1つの凹部が5つ形成されている。なお、段差の数はこれに限定されるものではない。このようにしても主素子領域のベース厚を実質的に薄くすることができるので、同様な効果を得ることができる。

## 【0122】

## (第13の実施形態)

図30は、本発明の第13の実施形態に係る高耐圧半導体装置の要部を示す断面図である。

## 【0123】

本実施形態が第12の実施形態と異なる点は、高不純物濃度のp型アノード層3が無いことにある。これによってp型アノード層2の表面濃度を下げる所以である。これによってp型アノード層2の表面濃度を下げるので、ダイオードの逆回復時の最大逆方向電流が低減され、逆回復損失の小さなダイオードを実現することができる。ただし、本実施形態では、第6の実施形態よりもp型アノード層2の面積は広くしてある。これにより、順方向電圧V<sub>F</sub>を低く保つことができる。

## 【0124】

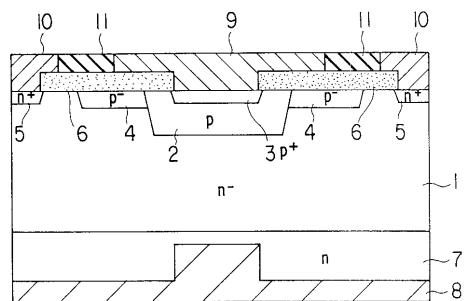

## (第14の実施形態)

図31は、本発明の第14の実施形態に係る高耐圧半導体装置の要部を示す断面図である。

## 【0125】

本実施例の特徴は、n型カソード層7に図20の素子の特徴に加えて、裏面の凹部の底部および側壁部に接するところのn型カソード層4の表面に、高不純物濃度のn型カソード層14を形成したことにある。これにより、電子の注入効率がより高くなり、特に順方向電圧降下を低くした場合に有効である。

## 【0126】

図31に、本実施形態の変形例を示す。この素子では、裏面に段差が1つの凹部を3つ形成したことにある。なお、凹部の数は2つでも4つ以上でも良い。

## 【0127】

10

20

30

40

50

## (第15の実施形態)

図33は、本発明の第15の実施形態に係る高耐圧半導体装置の要部を示す断面図である。本実施形態の特徴は、第14の実施形態の高耐圧半導体装置において、高不純物濃度のn型カソード層14を省き、素子構造を簡略したことがある。

## 【0128】

次に、本発明の第2の態様の実施形態(第16乃至第21の実施形態)を説明する。なお、上記の実施形態では第1導電型層としてn型、第2導電型層としてp型を用いているが、導電型を逆にしてもよい。また、同一箇所には、同一番号を付して、重複する説明を省略する。

## 【0129】

10

## (第16の実施形態)

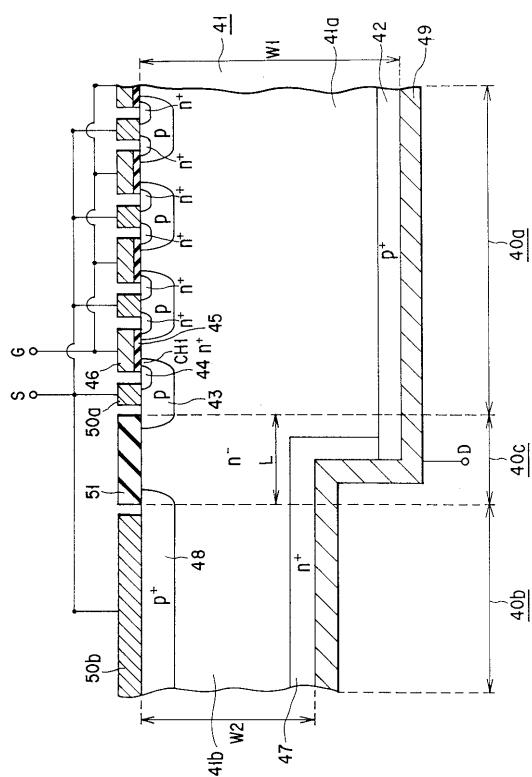

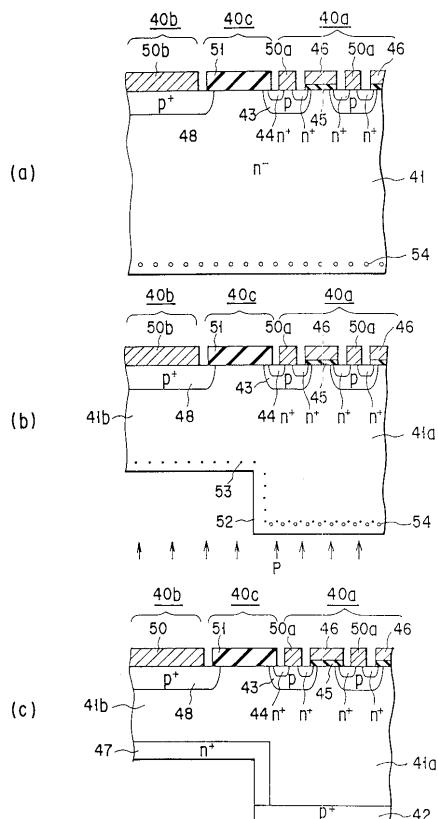

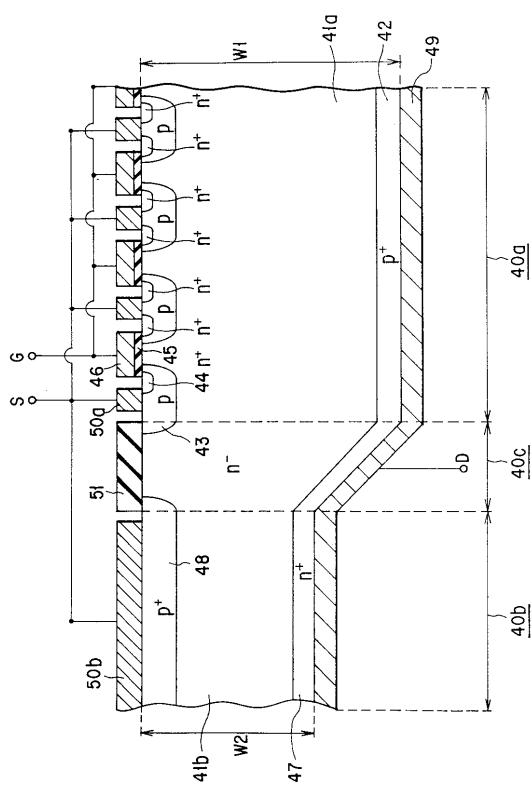

図34は、本発明の第16の実施形態に係る電力用半導体装置の断面図を示す。図34において、41は高抵抗のn型ベース層(半導体基板)を示しており、このn型ベース層41の一方の面(裏面)には、選択的に凹部が形成されている。

## 【0130】

n型ベース層41の凹部が形成されていない領域40aの裏面には、p型ドレイン層42が形成されており、他方の面(表面)には、p型ベース層43が選択的に形成されている。p型ベース層43内にはn型ソース層44が形成されている。n型ベース層41とn型ソース層44との間のp型ベース層43上には、ゲート絶縁膜45を介してゲート電極46が形成されている。なお、これらゲート電極46、ゲート絶縁膜45、p型ベース層43、n型ベース層41及びn型ソース層44により、CH1をチャネル領域とする電子注入用MOSFETが構成されている。

20

## 【0131】

一方、n型ベース層41の凹部の底面(裏面)と側壁には、n型カソード層47が形成されている。また、n型ベース層41の他方の面(表面)で凹部と対向する領域には、p型アノード層48が形成されている。

## 【0132】

30

さらに、p型ドレイン層42上及びn型カソード層47上には、両層42, 47に接してドレイン電極(第2の主電極)49が形成されている。また、n型ソース層44、p型ベース層43上には、両層に接してソース電極50aが形成されている。p型アノード層48上にはソース電極(アノード電極)50bが形成されている。電極50aと電極50bにより、第1の主電極が構成され、ゲート電極46が副電極となる。なお、複数のソース電極、複数のゲート電極は、それぞれ相互に接続されており、図中では結線で模式的に表されている。

## 【0133】

上記の構成により、凹部が形成された領域40bにはダイオードが構成され、凹部が形成されない領域40aにはIGBTが構成されている。

## 【0134】

40

IGBT領域40aとダイオード領域40bの間で、絶縁膜51の下の領域40cは、IGBTとダイオードの分離領域である。この領域の幅Lは、キャリアの拡散長Ld以上とするのが望ましい。すなわち、キャリアのライフタイムを、拡散係数をDとしたとき、次の関係が満足されるようにする。

## 【0135】

$$L > L_d = (D)^{1/2}$$

あるいは、分離領域40cに、後述のライフタイムキラーを含ませてもよい。

## 【0136】

次に、このような半導体装置の動作を説明する。ドレイン電極49に正電圧、ソース電極50aに負電圧が印加されている時、ソースよりも正となる正電圧をゲート電極46に印加すると、p型ベース層43のゲート電極46に接した表面がn型に反転し、電子eがn型ソース層44から反転層を介してn型ベース層41aに注入されてp型ドレイン層42

50

に到達する。これに伴い、p型ドレン層42から正孔hがn型ベース層41に注入される。このようにn型ベース層41に電子eと正孔hの両方が注入され、伝導度変調が起こってオン電圧が低減される。

【0137】

一方、ターンオフ動作の際には、ソースに対して負である負電圧が絶縁ゲート46に印加される。これにより、ゲート電極46直下に形成されていた反転層が消失して電子注入が止まる。一方、n型ベース層41a中の正孔hは、その一部がp型ベース層43を介してソース電極50aに排出され、残りの正孔hは、電子eと再結合して消滅する。これにより、半導体装置はターンオフする。

【0138】

上記のような機構により、例えば図56において、インバータのTr1とTr4がオンしている状態(図56の(i)の状態)において、上側アーム素子Tr1がターンオフすると、誘導負荷による逆起電力が発生し、下側アーム素子Tr2のドレン電極(図34の参考番号49)が負に、ソース電極(図34の参考番号50a)が正にバイアスされる。この過程で、下側アーム素子のソース電極50aの電圧が上昇して、p型アノード層48とn型ベース層41bより構成されるpn接合が順バイアスされると、p型アノード層48からn型ベース層41bに正孔hが注入され、同時にn型カソード層47から電子eが注入されて、素子が逆方向にターンオンする。この結果、n型ベース層41bで伝導度変調が起り、ダイオード領域40bが低オン電圧で通電する(図56の(ii)の状態)。

10

【0139】

この場合、ダイオードを構成する高抵抗ベース層(基板)41bの厚さW2はIGBTを構成する高抵抗ベース層(基板)41aの厚さW1よりも薄いので、素子を逆方向に導通させた場合、低いオン電圧で通電することができる。

【0140】

つぎに、再びTr1がターンオンすると、Tr2の極性が反転し、逆回復電流(図56の(iii))が流れ、負荷電流(図56の(i))に重畠される。この現象は、一般にスイッチング素子(IGBT)のターンオン損失を増大させるが、本発明のダイオード部分は低オン抵抗であるため、高速化を図ることができる。

【0141】

なお、分離領域40cは、ダイオードが逆回復する際、IGBT領域に拡散したキャリアにより、IGBTのp型エミッタ42から正孔が逆注入したり、あるいはIGBTのn型ソース44が局所的にラッチアップしたりするのを抑制する。

20

【0142】

以上のように、本発明の電力用半導体装置は、逆並列還流ダイオードの機能が内蔵され、順方向においてスイッチング機能を有し、逆方向において導通特性を有する。すなわち、誘導負荷により逆起電力が発生すると、半導体装置が逆方向にターンオンし、低いオン電圧で通電する。

【0143】

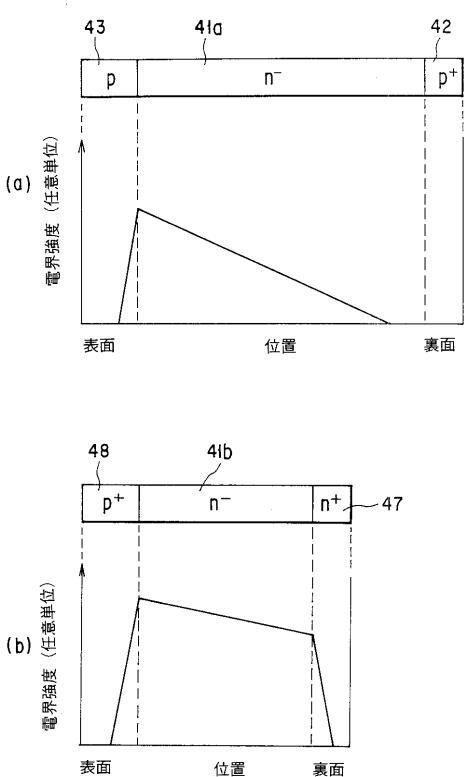

図35は、本発明の電力用半導体装置の原理を説明するための特性図である。図35(a)は、IGBT領域40aの表面から裏面にかけての深さ方向の電界強度を示す。IGBTは、ノンパンチスルーパー型のデバイスであるので、電界強度はn型ベース層41aの中でゼロに達している。一方、図35(b)のダイオードの電界強度は、ダイオードがパンチスルーパー型の構造を有しているので、n型ベース層41bの中では、図35(a)のn型ベース層41aと同じ傾斜でもって、アノード側からカソード側に向けて減少していくが、n型カソード層47の中で急激に減少してゼロとなる。さらに、図35(a)と図35(b)のそれぞれの電界強度の積分値は等しくなる。

30

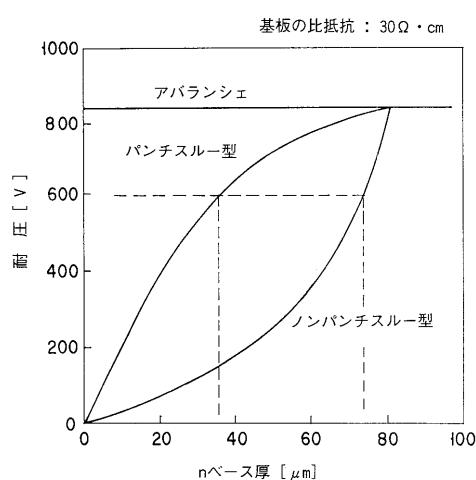

【0144】

図36は、ダイオード(パンチスルーパー型)とIGBT(ノンパンチスルーパー型)のn型ベース層の厚さと耐圧の関係を示したグラフである(基板の比抵抗が30 $\Omega$ ・cm場合)。ダ

40

50

イオードとIGBTが同じ耐圧（例えば600V）であるめには、ダイオードで約35μm、IGBTで約75μmあれば良いことがわかる。もし、ダイオードの厚さをIGBTに合わせて厚く（75μm）作ったとすると、ダイオードの耐圧は600V以上得られるが、オン電圧が過大なダイオードが得られる。このように、本発明ではIGBTとダイオードがそれぞれ最適なn型ベース厚を有する構造を提供している。

#### 【0145】

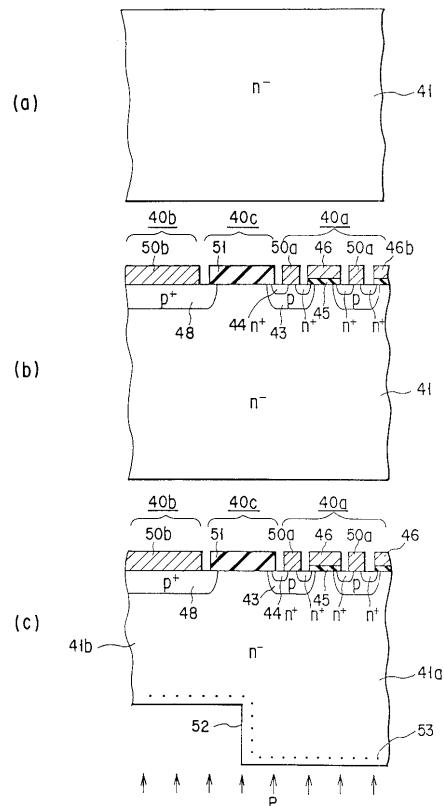

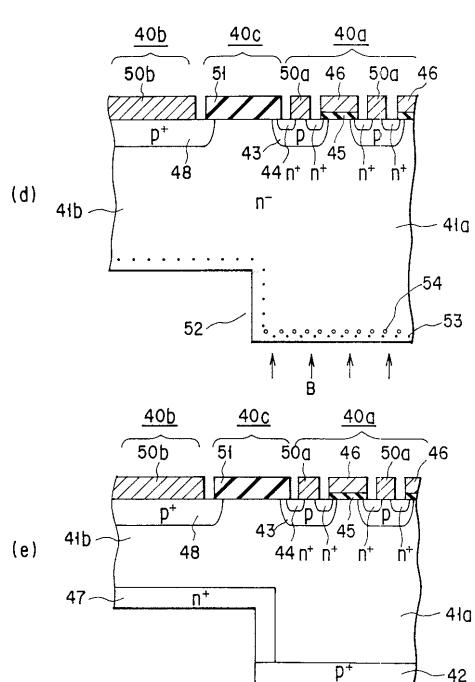

次に、図37を参照して、本発明の電力用半導体装置の製造方法を説明する。

#### 【0146】

まず、図37(a)に示すように、n型ベース層となる半導体基板41を用意する。次に、図37(b)に示すように、n型ベース基板の表面に、IGBTのpベース層となる複数のpウェル43と、ダイオードのp型アノードとなるp型層48を形成する。pウェル43の中には、それぞれn型ソース層43を形成し、隣接するpウェル間に露出するn型ベース基板の表面には、pウェル43、n型ソース層44の上部に延在するように、ゲート絶縁膜45を介してゲート電極46を形成する。同時に、n型ソース層44とpウェル43に接するようにソース電極50aを形成し、p型アノード層48の上にはアノード電極50bを形成する。さらに、IGBT領域40aとダイオード領域40bの間に分離領域40c用の絶縁膜51を形成する。

10

#### 【0147】

次に、図37(c)に示すように、n型ベース基板41裏面のダイオード領域40bに相当する部分をRIEを用いてドライエッチングし、凹部52を形成する。さらに、この凹部を含めてn型ベース基板41の裏面全面に、n型不純物53、例えばリン(P)をイオン注入する。

20

#### 【0148】

次に、図38(d)に示すように、nベース基板41裏面の凹部が形成されていない領域(IGBT領域)41aにp型不純物イオン54、例えばボロン(B)をイオン注入する。この時、p型不純物イオン54のドーズ量は、n型不純物イオン53のそれよりも多くする。例えば、n型不純物イオンとしてリンを $2 \times 10^{15} \text{ cm}^{-2}$ 、p型不純物としてボロンを $5 \times 10^{15} \text{ cm}^{-2}$ のドーズ量で注入する。

#### 【0149】

続いて、アニールを行うことにより、図38(e)に示すように、IGBT領域40aの裏面にp型層42、ダイオード領域40bの裏面にn型層47を形成する。

30

#### 【0150】

なお、IGBT形成領域40aに相当する領域は、電子線やプロトンなどの粒子線を照射する。また、ダイオード領域40b、分離領域40cに相当する領域は、キャリアのライフタイムを減少させるライフタイムキラーとしてAu, Pt, Fe等の重金属を堆積拡散する。

#### 【0151】

上記の図37(c)乃至図38(e)の工程は、図39のように変形して実施してもよい。すなわち、n型ベース基板41の裏面に予めp型イオン54をイオン注入しておき(図39(a))、その後図39(b)に示すように、凹部52を形成する。続いてn型イオン53をn型ベース基板41の裏面全体にイオン注入する。その後アニールを行うことにより、図39(c)に示すようにp型層42とn型層47を形成する。

40

#### 【0152】

以上で、逆並列還流ダイオードの機能が内蔵され、順方向においてスイッチング機能を有し、逆方向において導通特性を有する高電力半導体装置が完成する。

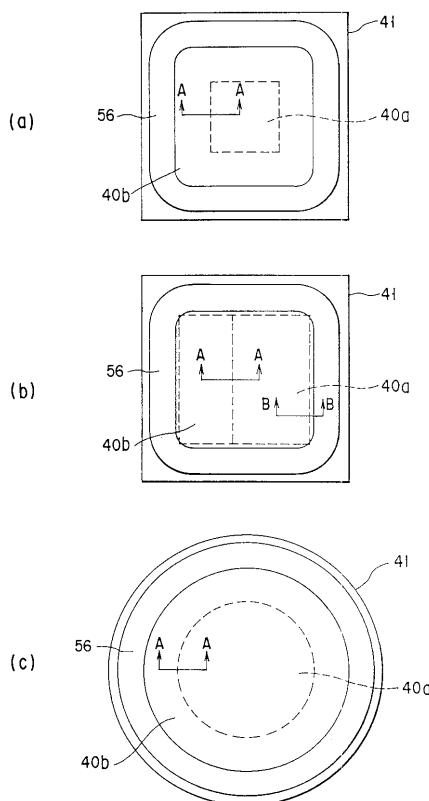

#### 【0153】

図34では、本発明の半導体装置の部分的な断面図のみが示されているが、半導体装置全体としては、図40の平面図に示すような構成とすることができます。図40において、56はリサーフ、ガードリング等が形成される接合終端領域である。図40(a)は角型チップを示し、IGBT領域40aがダイオード領域40bで取り囲まれている。図40(

50

b)も角型チップを示し、IGBT領域40aとダイオード領域40bとが並列に形成されている。図40(c)は、図40(a)の構成を丸型にしたものである。

#### 【0154】

なお、図40(b)において、IGBT領域40aと接合終端領域56とのB-B線に沿った断面は、例えば第1の態様の図18に示したように、IGBT領域の最も外側に接合終端構造が形成される。ダイオード領域40bと接合終端領域56との接続構造にも、第1の態様で述べた種々の構造が適用できる。

#### 【0155】

このように形成された半導体装置は、誘導負荷により逆起電力が発生すると、逆方向にターンオンする。その際、ダイオードは低オン電圧で導通される。よって、外付けの逆並列還流ダイオードが不要となり、高電流密度化と高速化が図られて、小型で高性能な半導体装置が実現される。

#### 【0156】

##### (第17の実施形態)

図41は、本発明の第17の実施形態に係る電力用半導体装置の要部断面図である。

#### 【0157】

本実施形態が第16の実施形態と異なる点は、ダイオード領域40bの裏面に形成される凹部が機械的研削やウェットエッティングにより形成され、凹部の側壁部が斜めに形成されていることである。これらの方法を用いると、凹部の深さを深く形成できるという利点がある。機械的研削は、ブリノ酸等によるウェットエッティングと併用してもよく、ウェットエッティングは、水酸化カリウム(KOH)等を使用することができる。

#### 【0158】

##### (第18の実施形態)

図42は、本発明の第18の実施形態に係る電力用半導体装置の要部断面図である。

#### 【0159】

本実施形態が第17の実施形態と異なる点は、IGBTのゲート電極50aがトレンチの中に形成されていることである。トレンチゲートの形成は、RIEなどを使用すればよく、良く知られているので説明を省略する。

#### 【0160】

このような構成であっても、第16の実施形態と同様な効果を得ることができ、かつIGBTのオン電圧を一層低減できる。

#### 【0161】

##### (第19の実施形態)

図43は、本発明の第19の実施形態に係る電力用半導体装置の要部断面図である。

#### 【0162】

本実施形態が第16の実施形態と異なる点は、IGBT領域40aとダイオード領域40bが同一の厚さの基板上に形成されていることである。その代わり、ダイオード領域40bのp型アノード層48が深く形成されている。

#### 【0163】

このため、ダイオード領域40bの耐圧を実質的に決定するn型ベース層41bの厚さW2'は、IGBT領域40aの耐圧を実質的に決定するn型ベース層41aの厚さW1'との間に、W2' < W1'なる関係を有する。

#### 【0164】

このような、このような構成であっても、第16の実施形態と同様な効果を得ることができる。

#### 【0165】

##### (第20の実施形態)

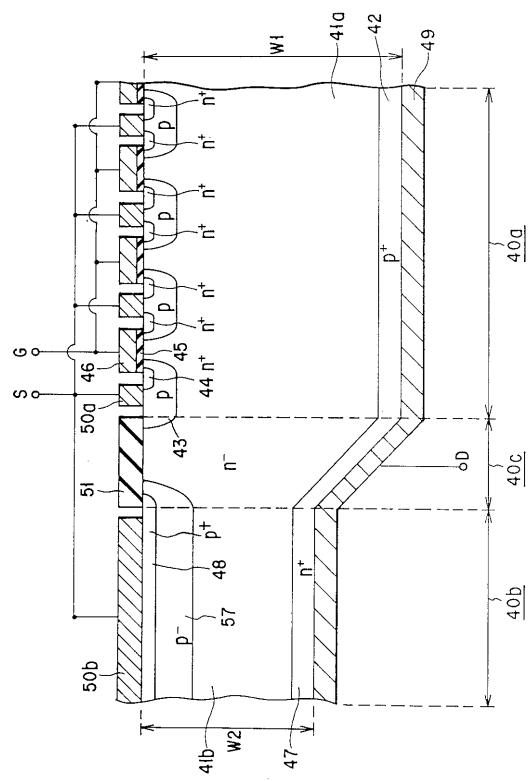

図44は、本発明の第20の実施形態に係る電力用半導体装置の要部断面図である。

#### 【0166】

本実施形態が第16の実施形態と異なる点は、ダイオード領域40bのp型アノード層4

10

20

30

40

50

8をとり囲み、これより深く形成されたp<sup>-</sup>型層57を有する点である。このp<sup>-</sup>型層57は、アノード層48からのホールの注入量を実質的に低減する働きをする。

【0167】

(第21の実施形態)

図45は、本発明の第21の実施形態に係る電力用半導体装置の要部断面図である。

【0168】

本実施形態が第16の実施形態と異なる点は、ダイオード領域40bがn型ベース基板41の表面に形成された凹部に設けられていることである。N型ベース基板41の裏面は平坦にされており、IGBT領域40aのn型ベース基板の厚さW1と、ダイオード領域のn型ベース基板の厚さW2との間には、W1>W2の関係が成り立つ。

10

【0169】

このような構成であっても第16の実施形態と同様な効果を得ることができる。

【0170】

次に、本発明の第3の態様の電力用半導体装置の実施形態(第22乃至第26の実施形態)を説明する。なお、これらの実施形態では第1導電型層としてn型、第2導電型層としてp型を用いているが、導電型を逆にしてもよい。また、同一箇所には同一番号を付して、重複する説明を省略する。

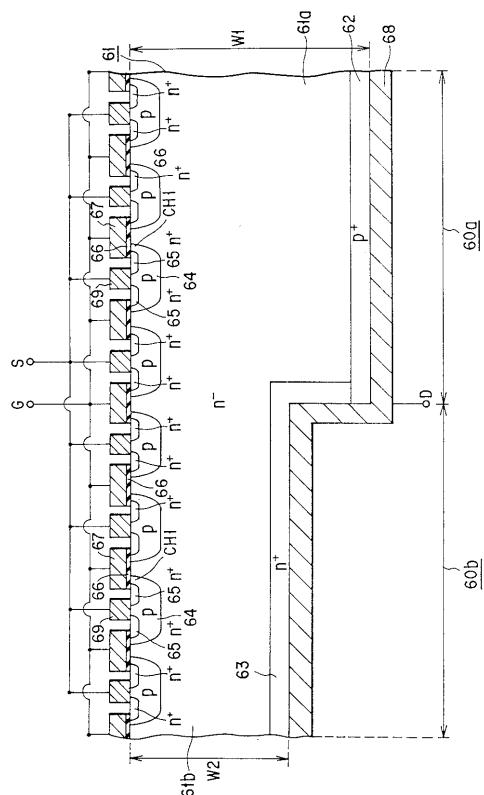

【0171】

(第22の実施形態)

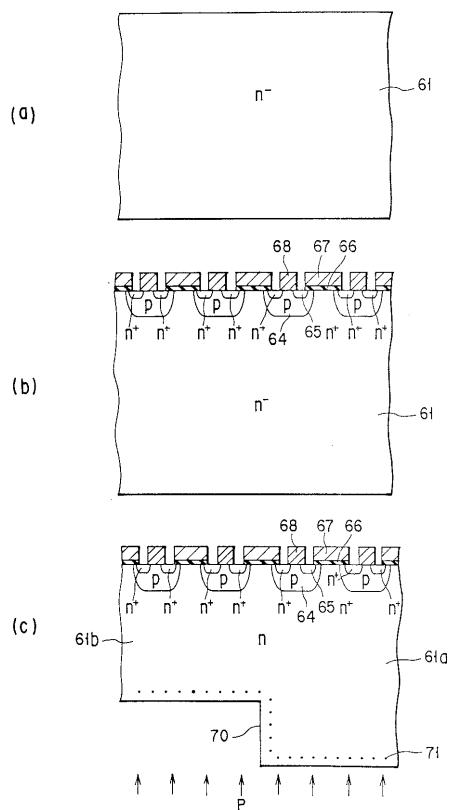

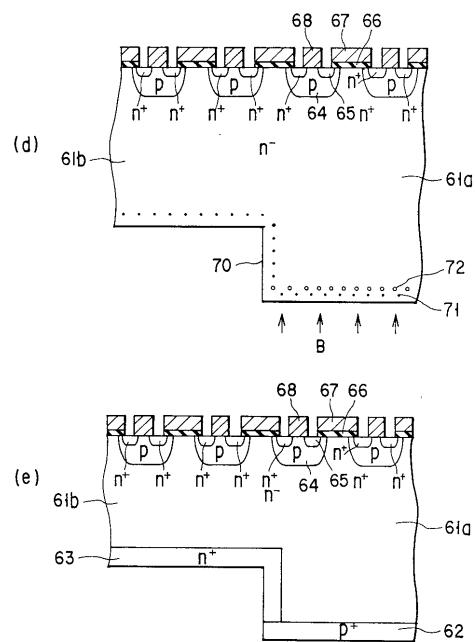

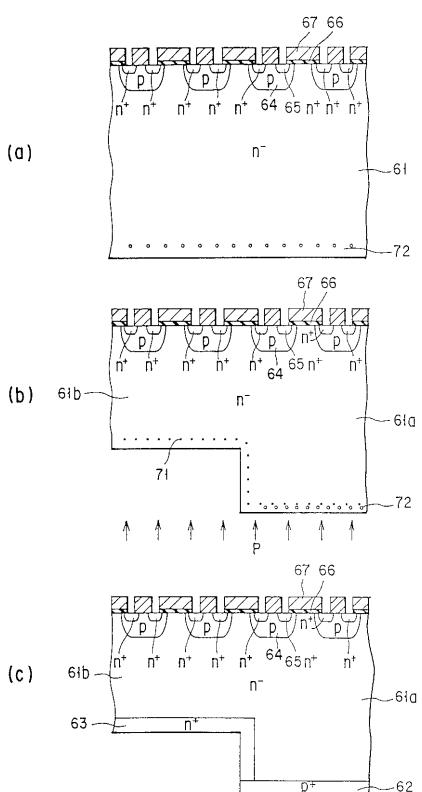

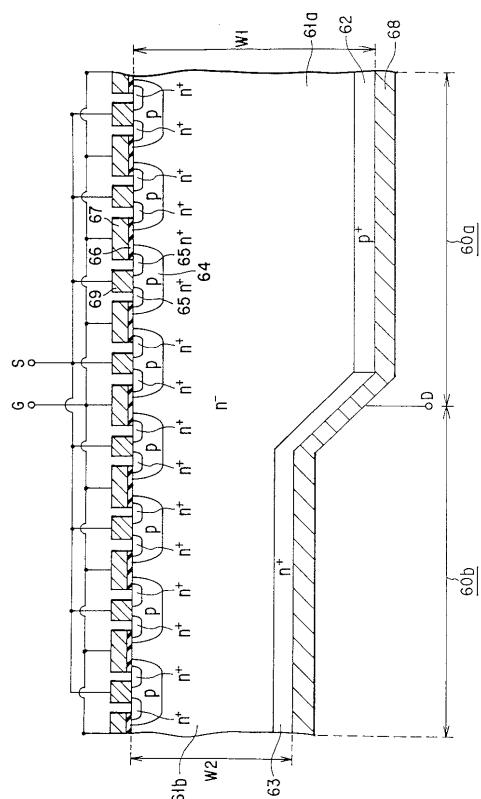

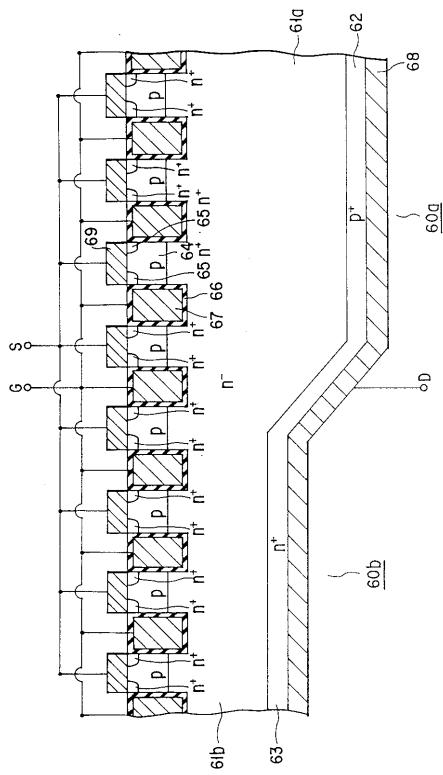

図46は、本発明の第22の実施形態に係る電力用半導体装置の要部断面図を示す。図46において、61は高抵抗のn型ベース層(半導体基板)を示しており、このn型ベース層61の一方の面(裏面)には、凹部が形成されている。この裏面で凹部が形成されていない領域60aにp型ドレイン層62が形成され、凹部が形成された領域60bにn型ドレイン層63が形成されている。

20

【0172】

一方、n型ベース層61の他方の面(表面)には、複数のp型ベース層64が選択的に形成され、各p型ベース層64内にはn型ソース層65が形成されている。さらに、n型ベース層61とn型ソース層65との間のp型ベース層64上には、ゲート絶縁膜66を介してゲート電極67が形成されている。なお、これらゲート電極67、ゲート絶縁膜66、p型ベース層64、n型ベース層61及びn型ソース層65により、CH1をチャネル領域とする電子注入用MOSFETが構成されている。

30

【0173】

p型ドレイン層62上及びn型ドレイン層63上には、両層62,63に接してドレイン電極(第2の主電極)68が形成されている。また、n型ソース層65上及びp型ベース層64上には、両層65,64に接してソース電極(第1の主電極)69が形成されている。ゲート電極69が副電極となる。なお、複数のソース電極、複数のゲート電極は、それぞれ相互に接続されており、図中では結線で模式的に表されている。

【0174】

上記のように、p型ドレイン層62が形成された領域60aにはIGBTが構成されており、n型ドレイン層63が形成された領域60bには、パワーMOSFETが構成されている。

40

【0175】

以上のように、本発明の電力用半導体装置は、IGBTとMOSFETとが並列接続され、かつMOSFETを構成する高抵抗のn型ベース層(基板)61bの厚さW2がIGBTを構成する高抵抗のn型ベース層(基板)61aの厚さW1より小さいことが特徴である。

【0176】

次に、このような半導体装置の動作を説明する。ドレイン電極68に正電圧、ソース電極69に負電圧が印加されている時、ソースよりも正となる正電圧がゲート電極69に印加されると、p型ベース層64のゲート電極67に接した表面がn型に反転し、電子eがn

50

型ソース層 6 5 から反転層を介して n 型ベース層 6 1 に注入される。

【 0 1 7 7 】

ここで、ドレイン電流が小さくドレイン電圧も小さい場合、n 型ベース層 6 1 に注入された電子 e は、p 型ドレイン層 6 2 と n 型ベース層 6 1 とによって構成される p n 接合のビルトインポテンシャルを越えることができない。このため、電子 e は p 型ドレイン層 6 2 には流れ込みず、n 型ドレイン層 6 3 に流れ込む。すなわち低電流領域では、ソース電極 6 9、n 型ソース層 6 5、反転層（チャネル）CH 1、n 型ベース層 6 1 b、n 型ドレイン層 6 3、ドレイン電極 6 8 を結ぶ経路が多数キャリアの流路となるので、p n 接合に起因する電圧降下が生じず、零電圧から電流が立ち上がる。

【 0 1 7 8 】

次に、電流が増加してドレイン電圧が上昇してくると、上記 p n 接合が順バイアスされて、電子 e はビルトインポテンシャルを越えて p 型ドレイン層 6 2 に流入するようになる。これに伴い、p 型ドレイン層 6 2 から n 型ベース層 6 1 に正孔 h が注入される。結果的に、n 型ベース層 6 1 に電子 e と正孔 h の両方が注入され、伝導度変調が起こる。これにより半導体装置は低オン電圧で導通する。

【 0 1 7 9 】

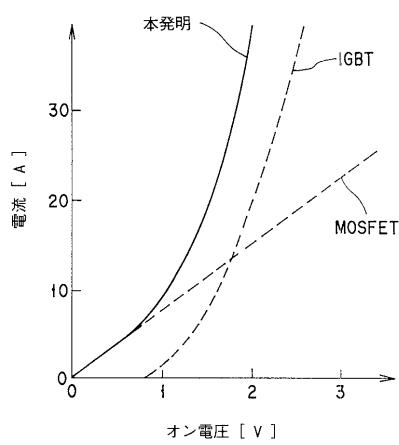

特に、本発明の半導体装置では、MOSFET を構成する高抵抗ベース層（基板）6 1 b の厚さ W 2 が IGBT を構成する高抵抗ベース層（基板）6 1 a の厚さ W 1 よりも薄いことから、低電流領域でのオン抵抗を極めて小さくできる。以上の機構により、本発明の半導体装置では、低電流領域から高電流領域に亘って、オン抵抗を低減することができる。図 4 7 は、このような本発明の半導体装置のオン特性を説明する特性図である。

【 0 1 8 0 】

また、MOSFET は、パンチスルーニードル構造を有しているので、図 3 5 を使用して説明した特徴は、本実施形態の半導体装置にもそのまま当てはめることができる。

【 0 1 8 1 】

一方、ターンオフ動作の際には、ソースに対して負である負電圧が絶縁ゲート 6 7 に印加される。これにより、ゲート電極 6 7 直下に形成されていた反転層が消失して電子注入が止まる。一方、n 型ベース層 6 1 中の正孔 h は、その一部が p 型ベース層 6 4 を介してソース電極 6 9 に排出され、残りの正孔 h は、電子 e と再結合して消滅する。これにより、半導体装置はターンオフする。

【 0 1 8 2 】

次に、図 4 8、図 4 9 を参照して、本発明の電力用半導体装置の製造方法を説明する。

【 0 1 8 3 】

まず、図 4 8 ( a ) に示すように、n 型ベース層となる半導体基板 6 1 を用意する。次に、図 4 8 ( b ) に示すように、n 型ベース基板の上面に、MOSFET および IGBT の p ベース層となる複数の p ウェル 6 3 を形成する。p ウェル 6 3 の中には、それぞれ n 型ソース層 6 5 を形成し、隣接する p ウェル間に露出する n 型ベース基板の表面には、p ウェル 6 3、n 型ソース 6 5 の上部に延在するように、ゲート絶縁膜 6 6 を介してゲート電極 6 7 を形成する。同時に、ソース電極 6 8 を形成する。

【 0 1 8 4 】

次に、図 4 8 ( c ) に示すように、n 型ベース基板 6 1 裏面の MOSFET 領域 6 0 b に相当する部分を RIE を用いてドライエッチングし、凹部 7 0 を形成する。続いて、IGBT 形成領域 6 0 a に相当する領域に、電子線やプロトン等の粒子線を照射する。さらに、この凹部を含めて n 型ベース基板 6 1 の裏面全面に、n 型不純物 7 1、例えばリン ( P ) をイオン注入する。

【 0 1 8 5 】

次に、図 4 9 ( d ) に示すように、n ベース基板 6 1 裏面の凹部が形成されていない領域 (IGBT 領域) 6 1 a に p 型不純物イオン 7 2、例えばボロン ( B ) をイオン注入する。この時、p 型不純物イオン 7 2 のドーズ量は、n 型不純物イオン 7 1 のそれよりも多くする。例えば、n 型不純物イオンとしてリンを  $2 \times 10^{15} \text{ cm}^{-2}$ 、p 型不純物としてボロ

10

20

30

40

50

ンを  $5 \times 10^{15} \text{ cm}^{-2}$  のドーズ量で注入する。

【0186】

続いて、アニールを行うことにより、図49(e)に示すように、IGBT領域60aの裏面にp型ドレイン層62、MOSFET領域60bの裏面にn型ドレイン層63を形成する。

【0187】

上記の図48(c)乃至図49(e)の工程は、図50のように変形して実施してもよい。すなわち、n型ベース基板61の裏面に予めp型イオン72をイオン注入しておき(図50(a))、その後図50(b)に示すように、凹部72を形成する。続いてn型イオン71をn型ベース基板61の裏面全体にイオン注入する。その後アニールを行うことにより、図50(c)に示すようにp型ドレイン層62とn型ドレイン層63を形成する。

10

【0188】

以上で、MOSFETとIGBTが並列接続された電力用半導体装置が完成する。

【0189】

図46では、本発明の半導体装置の部分的な断面図のみが示されているが、半導体装置全体としては、第16の実施形態と同様に、図40の平面図に示すような構成とすることができます。図40において、40bをMOSFET領域と読み替えれば、そのまま本実施形態に適用することができる。

【0190】

以上のように、本発明によれば、低電流領域では主に、ソース電極69、n型ソース層65、反転層(チャネル)CH1、n型ベース層61b、n型ドレイン層63、ドレイン電極68を結ぶ経路が多数キャリアの流路となるので、pn接合に起因する電圧降下が生じず、零電圧から電流が立ち上がる。一方、高電流領域では、p型ドレイン層62からn型ベース層61aに少数キャリアが注入されるので、伝導度変調が起きる。従って、低電流領域から高電流領域に亘って、オン抵抗を低減することができる。

20

【0191】

(第23の実施形態)

図51は、本発明の第23の実施形態に係る電力用半導体装置の要部断面図である。

【0192】

本実施形態が第22の実施形態と異なる点は、MOSFET領域60bの裏面に形成される凹部が機械的研削やウェットエッティングにより形成され、凹部の側壁部が斜めに形成されていることである。これらの方法を用いると、凹部の深さを深く形成できるという利点がある。機械的研削は、弗硝酸等によるウェットエッティングと併せておこなってもよく、ウェットエッティングは、水酸化カリウム(KOH)等を用いて行うことができる。

30

【0193】

(第24の実施形態)

図52は、本発明の第24の実施形態に係る電力用半導体装置の要部断面図である。

【0194】

本実施例が第23の実施形態と異なる点は、IGBT若しくはMOSFETのゲート電極67がトレンチの中に形成されていることである。トレンチゲートはRIE等を用いて形成すればよく、その形成方法は良く知られているので説明を省略する。

40

【0195】

このような、このような構成であっても、第23の実施形態と同様な効果をえることができ、かつIGBTおよびMOSFETをさらに低オン抵抗化できる。

【0196】

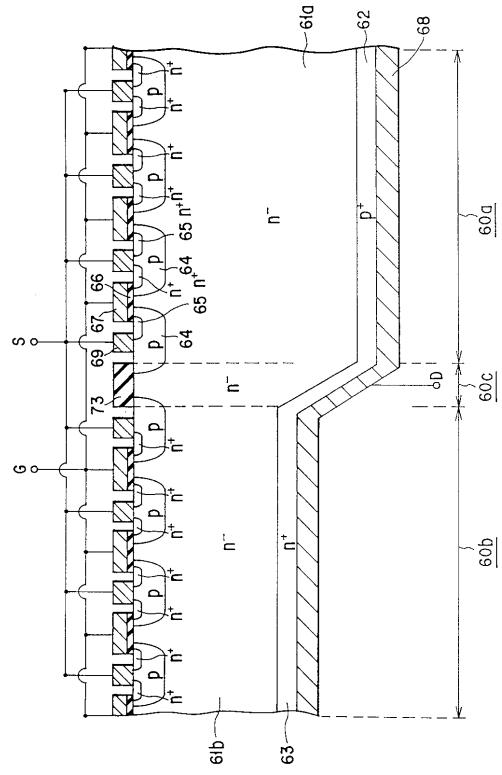

(第25の実施形態)

図53は、本発明の第25の実施形態に係る電力用半導体装置の要部断面図である。

【0197】

本実施例が第23の実施形態と異なる点は、IGBT領域60aとMOSFET領域60bとの間に分離領域60cを有することである。分離領域60cは、本発明の素子がターン

50

オフする際、MOSFET領域に拡散した正孔により、MOSFET領域の動作のアンバランスが生じるのを抑制するためのものである。分離領域60cの幅が、キャリアの拡散長より短い場合は、IGBTと同様に、ライフタイムキラーを導入するのが望ましい。73は、分離領域上に設けられた絶縁膜である。

【0198】

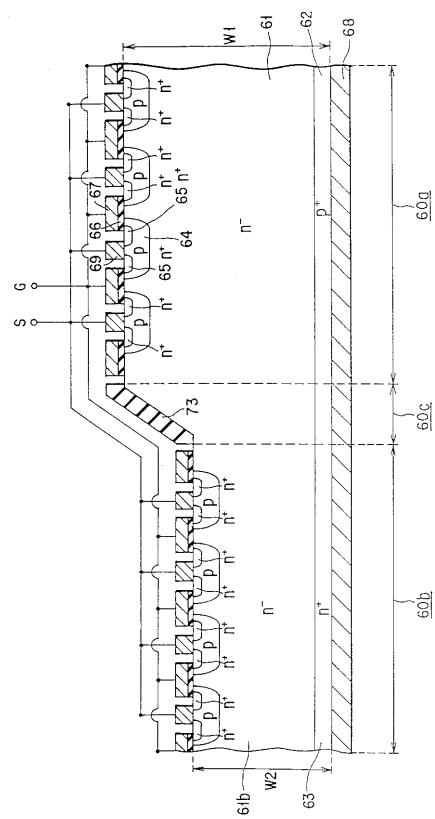

(第26の実施形態)

図54は、本発明の第26の実施形態に係る電力用半導体装置の要部断面図である。

【0199】

本実施形態が第23の実施形態と異なる点は、MOSFET領域60bがn型ベース基板61の表面に形成された凹部に設けられていることである。N型ベース基板61の裏面は平坦にされており、IGBT領域60aのn型ベース基板の厚さW1と、MOSFET領域のn型ベース基板の厚さW2との間には、W1>W2の関係が成り立つ。

10

【0200】

このような構成であっても第23の実施形態と同様な効果を得ることができる。

【0201】

【発明の効果】

以上詳述したように本発明の第1の態様によれば、半導体基板に凹部を形成することによって、高耐圧半導体素子が形成される領域を薄くしたり、半導体基板との界面に複数の段差を有する電界緩和構造を用いることにより、必要な耐圧を確保するために、電界緩和構造を用いるとともに、半導体基板を厚くしても、高耐圧半導体素子の順方向電圧降下、逆回復損失等の素子特性の劣化を防止できる高耐圧半導体装置を実現できるようになる。

20

【0202】

また、本発明の第2の態様によれば、逆並列還流ダイオードの機能が内蔵され、順方向においてスイッチング機能を有し、逆方向において導通特性を有する。これにより、誘導負荷により逆起電力が発生すると、半導体装置は逆方向にターンオフする。その際、ダイオードは低オン電圧で導通される。もって、逆並列還流ダイオードが不要となる結果、高電流密度化と高速化が図られて、小型で高性能な半導体装置が実現される。

【0203】

また、本発明の第3の態様によれば、低電流領域では主に、薄い高抵抗ベース層を有するMOSFET領域をキャリアが流れ、高電流領域ではIGBT領域を流れる。これにより、低電流領域ではpn接合に起因する電圧降下が生じないので、零電圧から電流が立ち上がり、高電流領域では、p型ドレイン層から少数キャリアが注入されるので、伝導度変調が起きる。従って、低電流領域から高電流領域に亘って、オン抵抗を低減することができる。

30

【図面の簡単な説明】

【図1】本発明の第1の実施形態に係る高耐圧半導体装置の要部を示す断面図。

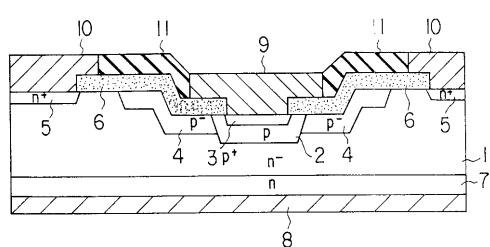

【図2】従来のp型リサーフ層を用いた高耐圧半導体装置の断面図に、電界強度のプロファイルを併記した図。

【図3】第1の実施形態における電界分布を説明するための断面図に、電界強度のプロファイルを併記した図。

40

【図4】第1の実施形態において凹部の深さが浅い場合の高耐圧半導体装置の断面図に、電界強度のプロファイルを併記した図。

【図5】第1の実施形態において凹部の深さが中間の場合の高耐圧半導体装置の断面図に、電界強度のプロファイルを併記した図。

【図6】第1の実施形態において凹部の深さが深い場合の高耐圧半導体装置の断面図に、電界強度のプロファイルを併記した図。

【図7】第1の実施形態における凹部の素子構造の形成方法を段階的に示す断面図。

【図8】第1の実施形態の高耐圧半導体装置の変形例を示す断面図。

【図9】第1の実施形態の高耐圧半導体装置の他の変形例を示す断面図。

【図10】本発明の第2の実施形態に係る高耐圧半導体装置の要部を示す断面図。

50

- 【図11】本発明の第3の実施形態に係る高耐圧半導体装置の要部を示す断面図。

- 【図12】本発明の第4の実施形態に係る高耐圧半導体装置の要部を示す断面図。

- 【図13】本発明の第5の実施形態に係る高耐圧半導体装置の要部を示す断面図。

- 【図14】本発明の第6の実施形態に係る高耐圧半導体装置の要部を示す断面図。

- 【図15】本発明の凹部の素子構造の形成方法を段階的に示す半導体装置の断面図。

- 【図16】図15の高耐圧半導体装置の変形例を示す断面図。

- 【図17】本発明の第7の実施形態に係る高耐圧半導体装置を示す断面図。

- 【図18】本発明の第8の実施形態に係る高耐圧半導体装置の要部を示す断面図。

- 【図19】本発明の第9の実施形態に係る高耐圧半導体装置の要部を示す断面図。

- 【図20】本発明の第10の実施形態に係る高耐圧半導体装置の要部を示す断面図。 10

- 【図21】図20の高耐圧半導体装置の変形例を示す断面図。

- 【図22】本発明の第11の実施形態に係る高耐圧半導体装置の要部を示す断面図。

- 【図23】図22の高耐圧半導体装置の基本構造の形成方法を段階的に示す断面図。

- 【図24】図22の高耐圧半導体装置の基本構造の他の形成方法を段階的に示す断面図。

- 【図25】図22の高耐圧半導体装置の基本構造のさらに他の形成方法を段階的に示す断面図。 20

- 【図26】図22の高耐圧半導体装置の基本構造のさらに他の形成方法を段階的に示す断面図。

- 【図27】本発明の第12の実施形態に係る高耐圧半導体装置の要部を示す断面図。

- 【図28】図27の凹部の素子構造の形成方法を段階的に示す断面図。 20

- 【図29】図27の高耐圧半導体装置の変形例を示す断面図。

- 【図30】本発明の第13の実施形態に係る高耐圧半導体装置の要部を示す断面図。

- 【図31】本発明の第14の実施形態に係る高耐圧半導体装置の要部を示す断面図。

- 【図32】図29の高耐圧半導体装置の変形例を示す断面図。

- 【図33】本発明の第15の実施形態に係る高耐圧半導体装置の要部を示す断面図。

- 【図34】本発明の第16の実施形態に係る電力用半導体装置の要部を示す断面図。

- 【図35】(a)、(b)は、それぞれ図34のIGBT部、ダイオード部の電界強度のプロファイルを示す図。 30

- 【図36】パンチスルーラー型素子(ダイオード等)とノンパンチスルーラー型素子(IGBT等)について、n型ベース層の厚さと耐圧の関係を比較した図。

- 【図37】図34の電力用半導体装置の基本構造の製造方法を段階的に示す断面図。

- 【図38】図37に続く工程を示す断面図。

- 【図39】図37(c)乃至図38(e)に対応する他の製造方法を示す断面図。

- 【図40】図34の電力用半導体装置が採り得る平面形状を示した図で、図34は、図40(a)、(b)、(c)の各々のA-A線に沿った断面図に相当。 40

- 【図41】本発明の第17の実施形態に係る電力用半導体装置の要部を示す断面図。

- 【図42】本発明の第18の実施形態に係る電力用半導体装置の要部を示す断面図。

- 【図43】本発明の第19の実施形態に係る電力用半導体装置の要部を示す断面図。

- 【図44】本発明の第20の実施形態に係る電力用半導体装置の要部を示す断面図。

- 【図45】本発明の第21の実施形態に係る電力用半導体装置の要部を示す断面図。

- 【図46】本発明の第22の実施形態に係る電力用半導体装置の要部を示す断面図。

- 【図47】図46の電力用半導体装置の電圧-電流特性を説明するための特性図。

- 【図48】図46の電力用半導体装置の基本構造の製造方法を段階的に示す断面図。

- 【図49】図48に続く工程を示す断面図。

- 【図50】図48(c)乃至図49(e)に対応する他の製造方法を示す断面図。

- 【図51】本発明の第23の実施形態に係る電力用半導体装置の要部を示す断面図。

- 【図52】本発明の第24の実施形態に係る電力用半導体装置の要部を示す断面図。

- 【図53】本発明の第25の実施形態に係る電力用半導体装置の要部を示す断面図。

- 【図54】本発明の第26の実施形態に係る電力用半導体装置の要部を示す断面図。

- 【図55】従来の高耐圧ダイオードの主要部の素子構造を示す部分断面図。 50

【図56】従来のIGBTを用いたインバータの主要部の回路構成図。

【図57】従来のIGBTの主要部の断面図。

【図58】IGBTの電圧-電流特性を示す特性図。

【符号の説明】

- |                         |    |

|-------------------------|----|

| 1 ... 第1のn型カソード層(半導体基板) | 10 |

| 2 ... 第1のp型アノード層        |    |

| 3 ... 第2のp型アノード層        |    |

| 4 ... p型リサーフ層(電界緩和構造)   |    |

| 5 ... n型チャネルストップ層       |    |

| 6 ... 高抵抗膜              |    |

| 7 ... n型カソード層           |    |

| 8 ... カソード電極            |    |

| 9 ... アノード電極            |    |

| 10 ... 電極               |    |

| 11 ... 絶縁膜              |    |

| 12 ... p型ガードリング層        |    |

| 13 ... p型リサーフ層(電界緩和構造)  |    |

| 14 ... 高濃度nカソード層        |    |

| 21 ... 第1のn型ベース層(半導体基板) | 20 |

| 22 ... 第1のp型ベース層        |    |

| 23 ... 第2のp型ベース層        |    |

| 24 ... n型ソース層           |    |

| 25 ... ゲート絶縁膜           |    |

| 26 ... ゲート電極            |    |

| 27 ... p型リサーフ層          |    |

| 28 ... n型チャネルストップ層      |    |

| 29 ... 高抵抗膜             |    |

| 30 ... 第2のn型ベース層        |    |

| 31 ... p型ドレイン層          |    |

| 32 ... ドレイン電極           | 30 |

| 33 ... ソース電極            |    |

| 34 ... 電極               |    |

| 35 ... 絶縁膜              |    |

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図10】

【図9】

【図11】

【図12】

【図14】

【図13】

【図15】

【図16】

【図17】

【図18】

【図20】

【図19】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

### 【図31】

【 図 3 3 】

### 【図3-2】

【図3-4】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図44】

【図45】

【図46】

【図47】

【 図 4 8 】

【図49】

【図50】

【 図 5 1 】

【図 5 2】

【図 5 3】

【図 5 4】

【図 5 5】

【図 5 6】

【図57】

【図58】

---

フロントページの続き

(72)発明者 附田 正則

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝研究開発センター内

(72)発明者 四戸 孝

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝研究開発センター内

(72)発明者 山口 正一

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝研究開発センター内

審査官 河口 雅英

(56)参考文献 特開平05-152574 (JP, A)

特開平07-153951 (JP, A)

特開平04-014263 (JP, A)

特開平02-082534 (JP, A)

特開昭53-127270 (JP, A)

実開平03-010556 (JP, U)

特開平01-272151 (JP, A)

特開昭63-053969 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/861

H01L 29/06

H01L 29/739

H01L 29/78