(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-59874

(P2014-59874A)

(43) 公開日 平成26年4月3日(2014.4.3)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>G06F 12/06 (2006.01)</b> | G06F 12/06 | 522A 5B060  |

| <b>HO4N 5/76 (2006.01)</b>  | HO4N 5/76  | Z 5C053     |

| <b>HO4N 5/907 (2006.01)</b> | HO4N 5/907 | B 5C122     |

| <b>HO4N 5/91 (2006.01)</b>  | HO4N 5/91  | J           |

| <b>HO4N 5/225 (2006.01)</b> | HO4N 5/225 | F           |

審査請求 未請求 請求項の数 23 O L (全 22 頁)

(21) 出願番号 特願2013-191525 (P2013-191525)

(22) 出願日 平成25年9月17日 (2013.9.17)

(31) 優先権主張番号 10-2012-0102471

(32) 優先日 平成24年9月14日 (2012.9.14)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100086368

弁理士 萩原 誠

(72) 発明者 尹 松 虎

大韓民国京畿道龍仁市水枝区豊徳川2洞

三星5次アパート523棟702号

最終頁に続く

(54) 【発明の名称】連続撮影イメージデータを処理する方法と装置

## (57) 【要約】

【課題】連続撮影イメージデータを処理する方法と装置とを提供する。

【解決手段】それぞれの連続撮影イメージデータを生成するマルチブル連続撮影動作が実行される間に、イメージ処理システムに含まれ、第1メモリ領域と第2メモリ領域とを含むメモリアレイを含むフラッシュ保存装置の動作方法は、ホストから領域割り当て情報を受信する段階と、連続撮影動作が実行される間に、領域割り当て情報に基づいて、第1メモリ領域の一部を、連続撮影イメージデータを臨時保存するための専用連続撮影イメージデータバッファ領域に割り当てる段階と、正常プログラム動作中に、第2メモリ領域の一部を、正常データを保存するための正常データ領域に割り当てる段階と、を含み、第1メモリ領域は、第1速度で行われる正常プログラム動作を含むデータアクセス動作を支援し、第2メモリ領域は、第1速度よりも遅い第2速度で行われるデータアクセス動作を支援する。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

それぞれの連続撮影イメージデータを生成するマルチプル連続撮影動作が実行される間に、イメージ処理システムに含まれ、第1メモリ領域と第2メモリ領域とを含むメモリアレイを含むフラッシュ保存装置の動作方法において、

ホストから領域割り当て情報を受信する段階と、

前記連続撮影動作が実行される間に、前記領域割り当て情報に基づいて、前記第1メモリ領域の一部を、前記連続撮影イメージデータを臨時保存するための専用連続撮影イメージデータバッファ領域に割り当てる段階と、

正常プログラム動作中に、前記第2メモリ領域の一部を、正常データを保存するための正常データ領域に割り当てる段階と、を含み、

前記第1メモリ領域は、第1速度で行われる前記正常プログラム動作を含むデータアクセス動作を支援し、

前記第2メモリ領域は、前記第1速度よりも遅い第2速度で行われるデータアクセス動作を支援するフラッシュ保存装置の動作方法。

**【請求項 2】**

前記領域割り当て情報は、イメージ解像度設定、連続撮影フレームレート、及び連続撮影時間のうち少なくとも2つ、または連続撮影イメージデータ(CSID)バッファ領域サイズ値を含む請求項1に記載のフラッシュ保存装置の動作方法。

**【請求項 3】**

前記第1メモリ領域は、シングルレベルメモリセルで動作するフラッシュメモリセルを含み、前記第2メモリ領域は、マルチレベルメモリセルで動作するフラッシュメモリセルを含む請求項1に記載のフラッシュ保存装置の動作方法。

**【請求項 4】**

前記フラッシュ保存装置の動作方法は、前記イメージ処理システムの初期化動作中に、前記ホストに含まれたメモリに前記領域割り当て情報を保存する段階をさらに含む請求項1に記載のフラッシュ保存装置の動作方法。

**【請求項 5】**

前記フラッシュ保存装置は、前記ホストから受信されたSWITCH命令に応答して、前記領域割り当て情報を保存するVENDOR\_SPECIFIC\_FIELDを有するEXT\_CSDレジスタを含むエンベデッドマルチメディアカードである請求項1に記載のフラッシュ保存装置の動作方法。

**【請求項 6】**

前記ホストは、プロセッサとカメラモジュールとを含み、前記方法は、

前記カメラモジュールで前記連続撮影イメージデータを生成し、前記連続撮影イメージデータに関連した連続撮影イメージデータフラグを生成し、前記プロセッサに前記連続撮影イメージデータと前記連続撮影イメージデータフラグとを提供する段階と、

前記プロセッサを用いてRAMに前記連続撮影イメージデータを保存する段階と、

前記領域割り当て情報と前記連続撮影イメージデータフラグとに応答して、前記プロセッサを用いて前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータをプログラミングする段階と、のうち少なくとも1つを前記マルチプル連続撮影動作に含む請求項1に記載のフラッシュ保存装置の動作方法。

**【請求項 7】**

前記ホストは、プロセッサとカメラモジュールとを含み、前記フラッシュ保存装置は、eMMCであり、前記方法は、

前記カメラモジュールで前記連続撮影イメージデータを生成し、前記連続撮影イメージデータに関連した連続撮影イメージデータフラグを生成し、前記プロセッサに前記連続撮影イメージデータと前記連続撮影イメージデータフラグとを提供する段階と、

前記プロセッサを用いてRAMに前記連続撮影イメージデータを保存する段階と、

前記領域割り当て情報と前記連続撮影イメージデータフラグとに応答して、前記プロセ

10

20

30

40

50

ッサを用いて前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータをプログラミングする段階と、のうち少なくとも1つを前記マルチプル連続撮影動作に含み、

前記連続撮影イメージデータフラグは、CMD23命令のcontext IDであって、前記ホストから前記MMCに伝送され、前記連続撮影イメージデータは、CMD25命令のデータであって、前記ホストから前記MMCに伝送される請求項1に記載のフラッシュ保存装置の動作方法。

【請求項8】

前記フラッシュ保存装置の動作方法は、

前記マルチプル連続撮影動作のうち少なくとも1つを実行した後、移送命令を前記ホストから前記フラッシュ保存装置に伝送する段階と、

前記専用連続撮影イメージデータバッファ領域に保存された前記連続撮影イメージデータの一部を前記第2メモリ領域にコピーする前記移送命令に応答して移送動作を行う段階と、

をさらに含む請求項6に記載のフラッシュ保存装置の動作方法。

【請求項9】

前記フラッシュ保存装置は、前記プロセッサと共に前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータの前記プログラミングを制御するフラッシュコントローラとページバッファとを含む請求項8に記載のフラッシュ保存装置の動作方法。

【請求項10】

前記移送命令は、連続撮影動作の実行後、一定の時間が経過した後、前記ホストから前記フラッシュ保存装置に伝送される請求項8に記載のフラッシュ保存装置の動作方法。

【請求項11】

前記ホストは、プロセッサとカメラモジュールとを含み、前記方法は、

前記カメラモジュールで前記連続撮影イメージデータを生成し、前記連続撮影イメージデータのサイズを指示する連続撮影イメージデータフラグを生成し、前記プロセッサに前記連続撮影イメージデータと前記連続撮影イメージデータフラグとを提供する段階と、

前記プロセッサを用いてRAMに前記連続撮影イメージデータを保存する段階と、

前記連続撮影イメージデータのサイズと前記専用連続撮影イメージデータバッファ領域の残りの使用可能なメモリ領域のサイズとを比較する段階と、

前記連続撮影イメージデータのサイズが、前記専用連続撮影イメージデータバッファ領域の残りの使用可能なメモリ領域のサイズよりも小さいか同じである時、前記領域割り当て情報と前記連続撮影イメージデータフラグとに応答して、前記プロセッサを用いて前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータをプログラミングし、そうではない時、前記プロセッサを用いて前記第2メモリ領域に前記連続撮影イメージデータをプログラミングする段階と、のうち少なくとも1つを前記マルチプル連続撮影動作に含む請求項1に記載のフラッシュ保存装置の動作方法。

【請求項12】

前記RAMに前記連続撮影イメージデータを保存する段階は、

前記マルチプル連続撮影動作が実行される間に、前記RAMに前記連続撮影イメージデータをバッファリングし、前記連続撮影イメージデータを前記RAMから前記フラッシュメモリ装置に伝送する請求項11に記載のフラッシュ保存装置の動作方法。

【請求項13】

連続撮影イメージデータを生成するホストと、

第1メモリ領域と第2メモリ領域とを含むメモリセルアレイを含むフラッシュ保存装置と、を含み、

前記第1メモリ領域の一部は、前記連続撮影イメージデータを一時的に保存する専用連続撮影イメージデータバッファ領域であり、前記第2メモリ領域は、正常プログラム動作中に、前記ホストから前記フラッシュ保存装置に提供される正常データを保存し、

前記第1メモリ領域は、第1速度で行われる前記正常プログラム動作を含むデータア

10

20

30

40

50

セス動作を支援し、

前記第2メモリ領域は、前記第1速度よりも遅い第2速度で行われるデータアクセス動作を支援するイメージ処理システム。

【請求項14】

前記第1メモリ領域は、シングルレベルメモリセルで動作するフラッシュメモリセルを含み、前記第2メモリ領域は、マルチレベルメモリセルで動作するフラッシュメモリセルを含む請求項13に記載のイメージ処理システム。

【請求項15】

前記ホストは、

プロセッサと、

前記連続撮影イメージデータを前記プロセッサに提供するカメラモジュールと、

前記イメージ処理システムによって実行される連続撮影動作のシーケンスの間に、リアルタイムで前記プロセッサから受信した前記連続撮影イメージデータをバッファリングするRAMと、

を含む請求項14に記載のイメージ処理システム。

【請求項16】

前記フラッシュ保存装置は、前記プロセッサから受信した前記領域割り当て情報に応答して、前記第1メモリ領域に前記専用連続撮影イメージデータバッファ領域を定義するフラッシュコントローラを含む請求項15に記載のイメージ処理システム。

【請求項17】

前記プロセッサは、前記ホストから前記フラッシュ保存装置に伝送されるデータが、前記連続撮影イメージデータであることを指示する連続撮影イメージデータフラグをさらに提供し、

前記フラッシュコントローラは、前記連続撮影イメージデータフラグに応答して、前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータを保存する請求項16に記載のイメージ処理システム。

【請求項18】

前記フラッシュコントローラは、前記連続撮影イメージデータのサイズが、前記専用連続撮影イメージデータバッファ領域で残りの利用可能なメモリ領域のサイズよりも小さいか同じである時、前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータを保存し、そうではない時、前記フラッシュコントローラは、前記第2メモリ領域に前記連続撮影イメージデータを保存する請求項17に記載のイメージ処理システム。

【請求項19】

前記プロセッサは、前記フラッシュ保存装置に移送命令をさらに提供し、前記移送命令に応答して、前記フラッシュコントローラは、前記専用連続撮影イメージデータバッファ領域に保存される前記連続撮影イメージデータの一部を前記第2メモリ領域にコピーする請求項16に記載のイメージ処理システム。

【請求項20】

前記フラッシュコントローラは、連続撮影動作の実行後、所定の時間が経った後に、前記ホストから前記移送命令を受信できない時、前記専用連続撮影イメージデータバッファ領域に保存された前記連続撮影イメージデータの一部を前記第2メモリ領域にコピーする請求項19に記載のイメージ処理システム。

【請求項21】

前記ホストは、前記カメラモジュールから前記連続撮影イメージデータを受信するか、前記プロセッサから前記連続撮影イメージデータを受信するフラッシュ保存装置インターフェースコントローラをさらに含む請求項20に記載のイメージ処理システム。

【請求項22】

前記RAMは、DRAMである請求項20に記載のイメージ処理システム。

【請求項23】

前記ホストと前記フラッシュ保存装置は、システム・オン・チップ(SoC)製造技術

10

20

30

40

50

を使って共通基板上に製造される請求項 22 に記載のイメージ処理システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、連続撮影イメージデータを処理する方法と装置とに係り、特に、RAM (Random Access Memory) のデータ保存容量と無関係に不揮発性保存装置に高解像度 (high-resolution) の連続撮影機能によって生成された連続撮影イメージデータをリアルタイムで処理し、保存可能な方法と装置とに関する。

【背景技術】

【0002】

最近のモバイル装置、例えば、スマートフォン、タブレットPC、及びデジタルカメラは、アプリケーション及び運用体制を実行させる間に使われるRAM、ユーザデータを保存するために使われる不揮発性保存装置、及びイメージデータ（例えば、スチルイメージデータ及び／または連続撮影イメージデータ）を生成可能なカメラモジュールを含む。

カメラモジュールに含まれたカメラのピクセル (pixels) の数が増加するにつれて、イメージ解像度も増加する。多数のピクセルが、また向上した連続撮影機能を支援する。

【0003】

連続撮影機能を支援するモバイル装置は、一般的に連続撮影機能によって生成された連続撮影イメージデータをRAMの専用部分に保存する。RAMに保存された連続撮影イメージデータは、RAMの専用部分がいっぱいになった時、不揮発性保存装置にコピーされる。このようなモバイル装置は、与えられた時間制限内に連続撮影イメージデータをRAMに保存するために、十分に速いライトモード (write mode) で動作できるよう、前記2ステップ (step)（例えば、まず、RAMの専用部分をいっぱいにし、次いでRAMに保存された連続撮影イメージデータを不揮発性メモリに移動させる段階）を反復する。しかし、最近の不揮発性保存装置の利用可能なライトモードでは、類似している時間制限内に行うのには遅いという問題がある。

また、特定のイメージ処理システムによってキャプチャされる連続撮影イメージの当該個数とRAMに保存された連続撮影イメージデータのライトブロックサイズだけではなく、連続撮影イメージデータ保存に割り当てられたRAMの専用部分のサイズが制限されるという問題もある。

【0004】

連続撮影機能中に、モバイル装置によって実行された特定アプリケーションがRAMに相当なメモリ領域を要求するのに対応するために、連続撮影イメージデータの保存に割り当てられるRAMの専用部分のサイズを増加するための多くの試みは、非現実的なものとなっている。RAMのデータ保存容量が延長された連続撮影命令によっていっぱいになると、連続撮影命令は中断されなければならないか、連続撮影イメージデータの結果の解像度は低下する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許出願公開2007-0211530号公報

【特許文献2】米国特許第7769944号公報

【特許文献3】米国特許出願公開2009-0300269号公報

【特許文献4】米国特許出願公開2011-0019470号公報

【特許文献5】特開2004-201226号公報

【特許文献6】特開2007-318344号公報

【特許文献7】特開2008-242503号公報

【特許文献8】特開2009-231900号公報

10

20

30

40

50

【特許文献 9】特開 2011-097448 号公報

【特許文献 10】韓国特許出願公開 2012-0003282 号

【特許文献 11】韓国特許出願公開 2012-0031434 号

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明が解決しようとする技術的な課題は、RAMの容量と無関係に高解像度の連続撮影イメージデータを不揮発性保存装置にライトして、ライト性能を保証しながら、連続撮影イメージデータを処理する方法と装置とを提供することにある。

【課題を解決するための手段】

【0007】

それぞれの連続撮影イメージデータを生成するマルチプル(multiple)連続撮影動作が実行される間に、イメージ処理システムに含まれ、第1メモリ領域と第2メモリ領域とを含むメモリアレイを含むフラッシュ保存装置の動作方法は、ホストから領域割り当て情報を受信する段階と、前記連続撮影動作が実行される間に、前記領域割り当て情報に基づいて、前記第1メモリ領域の一部を、前記連続撮影イメージデータを臨時保存するための専用連続撮影イメージデータバッファ領域に割り当てる段階と、正常プログラム動作中に、前記第2メモリ領域の一部を、正常データを保存するための正常データ領域に割り当てる段階と、を含み、前記第1メモリ領域は、第1速度で行われる前記正常プログラム動作を含むデータアクセス動作を支援し、前記第2メモリ領域は、前記第1速度よりも遅い第2速度で行われるデータアクセス動作を支援する。

【0008】

前記領域割り当て情報は、イメージ解像度設定、連続撮影フレームレート、及び連続撮影時間のうち少なくとも2つ、または連続撮影イメージデータ(CSID)バッファ領域サイズ値を含む。

前記第1メモリ領域は、シングルレベルメモリセルで動作するフラッシュメモリセルを含み、前記第2メモリ領域は、マルチレベルメモリセルで動作するフラッシュメモリセルを含む。前記フラッシュ保存装置の動作方法は、前記イメージ処理システムの初期化動作中に、前記ホストに含まれたメモリに前記領域割り当て情報を保存する段階をさらに含む。

前記フラッシュ保存装置は、前記ホストから受信されたSWITCH命令に応答して、前記領域割り当て情報を保存するVENDOR\_SPECIFIC\_FILEフィールドを有するEXT\_CSDレジスタを含むエンベッドマルチメディアカードである。

【0009】

前記ホストは、プロセッサとカメラモジュールとを含み、前記方法は、前記カメラモジュールで前記連続撮影イメージデータを生成し、前記連続撮影イメージデータに関連した連続撮影イメージデータフラグを生成し、前記プロセッサに前記連続撮影イメージデータと前記連続撮影イメージデータフラグとを提供する段階と、前記プロセッサを用いてRAMに前記連続撮影イメージデータを保存する段階と、前記領域割り当て情報と前記連続撮影イメージデータフラグとに応答して、前記プロセッサを用いて前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータをプログラミングする段階と、のうち少なくとも1つを前記マルチプル連続撮影動作に含む。

【0010】

前記ホストは、プロセッサとカメラモジュールとを含み、前記フラッシュ保存装置は、eMMCであり、前記方法は、前記カメラモジュールで前記連続撮影イメージデータを生成し、前記連続撮影イメージデータに関連した連続撮影イメージデータフラグを生成し、前記プロセッサに前記連続撮影イメージデータと前記連続撮影イメージデータフラグとを提供する段階と、前記プロセッサを用いてRAMに前記連続撮影イメージデータを保存する段階と、前記領域割り当て情報と前記連続撮影イメージデータフラグとに応答して、前記プロセッサを用いて前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメ

10

20

30

40

50

ージデータをプログラミングする段階と、のうち少なくとも1つを前記マルチプル連続撮影動作に含み、前記連続撮影イメージデータフラグは、CMD23命令のcontext IDであって、前記ホストから前記MMCに伝送され、前記連続撮影イメージデータは、CMD25命令のデータであって、前記ホストから前記MMCに伝送される。

#### 【0011】

前記フラッシュ保存装置の動作方法は、前記マルチプル連続撮影動作のうち少なくとも1つを実行した後、移送命令を前記ホストから前記フラッシュ保存装置に伝送する段階と、前記専用連続撮影イメージデータバッファ領域に保存された前記連続撮影イメージデータの一部を前記第2メモリ領域にコピーする前記移送命令に応答して移送動作を行う段階と、をさらに含む。

前記フラッシュ保存装置は、前記プロセッサと共に前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータの前記プログラミングを制御するフラッシュコントローラとページバッファとを含む。前記移送命令は、連続撮影動作の実行後、一定の時間が経過した後、前記ホストから前記フラッシュ保存装置に伝送される。

#### 【0012】

前記ホストは、プロセッサとカメラモジュールとを含み、前記方法は、前記カメラモジュールで前記連続撮影イメージデータを生成し、前記連続撮影イメージデータのサイズを指示する連続撮影イメージデータフラグを生成し、前記プロセッサに前記連続撮影イメージデータと前記連続撮影イメージデータフラグとを提供する段階と、前記プロセッサを用いてRAMに前記連続撮影イメージデータを保存する段階と、前記連続撮影イメージデータのサイズと前記専用連続撮影イメージデータバッファ領域の残りの使用可能なメモリ領域のサイズとを比較する段階と、前記連続撮影イメージデータのサイズが、前記専用連続撮影イメージデータバッファ領域の残りの使用可能なメモリ領域のサイズよりも小さいか同じである時、前記領域割り当て情報と前記連続撮影イメージデータフラグとに応答して、前記プロセッサを用いて前記専用連続撮影イメージデータバッファ領域に前記連続撮影イメージデータをプログラミングし、そうではない時、前記プロセッサを用いて前記第2メモリ領域に前記連続撮影イメージデータをプログラミングする段階と、のうち少なくとも1つを前記マルチプル連続撮影動作に含む。

前記RAMに前記連続撮影イメージデータを保存する段階は、前記マルチプル連続撮影動作が実行される間に、前記RAMに前記連続撮影イメージデータをバッファリングし、前記連続撮影イメージデータを前記RAMから前記フラッシュメモリ装置に伝送する。

#### 【0013】

本発明の実施形態によるイメージ処理システムは、連続撮影イメージデータを生成するホストと、第1メモリ領域と第2メモリ領域とを含むメモリセルアレイを含むフラッシュ保存装置と、を含み、前記第1メモリ領域の一部は、前記連続撮影イメージデータを一時的に保存する専用連続撮影イメージデータバッファ領域であり、前記第2メモリ領域は、正常プログラム動作中に、前記ホストから前記フラッシュ保存装置に提供される正常データを保存し、前記第1メモリ領域は、第1速度で行われる前記正常プログラム動作を含むデータアクセス動作を支援し、前記第2メモリ領域は、前記第1速度よりも遅い第2速度で行われるデータアクセス動作を支援する。

#### 【発明の効果】

#### 【0014】

本発明の実施形態による連続撮影イメージデータを処理する方法と装置は、連続撮影動作中に、連続撮影イメージデータをバッファリングするために使われるホスト-提供RAMのデータ保存能力と無関係に、保存装置に高解像度を有する撮影イメージデータをライトする許容可能なライト性能を保証することができる。

#### 【図面の簡単な説明】

#### 【0015】

【図1】本発明の実施形態による1つ以上の連続撮影モードでの動作が可能なイメージ処理システムのブロック図。

10

20

30

40

50

【図2】図1に示されたフラッシュ保存装置のブロック図。

【図3】本発明の実施形態によって図1に示されたイメージ処理システムによって行われる連続撮影動作を説明するフローチャート。

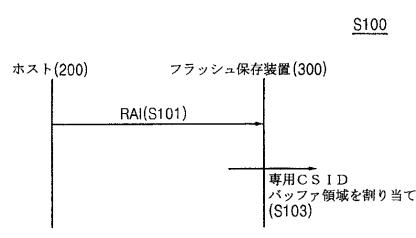

【図4】図3の連続撮影を行う方法の初期化段階(ステップS100)の一実施形態を説明するデータフローチャート。

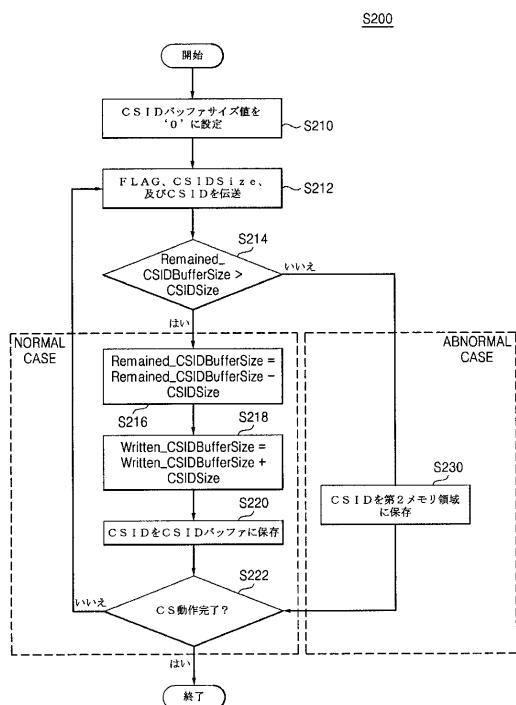

【図5】図3の連続撮影を行う方法の連続撮影動作段階(ステップS200)の一実施形態を説明するフローチャート。

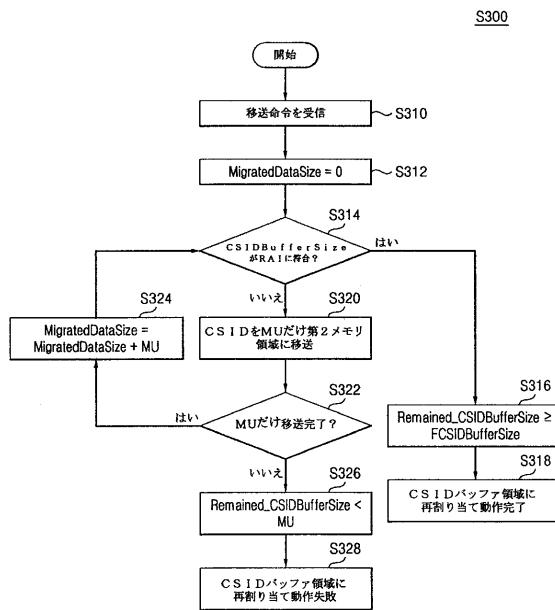

【図6】図3の連続撮影を行う方法の移送動作段階(ステップS300)の一実施形態を説明するフローチャート。

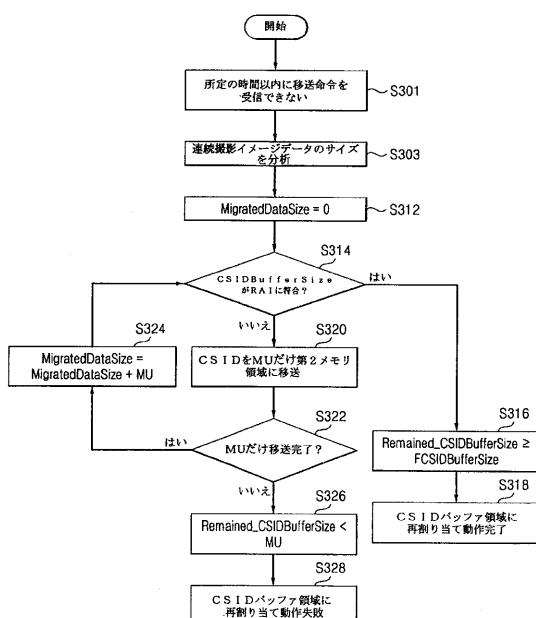

【図7】図3の連続撮影を行う方法の移送動作段階(ステップS300)の他の実施形態を説明するフローチャート。

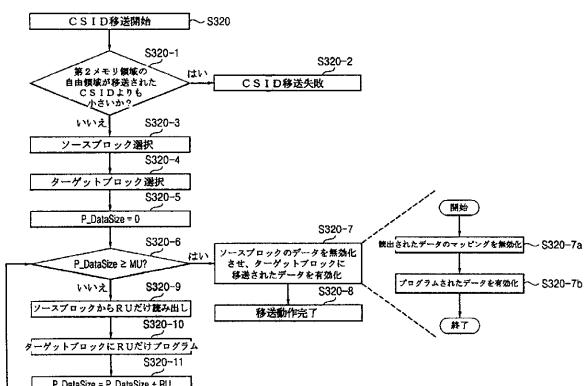

【図8】図6と図7との320段階、すなわち、専用CSDバッファ領域から第2メモリ領域に連続撮影イメージデータを移送する段階を説明するフローチャート。

【図9】本発明の実施形態によって連続撮影動作後にアドレスマッピングを説明するブロック図(その1)。

【図10】本発明の実施形態によって連続撮影動作後にアドレスマッピングを説明するブロック図(その2)。

【発明を実施するための形態】

【0016】

以下、添付した図面を参照して、本発明を詳しく説明する。

図1は、本発明の実施形態による1つ以上の連続撮影モードでの動作が可能なイメージ処理システムのブロック図を示す。イメージ処理システム100は、ホスト200とフラッシュ保存装置300とを含む。イメージ処理システム100は、パソコン、ラップトップコンピュータ、スマートフォン、タブレットPC、またはデジタルカメラなどの内にまたは一部として具現可能である。

ホスト200は、“連続撮影イメージデータ(continuous shooting image data)”または“CSD”を生成する1つまたはそれ以上の連続撮影モードで動作する。連続撮影モードは、バーストモード(burst mode)、マルチショットモード(multi-shot mode)または連続ビデオモード(continuous video mode)などを含みうる。

【0017】

実施形態によって、連続撮影モードで動作中にホスト200によって生成された連続撮影イメージデータは、フラッシュ保存装置300にリアルタイム(on-the-fly)に伝送することができる。本明細書で、‘リアルタイム’とは、データがリアルタイムで生成されるやいなや、処理されることを意味する。

ホスト200は、ROM(Read Only Memory)210、プロセッサ220、カメラモジュール230、RAM240、フラッシュ保存装置インターフェースコントローラ250、及びユーチューブインターフェース260を含む。ホスト200は、システム・オン・チップ(System on Chip; SoC)製造技術として具現可能である。連続撮影モードの間に、カメラモジュール230は、連続撮影イメージデータ(CSD)を多様に生成することができる。

【0018】

ROM210は、ホスト200の動作を制御するために必要なOS(Operation System)の関連ファイル、1つ以上のアプリケーションを定義するデータまたはホストファームウェア(host firmware)を保存する。前記OS及び/または前記ホストファームウェアは、ROM210からRAM240にロードされた後、プロセッサ220の制御によって実行可能である。ROM210は、1つ以上の不揮発性メモリ装置を使って具現可能である。

【0019】

OS及び/またはホストファームウェアの指示によって、プロセッサ220は、カメラ

10

20

30

40

50

モジュール230、カメラモジュール230とRAM240との相互動作、フラッシュ保存装置インターフェースコントローラ250、及びユーザインターフェース260の動作を制御するために使われる。

#### 【0020】

RAM240は、揮発性メモリ装置、例えば、DRAM(Dynamic RAM)、SRAM(Static RAM)、T-RAM(Thyristor RAM)、Z-RAM(Zero Capacitor RAM)、またはTTRAM(Twin Transistor RAM)などとして具現可能である。図1を参照すると、RAM240は、リアルタイムで連続撮影イメージデータ(CSID)をバッファリングすることができるDRAMであると仮定することができる。

10

#### 【0021】

連続撮影モード初期化の間に、プロセッサ220は、フラッシュ保存装置インターフェースコントローラ250を通じてフラッシュ保存装置300に伝送される“領域割り当て情報(RAI)”の生成に使われる。領域割り当て情報(RAI)は、定義されたイメージ解像度(image resolution)、連続撮影フレームレート(continuous shooting frame rate)、連続撮影イメージデータ(CSID)バッファ領域サイズ値、及び連続撮影時間のうち少なくとも1つを含みうる。

#### 【0022】

特定の領域割り当て情報(RAI)は、イメージ処理システム100またはイメージ処理システム100の統合ホストの製造者によってあらかじめ決定されるか、またはユーザインターフェース(User Interface; UI)260を通じてイメージ処理システム100に伝送されるユーザ入力と一致するように定義されうる。領域割り当て情報(RAI)の規定と使用は、以下、複数種の追加細部事項で説明されうる。

20

ホスト200は、UI260の少なくとも一部をディスプレイするためのディスプレイ(図示せず)をさらに含みうる。このディスプレイは、TFT-LCD(Thin Film Transistor-Liquid Crystal Display)、LED(Light Emitting Diode)ディスプレイ、OLED(Organic LED)ディスプレイ、AMOLED(Active-Matrix OLED)ディスプレイ、またはフレキシブルディスプレイ(Flexible Display)として具現可能である。

30

#### 【0023】

連続撮影モードの間に、プロセッサ220は、フラッシュ保存装置300にプロセッサ220によって伝送される特定のデータが連続撮影イメージデータ(CSID)であることを指示する連続撮影イメージデータフラグ(FLAG)を生成することができる。さらに、連続撮影モードが終了した後、またはほぼ終了した後、プロセッサ220は、移送命令(Migration Command; MC)を生成し、移送命令(MC)をフラッシュメモリ保存インターフェースコントローラ250を通じてフラッシュ保存装置300に伝送することができる。

#### 【0024】

移送命令(MC)は、連続撮影イメージデータフラグ(FLAG)及び/または領域割り当て情報(RAI)と共に、または個別的に伝送することができる。移送命令(MC)が、フラッシュメモリインターフェースコントローラ250によって受信されれば、移送命令(MC)は、連続撮影イメージデータの保存のための専用フラッシュ保存装置300の領域(すなわち、連続撮影イメージデータ領域)を確保または割り当てるために解析される。

40

#### 【0025】

場合I(CASEI)のように、カメラモジュール230によって提供された連続撮影イメージデータ(CSID)は、フラッシュ保存装置インターフェースコントローラ250を通じてカメラモジュール230からフラッシュ保存装置300に直接伝送することができる。しかし、場合II(CASEII)のように、カメラモジュール230から提供

50

された連続撮影イメージデータ（C S I D）は、R A M 2 4 0で臨時バッファリングされた後、フラッシュ保存装置インターフェースコントローラ2 5 0を通じてフラッシュ保存装置3 0 0に間接伝送することができる。

#### 【0 0 2 6】

バッファリングされた連続撮影イメージデータ（C S I D）は、プロセッサ2 2 0の制御によってフラッシュ保存装置インターフェースコントローラ2 5 0を通じてR A M 2 4 0からフラッシュ保存装置3 0 0に提供されうる。

場合I（C A S E I）または場合II（C A S E I I）で、イメージ処理システム1 0 0は、リアルタイムで、そして、相対的に高いデータ処理速度で不揮発性メモリ装置3 0 0への連続撮影イメージデータ（C S I D）の保存に使われる。

10

#### 【0 0 2 7】

すなわち、図1のホスト2 0 0は、連続撮影イメージデータ（C S I D）を保存するために使われるR A M 2 4 0の一部が完全にいっぱいになるまで待機せずとも、プロセッサ2 2 0とフラッシュ保存装置インターフェースコントローラ2 5 0とを用いてリアルタイムでフラッシュ保存装置3 0 0に連続撮影イメージデータ（C S I D）を保存することができる。

その結果、ホスト2 0 0は、R A M 2 4 0によって提供された特別な連続撮影イメージデータ保存容量と無関係に、カメラモジュール2 3 0によって提供された連続撮影イメージデータ（C S I D）をリアルタイムでフラッシュ保存装置3 0 0に処理して保存することができる。

20

#### 【0 0 2 8】

したがって、与えられた連続撮影モードと与えられたデータ解像度とで動作するためのホスト2 0 0の能力は、R A M 2 4 0のデータ保存能力またはR A M 2 4 0の利用可能なデータ保存容量によって制限されるものではない。このような結果は、R A M 2 4 0のサイズと使用によって、それらのデータ処理能力が制限される従来の特定データ処理システムでの連続撮影モードの動作の規定方法と相当比較される。

したがって、図1のようなイメージ処理システムは、連続撮影モード機能をユーザにさらに有用に提供することができる。

#### 【0 0 2 9】

図1では、説明の便宜上、ホスト2 0 0が、場合I（C A S E I）と場合II（C A S E I I）とのうち何れか1つを選択的に実行できるように図示されているが、実施形態によって、ホスト2 0 0は、場合I（C A S E I）のみを実行するか、または場合II（C A S E I I）のみを実行することができる。

30

図1を再び参照すると、フラッシュ保存装置インターフェースコントローラ2 5 0は、フラッシュ保存装置3 0 0とホスト2 0 0との間でライト（w r i t e）動作中に、“ライトデータ”を通信し、リード（r e a d）動作中に、“リードデータ”を通信することができる。

#### 【0 0 3 0】

また、フラッシュ保存装置インターフェースコントローラ2 5 0は、場合IIによって、プロセッサ2 2 0から連続撮影イメージデータ（C S I D）、領域割り当て情報（R A I）、フラグ（F L A G）、及び／または移送命令（M C）をフラッシュ保存装置3 0 0への伝送に使われる。また、フラッシュ保存装置インターフェースコントローラ2 5 0は、場合Iによって、カメラモジュール2 3 0から連続撮影イメージデータ（C S I D）をフラッシュ保存装置3 0 0に伝送しうる。

40

#### 【0 0 3 1】

イメージ処理システム1 0 0は、ユーザがU I 2 6 0を通じて1つ以上の“解像度パラメータ”（例えば、イメージ解像度、連続撮影フレームレート、及び／または連続撮影時間）を入力することを許容することができる。選択的に、1つ以上の解像度パラメータは、イメージ処理システム1 0 0の製造者によってあらかじめ設定しうる。他の例では、プロセッサ2 2 0は、1つ以上の解像度パラメータによって領域割り当て情報（R A I）を

50

生成するのに使われる。

【0032】

フラッシュ保存装置300は、フラッシュメモリ装置またはフラッシュメモリ基盤のデータ保存装置として多様に具現可能である。フラッシュ保存装置300は、イメージ処理システム100内に内蔵されるか、集積され、エンベデッドマルチメディアカード(eMMC)のようにイメージ処理システム100に着脱可能である。フラッシュ保存装置300は、SSD(Solid State Drive)、UFS(Universal Flash Storage)、SDカード(Secure Digital card)、USBフラッシュドライブ(Universal Serial Bus flash drive)、SIM(Subscriber Identification Module)カード、またはUSIM(Universal Subscriber Identity Module)カードであり得る。

10

フラッシュメモリタイプ保存装置は、図1の実施形態と仮定されうるが、他のタイプの保存装置は、フラッシュメモリの代わりをするか、付け加えて使用される。

【0033】

実施形態によって、図1のフラッシュ保存装置300は、EEPROM(Electrically Erasable Programmable Read-Only Memory)、MRAM(Magnetic RAM)、スピントルクMRAM(Spin-Transfer Torque MRAM)、Conductive bridging RAM(CBRAM)、FeRAM(Ferroelectric RAM)、PRAM(Phase change RAM)、抵抗メモリ(Resistive RAM: RRAM(登録商標)またはReRAM)、ナノチューブRRAM(Nanotube RRAM)、ポリマRAM(Polymer RAM: PoRAM)、ナノ浮遊ゲートメモリ(Nano Floating Gate Memory: NFGM)、ホログラフィックメモリ(Holographic Memory)、分子電子メモリ素子(Molecular Electronics Memory Device)、または絶縁抵抗変化メモリ(Insulator Resistance Change Memory)で代替されうる。

20

【0034】

フラッシュ保存装置300は、1つ以上のメモリセルアレイに配列されるフラッシュメモリセルを含む。このメモリセルは、メモリセルアレイ内に指定された領域によってシングルレベルデータ技術(single level data techniques)及び/またはマルチレベル(Multi-Level)データ技術を使ってアクセスすることができる。

30

フラッシュ保存装置300は、シングルレベルメモリセル及び/またはトリプルレベルセル(Triple Level Cells; TLCs)及び/またはクワッドレベルセル(Quad Level Cells; QLCs)のようなマルチレベルメモリセル(Multi-Level Memory Cells)を含みうる。

【0035】

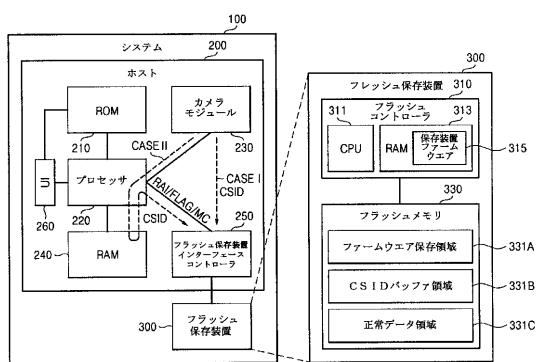

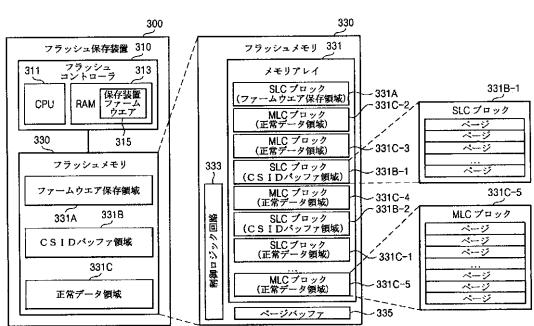

図2は、図1に示されたフラッシュ保存装置のブロック図を示す。図1と図2とを参照すると、フラッシュ保存装置300は、フラッシュコントローラ310とフラッシュメモリ330とを含む。

40

連続撮影(CS)モードで、フラッシュコントローラ310は、メモリセルアレイ331内の多様なメモリ領域の定義と割り当て、連続撮影イメージデータ(CSID)の保存、及び移送命令(MC)の受信による移送動作の実行を制御することができる。例えば、フラッシュコントローラ310は、ホスト200から出力された移送命令(MC)を解析し、フラッシュメモリ330による相応する移送命令の実行を制御することができる。すなわち、フラッシュコントローラ310は、連続撮影イメージデータ(CSID)が割り当てされた連続撮影イメージデータメモリ領域に保存される間に、“正常連続撮影イメージデータ時間区間”のモニタに使われる。

50

## 【0036】

フラッシュコントローラ310は、正常連続撮影イメージデータ時間区間によって移送動作の実行を制御することができる。フラッシュコントローラ310は、CPU(Central Processing Unit)311とRAM313とを含む。CPU311は、ファームウェア315としてRAM313に実行のためにロードされるが、図1のROM21及び/またはフラッシュメモリ330のソフトウェアによって指示されて、フラッシュ保存装置300の全般的な動作を制御する。

図1のフラッシュメモリ330は、メモリアレイ331、制御ロジック回路333、及びページバッファ335を追加的に含む。

## 【0037】

図2で、フラッシュメモリ330は、不揮発性ファームウェア保存領域331A、連続撮影イメージデータ(CSID)バッファ領域331B、及び正常データ領域331Cとして割り当てられたメモリ領域を含む。

ファームウェア保存領域331AとCSIDバッファ領域331Bのそれぞれは、SLCを含みうる。逆に、正常データ領域331Cは、SLC及び/またはMLCを含みうる。

## 【0038】

すなわち、ファームウェア保存領域331AとCSIDバッファ領域331Bとのデータアクセス(access)速度(例えば、プログラミング(programming)速度)は、正常データ領域331Cのデータアクセス速度よりも相対的に速い。

したがって、ファームウェア保存領域331AとCSIDバッファ領域331Bは、第1速度で実行されるデータアクセス動作を支援することができるフラッシュメモリ330の第1メモリ領域を形成し、正常データ領域331Cは、第2速度で実行されるデータアクセス動作を支援することができるフラッシュメモリ330の第2メモリ領域を形成する。ここで、第1速度は、第2速度よりも速い。

## 【0039】

図2で、第1メモリ領域の少なくとも一部は、連続撮影イメージデータ(CSID)のみを保存するために専用CSIDバッファ領域に指定されて動作することができる。逆に、第2メモリ領域は、正常に行われたリード動作とライト動作とによって生成された正常データ(例えば、ユーザ定義データ、ペイロード(payload)データなど)を保存するために使われる。

図2で、ファームウェア保存領域331A、CSIDバッファ領域331B、及び正常データ領域331Cのそれぞれは、1つまたはそれ以上の割り当てられたメモリブロック(memory block)を含み、各メモリブロックは、割り当てられた領域によってSLCまたはMLCを含みうる。

## 【0040】

フラッシュコントローラ310によって実行される保存装置ファームウェア315は、ホスト200から受信された領域割り当て情報(RAI)を解析することができる。領域割り当て情報(RAI)に応答して、フラッシュコントローラ310は、フラッシュメモリ330の各指定された領域に1つまたはそれ以上のブロック(例えば、331A、331B-1、331B-2、及び331C-1~331C-5)を割り当てる。例えば、各ブロック331A、331B-1、及び331B-2は、相対的に速い速度で実行される1つまたはそれ以上のアクセス動作を支援するように具現されたSLCを含むブロックと仮定する。したがって、フラッシュコントローラ310は、ブロック331Aをファームウェア保存領域331Aに割り当て、各ブロック331B-1、331B-2を専用CSIDバッファ領域に割り当てる。

## 【0041】

逆に、フラッシュコントローラ310は、相対的に遅い速度で実行される1つまたはそれ以上のアクセス動作を支援するように具現されたMLCを含む各ブロック(331C-1~331C-5まで)を正常データ領域331Cに割り当てる。

10

20

30

40

50

図2で、各SLCブロックと各MLCブロックは、複数のページ(pages)を含みます。実施形態によって、特定のページは、共通ワードライン(common word line)に沿って整列された複数のメモリセル(例えば、複数のSLCまたは複数のMLC)によって形成されます。他の実施形態によって、ブロック(block)またはメモリブロックは、フラッシュメモリ装置のイレーズ(erase)単位であり、ページ(page)は、フラッシュメモリ装置のライト(プログラム)単位またはリード単位を意味する。

#### 【0042】

フラッシュコントローラ310の制御によって、コントロールロジック回路333は、フラッシュメモリ330の選択された複数のメモリセルに直接データアクセス動作(リード、ライト(プログラム、及び/または削除動作))の実行を制御することができる。

ページバッファ335は、データタイプ及び/または実行される動作のタイプによって、ホスト200から受信したプログラムデータ(すなわち、正常ライトデータまたは連続撮影イメージデータ(CSID))をフラッシュメモリ330の第1メモリ領域または第2メモリ領域にプログラムすることができる。

#### 【0043】

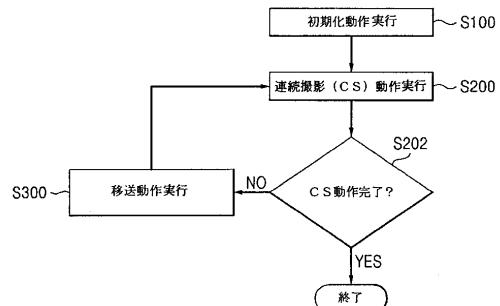

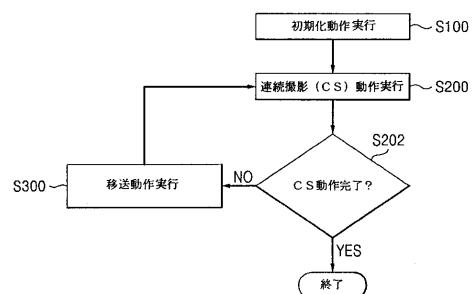

図3は、本発明の実施形態によって、図1に示されたイメージ処理システムによって行われる連続撮影動作を説明するフローチャートである。図3の方法は、イメージ処理システム100の初期化動作を行う段階(ステップS100)と、連続撮影(CS)動作を行う段階(ステップS200)と、連続撮影(CS)動作が長期間行われる場合(ステップS202=NO)と、移送動作を行う段階(ステップS300)と、連続撮影(CS)動作が完了する場合、終了する段階(ステップS202=YES)と、を含む。各段階は、以下、関連した実施形態によって詳しく説明される。

#### 【0044】

図4は、図3の連続撮影を行う方法の初期化段階(ステップS100)の一実施形態を説明するデータフローチャートである。図1、図2、図3及び図4を参照すると、イメージ処理システム100は、フラッシュ保存装置インターフェースコントローラ250を通じてプロセッサ220からフラッシュコントローラ310に領域割り当て情報(RAI)を伝送する初期化(ステップS100)を行う(ステップS101)。

領域割り当て情報(RAI)に応答して、フラッシュコントローラ310で実行される保存装置ファームウェア315は、受信された領域割り当て情報(RAI)を解析し、1つまたはそれ以上のSLCメモリブロックを専用CSIDバッファ領域に割り当てる(ステップS103)。

#### 【0045】

例えば、領域割り当て情報(RIA)による解像度パラメータとして、フレーム当たり与えられたイメージ解像度が、8Mbytesであり、秒当たり連続撮影フレームレートが、10フレームであり、連続撮影時間が、2秒である時、フラッシュコントローラ310は、連続撮影イメージデータ(CSID)を保存するための専用CSIDバッファ領域のために最小160Mbytes(=8Mbytes\*10/s\*2s)を割り当てる(ステップS103)。

#### 【0046】

領域割り当て情報(RAI)は、レジスタまたはフラッシュメモリ330内で定義された位置に保存することができる。しかし、フラッシュ保存装置300が、extented card specific data register(EXT\_CSDレジスタ)を含むeMMCである場合、領域割り当て情報(RAI)は、ホスト200から提供されたSWITCH命令に基づいて、EXT\_CSDレジスタのVENDOR\_SPECIFIC\_FIELD FIELDに保存することができる。

すなわち、専用CSIDバッファ領域は、フラッシュメモリ330に保存された領域割り当て情報(RAI)またはEXT\_CSDレジスタのVENDOR\_SPECIFIC\_FIELD FIELDによって割り当てられる。

10

20

30

40

40

50

## 【0047】

本明細書は、eMMCの構造、規約、及び／または動作条件を定義及び／または規定するJEDEC (Joint Electron Devices Engineering Council) 標準を参照する。

前記標準は、<http://www.jedec.org>に依頼して容易に得られる。例えば、eMMC標準、2012年6月(例えば、JESD84-B451)に発行されたバージョン(version)4.51は、本発明の実施形態を理解するための有用な多くの用語と技術的定義とを含んでいる。

## 【0048】

図5は、図3の連続撮影を行う方法の連続撮影動作段階(ステップS200)の一実施形態を説明するフローチャートである。図1、図2、図3及び図5を参照すると、連続撮影(CSID)動作が始まれば、フラッシュメモリ330で専用CSIDバッファ領域の現在サイズを定義する“連続撮影イメージデータ(CSID)バッファ領域サイズ値”が、0に設定される(ステップS210)。

10

## 【0049】

ホスト200は、伝送されるデータが連続撮影イメージデータ(CSID)であることを指示する連続撮影イメージデータフラグ(FLAG)を伝送しうる。また、ホスト200は、フラッシュメモリ330のCSIDバッファ領域に保存される連続撮影イメージデータ(CSID)と共に連続撮影イメージデータ(CSID)のサイズを定義する連続撮影イメージデータサイズ値(CSIDSize)を伝送しうる(ステップS212)。

20

## 【0050】

CSIDフラグ(FLAG)、CSIDサイズ値(CSIDSize)、及び連続撮影イメージデータ(CSID)を受信すれば、CSIDサイズ値(CSIDSize)によって連続撮影イメージデータ(CSID)を専用連続撮影イメージデータ領域にライトする連続撮影イメージデータライト動作が実行されるように、フラッシュコントローラ310は、フラッシュメモリ330の動作を制御することができる。

20

## 【0051】

連続撮影イメージデータライト動作を実行するために、フラッシュメモリコントローラ310は、現在計算されたCSIDバッファ領域の残り(remaining)のメモリ領域のサイズを指示する残りのCSIDバッファ領域値(remaining\_CSIDBuffferSize)が受信されたCSIDサイズ値(CSIDSize)よりも大きいかを判断することができる(ステップS214)。

30

## 【0052】

非正常な場合(ABNORMAL CASE)、すなわち、段階S214がいいえ(NO)であり、連続撮影イメージデータバッファ領域の残りのメモリ領域が、連続撮影イメージデータ(CSID)の保存に不足すれば、入力された連続撮影イメージデータ(CSID)は、第2メモリ領域、例えば、図2の正常データ領域331Cに保存しなければならない(ステップS230)。

30

## 【0053】

たとえ非正常な場合(ABNORMAL CASE)に、専用連続撮影イメージデータバッファ領域が受信された連続撮影イメージデータ(CSID)を保存できないよう小さな場合でも、ホスト200は、連続撮影イメージデータ(CSID)をフラッシュメモリ300に伝送しうる。すなわち、図1と図2とを参照して説明した実施形態と一貫性のために、フラッシュコントローラ310は、受信された連続撮影イメージデータ(CSID)が第1メモリ領域の代わりに、フラッシュメモリアレイ331で定義された第2メモリ領域に保存されるようにフラッシュメモリ330を制御することができる。

40

## 【0054】

非正常な場合(ABNORMAL CASE)は、例えば、初期連続撮影動作に関連した移送動作が実行される前に、その次の連続撮影動作が行われる時、入って来る(incoming)連続撮影イメージデータ(CSID)が、現在定義された専用CSIDバッ

50

ファ領域よりも大きい時、または連続撮影動作の頻度が増加する時に発生することがある。

しかし、正常な場合 (N O R M A L C A S E ) で、 C S I D バッファ領域の残り ( または、残存 ) のメモリ領域のサイズが、連続撮影イメージデータ ( C S I D ) の保存に適切な時 ( S 2 1 4 = はい ) には、フラッシュメモリコントローラ 3 1 0 は、現在連続撮影イメージデータバッファ領域値から連続撮影イメージデータサイズ値を減算して、新たな残りの連続撮影イメージデータバッファ領域値 ( R e m a i n e d \_ C S I D B u f f e r S i z e ) を計算することができる ( ステップ S 2 1 6 ) 。

#### 【 0 0 5 5 】

引き続き、フラッシュメモリ 3 3 0 は、現在使用中である C S I D バッファ領域の書き込まれた領域のサイズ値 ( W r i t t e n \_ C S I D B u f f e r S i z e ) を計算することができる。 C S I D バッファ領域の書き込まれた領域の新たな値は、 C S I D バッファ領域の書き込まれた領域の現在値 ( W r i t t e n \_ C S I D B u f f e r S i z e ) と連続撮影イメージデータ ( C S I D ) のサイズ値 ( C S I D S i z e ) とを加えて計算されうる ( ステップ S 2 1 8 ) 。

#### 【 0 0 5 6 】

フラッシュメモリ 3 3 0 は、フラッシュメモリコントローラ 3 1 0 の制御によって第 1 メモリ領域 3 3 1 B 内の専用 C S I D バッファ領域に連続撮影イメージデータ ( C S I D ) を保存することができる ( ステップ S 2 2 0 ) 。そして、ホスト 2 0 0 は、連続撮影 ( C S ) 動作が完了したか否かを判断することができる ( ステップ S 2 2 2 ) 。もし、完了していない場合 ( S 2 2 2 = いいえ ) 、連続撮影 ( C S ) 動作が完了するまで前述した動作が続く。

#### 【 0 0 5 7 】

非正常な場合 ( A B N O R M A L C A S E ) と正常な場合 ( N O R M A L C A S E ) とで説明したように、専用 C S I D バッファ領域で利用可能な領域のサイズが入って来る連続撮影イメージデータ ( C S I D ) のサイズよりも大きな場合、フラッシュコントローラ 3 1 0 は、連続撮影イメージデータ ( C S I D ) が第 1 メモリ領域 3 3 1 B の専用 C S I D バッファ領域に保存されるようにフラッシュメモリ 3 3 0 を制御することができる。

#### 【 0 0 5 8 】

それ以外の場合、フラッシュコントローラ 3 1 0 は、専用 C S I D バッファ領域以外の他の領域、例えば、フラッシュメモリ 3 3 0 の第 2 メモリ領域 3 3 1 C の正常データ領域に連続撮影イメージデータ ( C S I D ) が保存されるようにフラッシュメモリ 3 3 0 を制御することができる。

本発明の実施形態によって、フラッシュ保存装置 3 0 0 が、 e M M C を用いて具現される時、連続撮影イメージデータフラグ ( F L A G ) は、命令 C M D 2 3 を用いて伝送され、連続撮影イメージデータ ( C S I D ) は、命令 ( C M D 2 5 ) を用いて伝送することができる。

#### 【 0 0 5 9 】

図 6 は、図 3 の連続撮影を行う方法の移送動作段階 ( ステップ S 3 0 0 ) の一実施形態を説明するフローチャートである。図 6 の再割り当て ( r e - a l l o c a t i o n ) 動作は、イメージ処理システムによって実行されるマルチプル連続撮影 ( C S ) 動作であって、イメージ処理システムの初期化動作中に、またはリアルタイムで行われる。

図 1 、図 2 、図 3 及び図 6 を参照すると、再割り当て動作は、ホストの連続撮影動作中に、容認されるライト性能を保持または保証するために、専用領域バッファ領域 ( C S I D B u f f e r ) を必須的に初期化する。ここで、初期化は、 C S D I バッファ領域を空に ( e m p t y ) することを含む。すなわち、ホスト 2 0 0 によって連続撮影 ( C S ) 区間の間に、マルチプル、すなわち、連続して実行される連続撮影 ( C S ) 動作が行われる。

#### 【 0 0 6 0 】

10

20

30

40

50

マルチプル、すなわち、連続して実行される連続撮影（CS）動作は、フラッシュ保存装置300と通信する1つまたはそれ以上の移送命令を含みうる（ステップS310）。ここで、受信した領域割り当て情報（RAI）によって定義された専用CSIDバッファ領域のサイズによって、ホスト200は、移送命令生成のタイミング（timing）を調節することができる。

#### 【0061】

説明の便宜上、連続して実行される連続撮影（CS）動作によって生成された連続撮影イメージデータの各ブロックのサイズは、同一であると仮定する。したがって、フラッシュコントローラ310は、移送命令が受信されれば、移送データユニット（簡単に、移送ユニット（MU））サイズ（MigratedDataSize）を“0”に初期化する（ステップS312）。

そして、フラッシュコントローラ310は、専用CSIDバッファ領域の現在割り当てられたサイズ（CSIDBufferSize）が受信された領域割り当て情報（RAI）に符合するか否かを判断する（ステップS314）。

#### 【0062】

連続撮影（CS）動作中に（S314＝はい）、専用CSIDバッファ領域のサイズが、ライト性能を保証するほど十分な時、すなわち、現在連続撮影動作の実行後に専用CSIDバッファ領域の残りのメモリ領域のサイズ（Remained\_CSIDBufferSize）が、次の連続撮影動作の実行後に残っている専用CSIDバッファ領域のメモリ領域のサイズ（FCSIDBufferSize）と少なくとも同じか、それより大きい時、専用CSIDバッファ領域のメモリ領域再割り当て動作は完了する（ステップS318）。

#### 【0063】

すなわち、現在連続撮影（CS）動作の実行後の専用CSIDバッファ領域の利用可能なメモリ領域の現在残っているサイズ（Remained\_CSIDBufferSize）が、連続撮影（CS）動作のシーケンス（sequence）で次の連続撮影（CS）動作の実行に必要なメモリ領域のサイズ（FCSIDBufferSize）と同じか大きい時、ライト性能は、許容レベルを保持し、この時点で、連続撮影動作のシーケンスに関連したメモリ領域再割り当ては、これ以上必要ない。

#### 【0064】

しかし、専用CSID領域のサイズ（CSIDBufferSize）が、許容されたライト性能の保証に不十分な時（S314＝いいえ）、すなわち、残りのメモリ領域のサイズ（Remained\_CSIDBufferSize）が、現在領域割り当て情報（RAI）の観点と専用CSIDバッファ領域に関連した現在連続撮影動作と次の連続撮影動作に必要なメモリ領域のサイズ（FCSIDBufferSize）よりも小さい時、専用CSIDバッファ領域に現在保存された連続撮影イメージデータ（CSID）の移送ユニット（MU）は、専用CSIDバッファ領域で残りの利用可能なメモリ領域のサイズを増加させるために、すなわち、残っているメモリ領域のサイズ（Remained\_CSIDBufferSize）を増加させるために、専用CSIDバッファ領域から第2メモリ領域331Cにコピーされうる（ステップS320）。

#### 【0065】

専用CSIDバッファ領域から連続撮影イメージデータ（CSID）移送が完了すれば（ステップS322＝はい）、移送された連続撮影イメージデータの累積サイズ（MigratedDataSize）は、専用CSIDバッファ領域からコピーされた連続撮影イメージデータ（CSID）の実際量によって移送ユニット（MU）だけ増加する（ステップS324）。

#### 【0066】

再割り当て動作の段階（ステップS314～ステップS324）は、専用CSIDバッファ領域の残りの利用可能なメモリ領域のサイズが連続撮影動作のシーケンスで進行する連続撮影動作の許容可能なライト性能を十分に保証できるまで反復されうる。しかし、専

10

20

30

40

50

用 C S I D バッファ領域の残りのメモリ領域のサイズが、移送ユニット ( M U ) よりも小さければ、専用 C S I D バッファ領域に関連した再割り当て動作は失敗となる ( ステップ S 3 2 8 ) 。

#### 【 0 0 6 7 】

図 7 は、図 3 の連続撮影を行う方法の移送動作段階 ( ステップ S 3 0 0 ) の他の実施形態を説明するフローチャートである。図 7 の方法は、所定の時間以内に移送命令 ( M C ) を受信することを除けば、図 6 の方法と実質的に同一であり、図 7 の方法は、所定の時間の間に、移送命令を受信しないと仮定し ( ステップ S 3 0 1 ) 、許容可能なライト性能を保証するために、現在連続撮影イメージデータ ( C S I D ) のサイズを分析することが必要である ( ステップ S 3 0 3 ) 。

10

#### 【 0 0 6 8 】

すなわち、ホスト 2 0 0 が、所定の時間以内にフラッシュ保存装置 3 0 0 に移送命令を伝送しない時、フラッシュ保存装置 3 0 0 は、移送命令の受信に無関係に、ホスト 2 0 0 から伝送された連続撮影イメージデータ ( C S I D ) のサイズを分析し、該分析の結果によって、移送命令の実行如何を決定することができる ( ステップ S 3 0 3 ) 。

したがって、最後の連続撮影動作を含むマルチプル連続撮影動作が、ホスト 2 0 0 によって行われる時、最後の連続撮影動作の結果として、ホスト 2 0 0 によって提供され、専用 C S I D バッファ領域に書き込まれた連続撮影イメージデータ ( C S I D ) は、所定の時間以内に移送命令が受信されないとしても、第 2 メモリ領域にフラッシュ保存装置 3 0 0 によってコピーされうる。

20

#### 【 0 0 6 9 】

図 6 と図 7 とを参考にして説明したように、移送動作は、ホスト 2 0 0 から受信した移送命令 ( M C ) に応答して、または連続撮影動作の実行後、所定の時間の経過に応答して、フラッシュ保存装置 3 0 0 によって行われる。

図 8 は、図 6 と図 7 との 3 2 0 段階、すなわち、専用 C S I D バッファ領域から第 2 メモリ領域に連続撮影イメージデータを移送する段階を説明するフローチャートである。図 6 、図 7 、及び図 8 を参照すると、専用 C S I D バッファ領域の残りの利用可能なメモリ領域のサイズ ( R e m a i n e d \_ C S I D B u f f e r S i z e ) を増やすために、専用 C S I D バッファ領域に現在保存された連続撮影イメージデータ ( C S I D ) の移送ユニット ( M U ) は、専用 C S I D バッファ領域から第 2 メモリ領域に移送されうる ( ステップ S 3 2 0 ) 。

30

#### 【 0 0 7 0 】

フラッシュコントローラ 3 1 0 は、コピーされた連続撮影イメージデータのサイズと第 2 メモリ領域の自由領域、すなわち、利用可能なメモリ領域のサイズとを比較することができる ( ステップ S 3 2 0 - 1 ) 。比較の結果、移送された連続撮影イメージデータサイズが、第 2 メモリ領域の自由領域のサイズよりも大きい時 ( S 3 2 0 - 1 = はい ) 、図 6 と図 7 との段階 ( ステップ S 3 2 0 ) 、すなわち、連続撮影イメージデータ移送段階 ( ステップ S 3 2 0 ) は失敗する ( ステップ S 3 2 0 - 2 ) 。

#### 【 0 0 7 1 】

しかし、比較の結果、コピーされた連続撮影イメージデータのサイズが、第 2 メモリ領域の自由領域のサイズよりも小さい時 ( ステップ S 3 2 0 - 1 = いいえ ) 。フラッシュコントローラ 3 1 0 は、連続撮影イメージデータ ( C S I D ) を保存する専用 C S I D バッファ領域のソースブロック ( s o u r c e \_ b l o c k ) 、例えば、 S L C ブロックを選択し ( ステップ S 3 2 0 - 3 ) 、コピーされた連続撮影イメージデータが、プログラムされる第 2 メモリ領域のターゲットブロック ( t a r g e t \_ b l o c k ) 、例えば、 M L C ブロックをさらに選択する ( ステップ S 3 2 0 - 4 ) 。

40

#### 【 0 0 7 2 】

例えば、フラッシュコントローラ 3 1 0 は、 S L C ブロック 3 3 1 C - 1 と M L C ブロック 3 3 1 C - 2 のそれぞれを選択すると仮定すれば、第 2 メモリ領域にプログラムされたデータ ( P \_ D a t a S i z e ) のサイズ値は、 0 に設定しうる ( ステップ S 3 2 0 -

50

5)。

フラッシュコントローラ310は、プログラムされたデータのサイズ(P\_DataSize)と移送ユニット(MU)とを比較することができる(ステップS320-6)。

【0073】

移送ユニット(MU)が、プログラムされたデータのサイズ(P\_DataSize)よりも大きい時、フラッシュメモリ330は、ソースブロックからリードユニット(Read Unit; RU)だけ読み取る(ステップS320-9)。したがって、フラッシュメモリ330は、ターゲットブロックにリードユニット(RU)だけ保存することができる(ステップS320-10)。移送動作は、例えば、ソースブロックからターゲットブロックにリードユニット(RU)だけを移送するか、コピーする動作は、ページバッファ335を用いる内部移送動作とフラッシュコントローラ310に含まれたSRAMを用いる外部移送動作とを含む。10

フラッシュコントローラ310は、リードユニット(RU)だけプログラムされたデータのサイズ(P\_DataSize)を増加させ、そして、ステップS320-6の段階を再び行うことができる。

【0074】

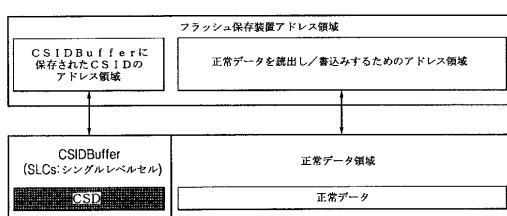

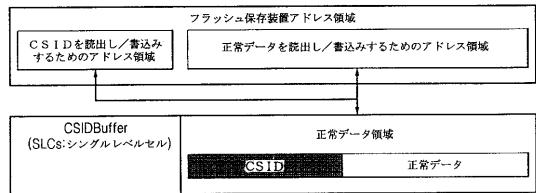

図9と図10は、本発明の実施形態によって、連続撮影動作後にアドレスマッピング(address mapping)を説明するブロック図を示す。

図8、図9、及び図10を参照すると、プログラムされたデータのサイズ(P\_DataSize)が、移送ユニット(MU)と同じか大きい時(ステップS320-6)、ソースブロックのデータは無効化され、ターゲットブロックに移送されたデータは有効化される(ステップS320-7)。図9と図10と参照すると、第1メモリ領域331Bの専用CSDバッファ領域のソースブロックから移送ユニットだけ読み取られたイメージデータに対するアドレス領域と前記ソースブロックとのアドレスマッピングは、無効化され(ステップS320-7a)、第2メモリ領域331Cのターゲットブロックに移送ユニット(MU)だけ保存されたイメージデータに対するアドレス領域と前記ターゲットブロックとのアドレスマッピングは、有効化される(ステップS320-7b)。20

【0075】

アドレスリマッピング(address remapping)が終了した後(ステップS320-7)、連続撮影イメージデータ(CSD)の一部、例えば、第1メモリ領域331Bの専用領域に保存された移送ユニット(MU)は、第2メモリ領域331Cに移送される。段階(ステップS310-1~ステップS320-8)は、第1メモリ領域331Bの専用CSDバッファ領域に保存されたあらゆる連続撮影イメージデータ(CSD)が、第2メモリ領域331Cにコピーされるまで行われる。30

【産業上の利用可能性】

【0076】

本発明は、イメージ処理システムに使われる。

【符号の説明】

【0077】

100:イメージ処理システム

40

200:ホスト

210:ROM

220:プロセッサ

230:カメラモジュール

240:RAM

250:フラッシュ保存装置インターフェースコントローラ

260:ユーザインターフェース

300:フラッシュ保存装置

310:フラッシュコントローラ

330:フラッシュメモリ

50

3 3 1 A : ファームウェア保存領域

3 3 1 B : 連続撮影イメージデータバッファ領域

3 3 1 C : 正常データ領域

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図9】

## 【図10】

---

フロントページの続き

(72)発明者 康 貞 旭

大韓民国京畿道富川市遠美区中1洞 ボーラム村 東南アパート1120棟602号

(72)発明者 鄭 云 在

大韓民国京畿道軍浦市宮内洞 白頭 漢陽アパート991棟1601号

F ターム(参考) 5B060 CB01 MM03

5C053 FA08 FA27 GB06 LA01

5C122 DA03 DA04 EA37 EA68 FA08 GA09 GA24 HA35 HA61 HA68

HA71 HA86 HA88 HB01 HB10