(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4840964号

(P4840964)

(45) 発行日 平成23年12月21日(2011.12.21)

(24) 登録日 平成23年10月14日(2011.10.14)

(51) Int.Cl.

F 1

G 01 R 33/04

(2006.01)

G 01 R 33/04

G 01 R 15/20

(2006.01)

G 01 R 15/02

H 01 F 38/28

(2006.01)

H 01 F 40/06

B

請求項の数 7 (全 19 頁)

(21) 出願番号

特願2005-240848 (P2005-240848)

(22) 出願日

平成17年8月23日 (2005.8.23)

(65) 公開番号

特開2007-57294 (P2007-57294A)

(43) 公開日

平成19年3月8日 (2007.3.8)

審査請求日

平成20年8月20日 (2008.8.20)

(73) 特許権者 000227180

日置電機株式会社

長野県上田市小泉8 1番地

(74) 代理人 100086449

弁理士 熊谷 浩明

(72) 発明者 山岸 君彦

長野県上田市大字小泉字桜町8 1番地 日

置電機株式会社内

(72) 発明者 渡辺 英雄

長野県上田市大字小泉字桜町8 1番地 日

置電機株式会社内

(72) 発明者 鈴木 康文

長野県上田市大字小泉字桜町8 1番地 日

置電機株式会社内

最終頁に続く

(54) 【発明の名称】 フラックスゲート素子および電流センサ

## (57) 【特許請求の範囲】

## 【請求項 1】

短辺部と長辺部とを矩形枠枠状に連続させてなる複数個の磁性薄片体と、その長さ方向に一定間隔をもつて配置される前記各磁性薄片体の全体を覆った際にその周縁部に余白がはみ出るように残置される面サイズの矩形形状を呈してそれぞれの両面を一体に覆う一対の絶縁内層体と、これら絶縁内層体の各外表面に對面合致させて各別に覆設される一側基板体と他側基板体とで構成される励磁ユニットと、前記一側基板体と前記他側基板体との各外表面に對面合致させて各別に覆設される一対の絶縁外層体とを少なくとも備えて前記磁性薄片体部位の別での折曲を可能に一体的に形成され、

前記磁性薄片体のそれぞれと各別に對面する位置にある一側基板体と他側基板体とのそれぞれの前記外表面には、磁性薄片体の一方の前記長辺部と他方の前記長辺部との別に各個独立にそれぞれの長さ方向に交差させ、かつ、隣接相互間を非導通として配列させた多數条のパターン層を双方でジグザグ状となる配置関係で設け、

対応関係にある前記絶縁内層体を覆うべく対向配置させた際の一側基板体の前記パターン層と他側基板体の前記パターン層とは、前記長辺部からはみ出る部位にある対面部位相互をめっきスルーホールを介して各別に導通させることで、一方の前記長辺部には1本の巻線と同等な一側励磁部を、他方の前記長辺部には1本の巻線と同等な他側励磁部をそれぞれ各別に形成するとともに、前記各一側励磁部相互を直列に、前記各他側励磁部相互を直列に各別に接続させることで、一方の前記長辺部には長い磁路長を確保できる1本の巻線と同等な一側励磁部を、他方の前記長辺部には長い磁路長を確保できる1本の巻線と同

等な他側励磁部をそれぞれ各別に形成して前記励磁ユニットとしたことを特徴とするフラックスゲート素子。

【請求項 2】

分割された一側大径コア片部と他側大径コア片部とを相互に対向配置させてなる大径磁気コア体と、該大径磁気コア体側と同心状に分割配置された一側小径コア片部と他側小径コア片部とを前記大径磁気コア体の内側に寄り添うように相互を対向配置させてなる小径磁気コア体と、これら大径磁気コア体と小径磁気コア体との間の各分割周方向に沿わせ、かつ、ギャップを介して各別に配置されるフラックスゲート素子とで構成され、

該フラックスゲート素子は、短辺部と長辺部とを矩形枠状に連続させてなる磁性薄片体と、該磁性薄片体より大きな面サイズの矩形形状を呈して前記磁性薄片体の両面に各別に覆設される一対の絶縁内層体と、これら絶縁内層体の各外表面に對面合致させて各別に覆設される一側基板体と他側基板体とで構成される励磁ユニットと、前記一側基板体と前記他側基板体との各外表面に對面合致させて各別に覆設される一対の絶縁外層体とを少なくとも備えてその長さ方向への撓曲を可能に一体的に形成するとともに、一側基板体と他側基板体とのそれぞれの前記外表面には、磁性薄片体の一方の前記長辺部と他方の前記長辺部との別に各個独立にそれぞれの長さ方向に交差させ、かつ、隣接相互間を非導通として配列させた多数条のパターン層を双方でジグザグ状となる配置関係で設け、

前記励磁ユニットは、対応関係にある前記絶縁内層体を覆うべく対向配置させた際の一側基板体の前記パターン層と他側基板体の前記パターン層とを前記長辺部からはみ出る部位にある対面部位相互をめっきスルーホールを介して各別に導通させることで、一方の前記長辺部には 1 本の巻線と同等な一側励磁部を、他方の前記長辺部には 1 本の巻線と同等な他側励磁部をそれぞれ形成してなり、

前記一側大径コア片部と前記一側小径コア片部とを含む外周から前記他側大径コア片部と前記他側小径コア片部とを含む外周へと巻回された電気信号検出のための巻線を具備させたことを特徴とする電流センサ。

【請求項 3】

大径磁気コア体と小径磁気コア体との間の各分割周方向に各別に介在配置される前記フラックスゲート素子は、前記各磁性薄片体部位が相互に重なり合うように折曲させて配置した請求項 1 に記載のフラックスゲート素子である請求項 2 に記載の電流センサ。

【請求項 4】

前記フラックスゲート素子は、前記大径磁気コア体と前記小径磁気コア体との対向面における少なくともいずれか一方の側の面に形成された凹陥部内に配置して各分割周方向に各別に介在配置させた請求項 2 または 3 に記載の電流センサ。

【請求項 5】

略環状を呈する大径磁気コア体と、該大径磁気コア体と同心状に配置される小径磁気コア体と、これら大径磁気コア体と小径磁気コア体との間に周回配置されるフラックスゲート素子とで構成され、

該フラックスゲート素子は、短辺部と長辺部とを矩形枠状に連続させてなる磁性薄片体と、該磁性薄片体より大きな面サイズの矩形形状を呈して前記磁性薄片体の両面に各別に覆設される一対の絶縁内層体と、これら絶縁内層体の各外表面に對面合致させて各別に覆設される一側基板体と他側基板体とで構成される励磁ユニットと、前記一側基板体と前記他側基板体との各外表面に對面合致させて各別に覆設される一対の絶縁外層体とを少なくとも備えてその長さ方向への撓曲を可能に一体的に形成するとともに、一側基板体と他側基板体とのそれぞれの前記外表面には、磁性薄片体の一方の前記長辺部と他方の前記長辺部との別に各個独立にそれぞれの長さ方向に交差させ、かつ、隣接相互間を非導通として配列させた多数条のパターン層を双方でジグザグ状となる配置関係で設け、

前記励磁ユニットは、対応関係にある前記絶縁内層体を覆うべく対向配置させた際の一側基板体の前記パターン層と他側基板体の前記パターン層とを前記長辺部からはみ出る部位にある対面部位相互をめっきスルーホールを介して各別に導通させることで、一方の前記長辺部には 1 本の巻線と同等な一側励磁部を、他方の前記長辺部には 1 本の巻線と同等

10

20

30

40

50

な他側励磁部をそれぞれ形成してなり、

前記一側大径コア片部と前記一側小径コア片部とを含む外周から前記他側大径コア片部と前記他側小径コア片部とを含む外周へと巻回された電気信号検出のための巻線を具備させたことを特徴とする電流センサ。

【請求項 6】

前記大径磁気コア体と前記小径磁気コア体との間に介在配置される前記フラックスゲート素子は、2周以上の連續周回が自在な長さを有する請求項5に記載の電流センサ。

【請求項 7】

前記フラックスゲート素子は、前記大径磁気コア体と前記小径磁気コア体との対向面における少なくともいずれか一方の側の面に形成された凹陥部内に収容させて周回配置した請求項5または6に記載の電流センサ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、磁気コアに囲繞される被測定導体から電流などの電気信号を検出する際に好適に用いることができるフラックスゲート素子および電流センサに関する技術である。

【背景技術】

【0002】

通常、電流センサは、被測定導体に流れる電流により磁気コア内に発生する磁束を磁気検出素子を介して検出して電圧値もしくは電流値として測定できるように形成されている。

【0003】

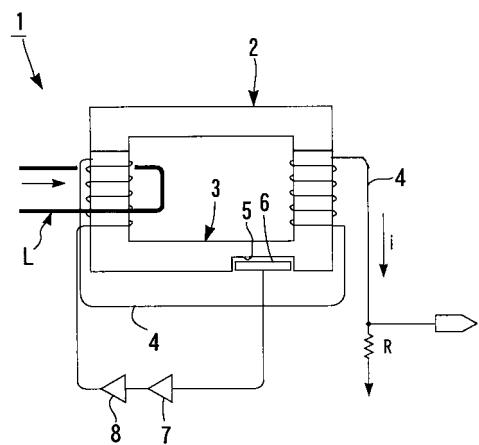

図17は、下記特許文献1に示されている分割型の電流センサと被測定導体との関係を示す説明図である。

【特許文献1】特許第3522840号公報

【0004】

同図によれば、電流センサ1は、一側コア部2と帰還巻線4を有する他側コア部3とを備え、該他側コア部3の側に設けられた凹陥部5内に磁気検出素子6を配置して形成されている。

【0005】

この場合、被測定導体Lは、開閉自在に配設されている一側コア部2側を開けることで活線状態のもとで導入することができる。また、電流センサ1側には、導入された被測定導体Lを流れる電流により磁束が発生し、該磁束は磁気検出素子6により検出される。

【0006】

しかも、その際の検出信号は、増幅回路7とバッファアンプ8とを経た後に帰還巻線4に接続され、被測定導体Lにより発生する磁束を打ち消すように帰還巻線4を流れ、その平衡時における電流をシャント抵抗Rを介して電圧値として出力することができるようになっている。

【0007】

このため、図17の電流センサ1による場合には、入力電流に比例した出力信号を得ることができるほか、ゼロフラックス動作により直線性に優れた特性を得ることもできる。

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかし、図17の電流センサ1による場合には、磁気検出素子6の位置のバランスが必ずしもよいとはいえず、増幅器動作域の周波数での被測定導体Lの位置の影響が大きくなるという不都合があった。また、被測定導体Lが磁気検出素子6に近いとプラス誤差が、遠いとマイナス誤差が発生する不安定さもあった。

【0009】

さらに、磁気検出素子6は、他側コア部3のギャップ位置に配置されているため、過電

10

20

30

40

50

流により他側コア部3側が帯磁してしまった場合にその漏れ磁束を検出してしまい、被測定導体Lに電流が流れていなきにもオフセット信号を出力してしまい、それだけ直流の直線性が悪化してしまう不具合もあった。

【0010】

本発明は、従来技術の上記課題に鑑み、磁気コア内の被測定導体の位置の如何にかかわらず安定した特性が得られるばかりでなく、帯磁しても出力にオフセット信号が現れないようにする上で有効なフラックスゲート素子および電流センサを提供することに目的がある。

【課題を解決するための手段】

【0011】

本発明は、上記目的を達成すべくなされたものであり、そのうちの第1の発明（フラックスゲート素子）は、短辺部と長辺部とを矩形枠枠状に連続させてなる複数個の磁性薄片体と、その長さ方向に一定間隔をおいて配置される前記各磁性薄片体の全体を覆った際にその周縁部に余白がはみ出るよう残置される面サイズの矩形形状を呈してそれぞれの両面を一体に覆う一対の絶縁内層体と、これら絶縁内層体の各外表面に對面合致させて各別に覆設される一側基板体と他側基板体とで構成される励磁ユニットと、前記一側基板体と前記他側基板体との各外表面に對面合致させて各別に覆設される一対の絶縁外層体とを少なくとも備えて前記磁性薄片体部位の別での折曲を可能に一体的に形成され、前記磁性薄片体のそれぞれと各別に對面する位置にある一側基板体と他側基板体とのそれぞれの前記外表面には、磁性薄片体の一方の前記長辺部と他方の前記長辺部との別に各個独立にそれぞれの長さ方向に交差させ、かつ、隣接相互間を非導通として配列させた多数条のパターン層を双方でジグザグ状となる配置関係で設け、対応関係にある前記絶縁内層体を覆うべく対向配置させた際の一側基板体の前記パターン層と他側基板体の前記パターン層とは、前記長辺部からはみ出る部位にある対面部位相互をめっきスルーホールを介して各別に導通させることで、一方の前記長辺部には1本の巻線と同等な一側励磁部を、他方の前記長辺部には1本の巻線と同等な他側励磁部をそれぞれ各別に形成するとともに、前記各一側励磁部相互を直列に、前記各他側励磁部相互を直列に各別に接続することで、一方の前記長辺部には長い磁路長を確保できる1本の巻線と同等な一側励磁部を、他方の前記長辺部には長い磁路長を確保できる1本の巻線と同等な他側励磁部をそれぞれ各別に形成して前記励磁ユニットとしたことを最も主要な特徴とする。

【0012】

【0013】

また、第2の発明（電流センサ）は、分割された一側大径コア片部と他側大径コア片部とを相互に對向配置させてなる大径磁気コア体と、該大径磁気コア体側と同心状に分割配置された一側小径コア片部と他側小径コア片部とを前記大径磁気コア体の内側に寄り添うように相互を對向配置させてなる小径磁気コア体と、これら大径磁気コア体と小径磁気コア体との間の各分割周方向に沿わせ、かつ、ギャップを介して各別に配置されるフラックスゲート素子とで構成され、該フラックスゲート素子は、短辺部と長辺部とを矩形枠枠状に連続させてなる磁性薄片体と、該磁性薄片体より大きな面サイズの矩形形状を呈して前記磁性薄片体の両面に各別に覆設される一対の絶縁内層体と、これら絶縁内層体の各外表面に對面合致させて各別に覆設される一側基板体と他側基板体とで構成される励磁ユニットと、前記一側基板体と前記他側基板体との各外表面に對面合致させて各別に覆設される一対の絶縁外層体とを少なくとも備えてその長さ方向への撓曲を可能に一体的に形成するとともに、一側基板体と他側基板体とのそれぞれの前記外表面には、磁性薄片体の一方の前記長辺部と他方の前記長辺部との別に各個独立にそれぞれの長さ方向に交差させ、かつ、隣接相互間を非導通として配列させた多数条のパターン層を双方でジグザグ状となる配置関係で設け、前記励磁ユニットは、対応関係にある前記絶縁内層体を覆うべく対向配置させた際の一側基板体の前記パターン層と他側基板体の前記パターン層とを前記長辺部からはみ出る部位にある対面部位相互をめっきスルーホールを介して各別に導通させることで、一方の前記長辺部には1本の巻線と同等な一側励磁部を、他方の前記長辺部には1本

10

20

30

40

50

の巻線と同等な他側励磁部をそれぞれ形成してなり、前記一側大径コア片部と前記一側小径コア片部とを含む外周から前記他側大径コア片部と前記他側小径コア片部とを含む外周へと巻回された電気信号検出のための巻線を具備させたことを最も主要な特徴とする。

【0014】

第2の発明において大径磁気コア体と小径磁気コア体との間の各分割周方向に各別に介在配置される前記フラックスゲート素子には、前記各磁性薄片体部位が相互に重なり合うように折曲させて配置した請求項1に記載のフラックスゲート素子を用いることもできる。また、前記フラックスゲート素子は、前記大径磁気コア体と前記小径磁気コア体との対向面における少なくともいずれか一方の側の面に形成された凹陥部内に配置して各分割周方向に各別に介在配置させておくこともできる。

10

【0015】

さらに、第3の発明（電流センサ）は、略環状を呈する大径磁気コア体と、該大径磁気コア体と同心状に配置される小径磁気コア体と、これら大径磁気コア体と小径磁気コア体との間に周回配置されるフラックスゲート素子とで構成され、該フラックスゲート素子は、短辺部と長辺部とを矩形囲枠状に連続させてなる磁性薄片体と、該磁性薄片体より大きな面サイズの矩形形状を呈して前記磁性薄片体の両面に各別に覆設される一対の絶縁内層体と、これら絶縁内層体の各外表面に対面合致させて各別に覆設される一側基板体と他側基板体とで構成される励磁ユニットと、前記一側基板体と前記他側基板体との各外表面に対面合致させて各別に覆設される一対の絶縁外層体とを少なくとも備えてその長さ方向への撓曲を可能に一体的に形成するとともに、一側基板体と他側基板体とのそれぞれの前記外表面には、磁性薄片体の一方の前記長辺部と他方の前記長辺部との別に各個独立にそれぞれの長さ方向に交差させ、かつ、隣接相互間を非導通として配列させた多数条のパターン層を双方でジグザグ状となる配置関係で設け、前記励磁ユニットは、対応関係にある前記絶縁内層体を覆うべく対向配置させた際の一側基板体の前記パターン層と他側基板体の前記パターン層とを前記長辺部からはみ出る部位にある対面部位相互をめっきスルーホールを介して各別に導通させることで、一方の前記長辺部には1本の巻線と同等な一側励磁部を、他方の前記長辺部には1本の巻線と同等な他側励磁部をそれぞれ形成してなり、前記一側大径コア片部と前記一側小径コア片部とを含む外周から前記他側大径コア片部と前記他側小径コア片部とを含む外周へと巻回された電気信号検出のための巻線を具備させたことを最も主要な特徴とする。

20

【0016】

第3の発明において前記大径磁気コア体と前記小径磁気コア体との間に介在配置される前記フラックスゲート素子は、2周以上の連続周回が自在な長さを有するフラックスゲート素子を用いることもできる。また、前記フラックスゲート素子は、前記大径磁気コア体と前記小径磁気コア体との対向面における少なくともいずれか一方の側の面に形成された凹陥部内に収容させて周回配置するものであってもよい。

30

【発明の効果】

【0017】

本発明のうち、第1の発明によれば、フラックスゲート素子の全体を小さな面サイズのもとでその厚さを薄くして形成することができるので、電流センサを構成する大径磁気コア体と小径磁気コア体との間にギャップを小さくして配置することができる。このため、これを組み込むことにより簡単な構造のもとで外部磁界の影響を受けずらい電流センサを得ることができる。

40

【0018】

また、励磁ユニットは、複数個の磁性薄片体部位の別に各別に形成することができるのと、各磁性薄片体部位が相互に重なり合うように折曲することで磁路長を長く確保することができ、その結果、磁界検出感度をより上げることができる。

【0019】

一方、第2の発明によれば、各フラックスゲート素子の内側に一側小径コア片部または他側小径コア片部が配置されているので、過大磁界やギャップなどの感度変化に対しての

50

悪影響を大幅に低減することができる。また、大径磁気コア体と小径磁気コア体とが過電流により帯磁したとしても、電流センサ自体はその測定時に閉止されており帯磁した磁束が漏れないようすることができるので、出力にオフセット信号が現れることはない。さらに、外部磁界との関係では、各フラックスゲート素子の外側に一側大径コア片部または他側大径コア片部が配置されているので、これらにより好ましいシールド効果を得ることができる。さらにまた、一側大径コア片部および他側大径コア片部は、ゼロフラックス動作の負帰還動作に入るため、高周波大電流の発熱を抑えたり、周波数特性の悪化を改善することができる。しかも、電流センサには、薄いフラックスゲート素子が用いられているので、ギャップをそれだけ小さくして外部磁界の影響を受けずらくすることができる。

## 【0020】

10

第2の発明において励磁ユニットを複数個の磁性薄片体部位の別に各別に形成して相互に重なり合うように折曲させてその磁路長を実質的に長くしたフラックスゲート素子を大径磁気コア体と小径磁気コア体との間の各分割周方向に各別に介在配置するならば、それだけ磁界検出感度の優れた電流センサを得ることができる。

## 【0021】

しかも、前記フラックスゲート素子を凹陥部内に配置して各分割周方向に各別に介在配置させた場合には、大径磁気コア体と小径磁気コア体との間にギャップをなくして外部磁界の影響をより受けずらくすることができる。

## 【0022】

20

また、第3の発明によれば、周回させたフラックスゲート素子の内側に小径磁気コア体が配置されているので、過大磁界やギャップなどの感度変化に対しての悪影響を大幅に低減することができる。また、大径磁気コア体と小径磁気コア体とが過電流になって帯磁したとしても、電流センサ自体は常に完全閉止されて帯磁した磁束が漏れることはないので、出力にオフセット信号が現れることはない。さらに、外部磁界との関係では、フラックスゲート素子の外側に大径磁気コア体が配置されているので、好ましいシールド効果を得ることができる。さらにまた、大径磁気コア体は、ゼロフラックス動作の負帰還動作に入るため、高周波大電流の発熱を抑えたり、周波数特性の悪化を改善することができる。しかも、電流センサには、薄いフラックスゲート素子が用いられているので、ギャップをそれだけ小さくして外部磁界の影響を受けずらくすることができる。

## 【0023】

30

第3の発明においては、フラックスゲート素子を大径磁気コア体と小径磁気コア体との間に2周以上の連続周回を自在にして介在配置させることにより、磁路長を長く確保することができる、それだけ磁界検出感度の優れた電流センサを得ることができる。

## 【0024】

しかも、フラックスゲート素子を凹陥部内に配置した場合には、大径磁気コア体と小径磁気コア体との間にギャップをなくして外部磁界の影響を受けずらくすることができる。

## 【発明を実施するための最良の形態】

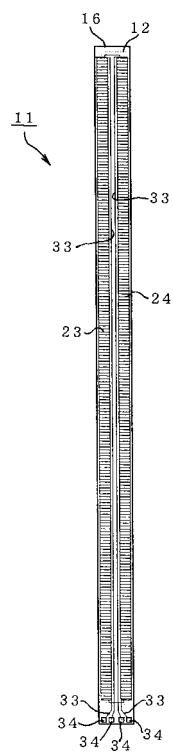

## 【0025】

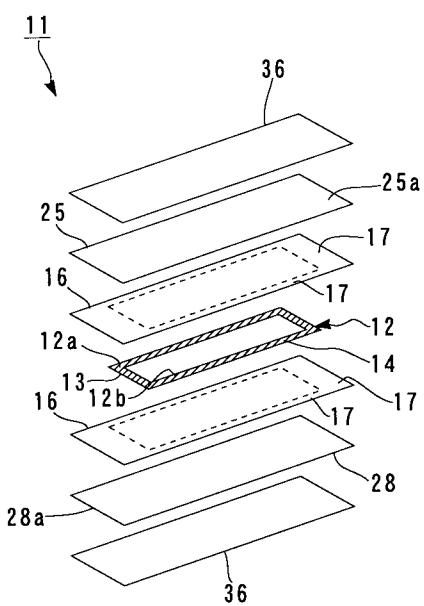

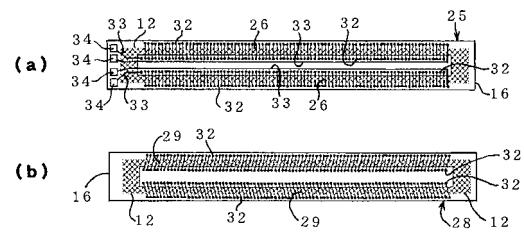

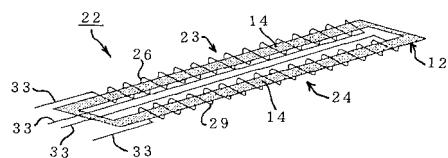

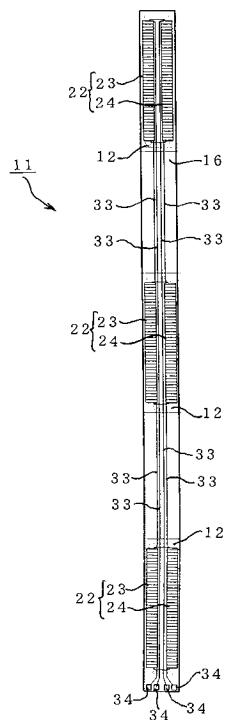

図1は、本発明に係る電流センサに組み込まれるフラックスゲート素子の構造例を示す分解斜視図であり、図2は、上記フラックスゲート素子を構成している励磁ユニットの一例を示すものであり、そのうちの(a)は一側基板体をその外表面(図では上面)側からみた説明図を、(b)は他側基板体をその外表面(図では下面)側からみた説明図をそれぞれ示す。また、図3は、励磁ユニットが備える一側励磁部と他側励磁部とを等価構造的に模式化して示す斜視図である。

40

## 【0026】

これらの図によれば、フラックスゲート素子11は、矩形枠状に連続させてなる磁性薄片体12と、該磁性薄片体12の両面に各別に覆設される一対の絶縁内層体16,16と、これら絶縁内層体16の各外表面16aに各別に覆設される一側基板体25と他側基板体28とで構成される励磁ユニット22と、一側基板体25の外表面25aと他側基板体28の外表面28aとに各別に覆設される一対の絶縁外層体36,36とを少なくとも

50

備えて、フレキシブル基板のような可撓性を有して長さ方向への撓曲を可能に一体的に形成されている。

【0027】

このうち、磁性薄片体12は、パーマロイヤアモルファスを含む強磁性材料を用いて例えれば厚さが20μm程度で、幅が10mmの適宜長さの短辺部12aと、該短辺部12aの長さよりも長い長辺部12bとを矩形囲枠状に連続させることで一体形成されている。

【0028】

絶縁合成樹脂層などからなる絶縁内層体16は、磁性薄片体12よりも大きな面サイズ(図1中の破線による囲繞領域が磁性薄片体12の位置する部位)のもとで該磁性薄片体12の両面に各別に覆設される。具体的には、磁性薄片体12の外周縁側からの突出部17を有して磁性薄片体12の面サイズよりもやや大きな略相似形を呈する面サイズのもとで全面的に覆うことができる適宜の厚さの矩形形状を呈して形成されている。

【0029】

励磁ユニット22を構成している一側基板体25と他側基板体28とのそれぞれは、絶縁内層体16と略対面合致する面サイズが付与されて形成されている。

【0030】

このうち、図1では上方に位置している絶縁内層体16の外表面16a側に配置される一側基板体25は、磁性薄片体12の一方の長辺部14と他方の長辺部14との別に、各個独立にそれぞれの長さ方向と略直交するように交差させ、かつ、図2(a)に示すように隣接相互間を非導通として配列させた多数本の線状のパターン層26を備えている。この場合、各パターン層26は、長辺部14の幅に対しその両方向にてはみ出る長さを有して一側基板体25の外表面25a側に形成されている。

【0031】

また、図1では下方に位置している絶縁内層体16の外表面16a側に配置される他側基板体28は、磁性薄片体12の一方の長辺部14と他方の長辺部14との別に、各個独立にそれぞれの長さ方向に斜行して交差させ、かつ、図2(b)に示すように隣接相互間を非導通として配列させた多数本の線状のパターン層29を備えている。この場合、各パターン層29は、長辺部14の幅に対しその両方向にてはみ出る長さを有して他側基板体28の外表面28a側に形成されている。

【0032】

このため、磁性薄片体12を間に挟んで対面合致させた一対の絶縁内層体16,16に対し、一側基板体25と他側基板体28とをそれぞれの外表面16a側に略対面合致させて覆設した際には、各パターン層26と各パターン層29とを、その一端側相互と他端側相互とが対向する位置関係でジグザグ状に対面配置することになる。

【0033】

したがって、一側基板体25側の各パターン層26と他側基板体28側の各パターン層29とは、長辺部14を除く部位に位置することになる一端側相互と他端側相互とに絶縁内層体16をも含めた貫通孔を設け、これらの各貫通孔にめっき処理を施してめっきスルーホール32を形成することで、図3に模式的に示されているように一方の長辺部14には1本の巻線を巻回したと同等の一側励磁部23が、他方の長辺部14にも1本の巻線を巻回したと同等の他側励磁部24が形成され、これら一側励磁部23と他側励磁部24とで励磁ユニット22が形成されることになる。図2(a)中の符号33は、接続用パターン層を、34は、各接続用パターン層33と各別に接続されるランド層をそれぞれ示す。

【0034】

一方、絶縁合成樹脂層などからなる絶縁外層体36は、一側基板体25の外表面25aと他側基板体28の外表面28aとに各別に覆設される。すなわち、絶縁外層体36は、一側基板体25と他側基板体28とのそれぞれに各別に対面合致する面サイズと適宜の厚さとが付与されでそれぞれに覆設されている。

【0035】

このような構造を備えて形成されるフラックスゲート素子11は、これが配設される後

10

20

30

40

50

述する磁気センサ 4 1 または 5 1 との関係で、例えば図 6 に示すように形成したり、図 1 1 に示すようにして形成することもできる。

【 0 0 3 6 】

すなわち、第 1 の発明である図 6 に示すフラックスゲート素子 1 1 は、図 1 に示す短辺部 1 3 と長辺部 1 4 と同様に矩形枠枠状に連続させてなる複数個、図 6 の例では 3 個の磁性薄片体 1 2 と、その長さ方向に一定間隔をおいて配置される各磁性薄片体 1 2 に対しその全体をやや上回る程度で覆うに足りる面サイズの矩形形状を呈してそれぞれの両面を一体に覆う一対の絶縁内層体 1 6 , 1 6 と、これら絶縁内層体 1 6 の各外表面に対面合致させて各別に覆設できる長さの図 1 に示すと同様な一側基板体 2 5 と他側基板体 2 8 とで構成される 3 個の励磁ユニット 2 2 と、図 1 に示す一側基板体 2 5 と他側基板体 2 8 との各外表面 2 5 a , 2 8 a と同様にして対面合致させて各別に覆設できる長さの図 1 に示すと同様な一対の絶縁外層体 3 6 , 3 6 とを備えて各磁性薄片体 1 2 部位の別での折曲を可能に一体的に形成されている。しかも、磁性薄片体 1 2 のそれぞれと各別に対面する位置にある一側基板体 2 5 と他側基板体 2 8 とのそれぞれの外表面 2 5 a , 2 8 a には、図 2 に示すような磁性薄片体 1 2 の一方の長辺部 1 4 と他方の長辺部 1 4 との別に各個独立にそれぞれの長さ方向に交差させ、かつ、隣接相互間を非導通として配列させた多数条のパターン層 2 6 , 2 9 を双方でジグザグ状となる配置関係で設けられている。そして、対応関係にある絶縁内層体 1 6 を覆うべく対向配置させた際の一側基板体 2 5 のパターン層 2 6 と他側基板体 2 8 のパターン層 2 9 とは、長辺部 1 4 からはみ出る部位にある対面部位相互をめっきスルーホール 3 2 を介して各別に導通させることで、一方の長辺部 1 4 には 1 本の巻線と同等な一側励磁部 2 3 が、他方の長辺部 1 4 には 1 本の巻線と同等な他側励磁部 2 4 がそれぞれ各別に形成されている。また、各一側励磁部 2 3 , 2 3 相互は一方の接続用パターン層 3 3 を介して直列に、各他側励磁部 2 4 , 2 4 相互は他方の接続用パターン層 3 3 を介して直列に各別に接続させることで、一方の長辺部 1 4 には磁路長を長く確保できる 1 本の巻線と同等な一側励磁部 2 3 を、他方の前記長辺部にも磁路長を長く確保できる 1 本の巻線と同等な他側励磁部 2 4 をそれぞれ各別に形成して励磁ユニット 2 2 が形成されている。このため、フラックスゲート素子 1 1 は、励磁ユニット 2 2 を図 7 に示すように 3 層に重ね合わせた状態となるように折曲して使用することができる。なお、図 6 中の符号 3 4 は、各接続用パターン層 3 3 と各別に接続されているランド層を示す。

【 0 0 3 7 】

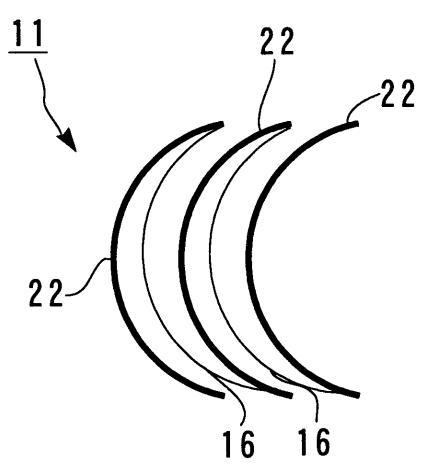

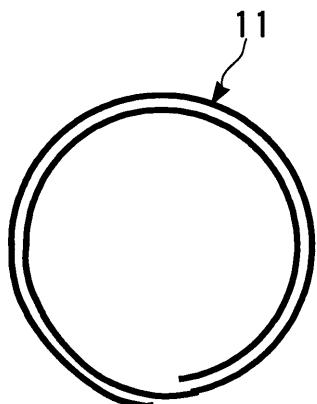

また、図 1 に示すフラックスゲート素子の変形例である図 1 1 に示すフラックスゲート素子 1 1 は、1 周分に満たない程度から 1 周分程度、あるいは図 1 2 に示すように 1 周分以上を連続周回させることができる長さが付与されて形成されており、必要によっては 3 周分以上を連続周回させることができる長さを付与して形成することもできる。

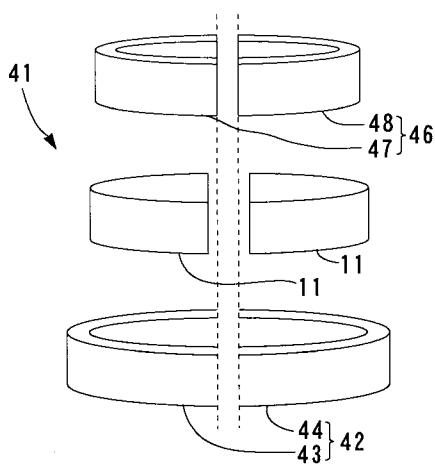

【 0 0 3 8 】

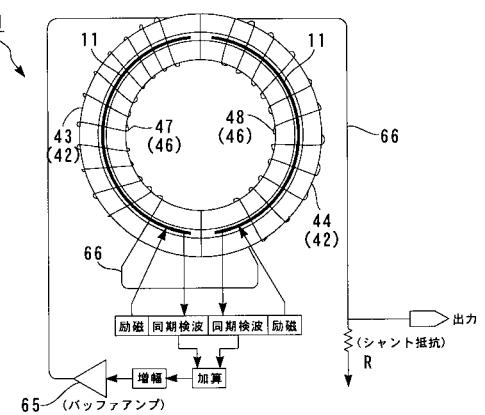

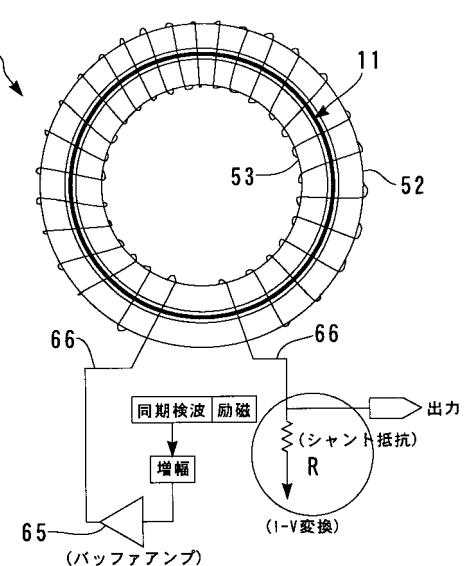

図 4 は、図 1 に示すフラックスゲート素子 1 1 を組み込んで形成される第 2 の発明に係る電流センサの構造例を示す分解斜視図であり、図 5 は、その組立て後の状態を示した説明図である。

【 0 0 3 9 】

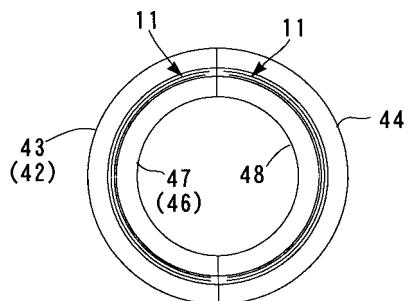

すなわち、分割型の電流センサ 4 1 は、大径磁気コア体 4 2 と、該大径磁気コア体 4 2 の内側に配置される小径磁気コア体 4 6 と、これら大径磁気コア体 4 2 と小径磁気コア体 4 6 との間に介在配置されるフラックスゲート素子 1 1 とを少なくとも備えて構成されている。

【 0 0 4 0 】

このうち、大径磁気コア体 4 2 は、半円状に 2 分割された一側大径コア片部 4 3 と他側大径コア片部 4 4 とを略円環状を呈するように対向配置することで構成されている。

【 0 0 4 1 】

小径磁気コア体 4 6 は、大径磁気コア体 4 2 側と同心状となって 2 分割された一側小径コア片部 4 7 と他側小径コア片部 4 8 とを大径磁気コア体 4 2 の内側に寄り添うように対

10

20

30

40

50

向配置することで構成されている。なお、導体位置による感度変化に対しての悪影響を大幅に低減する観点からは、一側小径コア片部47および他側小径コア片部48を厚くして形成しておくのが好ましい。

【0042】

この場合、フラックスゲート素子11は、大径磁気コア体42と小径磁気コア体46との間の各分割周方向、つまり一側大径コア片部43と一側小径コア片部47との間と、他側大径コア片部44と他側小径コア片部48との間とのそれぞれに各別に介在配置されている。

【0043】

また、大径磁気コア体42とフラックスゲート素子11と小径磁気コア体46とをこのようにして配置した後は、少なくとも各フラックスゲート素子11が位置している外周に例えれば1本のエナメル銅線を巻回してなる巻線として引き出された帰還巻線66を介して電気信号の検出を自在とすることで電流センサ41を構成している。

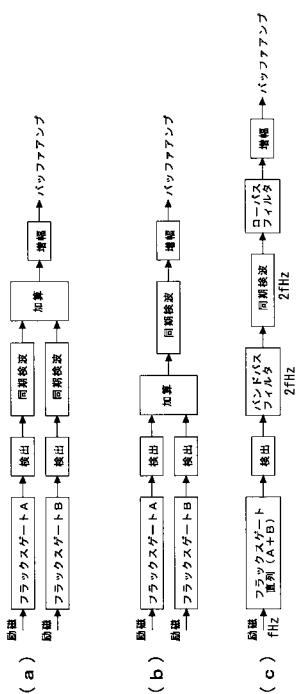

【0044】

この場合における電気信号の検出は、図8(a),(b),(c)に示す方法により行われる。このうち、図8(a)に示す方法によれば、図5からも明らかなように、活線状態にある被測定導体(図示せず)により一方のフラックスゲート素子11と他方のフラックスゲート素子11とのそれぞれが励磁され、これらを同期検波した後、加算回路、增幅回路およびバッファアンプ65を経て帰還巻線66に流し、その平衡時における電流をシャント抵抗Rを介して電圧値として出力されることで得られるようになっている。また、図8(b)に示す方法によれば、活線状態にある被測定導体(図示せず)により一方のフラックスゲート素子11と他方のフラックスゲート素子11とのそれぞれが励磁され、これらを加算回路を経て同期検波した後、増幅回路およびバッファアンプ65を経て帰還巻線66に流し、その平衡時における電流をシャント抵抗Rを介して電圧値として出力されることで得られるようになっている。さらに、図8(c)に示す方法によれば、一方のフラックスゲート素子11と他方のフラックスゲート素子11とを直列に接続して検出し、これを2fHzのバンドパスフィルタを介在させてノイズ成分となるfHz成分を除去した上で同期検波した後、ローパスフィルタを通して最終ノイズを除去し、増幅回路およびバッファアンプ65を経て帰還巻線66に流し、その平衡時における電流をシャント抵抗Rを介して電圧値として出力されることで得られるようになっている。

【0045】

図9は、第2の発明に係る電流センサの他例についての大径磁気コア体42とフラックスゲート素子11と小径磁気コア体46との配置関係を示す説明図である。

【0046】

この他例においては、大径磁気コア体42と小径磁気コア体46との構成は上記一例と同じであるものの、例えば図6に示すフラックスゲート素子11を図7に示すように折曲して各励磁ユニット22を重ね合わせた状態で配置されることになる。

【0047】

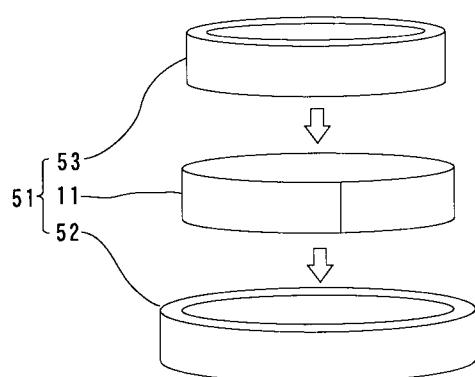

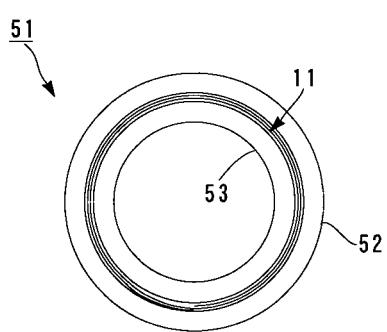

一方、図10は、図1に示すフラックスゲート素子11を組み込んで形成される第3の発明に係る電流センサの構造例を示す分解斜視図であり、図11は、その組立て後の状態を示した説明図である。

【0048】

すなわち、貫通型の電流センサ51は、略円環状を呈する大径磁気コア体51と、該大径磁気コア体51と同心状に配置される小径磁気コア体53と、これら大径磁気コア体51と小径磁気コア体53との間に1周にて周回配置されるフラックスゲート素子11とを少なくとも備えて構成されている。

【0049】

また、大径磁気コア体52とフラックスゲート素子11と小径磁気コア体53とをこのようにして配置した後は、その外周に例えれば1本のエナメル銅線を巻回してなる巻線として引き出された帰還巻線67を介して電気信号の検出を自在とすることで電流センサ51

10

20

30

40

50

を構成している。

【0050】

この場合における電気信号の検出は、活線状態とした被測定導体（図示せず）によりフラックスゲート素子11が励磁され、これを同期検波した後に増幅回路およびバッファアンプ65を経て帰還巻線67に流し、その平衡時における電流をシャント抵抗Rを介して電圧値として出力することで得られるようになっている。

【0051】

図14は、第3の発明に係る電流センサの他例についての大径磁気コア体52とフラックスゲート素子11と小径磁気コア体53との配置関係を示す説明図である。

【0052】

この他例においては、大径磁気コア体52と小径磁気コア体53との構成は上記一例と同じであるものの、例えば図12に示す長さのフラックスゲート素子11を図13に示すように2周分を連続周回させた上で、大径磁気コア体52と小径磁気コア体53との間に介在配置させてある。なお、この場合におけるフラックスゲート素子11は、3周分以上を連続周回させて配置させておくこともできる。

【0053】

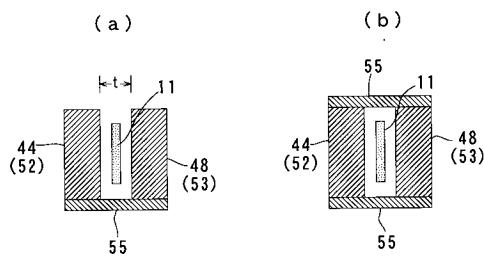

図15は、第2発明および第3発明においての大径磁気コア体42または52と、小径磁気コア体46または53との間に介在配置されるフラックスゲート素子11の配置構造を模式的に示す拡大断面図である。

【0054】

この場合、図5に示す分割型の電流センサ41にあっては、フラックスゲート素子11を、図5に示す電流センサ41における一側大径コア片部43と一側小径コア片部47との間、および他側大径コア片部44と他側小径コア片部48との間のそれぞれに介在配置する。このようにフラックスゲート素子11を介在配置させた後は、図5に示す電流センサ41における一側大径コア片部43と一側小径コア片部47との一側面および他側大径コア片部44と他側小径コア片部48とにおける一側面を、板状の磁性材55で例えば図15(a)に示すように片面シールドとして覆ったり、一側大径コア片部43と一側小径コア片部47との両側面および他側大径コア片部44と他側小径コア片部48とにおける両側面を、図15(b)に示すように両面シールドとして覆うのが好ましい。

【0055】

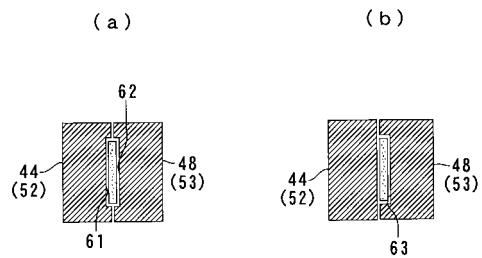

また、フラックスゲート素子11は、一側大径コア片部43と一側小径コア片部47との対向面の双方に、および他側大径コア片部44と他側小径コア片部48との対向面の双方にそれぞれ設けられている凹陥部61, 62を介して図16(a)に示すように介在配置させることができる。さらに、フラックスゲート素子11は、いずれか一方の側の面にのみ、例えば他側小径コア片部48の側にのみ設けられている凹陥部63を介して図16(b)に示すように介在配置させることもできる。

【0056】

このような配置パターンは、図11に示す貫通型の電流センサ51においても同様に行なうことができる。すなわち、フラックスゲート素子11は、大径磁気コア体52と小径磁気コア体53との間に介在配置させた上で、これら大径磁気コア体52と小径磁気コア体53との一側面を板状の磁性材55で例えば図15(a)に示すように片面シールドとして覆ったり、図15(b)に示すように両面シールドとして覆うのが好ましい。また、フラックスゲート素子11は、大径磁気コア体52と小径磁気コア体53との対向面の双方に設けられている凹陥部61, 62を介して図16(a)に示すように介在配置させることができる。さらに、フラックスゲート素子11は、いずれか一方の側の面にのみ、例えば小径磁気コア体53の側にのみ設けられている凹陥部63を介して図16(b)に示すように介在配置させることもできる。

【0057】

次に、上記構成からなる本発明において電流センサに組み込まれる図1～図3に示すフラックスゲート素子の作用・効果について、まず説明すれば、フラックスゲート素子11

10

20

30

40

50

の全体は、磁性薄片体 12 と、該磁性薄片体 12 の両面に各別に覆設される一対の絶縁内層体 16, 16 と、これら絶縁内層体 16 の各外表面 16a に各別に覆設される一側基板体 25 と他側基板体 28 とで構成される励磁ユニット 22 と、一側基板体 25 の外表面 25a と他側基板体 16 の外表面 28a とに各別に覆設される一対の絶縁外層体 36, 36 とを少なくとも備え、コンパクトで非常に薄い薄片状となって一体的に形成されている。

#### 【0058】

このため、ラックスゲート素子 11 は、例えば図 15(a) に示すように介在配置させる場合であっても、電流センサ 41 または 51 を構成する大径磁気コア体 42 または 52 と小径磁気コア体 46 または 53 との間にギャップ  $t$  を小さくして配置することができるようになる。このため、ラックスゲート素子 11 は、これを組み込むことにより簡単な構造のもとで外部磁界の影響を受けずらい電流センサ 41 または 51 を得ることが可能となる。

#### 【0059】

また、第 1 の発明であるラックスゲート素子 11 は、励磁ユニット 22 を図 6 に示すように一定間隔を介在させた複数の磁性薄片体 12 部位(図示例では 3 力所)に各別に形成することができる。このため、第 1 の発明であるラックスゲート素子 11 によれば、図 7 に示すように折曲して重ね合わせて上で、図 9 に示すように大径磁気コア体 42 と小径磁気コア体 46 との間に各別に配置することにより、磁路長を長く確保することができる。したがって、これを組み込んだ電流センサ 41 の磁界検出感度を上げることができる。

10

20

#### 【0060】

さらに、図 1 に示すラックスゲート素子 11 は、図 12 に示すようにその長さを所望する長さとなるように長くして形成することもでき、このように長く形成する場合には、図 13 に示すように例えば 2 周分を連続周回させることができるので、大径磁気コア体 52 と小径磁気コア体 53 との間に図 14 に示すようにして介在配置させてその全体磁路長を長く確保することができる。したがって、これを組み込んだ電流センサ 51 の磁界検出感度を上げることができる。

#### 【0061】

一方、図 1 に示すラックスゲート素子 11 を組み込んでなる第 2 の発明に係る電流センサの作用・効果を図 4 および図 5 に示す例に基づいて説明すれば、開閉可能な電流センサ 41 は、大径磁気コア体 42 と、該大径磁気コア体 42 の内側に配置される小径磁気コア体 46 と、これら大径磁気コア体 42 と小径磁気コア体 46 との間に介在配置されるラックスゲート素子 11 とを含んで構成されている。

30

#### 【0062】

この場合、大径磁気コア体 42 は、2 分割された一側大径コア片部 43 と他側大径コア片部 44 とを対向配置し、小径磁気コア体 46 は、同様に 2 分割された一側小径コア片部 47 と他側小径コア片部 48 とを大径磁気コア体 42 の内側に寄り添うように対向配置されている。

#### 【0063】

しかも、ラックスゲート素子 11 は、一側大径コア片部 43 と一側小径コア片部 47 との間と、他側大径コア片部 44 と他側小径コア片部 48 との間とに各別に介在配置されている。

40

#### 【0064】

このように、電流センサ 41 は、各ラックスゲート素子 11 の内側に一側小径コア片部 47 または他側小径コア片部 48 を配置して形成されているので、これら一側小径コア片部 47 および他側小径コア片部 48 により過大磁界やギャップなどの感度変化に対しての悪影響を大幅に低減することができる。

#### 【0065】

また、帯磁の問題については、大径磁気コア体 42 と小径磁気コア体 46 とが過電流により帯磁したとしても、電流センサ 41 自体はその測定時に閉止されており帯磁した磁束

50

が漏れないようすることができるので、出力にオフセット信号が現れることはない。

【0066】

さらに、外部磁界に対しては、各フラックスゲート素子11の外側に一側大径コア片部43または他側大径コア片部44が配置されているので、これら一側大径コア片部43および他側大径コア片部44により好ましいシールド効果を得ることができる。

【0067】

さらにまた、一側大径コア片部43および他側大径コア片部44は、ゼロフラックス動作の負帰還動作に入るため、高周波大電流の発熱を抑えたり、周波数特性の悪化を改善することができる。

【0068】

しかも、電流センサ41は、フレキシブル基板のようにその厚さが極めて薄く形成されているフラックスゲート素子11を大径磁気コア体42側と小径磁気コア体46側との間に図15(a)に示すように介在配置させてあるので、大径磁気コア体42側と小径磁気コア体46側との間のギャップtをそれだけ小さくすることができる。

【0069】

また、図6に示すように3カ所に励磁ユニット22を備え、これを図7に示すように折曲して重ね合わせた上で、図9に示すように大径磁気コア体42と小径磁気コア体46との間にフラックスゲート素子11として各別に配置して電流センサ41を形成している場合には、それだけ磁路長を長く確保して磁界検出感度を上げることができる。

【0070】

図1に示すフラックスゲート素子11を組み込んでなる第3発明に係る電流センサの作用・効果を図10および図11に示す例に基づいて説明すれば、貫通型の電流センサ51は、円環状の大径磁気コア体52と、該大径磁気コア体42の内側に配置される円環状の小径磁気コア体53と、これら大径磁気コア体52と小径磁気コア体53との間に介在配置されるフラックスゲート素子11とを含んで構成されている。

【0071】

この場合、フラックスゲート素子11は、大径磁気コア体52と小径磁気コア体53との間に、その周方向に向けて1周させることで介在配置されている。

【0072】

このように、電流センサ51は、1周させたフラックスゲート素子11の内側に小径磁気コア体53を配置して形成されているので、過大磁界やギャップなどの感度変化に対しての悪影響を大幅に低減することができる。

【0073】

また、帯磁の問題については、大径磁気コア体52と小径磁気コア体53とが過電流になって帯磁したとしても、電流センサ51自体は常に完全閉止されて帯磁した磁束が漏れることはないので、出力にオフセット信号が現れることはない。

【0074】

さらに、外部磁界に対しては、フラックスゲート素子11の外側に大径磁気コア体52が配置されているので、該大径磁気コア体52により好ましいシールド効果を得ることができる。

【0075】

さらにまた、大径磁気コア体52は、ゼロフラックス動作の負帰還動作に入るため、高周波大電流の発熱を抑えたり、周波数特性の悪化を改善することができる。

【0076】

しかも、電流センサ51は、その厚さが極めて薄く形成されているフラックスゲート素子11を大径磁気コア体52と小径磁気コア体53との間に介在配置させてあるので、大径磁気コア体52と小径磁気コア体53との間のギャップtを図15(a)に示すように小さくすることができる。

【0077】

また、図12に示すように十分に長く形成されたフラックスゲート素子11を図13に

10

20

30

40

50

示すように2周となるように周回させた上で、図14に示すように大径磁気コア体52と小径磁気コア体53との間に配置して電流センサ51を形成している場合には、それだけ磁路長を長く確保して磁界検出感度を上げることができる。

【0078】

さらに、第2の発明に係る磁気センサ41および第3の発明に係る磁気センサ51において、図16(a)に示す凹陥部61, 62や図16(b)に示す凹陥部63が形成されている場合には、ギャップをより小さくしてラックスゲート素子11を介在配置させることができるので、外部磁界の影響をより受けずらい構造を付与して磁気センサ41または51を形成することができる。

【0079】

なお、図1および図6に示すラックスゲート素子11は、印刷回路基板製造技術により形成されるものである。その一例をサブトラクティブ法による場合につき説明すれば、絶縁基板に銅箔を貼り、必要部位に耐エッチング性インクをスクリーン印刷法で塗布した後、導体パターン部分のみを露光して現像を行い、露光した部分にのみ耐エッチング性被膜を残した上でエッチングを行い、最後にエッティングレジストを剥離・除去して導体パターン(本発明ではパターン層25, 29、接続パターン層33およびランド層34)を露出させることで行われる。

【0080】

また、めっきスルーホール32は、対向位置にある個々のパターン層25, 29相互を貫通させた通孔を設け、該通孔に例えば無電解銅めっき処理を施すなどして形成することができる。

【図面の簡単な説明】

【0081】

【図1】本発明に係る電流センサに組み込まれるラックスゲート素子の構造例を示す分解斜視図。

【図2】図1においてラックスゲート素子を構成している励磁ユニットの一例を示すものであり、そのうちの(a)は一側基板体をその外表面側からみた説明図を、(b)は他側基板体をその外表面側からみた説明図をそれぞれ示す。

【図3】励磁ユニットが備える一側励磁部と他側励磁部とを等価構造的に模式化して示す斜視図。

【図4】図1のラックスゲート素子を組み込んで形成される第2の発明に係る電流センサの構造例を示す分解斜視図。

【図5】図4の電流センサの組立て後の状態を示す説明図。

【図6】第1の発明に係るラックスゲート素子の構成例を示す説明図。

【図7】図6に示すラックスゲート素子を折曲した状態で示す説明図。

【図8】図5に示す電流センサを用いた電気信号の検出手法を(a)～(c)として場合分けして示す説明図。

【図9】第1の発明に係るラックスゲート素子を組み込んだ電流センサを示す説明図。

【図10】図1のラックスゲート素子を組み込んで形成される第3の発明に係る電流センサの構造例を示す分解斜視図。

【図11】図10の電流センサの組立て後の状態を示す説明図。

【図12】図1に示すラックスゲート素子の変形例を示す説明図。

【図13】図12に示すラックスゲート素子を2周回させた状態で示す説明図。

【図14】図12に示すラックスゲート素子を2周回させて組み込んだ電流センサを示す説明図。

【図15】第2発明および第3発明においての大径磁気コア体と小径磁気コア体との間に介在配置されるラックスゲート素子の配置例を(a), (b)として場合分けして示す要部拡大断面図。

【図16】第2発明および第3発明においての大径磁気コア体と小径磁気コア体との間に介在配置されるラックスゲート素子の配置他例を(a), (b)としてパターン別に示す説明図。

10

20

30

40

50

す要部拡大断面図。

【図17】特許文献1に示されている分割型の電流センサと被測定導体との関係を示す説明図。

【符号の説明】

【0082】

|                 |            |    |

|-----------------|------------|----|

| 1 1             | フラックスゲート素子 |    |

| 1 2             | 磁性薄片体      |    |

| 1 2 a           | 外周縁        |    |

| 1 2 b           | 内周縁        |    |

| 1 3             | 短辺部        | 10 |

| 1 4             | 長辺部        |    |

| 1 6             | 絶縁内層体      |    |

| 1 6 a           | 外表面        |    |

| 1 7             | 突出部        |    |

| 2 2             | 励磁ユニット     |    |

| 2 3             | 一側励磁部      |    |

| 2 4             | 他側励磁部      |    |

| 2 5             | 一側基板体      |    |

| 2 5 a           | 外表面        |    |

| 2 6             | パターン層      | 20 |

| 2 8             | 他側基板体      |    |

| 2 9             | パターン層      |    |

| 3 2             | めっきスルーホール  |    |

| 3 3             | 接続用パターン層   |    |

| 3 4             | ランド層       |    |

| 3 6             | 絶縁外層体      |    |

| 4 1             | 電流センサ      |    |

| 4 2             | 大径磁気コア体    |    |

| 4 3             | 一側大径コア片部   |    |

| 4 4             | 他側大径コア片部   | 30 |

| 4 6             | 小径磁気コア体    |    |

| 4 7             | 一側小径コア片部   |    |

| 4 8             | 他側小径コア片部   |    |

| 5 1             | 電流センサ      |    |

| 5 2             | 大径磁気コア体    |    |

| 5 3             | 小径磁気コア体    |    |

| 5 5             | 磁性材        |    |

| 6 1 , 6 2 , 6 3 | 凹陥部        |    |

| 6 5             | バッファアンプ    |    |

| 6 6             | 帰還巻線       | 40 |

| t               | ギャップ       |    |

| R               | シャント抵抗     |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図 1 0】

【図 1 1】

【図 1 2】

【図 1 3】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

審査官 中村 和正

(56)参考文献 特開2003-270310 (JP, A)

特開2001-099654 (JP, A)

特開2004-257904 (JP, A)

特開2004-257905 (JP, A)

特開2004-138558 (JP, A)

特開2001-264360 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G01R 33/04

G01R 15/20

H01F 38/28